# (19)대한민국특허청(KR) (12) 등록특허공보(B1)

(51) . Int. Cl. H01L 21/28 (2006.01) (45) 공고일자

2007년08월02일

(11) 등록번호 (24) 등록일자 10-0744689 2007년07월25일

(21) 출원번호 10-2006-0017208 (22) 출원일자

2006년02월22일

(65) 공개번호 (43) 공개일자

심사청구일자

2006년02월22일

(73) 특허권자 주식회사 하이닉스반도체

경기 이천시 부발읍 아미리 산136-1

(72) 발명자

아태항

서울 관악구 봉천11동 1707 은천아파트 103-306

이영호

경기 성남시 분당구 분당동 샛별마을우방아파트 301-802

(74) 대리인

특허법인 신성

(56) 선행기술조사문헌 KR100422906 B1

KR1020010036018 A

KR100538815 B1

심사관: 양희용

전체 청구항 수 : 총 17 항

### (54) 반도체 소자의 콘택 형성 방법

#### (57) 요약

본 발명은 반도체 소자의 콘택 저항을 감소시키는데 적합한 반도체 소자의 콘택 형성 방법을 제공하기 위한 것으로, 이를 위한 본 발명의 콘택 형성 방법은 반도체 기판 상부에 콘택홀을 형성하는 단계; 상기 콘택홀이 형성된 반도체 기판에 대해 전처리를 실시하는 단계; 상기 전처리가 실시된 콘택홀을 포함하는 상기 반도체 기판의 표면을 따라 실리콘막을 형성하는 단계; 상기 실리콘막의 표면을 따라 메탈막을 형성하는 단계; 상기 실리콘막과 상기 메탈막을 반응시켜 상기 콘택홀의 반 도체 기판에 접촉되는 메탈 실리사이드를 형성하는 단계; 및 상기 메탈 실리사이드 상에 상기 콘택홀을 채우는 콘택충을 형성하는 단계를 포함하며 이에 따라 본 발명은 반도체 소자의 콘택 저항 감소, 신뢰성 및 수율을 향상시킬 수 있는 효과가 있다.

#### 대표도

도 2c

특허청구의 범위

## 청구항 1.

삭제

## 청구항 2.

반도체 기판 상부에 콘택홀을 형성하는 단계;

상기 콘택홀이 형성된 반도체 기판에 대해 전처리를 실시하는 단계;

상기 전처리가 실시된 콘택홀을 포함하는 상기 반도체 기판의 표면을 따라 실리콘막을 형성하는 단계;

상기 실리콘막의 표면을 따라 메탈막을 형성하는 단계;

상기 실리콘막과 상기 메탈막을 반응시켜 상기 콘택홀의 반도체 기판에 접촉되는 메탈 실리사이드를 형성하는 단계; 및

상기 메탈 실리사이드 상에 상기 콘택홀을 채우는 콘택층을 형성하는 단계

를 포함하는 반도체 소자의 콘택 형성 방법.

# 청구항 3.

제2항에 있어서,

상기 전처리는,

습식 세정 또는 건식 세정으로 진행하는 반도체 소자의 콘택 형성 방법.

### 청구항 4.

제3항에 있어서,

상기 습식 세정은,

황산 용액 $(H_2SO_4)$ 과 과산화수소 $(H_2O_2)$  용액을 혼합한 용액 또는 불산 관련 용액(HF 또는 BOE)을 사용하며,  $20\sim150$   $^{\circ}$ 의 온도 분위기에서 진행하는 반도체 소자의 콘택 형성 방법.

### 청구항 5.

제3항에 있어서,

상기 건식 세정은,

수소, 질소, NF $_3$ , HF 및 NH $_3$  으로 이루어진 그룹에서 선택된 어느 한 물질 또는 두 물질을 사용하여 플라즈마 공정 또는 열공정을 사용하며, 상기 플라즈마 공정은  $100\sim400$ ℃ 의 온도 분위기, 상기 열공정은  $750\sim850$ ℃ 의 온도 분위기에서 진행하는 반도체 소자의 콘택 형성 방법.

### 청구항 6.

제2항에 있어서,

상기 실리콘막은 고상에피택시(SPE) 공정에 의해 성장시키고.

상기 고상에피택시공정에 의해 성장시키는 증착방식은 LPCVD, VLPCVD, PECVD, UHVCVD, RTCVD, APCVD 및 MBE 로 이루어진 그룹에서 선택된 어느 한 장비를 사용하는 반도체 소자의 콘택 형성 방법.

## 청구항 7.

제2항에 있어서,

상기 실리콘막은,

비정질 실리콘막, 폴리실리콘막 및 에피택셜 실리콘막으로 이루어진 그룹에서 선택된 어느 한 물질을 사용하는 반도체 소자의 콘택 형성 방법.

## 청구항 8.

제6항에 있어서,

상기 실리콘막은,

실리콘저마늄막을 사용하는 반도체 소자의 콘택 형성 방법.

## 청구항 9.

제6항에 있어서,

상기 실리콘막은 450~750℃ 의 온도 분위기에서 100~400Å 두께로 형성하는 반도체 소자의 콘택 형성 방법.

## 청구항 10.

제7항에 있어서,

상기 실리콘막 내에는 도펀트로서 인, 비소 또는 보론이 도핑된 반도체 소자의 콘택 형성 방법.

## 청구항 11.

제10항에 있어서,

상기 도펀트의 도핑농도는 1E19~1E22 atoms/cm<sup>3</sup> 을 갖는 반도체 소자의 콘택 형성 방법.

## 청구항 12.

제2항에 있어서,

상기 실리콘막 상에 메탈막을 형성하는 단계는,

상기 메탈막 형성 전, 전처리를 진행하는 단계를 더 포함하는 반도체 소자의 콘택 형성 방법.

### 청구항 13.

제12항에 있어서,

상기 전처리는

습식 세정 또는 건식 세정을 진행하는 반도체 소자의 콘택 형성 방법.

#### 청구항 14.

제2항에 있어서,

상기 메탈막은,

Ti, Co, Ni, 및 Mo 으로 이루어진 그룹에서 선택된 어느 한 물질로 형성하는 반도체 소자의 콘택 형성 방법.

## 청구항 15.

제2항에 있어서,

상기 실리콘막과 상기 메탈막을 반응시켜 상기 반도체 기판 상에 메탈 실리사이드를 형성하는 단계는,

700~850℃ 의 온도 분위기에서 열처리를 진행하는 반도체 소자의 콘택 형성 방법.

### 청구항 16.

제2항에 있어서,

상기 콘택층은, 상기 콘택층 하부에 베리어 메탈을 포함하는 반도체 소자의 콘택 형성 방법.

## 청구항 17.

제16항에 있어서,

상기 베리어 메탈은 TiN 또는 WN으로 형성하는 반도체 소자의 콘택 형성 방법.

### 청구항 18.

제2항에 있어서,

상기 콘택층은,

비저항이 매우 낮은 텅스텐막과 같은 메탈로 형성하는 반도체 소자의 콘택 형성 방법.

#### 명세서

# 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 반도체 제조 기술에 관한 것으로, 특히 반도체 소자의 콘택(Contact)형성 방법에 관한 것이다.

반도체 소자가 점점 고집적화됨에 따라 콘택 면적도 감소하므로 콘택 저항(Contact Resistance)이 증가하고, 동작 전류 (Operation Current)가 감소하면서 반도체 소자의 동작 속도, 신뢰성(Reliability) 및 tWR(Write Recovery Time)의 열화 (Degradation)에 따른 수율(Yield)까지도 영향을 받고 있다. 따라서, 향후 차세대 반도체 소자에서는 소자의 슈링크 (Shrink)에 따라 콘택 면적이 감소할지라도 콘택 저항을 낮게 유지하는 것이 매우 중요한 항목이 되었다.

이런 상황에서 소자의 콘택 저항을 낮추고 동작 전류를 향상시키고자, 실리콘 기판 정션 부분의 도펀트 농도를 높이거나 현재 사용중인 콘택 폴리실리콘 내의 도펀트인 인(Phosphorus) 농도를 높이는 방법을 사용 중이나, 이는 오히려 소자의 채널 도펀트(Dopant) 재분포(Redistribution)와 이에 따른 숏 채널 이펙트(Short Channel Effect; SCE) 증가, 채널/정션 인접 영역에서의 전기장(Electric Field)의 증가에 따른 누설 전류(Leakage Current)를 증가시키고, 결국은 가장 중요한 소자의 리프레시(tREF, refresh, data retention time) 특성을 저하시킬 수 있다. 또한, 폴리실리콘 증착시 대기압 하에서 퍼니스에 로딩(Loading)될 때 존재하는 산소 농도(대략 수십 ppm)에 의해 폴리실리콘과 실리콘 기판 사이 계면에 미세 산화막이 형성됨으로써 이것이 소자의 콘택 저항을 증가시키는 한 원인이 되고 있다. 이런 면에서 폴리실리콘으로는 앞으로 반도체 소자가 계속 고집적화되는 추세에 따라 콘택 저항을 낮추고 소자의 특성을 향상시키기 어려운 상황이다.

상기와 같은 문제점들을 극복하고 소자의 콘택 저항을 낮출 뿐만 아니라 소자 특성을 향상시키고자 개발되고 있는 것이 에 피택셜 실리콘(Epitaxial Si)이다. 그 중에서도 SEG(Selective Epitaxial Growth)가 콘택 저항을 감소시키는데 유용하여 국내외적으로 활발히 연구 개발되고 있지만, 이 공정은 고온 공정(∼850℃)이므로 반도체 소자의 셀 접합(Cell Junction) 특성을 매우 열화시키므로 현재 저온 SEG 개발에 많은 노력을 기울이고 있다.

그러나, 기존 반도체 소자 제조 공정에 그대로 적용하면서 저온 증착이 가능하고 저농도의 도핑 농도로도 충분히 기존 폴리실리콘의 문제점을 극복할 수 있는 것으로서 고상에피택시(Solid Phase Epitaxy; 고상에피택시) 공정이 있다.

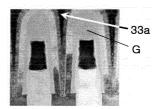

도 1a 및 도 1b는 종래 기술에 따른 반도체 소자의 콘택을 나타낸 TEM 사진이다.

도 1a를 참조하면, 반도체 기판(11) 상에 게이트 절연막, 게이트 전도막 및 게이트 하드마스크가 차례로 적충된 게이트 패턴(G)이 형성되고, 게이트 패턴(G)의 양측벽에는 스페이서(12)가 형성되며, 랜딩 플러그 콘택(Landing Plug Contact) 공정을 진행하기 위하여 게이트 패턴(G)을 포함하는 전면에 충간절연막(도시하지 않음)을 중착하고, 평탄화 공정을 진행하여 게이트 패턴(G) 사이를 모두 매립한 후, 콘택이 형성될 영역을 오픈하기 위한 랜딩 플러그 콘택 식각 공정을 진행하여 인접하는 게이트 패턴(G) 사이의 콘택 예정 영역 즉, 랜딩 콘택홀(13)을 확보한다.

이어서, 랜딩 콘택홀(13)의 내부에 고상에피택시 공정을 진행하게 되는데, 그 증착 조건은 SiH<sub>4</sub>/PH<sub>3</sub> 가스를 사용하여

500~650℃ 범위의 온도에서 인(Phosphorus) 도핑은 비교적 낮은 1.5E19~1.5E20 atoms/cm³의 농도를 갖는 비정질 실리콘(Amorphous Si, 15)을 형성하는 것이다. 도 1a에서 보듯이, 이와 같이 초기 증착된 비정질 실리콘을 형성하였을 때 실리콘 기판 바로 위에는 에치택셜 실리콘(14)이 형성될 뿐만 아니라 에피택셜 실리콘 상에는 비정질 실리콘(15)이 동시에 형성되는 이중층을 이루게 된다.

도 1b를 참조하면, 초기 증착된 고상에피택시는 이어서 열공정(550∼650℃의 온도 범위, 10시간∼30분, 질소분위기)을 진행하면, 반도체 기판(11) 계면에서부터 에피택셜 실리콘(14)이 랜딩 콘택홀(13)을 채우면서 상부 영역까지 재성장하게된다. 결국, 저온 공정인 고상에피택시에 의해 소자의 콘택을 형성할 때, 기존의 폴리실리콘 보다 더 낮은 콘택 저항을 얻을 수 있다.

그러나 상술한 바와 같이, 소자가 더욱 초고집적화 됨에 따라 에피택셜 실리콘도 실리콘이란 물질 자체의 비저항 측면에서 한계가 있는데 이는 에피택셜 실리콘에 인을 1E20 atoms/cm<sup>3</sup> 이상으로 도핑하더라도 약  $1.4m\Omega$ -cm 의 비저항 값을 보이고 있고, 이보다 더 낮추기가 어려운 상황이다.

따라서, 향후 70mm 테크놀로지 이하의 초고집적 차세대 반도체 소자에서는 에피택셜 실리콘을 적용시의 콘택 저항보다 낮은 콘택 저항을 필요로 할 수 있으며 아울러 소자의 신뢰성 및 수율도 충분히 확보할 필요가 있다.

#### 발명이 이루고자 하는 기술적 과제

본 발명은 상기한 종래 기술의 문제점을 해결하기 위해 제안된 것으로, 반도체 소자의 콘택 저항을 감소시키는데 적합한 반도체 소자의 콘택 형성 방법을 제공하는데 그 목적이 있다.

#### 발명의 구성

상기 목적을 달성하기 위한 특징적인 본 발명은 반도체 기판 상부에 콘택홀을 형성하는 단계; 상기 콘택홀이 형성된 반도체 기판에 대해 전처리를 실시하는 단계; 상기 전처리가 실시된 콘택홀을 포함하는 상기 반도체 기판의 표면을 따라 실리콘막을 형성하는 단계; 상기 실리콘막의 표면을 따라 메탈막을 형성하는 단계; 상기 실리콘막과 상기 메탈막을 반응시켜 상기 콘택홀의 반도체 기판에 접촉되는 메탈 실리사이드를 형성하는 단계; 및 상기 메탈 실리사이드 상에 상기 콘택홀을 채우는 콘택층을 형성하는 단계를 포함한다.

이하, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 본 발명의 기술적 사상을 용이하게 실시할 수 있을 정도로 상세히 설명하기 위하여, 본 발명의 가장 바람직한 실시예를 첨부 도면을 참조하여 설명하기로 한다.

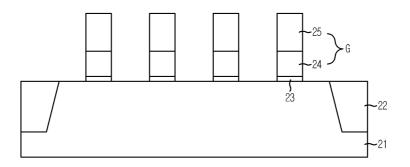

도 2a 내지 도 2e는 본 발명의 일실시예에 따른 반도체 소자의 콘택 형성 방법을 도시한 단면도이다.

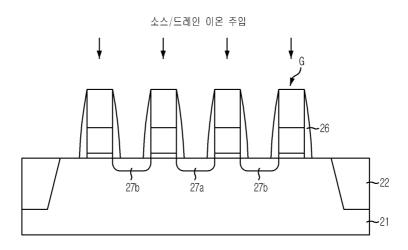

도 2a에 도시된 바와 같이, 반도체 기판(21)의 소정 영역에 STI(Shallow Trench Isolation) 공정을 실시하여 소자분리막 (22)을 형성한다. 이어서, 반도체 기판(21) 상에 게이트 절연막(23), 게이트 전도막(24) 및 게이트 하드마스크(25)의 순서로 증착된 다수의 게이트 패턴(G)을 형성한다. 이 때, 게이트 절연막(23)은 열산화, 건식 산화 또는 습식 산화를 실시하여 형성되고, 게이트 전도막(24)은 폴리실리콘막, 텅스텐막, 텅스텐실리사이드의 그룹에서 선택된 어느 한 물질을 단독 또는 이들의 적층 구조를 사용한다.

도 2b에 도시된 바와 같이, 게이트 패턴(G)을 포함하는 반도체 기판(21) 상에 절연막을 증착한 후 전면 식각하여 게이트 패턴(G)의 양측벽에 접하는 게이트 스페이서(26)를 형성한다. 게이트 하드마스크(25)와 게이트 스페이서(26)는 후속 층간 절연막과 식각 선택비를 갖는 물질을 이용하되, 층간절연막이 실리콘 산화막인 경우 실리콘 질화막을 사용한다.

그런 다음, 게이트 패턴(G) 및 게이트 스페이서(26) 또는 별도의 이온주입마스크를 포함하는 이온 주입 베리어를 이용한 이온 주입 공정을 진행하여 게이트 패턴(G)의 양측 하부 반도체 기판(21) 내부에 소스/드레인 영역(27a, 27b)을 형성한다.

소스/드레인 영역(27a, 27b)에서 비트라인접합영역(27a)은 후속 비트라인이 콘택될 영역이고, 스토리지노드접합영역 (27b)은 스토리지노드가 콘택될 영역이며, 소스/드레인 영역(27a, 27b)은 바람직하게 N형 불순물이 도핑된다. 예컨대, N형 불순물로는 인(P) 또는 아세닉(As)를 사용한다.

위와 같이, 비트라인접합영역(27a)과 스토리지노드접합영역(27b)이 게이트 패턴(G) 사이에 형성되어 하나의 셀 트랜지스터가 완성되고, 비트라인접합영역(27a)과 스토리지노드접합영역(27b) 사이의 활성 영역 아래에서 채널 영역이 정의된다.

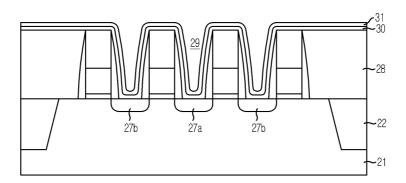

도 2c에 도시된 바와 같이, 반도체 기판(21)의 전면에 충간절연막(28)을 중착한다. 충간절연막(28)은 BPSG, USG, TEOS, PST 또는 BSG 중에서 선택되는 실리콘 산화막계 물질을 이용한다.

다음으로, 게이트 패턴(G)의 상부가 드러날 때까지 충간절연막(28)을 CMP를 통하여 평탄화시킨다. 이어서, 포토/식각 공정 즉, 포토레지스트 도포, 노광 및 현상을 통해 콘택 마스크를 형성한 후 콘택 마스크를 식각 마스크로 충간절연막(28)을 식각하여 랜딩 플러그를 형성하기 위한 랜딩 콘택홀(LPC, 29)을 형성한다.

이 때, 초고집적소자에서는 하부층과의 포토/식각 공정 마진이 부족하므로 층간절연막(28)을 게이트 하드마스크(25) 및 게이트 스페이서(26)와 식각 선택비가 좋은 조건에서 자기정렬콘택식각(Self Align Contact; SAC)을 진행한다. 이에 따라 포토 공정에 의해 노출된 층간절연막(28)인 실리콘 산화막계 물질은 빠른 속도로 식각되지만, 게이트 하드마스크(25) 및 게이트 스페이서(26)인 실리콘 질화막의 식각 속도는 느리므로 게이트 패턴(G)의 상부 또는 측벽의 실리콘 질화막은 어느 정도 보호되면서 반도체 기판(21)의 접합층(27a. 27b)을 노출시킨다.

한편, 충간절연막(28)을 식각하여 형성된 랜딩 콘택홀(29)의 측벽 및 저면에는 유기 오염물(도시하지 않음)이 잔류하며 랜딩 콘택홀(29)이 형성되면서 노출된 접합충(27a, 27b)의 표면에는 자연 산화막이 형성된다. 유기 오염물은 소자의 누설 전류 특성을 저하시키며, 자연 산화막은 콘택 저항을 증가시켜 소자의 전기적 특성을 저하시키는 요인이 된다.

이러한 유기 오염물 및 자연 산화막을 제거하기 위하여, 랜딩 콘택홀(29)을 형성한 후 전처리 공정(Pretreatment)을 진행한다. 전처리 공정은 건식 세정과 습식 세정 모두 진행하거나, 건식 세정만으로 진행할 수 있다. 이와 같은 전처리 공정은 세정을 진행하여 콘택 물질 증착 전, 탄소 성분의 폴리머성 잔류 유기 오염물과 산소 성분의 자연 산화막을 제거하는 공정이다.

습식 세정은, 황산 용액 $(H_2SO_4)$ 과 과산화수소 $(H_2O_2)$  용액을 혼합한 용액 또는 불산 관련 용액(HF 또는 BOE)을 사용하여 후 습식 세정(HF-Last Cleaning)을 실시하며,  $20\sim150$   $^{\circ}$  의 온도 분위기에서 진행한다.

건식 세정은 수소, 질소, NF<sub>3</sub>, HF 및 NH<sub>3</sub> 으로 이루어진 그룹에서 선택된 어느 한 물질을 사용하여 플라즈마 공정 또는 열 공정을 사용하며, 플라즈마 공정은  $100\sim400$ ℃ 의 온도 분위기, 열공정은  $750\sim850$ ℃ 의 온도 분위기에서 진행한다.

전처리 공정을 진행한 후 랜딩 콘택홀(29) 및 충간절연막(28)의 표면 상에 실리콘막(30)을 형성한다. 일예로, 실리콘막(30)은 고상에피택시 공정에 의해 성장시키는데, 반도체 기판(21) 표면에 형성된 초기 증착 상태의 실리콘막(30)은 에피(Epi) 상태와 비정질 상태의 이중층으로 구성된다. 따라서, 랜딩 콘택홀(29)을 포함하는 충간절연막(28)의 표면을 따라 일정한 두께로 형성할 수 있다.

실리콘막(30)을 고상에피택시 공정에 의해 성장시키는 증착 방식은, LPCVD(Low Pressure Chemical Vapor Deposition), VLPCVD(Very Low Pressure Chemical Vapor Deposition), PECVD(Plasma Enhanced Low Pressure Chemical Vapor Deposition), UHVCVD(Ultra High Vacuum Chemical Vapor Deposition), RTCVD(Rapid Thermal Chemical Vapor Deposition), APCVD(Atmosphere Pressure Chemical Vapor Deposition) 및 MBE( Molecular Beam Epitaxy) 로 이루어진 그룹에서 선택된다.

고상에피택시 공정을 이용하여 콘택 물질로 사용하는 비정질 실리콘과 에피 실리콘을 형성하였으나, 고상에피택시 공정에 의해 형성되는 콘택 물질은 실리콘 외에 저마늄(Ge), 실리콘저마늄(SiGe)도 적용가능하다. 또한, 실리콘막(30)은 비정질 실리콘막, 폴리실리콘막 및 에피택셜 실리콘막으로 이루어진 그룹에서 선택된 어느 한 물질을 사용할 수도 있다.

실리콘막(30) 내에는 도펀트로서 인, 비소 또는 보론이 도핑되고, 실리콘막(30)내 도펀트의 도핑 농도는 1E19~1E22 atoms/cm<sup>3</sup> 을 갖는다. 또한, 실리콘막(30)은, 450~750℃ 의 온도 분위기에서 형성하며, 100~400Å 두께를 갖는다.

한편, 실리콘막(30)을 먼저 형성하지 않고, 직접 메탈 물질을 증착하고 이를 메탈 실리사이드로 형성하면, 메탈 물질의 원자 성분이 후속 열공정에 의해 채널 혹은 접합 영역으로까지 확산한 후, 이것이 딥 레벨 금속 오염원(Deep Level Metallic Impurity)으로 작용하여 문턱 전압(Threshold Voltage)을 크게 변동시키고, GOI(Gate Oxide Integrity) 등과 같은 소자의 특성을 심각하게 열화시킨다. 따라서, 랜딩 콘택홀(29) 내부의 반도체 기판(21) 상에 메탈 실리사이드를 형성하여 콘택 저항을 감소시키기 위해서는 실리콘막(30)의 형성이 먼저 진행되어야 한다. 그리고, 메탈 실리사이드를 형성할 때, 특정 메탈 물질과 실리콘막(30)의 소모 비율이 각각 다르므로, 이를 고려하여 실리콘막(30)과 메탈 물질의 두께를 정의한다.

실리콘막(30)을 형성한 후, 메탈 실리사이드를 형성하기 위한 메탈 물질을 증착하기 전 단계로서 습식 또는 건식 세정으로 전처리를 진행한다. 계속해서, 전처리 공정을 진행한 후 랜딩 콘택홀(29)의 내부에 실리사이드를 형성하기 위한 메탈물질로서 Ti막(31)을 증착한다. 한편, 실리사이드를 형성하기 위한 메탈물질로 실시예에서는 Ti막(31)을 사용하였으나 Ti막(31) 뿐만 아니라 코 발트(Co), 니켈(Ni) 또는 몰리브덴(Mo)으로 이루어진 그룹에서 선택된 어느 한 물질을 사용할 수 있다.

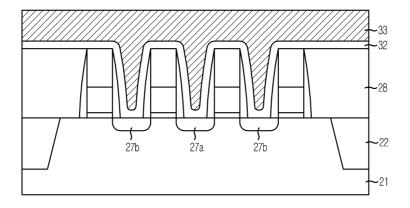

도 2d에 도시된 바와 같이, Ti막(31)을 증착한 후, 700~850℃ 의 온도 분위기에서 열처리를 실시하여 Ti막(31)과 실리콘막(30)을 반응시켜 Ti 실리사이드(32)를 형성한다. Ti 실리사이드(32)를 형성할 때, 실리콘막(30)이 모두 소모됨으로써, 반도체 기판(21) 표면에 Ti 실리사이드(32)가 직접 콘택되게 된다. 여기서, Ti 실리사이드(32)는 Ti막(31)과 실리콘막(30)이 반응하여 형성된 것이므로, Ti 실리사이드(32) 뿐만 아니라 Co 실리사이드, Ni 실리사이드 와 Mo 실리사이드로 형성할수도 있다.

다음으로, Ti 실리사이드(32)를 형성한 후, 랜딩 콘택홀(29)이 모두 채워지지 않을 때에는, 랜딩 콘택홀(29) 내부에 베리어 메탈(Barrier Metal, 도시하지 않음)을 증착하고, 베리어 메탈 상에 비저항이 매우 낮은 텅스덴막(33, 1~20μΩ-cm)을 증착하여 랜딩 콘택홀(29)을 모두 매립한다. 베리어 메탈은 TiN 또는 WN을 사용한다.

한편, 텅스텐막(33) 내에는 도펀트 도핑을 하지 않으므로, 기존 실리콘의 경우에 도펀트의 재분포 또는 확산과 같은 거동이 없으므로, 채널/접합 영역에서의 누설 전류 등을 포함한 접합 특성 열화 문제가 없다. 따라서, 소자의 리프레시 특성에도 거의 영양을 주지 않아 동작 특성이 개선되는 효과가 있다.

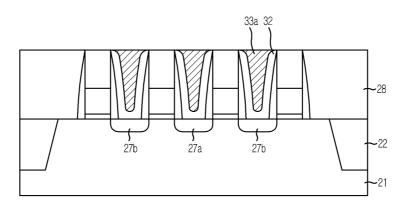

도 2e에 도시된 바와 같이, 화학적·기계적 연마(Chemical Mechanical Polishing; CMP) 또는 전면 식각(Etch Back)을 실시하여 게이트 패턴(G)의 게이트 하드마스크(25)가 노출되는 타겟으로 텅스텐막(33)을 평탄화한다.

평탄화 공정을 마친 후 인접하는 게이트 패턴(G) 사이에는, 반도체 기판(21) 상에 Ti 실리사이드(32)가 직접 콘택되고, Ti 실리사이드(32) 상에는 텅스텐막(33)이 증착된 구조의 랜딩 플러그(33a)가 형성됨을 알 수 있다.

계속해서, 도면에 도시하지는 않았지만 비트라인 및 캐패시터 형성 공정을 진행한다.

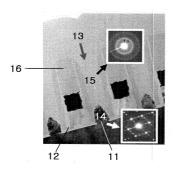

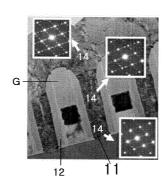

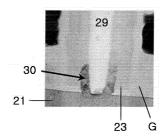

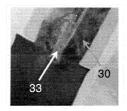

도 3a 내지 도 3c는 본 발명의 실시예를 나타낸 TEM 사진이다.

도 3a를 참조하면, 랜딩 콘택홀(29) 내부에 실리콘막(30)이 형성된 것을 알 수 있고, 도 3b를 참조하면, 실리콘막(30) 상에 베리어 메탈 및 텅스텐막(33)이 형성된 것을 알 수 있다. 자세한 설명은 도 2c를 참조한다.

도 3c를 참조하면, 랜딩 콘택홀(29) 내부에 메탈 실리사이드, 베리어 메탈 및 텅스텐막으로 이루어진 랜딩 플러그(33a)가 형성됨을 알 수 있다. 자세한 설명은 도 2e를 참조한다.

상술한 바와 같이, 초고집적화 되는 반도체 소자의 플러그를 제조할 때, 에피택셜 실리콘을 플러그로 사용했을 때의 콘택저항보다 더 낮은 콘택 저항을 구현하기 위해 랜딩 콘택홀 내부에 실리콘막을 형성하고, 실리콘막 상에 메탈 물질을 증착한 후 열처리 하여 메탈 실리사이드를 형성하고, 메탈 실리사이드 상에 베리어 메탈 및 텅스텐막을 형성함으로써, 콘택 저항을 현저히 감소시킬 수 있다.

또한, 텅스텐막 내부에는 도펀트를 도핑하지 않으므로 후속 열공정시 도펀트 이동에 따른 정션 특성 열화 문제가 발생하지 않아, 소자 특성이 열화되지 않는 효과가 있다.

본 발명의 기술 사상은 상기 바람직한 실시예에 따라 구체적으로 기술되었으나, 상기한 실시예는 그 설명을 위한 것이며 그 제한을 위한 것이 아님을 주의하여야 한다. 또한, 본 발명의 기술 분야의 통상의 전문가라면 본 발명의 기술 사상의 범위 내에서 다양한 실시예가 가능함을 이해할 수 있을 것이다.

### 발명의 효과

상술한 본 발명은 반도체 소자의 콘택 저항 감소, 신뢰성 및 수율을 향상시킬 수 있는 효과가 있다.

## 도면의 간단한 설명

도 1a 및 도 1b는 종래 기술에 따른 반도체 소자의 콘택을 나타낸 TEM 사진.

도 2a 내지 도 2e는 본 발명의 실시예에 따른 반도체 소자의 콘택 형성 방법을 도시한 단면도.

도 3a 내지 도 3c는 본 발명의 실시예를 나타낸 TEM 사진.

\* 도면의 주요 부분에 대한 부호의 설명

21 : 반도체 기판 22 : 소자분리막

23: 게이트 절연막 24: 게이트 전도막

25: 게이트 하드마스크 26: 게이트 스페이서

28 : 층간절연막 29 : 랜딩 콘택홀

30 : 실리콘막 31 : Ti

32 : Ti 실리사이드 33a : 랜딩 플러그

#### 도면

### 도면1a

도면1b

# 도면2a

# 도면2b

# 도면2c

# 도면2d

도면2e

도면3a

도면3b

도면3c