#### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2010-225228 (P2010-225228A)

(43) 公開日 平成22年10月7日(2010.10.7)

(51) Int.Cl.

FI

テーマコード (参考)

G 1 1 C 13/00

(2006.01)

G 1 1 C 13/00

Α

審査請求 未請求 請求項の数 5 OL (全 32 頁)

| (21) 出願番号<br>(22) 出願日 | 特願2009-70862 (P2009-70862)<br>平成21年3月23日 (2009.3.23) | (71) 出願人 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号 |  |

|-----------------------|------------------------------------------------------|----------|---------------------------------------|--|

|                       |                                                      | (74)代理人  | 100092820<br>弁理士 伊丹 勝                 |  |

|                       |                                                      | (74)代理人  | 100106389<br>弁理士 田村 和彦                |  |

|                       |                                                      | (72) 発明者 | 京盤 直哉<br>神奈川県横浜市栄区笠間2-5-1 ST          |  |

|                       |                                                      |          | E ビル内 東芝メモリシステムズ株式会社<br>内             |  |

|                       |                                                      | (72) 発明者 | 前嶋 洋<br>東京都港区芝浦一丁目1番1号 株式会社<br>東芝内    |  |

|                       |                                                      |          |                                       |  |

## (54) 【発明の名称】不揮発性半導体記憶装置

#### (57)【要約】

【課題】低消費電力及び高速アクセスを実現した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、マトリクス状に配置された複数のメモリセル、及びメモリセルに対しデータ書き込みに必要なバイアス電圧を供給するデータ書き込み手段からなる複数のバンクを有し、所定数のパンクに属する所定数のメモリセルからなる複数のページに論理的に分割されたメモリコアと、データ書き込み手段を制御し、ページに対してデータを書き込むページ書き込みを、所定数のメモリセルからなる書き込み単位毎に行う制御手段とを備える。制御手段は、ページ書き込みを、プログラム動作及びベリファイ動作において正常なデータ書き込みが確認できなかった書き込み単位についてのみ、次ステップ以後においてプログラム動作及びベリファイ動作を実行することを特徴とする。

【選択図】図7

#### 【特許請求の範囲】

#### 【請求項1】

マトリクス状に配置された複数のメモリセル、及び前記メモリセルに対しデータ書き込みに必要なバイアス電圧を供給するデータ書き込み手段からなる複数のバンクを有し、所定数の前記バンクに属する所定数の前記メモリセルからなる複数のページに論理的に分割されたメモリコアと、

前記データ書き込み手段を制御し、前記ページに対してデータを書き込むページ書き込みを、所定数の前記メモリセルからなる書き込み単位毎に行う制御手段と

を備え、前記制御手段は、

前記ページ書き込みを、プログラム動作及びベリファイ動作からなるステップの繰り返 しで実行し、

前記ベリファイ動作において正常なデータ書き込みが確認できなかった前記書き込み単位についてのみ、次ステップ以後において前記プログラム動作及びベリファイ動作を実行する

ことを特徴とする不揮発性半導体記憶装置。

#### 【請求項2】

マトリクス状に配置された複数のメモリセル、及び前記メモリセルに対しデータ書き込みに必要なバイアス電圧を供給するデータ書き込み手段からなる複数のバンクを有し、所定数の前記バンクに属する所定数の前記メモリセルからなる複数のページに論理的に分割されたメモリコアと、

前記データ書き込み手段を制御し、前記ページに対してデータを書き込むページ書き込みを、所定数の前記メモリセルからなる書き込み単位毎に行う制御手段と、

書き込みデータを検査し、データ書き込みが不要な前記バンクに属するデータ書き込み 手段に対して、前記バイアス電圧の供給を抑制するバイアス抑制信号を活性化する書き込 みデータ検査手段と

を備え、

前記制御手段は、前記ページ書き込みを、プログラム動作及びベリファイ動作からなるステップの繰り返しで実行し、

所定の前記バンクのデータ書き込み手段は、前記バイアス抑制信号が活性化されている 場合、前記バイアス電圧を供給しない

ことを特徴とする不揮発性半導体記憶装置。

#### 【請求項3】

マトリクス状に配置された複数のメモリセル、及び前記メモリセルに対しデータ書き込みに必要なバイアス電圧を供給するデータ書き込み手段からなる複数のバンクを有し、所定数の前記バンクに属する所定数の前記メモリセルからなる複数のページに論理的に分割されたメモリコアと、

前記データ書き込み手段を制御し、前記ページに対してデータを書き込むページ書き込みを、所定数の前記メモリセルからなる書き込み単位毎に行う制御手段と、

異なる前記書き込み単位に属し、かつ、同一の前記バンクに対する書き込みデータを検査し、データ書き込みが不要なデータであった場合、該当する前記バンクのデータ書き込み手段に対して、前記バイアス電圧の供給を抑制するバイアス抑制信号を活性化する書き込みデータ検査手段と

を備え、

前記制御手段は、前記ページ書き込みを、プログラム動作及びベリファイ動作からなるステップの繰り返しで実行し、

所定の前記バンクのデータ書き込み手段は、前記バイアス抑制信号が活性化されている場合、前記バイアス電圧を供給しない

ことを特徴とする不揮発性半導体記憶装置。

#### 【請求項4】

10

20

30

40

所定の前記書き込み単位において、データ書き込みが不要な前記バンクについては、同 ーバンクに属する他の前記書き込み単位におけるデータ書き込みを実行する ことを特徴とする請求項1~3のいずれか1項記載の不揮発性半導体記憶装置。

#### 【請求項5】

前記プログラム動作及び前記ベリファイ動作は、書き込み単位毎に交互に実行される ことを特徴とする請求項1~4のいずれか1項記載の不揮発性半導体記憶装置。

【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本発明は、不揮発性半導体記憶装置に関し、例えば、可変抵抗素子を用いた電気的書き換え可能な不揮発性半導体記憶装置に関する。

## 【背景技術】

### [0002]

近年、フラッシュメモリの後継候補として、抵抗変化メモリが注目されている。ここで、抵抗変化メモリ装置には、遷移金属酸化物を記録層としてその抵抗値状態を不揮発に記憶する狭義の抵抗変化メモリ(ReRAM:Resistive RAM)の他、カルコゲナイド等を記録層として用いてその結晶状態(導体)と非晶質状態(絶縁体)の抵抗値情報を利用する相変化メモリ(PCRAM:Phase Change RAM)も含むものとする。

#### [00003]

抵抗変化メモリの可変抵抗素子には、2種類の動作モードがあることが知られている。1つは、印加電圧の極性を切り替えることにより、高抵抗状態と低抵抗状態とを設定するもので、これはバイポーラ型といわれる。もう1つは、印加電圧の極性を切り替えることなく、電圧値と電圧印加時間を制御することにより、高抵抗状態と低抵抗状態の設定を可能とするもので、これはユニポーラ型といわれる。

#### [0004]

高密度メモリセルアレイを実現するためには、ユニポーラ型が好ましい。ユニポーラ型の場合、トランジスタを用いることなく、ビット線及びワード線の交差部に可変抵抗素子とダイオード等の整流素子とを重ねるクロスポイント型のメモリセルとすることにより、セルアレイが構成できるからである。更にこのようなメモリセルアレイを三次元的に積層配列することにより、セルアレイ面積を増大させることなく、大容量を実現することが可能になる(特許文献1、非特許文献1参照)。

#### [00005]

特許文献 1 には、半導体基板上にメモリセルアレイが積層された三次元メモリセルアレイ構造を有する相変化メモリ装置が記載されている。この相変化メモリ装置において、選択メモリセルに接続されたビット線を"H"レベルから"L"レベルに制御するとともに、選択メモリセルに接続されたワード線を"L"レベルから"H"レベルに制御することで、選択メモリセルに電流を流している。この電流を検知することで、二値データの書き込み / 読み出しを行っている。

#### [0006]

しかし、メモリセルアレイ上の大部分の非選択メモリセルは、選択メモリセルが接続されたワード線及びビット線と異なるワード線及びビット線に接続されており、選択メモリセルとは逆のバイアス電圧が印加される。その結果、非選択メモリセルでリーク電流が生じることになり、電流消費が増大することになる。

#### [0007]

また、リーク電流との関係から同時選択できるメモリセル数が制限されるため、フラッシュメモリと同様の数kバイト毎のページアクセスを実行するには、チップ内部で、数バイトずつシーケンシャルにアクセスする必要があり、処理速度が遅くなる点も問題となる

#### 【先行技術文献】

#### 【特許文献】

50

10

20

30

[00008]

【特許文献1】特表2005-522045号公報

【非特許文献】

[0009]

【非特許文献 1】M. Johnson, et al., 512-Mb PROM With a Three-Dimensional Array of Diode/Antifuse Memory Cells, IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL.38 NO.1 1, NOVEMBER 2003 p.1920.

【発明の概要】

【発明が解決しようとする課題】

[ 0 0 1 0 ]

本発明は、低消費電力及び高速アクセスを実現した不揮発性半導体記憶装置を提供することを目的とする。

【課題を解決するための手段】

[0011]

本発明の一態様に係る不揮発性半導体記憶装置は、マトリクス状に配置された複数のメモリセル、及び前記メモリセルに対しデータ書き込みに必要なバイアス電圧を供給するデータ書き込み手段からなる複数のパンクを有し、所定数の前記バンクに属する所定数の前記メモリセルからなる複数のページに論理的に分割されたメモリコアと、前記データ書き込み手段を制御し、前記ページに対してデータを書き込むページ書き込みを、所定数の前記メモリセルからなる書き込み単位毎に行う制御手段とを備える。前記制御手段は、前記ページ書き込みを、プログラム動作及びベリファイ動作からなるステップの繰り返しで実行し、前記ベリファイ動作において正常なデータ書き込みが確認できなかった前記書き込み単位についてのみ、次ステップ以後において前記プログラム動作及びベリファイ動作を実行することを特徴とする。

[0012]

本発明の別の一態様に係る不揮発性半導体記憶装置は、マトリクス状に配置された複数のメモリセル、及び前記メモリセルに対しデータ書き込みに必要なバイアス電圧を供給するデータ書き込み手段からなる複数のパンクを有し、所定数の前記バンクに属する所定数の前記メモリセルからなる複数のページに論理的に分割されたメモリコアと、前記データ書き込み手段を制御し、前記ページに対してデータを書き込むページ書き込みを、所定数の前記メモリセルからなる書き込み単位毎に行う制御手段と、書き込みデータを検査し、データ書き込みが不要な前記バンクに属するデータ書き込み手段に対して、前記バイアス電圧の供給を抑制するバイアス抑制信号を活性化する書き込みデータ検査手段とを備える。前記制御手段は、前記ページ書き込みを、プログラム動作及びベリファイ動作からなるステップの繰り返しで実行する。所定の前記バンクのデータ書き込み手段は、前記バイアス和制信号が活性化されている場合、前記バイアス電圧を供給しないことを特徴とする。

[0013]

本発明の更に別の一態様に係る不揮発性半導体記憶装置は、マトリクス状に配置された複数のメモリセル、及び前記メモリセルに対しデータ書き込みに必要なバイアス電圧を供給するデータ書き込み手段からなる複数のバンクを有し、所定数の前記バンクに属する所定数の前記メモリセルからなる複数のページに論理的に分割されたメモリコアと、前記ページに対してデータを書き込みを、明定数の前記メモリセルからなる書き込み単位毎に行う制御手段と、異なっての表さいの前記バンクに対する書き込みデータを検査してデータ書き込みが不要なデータであった場合、該当する前記バンクのデータ書き込みがイアス電圧の供給を抑制するバイアス抑制信号を活性化する書き込みがブログラム動作及びベリファイ動作がある。前記制御手段は、前記ページ書き込みを、プログラム動作及びベリファイ動作があるステップの繰り返しで実行する。所定の前記バイアス電圧を供給しないことを特徴とする。

10

20

30

40

20

30

40

50

#### 【発明の効果】

[0014]

本発明によれば、低消費電力及び高速アクセスを実現した不揮発性半導体記憶装置を提供することができる。

【図面の簡単な説明】

- [0015]

- 【 図 1 】 本 発 明 の 第 1 の 実 施 形 態 に 係 る 不 揮 発 性 メ モ リ の 機 能 ブ ロ ッ ク 図 で あ る 。

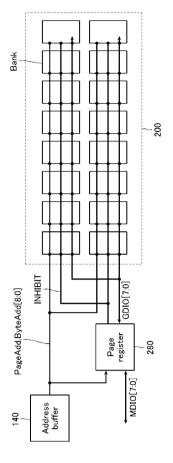

- 【図2】同実施形態に係る不揮発性メモリのメモリコアを示す図である。

- 【図3】同実施形態に係る不揮発性メモリのメモリセルアレイの等価回路図である。

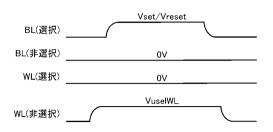

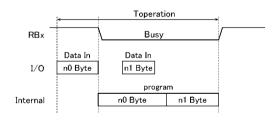

- 【図4】同実施形態に係る不揮発性メモリにおけるデータ書き込み時の各配線に供給される電圧波形図である。

- 【図 5 】同実施形態に係る不揮発性メモリにおける各配線の状態とメモリセルに印加されるバイアス電圧及び対象メモリセル数の関係を示す図である。

- 【図 6 】同実施形態に係る不揮発性メモリにおけるページ書き込み動作を説明する図である。

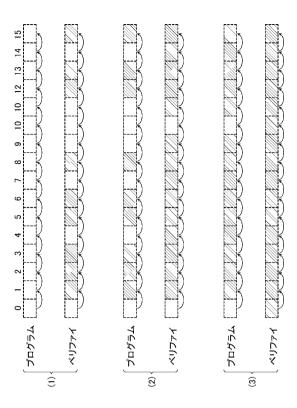

- 【図7】同実施形態に係る不揮発性メモリにおけるページ書き込み動作を説明する図である。

- 【図8】同実施形態に係る不揮発性メモリのアドレスバッファ及びページレジスタとバンクとの信号接続関係を示す図である。

- 【図9】同実施形態に係る不揮発性メモリにおけるカラムアドレスの構成を示す図である

- 【図10】同実施形態に係る不揮発性メモリのバンクの内部構成例を示す図である。

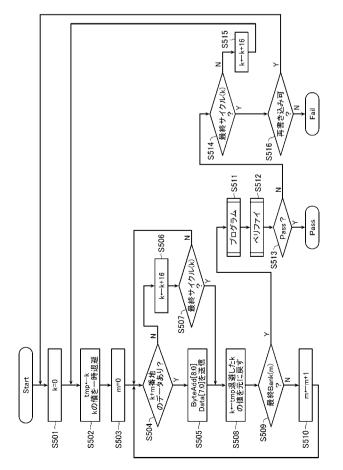

- 【図11】同実施形態に係る不揮発性メモリにおけるページ書き込み動作のフローチャートである。

- 【図 1 2 】同実施形態に係る不揮発性メモリにおける他のページ書き込み動作のフローチャートである。

- 【図13】本発明の第2の実施形態に係る不揮発性メモリにおけるページ書き込み動作を 説明する図である。

- 【図14】同実施形態に係る不揮発性メモリのアドレスバッファ及びページレジスタとバンクとの信号接続関係を示す図である。

- 【図15】同実施形態に係る不揮発性メモリのページレジスタ周辺の内部構成例を示す図である。

- 【図16】同実施形態に係る不揮発性メモリのバンクの内部構成例を示す図である。

- 【図17】同実施形態に係る不揮発性メモリにおけるページ書き込み動作時のタイミング チャートである。

- 【図18】同実施形態に係る不揮発性メモリのバンクの他の内部構成例を示す図である。

- 【 図 1 9 】同実施形態に係る不揮発性メモリにおけるページ書き込み動作時の他のタイミ ングチャートである。

- 【図 2 0 A 】本発明の第 3 の実施形態に係る不揮発性メモリにおけるページ書き込み動作を説明する図である。

- 【 図 2 0 B 】同実施形態に係る不揮発性メモリにおけるページ書き込み動作を説明する図 である。

- 【 図 2 1 】同実施形態に係る不揮発性メモリのページレジスタ周辺の内部構成例を示す図である。

- 【 図 2 2 】 本 発 明 の 第 4 の 実 施 形 態 に 係 る 不 揮 発 性 メ モ リ に お け る ペ ー ジ 書 き 込 み 動 作 を 説 明 す る 図 で あ る 。

- 【図23】同実施形態に係る不揮発性メモリのアドレスバッファ及びページレジスタとバンクとの信号接続関係を示す図である。

- 【図24】同実施形態に係る不揮発性メモリのバンクの内部構成例を示す図である。

- 【図25】同実施形態に係る不揮発性メモリにおけるページ書き込み動作時のタイミング

チャートである。

【図 2 6 】同実施形態に係る不揮発性メモリにおけるページ書き込み動作のフローチャートである。

- 【図27】同実施形態に係る不揮発性メモリにおけるベリファイ動作時のタイミングチャートである。

- 【図28】図27の動作を実現するフローチャートである。

- 【図29】本発明の第5の実施形態に係る不揮発性メモリのページレジスタの論理構成を示す図である。

- 【図30】同実施形態に係る不揮発性メモリにおけるページ書き込み動作のフローチャートである。

- 【図31】同実施形態に係る不揮発性メモリにおけるタスクスケジューリングを示す図である。

- 【図32】NANDフラッシュメモリにおけるページ書き込み動作を説明する図である。

- 【図33】NANDフラッシュメモリにおけるブロック消去動作を説明する図である。

- 【図34】本発明の第1の実施形態に対する比較例におけるページ書き込み動作を説明する図である。

- 【図35】本発明の第2の実施形態に対する比較例におけるページ書き込み動作を説明する図である。

- 【図36】本発明の第4の実施形態に対する比較例におけるページ書き込み動作を説明する図である。

- 【図37】本発明の第5の実施形態に対する比較例におけるタスクスケジューリングを示す図である。

- 【発明を実施するための形態】

- [ 0 0 1 6 ]

以下、図面を参照しながら、本発明に係る不揮発性メモリの実施の形態について詳細に 説明する。

- [0017]

- 「第1の実施形態]

- 図1は、本発明の第1の実施形態に係る不揮発性メモリの機能ブロック図である。

- [0018]

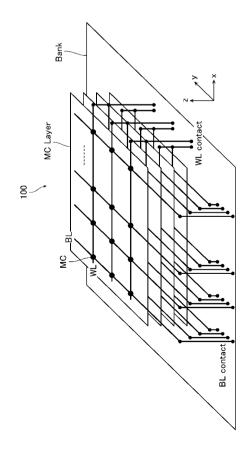

この不揮発性メモリは、メモリコア100を備える。メモリコア100は、図2に示すような三次元的に配置された複数のバンクからなる。これらバンクは、それぞれメモリセルアレイ層を複数積層してなる。メモリセルアレイ層は、それぞれロウ方向(図2の×方向)に延びる複数のワード線WLと、このワード線WLに交差するカラム方向(図2のッ方向)に延びる複数のビット線BLと、これらワード線WL及びビット線BLの各交差部に設けられたメモリセルMCを備える。各メモリセルアレイ層は、それぞれのワード線WL及びビット線BLの一端に設けられたワード線コンタクト及びビット線コンタクトを介して、メモリセルアレイ層の下に配置されたシリコン基板に接続されている。このシリコン基板上には、ビット線BLに接続されるセンスアンプ回路、書き込みデータを一時保持するレジスタ回路、ワード線WL及びビット線BLのバンク内デコーダを含む各論理回路が配置されている。

[0019]

また、不揮発性メモリは、外部とのインタフェースとなるコントロールピン情報及びエノのピン情報を受ける入力バッファ110及び120、コマンドを解釈するコマンドデコーダ130、入力バッファ120から与えられるアドレスを保持するアドレスバッファ140、入力バッファ120から与えられる入力データを保持するデータバッファ150、及びデータを外部に出力する出力バッファ160を備える。さらに、制御手段として、メモリコア100のアクセスを制御するシーケンス制御部170、データを保持し、メモリコア100を制御するアレイ制御部190a、及びページレジスタ180を制御するページレジスタ制御部

10

20

30

40

190bを備える。

#### [0020]

入力バッファ110は、不揮発性メモリのコントロールピン情報に基づいて、I/Oピンのデータの入出力、コマンド/アドレス/データの識別、書き込み保護等の状態の認識を行う。ここで、コントロールピン情報としては、不揮発性メモリの選択を行うチップ・イネーブル信号/CE×、I/Oピン上のコマンド、アドレス、及びデータを不揮発性メモリ内部に取り込むライト・イネーブル信号/WE×、I/Oピンからのデータ出力を許可するリード・イネーブル信号/RE×、コマンドを不揮発性メモリ内部に取り込む際に使用するコマンド・ラッチ・イネーブ信号CLE×、アドレスあるいは入力データを、不揮発性メモリ内部に取り込む際に使用するアドレス・ラッチ・イネーブル信号ALE×、電源投入直後等の不安定期間において記憶データを保護する際に使用するライト・プロテクト信号/WP×がある。

[0021]

入力バッファ120は、双方向バスで構成されたI/Oピンを介し、外部からの入力データを受信する。入力バッファ120は、コントロールピン情報に基づいて入力バッファ110から送信された信号で制御されるが、この信号に応じて、入力データをコマンドデコーダ130、アドレスバッファ140、又はデータバッファ150のいずれかに振り分ける。

[0022]

コマンドデコーダ130は、入力バッファ120から送信されたコマンドを解釈し、必要に応じてシーケンス制御部170を起動させる。

[0023]

アドレスバッファ140は、入力バッファ120から送信されたアドレスを保持し、アレイ制御部190aやページレジスタ180に送信する。最終的に、このアドレスは、メモリセルMCのワード線WL及びビット線BLの選択/非選択の決定に供される。また、アドレスバッファ140は、必要に応じてシーケンス制御部170の指示を受けてアドレス初期化(Preset)やカウントアップ(CountUp)等を実行する。

[0024]

データバッファ150は、入力バッファ120から送信された入力データを一時保持し、この入力データを書き込みデータとして入力データバスDIN及び内部双方向データバスMDIO[7:0]を介してページレジスタ180に送信する。一方、データ出力時には、ページレジスタ180への書き込みデータ送信を停止し、内部双方向データバスMDIO「7:0]における書き込みデータと読み出しデータとの衝突を回避させる。

[0025]

出力バッファ160は、内部双方向データバスMDIO[7:0]及び出力データバスDOUT[7:0]を介してページレジスタ180から送信された読み出しデータを受信し、この読み出しデータを出力データとしてI/Oピンを介して外部に出力する。出力バッファ160は、読み出しデータの他、メモリセルMCのID情報等も出力する。さらに、データ読み出し動作時以外のときには、I/Oピンのドライブを停止させる役割も持つ

[ 0 0 2 6 ]

シーケンス制御部170は、不揮発性メモリのデータ読み出し/書き込み/消去動作の全てを制御する。その制御には、メモリセルアレイに必要なバイアス電圧の供給の指示や、アドレスレジスタ140に対するアドレスの変更指示(CountUp、Preset)等も含まれる。

[ 0 0 2 7 ]

ページレジスタ180は、少なくとも1バイト以上のレジスタから構成される。ページレジスタ180は、共通データバスGDIO[7:0]を介し、メモリセルアレイに書き込む書き込みデータを保持したり、メモリセルアレイから読み出した読み出しデータを保持したりする。

10

20

30

40

20

30

40

50

#### [0028]

アレイ制御部190a及びページレジスタ制御部190bは、シーケンス制御部170からの指示によって起動する。アレイ制御部190aは、メモリセルアレイに対して必要なバイアス電圧の供給をしたり、メモリセルアレイの下部に配置されているセンスアンプ回路の起動やレジスタ回路の動作を制御したりする。一方、ページレジスタ制御部190bは、ページレジスタ180を制御する。

#### [0029]

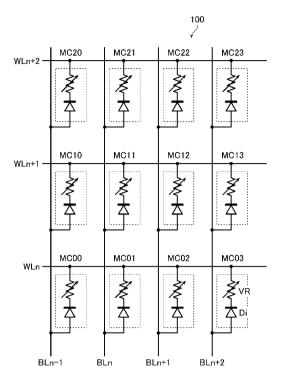

図3は、図2に示すメモリコア100のメモリセルアレイの等価回路図である。

#### [0030]

図3には、3本のワード線WL、4本のビット線BL、及びこれらワード線WL及びビット線BLの各交差部に設けられた12個のメモリセルMCが表されている。各メモリセルMCは、アノードがビット線BLに接続されたダイオードDiと、このダイオードDiのカソード及びワード線WL間に接続された可変抵抗素子VRとの直列接続からなる。なお、メモリセルMCを構成するダイオードDi及び可変抵抗素子VRの配置や極性は、図3の例に限定されるものではない。また、ダイオードDiに代えてスイッチトランジスタを配置することもできる。

#### [0031]

可変抵抗素子VRは、例えば、電極/遷移金属酸化物/電極からなる構造を有するものなどがあり、電圧、電流、熱等の印加条件によって金属酸化物の抵抗値変化をもたらし、その抵抗値の異なる状態を情報として不揮発に記憶する。この可変抵抗素子VRとしては、より具体的には、カルコゲナイド等のように結晶状態と非晶質状態の相転移により抵抗値を変化させるもの(PCRAM)、金属陽イオンを析出させて電極間に架橋(Conducting bridge)を形成したり、析出した金属をイオン化して架橋を破壊したりすることで抵抗値を変化させるもの(CBRAM:Conductive Bridging RAM)、電圧あるいは電流印加により抵抗値が変化するもの(ReRAM)(電極界面に存在する電荷トラップにトラップされた電荷の存在の有無により抵抗変化が起きるものと、酸素欠損等に起因する伝導パスの存在の有無により抵抗変化が起きるものとに大別される)等を用いることができる

#### [0032]

ユニポーラ型のReRAMの場合、メモリセルMCに対するデータの書き込みは、可変抵抗素子VRに、例えば、3.5V(ダイオードDiの電圧降下分を含めると実際には4.5V程度)の電圧、10nA程度の電流を10ns-100ns程度の時間印加する。これによって、可変抵抗素子VRが高抵抗状態から低抵抗状態へと変化する。以下、この可変抵抗素子VRを高抵抗状態から低抵抗状態へ変化させる動作をセット動作という。

#### [0033]

セット動作後の低抵抗状態の可変抵抗素子VRに、例えば、0.8 V(ダイオードDi の電圧降下分を含めると実際には1.8 V程度)の電圧、1  $\mu$  A -10  $\mu$  A 程度の電流を50 n s -2  $\mu$  s 程度の時間印加する。これによって、可変抵抗素子VRが低抵抗状態から高抵抗状態へと変化する。以下、この可変抵抗素子VRを低抵抗状態から高抵抗状態へ変化させる動作をリセット動作という。

## [0034]

図 4 は、図 3 のようなメモリセルアレイに対するセット / リセット動作時の動作波形を示す図である。

## [0035]

通常、全てのワード線WL及びビット線BLは、"L"(0V)となっている。ここで、選択ビット線BLに対し、セット/リセット動作に必要な電圧Vset/Vreset を印加し、非選択ワード線WLに電圧Vset/Vresetよりも高い電圧VuselWLを印加する。この場合、選択ワード線WL及び選択ビット線BL間に接続された選択メモリセルMCのダイオードDiには順方向バイアスがかかり、可変抵抗素子VRの抵抗状態は、低抵抗状態あるいは高抵抗状態に遷移する。一方、非選択メモリセルMCのダイ

20

30

40

50

オードDiには逆方向バイアスがかかり、可変抵抗素子VRの抵抗状態は遷移しない。その結果、選択メモリセルMCだけにデータを書き込むことが可能となる。

[0036]

図5は、セット動作時のワード線WL及びビット線BLの選択/非選択状態と、そのワード線WL及びビット線BLの交差部に接続されたメモリセルMCに印加されるバイアス電圧と、対象となるメモリセルMC数の関係を表している。この図は、ワード線WL及びビット線BLが各1024本、メモリセルMC数が1024×1024=1Mと仮定したものである。図5から分かるように、非選択ワード線WL及び非選択ビット線BLに接続されたメモリセルMCには、上記の通り、逆方向バイアス(0・VuselWL)が印加されており、その対象メモリセルMC数は、1M-(1K+1023)となる。つまり、1個の選択メモリセルMCに対するデータ書き込みを実行したい場合、バンク内の大多数の非選択メモリセルMCに対して逆方向バイアスを印加する必要があり、逆バイアスリークが消費電流増大をもたらす。したがって、これを抑制することで、不揮発性メモリの低消費電力化を図ることができる。

[0037]

次に、本実施形態におけるページ動作を説明するが、その前に、比較例としてNANDフラッシュメモリの書き込み/消去動作について説明する。

[0038]

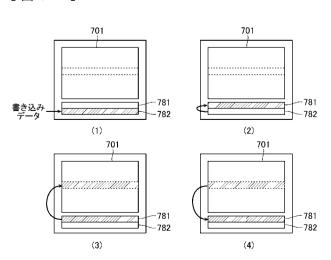

図32は、NANDフラッシュメモリにおける書き込み動作を説明する図である。NANDフラッシュメモリの書き込み動作はページ単位で行われる。

[0039]

先ず、図32(1)において、外部から与えられた入力データは書き込みデータとしてキャッシュレジスタ782に保持される。キャッシュレジスタ782は、少なくともページ長分の記憶領域があり、1ページ分の書き込みデータを保持することができる。

[0040]

続いて、図32(2)において、キャッシュレジスタ782に保持されている1ページ 分の書き込みデータがデータレジスタ781にコピーされる。

[0041]

続いて、図32(3)において、データレジスタ781にコピーされた1ページ分の書き込みデータがメモリセルアレイ701の所定の選択ページに対し一括にプログラムされる。

[ 0 0 4 2 ]

続いて、図32(4)において、選択ページにプログラムされたデータとデータレジスタ781に保持されていた元データとの比較によってベリファイが実行される。ここで、フェールビット数が許容範囲内であった場合、ページ書き込み動作が完了する。一方、フェールビット数が許容範囲外であれば、上記、図32(3)及び(4)に示す処理が、フェールビット数が許容範囲内になるまで繰り返される。

[0043]

一方、消去動作については、複数のページ、例えば、32ページからなるブロック単位で行われる。

[0044]

図33(1)において、メモリセルアレイ701の所定の選択ブロックが一括に消去された後、図33(2)において、この選択ブロックとデータレジスタとの比較によってベリファイが実行される。以降、選択ブロックが消去されるまで図33(1)及び(2)の処理が繰り返される。

[0045]

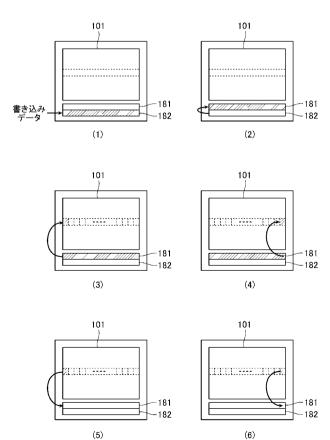

図 6 は、本実施形態に係る不揮発性メモリにおけるページ書き込み動作を説明する図である。

[0046]

先ず、図6(1)において、外部から与えられた入力データが書き込みデータとしてキ

ャッシュレジスタ182に保持される。

#### [0047]

続いて、図 6 ( 2 )において、キャッシュレジスタ 1 8 2 に保持されている書き込みデータがデータレジスタ 1 8 1 にコピーされる。

#### [ 0 0 4 8 ]

続いて、図6(3)~(4)にかけて、データレジスタ181に保持されているデータはいくつかの書き込み単位分のデータに分割され、書き込み単位毎にプログラムされる。例えば、1ページが2kバイト、書き込み単位が128バイトの場合、最大で16回繰り返される。以下、書き込み単位に対するプログラム動作又はベリファイ動作1回を"1サイクル"と呼ぶ。

[0049]

続いて、図6(5)~(6)にかけて、プログラム動作と同様、書き込み単位毎にベリファイが実行される。ここで、1ページ分のベリファイが実行された後、フェールビット数が許容範囲以内であれば、ページ書き込み動作が完了する。一方、フェールビット数が許容範囲外であれば、上記、図6(3)~(6)に示す処理が、フェールビット数が許容範囲内になるまで繰り返される。

[0050]

ページ消去動作については、上記ページ書き込み動作と同様であるため、説明を省略する。

[0051]

次に、図6(3)~(6)のページ書き込み動作について、比較例となるページ書き込み動作とともに詳述する。

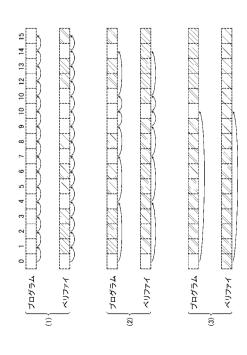

[0052]

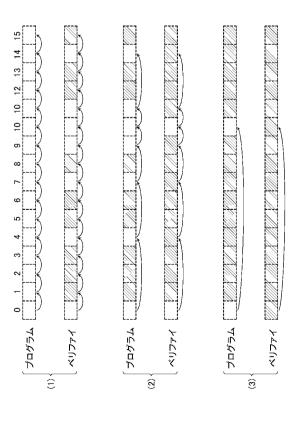

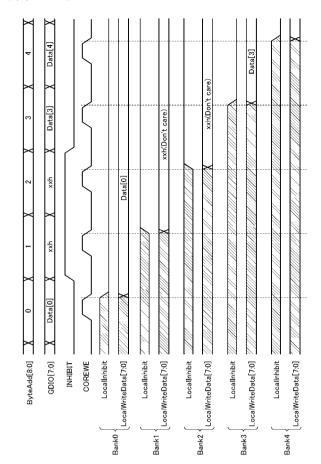

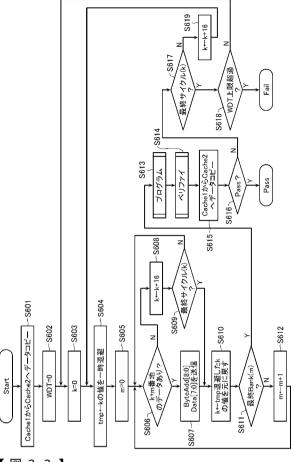

図7及び図34は、本実施形態及び比較例における各ステップのプログラム動作及びベリファイ動作を説明する図である。図中の点線による四角は書き込み単位であり、斜線が施してある四角は、データ書き込みが完了した書き込み単位を表し、斜線が施されていない四角はフェールビットの存在などによりデータ書き込みが完了していない書き込み単位を表している。また、図は、16個の書き込み単位<0>~<15>からなるページに対するページ書き込み動作の場合である。

[0053]

比較例の場合、図34(1)~(3)のとおり、データ書き込みが完了しているか否かに関わらず、全ての書き込み単位に対するシーケンシャルにプログラム動作が実行され、その後、全ての書き込み単位に対するシーケンシャルなベリファイ動作が実行される。したがって、プログラム動作及びベリファイ動作合わせて1ステップあたり32サイクル要し、3ステップの合計では96サイクル要することになる。

[0054]

一方、本実施形態の場合、図7(1)に示す1ステップ目では、比較例と同様に全ての書き込み単位に対するシーケンシャルなプログラム動作が実行され、その後、全ての書き込み単位に対するシーケンシャルなベリファイ動作が実行される。1ステップ目のベリファイでは、書き込み単位<1>、<2>等、9個の書き込み単位がベリファイをパスしたものとする。このステップは、32サイクルの処理時間を要する。

[0055]

続いて、図7(2)に示す2ステップ目では、1ステップ目でベリファイをパスした書き込み単位<1>、<2>等がスキップされながら、プログラム動作とベリファイ動作が実行される。2ステップ目のベリファイでは、新たに書き込み単位<4>、<7>等、5個の書き込み単位がベリファイをパスしたものとする。このステップは、14サイクルの処理時間を要する。

[0056]

続いて、図 7 ( 3 )に示す 3 ステップ目では、 2 ステップ目まででベリファイをパスした書き込み単位 < 1 > 、 < 2 > 等がスキップされながら、プログラム動作とベリファイ動

10

20

30

40

(11)

作が実行される。 3 ステップ目終了時点で、全ての書き込み単位がベリファイをパスした ものとする。このステップは、 4 サイクルの処理時間を要する。

[0057]

以上、本実施形態の場合、1~3ステップを合計50サイクルで処理することができ、 比較例の場合と比べ、処理を高速化することができる。また、これに伴い低消費電力を実 現することができる。

[0058]

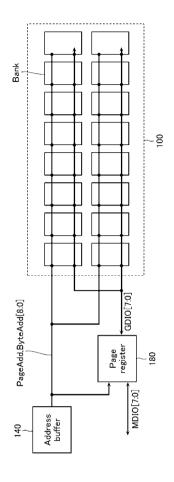

次に、図7のページ書き込み動作を実現する不揮発性メモリの内部構成例について説明する。

[0059]

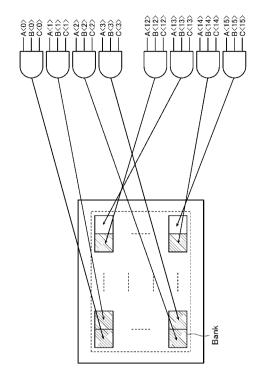

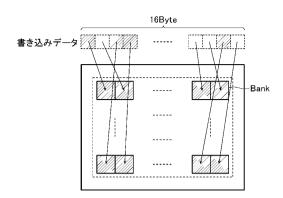

図8は、本実施形態に係る不揮発性メモリのアドレスバッファ140及びページレジスタ180と複数のバンクからなるメモリコア100との信号接続関係を示す図である。ここで、メモリコア100は、16個のバンクを有するものとする。また、1ページは、512バイトから成り、書き込み単位は、各バンク1バイトずつの合計16バイトとする。したがって、1ステップは、プログラム動作及びベリファイ動作合わせて最大64サイクルで処理される。

[0060]

アドレスバッファ140は、ページアドレスPageAddと、1ページ内のカラムアドレスByteAdd[8:0]の各信号をメモリコア100の各バンクに対して共通に送信する。

[0061]

ここで、カラムアドレス B y t e A d d [ 8 : 0 ] は、図 9 に示すとおり、書き込み単位を指定する第 1 のアドレス部分 B y t e A d d [ 8 : 4 ] とバンクを指定する第 2 のアドレス部分 B y t e A d d [ 3 : 0 ] で構成される。

[0062]

ページレジスタ180は、入出力ピン側に接続された内部双方向データバスMDIO[7:0]を介して入力バッファ120及び出力バッファ160とのデータの入出力を行う。また、ページレジスタ180は、メモリコア100側に接続された共通データバスGDIO[7:0]を介して各バンクとのデータの入出力を行う。

[0063]

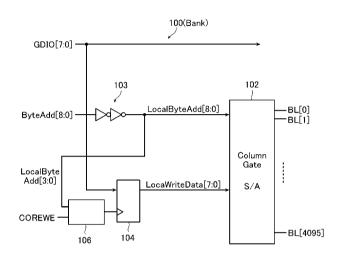

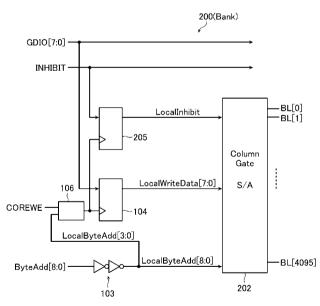

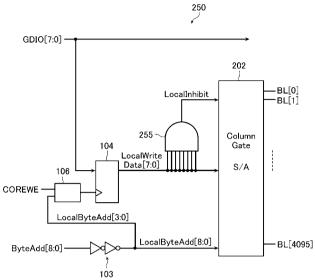

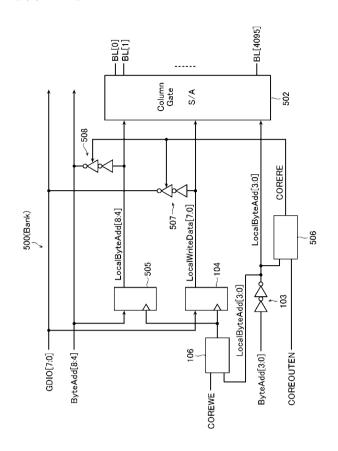

図10は、各バンクの内部構成例を示した図である。

[0064]

アドレスバッファ140から送信されたカラムアドレス Byte Add [8:0]は、必要に応じてバッファ回路103を経た後(図10ではバッファが2個挿入されている)、ローカルカラムアドレス Local Byte Add [8:0]としてカラムゲート及びセンスアンプ102に送信される。また、カラムアドレス Byte Add [8:0]のうち、バンクを指定する第2のアドレス部分に相当する Local Byte Add [3:0]は、バンクアドレスデコーダ106に送信される。

[0065]

バンクアドレスデコーダ 1 0 6 は、カラムアドレス B y t e A d d [ 3 : 0 ] の他、アレイ制御部 1 9 0 a から送信された書き込み許可信号 C O R E W E を受けて、この書き込み許可信号 C O R E W E が活性化されており、かつ、第 2 のアドレス部分に相当するローカルカラムアドレス L o c a l B y t e A d d [ 3 : 0 ] が当該バンクを指定するものであることを条件に、ローカルデータラッチ 1 0 4 に対して、データラッチのタイミングを通知する。

[0066]

この通知を受けたローカルデータラッチ 1 0 4 は、このタイミングで、共通データバスGDIO[7:0]にある書き込みデータをラッチした後、ローカル書き込みデータLocalWriteData[7:0]としてカラムゲート及びセンスアンプ 1 0 2 に送信する。

10

20

30

40

20

30

40

50

[0067]

最終的に、ローカルカラムアドレスLocalByteAdd[8:0]及びローカル書き込みデータLocalWriteData[7:0]を受けたカラムゲート及びセンスアンプ102は、これら信号に基づいて、所定のビット線BLを選択するとともに、これ以外の非選択ビット線BLに対して逆方向のバイアス電圧を供給する。

[0068]

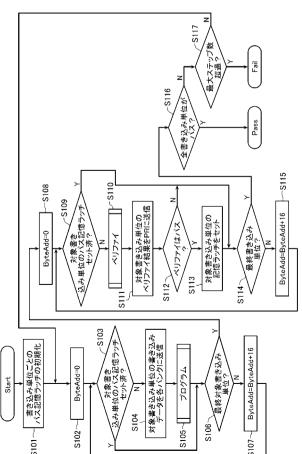

次に、図11を用いてページ書き込み動作の手順を説明する。

[0069]

先ず、S101において、書き込み単位毎に用意された図示されないパス記憶ラッチを初期化する。ここで、パス記憶ラッチは、各書き込み単位がベリファイをパスしたか否かを記憶するフラグである。

[0070]

続いて、S102において、カラムアドレスByteAddを0に初期化する。

[ 0 0 7 1 ]

続いて、S103において、カラムアドレスByteAddで指定された書き込み単位 (以下、"対象書き込み単位"と呼ぶ)について、ベリファイをパスしているかを判定する。ここで、ベリファイをパスしている場合、後に説明するS104及びS105の処理をスキップする。

[ 0 0 7 2 ]

続いて、S104において、対象書き込み単位に対する書き込みデータをページレジスタ180から各バンクに向けて送信する。

[0073]

続いて、S105において、バンク毎に、S104で送信された書き込みデータをプログラムする。

[0074]

続いて、S106において、対象書き込み単位がページ内の最後の書き込み単位かを判断する。最後の書き込み単位でない場合、S107において、次の書き込み単位を対象書き込み単位にするため現在のカラムアドレスByteAddに16(書き込み単位長分)加算した後、S103に遷移する。一方、最後の書き込み単位であった場合、S108に遷移する。

[0075]

続いて、S108において、カラムアドレスByteAddを0に初期化する。

[0076]

続いて、S109において、対象書き込み単位について、ベリファイをパスしているかを判定する。ここで、ベリファイをパスしている場合、後に説明するS110~S113の処理をスキップする。

[0077]

続いて、S 1 1 0 において、対象書き込み単位に対するベリファイ動作を実行し、S 1 1 1 において、ベリファイ結果をページレジスタ 1 8 0 に送信する。

[0078]

続いて、S112において、ベリファイの結果を判定し、パスしている場合には、S113において、パス記憶ラッチをセットしておく。

[0079]

続いて、S114において、対象書き込み単位がページ内の最後の書き込み単位かを判定する。最後の書き込み単位でない場合、S115において、次の書き込み単位を対象書き込み単位にするため現在のカラムアドレスByteAddに16(書き込み単位長分)加算した後、S109に遷移する。一方、最後の書き込み単位であった場合、S116に遷移する。

[0800]

続いて、S116において、全てのパス記憶ラッチがセットされているかを判定する。

ここで、全てのパス記憶ラッチがセットされている場合、つまり、全ての書き込み単位がベリファイをパスしている場合、ページ書き込みが正常終了(Pass)となる。一方、いずれかのパス記憶ラッチがリセットのままであった場合、つまり、いずれかの書き込み単位がまだベリファイをパスしていない場合、S117に遷移する。

[0081]

続いて、S117において、最大ステップ数に達したかを判定する。最大ステップ数は、ページ書き込みするための許容時間や、データ書き込みによって生じるメモリセルMCのストレスなどを勘案して予め設定しておいた数である。ここで、まだ最大ステップ数に達していない場合、S102に遷移する。一方、最大ステップ数に達した場合、ページ書き込みが失敗したものとして終了する(Fail)。

[0082]

[別の手順によるページ書き込み動作]

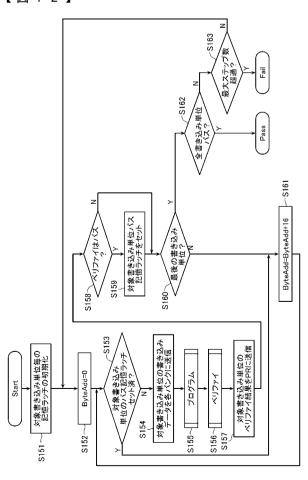

次に、図11とは別の手順によってページ書き込み動作する例について説明する。

[0083]

図11の場合、全ての書き込み単位に対してシーケンシャルにプログラム動作を実行し 、その後、全ての書き込み単位に対してシーケンシャルにベリファイ動作を実行した。

[0084]

これに対し、図12に示す例では、書き込み単位毎にプログラム動作及びベリファイ動作を連続して実行し、これをページ内の最後の書き込み単位まで繰り返す。

[0085]

先ず、 S 1 5 1 において、書き込み単位毎に用意されたパス記憶ラッチを初期化する。

[0086]

続いて、S152において、カラムアドレスByteAddを0に初期化する。

[0087]

続いて、S153において、対象書き込み単位について、ベリファイをパスしているかを判定する。ここで、ベリファイをパスしている場合、後に説明するS154~S160の処理をスキップする。

[0088]

続いて、S154において、対象書き込み単位に対する書き込みデータをページレジスタ180から各バンクに向けて送信する。

[0089]

続いて、S155において、対象書き込み単位に対するプログラム動作を実行する。

[0090]

続いて、 S 1 5 6 において、対象書き込み単位に対するベリファイ動作を実行し、 S 1 5 7 において、ベリファイ結果をページレジスタ 1 8 0 に送信する。

[0091]

続いて、 S 1 5 8 において、ベリファイの結果を判定し、パスしている場合には、 S 1 5 9 において、パス記憶ラッチをセットしておく。

[0092]

続いて、S160において、対象書き込み単位がページ内の最後の書き込み単位かを判定する。最後の書き込み単位でない場合、S161において、次の書き込み単位を対象書き込み単位にするため現在のカラムアドレスByteAddに16(書き込み単位長分)加算した後、S153に遷移する。一方、最後の書き込み単位であった場合、S162に遷移する。

[0093]

続いて、S162において、全てのパス記憶ラッチがセットされているかを判定する。ここで、全てのパス記憶ラッチがセットされている場合、つまり、全ての書き込み単位がベリファイをパスしている場合、ページ書き込みが正常終了(Pass)となる。一方、いずれかのパス記憶ラッチがリセットのままであった場合、つまり、いずれかの書き込み単位がまだベリファイをパスしていない場合、S163に遷移する。

10

20

30

40

20

30

40

50

#### [0094]

続いて、S163において、最大ステップ数に達したかを判定する。ここで、まだ最大ステップ数に達していない場合、S152に遷移する。一方、最大ステップ数に達した場合、ページ書き込みが失敗したものとして終了する(Fail)。

#### [0095]

以上、本実施形態によれば、図11及び図12のページ書き込み動作いずれの場合であっても、ベリファイをパスした書き込み単位については、次ステップにおけるプログラム動作及びベリファイ動作がスキップされるため、ページ書き込み動作に要する総サイクル数を削減することができる。その結果、ページ書き込み動作の処理速度を向上させることができ、消費電力も低減することができる。

[0096]

「第2の実施形態]

次に、本発明の第2の実施形態に係る不揮発性メモリにおけるページ書き込み動作について、比較例とともに説明する。

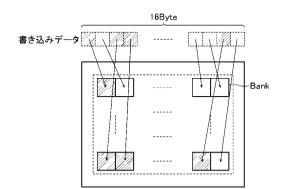

#### [0097]

図35は、比較例におけるページ書き込み動作を説明する図である。ここで、書き込みデータのうち、斜線が施された書き込みデータについては、書き込みビットが存在することを表す。斜線が施されていない書き込みデータについては、書き込みビットが存在しないことを表す(以下、"ブランクデータ"と呼ぶ)。また、斜線が施されたバンクは、データ書き込み時にバイアス電圧が供給されるバンクを表している。なお、書き込み単位長にあたる16バイトのデータは、メモリコアが備える16のバンクにそれぞれ1バイトずつ分散されているものとする。

[0098]

図35に示す比較例の場合、書き込みデータがブランクデータであるか否かに関わらず、全てのバンクに対してバイアス電圧が供給される。この場合、データ書き込みの必要がないバンクにおいても、非選択メモリセルに逆方向バイアスがかかり、その分余計なリーク電流が生じることになる。

[0099]

一方、図13に示す本実施形態の場合、比較例と異なり、書き込みビットが存在するバンクにのみバイアス電圧が供給され、書き込みビットが存在しないバンクにはバイアス電圧が供給されない。この場合、書き込みデータがブランクデータであるバンクについては、非選択メモリセルにおけるリーク電流が生じないため、比較例の場合に比べて、消費電力の低減を図ることができる。

[0100]

次に、図13に示すページ書き込み動作を実現する不揮発性メモリの内部構成について説明する。

[0101]

図 1 4 は、本実施形態におけるアドレスバッファ 1 4 0 及びページレジスタ 2 8 0 と複数のバンクからなるメモリコア 2 0 0 との信号接続関係を示す図である。

[0102]

アドレスバッファ140は、メモリコア200の各バンクに対し、ページアドレスPageAdd及びカラムアドレスByteAdd[8:0]を共通に送信する。また、ページレジスタ280は、内部双方向データバスMDIO[7:0]を介して送信/受信するデータを、共通データバスGDIO[7:0]を介してメモリコア200の各バンクに受信/送信する。さらに、データ検査手段であるページレジスタ280は、メモリコア200の各バンクに対して、バイアス電圧抑制信号INHIBITを送信する。このバイアス電圧抑制信号INHIBITが活性化された場合、対応するバンクへのバイアス電圧の供給が抑制される。

[0103]

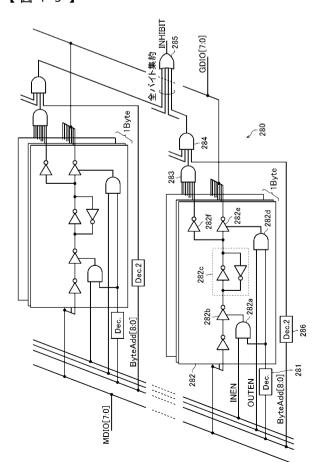

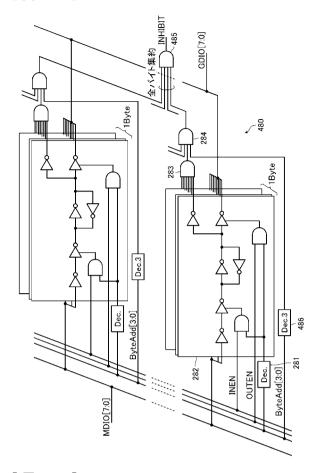

図15は、バイアス電圧抑制信号INHIBITを生成するページレジス280の内部

構成例を示す図である。

[0104]

ページレジスタ280は、1ビット毎に、ビットレジスタ282を備える。各ビットレジスタ282は、データを保持するフリップフロップ282cを備える。また、内部ツップ282cに転送するゲーテッドインバータ282b、このゲーテッドインバータ282bは、ビットンが活性化されたことを条件に、論理が一ト282aによって活性化される。ここで、ページレジスタ282の選択は、8つのページレジスタ282を1組とする1バイト単位に、カラムアドレスByteAdd[8:0]を入力とするデコーダ281によって行われる。さらに、フリップフロップ282cが保持する書き込みデータを共通データバスGDIO[7:0]に転送するゲーテッドインバータ282eを制御する論理ゲート282dによって活性化される。ゲーテッドインバータ282eを制御する論理が一ト282dによって活性の許可信号OUTENが活性化されたことを条件に、論理ゲート282dによって活性化される。

[0105]

ページレジスタ280は、さらに、バイアス電圧抑制信号INHIBITを生成するために、1バイト分のデータを集約する論理ゲート283と、論理ゲート283による集約結果を転送する論理ゲート284と、この論理ゲート284から転送された集約結果を全バイト分集約し、バイアス電圧抑制信号INHIBITを生成し出力する論理ゲート285とを備える。

[0106]

論理ゲート283は、8入力のANDゲートであり、各入力は、インバータ282 f を介して、各ビットレジスタ282のフリップフロップ282 c に接続されている。

[0107]

論理ゲート284は、上記論理ゲート283の出力と、カラムアドレスByteAdd[8:0]を入力とするアドレスデコーダ284の出力とを入力とするものであり、カラムアドレスByteAdd[8:0]によって対応するバイトが選択されたことを条件に、論理ゲート283の出力信号を論理ゲート285に転送する。

[0108]

論理ゲート285は、バイト毎に設けられた上記論理ゲート284の出力を入力とするORゲートであり、各バイトに書き込みビットが存在するか否かを全バイト分集約する役割を持つ。この論理ゲート285の出力がバイアス電圧抑制信号INHIBITであり、この信号は、カラムアドレスByteAdd[8:0]によって選択されたバイトが、ブランクデータであった場合に活性化される。

[0109]

図16は、図14に示すバンクの内部構成例を示す図である。

[ 0 1 1 0 ]

この内部構成例は、図10に示す第1の実施形態の場合のバンクの内部構成例に対し、 さらに、ローカルデータラッチ205を備えた構成例となっている。

[0111]

このローカルデータラッチ 2 0 5 は、ページレジスタ 2 8 0 から送信されるバイアス電圧抑制信号 I N H I B I T を受信し、このバイアス電圧抑制信号 I N H I B I T に応じて、バンクアドレスデコーダ 1 0 6 から通知されるタイミングで、各バンクに送信するローカルバイアス電圧抑制信号 L o c a l I n h i b i t を活性化させる。

[0112]

このローカルバイアス電圧抑制信号LocalInhibitを受けたカラムゲート及びセンスアンプ202は、ローカルバイアス電圧抑制信号LocalInhibitの状態に応じて、活性化されている場合には、ビット線BLへのバイアス電圧供給を停止する

10

20

30

40

[0113]

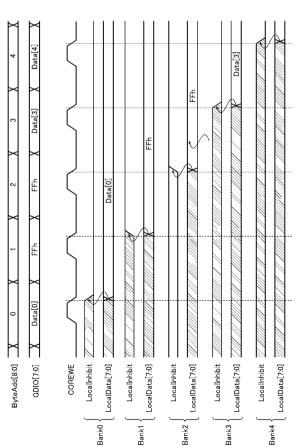

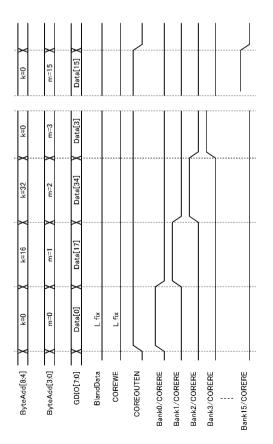

図 1 7 は、本実施形態に係る不揮発性メモリにおけるページ書き込み動作時のタイミングチャートである。ここで、斜線部分は、信号が不定であることを示す。

[0114]

図 1 7 の例では、カラムアドレス B y t e A d d [ 8 : 0 ] に合わせ、書き込みデータが共通データバス G D I O [ 7 : 0 ] を介して各バンクに供給される。ここで、ページレジスタ 2 8 0 は、ブランクデータが共通データバス G D I O [ 7 : 0 ] で送信されている間、バイアス電圧抑制信号 I N H I B I T を活性化させる。図 1 7 の場合、カラムアドレス B y t e A d d [ 8 : 0 ] = 1、2、つまり、バンク 1 及び 2 の書き込みデータを送信している間がこれに該当する。

[0115]

一方、各バンクのローカルデータラッチ205では、書き込み許可信号COREWEの立ち下がりのタイミングで、バイアス電圧抑制信号INHIBITがラッチされ、バンク毎のローカルバイアス電圧抑制信号LocalInhibitが活性化される。これを受けたカラムゲート及びセンスアンプ202は、ローカルバイアス電圧抑制信号LocalInhibitの状態に応じて、ビット線BLに対するバイアス電圧供給を抑制する。

[0116]

「別のバンクの内部構成例によるページ書き込み動作」

次に、別のメモリコア250のバンクの内部構成例について図18を用いて説明する。この内部構成例の場合でも、図13に示すページ書き込み動作を実現できる。

[0117]

メモリコア 2 5 0 の各バンクは、図 1 0 に示す第 1 の実施形態の場合のバンクの内部構成例に対し、さらに、論理ゲート 2 5 5 を備えた構成となっている。

[0118]

論理ゲート255は、ローカルデータラッチ104から出力されるローカル書き込みデータ[7:0]を入力とするANDゲートとなっている。この論理ゲート255の出力がローカルバイアス電圧抑制信号Loca1Inhibitとなっており、ローカル書き込みデータ[7:0]がブランクデータであった場合に活性化される。ローカルバイアス電圧抑制信号Loca1Inhibitの状態に図16の場合と同様、ローカルバイアス電圧抑制信号Loca1Inhibitの状態に応じて、ビット線BLに対するバイアス電圧供給を抑制する。

[0119]

図 1 9 は、図 1 8 に示す内部構成例を使用した場合のページ書き込み動作時のタイミングチャートである。

[0120]

図18のバンクの内部構成の場合、図19中の矢印で示すように、ローカルデータラッチ104から送信されるローカル書き込みデータLocalWriteData[7:0]の変化を受けてローカルバイアス電圧抑制信号LocalInhibitが変化する。例えば、バンク1及び2内のローカル書き込みデータLocalWriteData[7:0]がFFh、つまりブランクデータであった場合、ローカルバイアス電圧抑制信号LocalInhibitが活性化される。

[0121]

この図18の内部構成例によれば、バイアス電圧抑制信号INHIBITを生成する必要がないため、図15、図16の場合に比べ、内部構成を簡略化することができる。

[0122]

以上、本実施形態によれば、図14~17、あるいは図18~19のいずれの実施例においても、書き込みデータがブランクデータであるバンクについては、バイアス電圧の供給を抑制することができるため、その分だけ、非選択メモリセルで生じる電流リークを減少させることができる。したがって、低消費電力の不揮発性メモリを提供することができ

10

20

30

40

る。

### [0123]

## 「第3の実施形態]

第2の実施形態では、サイクル毎に、各バンクの書き込みデータがブランクデータか否かを判定し、バイアス電圧の供給 / 停止が制御されていた。しかし、この場合、制御が煩雑になることに加え、例えば、前サイクルでバイアス電圧の供給を停止させ、次サイクルでバイアス電圧の供給を再開させるような場合、バンクを再活性化させるための待ち時間が必要になる。その結果、ページ書き込み動作の処理速度が遅くなる可能性がある。

#### [0124]

そこで、本実施形態では、バンク毎に、全サイクルにおける書き込みビットの存否を判断し、書き込みビットが存在しなくなった時点でそれ以後のサイクルにおけるバイアス電圧の供給を停止させるものである。

#### [ 0 1 2 5 ]

図20A及び図20Bは、本実施形態におけるページ書き込み動作を説明する図である。図は、A~Cの3回のサイクルでページ書き込み動作を行う場合である。図20Aの四角は、書き込み単位であり、斜線が施されている四角は、書き込みビットが存在する書き込み単位を表している。また、図20Bの斜線が施されているバンクは、バイアス電圧が供給されるバンクを表している。

## [0126]

本実施形態の場合、バンクiの各サイクルにおける書き込みデータを A < i > ~ C < i > とすると、各サイクルにおいて、これらデータの論理積を取ることで、 A < i > ~ C < i > の全てがブランクデータとなるまで、バイアス電圧を供給される。

## [0127]

例えば、バンク 0 の場合、 A サイクルにおける書き込みデータ以外はブランクデータであるため、 B サイクル以後におけるバイアス電圧の供給を停止される。一方、バンク 1 4 の場合、 C サイクルにおける書き込みデータがブランクデータでないため、 C サイクル終了までの全サイクルについて、書き込みデータがブランクデータであるか否かに関わらずバイアス電圧が供給される。

#### [0128]

図 2 1 は、図 2 0 A 及び B に示すページ書き込み動作を実現するページレジスタ 4 8 0 の内部構成例であり、バンクに対するバイアス電圧の供給 / 停止を制御するバイアス電圧抑制信号 I N H I B I T を生成するものである。

#### [0129]

本実施形態におけるデータ検査手段であるページレジスタ480は、アドレスデコーダ486及び論理ゲート485が異なる点を除いて、図15に示す第2の実施形態におけるページレジスタ280と同様の構成となっている。

## [0130]

本実施形態におけるアドレスデコーダ486は、カラムアドレスByteAdd[3:0]のみを入力としている。したがって、カラムアドレスByteAdd[3:0]で指定されたバンクに割り当てられている全ての書き込みデータを論理ゲート485に集約させることができる。また、論理ゲート485は、第2の実施形態における論理ゲート285とは違いANDゲートとなっている。この場合、全バイトがブランクデータにならない限り、バイアス電圧抑制信号INHIBITは活性化されない。その結果、ページ長分のデータのうち、バンクに割り当てられた書き込みデータに書き込みビットが存在する限り、バイアス電圧の供給がされることになる。

## [0131]

なお、ページレジスタ480以外の内部構成については、第2の実施形態と同様であるので、説明を省略する。

#### [ 0 1 3 2 ]

本実施形態によれば、書き込みビットがなくなるまで、各バンクにバイアス電圧が供給

10

20

30

40

(18)

されるため、第2の実施形態に比べ、平均消費電力は大きくなるものの、図34に示す比較例と比べれば1バンクあたりの平均消費電力を低減することができる。また、第2の実施形態のように、バンクを再活性化させる必要がないため、制御を簡略化することができ、再活性化に伴う処理時間を省略でき、高速な動作を実現することができる。

#### [0133]

「第4の実施形態]

次に、本発明の第4の実施形態に係る不揮発性メモリにおけるページ書き込み動作について、比較例とともに説明する。

#### [0134]

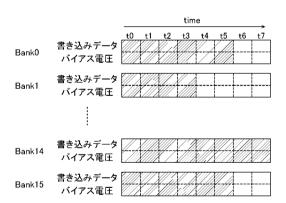

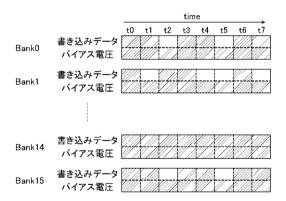

図36は、比較例におけるページ書き込み動作を説明する図である。図36は、サイクルと書き込みデータ及びバイアス電圧の関係をバンク毎に表したものである。上段は、書き込みデータであり、斜線は書き込みビットが存在することを意味する。一方、下段は、そのバンクに供給されるバイアス電圧であり、斜線はバイアス電圧が供給されていることを意味する。

#### [0135]

比較例の場合、書き込みデータがブランクデータか否かに関わらず、選択ページに関係する全てのバンクにバイアス電圧が供給される。したがって、例えば、バンク 0 の場合、時刻 t 2 、 t 5 では、書き込みデータがブランクデータであるにも関わらず、バイアス電圧が供給されることになる。

### [0136]

そこで、本実施形態では、図22に示すとおり、書き込みデータがブランクデータであった場合、次サイクルにおける書き込みデータを前倒しで書き込ませる。こうすることで、例えば、バンク0において、時刻t0~t7の8回のサイクルのうち、2回のサイクル(比較例の場合t2、t5におけるサイクル)で書き込みデータがブランクデータであった場合、時刻t5のサイクル終了時点で、すでにバンク0のページ書き込みが完了しているため、時刻t6以後は、バンク0に対するバイアス電圧供給を停止させることができる。この場合、ページ書き込み動作に要するサイクル数は、各バンクが要するサイクル数のうちの最大数(図22の場合、バンク14の8回)となるものの、ページ書き込み動作が完了したバンクについては、順次、バイアス電圧の供給が停止されるため、全バンクの平均消費電力を低減することができる。

#### [0137]

次に、図22に示すページ書き込み動作を実現する不揮発性メモリの内部構成について 説明する。

#### [0138]

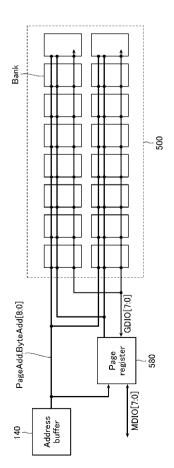

図 2 3 は、本実施形態におけるアドレスバッファ 1 4 0 及びページレジスタ 5 8 0 と複数のバンクからなるメモリコア 5 0 0 との信号接続関係を示す図である。

## [0139]

アドレスバッファ140は、ページアドレスPageAddと、1ページ内のカラムアドレスByteAdd[8:0]の各信号を出力する。このうち、ページアドレスPageAddについては、メモリコア500の各バンクに共通に送信される。一方、カラムアドレスByteAdd[8:0]については、書き込み単位を指定する第1のアドレスByteAdd[8:4]とバンクを指定する第2のアドレスByteAdd[3:0]に分割された上で、第1のアドレスByteAdd[8:4]については、ページレジスタ580を経由し、第2のアドレスByteAdd[3:0]については直接、メモリコア100の各バンクに共通に送信される。

## [0140]

ページレジスタ580は、入出力ピン側に接続された内部双方向データバスMDIO[7:0]を介して入力バッファ120及び出力バッファ160とのデータの入出力を行う。また、ページレジスタ580は、メモリコア100側に接続された共通データバスGDIO[7:0]を介して各バンクとのデータの入出力を行う。

10

20

30

40

20

30

40

50

[ 0 1 4 1 ]

次に、メモリコア500のバンクの内部構成例について図24を参照して説明する。

[0142]

アドレスバッファ 1 4 0 から送信されたカラムアドレス B y t e A d d [ 3 : 0 ] は、必要に応じて挿入されるバッファ回路 1 0 3 を経た後、ローカルカラムアドレス L o c a 1 B y t e A d d [ 3 : 0 ] としてカラムゲート及びセンスアンプ 5 0 2 に送信されるとともに、バンクアドレスデコーダ 1 0 6 にも送信される。

[0143]

バンクアドレスデコーダ 1 0 6 は、第 2 のアドレス部分に相当するLocalByteAdd[3:0]の他、アレイ制御部 1 9 0 a から送信された書き込み許可信号COREWEを受け、この書き込み許可信号COREWEが活性化されており、かつ、カラムアドレスByteAdd[3:0]が当該バンクを指定するものであることを条件に、ローカルデータラッチ 1 0 4 及びローカルアドレスラッチ 5 0 5 にラッチのタイミングを通知する。

[0144]

この通知を受けたローカルデータラッチ104は、このタイミングで、共通データバスGDIO[7:0]にある書き込みデータをラッチした後、ローカル書き込みデータLocalWriteData[7:0]としてカラムゲート及びセンスアンプ102に送信する。

[0145]

同様に、ローカルアドレスラッチ 5 0 5 は、バンクアドレスデコーダ 1 0 6 から通知されたタイミングで、第 1 のアドレス B y t e A d d [ 8 : 4 ] をラッチした後、ローカルカラムアドレス L o c a l B y t e A d d [ 8 : 4 ] としてカラムゲート及びセンスアンプ 1 0 2 に送信する。

[0146]

なお、データ書き込み動作の際は、出力許可信号 C O R E O U T E N 及び各バンク内部の読み出し許可信号 C O R E R E は非活性状態が維持されている。これによって、バス制御回路 5 0 7 及び 5 0 8 の出力が停止され、共通データバス G D I O [ 7 : 0 ] 及びカラムアドレス B y t e A d d [ 8 : 4 ] におけるデータ衝突が回避される。

[0147]

カラムゲート及びセンスアンプ 5 0 2 は、受信したローカルカラムアドレスLocal ByteAdd[8:0]及びローカル書き込みデータLocalWriteData[ 7:0]に基づいて、所定のビット線BLを選択し、それ以外のビット線BLを非選択の バイアス電圧でドライブする。

[0148]

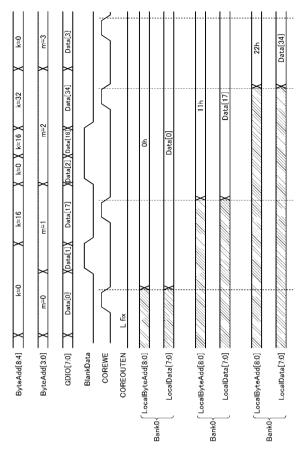

次に、図24に示す回路に与える入力波形例について図25を用いて説明する。ここで、カラムアドレスの第1のアドレス部分ByteAdd[8:4]を示すポインタを k 、第2のアドレス部分ByteAdd[3:0]を示すポインタを m としている。

[0149]

ページ書き込み動作に先立って、入力された書き込みデータがページレジスタ 5 8 0 から各バンクに送信されると同時に、各データのカラムアドレスアドレス B y t e A d d [8:4]が送信される。

[0150]

ページレジスタ 5 8 0 が保持する書き込みデータは、 k = 0 、 m = 0 から順番に各バンクへ送信される。図 2 4 の場合、 0 番地の書き込みデータは、そのまま送信される。

[0151]

続いて、 k=0、 m=1 に対する書き込みデータを送信しようとするとき、この書き込みデータがブランクデータであるため、ページレジスタ 5 8 0 の内部信号であるブランクデータ信号 B 1 a n k D a t a t a t a t b a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t a t

20

30

40

50

がない。ここで、次サイクルで書き込む予定の k = 1、 m = 1 に対する書き込みデータに書き込みビットが存在する場合、このデータを、 k = 0、 m = 0 のデータとともに書き込むことができるため、ページ書き込み動作に要する処理時間を短縮することができる。また、データ書き込み時の非選択メモリセルで生じるリーク電流の削減を図ることもできる

[0152]

具体的には、図25のように、k=0、m=1の書き込みデータData[1]を送信しようとする際に、ブランクデータ信号B1ankDataが活性化されたことを検知した場合、そのまま書き込みデータData[1]をバンクに送信せず、次サイクルで書くべき書き込みデータData[17]を送信する。また、これにともない、次サイクルの書き込みデータであることを指示するカラムアドレスByteAdd[8:4]も送信する。内部では、ブランクデータ信号B1ankDataの検知後、kの値を16(書き込み単位長分)だけインクリメントして次サイクルの書き込みデータを検査し、ブランクデータでない場合、この書き込みデータを送信する。

[ 0 1 5 3 ]

その後、 k の値を、インクリメントする前の値に戻した上で、 m をインクリメントして 、次のカラムアドレス B y t e A d d [ 8 : 0 ] のデータを送信する。

[0154]

m=2 の場合は、k=0 、 1 6 のデータ D a t a [ 2 ] 、 D a t a [ 1 8 ] がブランクデータであるため、k=3 2 までインクリメントした上で、m=2 、k=3 2 のアドレスに対する書き込みデータ D a t a [ 3 4 ] を送信する。

[ 0 1 5 5 ]

以下、他のバンクへの書き込みデータ送信も同様に継続される。

[ 0 1 5 6 ]

次に、図26を参照して、本実施形態におけるページ書き込み動作を説明する。なお、図26に示すページ書き込み動作は、主にシーケンス制御部170、ページレジスタ58 0、アレイ制御部190a及びページレジスタ制御部190bによって制御される。

[0157]

[0158]

続いて、S502において、ポインタkの値を別途設けられた図示しない一時保存レジスタtmpにその値を退避させる。この値は、書き込みデータとカラムアドレスの送信が終わるまで保持される。

[0159]

続いて、S503において、ポインタmを初期化する。具体的には、カラムアドレス Byte Add [3:0]を初期化する。これによってバンク0から書き込みデータの転送が開始される。

[0160]

続いて、S504において、2つのポインタk及びmで指示されたアドレスの書き込みデータがブランクデータか否かを判定する。具体的には、ブランクデータ信号B1ankDataが活性化されているかで判定する。その結果、書き込みビットが存在すれば、後に説明するS505に遷移し、ブランクデータであれば、S506に遷移する。

[0161]

続いて、S505において、ポインタk及びmで指示されたカラムアドレスByteAdd[8:0]と、このアドレスに対する書き込みデータを送信する。具体的には、書き込み許可信号COREWEをトリガとして、各バンクに配置されたローカルアドレスラッチ505及びローカルデータラッチ104に保持される。

[0162]

続いて、S506において、次サイクルにおける書き込みデータの検査に備え、ポイン

タ k を 1 6 だけインクリメントさせる。このポインタ k のインクリメントは、 k の値がページ内のアドレスを超えない範囲で許容される。そのため、 S 5 0 7 において、ページ内のアドレスを超えたか否かを判定する。ここで、アドレスがページの範囲内であれば、ポインタ k 及び m で指定されたアドレスに対する書き込みデータの検査をすべく S 5 0 4 に遷移する。一方、アドレスがページ範囲外であった場合、つまり、対象となるバンクに対するデータ書き込みが完了している場合には、送信済みの他バンクに対する書き込みデータの書き込みに備え、 S 5 0 8 に遷移する。

#### [0163]

続いて、 S 5 0 8 において、次のバンクに対する書き込みデータを送信するため、 S 5 0 2 で退避させたポインタ k の値を一時退避レジスタ t m p から復帰させる。

[0164]

続いて、S509において、他のバンクに対する書き込みデータの送信を継続するかを判定するため、最終バンクか否かを判定する。ここで、まだ書き込みデータが転送されていないバンクが存在する場合には、次のバンクのアドレスを指定するため、S510において、ポインタmをインクリメントした後、S504に遷移する。一方、最終バンク(m = 15)であった場合、全バンクに対する書き込みデータの送信が完了しているため、S511におけるプログラム動作及びS514におけるベリファイ動作に遷移する。ここで、S511におけるプログラム動作、S512におけるベリファイ動作は既知の動作手順によって実行する。

[0165]

続いて、S513において、ベリファイをパスしたかを判定し、パスしている場合には、ページ書き込み動作が完了する。一方、パスしていない場合には、追加書き込みをするかを判定するためS514に遷移する。

[0166]

最後のポインタkに達していない場合は、次のポインタkに関係する書込みを実行すべく、S515に遷移してポインタkをインクリメントした後、S502に遷移する。一方、最後のポインタkに達した場合はS516に遷移する。S516では、ポインタkを初期化して再度書き込むか否かを判断する。具体的には、図示せぬが、時間や書込みストレス回数等であらかじめ決められた値に達したか否かで判断する。実際には、最後のポインタkにおいてもなお書込みができないメモリセルがある、もしくは許容数を超える書込み不良ビットがある場合である。再度書き込むと判断された場合は、S5101に遷移して、ポインタkを初期化し、再度フローを実行する。一方、再度書き込まないと判断された場合は、書込み不良として動作を終了する(Fai1)。

[0167]

なお、以上の説明では、便宜的に処理を分けて説明しているが、回路動作上同時並行して実行でき る場合には、同一時刻で処理しても良い。また、動作上問題がなければ若干の前後処理は許容される。

[0168]

次に、ベリファイ動作中の、各バンクからページレジスタ180へのデータ転送動作について、図27及び図28を参照して説明する。

[0169]

図27は、ベリファイ動作中のタイミングチャートであり、図28は、送信された読み出しデータに対するベリファイ動作のフローを示す。

[0170]

出力許可信号 C O R E O U T E N によって、バス制御回路 5 0 7 及び 5 0 8 を活性化させるとともに、共通データバス G D I O [ 7 : 0 ] におけるデータの衝突を回避するため、入力バッファ 1 2 0 及びアドレスバッファ 1 4 0 の出力を停止させる。カラムアドレス B y t e A d d [ 8 : 4 ] が出力されると共にベリファイデータが共通データバス G D I O [ 7 : 0 ] に出力される。このときの共通データバス G D I O [ 7 : 0 ] のデータは、ページレジスタ 1 8

20

10

30

40

0 のカラムアドレス B y t e A d d [ 8 : 0 ] で指定された所定位置に保持され、ベリファイ結果並びに次の書き込みデータとして供される。

[0171]

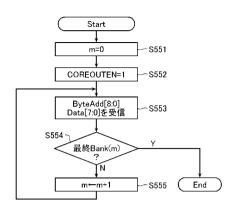

図28は、図27の動作波形をフローチャートとして記述したものである。

[0172]

先ず、S 5 5 1 において、ポインタmを初期化する。具体的にはカラムアドレス B y t e A d d [ 3 : 0 ] を初期化する。

[0173]

続いて、S552において、出力許可信号COREOUTENを活性化させ、各バンクからのベリファイデータの出力と、各バンクが持つカラムアドレスByteAdd[8:4]の出力を許可する。

[0174]

続いて、S553において、S552において出力されたデータを所定のレジスタに取り込む。ここでは、ページレジスタ180の所定カラムアドレスByteAdd[8:01に格納する動作が含まれる。

[0175]

続いて、S554において、全バンクのベリファイデータの転送が完了したかを判定し、完了している場合には、一連の送信動作を終了させる(End)。一方、完了していない場合には、S555において、ポインタmをインクリメントさせた後、S553に遷移する。ここでポインタmのインクリメントとは、具体的には、カラムアドレスByteAdd[3:0]のカウントアップを含むものである。

[0176]

以上のように本実施形態によれば、書き込みデータがブランクデータであった場合に、前倒しで次サイクルにおける書き込みデータが書き込まれるため、ページ書き込み動作の短縮を図ることができる。また、これにともない消費電力を低減することができる。

[0177]

「第5の実施形態]

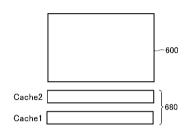

図 2 9 は、本発明の第 5 の実施形態に係る不揮発性メモリのメモリコア 6 0 0 及びページレジスタ 6 8 0 を概念的にしめしたものである。

[0178]

本実施形態において、ページレジスタ680は、少なくとも1バイト以上の異なる2つのキャッシュ、キャッシュ1及びキャッシュ2から構成されている。なお、このキャッシュは、3以上であっても構わない。

[ 0 1 7 9 ]

不揮発性メモリにデータを書き込む場合、ページレジスタ 6 8 0 のうちキャッシュ 2 の 所定のアドレスに所定の書き込みデータが格納される。

[0180]

ページ書き込み動作が開始された後は、キャッシュ1のデータはキャッシュ2にミラーリングされ、データ書き込みに供される。このキャッシュ2はデータ書き込み後のベリファイデータを格納する形態であっても、データ書き込み完了まで書き込みデータを保持する形態であってもよい。

[0181]

不揮発性メモリの多くは、ページ書き込み動作させる際、ページ長分のデータを一旦、キャッシュ 2 に保持し、その後、書き込みが開始される。したがって、間欠的に到着するデータを格納する必要がある場合には、最後の書き込みデータの到着を待ってからデータ書き込みを開始する必要がある。

[0182]

本実施形態では、この問題を解消し、ページ書き込み動作の高速化を図るものである。

[0183]

図30は、本実施形態におけるページ書き込み動作のフローチャートである。

10

20

30

[0184]

先ず、S601において、キャッシュ1に保持されている書き込みデータをキャッシュ 2 にコピーする。

[0185]

続いて、ウォッチドッグタイマ(以下、"WDT"と呼ぶ)を初期化する。これは、複数サイクルによってページ書き込み動作が実行されるため、所定時間を経過したデータ書き込みは書き込み不良として処理したい場合に必要となる。この場合、WDTをページ書き込み動作のバックグラウンドで動作させ、所定時間を経過してもなお書き込み動作が完了していない場合には、強制的に一連の動作を終了させる。なお、WDTに代えて、書き込みパルスの印加回数やその他時間と電圧から算出される手段で終了させることもできる

[0186]

続くS603からS614については、図25のS501からS512と同様であるため、説明を省略する。

[0187]

S613のプログラム動作及びS614のベリファイ動作に続き、S615において、キャッシュ1に対する書き込みデータの追加があった場合、既にデータ書き込みに供されているキャッシュ2の保持データに対する上書きを実行する。なお、キャッシュ1とキャッシュ2の保持データを論理演算し、書き込みデータの追加があったか否かを判断することもできる。

[0188]

続いて、S616において、ページ書き込み動作が完了したか否かを判断する。完了している場合はページ書き込み動作を終了する。一方、完了しておらず追加のページ書き込み動作が必要であると判断された場合には、S617に遷移する。

[0189]

続いて、S617において、ポインタkがページの最後に達していない場合には、再度、ページ書き込み動作を実行するため、S619においてポインタkをインクリメントした後、S604に戻る。また、最終のポインタkにおいてもなお追加で書き込む必要がある、具体的には、S615において検査した追加の書き込みデータがあった場合には、必要に応じてポインタkを初期化し、S603に戻る。但し、データ書き込みに伴うストレス印加等を考慮して、バックグラウンドで実行されているWDTがあらかじめ設定した上限に達したことを検知した場合には書き込み不良として処置するのが適当である。この判断はS618で行われる。

[0190]

以上の動作をタスクスケジューリングの観点から図30と図36に示す比較例を参照しながら説明する。

[0191]

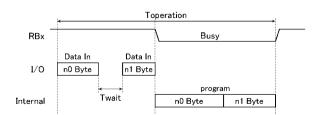

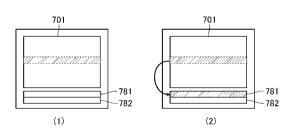

図31は、本実施形態におけるページ書き込み動作のタスクスケジューリングである。ページ長分(512バイト)のデータのうち最初のデータ群 n 0 バイト(n 0 < < 5 1 2)を待って書き込みが開始されている。内部ではこの n 0 バイトのデータ書き込みと並行して同一ページに属する別カラムアドレスのデータ群 n 1 バイトをキャッシュ 1 に保持することができる。ここで、データ群 n 1 が到着した場合、データ群 n 0 バイトのデータ書き込み後、データ群 n 1 バイトのデータ書き込みを連続して行うことができる。

[0192]

一方、図36に示す本実施形態を適用しなかった場合の比較例の場合、データ群 n 1 バイトの到着を待ってデータ書き込み動作が開始されるため、ページ書き込み動作に要する処理時間が増大する。また、データ群の到着を待つ期間 T w a i t 、不揮発性メモリを制御するホストと不揮発性メモリとを接続するバスが占有されるため、利便性が低下する点が問題となる。

[0193]

10

20

30

40

その点、本実施形態によれば、データ書き込みと次のデータを待つ動作を並行しておこなうことができるため、ページ書き込み動作の処理時間短縮を図ることができ、これにともなう消費電力の低減を図ることができる。また、ホストと本実施形態に係る不揮発性メモリとの通信によるバス占有時間を短縮できるため、可用性の高い不揮発性メモリを提供することができる。

#### [0194]

「その他 ]

以上、本発明を実施形態に沿って説明したが、この発明は実施例に限定されるものではなく、発明の要旨を逸脱しない範囲でその 実施方法を変更することが可能である。

#### 【符号の説明】

#### [0195]

100、200、250、400、500、600・・・メモリコア、101・・・メモリセルアレイ、102、202、502・・・カラムゲート及びセンスアンプ、103・・・バッファ回路、104、205・・・ローカルデータラッチ、106・・・バンクアドレスデコーダ、110・・・入力バッファ、120・・・入力バッファ、130・・・コマンドデコーダ、140・・・アドレスバッファ、150・・・データバッファ、160・・・出力バッファ、170・・・シーケンス制御部、180、280、580、680・・・ページレジスタ、181・・・データレジスタ、182・・・キャッシュレジスタ、190a・・・アレイ制御部、190b・・・ページレジスタ制御部、282・・・ビットレジスタ、286、486・・・アドレスデコーダ、505・・・ローカルアドレスラッチ、506・・・バス出力制御回路、507、508・・・バス制御回路。

20

10

## 【図1】

#

## 【図2】

## 【図3】

【図4】

【図5】

| WL  | BL  | バイアス電圧       | MC数          |

|-----|-----|--------------|--------------|

| 選択  | 選択  | Vset-0       | 1            |

| 選択  | 非選択 | 0            | 1024-1       |

| 非選択 | 選択  | Vset-VuselWL | 1024-1       |

| 非選択 | 非選択 | 0-VuselWL    | 1M-(1K+1023) |

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20A】

## 【図20B】

【図21】

【図22】

【図23】

【図24】

【図26】

【図27】

## 【図28】

## 【図29】

## 【図31】

## 【図32】

## 【図30】

【図33】

## 【図34】

【図35】

【図36】

## 【図37】