(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4708148号 (P4708148)

(45) 発行日 平成23年6月22日(2011.6.22)

(24) 登録日 平成23年3月25日(2011.3.25)

(51) Int.Cl. F 1

HO 1 L

21/60

(2006.01)

HO 1 L

21/92

6 O 2 G

HO 1 L

23/52

(2006.01)

HO 1 L

21/88

T

HO 1 L

21/3205

(2006.01)

HO 1 L

21/60

3 1 1 S

請求項の数 17 (全 19 頁)

(21) 出願番号 特願2005-294902 (P2005-294902) (22) 出願日 平成17年10月7日 (2005.10.7)

(65) 公開番号 特開2007-103848 (P2007-103848A)

(43) 公開日 平成19年4月19日 (2007.4.19) 審査請求日 平成20年10月2日 (2008.10.2) ||(73)特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

|(74)代理人 100080001

弁理士 筒井 大和

|(72)発明者 吉岡 明彦|

北海道亀田郡七飯町字中島145番地 株

式会社ルネサス北日本セミコンダクタ内

(72)発明者 鈴木 進也

北海道亀田郡七飯町字中島145番地 株式会社ルネサス北日本セミコンダクタ内

審査官 日比野 隆治

最終頁に続く

## (54) 【発明の名称】半導体装置

## (57)【特許請求の範囲】

## 【請求項1】

- (a)長方形状に形成された半導体基板と、

- (b)前記半導体基板上に形成された半導体素子と、

- (c)前記半導体素子上に形成された第1配線層と、

- (d)前記半導体基板上に形成され、前記半導体素子および前記第1配線層を覆うように形成された第1絶縁膜と、

- (e)前記第1絶縁膜上に形成されたパッドと、

- (f)前記第1絶縁膜上に形成され、前記パッドと同層の導電膜で形成された第2配線層と、

(g)前記パッドおよび前記第2配線層を覆うように形成され、前記パッドの上部に開口部を有する第2絶縁膜と、

(h)前記第2絶縁膜上に形成され、前記開口部を介して前記パッドに電気的に接続された長方形状の第1バンプ電極とを有し、

前記半導体基板の一方の長辺側には、前記パッドおよび出力用の前記第 1 バンプ電極が、前記半導体基板の長辺に沿う第 2 方向に所定の間隔で千鳥状に複数配置され、

前記半導体基板の他方の長辺側には、前記パッドおよび入力用の前記第1バンプ電極が、前記第2方向に所定の間隔で一列に複数配置され、

前記第1バンプ電極の各々は、前記第1バンプ電極の長辺が、前記半導体基板の短辺に 沿う第1方向に沿うように配置され、

平面的に見て、前記パッドの面積は、前記第1バンプ電極の面積に比べて小さく形成され、

前記第2配線層は、<u>前記半導体基板の両側の長辺において、</u>複数配置された前記第1バンプ電極と平面的に重なり、かつ、複数配置された前記第1バンプ電極の各長辺と交差するように延在していることを特徴とする半導体装置。

#### 【請求項2】

請求項1に記載の半導体装置において、

前記第1バンプ電極の前記第2方向における幅は、前記パッドの前記第2方向における幅より小さく形成され、

前記第1バンプ電極の前記第1方向における幅は、前記パッドの前記第1方向における幅より大きく形成されていることを特徴とする半導体装置。

### 【請求項3】

請求項1または2に記載の半導体装置において、

前記開口部は前記第1バンプ電極の短辺の一方側に形成されていることを特徴とする半導体装置。

## 【請求項4】

請求項1~3のいずれか一項に記載の半導体装置において、

前記第2絶縁膜は、窒化シリコン膜であることを特徴とする半導体装置。

#### 【請求項5】

請求項1~4のいずれか一項に記載の半導体装置において、

前記第1絶縁膜は、酸化シリコン膜であることを特徴とする半導体装置。

#### 【請求項6】

請求項1~5のいずれか一項に記載の半導体装置において、

前記第1バンプ電極は、金膜から構成されることを特徴とする半導体装置。

#### 【請求項7】

請求項1~6のいずれか一項に記載の半導体装置において、

前記パッドと前記第2配線層は、アルミニウム膜と前記アルミニウム膜の上下に積層形成されたチタン膜及び窒化チタン膜を含むことを特徴とする半導体装置。

## 【請求項8】

請求項1~7のいずれか一項に記載の半導体装置において、

前記第2配線層は、電源配線であることを特徴とする半導体装置。

# 【請求項9】

請求項1~8のいずれか一項に記載の半導体装置において、

前記第2方向に複数配置されているパッド間には、前記パッドおよび前記第2配線層と同層の導電膜は形成されていないことを特徴とする半導体装置。

#### 【請求項10】

請求項1~9のいずれか一項に記載の半導体装置において、

前記第2配線層は最上層配線であることを特徴とする半導体装置。

#### 【請求頃11】

請求項1~10のいずれか一項に記載の半導体装置において、

前記半導体素子は、液晶表示装置を駆動するための回路の一部を構成していることを特徴とする半導体装置。

# 【請求項12】

請求項11に記載の半導体装置において、

千鳥状に配置された前記第1バンプ電極は、前記液晶表示装置のゲート出力信号用またはソース出力信号用であることを特徴とする半導体装置。

#### 【請求項13】

請求項11または12に記載の半導体装置において、

前記第2絶縁膜上で、かつ、前記半導体基板の<u>両</u>短辺側に、出力用の第2バンプ電極が 前記第1方向に所定の間隔で千鳥状に複数配置され、 20

10

30

30

40

前記第2バンプ電極の各々は、前記第2バンプ電極の長辺が、前記第2方向に沿うように配置されていることを特徴とする半導体装置。

### 【請求項14】

請求項13に記載の半導体装置において、

前記第2バンプ電極は、前記液晶表示装置のゲート出力信号用であり、

前記半導体基板の一方の長辺の両端部に、前記液晶表示装置のゲート出力信号用であって千鳥状に配置された前記第1バンプ電極が形成され、

前記半導体基板の一方の長辺の前記両端部に形成され、かつ、千鳥状に配置された前記第 1 バンプ電極の間に、前記液晶表示装置のソース出力信号用であって千鳥状に配置された前記第 1 バンプ電極が形成されていることを特徴とする半導体装置。

# 【請求項15】

請求項14に記載の半導体装置において、

前記半導体基板上の両短辺側に、前記液晶表示装置のゲート駆動回路が形成され、

前記半導体基板の一方の長辺側に、前記液晶表示装置のソース駆動回路が形成され、

千鳥状に形成された前記第1バンプ電極は、前記ソース駆動回路が形成されている前記 半導体基板の長辺側に形成されていることを特徴とする半導体装置。

## 【請求項16】

請求項11~15のいずれか一項に記載の半導体装置において、

一列に配置された前記第 1 バンプ電極は、フレキシブルプリント基板と接続可能であることを特徴とする半導体装置。

#### 【請求項17】

請求項1~16のいずれか一項に記載の半導体装置において、

前記パッドの前記第1方向の幅は、前記第2配線層の前記第1方向の幅よりも小さいことを特徴とする半導体装置。

## 【発明の詳細な説明】

## 【技術分野】

#### [00001]

本発明は、半導体装置およびその製造技術に関し、特に、LCD(Liquid Crystal Dis play:液晶ディスプレイ)用のドライバに使用される半導体装置に適用して有効な技術に関するものである。

## 【背景技術】

## [0002]

特開平10-233507号公報(特許文献1)には、出力パッドを多数設けたドライバICのような半導体集積回路および電子時計などの電子回路装置において、チップ面積の縮小化を図り、生産効率の向上とコストダウンを図る技術が開示されている。

#### [0003]

具体的には、出力パッドに各々接続する駆動トランジスタ、あるいは、ロジック回路の上に平面的に重なって出力パッドを設けた。さらに、半導体装置の配線をアルミ配線だけでなく、バンプ電極あるいは、バリアメタルを用いている。また、プリント基板の上にフェイスダウン方式により半導体集積回路が電気的に接着されている場合の電気的接続は、半導体集積回路に設けられた半田バンプとプリント基板の配線とが直接、接続することにより形成される。この時半導体集積回路の外部接続端子であるバンプ電極はトランジスタの上に積層して設けられているとしている。

## [0004]

例えば、特許文献1の図18には、バンプ構造の出力パッドが、駆動用トランジスタの上に重なって配置されている。従って、平面的に駆動用トランジスタと出力パッドを重ねて配置できるために、チップ面積の縮小が可能となるとしている。また、特許文献1の図26には、拡散領域と別の拡散領域との間をバンプ配線により電気接続した場合の構造が開示されている。このような構造にすることにより、従来に比べ配線層を1層増すことができるとしている。

10

20

30

40

【特許文献1】特開平10-233507号公報

【発明の開示】

【発明が解決しようとする課題】

[0005]

近年、液晶を表示素子に用いたLCDが急速に普及しつつある。このLCDは、LCDを駆動するためのドライバによって制御されている。LCD用ドライバは半導体チップから構成されており、例えば、ガラス基板に実装される。LCD用ドライバを構成する半導体チップは、半導体基板上に複数のトランジスタと多層配線を形成した構造をしており、表面にバンプ電極が形成されている。そして、表面に形成されたバンプ電極を介して、ガラス基板に実装されている。このとき、バンプ電極によって半導体チップとガラス基板が接続されるが、接着力の向上の観点から、バンプ電極の面積を大きくして半導体チップとガラス基板の接着面積を大きくすることが行なわれている。すなわち、LCD用ドライバを構成する半導体チップのバンプ電極は、一般用途に用いられる半導体チップのバンプ電極に比べて大きさが遥かに大きくなっている特徴がある。

[0006]

LCD用ドライバにおいて、バンプ電極下にはパッシベーション膜となる絶縁膜が形成されており、この絶縁膜に設けられた開口部を介して、多層配線の最上層に形成されたパッドと接続されている。通常、開口部およびパッドは、バンプ電極の大きさに合わせて同程度の面積を有するように形成されている。

[0007]

上述したように、半導体チップに形成された多層配線の最上層には、大きなバンプ電極に対応したパッドが形成されている。すなわち、バンプ電極の大きさと同程度の面積を有するパッドが最上層に形成されている。このため、多層配線の最上層にパッド以外の配線を形成するスペースを確保するには、半導体チップのサイズを大きくしなければならない問題点がある。

[0008]

また、ボンディングパッドの直上にバンプ電極を形成する通常の構造では、実装するバンプ電極の位置が決まっているため、パッドなどの配線のレイアウト構成に制限がある。 したがって、半導体チップのサイズを効率良く縮小化できるレイアウト構成をとることが 困難である問題点がある。

[0009]

本発明の目的は、半導体チップのサイズを縮小化することのできる技術を提供することにある。

[0010]

また、本発明の他の目的は、半導体チップに形成されている配線のレイアウト構成の自由度を向上できる技術を提供することにある。

[0011]

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

[0012]

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

[0013]

本発明による半導体装置は、(a)半導体基板上に形成されたパッドと、(b)前記パッド上に開口部を有する絶縁膜と、(c)前記開口部を含む前記絶縁膜上に形成されたバンプ電極とを有する半導体チップを備える。そして、前記バンプ電極の大きさは、前記パッドの大きさに比べて大きくなっており、前記絶縁膜を介した前記バンプ電極の下層には、前記パッドとは異なる配線が形成されているものである。

[0014]

20

10

30

40

また、本発明による半導体装置は、(a)半導体基板上に形成されたパッドと、(b)前記パッド上に開口部を有する絶縁膜と、(c)前記開口部を含む前記絶縁膜上に形成されたバンプ電極とを有する半導体チップを備える。そして、前記バンプ電極の大きさは、前記パッドの大きさに比べて大きくなっており、前記バンプ電極には、幅の狭い第1部分と前記第1部分より幅の広い第2部分があることを特徴とするものである。

#### [0015]

本発明による半導体装置の製造方法は、(a)半導体基板上にパッドおよび前記パッドとは異なる配線を同層で形成する工程と、(b)前記パッドおよび前記パッドとは異なる配線上に絶縁膜を形成する工程とを備える。さらに、(c)前記絶縁膜に前記パッドの表面を露出する開口部を形成する工程と、(d)前記開口部を含む前記絶縁膜上にバンプ電極を形成する工程とを備える。そして、前記絶縁膜を介した前記バンプ電極の下層に、前記パッドおよび前記パッドとは異なる配線を形成することを特徴とするものである。

#### [0016]

また、本発明による半導体装置の製造方法は、(a)半導体基板上にパッドを形成する工程と、(b)前記パッド上に絶縁膜を形成する工程とを備える。さらに、(c)前記絶縁膜上に前記パッドの表面を露出する開口部を形成する工程と、(d)前記開口部を含む前記絶縁膜上にバンプ電極を形成する工程とを備える。そして、前記バンプ電極に、幅の狭い第1部分と前記第1部分よりも幅の広い第2部分を形成することを特徴とするものである。

# 【発明の効果】

#### [0017]

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明 すれば以下のとおりである。

#### [0018]

バンプ電極下の領域を有効活用でき、半導体チップのサイズを小さくすることができる。バンプ電極の位置に左右されずにパッドを配置することができるので、パッドなどの配線のレイアウト構成の自由度を向上させることができる。

#### 【発明を実施するための最良の形態】

## [0019]

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

#### [0020]

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

# [0021]

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。

# [0022]

同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうではないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

# [0023]

本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は 省略する。

## [0024]

10

20

40

30

#### (実施の形態1)

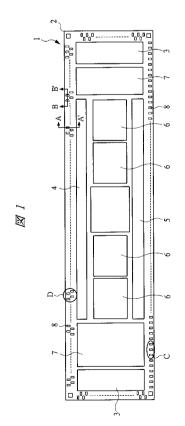

図1は本実施の形態1における半導体チップ1(半導体装置)の構成を示した平面図である。本実施の形態1における半導体チップ1は、LCD用のドライバである。図1において、半導体チップ1は、例えば細長い長方形状に形成された半導体基板2を有しており、その主面には、例えば液晶表示装置を駆動するLCD用のドライバが形成されている。このドライバは、LCDを構成するセルアレイの各画素に電圧を供給して液晶分子の向きを制御する機能を有しており、ゲート駆動回路3、ソース駆動回路4、液晶駆動回路5、グラフィックRAM(Random Access Memory)6および周辺回路7を有している。

#### [0025]

半導体チップ1の外周近傍には、複数のバンプ電極8が半導体チップ1の外周に沿って所定の間隔毎に配置されている。これら複数のバンプ電極8は、半導体チップ1の素子や配線が配置されたアクティブ領域上に配置されている。複数のバンプ電極8の中には乗積回路の構成に必要な集積回路用のバンプ電極と、集積回路の構成には必要とされないダミーバンプ電極が存在する。半導体チップ1の1つの長辺および2つの短辺近傍には、バプ電極8が千鳥状に配置されている。この千鳥状に配置されている複数のバンプ電極のバンプ電極8がイート出力信号用あるいはソース出力信号用のバンプ電極である。半導体チップ1の長辺中央に千鳥配置されたバンプ電極8がソース出力信号用のバンプ電極である。このような千鳥配置されたバンプ電極8がゲート出力信号用のバンプ電極である。このような千鳥配置を採用することが電極8がゲート出力信号用のバンプ電極である。このような千鳥配置を採用することができる。すなわち、チップサイズを縮小しつつ、バンプ電極の数を増やすことができる。

## [0026]

また、半導体チップ1の他方の長辺近傍には、千鳥配置ではなく一直線状に並ぶように バンプ電極8が配置されている。この一直線状に並ぶように配置されたバンプ電極8は、 デジタル入力信号用またはアナログ入力信号用のバンプ電極である。さらに、半導体チッ プ1の四隅近傍にはダミーバンプ電極が形成されている。なお、図1では、ゲート出力信 号用あるいはソース出力信号用のバンプ電極8を千鳥配置にし、デジタル入力信号用ある いはアナログ入力信号用のバンプ電極8を一直線状に配置している例について説明した。 しかし、ゲート出力信号用あるいはソース出力信号用のバンプ電極8を一直線状に配置し 、デジタル入力信号用あるいはアナログ入力信号用のバンプ電極8を千鳥配置にする構成 も可能である。

#### [0027]

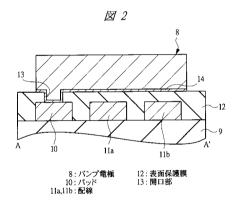

図2は、図1のA-A<sup>\*</sup>線で切断した断面を示す。図2において、最上層配線より下層の構造については省略している。図2に示していないが、半導体基板上には、MISFET (Metal Insulator Semiconductor Field Effect Transistor)などの半導体素子が形成され、この半導体素子上に多層配線が形成されている。図2ではこの多層配線のうち最上層の配線より上の構造が図示されている。

## [0028]

図2に示すように、例えば酸化シリコン膜よりなる絶縁膜9上には、最上層配線が形成されている。最上層配線としては、例えばパッド10やパッド10以外の配線11a、11bが形成されている。配線11a、11bとしては、例えば信号用の信号配線や電源用の電源配線あるいはダミー配線から形成されている。これらパッド10や配線11a、11bは例えばアルミニウム膜から構成されている。

### [0029]

パッド10および配線11a、11b上には、パッド10および配線11a、11bを覆うように表面保護膜(パッシベーション膜)12が形成されている。表面保護膜12は、例えば窒化シリコン膜などの絶縁膜から形成されている。そして、この表面保護膜12には、パッド10の表面を露出する開口部13が形成されており、開口部13内を含む表面保護膜12上には、下地の金属膜であるUBM膜14を介してバンプ電極8が形成され

10

20

30

40

10

20

30

40

50

ている。

## [0030]

また、バンプ電極 8 の下層には、前述のパッド 1 0 および配線 1 1 a、 1 1 b 等の配線層等の他に、パッド 1 0 および配線 1 1 a、 1 1 b 等の配線層よりも更に下層に複数の配線層が形成されている(図示せず)。同様に、バンプ電極 8 の下層には、前述のM I S F E T 等の半導体素子も形成されている(図示せず)。このように、本実施の形態では、バンプ電極 8 下の領域を有効に活用することで、半導体チップ 1 のチップ面積を縮小することのできる構成となっている。

## [0031]

ここで、本発明の特徴の1つは、バンプ電極8の大きさに比べて開口部13およびパッ ド10が小さくなるように形成している点である。通常、バンプ電極8の下部には、バン プ電極8と同程度の大きさを有する開口部13が形成され、この開口部13の下層にはバ ンプ電極8より大きいパッド10が形成されている。すなわち、バンプ電極8の下部には パッド10が形成されており、このパッド10の大きさは、バンプ電極8の大きさと同程 度であった。しかし、LCD用のドライバを構成する半導体チップ1においては、バンプ 電極 8 をガラス基板と接着させるため、面積が大きくなっている。したがって、バンプ電 極8の下層に形成されるパッド10の大きさも大きくなる。このとき、パッド10の大き さが大きいと、多層配線層の最上層にパッド10以外の配線を配置しようとしても、スペ ースを確保することが困難になり、半導体チップ1のサイズが大きくなってしまう。これ に対し、本実施の形態1では、図2に示すように、バンプ電極8の大きさに比べて開口部 13およびパッド10の大きさを小さくしている。言い換えれば、パッド10の大きさに 比べてバンプ電極8の大きさが大きくなっている。このように、バンプ電極8の大きさに 比べてパッド10の大きさを縮小化することにより、バンプ電極8の下層にパッド10以 外の配線11a、11bを形成するスペースを確保することができる。すなわち、バンプ 電極8の直下であって、パッド10と同層の最上層には、通常パッド10が形成されてい るので、他の配線を形成することができなかった。しかし、本実施の形態 1 では、バンプ 電極 8 の大きさに比べてパッド10の大きさを小さくするように構成したので、バンプ電 極8の直下であって、パッド10と同層の最上層に他の配線11a、11bを形成するス ペースを確保できる。したがって、バンプ電極8の直下にもパッド10以外の配線11a 11bを形成することができるので、バンプ電極8の直下のスペースを有効活用でき、 半導体チップ1のサイズを縮小化することができる。

# [0032]

本実施の形態1では、バンプ電極8の大きさを変えずに、パッド10の大きさをバンプ 電極8の大きさよりも小さくすることにより、バンプ電極8にパッド10以外の配線を形 成するスペースを設けることを特徴としている。つまり、ガラス基板に接着するバンプ電 極8の面積を確保しながら、バンプ電極8下にパッド10以外の配線を確保して、半導体 チップ1のサイズの縮小化を図っている。このような技術的思想は、背景技術で説明した 特許文献1には記載も示唆もされておらず、本実施の形態1に特有のものである。例えば 、パッドの大きさを変えずにバンプ電極の大きさを大きくすることにより、バンプ電極の 大きさをパッドの大きさに比べて大きくする構成をとることができるが、この場合、パッ ドの大きさ自体は縮小化されておらず、パッドの大きさを縮小化することによって形成さ れるスペースを確保することができない。したがって、半導体チップのサイズの縮小化を 図ることはできないのである。さらに、バンプ電極を大きくすると、半導体チップのサイ ズも大きくなるので、半導体チップの縮小化を図ることはできない。このように、バンプ 電極の大きさに対してパッド電極の大きさを小さくする方法には、バンプ電極自体の大き さを大きくする手段とパッド自体を小さくする手段がある。この2つの手段は、バンプ電 極の大きさに対してパッド電極の大きさが小さくなる点で共通するが、パッド自体を小さ くする手段では、バンプ電極下のパッドと同層の層にパッド以外の配線を形成するスペー スを確保できる点で顕著な相違点がある。さらに、パッド自体を小さくすることにより、 パッドの幅がパッド以外の配線で比較的幅の広い電源配線などに比べて小さくなる場合も ある。

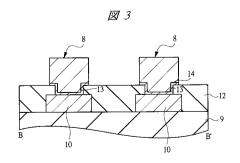

## [0033]

図3は、図1のB-B'線で切断した断面図を示している。図3に示すように、B-B'線で切断した断面において、絶縁膜9上にパッド10が形成されており、このパッド10を覆うように表面保護膜12が形成されている。そして、表面保護膜12には、開口部13が設けられており、この開口部13の底部において、パッド10の表面が露出している。そして、開口部13内を含む表面保護膜12上には、UBM膜14を介してバンプ電極8が形成されている。B-B'線で切断した断面方向においては、バンプ電極8の幅に対してパッド10の幅が同程度あるいは大きくなっている。すなわち、バンプ電極8の幅に比べて小さくなっており、バンプ電極8の直下に、パッド10の幅は、バンプ電極8の幅に比べて小さくなっており、バンプ電極8の直下に、パッド10の幅は、バンプ電極8の信号配線や電源配線などが形成されている。一方、図3に示すように、B-B'線で切断した断面方向においては、バンプ電極8の直下に形成されているパッド10の幅は、バンプ電極8の幅と同程度の大きさになっている。

#### [0034]

図4は、図1のC領域を拡大した平面図であり、直線状に配置されたバンプ電極8の直 下に配線を形成した様子を示す平面図である。図4に示すように、長方形の形状をしたバ ンプ電極8が短辺方向(長辺方向と交差する方向)に並んで配置されている。そして、バ ンプ電極8の下層には、表面保護膜12が形成されており、この表面保護膜12に開口部 13が形成されている。そして、表面保護膜12に設けられた開口部13の下層にはパッ ド10が形成されている。このパッド10は、開口部13を埋め込むようにして形成され たバンプ電極8と電気的に接続されている。パッド10は正方形の形状をしており、その 一辺の長さは、バンプ電極8の短辺の長さよりわずかに大きい程度である。したがって、 図4に示すように、バンプ電極8の短辺方向において、バンプ電極8の長さに比べてパッ ド10の長さはわずかに大きくなっている。一方、バンプ電極8の長辺方向においては、 バンプ電極8の長さに比べてパッド10の長さは遥かに小さくなっている。つまり、パッ ド10は、バンプ電極8よりも小さくなっており、パッド10は、バンプ電極8の一端部 下にだけ形成されていることになる。このため、バンプ電極8の長辺方向であって、パッ ド10と同層の配線層にはスペースが確保されることになる。このスペースには、パッド 10とは異なる配線11a~11cが形成されている。このように本実施の形態1によれ ば、バンプ電極8の直下に形成されるパッド10の大きさを小さくしたので、パッド10 と同層のバンプ電極8の直下に配線11a~11cを形成することができる。したがって 、長方形状をした大きなバンプ電極8の直下を有効活用することができるので、半導体チ ップの縮小化が可能となる。

## [0035]

配線11a~11cは、例えば信号配線、電源配線あるいはダミー配線からなり、様々な幅の配線を引き回すことができる。図4では、配線11cは、配線11a、11bに比べて幅が大きくなっている。通常パッドは、バンプ電極8の大きさと同程度に形成されているので、パッドの幅は配線の幅の中でも大きくなっている。しかし、本実施の形態1では、パッド10の大きさをバンプ電極8の大きさよりも小さくして、バンプ電極8の直下に配線を形成できるスペースを確保している。このため、パッド10の幅は、例えば確保したスペースに形成される電源配線などに比べて小さくなる場合がある。このように本実施の形態1による構成によれば、パッド10の幅がその他の一部の配線の幅よりも小さくなることがある。

## [0036]

配線11a~11cは、バンプ電極8の長辺方向に交差する方向に延在するように形成されている。なお、バンプ電極8の長辺方向に直交するように配線11a~11cを配置することが、スペースを有効に活用する観点から望ましいが、必ずしもバンプ電極8の長辺方向に直交するように形成しなくてもよい。例えば、配線のレイアウトによっては、斜めに交差するように配線を形成してもよい。この場合も、バンプ電極8の直下のスペース

10

20

30

40

を活用できるため、半導体チップの小型化が実現できる。

## [0037]

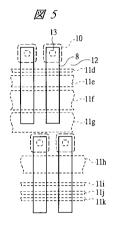

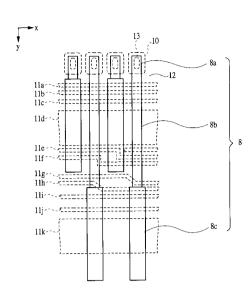

図5は、図1のD領域を拡大した平面図であり、千鳥状に配置されたバンプ電極8の直 下に配線を形成した様子を示す平面図である。図5においても、図4と同様に、バンプ電 極8の長辺方向の幅がパッド10の幅よりも遥かに大きくなっており、バンプ電極8の長 辺方向であって、パッド10と同層の層にスペースが確保されている。そして、このスペ ースに配線11d~11kが形成されている。千鳥状にバンプ電極 8 を形成した場合、バ ンプ電極8は図5に示すように、2段にわたってバンプ電極8が形成されている。このた め、一列にバンプ電極8を形成する場合に比べて、バンプ電極8の直下に形成されるスペ ースが大きくなる。すなわち、バンプ電極8の大きさに合わせてパッドを形成してしまう と、バンプ電極8の直下にパッド以外の配線を形成することができなくなる。このとき、 一列にバンプ電極8を形成する場合に比べて千鳥状にバンプ電極8を形成すると、バンプ 電極8が2列に形成されている分、配線を形成するスペースが狭くなる。しかし、図5に 示すように、本実施の形態1では、1段目の列に形成されているバンプ電極8の直下のス ペースに配線11d~11gを形成し、2段目の列に形成されているバンプ電極8の直下 のスペースに配線11h~11kを形成している。このため、バンプ電極8を千鳥状に配 置した場合であっても、バンプ電極8を一列に配置した場合と同程度にバンプ電極8の直 下に形成されたスペースを有効活用することができる。このように、半導体チップに形成 されているバンプ電極8において、一列に配置されているバンプ電極8下だけでなく、千 鳥状に配置されているバンプ電極8下にも配線を形成することができるので、半導体チッ プの小型化を推進することができる。

#### [0038]

また、図1のD領域(図5)では図1のC領域(図4)と比較して、バンプ電極8の数が多く配置されているが、これは後述の図15等に示すLCDの表示部20を構成する素子を駆動させるために、図1のD領域側により多くのバンプ電極8を配置させる必要があるからである。これら図1のD領域側のバンプ電極8は、主に、LCDの表示部20を構成する素子のゲート用およびソース用のために使用される。

#### [0039]

次に、本実施の形態 1 における半導体装置の製造方法について図面を参照しながら説明する。まず、図示はしないが、例えば、シリコン単結晶よりなる半導体基板上にMISFETなどの半導体素子を形成し、この半導体素子上に多層配線を形成する。図 6 では、最上層に形成された配線を示しており、この最上層に形成された配線より下層の構造については省略している。

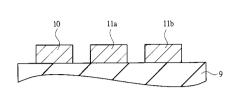

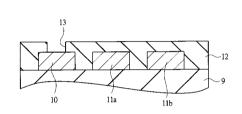

#### [0040]

図6に示すように、例えば酸化シリコン膜よりなる絶縁膜9を形成する。絶縁膜9は、例えば、CVD(Chemical Vapor Deposition)法を使用して形成することができる。そして、絶縁膜9上に、チタン/窒化チタン膜、アルミニウム膜およびチタン/窒化チタン膜を積層して形成する。その後、フォトリソグラフィ技術およびエッチング技術を使用して、積層膜をパターニングする。このパターニングにより、パッド10および配線11a、11bを形成する。このとき形成されるパッド10は、後述する工程で形成されるバンプ電極に比べて小さくなるようになっている。また、配線11a、11bはバンプ電極の直下に形成されるようになっている。

## [0041]

続いて、図7に示すように、パッド10および配線11a、11bを形成した絶縁膜9上に表面保護膜12を形成する。表面保護膜12は、例えば、窒化シリコン膜より形成され、例えば、CVD法により形成することができる。次に、フォトリソグラフィ技術およびエッチング技術を使用して、表面保護膜12に開口部13を形成する。この開口部13は、パッド10上に形成され、パッド10の表面を露出している。なお、開口部13の大きさはパッド10の大きさに比べて小さくなるように形成される。

# [0042]

10

20

30

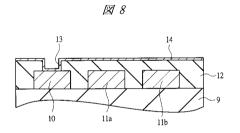

次に、図8に示すように、開口部13内を含む表面保護膜12上にUBM(Under Bump Metal)膜14を形成する。UBM膜14は、例えば、スパッタリング法を使用して形成でき、例えば、チタン膜、ニッケル膜、パラジウム膜、チタン・タングステン合金膜、窒化チタン膜あるいは金膜などの単層膜または積層膜により形成されている。ここで、UBM膜14は、バンプ電極8とパッド10や表面保護膜12との接着性を向上させる機能の他、この後の工程で形成される導体膜16の金属元素が配線11a,11b等に移動することや、反対に配線11a,11b等の金属元素が導体膜16側に移動するのを抑制または防止するバリア機能を有する膜である。また、UBM膜14の平面寸法は、開口部13よりも大きく、導体膜16とほぼ同じである。

# [0043]

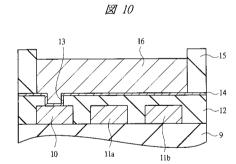

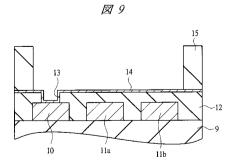

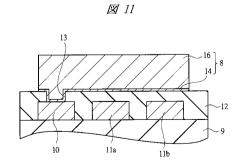

続いて、図9に示すように、UBM膜14上にレジスト膜15を塗布した後、このレジスト膜15に対して露光・現像処理を施すことによりパターニングする。パターニングは、バンプ電極形成領域にレジスト膜15が残らないように行なわれる。そして、図10に示すように、導体膜16として例えば、めっき法を使用して金膜を形成する。その後、図11に示すように、パターニングしたレジスト膜15およびレジスト膜15で覆われていたUBM膜14を除去することにより、導体膜16およびUBM膜14からなるバンプ電極8を形成する。次に、半導体基板をダイシングすることにより、個片化した半導体チップを得ることができる。

# [0044]

本実施の形態1によれば、バンプ電極8の直下に形成されるパッド10の大きさを小さくしたので、バンプ電極8の直下に配線11a、11bを形成することができる。すなわち、バンプ電極8の直下に、パッド10およびパッド10と同層で形成される配線11a、11bを形成することができるので、バンプ電極8の直下に形成されるスペースを有効活用でき、半導体チップの小型化を図ることができる。

#### [0045]

また、本実施の形態 1 における半導体装置の製造方法では、パッド 1 0 およびパッド 1 0 と同層に形成される配線 1 1 a、 1 1 bをバンプ電極 8 の直下に形成するようにパターニングする点以外は、通常の製造工程と同様である。したがって、製造工程の複雑化を招くことなく、本実施の形態 1 における半導体装置を製造することができる。つまり、製造工程の大幅な変更を行なわなくてもよい効果が得られる。

#### [0046]

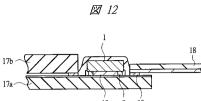

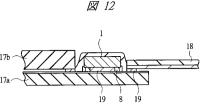

次に、上述するようにして形成された半導体チップを実装基板に接着して実装する。図12は、半導体チップ1をガラス基板17aに実装する場合(COG:Chip On Glass)を示したものである。図12に示すように、ガラス基板17aにはガラス基板17bが搭載されており、これによりLCDの表示部が形成される。そして、LCDの表示部の近傍のガラス基板17a上には、LCD用のドライバである半導体チップ1が搭載されている。半導体チップ1にはバンプ電極8が形成されており、バンプ電極8とガラス基板17a上に形成された端子とは異方導電フィルム(Anisotropic Conductive Film)19を介して接続されている。また、ガラス基板17aとフレキシブルプリント基板(Flexible Printed Circuit)18も異方導電フィルム19によって接続されている。このようにガラス基板17a上に搭載された半導体チップ1において、出力用のバンプ電極8はLCDの表示部に電気的に接続され、入力用のバンプ電極8はフレキシブルプリント基板18に接続されている。

# [0047]

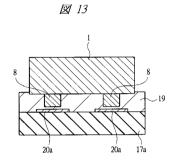

図13は、ガラス基板17aに半導体チップ1を搭載した部分を拡大した図である。図13において、ガラス基板17aには端子20aが形成されており、この端子20aに半導体チップ1に形成されているバンプ電極8が電気的に接続される。このとき、バンプ電極8と端子20aは直接接しているのではなく、異方導電フィルム19を介して接続されている。

# [0048]

10

20

30

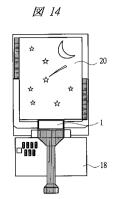

図14は、LCDの全体構成を示した図である。図14に示すように、ガラス基板上にLCDの表示部20が形成されており、この表示部20に画像が表示される。表示部の近傍のガラス基板上にはLCD用のドライバである半導体チップ1が搭載されている。半導体チップ1の近傍にはフレキシブルプリント基板18が搭載されており、フレキシブルプリント基板18とLCDの表示部20の間にドライバである半導体チップ1が搭載されている。このようにして、半導体チップ1をガラス基板17a上に搭載することができる。

L C D 用のドライバを実装基板に実装する形態の一例としてガラス基板 1 7 a に半導体チップ 1 を実装する C O G について説明したが、次に、半導体チップ 1 を実装する他の形態について説明する。

[0050]

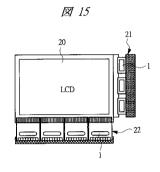

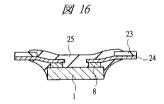

図15は、COG形態以外の実装形態で半導体チップ1を実装する様子を示したものであり、TCP(Tape Carrier Package)形態21とCOF(Chip On Film)形態22を示している。図16は、TCP形態によって半導体チップ1を実装基板に実装する様子を示した図である。図16において、実装基板はテープ状のフィルム基板(テープ基板)23であり、フィルム基板23には、例えば銅からなるリード24が形成されている。そして、このリード24にバンプ電極8が接着するように半導体チップ1がフィルム基板23に実装されている。なお、半導体チップ1はレジン25によって封止されている。図17は、ガラス基板17aとプリント基板28との間にTCP形態で実装した半導体チップ1を配置した例を示す図である。図17に示すように、ガラス基板17aとフィルム基板23に形成されたリード24とは異方導電フィルム26によって接続されており、同様に、フィルム基板23に形成されたリード24とは異方導電フィルム26によって接続されており、同様に、フィルム基板23に形成されたリード24とプリント基板28とは異方導電フィルム27によって接続されている。

[0051]

図18は、COF形態によって半導体チップ1を実装基板に実装する様子を示した図である。図18において、実装基板はテープ状のフィルム基板29である。TCP形態と同様にフィルム基板29上には銅よりなるリード30が形成されているが、TCP形態と異なり、リード30はバンプ電極8と接続する部位においても、フィルム基板29に固着している。そして、このリード30にバンプ電極8が接着するように半導体チップ1がフィルム基板29に実装されている。なお、半導体チップ1とフィルム基板29との隙間にはアンダーフィル31が形成されている。図19は、ガラス基板17aとプリント基板28との間にCOF形態で実装した半導体チップ1を配置した例を示す図である。図19に示すように、ガラス基板17aとフィルム基板29に形成されたリード30とは異方導電フィルム26によって接続されており、同様に、フィルム基板29に形成されたリード30とプリント基板28とは異方導電フィルム27によって接続されている。

[0052]

このように、LCD用のドライバである半導体チップ1を様々な形態によって実装することができる。

[0053]

(実施の形態2)

本実施の形態2では、バンプ電極の位置によらずにパッドの形成位置を最適な位置に決定することができるレイアウト自由度の高い半導体装置について説明する。

[0054]

図20は、本実施の形態2における半導体チップの一部を示した平面図である。図20において、パッド10は表面保護膜12に形成された開口部13を介してバンプ電極8の一部を構成するパッド接続部8aと接続されている。バンプ電極8は、パッド10に接続するパッド接続部8aと、実装基板の端子に接続する端子接続部8cと、パッド接続部8aと端子接続部8cとを接続する配線部8bから構成されている。通常、バンプ電極は、端子接続部だけから構成され、この端子接続部がパッドと接続されている。つまり、通常のバンプ電極では端子接続部がパッド接続部を兼ねており、パッド接続部と端子接続部が

10

20

30

40

平面的に重なっている。これに対し、本実施の形態2のバンプ電極8では、パッド接続部8aと端子接続部8cが平面的に異なる位置に形成されており、この平面的に異なる位置に形成されたパッド接続部8aと端子接続部8cとが配線部8bで接続された構造をしている。また、パッド接続部8aと端子接続部8cは、配線部8bと比較して、その平面形状の配線幅が大きくなるように形成されている。パッド接続部8aと端子接続部8cでは、それぞれパッド10と上記のガラス基板(またはフィルム基板)に設けられたリードに接続する必要があるため、その平面積をある程度確保する必要があるからである。配線部8bでは、その配線幅を小さくすることにより、他の配線部8bとの接触の可能性を防ぐことができ、配線引き回しの自由度を高めることが出来る。

## [0055]

このようにバンプ電極8を構成することにより、バンプ電極8の端子接続部8cを千鳥 状に配置しながら、パッド10を千鳥状に配置することなく、×方向へ一列に配置させる ことが可能となる。すなわち、バンプ電極の配置位置に左右されずにパッドの位置を決定 することができる。通常、バンプ電極とパッドとは平面的に重なり合うように配置されて いる。したがって、バンプ電極をγ方向に千鳥状に配置すると、パッドもγ方向に千鳥状 に配置されることになる。このとき、パッドは2列に配置されるが、パッドが配置されて いる箇所には、パッド以外の配線を引き回すことができない。このため、前記実施の形態 1で述べたように、バンプ電極の大きさに比べてパッドの大きさを小さくすることにより 、バンプ電極の直下にパッド以外の配線を形成する場合であっても、パッドがy方向に2 列に形成されているので、その分パッド以外の配線を形成するスペースを広げることがで きない。これに対し、本実施の形態2によれば、バンプ電極8を千鳥状に配置しても、パ ッド10は千鳥状にする必要はなく、図20に示すように×方向へ一列に配置させること が可能となる。したがって、パッド10のより占有されるスペースは、パッド10を2列 に配置する場合に比べて少なくなる。このように、パッド10によって占有されるスペー スを少なくできるので、パッド10と同層のバンプ電極8下に、パッド10以外の配線1 1 a~11 kを形成するスペースを充分確保できる。これにより、半導体チップの小型化 をさらに推進することができる。なお、バンプ電極8の直下に形成される配線11a~1 1kの形状は、直線状のものに限らず、折れ曲がっているものやあるいは曲線状の形状を しているものがあってもよい。

# [0056]

以上述べたように、本発明の特徴の1つは、バンプ電極8をパッド接続部8a、配線部8bおよび端子接続部8cから構成し、パッド接続部8aと端子接続部8cとを平面的に重ならないように配置したことにある。このように構成することにより、バンプ電極8を方向に延在するように形成して千鳥状に配置することにより、バッド10をx方向へこで、パッド10をx方向へ1列ラーできる。ここで、パッド10をx方向へ1列ラーできる。ここで、パッド10をx方向へは、ガラーへ1列ラーできる。ここで、バンプ電極8を構成する端子接続部8cは、ガラッド接続部8aのに表しなができる。ここで、接着力を確保する観点から幅が配線部8bやパッッド接続部8aのにはななっている。本実施の形態において、パンプ電極8は、パッド接続部8a、配線部8bおよび端子接続部8cから構成されているが、別の言いように構成は、「第1部分」8bと配線部8bよりも幅の広い端子接続部(第1部分)8cを有するように構成されているとも言える。このように構成することにより、バンプ電極8を狭ピッチで千鳥状に配置できる。と較的面積を広くする一方、配線部8bは、パッド接続部と端子接続部とを接続するので、にあるので、幅を狭くすることにより、バンプ電極8を狭ピッチで千鳥状に配置できる。

# [0057]

本実施の形態 2 によれば、バンプ電極の位置に左右されずに、パッドの配置位置を半導体チップのサイズを効率良く縮小化できる位置に配置できる。すなわち、パッドのレイアウト構成の自由度を向上させることができるので、半導体チップのサイズを効率良く縮小化することができる。また、バンプ電極 8 の端子接続部 8 c の面積をパッド 1 0 に関係な

10

20

30

40

く増大することができるので、実装基板との接着面積をフレキシブルに変更することができる。

#### [0058]

本実施の形態 2 における半導体装置の製造方法は前記実施の形態 1 とほぼ同様である。 異なる点は、バンプ電極 8 を形成する際、バンプ電極 8 をパッド接続部 8 a 、配線部 8 b および端子接続部 8 c を有するようにし、かつ、パッド接続部 8 a と端子接続部 8 c とが平面的に重ならないように形成する点である。そして、端子接続部 8 c の幅を配線部 8 b の幅に比べて広くなるようにする。このようにして、本実施の形態 2 における半導体装置を製造することができる。

## [0059]

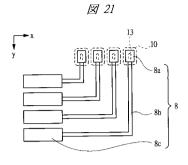

次に、本実施の形態 2 の変形例について説明する。図 2 1 は、本実施の形態 2 の変形例を示した平面図である。図 2 1 は、パッド 1 0 を x 方向へ一列に配置し、バンプ電極 8 の 端子接続部 8 c を y 方向へ一列に配置している場合を示したものである。このような場合も、バンプ電極 8 をパッド接続部 8 a 、配線部 8 b および端子接続部 8 c から構成を配置とにより実現できる。例えば、顧客の要求のよりバンプ電極 8 c が y 方向へ一列に配置することができる。すなわち、端子接続部 8 c の形成位置によらず、パッド 1 0 を配置することができる。なお、図示されていないが、図 2 1 においても、バンプ電極 8 の直下のパッド 1 0 を配置できる。なお、図示されていないが、図 2 1 においても、バンプ電極 8 の直下のパッド 1 0 の配置位置できるスペースを有効活用でき、半導体チップの小型化を実現することができる。最 6 に、パッド 1 0 のレイアウト構成の自由度が向上するので、パッド 1 0 の配置位置を 6 最 8 の配線部 8 b を直角に折れ曲がった形状から構成しているが、これに限らず、例えば曲線形状から構成するようにしてもよい。

#### [0060]

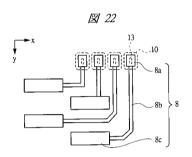

図22は、本実施の形態2の変形例を示した平面図である。図22は、パッド10をx方向へ一列に配置し、バンプ電極8の端子接続部8cをy方向へ千鳥状に配置している場合を示したものである。このような場合も、バンプ電極8をパッド接続部8a、配線部8bおよび端子接続部8cから構成することにより実現できる。例えば、顧客の要求のよりバンプ電極8cがy方向へ千鳥状に配置される場合においても、パッド10をy方向とは異なるx方向へ一列に配置することができる。すなわち、端子接続部8cの形成位置によらず、パッド10を配置することができる。なお、図示されていないが、図22においても、バンプ電極8の直下のパッド10と同層の層にはパッド10とは異なる配線が形成されている。このため、バンプ電極8の直下にできるスペースを有効活用でき、半導体チップの小型化を実現することができる。さらに、パッド10のレイアウト構成の自由度が向上するので、パッド10の配置位置を最適化することにより、半導体チップの小型化を推進できる。

## [0061]

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### [0062]

例えば、前述の実施の形態では、バンプ電極 8 およびパッド 1 0 の位置を半導体チップの 4 辺に配置した例を示したが、本発明はこれに限られるものではないのは勿論である。例えば、半導体チップ 1 の 4 辺近傍にパッド 1 0 を配置して、半導体チップ 1 の中央部にまでバンプ電極 8 を延在させることも可能である。また、半導体チップ 1 の中央部にパッド 1 0 を配置して、半導体チップ 1 の 4 辺近傍にまでバンプ電極 8 を延在させることも可能である。

## [0063]

前記実施の形態では、LCD用のドライバを例にして説明したが、これに限らず、バン

10

20

30

40

プ電極を有する半導体装置に幅広く適用することができる。

【産業上の利用可能性】

[0064]

本発明は、半導体装置を製造する製造業に幅広く利用することができる。

【図面の簡単な説明】

[0065]

- 【図1】本発明の実施の形態1における半導体チップの構成を示した平面図である。

- 【図2】図1のA-A′線で切断した断面を示した断面図である。

- 【図3】図1のB-B′線で切断した断面を示した断面図である。

- 【図4】図1のC線で示される領域の拡大図であって、直線状に配置されたバンプ電極の 10 直下に配線を形成した様子を示した平面図である。

- 【図5】図1のD線で示される領域の拡大図であって、千鳥状に配置されたバンプ電極の 直下に配線を形成した様子を示した平面図である。

- 【図6】実施の形態1における半導体装置の製造工程を示した断面図である。

- 【図7】図6に続く半導体装置の製造工程を示した断面図である。

- 【図8】図7に続く半導体装置の製造工程を示した断面図である。

- 【図9】図8に続く半導体装置の製造工程を示した断面図である。

- 【図10】図9に続く半導体装置の製造工程を示した断面図である。

- 【図11】図10に続く半導体装置の製造工程を示した断面図である。

- 【図12】半導体チップをガラス基板に実装する場合を示した図である。

- 【図13】ガラス基板に半導体チップを搭載した部分を拡大した図である。

- 【図14】LCDの全体構成を示した図である。

- 【図15】LCDの他の構成を示した図である。

- 【図16】TCP形態によって半導体チップを実装基板に実装する様子を示した図である

【図17】ガラス基板とプリント基板との間にTCP形態で実装した半導体チップを配置 した例を示す図である。

【図18】COF形態によって半導体チップを実装基板に実装する様子を示した図である

0

- 【図19】ガラス基板とプリント基板との間にCOF形態で実装した半導体チップを配置 30 した例を示す図である。

- 【図20】実施の形態2における半導体チップの一部を示した平面図である。

- 【図21】実施の形態2の変形例を示した平面図である。

- 【図22】実施の形態2の変形例を示した平面図である。

【符号の説明】

[0066]

- 1 半導体チップ

- 2 半導体基板

- 3 ゲート駆動回路

- 4 ソース駆動回路

- 5 液晶駆動回路

- 6 グラフィックRAM

- 7 周辺回路

- 8 バンプ電極

- 8 a パッド接続部

- 8 b 配線部

- 8 c 端子接続部

- 9 絶縁膜

- 10 パッド

- 11a~11k 配線

40

20

- 12 表面保護膜

- 1 3 開口部

- 1 4 UBM膜

- 15 レジスト膜

- 1 6 導体膜

- 17a ガラス基板

- 17b ガラス基板

- 18 フレキシブルプリント基板

- 19 異方導電フィルム

- 2 0 表示部

- 20a 端子

- 2 1 T C P 形態

- 2 2 COF形態

- 23 フィルム基板

- 2 4 リード

- 25 レジン

- 26 異方導電フィルム

- 27 異方導電フィルム

- 28 プリント基板

- 29 フィルム基板

- 30 リード

- 31 アンダーフィル

【図1】

【図2】

【図3】

10

【図4】

【図6】

)---llc

**Ø** 4

**Ø** 6

【図5】

【図7】

**図** 7

【図8】

【図10】

【図9】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図18】

【図17】

【図19】

図 19

# 【図20】

# 【図21】

**20**

# 【図22】

# フロントページの続き

# (56)参考文献 特許第4094656 (JP, B2)

特許第4585564(JP,B2)

特開2001-053100(JP,A)

特開2005-260207(JP,A)

特開2000-124249(JP,A)

特開平05-109813(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 21/60

H01L 21/3205

H01L 23/52