# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2006-310712 (P2006-310712A)

(43) 公開日 平成18年11月9日(2006.11.9)

(51) Int.C1.

$\mathbf{F} \mathbf{L}$

テーマコード (参考)

HO1C 7/10

(2006, 01)

HO1C 7/10

5E034

#### 審査請求 有 請求項の数 2 OL (全 15 頁)

(21) 出願番号 (22) 出願日 特願2005-134510 (P2005-134510)

平成17年5月2日(2005.5.2)

(71) 出願人 000003067

TDK株式会社

東京都中央区日本橋1丁目13番1号

(74)代理人 100088155

弁理士 長谷川 芳樹

(74)代理人 100092657

弁理士 寺崎 史朗

(74)代理人 100129296

弁理士 青木 博昭

(72) 発明者 森合 克成

東京都中央区日本橋一丁目13番1号 T

DK株式会社内

(72) 発明者 松岡 大

東京都中央区日本橋一丁目13番1号 T

DK株式会社内

最終頁に続く

(54) 【発明の名称】 積層型フィルタ

# (57)【要約】

【課題】 バリスタ部とインダクタ部との剥離が生じ難い積層型フィルタを提供すること。

【解決手段】 好適な実施形態の積層型フィルタ10は、バリスタ部20とインダクタ部とが積層された構造を有している。バリスタ部30は、内部電極31a,32aを備えるバリスタ層31,32が積層されてなり、このバリスタ層は、ZnOを主成分とし、添加物としてPr及びBiからなる群より選ばれる少なくとも一種の元素、Co並びにA1を含有している。また、インダクタ部20は、導体パターン21a~24aを備えるインダクタ層21~24が積層されてなり、このインダクタ層は、ZnOを主成分とし、Co及びA1を実質的に含有していないものである。

【選択図】 図2

#### 【特許請求の範囲】

### 【請求項1】

導体層及びバリスタ層を備えるバリスタ部と、導体層及びインダクタ層を備えるインダクタ部と、が積層された積層型フィルタであって、

前記バリスタ層は、ZnOを主成分とし、添加物として、Pr及びBiからなる群より選ばれる少なくとも一種の元素、Co並びにAlを含有しており、

前記インダクタ層は、ZnOを主成分とし、Co及びAlを実質的に含有していない、 ことを特徴とする積層型フィルタ。

#### 【請求項2】

表面から内部に拡散されたLiを更に含むことを特徴とする請求項1記載の積層型フィルタ。

【発明の詳細な説明】

#### 【技術分野】

# [0001]

本発明は、積層型フィルタ、より詳しくは、バリスタ部とインダクタ部とが積層されてなる積層型フィルタに関する。

#### 【背景技術】

#### [0002]

近年、電子機器は、高速動作のための伝送信号の高周波数化や、省電力化のための低電圧化等が進められている。このような状況下、電子機器においては、優れた信頼性を確保する観点から、ノイズやサージ等を除去する技術がますます重要になってきている。そこで、ノイズ及びサージの両方を一つのチップで除去し得る素子として、バリスタ部及びインダクタ部が積層されてなる積層型フィルタが注目を集めている。

#### [0003]

このような積層型フィルタとしては、半導体磁器と磁性材料磁器とを接合し、これを一体焼結して得られた複合機能素子が知られている(例えば、特許文献 1 参照)。

【特許文献1】特開平7-220906号公報

#### 【発明の開示】

【発明が解決しようとする課題】

#### [0004]

しかしながら、上述した従来の積層型フィルタでは、バリスタ部とインダクタ部とで素体を構成している材料が異なっているため、焼結時における両者の体積変化の程度が大きく異なり、このため、一体焼結の際に両者の境に応力が発生し易い傾向にあった。そして、これに起因して、バリスタ部とインダクタ部とが剥離し易いという問題があった。

#### [0005]

そこで、本発明はこのような事情に鑑みてなされたものであり、バリスタ部とインダク タ部との剥離が生じ難い積層型フィルタを提供することを目的とする。

【課題を解決するための手段】

#### [0006]

本発明者らは、まず、積層型フィルタにおいて、バリスタ部とインダクタ部との剥離を低減するために、インダクタ部を、バリスタ部を構成している素体と同じ材料により形成することを試みた。その結果、一体焼結を行った場合であっても、バリスタ部とインダクタ部との剥離が極めて生じ難くなることが判明した。

# [0007]

ところが、通常バリスタ部の素体を構成している材料は、極めて低抵抗であるという特性を有していることからインダクタの材料としては適しておらず、このような積層型フィルタは、高周波用途への適用が困難なものであった。

#### [0008]

そこで、本発明者らは、このような知見に基づいて更に研究を進めた結果、インダクタ 部をバリスタ部の構成材料と同じ素体から構成するとともに、両構成材料の添加物を異な 10

20

30

40

30

40

50

らせることによって、インダクタ部の素体の高抵抗化が図れることを見出し、本発明を完成させるに至った。

[0009]

すなわち、本発明の積層型フィルタは、導体層及びバリスタ層を備えるバリスタ部と、 導体層及びインダクタ層を備えるインダクタ部と、が積層された積層型フィルタであって 、バリスタ層は、ZnOを主成分とし、添加物として、Pr及びBiからなる群より選ば れる少なくとも一種の元素、Co並びにAlを含有しており、インダクタ層は、ZnOを 主成分とし、Co及びAlを実質的に含有していないことを特徴とする。

[0010]

このように、本発明に係る積層型フィルタは、バリスタ層及びインダクタ層の素体が同じ材料(ZnO)を主成分としている。よって、これらを一体焼結した場合であっても、両層の間に焼結時の素体の体積変化率の相違に基づく応力等が発生し難い。これにより、バリスタ部とインダクタ部との剥離が大幅に低減されるようになる。

[0011]

また、インダクタ層を構成している材料、すなわち、主成分としてZnOを含み、Co及びA1を実質的に含有していない材料は、ZnO単体や、上記バリスタ層の構成材料(ZnOにPr又はBi、Co及びA1を添加したもの)と比較して、極めて高抵抗率であり、低誘電率であるという特性を有している。したがって、かかる材料を含むインダクタ層は、優れたインダクタ特性を有するものとなる。

[0012]

また、本発明の積層型フィルタは、表面から内部に拡散されたLiを更に含むものであるとより好ましい。これにより、積層型フィルタにおけるインダクタ部が、一層インダクタ特性に優れるものとなる。その結果、積層型フィルタは、ノイズやサージを吸収する特性に更に優れるようになる。

- 【発明の効果】

- [0013]

本 発 明 に よ れ ば 、 バ リ ス タ 部 と イ ン ダ ク タ 部 と の 剥 離 が 生 じ 難 く 、 ま た 、 こ れ ら の バ リ ス タ 特 性 及 び イ ン ダ ク タ 特 性 が 極 め て 良 好 な 積 層 型 フ ィ ル タ を 提 供 す る こ と が 可 能 と な る

- 【発明を実施するための最良の形態】

- [0014]

以下、本発明の好適な実施形態について図面を参照して詳細に説明する。なお、全図を通じ、同一の要素には同一の符号を付すものとし、重複する説明は省略する。また、説明における上下左右等の位置関係は、いずれも図面の位置関係に基づくものとする。

[0015]

まず、図1~3を参照して、第1の実施形態に係る積層型フィルタ10の構造について 説明する。

[0016]

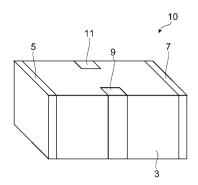

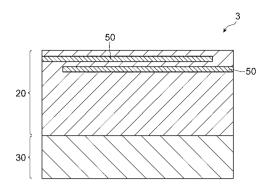

図1は、第1の実施形態の積層型フィルタを示す斜視図である。積層型フィルタ10は、素体3の長手方向の両端部に形成された一対の入出力電極5,7と、同じく素体3の側面に形成された一対のグランド電極9,11とを備えている。なお、素体3の底面は、積層型フィルタ10が外部基板(図示せず)に実装されたときに、当該外部基板に対向する面である。

[0017]

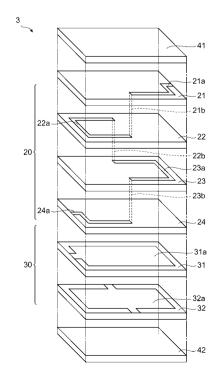

図 2 は、積層型フィルタの素体部分を示す分解斜視図である。図示されるように、積層型フィルタ 1 0 における素体 3 は、一対の保護層 4 1 , 4 2 の間に、インダクタ部 2 0 とバリスタ部 3 0 とからなる積層構造が挟まれた構造を有している。

[0018]

インダクタ部 2 0 は、導体パターン 2 1 a , 2 2 a , 2 3 a , 2 4 a (導体層)がそれぞれ設けられたインダクタ層 2 1 , 2 2 , 2 3 , 2 4 が積層されたものである。各層の導

20

30

40

50

体パターン 2 1 a , 2 2 a , 2 3 a , 2 4 a は、らせん状のコイルパターンの一部を構成するものであり、これらが貫通電極 2 1 b、 2 2 b、 2 3 b によって順次接続されることにより、コイルパターンが構成されている。このように、インダクタ部 2 0 は、コイル L (図 3 参照)を含む構造を有している。

#### [0019]

導体パターン 2 1 a は、その端部がインダクタ層 2 1 の端部に引き出されており、これが、コイルパターンにおける一方の端部となる。コイルパターンの当該端部(導体パターン 2 1 a ) は、素体 3 の縁部に引き出され、一方の入出力電極 7 に電気的に接続されることになる。

# [0020]

また、導体パターン24aは、その端部がインダクタ層24の端部に引き出されており、これが、コイルパターンのもう一方の端部となる。コイルパターンの当該端部(導体パターン24a)は、素体3における上記一方の端部と対向している側の縁部に引き出され、他方の入出力電極5に電気的に接続されることになる。

#### [0021]

導体パターン21a~24aは、インダクタのコイルパターンの構成材料として用いられる金属材料等から構成されるものである。また、インダクタ部20を構成する各インダクタ層21,22,23,24は、ZnOを主成分とするセラミック材料から構成されている。

## [0022]

インダクタ層21~24を構成するセラミック材料は、ZnOのほか、添加物としてPr、K、Na、Cs、Rb等の金属元素を含有していてもよい。なかでも、Prを添加すると特に好ましい。Prの添加により、インダクタ層21~24と後述するバリスタ層31,32との体積変化率の差を容易に低減することができる。また、インダクタ層21~24には、後述するバリスタ部30との接合性の向上を目的として、Cr、CaやSiが更に含まれていてもよい。インダクタ層21~24中に含まれるこれらの金属元素は、金属単体や酸化物等の種々の形態で存在することができる。インダクタ層21~24に含まれる添加物の好適な含有量は、当該インダクタ層に含まれるZnOの総量中、0.02mol%以上2mol%以下であると好ましい。これらの金属元素の含有量は、例えば、誘導結合高周波プラズマ発光分析装置(ICP)を用いて測定することができる。

#### [0023]

また、上記構成を有するインダクタ層21~24は、後述するバリスタ層31,32に含まれるCo及びA1を実質的に含有していないものである。ここで、「実質的に含有していない」状態とは、これらの元素を、インダクタ層21~24を形成する際に原料として意図的に含有させなかった場合の状態をいうものとする。例えば、バリスタ部30からインダクタ部20への拡散等によって意図せずにこれらの元素が含まれる場合は、「実質的に含有していない」状態に該当する。なお、インダクタ層21~24は、上述した条件を満たす限り、更なる特性の向上等を目的として、その他の金属元素等を更に含んでいてもよい。

### [0024]

バリスタ部 3 0 は、内部電極 3 1 a , 3 2 a ( 導体層 ) がそれぞれ設けられたバリスタ層 3 1 , 3 2 が積層されてなるものである。内部電極 3 1 a , 3 2 a は、それぞれバリスタ層 3 1 , 3 2 上に略矩形状に形成されており、これらは、積層方向において略全面が重なり合うように配置されている。ここで、内部電極 3 1 a は、その一部が、素体 3 の側面を構成するバリスタ層 3 1 の縁部に引き出されており、これにより入出力電極 5 と電気的に接続されることとなる。

#### [0025]

また、内部電極 3 2 a は、内部電極 3 1 a が引き出された縁部と直交している縁部の両側に引き出されており、この引き出し部においてグランド電極 9 , 1 1 とそれぞれ電気的に接続する。このように、バリスタ部 3 0 においては、内部電極 3 1 a , 3 2 a と、これ

30

40

50

らの間に配置されたバリスタ層31とからバリスタV(図3参照)が構成されている。

#### [0026]

内部電極 3 1 a , 3 2 a は、バリスタの内部電極に通常用いられる P d や A g - P d 合金等からなるものが適用できる。

#### [ 0 0 2 7 ]

バリスタ層31,32は、ZnOを主成分とするセラミック材料から構成されている。このセラミック材料中には、添加物として、Pr及びBiからなる群より選ばれる少なくとも一種の元素、Co並びにA1が更に含まれている。ここで、バリスタ層31,32は、Prに加えてCoを含むことから、優れた電圧非直線特性、すなわちバリスタ特性を有するものとなるほか、高い誘電率()を有するものとなる。また、A1を更に含むことから、低抵抗となる。逆に言えば、上述したインダクタ層21~24は、Co及びA1を含まないことから、バリスタ特性を有さず、また誘電率が小さく、しかも抵抗率が高いため、インダクタ部の構成材料として極めて好適な特性を有している。

#### [0028]

これらの添加物としての金属元素は、バリスタ層31,32において、金属単体や酸化物等の形態で存在することができる。なお、バリスタ層31,32は、更なる特性の向上を目的として、添加物として上述したもの以外の金属元素等(例えば、Cr、Ca、Si、K等)を更に含有していてもよい。

#### [0029]

上述したインダクタ部20におけるインダクタ層21~24は、その内部にLiを更に含有するものである。ただし、このLiは、原料としてこれらの層に添加されたものではなく、後述するような製造方法において、インダクタ部20及びバリスタ部30を備える積層体を形成した後に、この積層体の表面にLiを含む原料を付着させ、これが拡散することによって添加されたものである。ただし、バリスタ部30においては、バリスタ層31の内部電極31a及び内部電極32aに挟まれた領域がバリスタ特性を発現するが、かかる領域にはLiはできるだけ含まれないことが望ましい。そして、本実施形態においては、上述のように積層体の表面からLiを拡散させていることから、バリスタ層31の上記領域までLiが拡散されることが極めて少なく、当該領域にはLiが実質的に含まれない状態となっている。なお、積層型フィルタ10は、必ずしもLiが拡散されたものでなくてもよい。

#### [0030]

保護層41,42は、それぞれセラミック材料からなる層であり、インダクタ部20及びバリスタ部30からなる積層構造を、その積層方向の両側から挟みこむことで、各部20,30を保護するものである。この保護層41,42の構成材料は特に限定されず、種々のセラミック材料等を適用可能であるが、上述した積層構造との剥離を低減する観点からは、ZnOを主成分として含む材料が好ましい。

#### [0031]

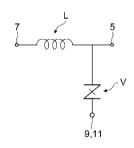

図3は、実施形態の積層型フィルタの等価回路を説明するための図である。上述した構成を有する積層型フィルタ10は、図3に示されるような等価回路を構成することになる。すなわち、積層型フィルタ10は、インダクタL及びバリスタVとでL型の回路を構成している。

#### [0032]

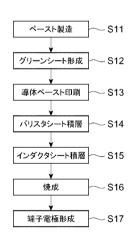

次に、図4を参照して本実施形態の積層型フィルタを製造する方法について説明する。

# [0033]

図4は、実施形態の積層型フィルタを製造する工程を説明するためのフロー図である。積層型フィルタ10の製造においては、まず、インダクタ層21~24、及び、バリスタ層31,32の原料となるセラミック材料を含むペーストを製造する(ステップS11)。具体的には、バリスタ層形成用のペーストは、主成分であるZnOに対し、添加物として、Pr及びBiからなる群より選ばれる少なくとも一種の元素、Co並びにAlのほか、必要に応じてCr、Ca、Si、K等を、焼成後に所望の含有量となるように加え、こ

20

30

40

50

(6)

れらのバインダー等を添加して混合することにより調製することができる。この場合の金属元素は、例えば、酸化物として添加することができる。

#### [0034]

また、インダクタ層形成用のペーストは、主成分であるZnOに対し、必要に応じて、添加物としてPr、Bi等の金属元素を加え、更にこれらにバインダー等を添加して混合することによって調製可能である。なお、インダクタ層形成用のペーストには、バリスタ層形成用のペーストとは異なり、Co及びAlは添加しない。ここで、上記金属元素は、例えば、酸化物、シュウ酸塩、炭酸塩等の化合物の形態で添加することができる。また、これらの添加量は、後述するような焼成を行った後の素体3において、金属元素が上述したような所望の含有量となるように調整する。

[0035]

これらのペーストを、プラスチックフィルム等の上にドクターブレード法等により塗布した後に乾燥させ、セラミック材料からなるグリーンシートを形成する(ステップS12)。これにより、インダクタ層21~24形成用のグリーンシート(以下、「インダクタシート」という)、及び、バリスタ層31,32形成用のグリーンシート(以下、「バリスタシート」という)を、それぞれ所要の枚数ずつ得る。次いで、得られたインダクタシートに対し、レーザーやパンチング等により所望の位置にスルーホールを形成する。なお、上記グリーンシートの形成において、プラスチックフィルム等は、塗布・乾燥後すぐに各シートから剥離してもよく、後述する積層の直前に剥離してもよい。また、このグリーンシートの形成工程においては、これらのシートとともに、上記と同様の方法でZnOを含む保護層41,42形成用のグリーンシートを形成する。

[0036]

次に、インダクタシート又はバリスタシートの上に、導体パターン21a~24a(インダクタ部20)又は内部電極31a,32a(バリスタ部30)を形成するための導体ペーストを、それぞれのシートに対して所望のパターンとなるようにスクリーン印刷する(ステップS13)。これにより、所望のパターンを有する導体ペースト層が設けられた各シートを得る。例えば、導体パターン形成用の導体ペーストとしては、PdやAg-Pd合金を主成分として含む導体ペーストが挙げられる。

[ 0 0 3 7 ]

続いて、保護層形成用のグリーンシートの上に、内部電極31a及び32aにそれぞれ対応する導体ペースト層が設けられたバリスタシートを順次積層する(ステップS14)。続いて、この上に、導体パターン24a、23a、22a及び21aにそれぞれ対応する導体ペースト層が設けられたインダクタシートを順次積層する(ステップS15)。さらに、これらの積層構造の上に、保護層形成用のグリーンシートを更に重ね、これらを圧着することにより、素体3の前駆体である積層体を得る。

[ 0 0 3 8 ]

その後、得られた積層体を、所望のサイズとなるようにチップ単位に切断した後、このチップを、所定温度(例えば、1000~1400)で焼成して、素体3を得る(ステップS16)。続いて、得られた素体3の表面からその内部にLiを拡散させる。ここでは、得られた素体3の表面にLi化合物を付着させた後、熱処理等を行う。Li化合物の付着には、密閉回転ポットを用いることができる。Li化合物としては、特に限定されないが、熱処理することによりLiが素体3の表面から導体パターン21a~24aや内部電極31a,32aの近傍にまで拡散できる化合物であり、例えば、Liの酸化物、水酸化物、塩化物、硝酸塩、ホウ酸塩、炭酸塩及びシュウ酸塩等が挙げられる。なお、積層型フィルタ10の製造において、このLi拡散の工程は必ずしも必須ではない。

[0039]

そして、このLi拡散された素体3の側面に、銀を主成分とするペーストを転写した後に焼き付けた後、更にめっきを施すことによって、入出力電極5,7及びグランド電極9,11をそれぞれ形成し、積層型フィルタ10を得る(ステップS17)。めっきは、電

気めっきにより行うことができ、例えば、CuとNiとSn、NiとSn、NiとAu、NiとPdとAu、NiとPdとAg、又は、NiとAg等を用いることができる。

#### [0040]

上記構成を有する積層型フィルタ10においては、上述の如く、インダクタ部20及びバリスタ部30をそれぞれ構成するインダクタ層21~24及びバリスタ層31,32が、ともにZnOを主成分とするセラミック材料から形成されている。このため、インダクタ部20とバリスタ部30とでは、焼成時に生じる体積変化の差が極めて小さい。したがって、これらを同時に焼成したとしても、両者の間にひずみや応力等が発生し難い。その結果、得られた積層型フィルタ10は、インダクタ部とバリスタ部とが異なる材料により形成された従来の積層型フィルタと比較して、両者の剥離が極めて生じ難いものとなる。

[0041]

また、インダクタ層 2 1 ~ 2 4 は、上述の如く、 Z n O を主成分とし、添加物として C o 及び A 1 を実質的に含有しないセラミック材料から構成される。このような材料は、インダクタの構成材料として十分な程度に高い抵抗率を有している。 具体的には、インダクタ材料として好適な 1 M を超える抵抗率を有するものとなり易い。このため、インダクタ部 2 0 は、単独では抵抗率の点で特性が不十分であった Z n O を主成分として含んでいるにもかかわらず、優れたインダクタ特性を発揮し得るものとなる。

[0042]

次 に 、 第 2 の 実 施 形 態 に 係 る 積 層 型 フィ ル タ に つ い て 、 図 5 ~ 図 8 を 参 照 し て 説 明 す る

[0043]

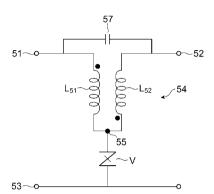

図 5 は、第 2 の実施形態に係る積層型フィルタの回路構成を示す図である。図 5 に示すように、本実施形態の積層型フィルタは、外部との接続を行う入力端子 5 1、出力端子 5 2、共通端子 5 3、コイル L 5 1 及びコイル L 5 2 からなる相互誘導素子 5 4、コンデンサ 5 7、並びに、バリスタ V からなる回路構成を有している。

[0044]

この回路において、入力端子 5 1、出力端子 5 2 及び共通端子 5 3 は外部との接続に供される。コンデンサ 5 7 は、入力端子 5 1 及び出力端子 5 2 に接続されている。また、相互誘導素子 5 4 において、コイル  $L_{5,1}$  (一次)側の一方の端子が入力端子 5 1 に接続され、コイル  $L_{5,2}$  (2次)側の反転誘導される一方の端子が出力端子 5 2 に接続されている。また、コイル  $L_{5,1}$  とコイル  $L_{5,2}$  の他方の端子同士は、接続端子 5 5 において接続されている。バリスタ V は、一方の端子が相互誘導素子 5 4 におけるコイル  $L_{5,1}$  とコイル  $L_{5,2}$  との接続点(接続端子 5 5)に接続され、他方の端子が共通端子 5 3 に接続されている。

[0045]

このような回路構成においては、入力端子 5 1 と出力端子 5 2 とが入れ替わっていてもよい。また、共通端子 5 3 はグランドに接地されることが好ましい。なお、相互誘導素子 5 4 は、例えば、コモンモードチョークコイル又はトランスによって構成することができる。

[0046]

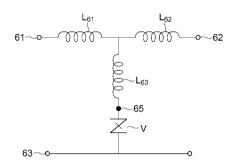

ここで、図5に示す回路構成は、等価的に図6に示す回路構成に変換することができる。図6は、図5の回路構成を等価的に変換した回路構成を示す図である。この回路構成は、入力端子61、出力端子62、共通端子63、コイルL<sub>61</sub>、コイルL<sub>62</sub>、コイルL<sub>63</sub>及びバリスタVから構成されている。

[0047]

かかる回路において、入力端子61、出力端子62及び共通端子63は外部との接続に供される。コイルL61及びコイルL62は、入力端子61と出力端子62との間に直列に接続されている。また、コイルL63とバリスタVとは、接続端子65において直列に接続されている。さらに、コイルL63における接続端子65に対して反対側の端子は、コイルL61とコイルL62との接続点に接続されており、バリスタVにおける接続端子

20

30

40

65に対して反対側の端子は、共通端子63に接続されている。

#### [ 0 0 4 8 ]

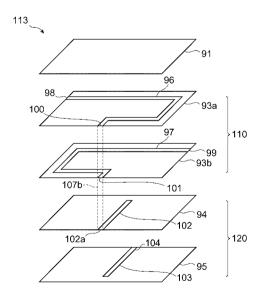

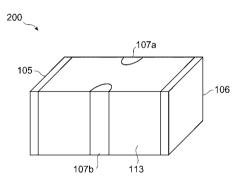

上述した回路構成を有する第2の実施形態の積層型フィルタは、図7及び図8に示すような構造を有している。図7は、第2の実施形態に係る積層型フィルタの素体部分を示す分解斜視図である。また、図8は、第2の実施形態に係る積層型フィルタの外形を示す斜視図である。図7に示されるように、積層型フィルタ200の素体部分(素体113)は、バリスタ部120、インダクタ部110及び保護層91が下方から順に積層された構造を有している。また、図8に示されるように、積層型フィルタ200は、素体113の長手方向の両端部に形成された一対の入出力電極105,106と、同じく素体113の側面に互いに対向するように形成された共通電極107a及び端子電極107bとを備えている。共通電極107aは、グランドに接続されるグランド電極である(上記回路構成における共通端子53又は共通端子63)。

#### [0049]

インダクタ部 1 1 0 は、導体パターン 9 6 , 9 7 (導体層)がそれぞれ設けられたインダクタ層 9 3 a , 9 3 b が積層されたものである。導体パターン 9 6 及び導体パターン 9 7 は、上述した回路構成において、一次側のコイル  $L_{5\,1}$  (コイル  $L_{6\,1}$  )及び 2 次側のコイル  $L_{5\,2}$  (コイル  $L_{6\,2}$  )をそれぞれ構成するものである。このインダクタ部 1 1 0 における導体パターン 9 6 , 9 7 やインダクタ層 9 3 a , 9 3 b の構成材料としては、上述した第 1 の実施形態における導体パターン 2 1 a ~ 2 4 a やインダクタ層 2 1 ~ 2 4 の構成材料と同様のものが挙げられる。

#### [0050]

導体パターン96の一方の端部98は、インダクタ層93aの一辺に引き出され、入力電極105に接続されている。導体パターン97の一方の端部99は、インダクタ層93bの一辺に引き出され、出力電極106に接続されている。また、導体パターン96,97の他方の端部100,101同士は、素体113の側面に形成された端子電極107bに接続されている。このように、導体パターン96及び導体パターン97によって、相互誘導素子54が構成されている。さらに、導体パターン96と導体パターン97とは、互いに対向する領域において容量結合しており、上述した回路構成におけるコンデンサ57を構成している。なお、導体パターン96及び97は、上記のような端子電極ではなく、スルーホール等によって接続されてもよい。

#### [0051]

バリスタ部120は、内部電極102,103がそれぞれ設けられたバリスタ層94,95が積層されてなるものである。内部電極102は、ストレートライン型のパターンを有しており、バリスタ層94の短手方向に沿って設けられている。この内部電極102の一方の端部102aは、バリスタ層94の縁部に引き出され、素体113の側面に形成された端子電極107bに接続されている。これにより、内部電極102が、導体パターン96,97の端部100,101にそれぞれ接続されている(上述した回路構成における接続端子55又は接続端子65)。

## [0052]

また、内部電極103は、ストレートライン型のパターンを有しており、バリスタ層95の短手方向に沿って、内部電極102と略平行に設けられている。この一方の端部104は、バリスタ層95の縁部に引き出され、素体113の側面に形成された共通電極107aに接続されている。

# [0053]

バリスタ部120においては、内部電極102,103と、これらの間に設けられたバリスタ層94とによって、バリスタVが構成されている。かかるバリスタ部120における内部電極102,103やバリスタ層94,95の構成材料としては、上述した第1の実施形態の内部電極31a,32aやバリスタ層31,32と同様の構成材料が挙げられる。

# [0054]

40

20

このような構成を有する本実施形態の積層型フィルタも、第1の実施形態と同様の構成材料からなるインダクタ層及びバリスタ層を備えることから、インダクタ部110とバリスタ部120との剥離が生じ難いものとなる。また、インダクタ層は、ZnOを主成分として含んでいるにもかかわらず高抵抗であり、優れたインダクタ特性を発揮し得るものとなる。

# [0055]

さらに、本実施形態の積層型フィルタは、図 5 又は図 6 に示すような回路構成を有していることから、特性インピーダンスに対する入力インピーダンスの整合が容易となる。このため、かかる積層型フィルタは、例えば、高圧の静電気等からの保護を可能としつつ、高速信号に対してもインピーダンス整合に優れたものとなる。

[0056]

以上、本発明の積層型フィルタ及びその製造方法の好適な実施形態について説明してきたが、本発明は必ずしも上述した実施形態に限定されるものではなく、その要旨を逸脱しない範囲で様々な変更が可能である。

#### [0057]

例えば、上記実施形態では、インダクタ部として、コイル状のパターンを形成し得る導体パターンが積層されてなるものを例示したが、これに限定されず、インダクタ部は、例えば、ストレートライン型の導体パターンが形成されたインダクタ層からなるものであってもよい。 具体的には、両端部を結ぶ直線状の導体パターンが設けられたインダクタ層を準備し、この単独層または複数層からなるものをインダクタ部としてもよい。この場合、直線状の導体パターンは、積層型フィルタにおける一対の入出力電極を接続する方向に設ける。このような構成を有するインダクタ部であっても、十分に優れたインダクタ特性を有するものとなる。

[0058]

さらに、本発明の積層型フィルタは、上述した等価回路やこれと同等の機能を有するものを構成できれば、その積層構造や電極等の形成位置を任意に変化させることができる。 すなわち、上述した実施形態ではバリスタ部の上にインダクタ部が設けられた構造を例示したが、例えば、一対のバリスタ部の間にインダクタ部が挟まれた構造としてもよい。また、入出力電極の位置関係は任意に変更してもよい。これらの構造を有する場合であっても、上述したような効果に優れる積層型フィルタが得られる。

[0059]

また、インダクタ部及びバリスタ部の積層数は、必ずしも上述した実施形態に限定されない。すなわち、例えば、導体パターンを備えるインダクタ層を繰り返し積層することで、コイルパターンにおけるターン数を更に増加させてもよい。また、内部電極が設けられたバリスタ層を更に繰り返して積層してもよい。これらの積層数は、所望とする積層型フィルタの特性にあわせて適宜調整することができる。

[0060]

ところで、積層型フィルタのインダクタ部において導体パターンを積層していると、インダクタ層を構成する材料が高誘電率を有する場合、積層方向に隣り合う導体パターンが結合して、当該導体パターン間に寄生容量が生じることになる。したがって、インダクタ部において導体パターンを積層した構成のものでは、特に、高周波用途への適用が困難な傾向にある。このような観点から、インダクタ層は、その誘電率が低い方が好ましく、具体的には、比誘電率が50以下であると好ましい。

【実施例】

[0061]

以下、本発明を実施例により更に詳細に説明するが、本発明はこれらの実施例に限定されるものではない。

「実施例1]

[0062]

(積層型フィルタの作製)

20

10

30

まず、上述した実施形態において図 4 を参照して説明した方法に従い、積層型フィルタの各サンプルを製造した。すなわち、まず、Z n O に P r  $_6$  O  $_1$   $_1$  、C o O 、C r  $_2$  O  $_3$  、C a C O  $_3$  、S i O  $_2$  、 K  $_2$  C O  $_3$  及び A 1  $_2$  O  $_3$  を添加したバリスタ層形成用ペーストを準備するとともに、Z n O に P r  $_6$  O  $_1$   $_1$  、C r  $_2$  O  $_3$  、C a C O  $_3$  、S i O  $_2$  及び K  $_3$  C O  $_3$  を添加したインダクタ層形成用のペーストを準備した。

#### [0063]

続いて、これらのペーストを用いて、バリスタシート及びインダクタシートを製造した。また、これとともに、ZnOのみを含む保護層形成用のグリーンシートを得た。その後、各シート上に、それぞれ図2に示すようなパターンとなるように、スクリーン印刷法により内部電極(バリスタ部)又は導体パターン(インダクタ部)形成用の導体ペーストを塗布した。なお、内部電極形成用のペーストとしては、Pdを主成分として含むものを用い、導体パターン形成用のペーストとしては、同様にPdを主成分として含むものを用いた。

# [0064]

次に、導体ペーストが塗布された各シート(バリスタシート及びインダクタシート)を、図2に示す順序で積層し、さらにこれらを一対の保護層形成用のグリーンシートで上下方向から挟んだ後、圧着して素体の前駆体である積層体を得た。こうして得られた積層体を焼成することにより素体を形成させた。そして、この素体に、Agペーストを焼き付けることにより入出力電極及びグランド電極を形成して、図1及び2に示す構造を有する積層型フィルタのサンプルを得た。

#### [0065]

なお、この実施例においては、後述するようなインダクタ部の特性評価を行うために、各サンプルの積層型フィルタにおけるインダクタ部中に、積層方向において平行に配置された一対の内部電極を設けた。図9は、インダクタ部に内部電極が設けられた状態の素体の断面構造を模式的に示す図である。図示されるように、各内部電極50は、それぞれの一方の端部が素体の対向する異なる端面にそれぞれ露出するように設けられており、これらの他方の端部は、積層方向からみて互いに重なり合うように設けられている。また、これらの内部電極は、いずれもコイルを構成する導体パターンとは接しないように設けられている。

# [0066]

(インダクタ部とバリスタ部との間の剥離の評価)

上述した方法により得られた積層型フィルタを観察したところ、いずれも、インダクタ 部とバリスタ部との間における剥離は認められなかった。

# [0067]

(インダクタ部の比誘電率及び抵抗率の測定)

得られた積層型フィルタを用い、各サンプルにおけるインダクタ部の比誘電率 ( ´)及び抵抗率(10<sup>6</sup> cm)を測定した。なお、比誘電率及び抵抗率の測定は以下に示すようにして行った。

# [0068]

すなわち、比誘電率 ( ´) は、インピーダンスアナライザ(4284A、ヒューレットパッカード社製)を用いて、各サンプルの、1MHz、入力信号レベル(測定電圧)1Vrmsの条件における静電容量(C)を測定し、得られた結果を、 ´= Cd/ 。Sの式に代入することにより算出した。また、抵抗率 ( ) は、各サンプルに1Vの直流電圧を印加した際に流れる電流値から抵抗(R)を求め、得られた結果を、 = RS/dの式に代入することにより算出した。なお、各式中、 。は真空の誘電率、dは図9に示した内部電極50間の距離、Sは内部電極50の重なり面積をそれぞれ示す。

#### [0069]

上記の測定の結果、インダクタ部の比誘電率は 2 0 ~ 3 0 であり、抵抗率は 1 × 1 0  $^6$  c m で あった。

# [0070]

50

20

以上のように、ZnOを主成分とし、添加物としてPr、Co及びAlを含むバリスタ層と、ZnOを主成分とし、Co及びAlを実質的に含有していないインダクタ層を有する積層型フィルタにおいては、バリスタ部とインダクタ部との剥離が極めて生じ難いことが確認された。また、この積層型フィルタにおけるインダクタ部は、比誘電率が50を下回り、また、抵抗率が1Mを超えることから、インダクタとして十分に実用可能であることが確認された。

#### 【図面の簡単な説明】

- [0071]

- 【図1】実施形態の積層型フィルタを示す斜視図である。

- 【図2】積層型フィルタの素体部分を示す分解斜視図である。

- 【図3】実施形態の積層型フィルタの等価回路を説明するための図である。

- 【図4】実施形態の積層型フィルタを製造する工程を説明するためのフロー図である。

- 【図5】第2の実施形態に係る積層型フィルタの回路構成を示す図である。

- 【図6】図5の回路構成を等価的に変換した回路構成を示す図である。

- 【 図 7 】 第 2 の 実 施 形 態 に 係 る 積 層 型 フィ ル タ の 素 体 部 分 を 模 式 的 に 示 す 分 解 斜 視 図 で ある。

- 【図8】第2の実施形態に係る積層型フィルタの外形を示す斜視図である。

- 【図9】インダクタ部に内部電極が設けられた状態の素体の断面構造を模式的に示す図である。

### 【符号の説明】

[0072]

3 ... 素体、5 , 7 ... 入出力電極、10 ... 積層型フィルタ、9 , 11 ... グランド電極、20 ... インダクタ部、21 , 22 , 23 , 24 ... インダクタ層、21 a , 22 a , 23 a , 24 a ... 導体パターン、21 b , 22 b , 23 b ... 貫通電極、30 ... バリスタ部、31 , 32 ... バリスタ層、31 a , 32 a ... 内部電極、41 , 42 ... 保護層、L ... コンデンサ、V ... バリスタ。

10

【図1】

【図2】 ----------- 21b 22a -20 22b 23a -23 23b -31a 30 32a

【図3】 【図4】

【図5】

【図6】

【図7】

# 【図8】

# 【図9】

# フロントページの続き

(72)発明者 佐藤 高弘

東京都中央区日本橋一丁目13番1号 TDK株式会社内

Fターム(参考) 5E034 CA08 CC03 DA07 DC01 DD05