(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4220351号 (P4220351)

(45) 発行日 平成21年2月4日(2009.2.4)

(24) 登録日 平成20年11月21日(2008.11.21)

(51) Int. CL. FLG11C 11/41 (2006, 01) G 1 1 C 11/34 Z G 1 1 C 11/413 (2006, 01) G 1 1 C 11/34 K G 1 1 C 11/34 1

> (全 23 頁) 請求項の数 32

特願2003-366262 (P2003-366262) (21) 出願番号 (22) 出願日 平成15年10月27日 (2003.10.27) (65) 公開番号 特開2004-146051 (P2004-146051A) (43) 公開日 平成16年5月20日(2004.5.20) 審査請求日 平成17年4月27日(2005.4.27) (31) 優先権主張番号 2002-065682

平成14年10月26日 (2002.10.26) (32) 優先日

(33) 優先権主張国 韓国(KR) ||(73)特許権者 390019839

三星電子株式会社

SAMSUNG ELECTRONICS CO., LTD.

大韓民国京畿道水原市靈通区梅灘洞416 416, Maetan-dong, Yeo ngtong-gu, Suwon-si, Gyeonggi-do 442-742

(KR)

||(74)代理人 100064908

弁理士 志賀 正武

|(74)代理人 100089037

弁理士 渡邊 隆

|(74)代理人 100108453

弁理士 村山 靖彦

最終頁に続く

(54) 【発明の名称】データ読み取り動作及び書き込み動作を同時に実行可能な集積回路及び方法

#### (57)【特許請求の範囲】

## 【請求項1】

入出力ポートが分離されており、クロック信号の1周期の間に書き込みアドレスと読み 取りアドレスとが入力される場合がある集積回路において、

複数のサブメモリブロックをそれぞれ具備するメモリブロックと、

前記メモリブロックに対応するキャッシュメモリブロックと、

前記書き込みアドレスまたは前記読み取りアドレスに応答して前記メモリブロック及び 前記キャッシュメモリブロックに格納されたデータを読み取るか、または前記メモリブロ ック及び前記キャッシュメモリブロックに前記データを書き込むタグメモリ制御部と、を 具備し、

前記タグメモリ制御部は、

前記クロック信号の1周期の間に入力される前記書き込みアドレス及び前記読み取りア ドレスの上位アドレスが同じである場合に、前記データの読み取り動作と書き込み動作と が前記メモリブロックと前記キャッシュメモリブロックとにそれぞれ分けられて前記1周 期の間に同時に実行されるように制御することを特徴とする集積回路。

## 【請求項2】

前記書き込みアドレス及び前記読み取りアドレスが相異なる場合、前記書き込みアドレ ス及び前記読み取りアドレスのそれぞれに対応する相異なる2個のサブメモリブロックが それぞれデコーディングされることを特徴とする請求項1に記載の集積回路。

#### 【請求項3】

(2)

前記集積回路は、

相互に分離されている書き込みアドレスデコーディングパスと読み取りアドレスデコー ディングパスとを具備し、

前記サブメモリブロックは、

前記書き込みアドレスデコーディングパスと前記読み取りアドレスデコーディングパスとにそれぞれ連結されることを特徴とする請求項1に記載の集積回路。

#### 【請求項4】

メモリブロック内部の相異なるサブメモリブロックのうち同じ下位アドレスを有するメモリセルは、前記キャッシュメモリブロックの1つのメモリセルに対応することを特徴とする請求項1に記載の集積回路。

【請求項5】

前記キャッシュメモリブロックのサイズは、前記1つのサブメモリブロックのサイズと同じであるか、それより大きいことを特徴とする請求項1に記載の集積回路。

### 【請求項6】

前記タグメモリ制御部は、前記キャッシュメモリブロックに対応する前記サブメモリブロックのアドレスを表すキャッシュメモリアドレス及び前記キャッシュメモリブロックに格納されているデータが有効であるかどうかを判断する有効判断情報を格納することを特徴とする請求項1に記載の集積回路。

#### 【請求項7】

前記タグメモリ制御部は、

前記サブメモリブロックのうち 1 つを選択する前記書き込みアドレスの上位アドレスと 前記読み取りアドレスの上位アドレスとが相等しい場合において、

前記書き込みアドレスと前記読み取りアドレスのいずれも前記キャッシュメモリアドレスと同一でなければ、前記読み取りアドレスに対応する前記メモリブロックで読み取り動作を実行して前記キャッシュメモリブロックで書き込み動作を実行し、

前記読み取り動作及び前記書き込み動作が同時に実行されることを特徴とする請求項 6 に記載の集積回路。

### 【請求項8】

前記タグメモリ制御部は、

前記サブメモリブロックのうち 1 つを選択する前記書き込みアドレスの上位アドレスと 前記読み取りアドレスの上位アドレスとが相等しい場合において、

前記書き込みアドレス及び前記読み取りアドレスのうち 1 つが前記キャッシュメモリアドレスと一致すれば、

前記キャッシュメモリアドレスと一致したアドレスに対応する動作が前記キャッシュメモリブロックで実行され、一致しないアドレスに対応する動作が前記メモリブロックで実行され、

前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致すれば、

前記キャッシュメモリブロックで読み取り動作が実行されて前記メモリブロックで書き 込み動作が実行され、

前記読み取り動作及び前記書き込み動作が同時に実行されることを特徴とする請求項 6 に記載の集積回路。

## 【請求項9】

前記タグメモリ制御部は、

前記サブメモリブロックのうち1つを選択する前記書き込みアドレスの上位アドレスと前記読み取りアドレスの上位アドレスとが相異なる場合において、

前記書き込みアドレス及び前記読み取りアドレスのうち1つが前記キャッシュメモリアドレスと一致すれば、

前記キャッシュメモリアドレスと一致したアドレスに対応する動作が前記キャッシュメ モリブロックで実行され、一致しないアドレスに対応する動作が前記メモリブロックで実 10

20

30

40

行され、

前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致すれば、

前記キャッシュメモリブロックで読み取り動作が実行されて前記メモリブロックで書き 込み動作が実行され、

前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致しなければ、

前記選択されたメモリブロックのうち前記書き込みアドレス及び前記読み取りアドレス に対応する相異なるサブメモリブロックで書き込み動作及び読み取り動作が実行され、

前記読み取り動作及び前記書き込み動作が同時に実行されることを特徴とする請求項 6 に記載の集積回路。

#### 【請求項10】

前記データは、SDRまたはDDRで入力または出力されることを特徴とする請求項1に記載の集積回路。

## 【請求項11】

入出力ポートが分離されている集積回路において、

複数のサブメモリブロックをそれぞれ具備するメモリブロックと、

前記それぞれのメモリブロックに対応し、所定のキャッシュ制御信号に応答して格納されたデータが出力されるか、またはデータが書き込まれる複数のキャッシュメモリブロックと、

前記それぞれのメモリブロックに対応し、書き込みアドレスまたは読み取りアドレス、 所定のデコーディング制御信号に応答して前記サブメモリブロックを制御するデコーディ ング信号を発生する複数のデコーディング部と、

書き込み選択信号または読み取り選択信号、前記書き込みアドレスまたは前記読み取りアドレスを受信し、クロック信号の1周期の間に入力される前記書き込みアドレスと前記読み取りアドレスとが同じである場合に、前記データの書き込み動作及び読み取り動作が前記1周期の間に同時に実行されるように前記キャッシュ制御信号または前記デコーディング制御信号を発生するタグメモリ制御部と、を具備することを特徴とする集積回路。

## 【請求項12】

前記デコーディング部は、それぞれ、前記サブメモリブロックに対応する複数のデコー ディング回路を具備することを特徴とする請求項11に記載の集積回路。

## 【請求項13】

前記デコーディング回路は、相互に分離されている書き込みアドレスデコーディングパス及び読み取りアドレスデコーディングパスと連結され、

前記サブメモリブロックは、前記書き込みアドレスデコーディングパスと前記読み取り アドレスデコーディングパスとにそれぞれ連結されることを特徴とする請求項12に記載 の集積回路。

#### 【請求項14】

前記書き込みアドレス及び前記読み取りアドレスが相異なる場合に、前記書き込みアドレス及び前記読取りアドレスにそれぞれ対応する相異なる2個のサブメモリブロックがそれぞれデコーディングされることを特徴とする請求項11に記載の集積回路。

#### 【請求項15】

前記メモリブロック内部の相異なるサブメモリブロックのうち同じ下位アドレスを有するメモリセルは、前記キャッシュメモリブロックの1つのメモリセルに対応することを特徴とする請求項11に記載の集積回路。

## 【請求項16】

前記キャッシュメモリブロックのサイズは、前記1つのサブメモリブロックのサイズと同じか、それより大きいことを特徴とする請求項11に記載の集積回路。

### 【請求項17】

前記タグメモリ制御部は、前記キャッシュメモリブロックに対応する前記サブメモリブ

20

10

30

40

ロックのアドレスを表すキャッシュメモリアドレス及び前記キャッシュメモリブロックに 格納されているデータが有効であるかを判断する有効判断情報を格納することを特徴とす る請求項11に記載の集積回路。

### 【請求項18】

前記タグメモリ制御部は、

前記サブメモリブロックのうち1つを選択する前記書き込みアドレスの上位アドレスと 前記読み取りアドレスの上位アドレスとが相等しい場合において、

前記書き込みアドレスと前記読み取りアドレスのいずれも前記キャッシュメモリアドレスと同一でなければ、前記デコーディング制御信号を発生して前記読み取りアドレスに対応する前記メモリブロックで読み取り動作を実行し、前記キャッシュメモリブロックで書き込み動作を実行し、

前記読み取り動作及び前記書き込み動作が同時に実行されることを特徴とする請求項 17 に記載の集積回路。

## 【請求項19】

前記タグメモリ制御部は、

前記サブメモリブロックのうち 1 つを選択する前記書き込みアドレスの上位アドレスと 前記読み取りアドレスの上位アドレスとが相等しい場合において、

前記書き込みアドレス及び前記読み取りアドレスのうち1つが前記キャッシュメモリアドレスと一致すれば、

前記キャッシュ制御信号を発生して前記キャッシュメモリアドレスと一致したアドレスに対応する動作を前記キャッシュメモリブロックで実行し、前記デコーディング制御信号を発生して前記キャッシュメモリアドレスと一致しないアドレスに対応する動作を前記メモリブロックで実行し、

前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致すれば、

前記キャッシュ制御信号を発生して前記キャッシュメモリブロックで読み取り動作を実行し、前記デコーディング制御信号を発生して前記メモリブロックで書き込み動作を実行し、

前記読み取り動作及び前記書き込み動作が同時に実行されることを特徴とする請求項 17 に記載の集積回路。

#### 【請求項20】

前記タグメモリ制御部は、

前記サブメモリブロックのうち 1 つを選択する前記書き込みアドレスの上位アドレスと前記読み取りアドレスの上位アドレスとが相異なる場合において、

前記書き込みアドレス及び前記読み取りアドレスのうち1つが前記キャッシュメモリアドレスと一致すれば、

前記キャッシュ制御信号を発生して前記キャッシュメモリアドレスと一致したアドレスに対応する動作を前記キャッシュメモリブロックで実行し、前記デコーディング制御信号を発生して前記キャッシュメモリアドレスと一致しないアドレスに対応する動作を前記メモリブロックで実行し、

前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致すれば、

前記キャッシュ制御信号を発生して前記キャッシュメモリブロックで読み取り動作を実行し、前記デコーディング制御信号を発生して前記メモリブロックで書き込み動作を実行し、

前記書き込みアドレス及び前記読み取りアドレスが全て前記キャッシュメモリアドレスと一致しなければ、

前記デコーディング制御信号を発生して前記選択されたメモリブロックのうち前記書き 込みアドレス及び前記読み取りアドレスに対応する相異なるサブメモリブロックで書き込 み動作及び読み取り動作を実行し、 10

20

30

40

前記読み取り動作及び前記書き込み動作が同時に実行されることを特徴とする請求項17に記載の集積回路。

#### 【請求項21】

前記データは、SDRまたはDDRで入力または出力されることを特徴とする請求項11に記載の集積回路。

## 【請求項22】

入出力ポートが分離されており、クロック信号の1周期の間に書き込みアドレスと読み取りアドレスとが入力される場合があり、複数のサブメモリブロックをそれぞれ具備する複数のメモリブロックと、前記メモリブロックに対応するキャッシュメモリブロックを具備する集積回路のデータの読み取り動作と書き込み動作とを同時に実行する方法において

10

- (a) クロック信号の1周期の間に前記書き込みアドレスと前記読み取りアドレスとが 共に入力されるか、前記書き込みアドレス及び前記読み取りアドレスのうち何れか1つだ け入力されるかを判断する段階と、

- (b)前記書き込みアドレスと前記読み取りアドレスとが共に入力されれば、前記書き込みアドレスの上位アドレスと前記読み取りアドレスの上位アドレスとが同一であるかどうかを判断する段階と、

- (c)前記書き込みアドレスの上位アドレスと前記読み取りアドレスの上位アドレスとが同一であれば、前記書き込みアドレスと前記読み取りアドレスとが所定のキャッシュメモリアドレスと同一であるかどうかを判断する段階と、

20

- (d)前記書き込みアドレスと前記読み取りアドレスのいずれも前記キャッシュメモリアドレスと同一でなければ、前記読取りアドレスに対応する前記メモリブロックで読み取り動作を実行し、前記キャッシュメモリブロックで書き込み動作を実行する段階と、を具備し、

- 前記(d)段階は、前記読み取り動作と前記書き込み動作とを前記クロック信号の1周期の間に同時に実行す<u>るこ</u>とを特徴とするデータの読み取り動作と書き込み動作とを同時に実行する方法。

#### 【請求項23】

前記(d)段階は、

(d1)前記キャッシュメモリブロックに格納されているデータが有効であるかどうかを判断する段階と、

30

- (d2)前記キャッシュメモリブロックに格納されているデータが有効でなければ、前記読み取りアドレスに対応する前記メモリブロックで読み取り動作を実行し、前記キャッシュメモリブロックで書き込み動作を実行する段階と、

- (d3)前記キャッシュメモリブロックに書き込まれたデータに関する情報をアップデートさせる段階と、

- (d4)前記キャッシュメモリブロックに格納されているデータが有効であれば、前記読み取りアドレスに対応する前記メモリブロックで読み取り動作を実行し、前記キャッシュメモリブロックに格納されている有効なデータを読み取って対応するメモリブロックに書き込む段階と、

40

(d5)前記キャッシュメモリブロックに書き込み動作を実行し、前記キャッシュメモリブロックに書き込まれたデータに関する情報をアップデートさせる段階と、を具備することを特徴とする請求項22に記載のデータの読み取り動作と書き込み動作とを同時に実行する方法。

#### 【請求項24】

前記キャッシュメモリアドレスは、前記キャッシュメモリブロックに対応する前記サブメモリブロックのアドレスを表すことを特徴とする請求項22に記載のデータの読み取り動作と書き込み動作とを同時に実行する方法。

### 【請求項25】

前記(c)段階は、

(c1)前記書き込みアドレス及び前記読み取りアドレスのうち1つが前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリアドレスと一致したアドレスに対応する動作を前記キャッシュメモリブロックで実行し、前記キャッシュメモリアドレスと一致しないアドレスに対応する動作を前記メモリブロックで実行する段階と、

( c 2 ) 前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリブロックで読み取り動作を実行し、前記メモリブロックで書き込み動作を実行し、前記メモリブロックに書き込まれたデータに関する情報をアップデートさせる段階と、を具備することを特徴とする請求項22に記載のデータの読み取り動作と書き込み動作とを同時に実行する方法。

## 【請求項26】

前記(b)段階は、

(b1)前記書き込みアドレスの上位アドレスと前記読み取りアドレスの上位アドレスとが同一でなければ、前記書き込みアドレスと前記読み取りアドレスとが前記キャッシュメモリアドレスと一致しているかを判断する段階と、

(b2)前記書き込みアドレス及び前記読み取りアドレスのうち何れか1つが前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリアドレスと一致したアドレスに対応する動作を前記キャッシュメモリブロックで実行し、前記キャッシュメモリアドレスと一致しないアドレスに対応する動作を前記メモリブロックで実行する段階と、

(b3)前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリブロックで読み取り動作を実行し、前記メモリブロックで書き込み動作を実行した後、前記メモリブロックに書き込まれたデータに関する情報をアップデートさせる段階と、

(b4)前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致しなければ、前記選択されたメモリブロックのうち前記書き込みアドレス及び前記読み取りアドレスに対応する相異なるサブメモリブロックで書き込み動作及び読み取り動作を実行する段階と、を具備することを特徴とする請求項22に記載のデータの読み取り動作と書き込み動作とを同時に実行する方法。

## 【請求項27】

前記(a)段階は、

(a1)前記書き込みアドレス及び前記読み取りアドレスのうち何れか1つだけ入力されれば、入力された前記書き込みアドレス及び前記読み取りアドレスのうち何れか1つが前記キャッシュメモリアドレスと一致するかを判断する段階と、

(a2)入力された前記書き込みアドレスまたは前記読み取りアドレスが前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリアドレスと一致した書き込みアドレスまたは読み取りアドレスに対応する動作を前記キャッシュメモリブロックで実行する段階と、

(a3)入力された前記書き込みアドレスまたは前記読み取りアドレスが前記キャッシュメモリアドレスと一致しなければ、前記キャッシュメモリアドレスと一致しない書き込みアドレスまたは読み取りアドレスに対応する動作を前記メモリブロックで実行する段階と、を具備することを特徴とする請求項22に記載のデータの読み取り動作と書き込み動作とを同時に実行する方法。

#### 【請求項28】

前記メモリブロック内部の相異なるサブメモリブロックのうち同じ下位アドレスを有するメモリセルは、前記キャッシュメモリブロックの1つのメモリセルに対応することを特徴とする請求項22に記載のデータの読み取り動作と書き込み動作とを同時に実行する方法。

#### 【請求項29】

前記キャッシュメモリブロックのサイズは、前記1つのサブメモリブロックのサイズと同じか、それより大きいことを特徴とする請求項22に記載のデータの読み取り動作と書き込み動作を同時に実行する方法。

10

20

30

20

30

40

50

## 【請求項30】

前記データは、SDRまたはDDRで入力または出力されることを特徴とする請求項22に記載のデータの読み取り動作と書き込み動作とを同時に実行する方法。

### 【請求項31】

分離された入力データポート及び出力データポートと、

複数のサブメモリブロックを具備するメモリブロックと、

1つのサブメモリブロックに格納されるデータと少なくとも同じ量のデータを格納できるキャッシュメモリブロックと、

対応するサブメモリブロックアドレスを有するキャッシュメモリブロックに有効なエントリーをはり、読み取り動作と書き込み動作とが実行されるアドレスが同じサブメモリブロックを指示する時、2つの動作のうち1つの動作を前記キャッシュメモリブロックを利用して実行することによって読み取り動作と書き込み動作とをクロック信号の1周期の間に同時に実行するように制御す<u>るタ</u>グメモリ制御部と、を具備することを特徴とする集積回路。

#### 【請求項32】

メモリブロックを複数のサブメモリブロックに区分する段階と、

1 つのサブメモリブロックに格納されるデータと少なくとも同じ量のデータを格納できるキャッシュメモリブロックを維持する段階と、

対応するサブメモリブロックアドレスを有するキャッシュメモリブロックに有効なエントリーをはる段階と、

読み取り動作と書き込み動作とが実行されるアドレスが同じメモリブロックを指示する時、2つの動作のうち1つの動作を前記キャッシュメモリブロックを利用して実行することによって読み取り動作と書き込み動作とをクロック信号の1周期の間に同時に実行し、

可能な場合に、相異なるサブメモリブロックでクロック信号の1周期の間に同時に読み取り動作と書き込み動作とを実行する段階と、を具備することを特徴とする、集積回路で同時に読み取り動作及び書き込み動作を実行する方法。

### 【発明の詳細な説明】

## 【技術分野】

### [0001]

本発明は、集積回路に係り、特に入出力ポートが分離された集積回路においてデータ読取り動作と書き込み動作とを同時に実行可能な集積回路及び方法に関する。

#### 【背景技術】

## [0002]

一般的な同期式RAM(Synchronous RAM:SRAM)は、1つのクロック周期毎に読取りデータまたは書き込みデータのうち何れか1つだけを伝送できる。

#### [0003]

二重データ率RAM(Double Data Rate RAM: DRAM)は、クロックの立上がリエッジと立下リエッジ毎にデータを伝送することによってデータ伝送率を倍増させた。しかし、一般的なメモリ装置はデータの入力とデータの出力とが1つのピンを通じて行われる。共通入出力ポートを利用する方法は、データの入力と出力とが独立して制御されないので、データの入力周波数と出力周波数とが制限される。

## [0004]

メモリ装置の帯域幅が重要になったことに対応して、分離された入出力ポートを使用する製品が登場した。すなわち、データの入力と出力とが独立して制御できるように入力ピンと出力ピンとが分離された製品である。分離された入力ピンと出力ピンとを有するメモリ装置は、クロックの1周期内に読み取り命令及び読み取りアドレス、又は、書き込み命令及び書き込みアドレス及び書き込みデータを共に受信できるので、動作周波数を増加させうる。

## [0005]

しかし、分離された入出力ポートを有するメモリ装置でも1つのクロック周期内で読み

取り命令及び読み取りアドレス、又は、書き込み命令及び書き込みアドレス及び書き込み データを受信する場合、読み取り動作と書き込み動作とが1つのクロック周期内に実行されるためには、2回のメモリセルアクセスが実行されなければならない。

#### [0006]

すなわち、データの読み取りと書き込みとのためのワードラインの活性化がクロックの1周期内において2回実行されなければならないので、クロック周波数がワードラインの活性化時間によって制限される問題がある。

## [0007]

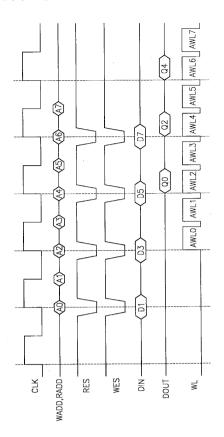

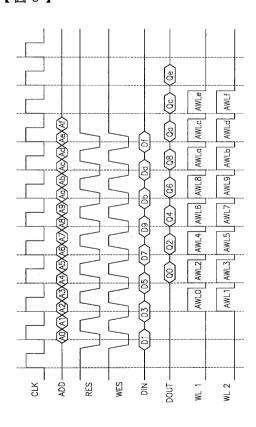

図1は、分離された入出力ポートを有するメモリ装置の動作を説明するタイミング図である。

10

## [0008]

アドレスとワードラインとの間の関係や入力データ及び出力データのレイテンシ(1atency)はメモリ装置の回路構成によって変わるので、図1では考慮されない。

#### [0009]

図1を参照すれば、クロック信号CLKの1周期内で書き込みアドレスWADDと読み取りアドレスRADDとが共に入力されている。クロック信号CLKの立上がリエッジで入力されるアドレスA0、A2、A4、A6が読み取りアドレスRADDであり、クロック信号CLKの立下リエッジで入力されるアドレスA1、A3、A5、A7が書き込みアドレスWADDである。

## [0010]

20

RESとWESは、それぞれ読取りアドレスRADDと書き込みアドレスWADDとを選択する読み取り選択信号及び書き込み選択信号である。

#### [0011]

読み取りアドレスRADD=A0によってワードラインAWL0が活性化され、ワードラインAWL0に応答してデータQ0が出力される。また、書き込みアドレスWADD=A1に応答してワードラインAWL1が活性化されれば、入力データD1が入力される。

#### [0012]

したがって、読み取り動作のためのワードラインAWL0と書き込み動作のためのワードラインAWL1との活性化のためにクロック信号CLKの1周期の長さが制限される。 すなわち、クロック信号の1周期の間にそれぞれ異なるアドレスを有するメモリセルに順次にアクセスしなければならないので、クロック信号CLKの周期を縮め難い問題がある

30

#### 【発明の開示】

【発明が解決しようとする課題】

## [0013]

本発明が解決しようとする技術的課題は、クロック信号の1周期内でメモリセルについての読み取り動作及び書き込み動作を同時に実行させることによってクロック信号の動作 周波数を増加させうる集積回路を提供するところにある。

## [0014]

本発明が解決しようとする他の技術的課題は、クロック信号の1周期内でメモリセルについての読み取り動作及び書き込み動作を同時に実行させることによってクロック信号の動作周波数を増加させうる方法を提供するところにある。

40

## 【課題を解決するための手段】

## [0015]

前記技術的課題を達成するための本発明の第1実施例による集積回路は、入出力ポートが分離されており、クロック信号の1周期の間に書き込みアドレスと読み取りアドレスとが入力される集積回路において、複数のサブメモリブロックをそれぞれ具備するメモリブロック、前記メモリブロックに対応するキャッシュメモリブロック及びタグメモリ制御部を具備する。

## [0016]

20

30

40

50

タグメモリ制御部は、前記書き込みアドレスまたは前記読み取りアドレスに応答して前記メモリブロック及び前記キャッシュメモリブロックに格納されたデータを読み取るか前記メモリブロック及び前記キャッシュメモリブロックに前記データを書き込む。

#### [0017]

特に、タグメモリ制御部は、前記書き込みアドレス及び前記読み取りアドレスが同じである場合に、前記データの読み取り動作と書き込み動作とが前記メモリブロックと前記キャッシュメモリブロックにそれぞれ分けられて同時に実行されるように制御することを特徴とする。

#### [0018]

前記書き込みアドレス及び前記読み取りアドレスが異なる場合、前記それぞれの書き込み及び読み取りアドレスに対応する相異なる2個のサブメモリブロックがそれぞれデコーディングされる。

#### [0019]

前記集積回路は、相互分離されている書き込みアドレスデコーディングパスと読み取りアドレスデコーディングパスとを具備し、前記サブメモリブロックは、前記書き込みアドレスデコーディングパスと前記読み取りアドレスデコーディングパスとにそれぞれ連結される。

## [0020]

メモリブロック内部の相異なるサブメモリブロックのうち同じ下位アドレスを有するメモリセルは、前記キャッシュメモリブロックの1つのメモリセルに対応する。前記キャッシュメモリブロックのサイズは、前記1つのサブメモリブロックのサイズと同じか、それより大きい。

#### [0021]

前記タグメモリ制御部は、前記キャッシュメモリブロックに対応する前記サブメモリブロックのアドレスを表すキャッシュメモリアドレス及び前記キャッシュメモリブロックに格納されているデータが有効であるかどうかを判断する有効判断情報を格納する。

#### [0022]

前記タグメモリ制御部は、前記サブメモリブロックのうち1つを選択する前記書き込みアドレスの上位アドレスと前記読み取りアドレスの上位アドレスとが相等しい場合、前記書き込みアドレス及び前記読み取りアドレスのいずれも前記キャッシュメモリアドレスと同一でなければ、前記読み取りアドレスに対応する前記メモリブロックで読み取り動作を実行し、前記キャッシュメモリブロックで書き込み動作を実行し、前記読み取り動作及び前記書き込み動作が同時に実行される。

#### [0023]

前記タグメモリ制御部は、前記サブメモリブロックのうち1つを選択する前記書き込みアドレスの上位アドレスと前記読み取りアドレスの上位アドレスが相等しい場合、前記書き込みアドレス及び前記読み取りアドレスのうち1つが前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリアドレスと一致したアドレスに対応する動作が前記キャッシュメモリブロックで実行されて、一致しないアドレスに対応する動作が前記メモリブロックで実行される。

## [0024]

前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリブロックで読み取り動作が実行され、前記メモリブロックで書き込み動作が実行されて前記読み取り動作及び前記書き込み動作が同時に実行される。

## [0025]

前記タグメモリ制御部は、前記サブメモリブロックのうち1つを選択する前記書き込み アドレスの上位アドレスと前記読み取りアドレスの上位アドレスとが相異なる場合、前記 書き込みアドレス及び前記読み取りアドレスのうち1つが前記キャッシュメモリアドレス と一致すれば、前記キャッシュメモリアドレスと一致したアドレスに対応する動作が前記

20

30

40

50

キャッシュメモリブロックで実行され、一致しないアドレスに対応する動作が前記メモリブロックで実行される。

#### [0026]

前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリブロックで読み取り動作が実行され、前記メモリブロックで書き込み動作が実行される。

#### [0027]

前記書き込みアドレス及び前記読み取りアドレスが全て前記キャッシュメモリアドレスと一致しないと、前記選択されたメモリブロックのうち前記書き込みアドレス及び前記読み取りアドレスに対応する相異なるサブメモリブロックで書き込み動作及び読み取り動作が実行され、前記読み取り動作及び前記書き込み動作が同時に実行される。

#### [0028]

前記データは、単一データ率(Single Data Rate:SDR)または二重データ率(Double Data Rate:DDR)で入力または出力される。

#### [0029]

前記技術的課題を達成するための本発明の第2実施例に集積回路は、入出力ポートが分離されている集積回路において複数のサブメモリブロックをそれぞれ具備するメモリブロック、キャッシュメモリブロック、デコーディング部及びタグメモリ制御部を具備する。

#### [0030]

キャッシュメモリブロックは、前記それぞれのメモリブロックに対応し、所定のキャッシュ制御信号に応答して格納されたデータが出力されるか、またはデータが書き込まれる。デコーディング部は、前記それぞれのメモリブロックに対応し、書き込みアドレスまたは読み取りアドレス、所定のデコーディング制御信号に応答して前記サブメモリブロックを制御するデコーディング信号を発生する。

#### [0031]

タグメモリ制御部は、書き込み選択信号または読み取り選択信号、前記書き込みアドレスまたは前記読み取りアドレスを受信し、クロック信号の1周期の間に入力される前記書き込みアドレスと前記読み取りアドレスとが同一であるかによって前記データの書き込み動作及び読み取り動作が同時に実行されるように前記キャッシュ制御信号または前記デコーディング制御信号を発生する。

## [0032]

前記デコーディング部は、それぞれ前記サブメモリブロックに対応する複数のデコーディング回路を具備する。前記デコーディング回路は相互分離されている書き込みアドレスデコーディングパス及び読み取りアドレスデコーディングパスと連結し、前記サブメモリブロックは前記書き込みアドレスデコーディングパスと前記読み取りアドレスデコーディングパスとにそれぞれ連結する。

## [0033]

前記他の技術的課題を達成するための本発明の第1実施例によるデータ読み取り動作と書き込み動作とを同時に実行する方法は、入出力ポートが分離されており、クロック信号の1周期の間に書き込みアドレスと読み取りアドレスとが入力され、複数のサブメモリブロックをそれぞれ具備する複数のメモリブロックと、前記メモリブロックに対応するキ積回路のデータ読み取り動作と書き込み動作とを同時に実行する方法において、(a)クロック信号の1周期の間に前記書き込みアドレスと前記読み取りアドレスとが全て入力されているか、前記書き込みアドレス及び前記読み取りアドレスのうち何れか1つだけ入力されているかを判断する段階、(b)前記書き込みアドレスの上位アドレスとが同一であるかを判断する段階、(c)前記書き込みアドレスが同一であれば、前記書き込みアドレスが同一であれば、前記書き込みアドレスが同一であれば、前記書き込みアドレスと前記読み取りアドレスの上位アドレスと前記読み取りアドレスの上位アドレスと前記読み取りアドレスの上位アドレスとが所定のキャッシュメモリアドレスと同一であるかを判断する段階、及び、(d)前記書き込みアドレス及び前記読み取りアド

20

30

40

50

レスのいずれも前記キャッシュメモリアドレスと同一でなければ、前記読み取りアドレス に対応する前記メモリブロックで読み取り動作を実行し、前記キャッシュメモリブロック で書き込み動作を実行する段階を具備する。

#### [0034]

前記d段階は、(d1)前記キャッシュメモリブロックに格納されているデータが有効であるかどうかを判断する段階、(d2)前記キャッシュメモリブロックに格納されているデータが有効でなければ、前記読み取りアドレスに対応する前記メモリブロックで読み取り動作を実行し、前記キャッシュメモリブロックで書き込み動作を実行する段階、(d3)前記キャッシュメモリブロックに書き込まれたデータに関する情報をアップデートさせる段階、(d4)前記キャッシュメモリブロックに格納されているデータが有効であれば、前記読み取りアドレスに対応する前記メモリブロックで読み取り動作を実行し、前記キャッシュメモリにかくのうされている有効なデータを読み取って対応するメモリブロックに書き込む段階、及び、(d5)前記キャッシュメモリブロックに書き込み動作を実行し、前記キャッシュメモリブロックに書き込まれたデータに関する情報をアップデートさせる段階を具備する。

#### [0035]

前記キャッシュメモリアドレスは、前記キャッシュメモリブロックに対応する前記サブメモリブロックのアドレスを示す。

#### [0036]

前記(c)は、(c1)前記書き込みアドレス及び前記読み取りアドレスのうち1つが前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリアドレスと一致したアドレスとに対応する動作を前記キャッシュメモリブロックで実行し、前記キャッシュメモリアドレスと一致しないアドレスに対応する動作を前記メモリブロックで実行する段階、及び、(c2)前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリブロックで読み取り動作を実行し、前記メモリブロックで書き込まれたデータに関する情報をアップデートさせる段階を具備する。

#### [0037]

前記(b)段階は、(b1)前記書き込みアドレスの上位アドレスと前記読み取りアドレスの上位アドレスとが同一でなければ、前記書き込みアドレスと前記読み取りアドレスとが前記キャッシュメモリアドレスと一致するかを判断する段階、(b2)前記書き込みアドレス及び前記読み取りアドレスのうち何れか1つが前記キャッシュメモリアドレスと一致したアドレスに対応する動作を前記レスと一致すれば、前記キャッシュメモリアドレスと一致したアドレスと一致しないアドレスとーないので実行し、前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリアドレスとーなければ、前記キャッシュメモリブロックで書き込み取りアドレスが共に前記キャッシュメモリブロックで書き込み動作を後、前記メモリブロックに書き込まれたデータに関する情報をアップデートさせっシュメモリブロックで読み取りかに書き込みアドレス及び前記読み取りアドレスとでする段階をリブロックで書き込みかけし、方に対応する相異なるサブメモリブロックで書き込みすたス及び前記読み取りかで書き込み動作及び読み取り動作を実行する段階を具備する。

## [0038]

前記(a)段階は、(a1)前記書き込みアドレス及び前記読み取りアドレスのうち何れか1つだけ入力されれば、入力された前記書き込みアドレス及び前記読み取りアドレスのうち何れか1つが前記キャッシュメモリアドレスと一致するかを判断する段階、(a2)入力された前記書き込みアドレスまたは前記読み取りアドレスが前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリアドレスと一致した書き込みアドレスまたは読み取りアドレスに対応する動作を前記キャッシュメモリプロックで実行する段階、及び、(a3)入力された前記書き込みアドレスまたは前記読み取りアドレスが前記キャッ

シュメモリアドレスと一致しなければ、前記キャッシュメモリアドレスと一致しない書き 込みアドレスまたは読み取りアドレスに対応する動作を前記メモリブロックで実行する段 階を具備する。

### [0039]

前記メモリブロック内部の相異なるサブメモリブロックのうち同じ下位アドレスを有するメモリセルは前記キャッシュメモリブロックの 1 つのメモリセルに対応することを特徴とする。

## [0040]

前記キャッシュメモリブロックのサイズは前記1つのサブメモリブロックのサイズと同じであるか大きいことを特徴とする。

10

## 【発明の効果】

#### [0041]

本発明による集積回路及びの読み取り動作と書き込み動作とを同時に実行する方法は、メモリブロックを複数のサブメモリブロックに区分し、それぞれのサブメモリブロックをデコーディングできるデコーディング回路と、あらゆるサブメモリブロックに連結される書き込みアドレスデコーディングパスと読み取りアドレスデコーディングパスとを別途に具備し、キャッシュメモリブロックを具備してクロック信号の1周期内で読み取り動作及び書き込み動作がメモリブロックとキャッシュメモリブロックとで分けられて同時に実行させることによって、クロック信号の動作周波数を増加させうる長所がある。

【発明を実施するための最良の形態】

20

### [0042]

本発明とその動作上の利点及び本発明の実施によって達成される目的を十分に理解するためには本発明の望ましい実施例を例示する図面及び図面に記載された内容が参照されるべきである。

#### [0043]

以下、図面を参照して本発明の望ましい実施例を説明することによって、本発明を詳細に説明する。各図面に提示された同じ符号は同じ構成要素を示す。

#### [0044]

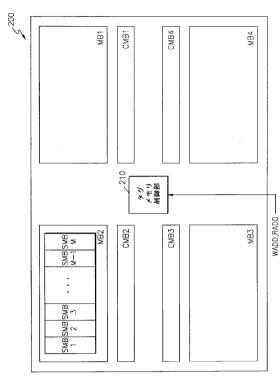

図 2 は、第 1 実施例による集積回路を示すブロック図である。図 2 を参照すれば、集積回路 2 0 0 は、複数のサブメモリブロック S M B 1 、 S M B 2 ~ S M B Mをそれぞれ具備するメモリブロック M B 1、 M B 2、 M B 3、 M B 4 と、それらのメモリブロック M B 1、 M B 2、 M B 3、 M B 4 に対応するキャッシュメモリブロック C M B 1、 C M B 2、 C M B 3、 C M B 4 と、タグメモリ制御部 2 1 0 とを具備する。図 2 の集積回路 2 0 0 は入出力ポートが分離されており、クロック信号の 1 周期の間に書き込みアドレスW A D D と読み取りアドレス R A D D とが入力される。

[0045]

メモリブロック M B 1、 M B 2、 M B 3、 M B 4 は相等しい構造であり、キャッシュメモリブロック C M B 1、 C M B 2、 C M B 3、 C M B 4 も相等しい構造であるので、メモリブロック M B 1、 M B 2、 M B 3、 M B 4 のうち第 2 のメモリブロック M B 2 と第 2 のキャッシュメモリブロック C M B 2 を中心として説明する。

40

30

## [0046]

書き込みアドレスWADD及び読み取りアドレスRADDは、それぞれ上位アドレスと下位アドレスとに区分される。上位アドレスは、複数のサブメモリブロックのうち何れか1つを指定するアドレスである。

#### [0047]

本発明の基本原理は、書き込みアドレスWADD及び読み取りアドレスRADDが同じである場合に、データの読み取り動作と書き込み動作とがメモリブロックとキャッシュメモリブロックとにそれぞれ分けられて同時に実行されることによってクロック信号の周期を短くされる点にある。

## [0048]

すなわち、書き込みアドレスWADDと読み取りアドレスRADDとが同一で同時に1つのメモリブロック(例えば、第2メモリブロックMB2)のうち同じサブメモリブロック(例えば、SMB2)にアクセスすべき場合に、サブメモリブロックSMB2でデータの読み取り動作が実行されれば、データの書き込み動作はサブメモリブロックSMB2に対応するキャッシュメモリブロックCMB2で実行させる。

#### [0049]

逆に、メモリブロックMB2でデータの書き込み動作が実行されれば、データの読み取り動作は、メモリブロックMB2に対応するキャッシュメモリブロックCMB2で実行させる。このようにすることによって、データの読み取り動作及び書き込み動作が同時に並列的に行われ、クロック信号の周期を短くすることができる。

## [0050]

このために、メモリブロックMB2内部の相異なるサブメモリブロックSMB1、SMB2、SMB3~SMBMのうち同じ下位アドレスを有するメモリセルは、キャッシュメモリブロックCMB2の1つのメモリセルに対応させられる。また、同じサブメモリブロックに対して書き込み動作と読み取り動作とが実行され続ける場合も発生しうるので、キャッシュメモリブロックのサイズは、1つのサブメモリブロックのサイズと同じであるか、それよりも大きくなければならない。

## [0051]

このような動作は、タグメモリ制御部210によって実行される。タグメモリ制御部210は、書き込みアドレスWADDまたは読み取りアドレスRADDに応答してメモリブロックMB1、MB2、MB3、MB4及びキャッシュメモリブロックCMB1、CMB2、CMB3、CMB4に格納されたデータを読み取るか、メモリブロックMB1、MB2、MB3、MB4及びキャッシュメモリブロックCMB1、CMB2、CMB3、CMB4にデータを書き込む。

#### [0052]

書き込みアドレスWADDと読取りアドレスRADDとが同一であり、メモリブロックMB2のうち1つのサブメモリブロックで読み取り動作が実行され、キャッシュメモリブロックCMB2に書き込まれたデータが元々書き込まれるべきメモリブロックMB2のうちサブメモリブロックのアドレスがキャッシュメモリアドレスとしてタグメモリ制御部210に格納される

## [0053]

すなわち、キャッシュメモリアドレスは、キャッシュメモリブロック CNB2 に格納されているデータが元々格納されるべきサブメモリブロックを指定する上位アドレスである

#### [0054]

入力されるアドレスのうちから下位アドレスを利用してタグメモリ制御部 2 1 0 に格納されたキャッシュメモリアドレスにアクセスし、アクセスされたキャッシュメモリアドレスと入力されたアドレスの上位アドレスとが比較される。

## [0055]

次回の書き込みアドレスWADDと読み取りアドレスRADDとが同一であり、また以前の書き込みアドレスWADDと読み取りアドレスRADDとも同一であるために、キャッシュメモリブロックCMB2に再び書き込み動作が実行されるべき場合がある。この場合、キャッシュメモリブロックCMB2に先に書き込まれていたデータが有効なデータであるかどうかを判断しなければならない。

## [0056]

有効なデータであれば、キャッシュメモリブロック CMB2 に先に書き込まれているデータを読み取ってメモリブロック MB2 の対応するサブメモリブロックに書き込んだ後、次回の書き込みアドレスWADDに対応するデータをキャッシュメモリブロック CMB2 に書き込まなければならないためである。キャッシュメモリブロック CMB2 に格納され

10

20

30

40

ているデータが有効であるかを判断する有効判断情報もタグメモリ制御部 2 1 0 に格納される。

## [0057]

また、書き込みアドレスWADD及び読み取りアドレスRADDが相異なる場合、それぞれの書き込みアドレスWADD、読み取りアドレスRADDに対応する相異なる2個のサブメモリブロックがそれぞれデコーディングされる。

#### [0058]

このために、集積回路200は、書き込みアドレスデコーディングパス(図示せず)と読み取りアドレスデコーディングパス(図示せず)が相互に独立するように分離されなければならない。そして、サブメモリブロックSMB1、SMB2、SMB3~SMBMは、書き込みアドレスデコーディングパスと読み取りアドレスデコーディングパスとにそれぞれ連結されねばならない。

#### [0059]

データは、SDRまたはDDRにおいて、入力ピンまたは出力ピンを通じて入力または出力される。

#### [0060]

タグメモリ制御部 2 1 0 がメモリブロック M B 2 及びキャッシュメモリブロック C M B 2 を制御してデータの読み取り及び書き込みを実行する動作は、図 3 及び図 4 を参照して後述する。

## [0061]

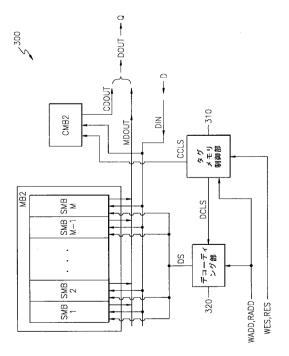

図3は、第2実施例による集積回路を示すブロック図である。集積回路300は、複数のサブメモリブロックSMB1、SMB2、SMB3~SMBMをそれぞれ含むメモリブロック、キャッシュメモリブロック、デコーディング部及びタグメモリ制御部310を具備する。

### [0062]

キャッシュメモリブロックはそれぞれのメモリブロックに対応し、所定のキャッシュ制御信号 C C L S に応答して格納されたデータが出力されるか、またはデータが書き込まれる。デコーディング部はそれぞれのメモリブロックに対応し、書き込みアドレスW A D D または読み取りアドレス R A D D、所定のデコーディング制御信号 D C L S に応答してサブメモリブロック S M B 1、 S M B 2、 S M B 3 ~ S M B M を制御するデコーディング信号 D S を発生する。

## [0063]

図 3 は、複数のメモリブロックのうち 1 つのメモリブロック M B 2 と複数のデコーディング部のうち 1 つのデコーディング部 3 2 0 、複数のキャッシュメモリブロックのうち 1 つのキャッシュメモリブロック C M B 2 を図示している。

#### [0064]

したがって、第2実施例による集積回路300の動作の説明も図3に示したメモリブロックMB2とキャッシュメモリブロックCMB2、デコーディング部320及びタグメモリ制御部310を利用して説明する。

#### [0065]

タグメモリ制御部310は、書き込み選択信号WESまたは読取り選択信号RES、書き込みアドレスWADDまたは読み取りアドレスRADDを受信し、クロック信号の1周期の間に入力される書き込みアドレスWADDと読取りアドレスRADDとが同じであるかどうかに応じて、データの書き込み動作及び読み取り動作が同時に実行されるようにキャッシュ制御信号CCLSまたはデコーディング制御信号DCLSを発生する。また、図面には示されていないが、読み取り選択信号RES及び書き込み選択信号WESもメモリブロックMB2及びキャッシュメモリブロックCMB2に印加されうる。

#### [0066]

図2の集積回路200と同様に前記デコーディング部は、それぞれサブメモリブロックSMB1、SMB2、SMB3~SMBMに対応する複数のデコーディング回路(図示せ

10

20

30

40

ず)を具備する。入力される書き込みアドレスWADD及び読み取りアドレスRADDが相異なる場合、それぞれの書き込みアドレスWADD、読み取りアドレスRADDに対応する相異なる2個のサブメモリブロックがそれぞれデコーディングされなければならないためである。

## [0067]

このために、デコーディング回路(図示せず)は、相互に分離されている書き込みアドレスデコーディングパス(図示せず)及び読み取りアドレスデコーディングパス(図示せず)と連結され、サブメモリブロックSMB1、SMB2、SMB3~SMBMは、書き込みアドレスデコーディングパス(図示せず)及び読み取りアドレスデコーディングパス(図示せず)にそれぞれ連結される。

[0068]

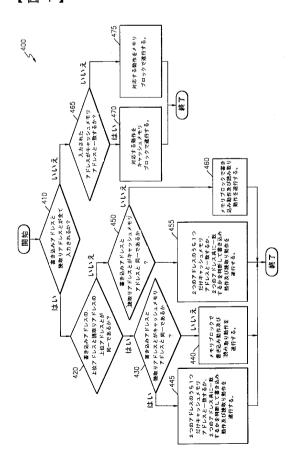

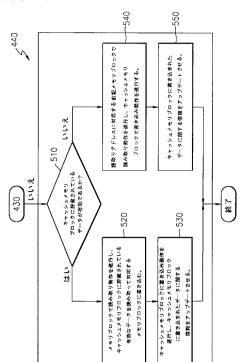

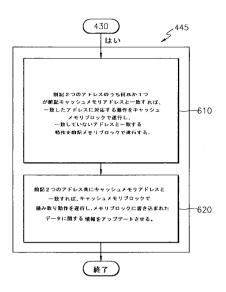

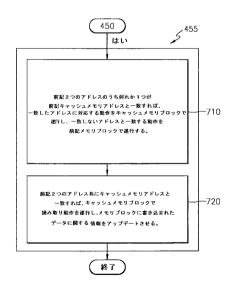

図4は、他の実施例によるデータの読み取り動作と書き込み動作とを同時に実行する方法を示すフローチャートである。図5は、図4の段階440を説明するフローチャートである。図6は、図4の段階445を説明するフローチャートである。図7は、図4の段階455を説明するフローチャートである。

[0069]

以下、図2ないし図7を参照してデータの読み取り動作と書き込み動作とを同時に実行する集積回路及び方法について説明する。

[0070]

まず、クロック信号の1周期の間に書き込みアドレスと読取りアドレスとが共に入力されるか、書き込みアドレス及び読み取りアドレスのうち何れか1つだけ入力されるかを判断する(段階410段階)。図3の書き込み選択信号WES及び読み取り選択信号RESによって判断されうる。

[0071]

ここでは、書き込み選択信号WESがローレベルであるか、読み取り選択信号RESがローレベルである場合に、それぞれ書き込みアドレスWADDと読み取りアドレスRADDとが入力されるものとする。もちろん、書き込み選択信号WES及び読み取り選択信号RESのレベルがハイレバルである場合に書き込みアドレスWADDと読み取りアドレスRADDとが入力されるように回路を構成することもできる。

[0072]

タグメモリ制御部 3 1 0 は、書き込み選択信号WESと読み取り選択信号RESとを受信し、書き込みアドレスWADDと読み取りアドレスRADDとを受信する。

[0073]

書き込みアドレスと読み取りアドレスとが共に入力されれば、書き込みアドレスの上位 アドレスと読み取りアドレスの上位アドレスとが同一であるかを判断する(段階 4 2 0 )

[0074]

書き込みアドレスWADDや読み取りアドレスRADDは、上位ビットにサブメモリブロックを指定する情報を有している。したがって、書き込みアドレスWADDや読み取りアドレスRADDが入力されれば、まず、書き込みアドレスWADDや読み取りアドレスRADDの上位アドレスを認識して、どのサブメモリブロックを指定するかを判断する。

[0075]

書き込みアドレスの上位アドレスと読み取りアドレスの上位アドレスとが同一であれば、書き込みアドレスと読み取りアドレスとが所定のキャッシュメモリアドレスと同一であるかを判断する(段階 4 3 0 )。

[0076]

書き込みアドレスWADDの上位アドレスと読み取りアドレスRADDの上位アドレスとが同一であれば、書き込みアドレスWADD及び読み取りアドレスRADDが同じサブメモリブロックを指定している。

[0077]

10

20

30

タグメモリ制御部310はキャッシュメモリアドレスを内部に格納している。キャッシュメモリアドレスは、キャッシュメモリブロック C M B 2 に対応するサブメモリブロックのアドレスを示す。もし書き込みアドレスW A D D がキャッシュメモリアドレスと同一であれば、書き込み動作はキャッシュメモリブロック C M B 2 で実行されなければならない

[0078]

書き込みアドレスと読み取りアドレスのいずれも前記キャッシュメモリアドレスと同一でなければ、前記読み取りアドレスに対応する前記メモリブロックで読み取り動作を実行し、前記キャッシュメモリブロックで書き込み動作を実行する(段階 4 4 0 )。

[0079]

段階 4 4 0 を図 5 を参照してもうさらに説明する。書き込みアドレスと読み取りアドレスのいずれも前記キャッシュメモリアドレスと同一でなければ、前記キャッシュメモリブロックに格納されているデータが有効であるかを判断する(段階 5 1 0 )。

[0800]

書き込みアドレスWADDと読み取りアドレスRADDのいずれも前記キャッシュメモリアドレスと同一でないことは、結局、メモリブロックMB2の同じサブメモリブロックで書き込み動作及び読み取り動作が実行されなければならないことを意味する。しかし、同じサブメモリブロックで書き込みワードラインと読み取りワードラインとを同時にイネーブルすることはできない。したがって、キャッシュメモリブロックCMB2を利用する

[0081]

前記キャッシュメモリブロックに格納されているデータが有効でなければ、前記読み取りアドレスに対応する前記メモリブロックで読み取り動作を実行し、前記キャッシュメモリブロックで書き込み動作を実行する(段階 5 4 0 )。

[0082]

書き込み動作と読み取り動作とが同じサブメモリブロックで実行されるべき場合は、読み取り動作が優先的に実行される。したがって、読み取りアドレスRADDに対応するメモリブロックMB2のサブメモリブロックで読み取り動作を実行する。そして、キャッシュメモリブロックCMB2に格納されていたデータが有効でないので、キャッシュメモリブロックCMB2に書き込み動作を実行する。

[0083]

タグメモリ制御部310はデコーディング制御信号DCLSをデコーディング部320に印加する。すると、デコーディング部320内部のデコーディング回路(図示せず)のうち読み取りアドレスRADDに対応するデコーディング回路は、デコーディング信号DSを発生して対応するサブメモリブロックをデコーディングする。すると、サブメモリブロックに格納されたデータが出力される。図3において、MDOUTは、メモリブロックMB2に格納されたデータが出力される経路である。Qは、出力ピンを意味する。出力ピンQと入力ピンDとは、分離されている。

[0084]

また、タグメモリ制御部310は、キャッシュ制御信号CCLSを発生してキャッシュ メモリブロックMB2で書き込み動作を実行する。

**[** 0 0 8 5 **]**

キャッシュメモリブロック C M B 2 に格納されたデータが変更されたので、前記キャッシュメモリブロックに書き込まれたデータに関する情報をアップデートさせる(段階 5 5 0)。このような情報のアップデートはタグメモリ制御部 3 1 0 で実行される。

[0086]

前記キャッシュメモリブロックに格納されているデータが有効であれば、前記読み取りアドレスに対応する前記メモリブロックで読み取り動作を実行し、前記キャッシュメモリブロックに格納されている有効なデータを読み取って対応するメモリブロックに書き込む(段階520)。

10

20

30

40

#### [0087]

書き込み動作と読み取り動作とが同じサブメモリブロックで実行されるべき場合、読み取り動作が優先的に実行されるので、読み取りアドレスRADDに対応するメモリブロックMB2のサブメモリブロックで読み取り動作を実行する。読み取り動作は、タグメモリ制御部310で発生されるデコーディング制御信号DCLSによって実行される。

#### [0088]

キャッシュメモリブロック C M B 2 に格納されたデータが有効なデータであるので、まず、キャッシュメモリブロック C M B 2 に格納されている有効なデータを読み取り、読み取られたデータをメモリブロックの対応するサブメモリブロックに書き込まなければならない。そして、キャッシュ制御信号 C C L S に応答してキャッシュメモリブロック C M B 2 に書き込まれたデータに関する情報をアップデートさせる(段階 5 3 0)。情報のアップデートもタグメモリ制御部 3 1 0 で実行される。

## [0089]

このようなデータの書き込み動作と読み取り動作とは同時に実行される。すなわち、サブメモリブロックとキャッシュメモリブロックCMB2とで書き込み動作と読み取り動作とが独立して実行されるので、書き込みワードラインと読み取りワードラインとは同時にイネーブルされうる。したがって、書き込みワードラインと読み取りワードラインとが順次にイネーブルされることによってクロック信号の周期を縮めるのに制限が生じる問題を解決できる。

#### [0090]

前記書き込みアドレス及び前記読み取りアドレスのうち1つが前記キャッシュメモリアドレスと一致しているか、前記書き込みアドレス及び前記読み取りアドレスの全てが前記キャッシュメモリアドレスと一致しているかを判断して書き込み動作及び読み取り動作を実行する(段階445)。

#### [0091]

段階 4 4 5 を図 6 を参照してさらに説明する。前記書き込みアドレス及び前記読み取りアドレスのうち 1 つが前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリアドレスと一致したアドレスに対応する動作を前記キャッシュメモリブロックで実行し、前記キャッシュメモリアドレスと一致しないアドレスに対応する動作を前記メモリブロックで実行する(段階 6 1 0 )。

## [0092]

すなわち、読み取りアドレスRADDがキャッシュメモリアドレスと一致し、書き込みアドレスWADDがキャッシュメモリアドレスと一致しなければ、キャッシュメモリブロックCMB2で読み取り動作を実行する。タグメモリ制御部310は、キャッシュ制御信号CCLSをキャッシュメモリブロックCMB2に印加して読み取り動作を実行する。読み取られたデータは図3でCDOUTとして示されている。

#### [0093]

また、タグメモリ制御部310は、デコーディング制御信号DCLSを発生してメモリブロックMB2で書き込み動作を実行させる。

## [0094]

逆に、書き込みアドレスWADDがキャッシュメモリアドレスと一致し、読み取りアドレスRADDがキャッシュメモリアドレスと一致しなければ、キャッシュメモリブロックCMB2で読み取り動作を実行する。

#### [0095]

前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリブロックで読み取り動作を実行し、前記メモリブロックで書き込み動作を実行し、前記メモリブロックに書き込まれたデータに関する情報をアップデートさせる(段階 6 2 0 )。

## [0096]

20

10

30

書き込みアドレス及び前記読み取りアドレスが全て前記キャッシュメモリアドレスと一致すれば、書き込み動作と読み取り動作が全てキャッシュメモリブロック CMB2で実行されなければならないことを意味する。しかし、これは同じサブメモリブロックで書き込み動作と読み取り動作とが同時に実行されないことと同じ理由で不可である。

## [0097]

したがって、キャッシュメモリブロックCMB2でキャッシュ制御信号CCLSに応答して読み取り動作を実行する。そして、デコーディング制御信号DCLSに応答してメモリブロックMB2の対応するサブメモリブロックで書き込み動作を実行する。元々キャッシュメモリブロックCMB2に書き込まれるべきデータがサブメモリブロックに書き込まれたものであるので、キャッシュメモリブロックCMB2に現在格納されているデータは有効でないデータとなる。したがって、このような情報をタグメモリ制御部310にアップデートさせる。

#### [0098]

段階 4 2 0 で、前記書き込みアドレスの上位アドレスと前記読み取りアドレスの上位アドレスとが同一でなければ、前記書き込みアドレスと前記読み取りアドレスとが前記キャッシュメモリアドレスと一致しているかを判断する(段階 4 5 0 )。

#### [0099]

前記書き込みアドレス及び前記読み取りアドレスのうち1つが前記キャッシュメモリアドレスと一致しているか、前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致しているかを判断して書き込み動作及び読み取り動作を実行する。(段階455)

段階 4 5 5 を図 7 を参照してさらに説明する。前記書き込みアドレス及び前記読み取りアドレスのうち何れか 1 つが前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリアドレスと一致したアドレスに対応する動作を前記キャッシュメモリブロックで実行し、前記キャッシュメモリアドレスと一致しないアドレスと一致する動作を前記メモリブロックで実行する(段階 7 1 0 )。

#### [ 0 1 0 0 ]

すなわち、読み取りアドレスRADDがキャッシュメモリアドレスと一致し、書き込みアドレスWADDがキャッシュメモリアドレスと一致しなければ、キャッシュ制御信号CCLSに応答してキャッシュメモリブロックCMB2で読み取り動作を遂行する。また、タグメモリ制御部310は、デコーディング制御信号DCLSを発生してメモリブロックMB2で書き込み動作を実行させる。

#### [0101]

逆に、書き込みアドレスWADDがキャッシュメモリアドレスと一致し、読み取りアドレスRADDがキャッシュメモリアドレスと一致しなければ、キャッシュメモリブロックCMB2で書き込み動作を実行し、メモリブロックMB2で読み取り動作を実行する。

## [0102]

前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリブロックで読み取り動作を実行し、前記メモリブロックで書き込み動作を実行し、前記メモリブロックに書き込まれたデータに関する情報をアップデートさせる(段階 7 2 0 )。

### [ 0 1 0 3 ]

前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致すれば、書き込み動作と読み取り動作とが共にキャッシュメモリブロックCMB2で実行されなければならないことを意味する。しかし、これは同じサブメモリブロックで書き込み動作と読み取り動作とが同時に実行されないことと同じ理由で不可である。

#### [0104]

したがって、キャッシュメモリブロックCMB2でキャッシュ制御信号CCLSに応答して読み取り動作を実行する。そして、デコーディング制御信号DCLSに応答してメモリブロックMB2の対応するサブメモリブロックで書き込み動作を実行する。元々キャッ

10

20

30

40

シュメモリブロック C M B 2 に書き込まれるべきデータがサブメモリブロックに書き込まれたものであるので、キャッシュメモリブロック C M B 2 に現在格納されているデータは有効でないデータとなる。したがって、このような情報をタグメモリ制御部 3 1 0 にアップデートさせる。

## [0105]

段階 4 5 0 で判断した結果、前記書き込みアドレス及び前記読み取りアドレスが共に前記キャッシュメモリアドレスと一致しなければ、前記選択されたメモリブロックのうち前記書き込みアドレス及び前記読み取りアドレスに対応する相異なるサブメモリブロックで書き込み動作及び読み取り動作を実行する(段階 4 6 0 )。

## [0106]

この場合は、書き込みアドレスWADD及び読み取りアドレスRADDが相異なるサブメモリブロックを指定している場合である。相異なるサブメモリブロックが指定されたので、それぞれのサブメモリブロックに対応するデコーディング回路(図示せず)を利用してデータの読み取り動作と書き込み動作とを実行する。

#### [0107]

各サブメモリブロックをデコーディングできるデコーディング回路を別途に具備しており、また書き込みアドレスデコーディングパスと読み取りアドレスデコーディングパスとが独立的に分離されているので、同じメモリブロックであっても相異なるサブメモリブロックであれば、同時に読み取り動作及び書き込み動作が実行できる。

## [0108]

段階410で、前記書き込みアドレス及び前記読取りアドレスのうち何れか1つだけ入力されれば、入力された前記書き込みアドレス及び前記読み取りアドレスのうち何れか1つが前記キャッシュメモリアドレスと一致するかを判断する(段階465)。

#### [0109]

入力された前記書き込みアドレスまたは前記読み取りアドレスが前記キャッシュメモリアドレスと一致すれば、前記キャッシュメモリアドレスと一致した書き込みアドレスまたは読み取りアドレスに対応する動作を前記キャッシュメモリブロックで実行する(段階 4 7 0 )。この場合は、クロック信号の1周期の間に書き込みアドレスWADD及び読み取りアドレスRADDのうち何れか1つだけ入力される。

## [0110]

この時は、入力されるアドレスがキャッシュメモリアドレスと一致すれば、キャッシュメモリブロックで対応する動作を実行し、キャッシュメモリアドレスと一致しなければ、メモリブロックMB2で対応する動作を実行する。

## [0111]

すなわち、書き込みアドレスWADDだけ入力され、入力された書き込みアドレスWADDがキャッシュメモリアドレスと一致するならば、キャッシュメモリブロックCMB2に書き込み動作を実行する。逆に、読み取りアドレスRADDだけ入力され、入力された読み取りアドレスRADDがキャッシュメモリアドレスと一致するならば、キャッシュメモリブロックCMB2に読み取り動作を実行する。この時、タグメモリ制御部310は、キャッシュ制御信号CCLSを発生してキャッシュメモリブロックCMB2で書き込みまたは読み取り動作を実行させる。

## [0112]

入力された前記書き込みアドレスまたは前記読み取りアドレスが前記キャッシュメモリアドレスと一致しなければ、前記キャッシュメモリアドレスと一致しない書き込みアドレスまたは読み取りアドレスに対応する動作を前記メモリブロックで実行する(段階 4 7 5 )。

#### [0113]

図8は、本発明の集積回路の動作を説明するタイミング図である。図8を参照すれば、 クロック信号CLKの1周期が図1のクロック信号CLKの1周期の半分に短縮されたこ とが分かる。これはクロック信号CLKの周波数が倍増されたことを意味する。 10

20

30

40

#### [0114]

従来においては、書き込み動作のためのワードラインと読み取り動作のためのワードラ インとがクロック信号CLKの1周期の間に順次にイネーブルされるので、クロック信号 CLKの周期を短くすることが難しかった。

#### [0115]

しかし、本発明による集積回路及び方法によれば、図8から分かるように、読み取り動 作のためのワードラインWL1と書き込み動作のためのワードラインWL2とがクロック 信号CLKの1周期の間に同時にイネーブルされるので、クロック信号CLKの周期を短 くすることができる。

## [0116]

本発明は、入出力ポートが分離され、クロック信号の1周期内に書き込みアドレスと読 み取りアドレスとを共に受けられる種々の集積回路に適用することができる。また、デー 夕は、SDRまたはDDRに分離された入力ピンまたは出力ピンを通じて入出力すること ができる。

#### [0117]

以上でのように、図面と明細書で最適実施例が開示された。ここで特定の用語が使われ たが、これは単に本発明を説明するための目的で使われたものであり、意味限定や特許請 求の範囲に記載された本発明の範囲を制限するために使われたものではない。したがって 、本技術分野の当業者であれば、これにより多様な変形及び均等な他の実施例が可能であ る点が理解できるであろう。したがって、本発明の真の技術的保護範囲は特許請求の技術 的思想によって定められなければならない。

【産業上の利用可能性】

## [0118]

本発明は集積回路に係り、特に二重データ率RAM(Double Data Rate RAM:DDR RAM)のように動作速度が速くて入出力ポートが分離された半導体集 積回路において好適に使用できる。

## 【図面の簡単な説明】

[0119]

【図1】分離された入出力ポートを有するメモリ装置の動作を説明するタイミング図であ

【図2】第1実施例による集積回路を示すブロック図である。

【図3】第2実施例による集積回路を示すブロック図である。

【図4】他の実施例によるデータの読み取り動作と書き込み動作とを同時に実行する方法 を示すフローチャートである。

【図5】図4の段階440を説明するフローチャートである。

【図6】図4の段階445を説明するフローチャートである。

【図7】図4の段階455を説明するフローチャートである。

【図8】本発明の集積回路の動作を説明するタイミング図である。

## 【符号の説明】

#### [0120]

2 0 0 集積回路

タグメモリ制御部 2 1 0

$SMB1 \sim SMBM$ サブメモリブロック

M B 1 、 M B 2 、 M B 3 、 M B 4 メモリブロック

CMB1、CMB2、CMB3、CMB4 キャッシュメモリブロック

WADD 書き込みアドレス

RADD読み取りアドレス 10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

## フロントページの続き

(74)代理人 100110364

弁理士 実広 信哉

(72)発明者 孫教民

大韓民国 京畿道 城南市 盆唐区 書 ヒョン 洞 96番地 示範団地宇成アパート 218 棟 1206号

(72)発明者 徐英豪

大韓民国 京畿道 水原市 勧善区 九雲洞 890番地

審査官 仲間 晃

(56)参考文献 特開平11-328976 (JP,A)

特開平03-286495(JP,A)

特開2000-173270(JP,A)

(58)調査した分野(Int.CI., DB名)

G 1 1 C 1 1 / 4 1

G11C 11/413