(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第5368508号 (P5368508)

(45) 発行日 平成25年12月18日(2013.12.18)

(24) 登録日 平成25年9月20日(2013.9.20)

(51) Int.Cl. F 1

**HO2M** 3/155 (2006, 01) C HO2M 3/155 HO2J 7/00 (2006, 01)H02 J 7/00 S B60R 16/03 670S (2006.01) B60R 16/02

請求項の数 10 (全 18 頁)

(21) 出願番号 特願2011-109338 (P2011-109338) (22) 出願日 平成23年5月16日 (2011.5.16)

(65) 公開番号 特開2012-244658 (P2012-244658A)

(43) 公開日 平成24年12月10日 (2012.12.10) 審査請求日 平成23年5月16日 (2011.5.16) ||(73)特許権者 000006013 | 三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

||(74)代理人 100073759

弁理士 大岩 増雄

||(74)代理人 100093562

弁理士 児玉 俊英

(74)代理人 100088199

弁理士 竹中 岑生

(74)代理人 100094916

弁理士 村上 啓吾

(72) 発明者 岩上 祐希

東京都千代田区丸の内二丁目7番3号 三

菱電機株式会社内

最終頁に続く

(54) 【発明の名称】 車載電子制御装置

## (57)【特許請求の範囲】

## 【請求項1】

車載バッテリから給電された電源電圧を入力電圧として作動し、所定の中間電圧を降圧生成するためのスイッチング電源を構成する開閉素子と、この開閉素子の後段に直列接続されて第一の安定化電圧又は第二の安定化電圧を生成する連続制御形の第一の定電圧制御電源又は第二の定電圧制御電源と、当該第一の定電圧制御電源又は第二の定電圧制御電源から給電され、少なくともマイクロプロセッサとプログラムメモリとRAMメモリとを有する主制御回路部又は当該主制御回路部と協働する補助制御回路部とを包含した制御回路部とを備えた車載電子制御装置であって、

前記開閉素子と前記第一の定電圧制御電源又は第二の定電圧制御電源との間には、誘導性素子である下流側コイルが直列接続され、当該下流側コイルの上流側には転流ダイオードがグランド回路との間に接続されると共に、下流側には出力コンデンサがグランド回路との間に接続されており、

前記下流側コイルのインダクタンスと前記開閉素子から給電される電気負荷の負荷抵抗との比率である誘導特定数の値は、前記開閉素子を開閉制御する開閉周期よりも大きな値のものが使用され、前記開閉素子はPチャンネル型又はNチャンネル型の電界効果トランジスタであって、該電界効果トランジスタのゲート回路には、逆導通抑制回路が接続されると共に、前記逆導通抑制回路は、前記開閉素子の上流側電位が下流側電位以下になったことを検出して当該開閉素子のゲート駆動回路を遮断するか、又は,前記開閉素子と直列接続された電流検出抵抗の両端電圧が当該開閉素子の逆導通による逆方向電圧を検出したこ

とによって前記開閉素子のゲート駆動回路を遮断し、

前記中間電圧が所定値未満に低下したときに少なくとも前記マイクロプロセッサを初期化 するためのリセット回路を備え、

前記電源電圧が一時的に異常低下したときに、<u>前記逆導通抑制回路によって</u>前記出力コンデンサの充電電荷が前記開閉素子の逆導通によって上流電源側に逆流してアンダーシュートが発生するのを抑制して、前記出力コンデンサのアンダーシュートによって、前記リセット回路が前記マイクロプロセッサの初期化を行うのを防止することを特徴とする車載電子制御装置。

## 【請求項2】

前記開閉素子と前記車載バッテリとの間には誘導性素子である上流側コイルが直列接続されると共に、該上流側コイルの下流側には電源コンデンサがグランド回路との間に接続され、前記上流側コイルのインダクタンスは前記下流側コイルのインダクタンスよりも小さな値であって、前記電源コンデンサの静電容量は、前記出力コンデンサの静電容量よりも大きな値であり、前記リセット回路は、前記車載バッテリから給電された電源電圧又は前記電源コンデンサの両端電圧である実働電源電圧が、所定の判定閾値電圧未満となったときは、前記マイクロプロセッサに対するリセット信号を発生し、前記判定閾値電圧は、前記第一の定電圧制御電源又は第二の定電圧制御電源が発生する前記第一の安定化電圧又は第二の安定化電圧よりも低い電圧に設定されていることを特徴とする請求項1に記載の車載電子制御装置。

## 【請求項3】

前記リセット回路は、前記中間電圧が第一の判定閾値電圧未満であるときには、前記マイクロプロセッサを初期化するためのリセット信号を発生し、前記中間電圧が前記第一の判定閾値電圧以上となって前記リセット信号が解除された後は、前記第一の判定閾値電圧よりは小さな値である第二の判定閾値電圧未満に低下したことによってリセット信号を発生する、ヒステリシス特性を有していることを特徴とする<u>請求項2</u>に記載の車載電子制御装置。

### 【請求項4】

前記リセット回路における第一の判定閾値電圧と第二の判定閾値電圧との間の差分電圧の値は、前記上流側コイルによって発生する電源電圧のアンダーシュートによる減少偏差電圧以上の値に設定されていることを特徴とする請求項3に記載の車載電子制御装置。

### 【請求項5】

前記リセット回路は、前記中間電圧が第一の判定閾値電圧未満であるときには、前記マイクロプロセッサを初期化するためのリセット信号を発生し、前記中間電圧が前記第一の判定閾値電圧以上となって前記リセット信号が解除された後は、前記第一の判定閾値電圧よりは小さな値である第二の判定閾値電圧未満に低下したことによってリセット信号を発生する、ヒステリシス特性を有していることを特徴とする請求項1に記載の車載電子制御装置。

### 【請求項6】

前記開閉素子と前記車載バッテリとの間には誘導性素子である上流側コイルが直列接続されると共に、該上流側コイルの下流側には電源コンデンサがグランド回路との間に接続され、

前記リセット回路における第一の判定閾値電圧と第二の判定閾値電圧との間の差分電圧の値は、前記上流側コイルによって発生する電源電圧のアンダーシュートによる減少偏差電圧以上の値に設定されていることを特徴とする請求項5に記載の車載電子制御装置。

#### 【請求項7】

前記開閉素子の下流位置には、前記補助制御回路部に給電する前記第一の定電圧制御電源と、前記主制御回路部に給電する前記第二の定電圧制御電源とが接続され、前記第一の定電圧制御電源が発生する前記第一の安定化電圧は、前記第二の定電圧制御電源が発生する前記第二の安定化電圧よりも大きな値であって、前記電源電圧又は実働電源電圧が異常低下したときに、前記リセット回路が前記マイクロプロセッサに対するリセット信号を発

10

20

30

40

生する前記判定閾値電圧と、前記中間電圧が異常低下したときに、前記リセット回路が前記マイクロプロセッサに対するリセット信号を発生する前記第一の判定閾値電圧とは、いずれも前記第一の安定化電圧よりは小さく、前記第二の安定化電圧よりも大きな中間値となっていることを特徴とする請求項 2 <u>、請求項 3 、請求項 5 のいずれか 1 項</u>に記載の車載電子制御装置。

#### 【請求項8】

前記開閉素子は、前記中間電圧に比例した検出電圧と所定の比較基準電圧との偏差積分値に応動した通電デューティで当該開閉素子の開閉制御を行なう負帰還通電率制御回路を備え、前記負帰還通電率制御回路を構成する後段比較器と、当該後段比較器に対する入力信号回路となる比較回路、偏差積分回路、およびパルス幅変調制御回路は、前記第一の安定化電圧を電源電圧として動作するのに対し、前記リセット回路で使用される判定閾値電圧と、前記第一の判定閾値電圧及び前記比較回路に入力される比較基準電圧は、前記電源電圧又は実働電源電圧から給電される基準電圧生成回路によって生成されていることを特徴とする請求項7に記載の車載電子制御装置。

### 【請求項9】

前記逆導通抑制回路は、前記車載バッテリから給電された電源電圧、又は前記電源コンデンサの両端電圧である実働電源電圧に比例した第一の電圧と、前記出力コンデンサの両端電圧である中間電圧に比例した第二の電圧とを比較して、前記開閉素子の上流側電位が下流側電位以下になったことを検出して前記開閉素子のゲート駆動回路を遮断することを特徴とする請求項1又は請求項2に記載の車載電子制御装置。

#### 【請求項10】

前記逆導通抑制回路は、前記開閉素子と直列接続された電流検出抵抗の両端電圧が、当該開閉素子の逆導通による逆方向電圧を検出したことによって前記開閉素子のゲート駆動回路を遮断し、前記電流検出抵抗は、正常動作中の前記開閉素子に対する過電流遮断制御用に使用されることを特徴とする請求項1又は請求項2に記載の車載電子制御装置。

## 【発明の詳細な説明】

#### 【技術分野】

## [0001]

この発明は、例えばエンジン制御装置、或いは変速機制御装置などの車載電子制御装置であって、特には車載バッテリから給電された電源電圧を降圧して中間電圧を得るスイッチング電源と、このスイッチング電源から給電される線形制御型の定電圧制御電源を介して、マイクロプロセッサを含む制御回路部に対して低消費電力・高精度な安定化電圧を供給する電源制御回路部を備えた車載電子制御装置に関するものである。

#### 【背景技術】

## [0002]

開閉素子の通電デューティを制御して所定の安定化電圧を得るスイッチング電源(或いはスイッチング・レギュレータ、チョッパ・レギュレータとも呼称される)は低消費電力で大電力の安定化電圧が得られるが、開閉素子の開閉動作に伴う出力電圧のリップル変動が発生するので、開閉素子に対して直列接続された第二の開閉素子の導通状態を連続制御して、更に高精度な安定化電圧を得る連続制御電源(リニア制御電源、ドロッパー電源、シリーズレギュレータなどと呼称される)を従属接続することが広く実用されている。この場合、連続制御電源の入力電圧(スイッチング電源の出力電圧)が安定していると出力の電圧差が少なくなって消費電力が抑制されることになるが、入力電圧が脈動していると入出力電圧差が大きくなって十分な消費電力の抑制が行えなくなる問題がある。スイッチング電源の出力電圧の脈動成分を低減するためには、直列接続されたチョークコイルのインダクタンスと出力コンデンサの静電容量を大きくし、開閉素子を高速周期で開閉すればよいが、この場合にはチョークコイルや出力コンデンサが大型化し、開閉素子のスイッチングロスによる発熱が増大する問題点がある。

また、開閉素子が導通駆動されているときの開閉素子の電圧降下が大きいと、開閉素子の 発熱が増大するだけでなく、車載バッテリの電源電圧が低下しているときに目標とする出 10

20

30

40

力電圧が得られず、最低保証電圧が上昇悪化する問題点がある。

## [0003]

例えば、下記の特許文献 1 によれば、互いに従属接続されたスイッチング電源(チョッパ・レギュレータ)と連続制御電源(シリーズ・レギュレータ)としてNPN型の接合トランジスタが使用されていて、各トランジスタのベース電流はスイッチング電源に給電する外部電源から供給されるようになっている。従って、前段トランジスタのベース電圧はコレクタ電圧以下に制限されているので、前段トランジスタが導通駆動されているときのコレクタ・エミッタ端子間の電圧降下が大きくなり、前段トランジスタの発熱が増大するだけでなく、電源電圧が低下しているときに目標とする出力電圧が得られず、最低保証電圧が上昇悪化する問題点がある。

[0004]

また、下記の特許文献 2 によれば、互いに従属接続されたスイッチング電源(1 次電源レギュレータ)と連続制御電源(2 次電源レギュレータ)のうち、前段側のスイッチング電源には P チャンネル型の電界効果トランジスタが使用されている。この場合、前段トランジスタが完全導通しているときのソース・ドレーン端子間の電圧降下は小さくなるが、 P チャンネル型トランジスタの場合には電源電圧が負荷側電圧以下に低下すると、トランジスタの逆導通状態が発生し、出力コンデンサの充電電圧にアンダーシュートが発生する問題点がある。

これを防止するために特許文献2の場合には、逆流防止用のダイオードがトランジスタのソース端子に直列接続されているので、前段トランジスタが導通駆動されているときのソース・ドレーン端子間の電圧降下が小さくても、逆流防止用のダイオードによる電圧降下を含めた電圧降下は大きくなり、ダイオードを含めた前段トランジスタの発熱が増大するだけでなく、電源電圧が低下しているときに目標とする出力電圧が得られず、最低保証電圧が上昇悪化する問題点がある。

【先行技術文献】

【特許文献】

[0005]

【特許文献1】特開平07-095765号公報(図1、要約)

【特許文献2】特開2003-316482号公報(図1、要約)

【発明の概要】

【発明が解決しようとする課題】

[0006]

前記特許文献 1 による直流安定化電源装置によれば、開閉素子の逆導通は発生しても高抵抗であって問題はないが、開閉素子の順方向電圧降下が大きくて、発熱と最低保証電圧の上昇悪化の問題がある。

また、前記特許文献 2 による電源回路によれば、開閉素子の逆導通は発生し得るが、逆流防止用のダイオードによって逆導通が防止されていて、当該ダイオードを含む開閉素子の順方向電圧降下が大きくて、発熱と最低保証電圧の上昇悪化の問題がある。

なお、電源電圧が異常低下したときに開閉素子に逆導通が発生すると、開閉素子の出力コンデンサの充電電荷がチョークコイルを通じて上流電源側へ放電し、両側電圧が一致してもチョークコイルに流れている電流は急には減衰せず、漸次は放電が持続することによって上流電源側の電圧よりは下流側の出力コンデンサの両端電圧が低くなるアンダーシュートが発生する。その結果、電源電圧は最低保証電圧以上であるにも関わらず、実際に得られた電圧が更に低い電圧となって、定電圧制御電源から駆動されるマイクロプロセッサが誤動作する問題がある。

[0007]

この発明は、上記のような問題点を解消するためになされたもので、開閉素子の順方向電圧降下を低減すると共に、電源電圧が異常低下したときのアンダーシュートを抑制し、 広範囲な電源電圧の変動に対して安定化した出力電圧を生成する低消費電力の定電圧制御 装置を備えた車載電子制御装置を提供することを目的とする。 10

20

30

40

#### 【課題を解決するための手段】

### [0008]

この発明に係る車載電子制御装置は、車載バッテリから給電された電源電圧を入力電圧 として作動し、所定の中間電圧を降圧生成するためのスイッチング電源を構成する開閉素 子と、この開閉素子の後段に直列接続されて第一の安定化電圧又は第二の安定化電圧を生 成する連続制御形の第一の定電圧制御電源又は第二の定電圧制御電源と、当該第一の定電 圧制御電源又は第二の定電圧制御電源から給電され、少なくともマイクロプロセッサとプ ログラムメモリとRAMメモリとを有する主制御回路部、又は当該主制御回路部と協働す る補助制御回路部とを包含した制御回路部とを備えた車載電子制御装置であって、前記開 閉素子と前記第一の定電圧制御電源又は第二の定電圧制御電源との間には、誘導性素子で ある下流側コイルが直列接続され、当該下流側コイルの上流側には転流ダイオードがグラ ンド回路との間に接続されると共に、下流側には出力コンデンサがグランド回路との間に 接続されており、前記下流側コイルのインダクタンスと前記開閉素子から給電される電気 負荷の負荷抵抗との比率である誘導特定数の値は、前記開閉素子を開閉制御する開閉周期 よりも大きな値のものが使用され、前記開閉素子はPチャンネル型又はNチャンネル型の 電界効果トランジスタであって、該電界効果トランジスタのゲート回路には逆導通抑制回 路が接続されると共に、前記逆導通抑制回路は、前記開閉素子の上流側電位が下流側電位 以下になったことを検出して当該開閉素子のゲート駆動回路を遮断するか、又は、前記開 閉素子と直列接続された電流検出抵抗の両端電圧が当該開閉素子の逆導通による逆方向電 圧を検出したことによって前記開閉素子のゲート駆動回路を遮断し、前記中間電圧が所定 値未満に低下したときに少なくとも前記マイクロプロセッサを初期化するためのリセット 回路を備え、前記電源電圧が一時的に異常低下したときに、前記逆導通抑制回路によって 前記出カコンデンサの充電電荷が前記開閉素子の逆導通によって上流電源側に逆流してア ンダーシュートが発生するのを抑制して、アンダーシュートによって前記リセット回路が 前記マイクロプロセッサの初期化を行うのを防止するようにしたものである。

### 【発明の効果】

## [0009]

この発明の車載電子制御装置によれば、開閉素子の出力回路に設けられた下流側コイルのインダクタンスを大きくして、下流側コイルから充電される出力コンデンサの脈動電圧を抑制することができる一方で、下流側コイルのインダクタンスを大きくしたことに伴って、車載バッテリの電源電圧が一時的に異常低下したときに発生する出力コンデンサの充電電圧のアンダーシュートを抑制し、みだりにマイクロプロセッサが初期化されるのを防止しながら、脈動電圧の小さな中間電圧が得られ、第一又は第二の定電圧制御電源を介して低消費電力で、高精度な安定化電圧を得ることができる効果がある。

## [0010]

また、中間電圧を得るための開閉素子が閉路駆動されているときの、電圧降下が小さくなって、電源電圧の最小保証電圧をより低く設定することができる効果がある。

### [0011]

上述した、またその他の、この発明の目的、特徴、効果は、以下の実施の形態における詳細な説明および図面の記載からより明らかとなるであろう。

【図面の簡単な説明】

#### [0012]

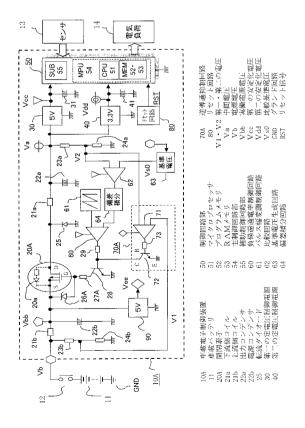

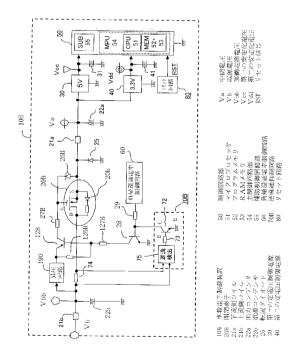

【図1】この発明の実施の形態1における車載電子制御装置の全体回路ブロック図である

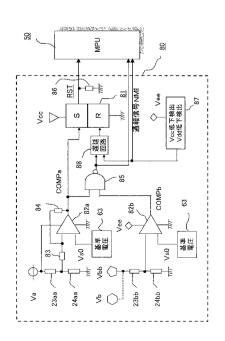

【図2】図1におけるリセット回路の詳細回路図である。

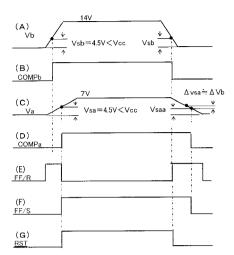

【図3】この発明の実施の形態1の全体動作説明用のタイムチャートである。

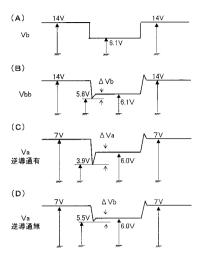

【図4】この発明の実施の形態1における異常電圧低下時のタイムチャートである。

【図5】この発明の実施の形態2における車載電子制御装置の部分回路ブロック図である

【発明を実施するための形態】

10

20

\_ \_

30

40

#### [0013]

以下、この発明の実施の形態について、図面を参照して詳述する。なお、各図中、同一または相対応する部分には同一符号をつけ、その説明を省略するものとする。

#### [0014]

実施の形態1.

#### (1)構成の説明

図1は、この発明の実施の形態1における車載電子制御装置の全体回路ブロック図である。図1において、密閉筐体内に収納されている車載電子制御装置10Aは、負端子がグランド回路GNDとなる車体に接続された車載バッテリ11から、図示しない電源リレーの出力接点12を介して電源電圧Vbとなる電源が供給され、図示しない接続コネクタを介して外部接続された車載センサ群13の動作状態と、後述のプログラムメモリ52に格納された制御プログラムの内容に応動して、図示しない接続コネクタを介して外部接続された車載電気負荷群14を駆動制御するようになっている。

車載電子制御装置10Aの内部にあって、スイッチング電源を構成する開閉素子20Aは車載バッテリ11と第一の定電圧制御電源30、第二の定電圧制御電源40との間に直列接続されていて、開閉素子20Aの上流側と下流側にはそれぞれ誘導性素子としてのチョークコイルである上流側コイル21b、下流側コイル21aが直列接続され、上流側コイル21bと下流側コイル21aの各下流端には、電源コンデンサ22bと出力コンデンサ22aとがグランド回路GNDとの間に接続されている。

## [0015]

なお、電源コンデンサ22bの両端電圧は、開閉素子20Aに対する実働電源電圧 V bbとなり、出力コンデンサ22aの両端電圧は中間電圧 V aとなるものであって、互いに直列接続された分圧抵抗23a、24aは中間電圧 V aを分圧して第二の電圧 V 2を生成し、互いに直列接続された分圧抵抗23b、24bは電源電圧 V b (又は実働電源電圧 V bb)を分圧して第一の電圧 V 1を生成するようになっている。また、開閉素子20Aと下流側コイル21aとの接続点とグランド回路GNDとの間には転流ダイオード25が接続されていて、開閉素子20Aが閉路されていたときに下流側コイル21aから出力コンデンサ22aや、第一の定電圧制御電源30、第二の定電圧制御電源40に給電されていたコイル電流は、開閉素子20Aが開路されたことによって転流ダイオード25に転流して、下流側コイル21aに蓄積されていた電磁エネルギーが放出されるようになっている。 P チャンネル型の電界効果トランジスタである開閉素子20Aのソース端子とゲート端子間には電圧制限ダイオード26Aが接続され、ゲート端子とグランド回路GNDとの間には、駆動抵抗27Aと駆動トランジスタ28との直列回路が接続されている。また、駆動トランジスタ28はベース抵抗29を介して後述の後段比較器60の出力端子に接続されている。

## [0016]

開閉素子20Aから安定化された中間電圧 V aが供給される第一の定電圧制御電源30は、図示しない負帰還制御回路を内蔵していて、出力電圧が例えば D C 5 V である第一の安定化電圧 V ccとなるように導通状態が連続制御され、負荷側コンデンサ31が接続されている。開閉素子20Aから安定化された中間電圧 V aが供給される第二の定電圧制御電源40も同様であり、図示しない負帰還制御回路を内蔵していて、出力電圧が例えば D C 3 . 3 V である第二の安定化電圧 V ddとなるように導通状態が連続制御され、負荷側コンデンサ41が接続されている

制御回路部50はマイクロプロセッサ51とプログラムメモリ52とRAMメモリ53を有する主制御回路部54と、この主制御回路部54と協働する論理回路又は図示しないサブCPUである補助制御回路部55を包含し、主制御回路部54には第二の安定化電圧Vddが供給され、補助制御回路部55には第一の安定化電圧Vccが供給されるようになっている。

#### [0017]

負帰還通電率制御回路を構成する後段比較器60の正側入力端子には、所定の周期で鋸歯状波信号パルスを発生して、後述の偏差積分値と比較されるパルス幅変調制御回路61の出力電圧が印加されている。前段側の比較回路62の正側入力端子には、分圧抵抗23a、24aに

10

20

30

40

よって分圧された中間電圧 Vaに比例した第二の電圧 V2が入力され、負側入力端子には、基準電圧生成回路63によって生成された所定の比較基準電圧 Vs0が入力されている。偏差積分回路64は第二の電圧 V2が比較基準電圧 Vs0以上であれば漸次出力電圧が増大し、第二の電圧 V2が比較基準電圧 Vs0以下であれば漸次出力電圧が減少するようになっているが、実際には第二の基準電圧 V2と比較基準電圧 Vs0との偏差成分に比例した出力も加算されて比例積分帰還信号電圧を生成するようになっている。

後段比較器60はパルス幅変調制御回路61の出力電圧である鋸歯状波信号パルスの電圧が偏差積分回路64の出力電圧以上となった時間帯において出力電圧レベルが「H」となり、ベース抵抗29、駆動トランジスタ28、駆動抵抗27Aを介して開閉素子20Aを閉路駆動するようになっている。

[0018]

逆導通抑制回路70Aを構成する電圧比較器71の正入力端子には、中間電圧 Vaを分圧して得られる第二の電圧 V2が印加され、負入力端子には電源電圧 Vb(又は実働電源電圧 Vbbでもよい)を分圧して得られる第一の電圧 V1が印加され、電圧比較器71の出力端子はベース抵抗73を介して遮断トランジスタ72を導通駆動するようになっている。

N P N 型接合トランジスタである遮断トランジスタ72のコレクタ端子とエミッタ端子とは、駆動トランジスタ28のベース端子とエミッタ端子との間に接続されている。

なお、開閉素子20Aのソース端子とドレーン端子の電位(グランド回路GNDからの電圧)が等しくなったときには、第一の電圧 V 1、第二の電圧 V 2 が等しくなる関係に分圧抵抗23 a、24aと、23b、24bの抵抗配分が設定されている。

[0019]

従って、第二の電圧 V 2が第一の電圧 V 1よりも大きくなる異常状態が発生すると、電圧比較器71の出力論理レベルが「H」となり、遮断トランジスタ72が導通することによって駆動トランジスタ28が不導通となり、開閉素子20Aも不導通状態となる。ただし、P チャンネル型の電界効果トランジスタである開閉素子20Aのソース端子とドレーン端子との間には、寄生ダイオード回路20aが並列接続された状態となっていて、ドレーン端子からソース端子へ逆流する電流を完全に遮断することはできない状態となっている。

[0020]

マイクロプロセッサ51に対するリセット回路80は、図 2 において後述するとおりである。補助制御電源90は実働電源電圧 V bb(又は電源電圧 V bであってもよい)から給電されて、例えば D C 5 V の小電力の補助安定化電圧 V eeを生成し、電圧比較器71や図 2 における前段比較器82b、終段電圧異常検出回路87の電源として使用されるようになっている。なお、図 1 において、後段比較器60と比較回路62を含む負帰還通電率制御回路全体の電源は第一の安定化電圧 V cc が使用されているが、第一の安定化電圧 V cc が所定の目標電圧に到達する前の状態で負帰還通電率制御回路が不作動であるときには、補助制御電源90の出力によって開閉素子20Aは閉路駆動されるようになっている。

[0021]

次に、図1におけるリセット回路80の詳細回路図である図2について説明する。図2において、リセット回路80を構成するフリップフロップ回路81はセット入力端子Sとリセット入力端子Rを備え、どちらか一方に論理レベル「H」の信号電圧が印加されると、その出力論理レベルは「H」となり、他方に論理レベル「H」の信号電圧が印加されるまでは、たとえ当該入力信号電圧の論理レベルが「L」に変化しても出力論理レベルは「H」を維持するようになっていて、セット入力信号Sに対する出力信号は、制御回路部50内のマイクロプロセッサ51に対するリセット信号RSTとして使用されている。

[0022]

なお、フリップフロップ回路81のセット入力端子Sとリセット入力端子Rの両方の論理レベルが「H」になると、リセット入力端子Rの方が優先されるようになっている。また、マイクロプロセッサ51はリセット信号RSTの論理レベルが「L」であるときにリセット処理が行われ初期化されるようになっている。従って、フリップフロップ回路81がリセットされるとマイクロプロセッサ51のリセットが行われるようになっている。

10

20

30

40

後段比較器82aの正入力端子は、入力抵抗83を介して分圧抵抗23aa、24aaの直列接続点に接続されているとともに、正帰還抵抗84を介して後段比較器82aの出力端子に接続されていて、分圧抵抗23aa、24aaは互いに直列接続されて中間電圧 V a が印加されている。後段比較器82aの負入力端子には、基準電圧生成回路63によって生成された基準電圧 V s 0 が印加され、後段比較器82aの出力端子は、フリップフロップ回路81のセット入力端子 S に接続されるとともに、論理積否定出力素子85の一方の入力端子に接続されている。前段比較器82bの正入力端子は、分圧抵抗23bb、24bbの直列接続点に接続されていて、分圧抵抗23bb、24bbは互いに直列接続されて実働電源電圧 V b b (又は電源電圧 V b であってもよい)が印加されている。

## [0023]

前段比較器82bの負入力端子には、基準電圧生成回路63によって生成された基準電圧 V s 0が印加され、前段比較器82bの出力端子は、論理積否定出力素子85の他方の入力端子に接続されている。論理積否定出力素子85の出力端子は、遅延回路88を介してフリップフロップ回路81のリセット入力端子 R に接続されているとともに、異常電圧低下に関する通報信号NMI としてマイクロプロセッサ51に送信され、マイクロプロセッサ51はリセット信号RSTによって初期化される前に緊急退避処理を行うようになっている。

#### [0024]

前段比較器82bの出力信号である前段比較信号COMPbは、実働電源電圧 V bb(又は電源電圧 V b)が判定閾値電圧 V sb(例えば D C 4 . 5 V)未満であると論理レベル「L」となり、後段比較器82aの出力信号である後段比較信号COMPaは中間電圧 V aが第一の判定閾値電圧 V sa(例えば D C 4 . 5 V 未満)であると論理レベル「L」となり、比較信号COMPa、COMPbのいずれか一方の論理レベルが「L」になるとフリップフロップ回路81がリセットされ、セット出力の論理レベルが「L」となることによってマイクロプロセッサ51のリセット処理が行われるようになっている。

#### [0025]

後段比較器82aの出力信号である後段比較信号COMPaは、中間電圧 Vaが第一の判定閾値電圧 Vsa(例えば D C 4 . 5 V)以上になると論理レベル「H」となり、フリップフロップ回路81がセットされ、セット出力の論理レベルが「H」となることによってマイクロプロセッサ51のリセットが解除されるようになっている。後段比較信号COMPaの論理レベルが一旦「H」になると、正帰還抵抗84によって正入力端子に対する加算電圧が発生することによって、例えば中間電圧 Vaが第二の判定閾値電圧 Vsaa = Vsa - Vsa(例えば4.5 - 0.5 = 4.0 V)未満になることによって、後段比較信号COMPaの論理レベルが「L」に復帰するようになっている。なお、上記の判定閾値電圧 Vsb、第一の判定閾値電圧 Vsa、第二の判定閾値電圧 Vsaaの値は、第一の安定化電圧 Vcc(例えば D C 5 V)と第二の安定化電圧 Vdd(例えば D C 3.3 V)との中間域の値を選択するのが適当である。

#### [0026]

フリップフロップ回路81のセット出力回路に接続されたプルダウン抵抗86は、第一の安定化電圧 V ccが確立してフリップフロップ回路81が動作を開始するまでは、リセット信号RSTを論理レベル「L」にしてマイクロプロセッサ51に対するリセット信号を有効にしておくものである。終段電圧異常検出回路87は、第一の安定化電圧 V ccが例えば D C 4.5 V以下であるか、第二の安定化電圧 V ddが例えば D C 3.0 V以下であるときに、タイマ回路88を介してフリップフロップ回路81のリセット入力端子 R に対して論理レベル「H」の信号を供給するとともに、異常電圧低下に関する通報信号MNIとしてマイクロプロセッサ51に送信され、マイクロプロセッサ51はリセット信号RSTによって初期化される前に緊急退避処理を行うようになっている。これにより、運転中に第一の安定化電圧 V cc や第二の安定化電圧 V ddが異常低下したときに、主制御回路部54や補助制御回路部55が不作動となる前に初期化処理を行うようになっている。

## [0027]

#### (2)作用・動作の説明

次に、図1、図2のとおり構成されたこの発明の実施の形態1の車載電子制御装置につ

10

20

30

40

いて、図3、図4で示すタイムチャートを用いて作用動作の詳細を説明する。

まず、図1、図2について概括説明を行なうと、図示しない電源スイッチが閉路されて、電源リレーの出力接点12が閉路すると、電子制御装置10A内のマイクロプロセッサ51が動作を開始し、車載センサ群13の動作状態と、プログラムメモリ52に予め書込まれている制御プログラムの内容に応動して、電気負荷群14の駆動制御が行われる。

図示しない電源スイッチが開路されると電源リレーは暫時継続駆動されていて、例えば運転中の学習情報を不揮発性のメモリに転送退避するなどの処理が完了してから、電源リレーが消勢されて出力接点が開路するようになっている。電源投入時の各部の電圧の立上り状態としては電源電圧 V b、実働電源電圧 V bb、中間電圧 V a、第二の定電圧制御電源40、第一の定電圧制御電源30の順で正常電圧に到達する。電源遮断時の各部の電圧の立下がり状態としては電源電圧 V b、実働電源電圧 V bb、中間電圧 V a、第一の定電圧制御電源30、第二の定電圧制御電源40の順で電圧が減衰する。

[0028]

図 2 で示されたリセット回路80は、電源電圧 V b (又は実働電源電圧 V b b)と中間電圧 V a との電圧レベルを監視して、マイクロプロセッサ51のリセット指令とその解除を行い、リセット指令が解除されたことによってマイクロプロセッサ51の動作が開始するようになっている。次に、電源投入と電源遮断に対応した各部の状態を示したタイムチャートである図 3 について説明する。

図3(A)は、電源電圧 V b の経時特性を示していて、電源投入に伴って0 V から例えば14 V まで上昇し、電源遮断に伴って14 V から0 V まで減衰する。なお、電源の投入・遮断時の増減勾配は時間軸を拡大し誇張して表現されていて以下同様である。

図 3 ( B )は、図 2 の前段比較信号COMPbの論理レベルを示していて、図 3 ( A )における電源電圧 V bが判定閾値電圧 V sb(例えば4.5 V )以上となった時点で論理レベルが「 L 」から「 H 」に変化しており、判定閾値電圧 V sb未満となった時点で「 H 」から「 L 」に復帰している。

[0029]

図3(C)は、中間電圧 Vaの経時特性を示していて、電源投入に伴って0 Vから例えば7 Vまで上昇し、電源遮断に伴って7 Vから0 Vまで減衰する。なお、中間電圧 Vaの立上り・立下り特性は、電源電圧 Vbの立上り・立下り特性よりも遅れており、これは電源コンデンサ22bや出力コンデンサ22aの影響と、中間電圧 Vaを得るための負帰還制御の応答性が影響している。

図 3 ( D ) は、図 2 の後段比較信号COMPaの論理レベルを示していて、図 3 ( C ) における中間電圧 V aが、第一の判定閾値電圧 V sa(例えば4.5 V ) 以上となった時点で論理レベルが「 L 」から「 H 」に変化しており、第二の判定閾値電圧 V saa(例えば4.5-0.5 = 4.0 V ) 未満となった時点で「 H 」から「 L 」に復帰している。

図3(E)は、図2のフリップフロップ回路81のリセット入力端子Rに入力された論理和否定出力素子85の出力信号の論理レベルを示していて、図3(B)の前段比較信号COMPbと図3(D)の後段比較信号COMPaとの、少なくともいずれか一方が論理レベル「L」であるときに出力論理レベルは「H」となっている。

[0030]

図3(F)は、図2のフリップフロップ回路81のセット入力端子Sに入力された後段比較信号COMPaの論理レベルを示していて、これは図3(D)と同じものである。図3(G)は、図2のフリップフロップ回路81のセット出力信号に相当し、マイクロプロセッサ51のリセット端子に入力されるリセット信号RSTの論理レベルを示していて、これは図3(E)のリセット入力信号の反転信号と同じ論理信号となっている。

但し、実際には正常運転中に第一の定電圧制御電源30又は第二の定電圧制御電源40自体の異常によって、第一の安定化電圧 V cc 又は第二の安定化電圧 V ddが異常低下すると、後段比較信号COMPaの論理レベルは暫時「H」を維持しているにも関わらず、フリップフロップ回路81はリセットされるので、図3(G)と図3(E)とが常に反転論理レベルになるわけではない。

10

20

30

40

#### [0031]

次に、正常運転中に電源電圧が一時的に急減して回復した場合の各部の状態を示したタイムチャートである図4について説明する。

図4(A)は、電源電圧 V b が一時的に D C 14 V から D C 6.1 V まで急減し、再び D C 14 V まで回復したことを示す電源電圧 V b の経時特性を示している。このような急減と回復は例えばエンジンの始動用電動機を駆動したような場合に発生する。

図4(B)は、図4(A)に対応した実働電源電圧Vbbの経時特性を示していて、電源電圧VbがDC14VからDC6.1Vに急減すると、実働電源電圧VbbもDC14VからDC6.1Vに急減するが、実働電源電圧Vbbにはアンダーシュートが発生して減少偏差電圧 Vb(例えばDC0.5V)が発生する。これは電源電圧Vbの急減に伴って、電源コンデンサ22bに蓄積されていた電荷が上流側コイル21bを介して放電し、急減した電源電圧Vbと電源コンデンサ22bの両端電圧が等しくなってからも、上流側コイル21bのインダクタンスの影響で暫時は放電が持続することによって発生するものである。電源電圧Vbが元の電圧に回復したときも同様であり、実働電源電圧Vbbはオーバシュートして増量偏差電圧が発生する。

#### [0032]

図4(C)は、図4(A)に対応した中間電圧Vaの経時特性を示していて、電源電圧VbがDC14VからDC6.1Vに急減すると、中間電圧VaはDC7VからDC6Vに急減するが、中間電圧Vaにはアンダーシュートが発生して減少偏差電圧 Vaが発生する。但し、図4(C)の場合には、図1の逆導通抑制回路70Aが設けられておらず、開閉素子20Aがドレーン端子からソース端子の方向へ逆導通している場合を示していて、減少偏差電圧 Vaは例えばDC2.1Vとなり、アンダーシュート電圧はDC3.9Vにまで低下している。その結果、図2における後段比較信号COMPaの論理レベルが一時的に「L」となって、マイクロプロセッサ51がリセットされることになる。

これは電源電圧 V b の急減に伴って出力コンデンサ22aに蓄積されていた電荷が下流側コイル21aを介して放電し、急減した実働電源電圧 V bbと出力コンデンサ22aの両端電圧が等しくなってからも、下流側コイル21aのインダクタンスの影響で暫時は放電が持続することによって発生するものである。電源電圧 V b が元の電圧に回復したときも同様であり、中間電圧 V a はオーバシュートして増量偏差電圧が発生する。

## [0033]

これに対し、図4(D)は、図4(C)と同様に中間電圧 Vaの経時特性を示しているが、図4(D)の場合には図1の逆導通抑制回路70Aが設けられていて、開閉素子20Aがドレーン端子からソース端子の方向へ逆導通しない場合を示している。

但し、開閉素子20Aのドレーン端子とソース端子間には、寄生ダイオードと直列抵抗を含む寄生ダイオード回路20aが並列接続された状態になっており、開閉素子20A自体の逆導通は阻止されていても、寄生ダイオード回路20aによる逆流電流が発生し、減少偏差電圧 Vaは例えばDC0.5 Vとなり、アンダーシュート電圧はDC5.5 Vにまで低下している。これは電源電圧 Vbの急減に伴って出力コンデンサ22aに蓄積されていた電荷が下流側コイル21aと寄生ダイオード回路20aとを介して放電し、急減した実働電源電圧 Vbbと出力コンデンサ22aの両端電圧が等しくなってからも、下流側コイル21aのインダクタンスの影響で暫時は放電が持続することによって発生するものである。

なお、電界効果トランジスタには寄生ダイオード回路が並列接続されているので、ゲート 回路で逆導通を防止しても効果がないと思われているが、実際には図4(C)と図4(D )で示すように歴然とした相違がある。

## [0034]

その結果、図4(D)の場合であれば、図2における後段比較信号COMPaの論理レベルは「H」を維持しておりマイクロプロセッサ51がリセットされることはない。電源電圧Vbが元の電圧に回復したときも同様であり、中間電圧Vaはオーバシュートして増量偏差電圧が発生する。電源電圧Vbや中間電圧Vaのオーバシュートに対しては、第一の定電圧制御電源30、第二の定電圧制御電源40によって除去されて第一安定化電圧Vcc、第二の安定

10

20

30

40

化電圧Vddが得られるようになっている。

### [0035]

なお、以上の説明では、開閉素子20AはPチャンネル型の電界効果トランジスタであるとして説明したが、これに代わって、Nチャンネル型の電界効果トランジスタに置き換えることが可能であることはいうまでもない。

#### [0036]

#### (3) 実施の形態 1 の特徴

以上の説明で明らかなとおり、この発明の実施形態1の車載電子制御装置は、以下のような特徴を有するものである。

### [0037]

この発明の実施形態 1 の車載電子制御装置は、車載バッテリ11から給電された電源電圧 Vbを入力電圧として作動し、所定の中間電圧 V aを降圧生成するためのスイッチング電源 を構成する開閉素子20Aと、この開閉素子の後段に直列接続されて第一の安定化電圧Vcc 又は第二の安定化電圧 V ddを生成する連続制御形の第一の定電圧制御電源30、又は第二 の定電圧制御電源40と、前記第一又は第二の定電圧制御電源から給電され、少なくともマ イクロプロセッサ51とプログラムメモリ52とRAMメモリ53とを有する主制御回路部54、 又は当該主制御回路部と協働する補助制御回路部55とを包含した制御回路部50とを備えた 車載電子制御装置10Aであって、開閉素子20Aと第一又は第二の定電圧制御電源30、40との 間には、誘導性素子である下流側コイル21aが直列接続されていて、当該下流側コイルの 上流側には転流ダイオード25がグランド回路GNDとの間に接続されていると共に、下流側 には出力コンデンサ22aがグランド回路GNDとの間に接続されており、下流側コイル21aの インダクタンス L a と、開閉素子20Aから給電される電気負荷の負荷抵抗 R 0 との比率であ る誘導特定数 La/R0の値は、開閉素子20Aを開閉制御する開閉周期よりも大きな値のもの が使用されていて、開閉素子20Aは P チャンネル型又は N チャンネル型の電界効果トラン ジスタであって、当該電界効果トランジスタのゲート回路には、逆導通抑制回路70Aが接 続されていると共に、中間電圧Vaが所定値未満に低下したときに、少なくともマイクロ プロセッサ51を初期化するためのリセット回路80を備え、電源電圧Vbが一時的に異常低 下したときに、出カコンデンサ22aの充電電荷が開閉素子20Aの逆導通によって上流電源側 に逆流してアンダーシュートが発生するのを抑制して、アンダーシュートによってリセッ ト回路80がマイクロプロセッサ51の初期化を行うのを防止するように構成されている。

### [0038]

即ち、実施の形態1による車載電子制御装置は、電源電圧の変動に伴う定電圧制御電源の消費電力の増大を抑制するために、開閉比率が制御される開閉素子によって安定化された中間電圧を生成し、中間電圧が異常低下すると制御回路部に設けられたマイクロプロセッサを初期化するものにおいて、開閉素子の逆導通抑制回路を備え、車載バッテリの電源電圧が異常低下したときに、開閉素子の出力回路に設けられた出力コンデンサの充電電荷が車載バッテリ側へ逆放電するのを抑制するようになっている。

従って、開閉素子の出力回路に設けられた下流側コイルのインダクタンスを大きくして下流側コイルから充電される出力コンデンサの脈動電圧を抑制することができる一方で、下流側コイルのインダクタンスを大きくしたことに伴って、車載バッテリの電源電圧が一時的に異常低下したときに発生する出力コンデンサの充電電圧のアンダーシュートを抑制し、みだりにマイクロプロセッサが初期化されるのを防止しながら、脈動電圧の小さな中間電圧が得られ、第一又は第二の定電圧制御電源を介して低消費電力で、高精度な安定化電圧を得ることができる効果がある。

#### [0039]

また、中間電圧を得るための開閉素子が閉路駆動されているときの、電圧降下が小さくなって、電源電圧の最小保証電圧をより低く設定することができる効果がある。

#### [0040]

また、実施の形態 1 の車載電子制御装置においては、開閉素子20Aと車載バッテリ11との間には誘導性素子である上流側コイル21bが直列接続されると共に、当該上流側コイル

10

20

30

の下流側には電源コンデンサ22bがグランド回路GNDとの間に接続されていて、上流側コイル21bのインダクタンス L b は、下流側コイル21aのインダクタンス L a よりも小さな値であって、電源コンデンサ22bの静電容量 C b は、出力コンデンサ22aの静電容量 C a よりも大きな値とされ、リセット回路80は、車載バッテリ11から給電された電源電圧 V b、または、電源コンデンサ22bの両端電圧である実働電源電圧 V b b が、所定の判定閾値電圧 V s b 未満となったときには、マイクロプロセッサ51に対するリセット信号RSTを発生し、判定閾値電圧 V s b は、第一の定電圧制御電源30、又は第二の定電圧制御電源40が発生する第一の安定化電圧 V cc、又は第二の安定化電圧 V ddの中のどちらか高い方の安定化電圧よりも低い電圧に設定されている。

## [0041]

即ち、実施の形態1の車載電子制御装置においては、開閉素子の開閉動作に応じて電源線に発生する電磁誘導ノイズを抑制するために、開閉素子の上流側に上流側コイルと電源コンデンサとが接続され、当該上流側コイルと電源コンデンサによって発生する開閉素子の入力電圧のアンダーシュートが、下流側コイルと出力コンデンサによって発生する中間電圧のアンダーシュートよりも小さくなるように規制されていると共に、電源電圧及び中間電圧が所定値未満となったときに、マイクロプロセッサを初期化する二重系のリセット回路を備えている。

従って、電源電圧が急減すると、リセット回路はマイクロプロセッサを直ちにリセットし、中間電圧が漸減異常低下するとマイクロプロセッサが誤動作をする前にリセット回路によってマイクロプロセッサがリセットされるので、第一の定電圧制御電源、第二の定電圧制御電源の上流及び下流位置に設けられる電源保持用コンデンサの容量が小さくても、マイクロプロセッサが誤動作せず、小型安価な電源回路を構成することができる特徴がある。

#### [0042]

また、実施の形態 1 の車載電子制御装置においては、リセット回路80は中間電圧 V aが第一の判定閾値電圧 V sa未満であるときには、マイクロプロセッサ51を初期化するためのリセット信号RSTを発生し、中間電圧 V aが第一の判定閾値電圧 V sa以上となってリセット信号RSTが解除された後は、第一の判定閾値電圧 V saよりは小さな値である第二の判定閾値電圧 V saa = V sa - V sa未満に低下したことによって、リセット信号RSTを発生するヒステリシス特性を有している。

## [0043]

即ち、中間電圧が異常低下したことに応動するリセット回路はヒステリシス特性を有しており、電源電圧が減少するときには、上昇するときよりも低い電圧でリセット信号を発生するようになっている。

従って、電源電圧に一時的なアンダーシュートが発生した場合に、妄りにリセット信号が発生しない特徴がある。

## [0044]

また、実施の形態 1 の車載電子制御装置においては、リセット回路80における第一の判定閾値電圧 V sa と、第二の判定閾値電圧 V sa との間の差分電圧 V sa の値は、上流側コイル21bによって発生する電源電圧 V bのアンダーシュートによる減少偏差電圧 V b以上の値に設定されている。

#### [0045]

即ち、リセット回路に設けられた判定閾値間の差分電圧は、上流側コイルによって発生する電源電圧のアンダーシュート電圧以上の値に設定されている。

従って、上流側コイルと電源コンデンサによって電磁誘導ノイズの流出が抑制されると共に、電源電圧のアンダーシュートによる異常電圧低下によってマイクロプロセッサが初期化されるのを防止することができる特徴がある。

### [0046]

また、実施の形態 1 の車載電子制御装置においては、開閉素子20Aの下流位置には補助制御回路部55に給電する第一の定電圧制御電源30と、主制御回路部54に給電する第二の定

10

20

30

40

電圧制御電源40とが接続され、第一の定電圧制御電源30が発生する第一の安定化電圧 V cc は、第二の定電圧制御電源40が発生する第二の安定化電圧 V ddよりも大きな値であって、電源電圧 V b、又は実働電源電圧 V bbが異常低下したときに、リセット回路80がマイクロプロセッサ51に対するリセット信号を発生する判定閾値電圧 V sbと、中間電圧 V aが異常低下したときに、リセット回路80がマイクロプロセッサ51に対するリセット信号を発生する第一の判定閾値電圧 V saとは、いずれも第一の安定化電圧 V ccよりは小さく、第二の安定化電圧 V ddよりも大きな中間値となっている。

## [0047]

即ち、リセット回路がマイクロプロセッサに対してリセット信号を発生する電源電圧の判定閾値と、中間電圧に対する第一の判定閾値電圧とは、いずれも第一の安定化電圧よりは小さく、第二の安定化電圧よりも大きな中間値となっていて、マイクロプロセッサは第二の安定化電圧によって作動するようになっている。

従って、電源電圧が急減したときは、電源電圧に対する判定閾値電圧に依存してリセット信号が発生するが、過渡的には中間電圧と第一の安定化電圧は正常値を維持しているのでマイクロプロセッサが誤動作せず、電源電圧が漸減したときには、中間電圧に対する第一の判定閾値電圧に依存してリセット信号が発生し、当該リセット信号の発生時点では第二の安定化電圧は正常値を維持していて、マイクロプロセッサの誤動作が発生しない特徴がある。

## [0048]

また、実施の形態 1 の車載電子制御装置においては、開閉素子20Aは、中間電圧 V a に比例した検出電圧と、所定の比較基準電圧 V s0との偏差積分値に応動した通電デューティで当該開閉素子の開閉制御を行なう負帰還通電率制御回路を備え、前記負帰還通電率制御回路を構成する後段比較器60と、当該後段比較器に対する入力信号回路となる比較回路62、偏差積分回路64、およびパルス幅変調制御回路61は、第一の安定化電圧 V ccを電源電圧として動作するのに対し、リセット回路80で使用される判定閾値電圧 V sbと、第一の判定閾値電圧 V sa及び比較回路62に入力される比較基準電圧 V s0は、電源電圧 V bb、又は実働電源電圧 V bbから給電される基準電圧生成回路63によって生成されている。

#### [0049]

即ち、負帰還通電率制御回路は、第一の安定化電圧と基準電圧生成回路によって生成された基準電圧を電源として動作するとともに、リセット回路は、電源電圧又は実働電源電圧及び中間電圧と基準電圧生成回路によって生成された基準電圧を電源として動作するようになっている。

従って、基準電圧生成回路は電源投入に伴って速やかに基準電圧を生成することができるので、第一の安定化電圧が正常値に到達するまでは、負帰還通電率制御回路は全通電状態に制御することができて、速やかに出力電圧を立ち上げることができるとともに、リセット回路は第一・第二の安定化電圧の状態とは無関係に動作して、電源電圧の低下時にマイクロプロセッサを確実にリセットすることができる特徴がある。

### [0050]

更に、実施の形態 1 の車載電子制御装置においては、逆導通抑制回路70Aは車載バッテリ11から給電された電源電圧 V b、又は電源コンデンサ22bの両端電圧である実働電源電圧 V bbに比例した第一の電圧 V 1 と、出力コンデンサ22aの両端電圧である中間電圧 V a に比例した第二の電圧 V 2 とを比較して、開閉素子20Aの上流側電位が下流側電位以下になったことを検出して開閉素子20Aのゲート駆動回路を遮断するようになっている。

## [0051]

即ち、中間電圧を得るための開閉素子の上流側電位が下流側電位以下になったことを検出して、当該開閉素子の駆動回路を遮断するようになっている。

従って、簡単な電圧比較回路によって開閉素子の逆導通の直前状態を検出して、開閉素子が逆導通しないようになっているので、開閉素子の開閉比率制御を行なう負帰還制御回路による開閉素子の閉路指令が無効となり、出力コンデンサの過放電によるアンダーシュートの発生が抑制される特徴がある。

10

20

30

### [0052]

実施の形態2.

## (1)構成と作用の説明

この発明の実施の形態 2 の車載電子制御装置について、部分回路ブロック図である図 5 を参照して、図 1 との相違点を中心にして説明する。なお、図中、図 1 との同一符号は、同一又は相当部分を示している。

図 5 において、密閉筐体内に収納されている車載電子制御装置10Bは、図 1 のものと同様に車載バッテリ11から、電源リレーの出力接点12を介して電源電圧 V b となる電源が供給され、車載センサ群13の動作状態と、プログラムメモリ52に格納された制御プログラムの内容に応動して、車載電気負荷群14を駆動制御するようになっている。

車載電子制御装置10Bの内部にあって、スイッチング電源を構成する開閉素子20Bは、車載バッテリ11と、第一の定電圧制御電源30、および第二の定電圧制御電源40との間に直列接続されていて、開閉素子20Bの上流側と下流側にはそれぞれ、誘導性素子としてのチョークコイルである上流側コイル21bと下流側コイル21aが直列接続され、上流側コイル21bと下流側コイル21aの各下流端には、電源コンデンサ22bと出力コンデンサ22aとがグランド回路GNDとの間に接続されていると共に、下流側コイル21aの上流端とグランド回路GND間には転流ダイオード25が接続されている。

## [0053]

開閉素子20BはNチャンネル型の電界効果トランジスタが使用されていて、開閉素子20Bは、例えばチャージポンプ回路である昇圧回路190の出力電圧によって導通駆動制御が行われるようになっている。昇圧回路190の出力電圧は、導通駆動トランジスタ128と駆動抵抗27Bを介して開閉素子20Bのゲート端子に接続され、開閉素子20Bのゲート端子とソース端子との間には、電圧制限ダイオード26Bが接続されている。PNP型の接合トランジスタである駆動トランジスタ128のベース端子には、駆動抵抗127Bを介して駆動トランジスタ28が接続され、駆動トランジスタ128のエミッタ端子とベース端子との間には、開路安定抵抗126Bが接続されている。

従って、開閉素子20Bは、駆動トランジスタ128と駆動トランジスタ28を介して負帰還通電率制御回路を構成する後段比較器60から開閉制御され、所望の中間電圧 Vaを生成するようになっている。なお、負帰還通電率制御回路やマイクロプロセッサ51に対するリセット回路80は、図1、図2のものと同じ制御内容となっている。

### [0054]

開閉素子20Bのドレーン端子には電流検出抵抗74が直列接続されていて、この電流検出抵抗74の両端電圧が所定値を超過すると、図示しない保護回路によって開閉素子20Bを強制遮断して過電流保護動作を行うようになっている。また、電源電圧 V b が異常低下して、開閉素子20Bの逆導通によって電流検出抵抗74に発生する逆方向電圧が所定値を超過すると、逆流検出回路75の出力論理レベルが「H」となり、ベース抵抗73を介して遮断トランジスタ72が導通駆動され、その結果、駆動トランジスタ28が不導通となって開閉素子20 B が開路するようになっている。

なお、開閉素子20B自体が開路しても、開閉素子20Bには寄生ダイオード回路20bによる逆流回路が構成されているため、一旦逆流が開始すると逆流検出回路75の出力は論理レベル「H」を維持し、開閉素子20B自体は断続動作せずに継続遮断されることになる。

#### [0055]

電源電圧 V b が回復して中間電圧 V a 以上の電圧になると、開閉素子20Bの逆導通状態は解除され、逆流検出回路75の出力論理レベルは「L」に復帰する。その結果、電源電圧 V b が一時的に急減したときに発生する中間電圧 V a のアンダーシュートが抑制されるようになっている。従って、図 5 で示す実施の形態 2 の車載電子制御装置も、図 1 の実施の形態 1 のものと同様に、図 3 、図 4 で示したタイムチャートに示すとおりの動作を行うようになっている。

なお、以上の説明では、開閉素子20BはNチャンネル型の電界効果トランジスタであるとして説明したが、これに代わって図1で説明したようなPチャンネル型の電界効果トラ

10

20

30

40

ンジスタに置き換えることが可能であることはいうまでもない。

### [0056]

(2)実施の形態2の特徴

以上の説明で明らかなとおり、この発明の実施形態 2 の車載電子制御装置は、以下のような特徴を有するものである。

## [0057]

この発明の実施形態 2 の車載電子制御装置は、車載バッテリ11から給電された電源電圧 V bを入力電圧として作動し、所定の中間電圧 V aを降圧生成するためのスイッチング電源を構成する開閉素子20Bと、この開閉素子20Bの後段に直列接続されて、第一の安定化電圧 V cc又は第二の安定化電圧 V ddを生成する連続制御形の第一の定電圧制御電源30又は第二の定電圧制御電源40と、当該第一又は第二の定電圧制御電源から給電され、少なくともマイクロプロセッサ51とプログラムメモリ52と R A M メモリ53とを有する主制御回路部54、又は主制御回路部54と協働する補助制御回路部55とを包含した制御回路部50とを備えた車載電子制御装置10Bであって、開閉素子20Bと第一の定電圧制御電源30又は第二の定電圧制御電源40との間には、誘導性素子である下流側コイル21aが直列接続されていて、当該下流側コイルの上流側には転流ダイオード25がグランド回路GNDとの間に接続されている。

そして、下流側コイル21aのインダクタンス Laと開閉素子20Bから給電される電気負荷の負荷抵抗 R 0との比率である誘導特定数 La/R 0の値は、開閉素子20Aを開閉制御する開閉周期よりも大きな値のものが使用されていて、開閉素子20Bは N チャンネル型又は P チャンネル型の電界効果トランジスタであって、当該電界効果トランジスタのゲート回路には、逆導通抑制回路70Bが接続されている。また、中間電圧 V a が所定値未満に低下した時に、少なくともマイクロプロセッサ51を初期化するためのリセット回路80を備え、電源電圧 V b が一時的に異常低下した時に、出力コンデンサ22aの充電電荷が開閉素子20Bの逆導通によって上流電源側に逆流してアンダーシュートが発生するのを抑制して、アンダーシュートによってリセット回路80がマイクロプロセッサ51の初期化を行うのを防止するようになっている。

## [0058]

そして、逆導通抑制回路70Bは、開閉素子20Bと直列接続された電流検出抵抗74の両端電圧が、開閉素子20Bの逆導通による逆方向電圧を検出したことによって開閉素子20Bのゲート駆動回路を遮断し、電流検出抵抗74は、正常動作中の開閉素子20Bに対する過電流遮断制御用に使用されるようになっている。

#### [0059]

即ち、実施の形態 2 においては、中間電圧を得るための開閉素子に直列接続された電流検出抵抗と、当該電流検出抵抗の両端電圧によって開閉素子の逆導通が検出されたことによって、当該開閉素子のゲート駆動回路を遮断するようになっている。

従って、電流検出回路を併用することによって開閉素子の逆導通状態を検出して、開閉素子が逆導通しないようになっているので、逆導通電流が所定値以下に制限され、出力コンデンサの過放電によるアンダーシュートの発生が抑制されると共に、開閉素子と直列接続された電流検出抵抗を用いて開閉素子の過電流抑制制御機能を付加することができる特徴がある。

### 【符号の説明】

## [0060]

10A、10B 車載電子制御装置、

11 車載バッテリ、

20A、20B 開閉素子、

21a 下流側コイル、

21b 上流側コイル、

22a 出力コンデンサ、

22b 電源コンデンサ、

GND グランド回路、

La、Lb インダクタンス、

R 負荷抵抗、

RST リセット信号、

Va 中間電圧、

Vb 電源電圧、

Vb 減少偏差電圧、

10

20

30

- -

40

- 25 転流ダイオード、

- 30 第一の定電圧制御電源、

- 40 第二の定電圧制御電源、

- 50 制御回路部、

- 51 マイクロプロセッサ、

- 52 プログラムメモリ、

- 53 RAMメモリ、

- 54 主制御回路部、

- 55 補助制御回路部、

- 60 後段比較器(負帰還通電率制御回路)、

- 61 パルス幅変調制御回路、

- 62 比較回路、

- 63 基準電圧生成回路、

- 64 偏差積分回路、

- 70A、70B 逆導通防止回路、

- 74 電流検出抵抗、

- 80 リセット回路。

Vbb 実働電源電圧、

Vcc 第一の安定化電圧、

Vdd 第二の安定化電圧、

Vsa 第一の判定閾値電圧、

Vsaa 第二の判定閾値電圧、

Vsa 差分電圧、

Vsb 判定閾値電圧、

Vs0 比較基準電圧。

10

## 【図1】

## 【図2】

50 80 80 Va Vb Vb Vb Vc Vc Vdd Vs0

【図3】

【図4】

【図5】

### フロントページの続き

(72)発明者 橋本 光司

東京都千代田区九段北一丁目13番5号 三菱電機エンジニアリング株式会社内

(72)発明者 山下 学

東京都千代田区九段北一丁目13番5号 三菱電機エンジニアリング株式会社内

(72)発明者 圖子 雄二

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72)発明者 西田 充孝

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

#### 審査官 永田 和彦

(56)参考文献 特開平7-95765 (JP,A)

特開2003-316482(JP,A)

特開2008-289254(JP,A)

特開2000-354363(JP,A)

特開2008-61435(JP,A)

特開2006-211785(JP,A)

特開2004-112922(JP,A)

特開平9-247929(JP,A)

特開平10-248246 (JP,A)

## (58)調査した分野(Int.CI., DB名)

H02M 3/00-3/44,

H02J 7/00-7/36,

B60R 16/03-16/033