(19) **日本国特許庁(JP)**

G 1 1 C 11/401

(51) Int. Cl.

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4552258号 (P4552258)

(45) 発行日 平成22年9月29日(2010.9.29)

(24) 登録日 平成22年7月23日(2010.7.23)

FI G11C 11/34 362H

G11C 11/34 371K

請求項の数 16 (全 29 頁)

(21) 出願番号 特願2000-90188 (P2000-90188)

(22) 出願日 平成12年3月29日 (2000.3.29) (65) 公開番号 特開2001-273764 (P2001-273764A)

(2006, 01)

(43) 公開日 平成13年10月5日 (2001.10.5) 審査請求日 平成18年12月7日 (2006.12.7) ||(73)特許権者 500174247

エルピーダメモリ株式会社 東京都中央区八重洲2-2-1

|(74)代理人 100123788

弁理士 宮崎 昭夫

(74)代理人 100106138

弁理士 石橋 政幸

(74)代理人 100127454

弁理士 緒方 雅昭

||(72)発明者 関口 知紀

東京都国分寺市東恋ケ窪一丁目280番地 株式会社 日立製作所 中央研究所内

最終頁に続く

(54) 【発明の名称】半導体記憶装置

# (57)【特許請求の範囲】

# 【請求項1】

第1方向に沿って配置された複数のメモリアレイ領域と、

上記複数のメモリアレイ領域と交互に配置された複数のセンスアンプ領域とを有し、

上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のビット線と、上記第1方向と直交する第2方向に沿って設けられた複数のワード線と、上記複数のビット線と上記複数のワード線との交差部に対応して設けられた複数のメモリセルとを備え、

各センスアンプ領域に隣接する両側のメモリアレイ領域のうちの一方に延びるビット線と他方に延びるビット線とから一対の信号を受けるセンスアンプが上記各センスアンプ領域内に設けられ、

メモリアレイ領域を2つ以上間に挾んで離れた2つのメモリアレイ領域に対するそれぞれのワード線選択タイミングが独立に制御されることを特徴とする半導体記憶装置。

# 【請求項2】

請求項1において、

上記メモリアレイ領域を1つ間に挾んで離れた2つのメモリアレイ領域に対するそれぞれのワード線選択タイミングが一定期間ずれて制御されることを特徴とする半導体記憶装置。

# 【請求項3】

請求項1又は2において、

20

上記メモリセルは、MOSFETとキャパシタとからなり、上記MOSFETのゲートが選択端子とされ、一方のソース,ドレインが入出力端子とされ、他方のソース,ドレインが上記キャパシタの一方の電極である蓄積ノードと接続されてなるダイナミック型メモリセルであって、

上記メモリアレイに設けられるキャパシタの他方の電極は、一体化されたプレート電極により構成されてなることを特徴とする半導体記憶装置。

#### 【請求項4】

第1方向に沿って配置された複数のメモリアレイ領域と、

上記複数のメモリアレイ領域と交互に配置された複数のセンスアンプ領域とを有し、

上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のビット線と、上記第1方向と直交する第2方向に沿って設けられた複数のワード線と、上記複数のビット線と上記複数のワード線との交差部に対応して設けられた複数のメモリセルとを備え、

各センスアンプ領域に隣接する両側のメモリアレイ領域のうちの一方に延びるビット線と他方に延びるビット線とから一対の信号を受けるセンスアンプが上記各センスアンプ領域内に設けられ、

メモリアレイ領域を 2 つ以上間に挾んで離れた 2 つのメモリアレイ領域に対するそれぞれのワード線選択アドレスが独立に設定されることを特徴とする半導体記億装置。

#### 【請求項5】

請求項4において、

上記メモリセルは、MOSFETとキャパシタとからなり、上記MOSFETのゲートが選択端子とされ、一方のソース,ドレインが入出力端子とされ、他方のソース,ドレインが上記キャパシタの一方の電極である蓄積ノードと接続されてなるダイナミック型メモリセルであって、

上記メモリアレイに設けられるキャパシタの他方の電極は、一体化されたプレート電極により構成されてなることを特徴とする半導体記憶装置。

## 【請求項6】

第 1 方向に沿って配置された複数のメモリアレイ領域と、上記複数のメモリアレイ領域と交互に配置された複数のセンスアンプ領域とを有し、

上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のビット線と、上記第1方向と直交する第2方向に沿って設けられた複数のワード線と、上記複数のビット線と上記複数のワード線との交差部に対応して設けられた複数のメモリセルとを備え

各センスアンプ領域に隣接する両側のメモリアレイ領域のうちの一方に延びるビット線と他方に延びるビット線とから一対の信号を受けるセンスアンプが上記各センスアンプ領域内に設けられ、

隣接して設けられた2つのメモリアレイ領域により1つのバンクを構成し、かかるバンクの複数個のうち1つのバンクを挟んで離れた2つのバンクに対するそれぞれのワード線選択タイミングが独立に制御されることを特徴とする半導体記億装置。

#### 【請求項7】

請求項6において、上記複数のバンクのうち互いに隣接する2つのバンクに対するそれぞれのワード線選択タイミングが一定期間ずれて制御されることを特徴とする半導体記憶装置。

# 【請求項8】

請求項6又は7において、

上記メモリセルは、MOSFETとキャパシタとからなり、上記MOSFETのゲートが選択端子とされ、一方のソース,ドレインが入出力端子とされ、他方のソース,ドレインが上記キャパシタの一方の電極である蓄積ノードと接続されてなるダイナミック型メモリセルであって、

上記メモリアレイに設けられるキャパシタの他方の電極は、一体化されたプレート電極

20

10

30

40

により構成されてなることを特徴とする半導体記憶装置。

# 【請求項9】

第1方向に沿って配置された複数のメモリアレイ領域と、上記複数のメモリアレイ領域 と交互に配置された複数のセンスアンプ領域とを有し、

上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のビ ット線と、上記第1方向と直交する第2方向に沿って設けられた複数のワード線と、上記 複数のビット線と上記複数のワード線との交差部に対応して設けられた複数のメモリセル とを備え、

各センスアンプ領域に隣接する両側のメモリアレイ領域のうちの一方に延びるビット線 と他方に延びるビット線とから一対の信号を受けるセンスアンプが上記各センスアンプ領 域内に設けられ、

隣接して設けられた2つのメモリアレイ領域により1つのバンクを構成し、かかるバン クの複数個のうち1のバンクを挾んで離れた2つのバンクに対するそれぞれのワード線選 択アドレスが独立に設定されることを特徴とする半導体記億装置。

# 【請求項10】

請求項9において、

上記メモリセルは、MOSFETとキャパシタとからなり、上記MOSFETのゲート が選択端子とされ、一方のソース,ドレインが入出力端子とされ、他方のソース,ドレイ ンが上記キャパシタの一方の電極である蓄積ノードと接続されてなるダイナミック型メモ リセルであって、

上記メモリアレイに設けられるキャパシタの他方の電極は、一体化されたプレート電極 により構成されてなることを特徴とする半導体記憶装置。

#### 【請求項11】

第1方向に沿って配置された複数のメモリアレイ領域と、上記複数のメモリアレイ領域 と交互に配置された複数のセンスアンプ領域とを有し、

上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のビ ット線と、上記第1方向と直交する第2方向に沿って設けられた複数のワード線と、上記 複数のビット線と上記複数のワード線との交差部に対応して設けられた複数のメモリセル とを備え、

各センスアンプ領域に隣接する両側のメモリアレイ領域のうちの一方に延びるビット線 と他方に延びるビット線とから一対の信号を受けるセンスアンプが上記各センスアンプ領 域内に設けられ、

上記1つのメモリアレイ領域により1つのバンクを構成し、かかるバンクの複数個のう ち2のバンクを挾んで離れた2つのバンクに対するそれぞれのワード線選択アドレスが独 立に設定されることを特徴とする半導体記億装置。

# 【請求項12】

請求項11において、1つのバンクを挟んで離れた2つのバンクをセンスアンプによる 微小信号増幅期間にはバンクの活性化が禁止されるものであることを特徴とする半導体記 憶装置。

#### 【請求項13】

請求項11において、

1つのバンクを挟んで離された2つのバンクは、一方が活性化された時には、他方は所 定時間遅れて活性化が許可されることを特徴とする半導体記憶装置。

# 【請求項14】

請求項11ないし13のいずれかにおいて、

上記メモリセルは、MOSFETとキャパシタとからなり、上記MOSFETのゲート が選択端子とされ、一方のソース,ドレインが入出力端子とされ、他方のソース,ドレイ ンが上記キャパシタの一方の電極である蓄積ノードと接続されてなるダイナミック型メモ リセルであって、

上記メモリアレイに設けられるキャパシタの他方の電極は、一体化されたプレート電極

20

10

30

40

により構成されてなることを特徴とする半導体記憶装置。

# 【請求項15】

複数の第1ビット線と、複数の第1ワード線と、上記複数の第1ビット線と上記複数の 第1ワード線に結合された複数の第1メモリセルを含む第1メモリマットと、

複数の第2ビット線と、複数の第2ワード線と、上記複数の第2ビット線と上記複数の第2ワード線との交点に結合された複数の第2メモリセルを含む第2メモリマットと、

上記第1メモリマットと上記第2メモリマットとの問の領域に形成される複数センスアンプとを含み、

上記複数のセンスアンプの各々は、上記複数の第1ビット線のうちの対応する1つと上記複数の第2ビット線のうちの対応する1つに結合され、

上記複数の第1メモリセルの各々は、第1及び第2電極を有する第1容量と、上記複数の第1ワード線のうちの対応する1つに結合されたゲートと、その一方が上記複数の第1ビット線のうちの対応する1つに結合されその他方が上記第1容量の上記第1電極に結合されたソース・ドレイン経路とを有する第1トランジスタとを含み、

上記複数の第2メモリセルの各々は、第3及び第4電極を有する第2容量と、上記複数の第2ワード線のうちの対応する1つに結合されたゲートと、その 方が上記複数の第2ビット線のうちの対応する1つに結合されその他方が上記第2容量の上記第3電極に結合されたソース・ドレイン径路とを有する第2トランジスタとを含み、

上記複数の第1メモリセルの上記第1容量の上記第2電極の各々及び上記複数の第2メモリセルの上記第2容量の上記第4電極の各々は、上記第1メモリマット、上記第2メモリマット及び上記複数のセンスアンプの上に配置された1つの導電層に結合され、

上記メモリマットを2つ以上間に挾んで離れた2つのメモリマットに対するそれぞれのワード線選択アドレスが独立に設定されることを特徴とする半導体記億装置。

#### 【請求項16】

複数の第1ビット線と、複数の第1ワード線と、上記複数の第1ビット線と上記複数の 第1ワード線に結合された複数の第1メモリセルを含む第1メモリマットと、

複数の第2ビット線と、複数の第2ワード線と、上記複数の第2ビット線と上記複数の第2ワード線との交点に結合された複数の第2メモリセルを含む第2メモリマットと、

上記第1メモリマットと上記第2メモリマットとの問の領域に形成される複数センスアンプとを含み、

上記複数のセンスアンプの各々は、上記複数の第1ビット線のうちの対応する1つと上記複数の第2ビット線のうちの対応する1つに結合され、

上記複数の第1メモリセルの各々は、第1及び第2電極を有する第1容量と、上記複数の第1ワード線のうちの対応する1つに結合されたゲートと、その一方が上記複数の第1ビット線のうちの対応する1つに結合されその他方が上記第1容量の上記第1電極に結合されたソース・ドレイン経路とを有する第1トランジスタとを含み、

上記複数の第2メモリセルの各々は、第3及び第4電極を有する第2容量と、上記複数の第2ワード線のうちの対応する1つに結合されたゲートと、その 方が上記複数の第2ビット線のうちの対応する1つに結合されその他方が上記第2容量の上記第3電極に結合されたソース・ドレイン径路とを有する第2トランジスタとを含み、

上記複数の第1メモリセルの上記第1容量の上記第2電極の各々及び上記複数の第2メモリセルの上記第2容量の上記第4電極の各々は、上記第1メモリマット、上記第2メモリマット及び上記複数のセンスアンプの上に配置された1つの導電層に結合され、

隣接して設けられた2つのマットにより1つのバンクを構成し、かかるバンクの複数個のうち1のバンクを挟んで離れた2つのバンクに対するそれぞれのワード線選択アドレスが独立に設定されることを特徴とする半導体記億装置。

## 【発明の詳細な説明】

# [0001]

# 【発明の属する技術分野】

この発明は、半導体記憶装置に関し、主にワード線とビット線の交点にダイナミック型メ

10

20

30

モリセルが配置されてなるいわゆる 1 交点方式のメモリアレイを用い、多数のバンクを備えたものに利用して有効な技術に関するものである。

#### [00002]

# 【従来の技術】

本発明を成した後の調査によって、後で説明する本発明に関連すると思われるものとして、特開平4-134691号公報(以下、先行技術1という)、特開平2-289988号公報(以下、先行技術2という)、特開平9-213069号公報(以下、先行技術3という)、特開平4-66929号公報(以下、先行技術4という)、特開平9-246482号公報(以下、先行技術5という)があることが判明した。先行技術1ないし5の公報においては、MOS容量を利用した情報記憶キャパシタを用い、かつオープンビットライン型(1交点方式)のセンスアンプを交互配置するものが開示されている。しかしながら、これらの公報には、いずれにおいても後に説明するような本願発明に係るマルチバンク構成のDRAMに向けた配慮は何ら開示されていない。

# [0003]

# 【発明が解決しようとする課題】

ダイナミック型RAM(以下、単にDRAMという)ではコスト低減が望まれている。そのためにはチップサイズの低減が最も効果的である。これまでは微細化を推し進めてメモリセルサイズを縮小してきたが、今後はメモリアレイの動作方式も変えることにより、さらにセルサイズを縮小する必要がある。メモリアレイの動作方式を2交点から1交点に変えることにより、同一のデザインルールを用いて理想的にはセルサイズを75%低減できる。しかし、1交点方式のメモリアレイは2交点方式のメモリアレイと比較して、ビット線等に乗るアレイノイズが大きいという問題がある。

#### [0004]

一方、システム性能向上のため、ランバス(Rambus ) DRAMやロジック混載 DRAM においては、マルチバンク構成の DRAMアレイが重要となってきている。 1 交点アレイのマルチバンクの DRAMを構成した場合、上記のように 1 交点方式のメモリアレイは 2 交点方式のメモリアレイと比較してビット線等に乗るアレイノイズが大きいという問題があり、隣接したマット間のノイズの干渉がマルチバンク構成では大きな問題となることが判明した。加えて、 1 交点でセンスアンプを交互配置した場合に生ずる端マットによるチップ面積の増加も問題であり、マルチバンク構成の DRAMに向けたこれらの問題の解決法を検討する中で発明が生まれるに至った。

# [0005]

この発明の目的は、高集積化と動作の安定化を実現したマルチバンク構成の半導体記憶装置を提供することにある。この発明の他の目的は、高集積化と動作の安定化を図りつつ、 使い勝手のよい半導体記憶装置を提供することにある。この発明の前記ならびにそのほか の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

# [0006]

## 【課題を解決するための手段】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば、下記の通りである。第1方向に沿って配置された複数のメモリアレイ領域と交互に配置された複数のセンスアンプ領域を設け、上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のビット線と、上記第1方向と直交する第2方向に沿って設けられた複数のワード線と、上記複数のビット線と上記複数のワード線との交差部に対応して設けられた複数のメモリセルを設け、各センスアンプ領域に隣接する両側のメモリアレイ領域のうちの一方に延びるビット線と他方に延びるビット線とから一対の信号を受けるセンスアンプを設け、メモリアレイ領域を2つ以上間に挾んで離れた2つのメモリアレイ領域に対するそれぞれのワード線選択タイミング又はアドレスを独立に設定する。

#### [0007]

本願において開示される発明のうち他の代表的なものの概要を簡単に説明すれば、下記の通りである。第1方向に沿って配置された複数のメモリアレイ領域と交互に配置された複

10

20

30

40

20

30

40

50

数のセンスアンプ領域を設け、上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のビット線と、上記第1方向と直交する第2方向に沿って設けられた複数のワード線と、上記複数のビット線と上記複数のワード線との交差部に対応して設けられた複数のメモリセルを設け、各センスアンプ領域に隣接する両側のメモリアレイ領域のうちの一方に延びるビット線と他方に延びるビット線とから一対の信号を受けるセンスアンプを設け、隣接して設けられた2つのメモリアレイ領域により1つのバンクを構成し、かかるバンクの複数個のうち1のバンクを挟んで離れた2つのバンクに対するそれぞれのワード線選択アドレスを独立に設定する。

# [00008]

# 【発明の実施の形態】

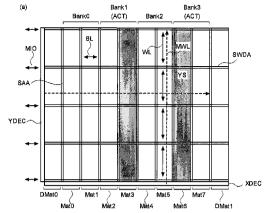

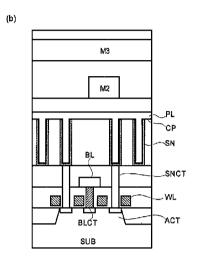

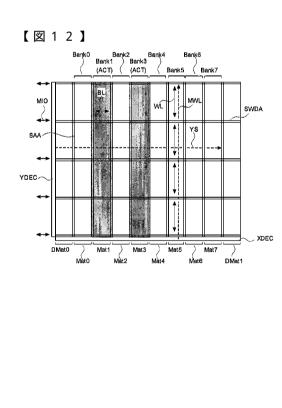

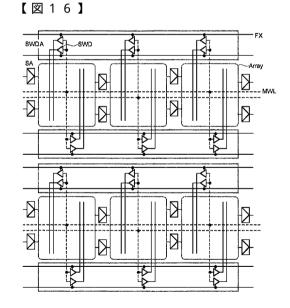

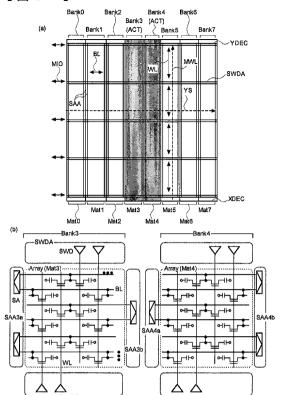

図1には、この発明に係るDRAMの一実施例の概略構成図が示されている。図1(a)には、マットとバンクの関係を示すレイアウトが例示的に示され、図1(b)は1つのバンクのマット構成が例示的に示されている。図1(a)において、メモリアレイに接する部分には、行デコーダXDECと列デコーダYDECとが設けられる。行デコーダXDECは、それに対応したメモリアレイを貫通するように延長されるメインワード線MWLの選択信号を形成する。

## [0009]

上記行デコーダ X D E C には、サブワード選択用のサブワード選択線のドライバも設けられ、上記メインワード線と平行に延長されてサブワード選択線の選択信号が伝えられる。列デコーダ Y D E C は、それに対応したメモリアレイを貫通するように延長されたカラム選択線 Y S を通してセンスアンプ列 S A A に設けられたカラム選択スイッチに選択信号を供給する。

#### [0010]

上記メモリアレイは、複数からなるアレイ(Array)又はマット(Mat)に分割される。 同図の例では、上記メインワード線MWL方向には 4 つに分割され、上記カラム選択線 YS方向には 1 0 分割される。上記 1 つのアレイは、センスアンプ領域(又はセンスアンプ列)SAA、サブワードドライバ領域(又はサブワードドライバ列)SWDAに囲まれて形成される。上記センスアンプ領域SAAと上記サブワードドライバ領域SWDAとの交差部は、交差領域(クロスエリア)とされる。

# [0011]

上記センスアンプ領域SAAに設けられるセンスアンプSAは、CMOS構成のラッチ回路により構成され、かかるセンスアンプSAを中心にして左右に延長される相補ビット線の信号を増幅するという、いわゆる1交点方式とされる。1つのアレイは、特に制限されないが、サブワード線が512本と、それと直交する相補ビット線の一方(又はデータ線)は1024本とされる。したがって、上記のような1つのアレイでは、約512Kビットのような記憶容量を持つようにされる。

# [0012]

図 1 (b)において、ビット線BLとワード線WLの全ての交点にMOSトランジスタとセル容量からなるメモリセルが接続されている。ビット線BLにはセンスアンプSA、ワード線WLにはサブワードドライバSWDが接続される。サブワードドライバSWDとセンスアンプSAで囲まれるアレイ(Array)領域内にはメモリセルがアレイ状に配置される。

# [0013]

上記センスアンプSAはアレイ領域(Array)に対して交互配置されており、例示的に示されているマット(Mat)2内のビット線BLに注目すると左右のセンスアンプSAに交互に接続されている。ここではビット線BLの1本おきに左右のセンスアンプSAに接続される場合を示したが、ビット線BLの2本おきに左右のセンスアンプSAに接続されてもよい。

# [0014]

行デコーダ(XDEC)から出力されるメインワード線MWLはワード線WLと同方向に

20

30

40

50

配線され、サブワードドライバ列SWDAにメインワード選択信号を入力する。列デコーダ(YDEC)から出力されるカラム(列)選択線YSはビット線BLと同方向に配線され、センスアンプ列SAAに設けられるカラムスイッチに列選択線を入力する。この実施例では、センスアンプSAとサブワードドライバSWDにより囲まれた領域をアレイ(Array)といい、ワード線方向にならんだ複数のアレイをマットと呼ぶことにする。

# [0015]

この発明に係る1交点アレイ従属バンクDRAMでは、上記のように隣接した2つのマットで1つのバンクを構成する。例えば、バンク1はマット2、3から構成される。そして、あるバンクを活性化した後、そのバンクをプリチャージするまでは隣接バンクの活性化を禁止するようにされる。バンクの境界ではセンスアンプが左右のバンクから共用されているため従属バンク構成となる。また、最も外側には参照ビット線BLが設けられるダミーマットDMat0 とDMat1 が配置される。

#### [0016]

図1(a)において、メインワード線の数を減らすために、言い換えるならば、メインワード線の配線ピッチを緩やかにするために、特に制限されないが、1つのメインワード線に対して、ビット線方向に4本からなるサブワード線を配置させる。メインワード線方向には4本に分割され、及びビット線方向に対して上記4本ずつが割り当てられたサブワード線の中から1本のサブワード線を選択するために、サブワード選択ドライバが上記行デコーダXDECに配置される。このサブワード選択ドライバは、上記サブワードドライバの配列方向(サブワードドライバ列SWDA)に延長される4本のサブワード選択線の中から1つを選択する選択信号を形成する。

#### [0017]

上記 2 つのアレイ A rray (Mat2 とMat3)の間に設けられたセンスアンプ列 S A A 3 のセンスアンプ S A は、上記 2 つのアレイ (Mat2 とMat3)の両側に延長するような一対のビット線に接続される。これらのセンスアンプ S A は、上記センスアンプ列 S A A において、2 つのビット線毎に 1 つのセンスアンプ S A が配置される。したがって、上記アレイ(Mat2 とMat3)の間に設けられたセンスアンプ列 S A A には、前記のようにビット線 B L が 1 0 2 4 本ある場合には、その半分の 5 1 2 個のセンスアンプ S A が設けられる。

# [0018]

そして、アレイ(Mat2)において、残りの512本のビット線は、アレイ(Mat2)と図示しないアレイ(Mat1)との間に設けられたセンスアンプ列SAAに設けられたセンスアンプ列SAAに設けられたセンスアンプSAに接続される。アレイ(Mat3)において、残り512本のビット線は、アレイ(Mat3)と図示しないアレイ(Mat4)との間に設けられたセンスアンプ列SAAに設けられたセンスアンプSAのビット線方向の両側の分散配置によって、2本分のビット線に対して1つのセンスアンプを形成すればよいから、センスアンプSAとビット線BLのピッチを合わせて高密度にサブアレイ及びセンスアンプ列を形成することができる。

## [0019]

このことは、サブワードドライバSWDにおいても同様である。1つのアレイArrayに設けられた512本のサブワード線WLは、256本ずつに分けられてアレイArrayの両側に配置されたサブワードドライバ列SWDAの256個のサブワードドライバSWDに接続される。この実施例では、2本のサブワード線WLを1組として、2個ずつのサブワードドライバSWDが分散配置される。つまり、2本のサブワード線を1組として、2つのサブワードドライバSWDがアレイArrayの一端側(図の上側)に配置され、それと隣接する上記同様の2本のサブワード線を1組として、2つのサブワードトライバSWDがアレイArrayの他端側(図の下側)に配置される。

#### [0020]

上記サブワードドライバSWDは、図示しないが、それが形成されるサブワードドライバ列SWDAを挟んで両側に設けられるサブアレイのサブワード線の選択信号を形成する。 これにより、メモリセルの配列ピッチに合わせて形成されたサブワード線に対応して、サ

20

30

40

50

ブワードドライバSWDを効率よく分散配置させるとともに、サブワードドライバSWDから遠端部のメモリセルまでの距離が短くなってサブワード線WLによるメモリセルの選択動作を高速に行なうようにすることができる。

# [0021]

特に制限されないが、上記各メモリセルが形成されるアレイArrayにおいて、記憶キャパシタの上部電極(プレート電極)はアレイ内の全てのメモリセルMCで共通に形成されて平面状の電極とされる。かかるプレート電極への給電は、ビット線BLの延長方向に配線された電源配線より接続部を介して、サブワードドライバ列SWDAとアレイとの境界で行うようにされる。そして、アレイ間のプレート電極は、センスアンプ列の隙間を利用して、プレート電極と同じ電極材料により相互に接続される。

# [0022]

つまり、アレイにそれぞれ形成される上記のようなプレート電極を、プレート層自体を用いた配線で互いに接続する。しかも、この配線をセンスアンプ列SAAを貫通させるよう多数設けて、2つのプレート電極の間の抵抗を大幅に下げるようにするものである。これによって、上記アレイ相互のビット線BL間に選択されたメモリセルMCから読み出された微小信号をセンスアンプSAによって増幅する際にプレート電極に生ずる互いに逆相になるノイズを高速に打ち消すことが可能になり、プレート電極に生ずるノイズを大幅に低減させることが可能になる。

## [0023]

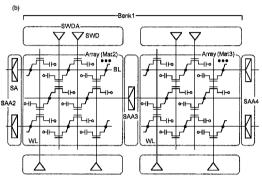

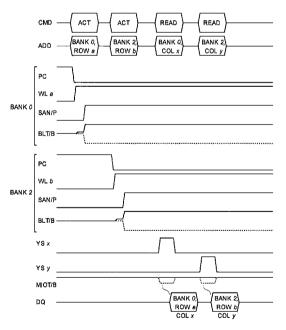

図2には、この発明に係るDRAMの動作の一例の説明図が示されている。同図においては、連続して2つのバンクが活性化されたときの動作を示されている。この実施例では、前記のようにあるバンクを活性化した後、そのバンクをプリチャージするまでは隣接バンクの活性化を禁止するようにされる。したがって、例えばバンク(Bank)1のうちの右側のマット中のワード線WL3が活性化された後、バンク3(Bank)のうちの左側のマット中のワード線WL6が活性化される時が、最も近接したマットが続けて活性化される例である。

## [0024]

最初に増幅されるバンク1における右側マットのビット線BL4Tはバンク2中の左側マットのビット線BL4Bを参照用ビット線BLとして用い、後に増幅されるバンク3の左側マットのビット線BL6Tは上記バンク2中の右側マットのビット線BL6Bを参照用ビット線BLに用いる。上記バンク2に属する左側マットの参照用として用いられるビット線BL4Bと、上記バンク2に属する右側マットの参照用として用いられるビット線BL6Bは上記のように左右異なるマットに存在しているため、ビット線BL4Bの増幅により、基板SUB4にノイズが加わつても、ビット線BL6Bにはノイズが戻らない。

# [0025]

ここで、上記1交点アレイでのノイズの発生原理について説明する。図9には非選択ワード線ノイズの発生原理の説明図が示されている。図9(a)において、ワーストケースとして選択マット(ワード線が選択される)のビット線が1本を除いて全てロウレベル(L)に増幅され、反対側のマット(ワード線は非選択となりビット線は参照用に用いられる)のビット線が1本を除いて全てハイレベル(H)に増幅される。このとき、選択マット中の1本だけハイレベル(H)の信号が出ているビット線が、非選択ワード線からノイズを受け、誤つて増幅される危険がある。

# [0026]

一例としてセンスアンプSAの左側マットのワード線WL0が活性化され、ビット線BL1Tにのみハイレベル(H)の信号がでてきて、その他のビット線BL0T、BL2T等にはロウレベル(L)の信号が読み出される場合を考える。さらにメモリセルのリーク等の理由により、ビット線BL1Tに生ずるハイレベル(H)のメモリセルからの電荷分散による信号が少ないとする。センスアンプSA0~SA3を活性化すると、信号が大きくでてきているビット線対BL0T/B、BL2T/B等は早く増幅される。一方、信号が少ないビット線対BL1T/Bは増幅が遅くなる。

#### [0027]

このとき、選択マットのワード線WL1には上記一斉にロウレベルに変化するビット線BL0T,BL2Tとの寄生容量CBLWLによってビット線BL1Tの電位を下げるようなノイズNoiseが発生し、逆に非選択マットのワード線WL2には上記一斉にハイレベルに変化するビット線BL0B,BL2Bからの上記ような寄生容量によるカップリングによってビット線BL1Bの電位を上げるようなノイズNoiseが発生し、上記メモリセルから読み出されたビット線BL1TとBL1Bの電位差を逆転させるようになると、センスアンプSA1はそれを増幅してしまうので誤動作してしまう。

# [0028]

上記のような 1 交点方式のメモリアレイではメモリセルに蓄積されている信号電荷量が減少してきたときに、情報が誤って読み出される危険性が高い。このことは、リフレッシュ特性の劣化につながり、 DRAMの歩留まりを大きく低下させる原因となる。

#### [0029]

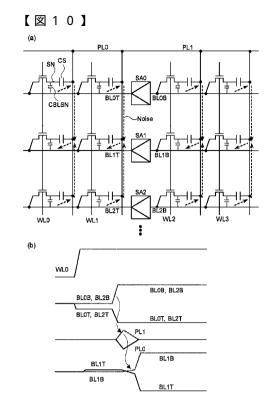

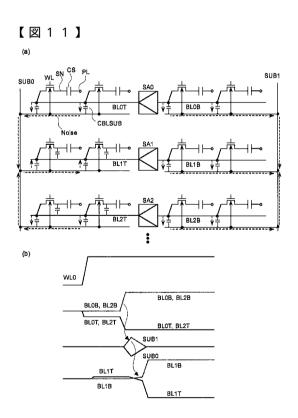

以上では、非選択ワード線に生じるノイズを例にとったが、同様のメカニズムのノイズが、図10に示すようなプレートPLとの寄生容量CBLSN、及び図11に示すような基板SUBとの寄生容量CBLSUBによるカップリングによって生ずる。これらのノイズにより、読み出し時のビット線上の信号量が減少し、メモリアレイの読み出しマージンを劣化させるのである。

# [0030]

このようなノイズ発生のメカニズムは、センスアンプを挟んだ2つのメモリマット内において発生するものであり、前記図1及び図2のような実施例では、バンク2のセンスアンプSA5は活性化されず、それに対応した2つのマットに設けられるビット線は、他のバンク1と3の選択ビット線の信号をセンスするための参照用としてのみ用いられるだけである。したがって、上記バンク1とバンク3との間には、上記のようなノイズ経路が問題にならない。これにより、この発明に係る1交点アレイ従属バンクDRAMでは信号の減少が起こらず、読み出しマージンが拡大され、安定動作が可能になる。なお、図2では示されていないが、バンク1がプリチャージされた後、すぐにバンク3が活性化される場合も同様に、バンク3のビット線BL6Bにはノイズが加わらないため読み出しマージンが拡大される。

# [0031]

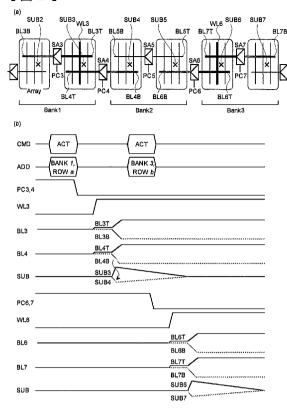

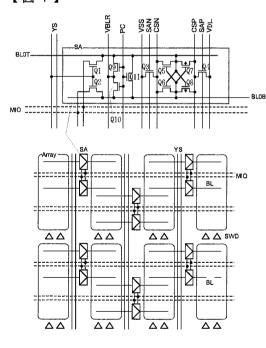

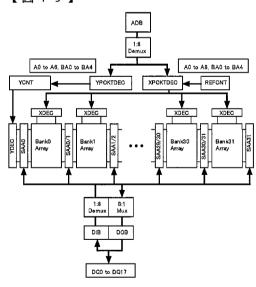

図3には、この発明に係る1交点アレイ従属バンクDRAMにおけるデータの入出力経路の一実施例を説明するためのブロック図が示されている。この実施例では、アレイArrayに設けられる複数のビット線は、2本ずつが2個のセンスアンプSAに設けられ、かかるアレイArrayの左右に交互に振り分けられて設けられる。センスアンプSAは、1つの回路が代表として例示的に示されている。

# [0032]

センスアンプSAは、ゲートとドレインとが交差接続されてラッチ形態にされたNチャンネル型の増幅MOSFETQ5,Q6及びPチャンネル型の増幅MOSFETMOSFETQ7,Q8からなるCMOSラッチ回路で構成される。Nチャンネル型MOSFETQ5とQ6のソースは、共通ソース線CSNに接続される。Pチャンネル型MOSFETQ7とQ8のソースは、共通ソース線CSPに接続される。

#### [0033]

上記共通ソース線CSNとCSPには、それぞれパワースイッチMOSFETQ3とQ4が接続される。特に制限されないが、Nチャンネル型の増幅MOSFETQ5とQ6のソースが接続された共通ソース線CSNには、かかるセンスアンプ領域に分散して配置されたNチャンネル型のパワースイッチMOSFETQ3により接地電位供給線VSSが与えられる。上記Pチャンネル型の増幅MOSFETQ7とQ8のソースが接続された共通ソース線CSPには、Nチャンネル型のパワーMOSFETQ4が設けられて動作電圧VDLが与えられる。

# [0034]

10

20

30

20

30

40

50

上記 N チャンネル型のパワーMOSFETQ3とQ4のゲートには、センスアンプ活性化信号SANとSAPが供給される。特に制限されないが、SAPのハイレベルは昇圧電圧VPPレベルの信号とされる。つまり、昇圧電圧VPPは、上記電源電圧VDLに対してMOSFETQ4のしきい値電圧以上に昇圧されたものであり、上記Nチャンネル型MOSFETQ4を十分にオン状態にして、その共通ソース線CSPの電位を上記動作電圧VDLにすることができる。

#### [0035]

上記センスアンプSAの入出力ノードには、相補ビット線BL0TとBL0Bを短絡させるイコライズMOSFETQ11と、相補ビット線BL0TとBL0Bにハーフプリチャージ電圧VBLRを供給するスイッチMOSFETQ9とQ10からなるプリチャージ(イコライズ)回路が設けられる。これらのMOSFETQ9~Q11のゲートは、共通にプリチャージ(ビット線イコライズ)信号PCが供給される。このプリチャージ信号PCを形成するドライバ回路は、図示しないが、前記図2に示したクロスエリアにインバータ回路を設けて、その立ち上がりや立ち上がりを高速にする。つまり、バンクアクセスの開始時にワード線選択タイミングに先行して、各クロスエリアに分散して設けられたインバータ回路を通して上記プリチャージ回路を構成するMOSFETQ9~Q11を高速に切り替えるようにするものである。

## [0036]

センスアンプSAの一対の入出力ノードは、相補ビット線BL0T,BL0Bに接続されることの他、MOSFETQ1とQ2からなるカラム(Y)スイッチ回路を介してセンスアンプ列に沿って延長されるローカル(サブ)入出力線SIOに接続される。上記MOSFETQ1とQ2のゲートは、カラム選択線YSに接続され、かかるカラム選択線YSが選択レベル(ハイレベル)にされるとオン状態となり、上記センスアンプSAの入出力ノードとローカル入出力線SIOを接続させる。

#### [0037]

これにより、センスアンプSAの入出力ノードは、それを挟んで設けられる2つのアレイのうち、選択されたアレイのワード線との交点に接続されたメモリセルの記憶電荷に対応して変化するビット線のハーフプリチャージ電圧に対する微小な電圧変化を、非選択とされたアレイ側のビット線のハーフプリチャージ電圧を参照電圧として増幅し、上記カラム選択線YSにより選択されたものが、上記カラムスイッチ回路(Q1とQ2)等を通してローカル入出力線SIOに伝えられる。

# [0038]

メインワード線の延長方向に並ぶセンスアンプ列上を上記ローカル入出力線SIOが延長され、サブ増幅回路(Sub A M P)を介して増幅せされた信号がそれと直交する方向、つまりカラム選択線YS方向に延長されるメイン入出力線MIOを通して、列デコーダ部に設けられたメインアンプに伝えられて、アレイの分割数に対応して複数ビット単位でパラレルに出力される。このような入出力線構成は1マットから読み出すデータが4ビット程度で、YSの本数が多いときに適した方式である。上記SIOとMIOの間はサブアンプでなく、単なるスイッチで接続されようにしてもよい。

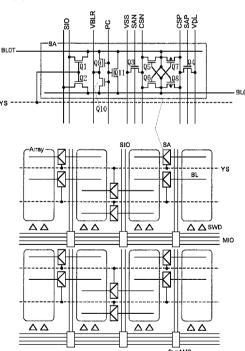

## [0039]

図4には、この発明に係る1交点アレイ従属バンクDRAMにおけるデータの入出力経路の他の一実施例を説明するためのプロック図が示されている。この実施例では、カラム選択線YSをワード線方向に配線し、センスアンプSAのデータをビット線方向に配線されたメイン入出力線MIOに直接読み出している。これはメイン入出力線MIOの本数が多く、例えば128ビット程度の多ビットのデータを一度に上記メイン入出力線MIOへ読み出す場合に適した回路構成である。

## [0040]

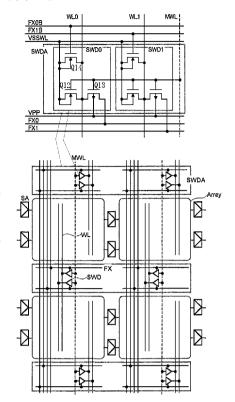

図5には、この発明に係る1交点アレイ従属バンクDRAMにおけるワード線の選択回路の一実施例を説明するためのブロック図が示されている。この実施例では、アレイArrayに設けられる複数のワード線は、2本ずつが2個のサブワードドライバに設けられ、かか

(11)

るアレイArrayの上下に交互に振り分けられて設けられる。サブワードドライバSWDは、上記2個の回路SWD1とSWD2が代表として例示的に示されている。

## [0041]

1つのサブワードドライバSWD0は、Nチャンネル型MOSFETQ12とPチャンネル型MOSFETQ13からなるCMOSインバータ回路と、上記Nチャンネル型MOSFETQ12に並列に設けられたNチャンネル型MOSFETQ14から構成される。上記Nチャンネル型MOSFETQ12とQ14のソースは、サブワード線の非選択レベルVSS(0V)に対応した電源供給線VSSWLに接続される。Pチャンネル型MOSFETQ13が形成されるNウェル領域(基板)に昇圧電圧を供給する電源供給線VPPが設けられる。

[0042]

上記サブワードドライバSWD0のCMOSインバータ回路を構成するMOSFETQ12とQ13のゲートには、残りのサブワードドライバの同様なMOSFETのゲートと共通にメインワード線MWLに接続される。そして、上記CMOSインバータ回路を構成するPチャンネル型MOSFETQ13のソースは、それに対応するサブワード選択線FX0に接続され、上記サブワードドライバSWD1に設けられたMOSFETQ14のゲートには、サブワード選択線FX0Bが供給される。残りのサブワードドライバSWD1には、上記サブワード選択線FX1とFX1Bにそれぞれ接続される。

[0043]

サブワード線WL0が選択されるときは、メインワード線MWLがロウレベルにされる。そして、上記サブワード線WL0に対応したサブワード選択線FX0が昇圧電圧VPPのようなハイレベルにされる。これにより、サブワードドライバSWD0のPチャンネル型MOSFETQ13がオン状態となって、サブワード選択線FX0の選択レベルVPPをサブワード線WL0に伝える。このとき、サブワードドライバSWD0において、サブワード選択線FX0BのロウレベルによりMOSFETQ14はオフ状態になっている。

[0044]

上記メインワード線MWLがロウレベルの選択状態にされた他のサブワードドライバSDW1においては、Pチャンネル型MOSFETがオン状態になるが、サブワード線選択線FX1Bのハイレベルにより、Nチャンネル型MOSFETがオン状態となって、サブワード線WL1を非選択レベルVSSにする。メインワード線MWLがハイレベルにされる非選択のサブワードドライバでは、かかるメインワード線MWLのハイレベルによって、上記CMOSインバータ回路のNチャンネル型MOSFETがオン状態となって、各サブワード線を非選択レベルVSSにするものである。

[0045]

このように3個のMOSFETにより、2つのアレイに対応した一対のサブワード線を選択するので、前記1交点方式のアレイ(マット)に設けられる高密度で配置されるサブワード線WLのピッチに合わせてサブワードドドライバを形成することができ、2交点方式と同一のデザインルールを用いて理想的にはセルサイズを75%低減できる1交点方式に適合させたサブワードドライバの配置が可能になる。

[0046]

上記のように2本のサブワード線WL毎に、アレイの両側に2個ずつの組み合わせでサブワードドライバを分散配置した場合、2つのサブワードドライバを構成するPチャンネル型MOSFETを同一のN型ウェル領域に形成でき、Nチャンネル型MOSFETを同一のP型ウェル領域に形成することができるものとなり、結果としてサブワードドライバの高集積化を可能にするものである。このことは、前記のようなセンスアンプにおいても同様に2本のビット線BL毎にアレイの両側に2個ずつの組み合わせで分散配置するものである。

[0047]

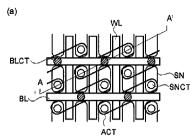

図 6 には、この発明に係る 1 交点アレイ D R A M におけるメモリセルの構造が示されている。図 6 (a)のレイアウトにおける A - A  $^{\prime}$  部分の断面図を図 6 (b)に示している。

10

20

30

40

1 交点アレイではビット線 B L とワード線W L の全ての交点にM O S トランジスタとセル容量からなるメモリセルが接続されている。 A C T はM O S トランジスタの活性領域、 S N はセル容量の下部電極、 S N C T は S N と A C T を接続するコンタクト、 B L C T は B L と A C T を接続するコンタクト、 C P は容量絶縁膜を示す。セル容量の上部電極プレート P L はマット内の全てのメモリセルで共通に接続され、平面状に配置される。 M O S トランジスタの基板 S U B も同様にマット内で共通に接続されている。 プレートの上部には 2 層の金属配線 M 2 、 M 3 が配線される。この例では M 2 をワード線方向に配線してメインワード線( M W L )に用い、 M 3 をビット線方向に配線して列選択線( Y S )に用いている場合を示す。

# [0048]

メモリセルはCOB(Capacitor over Bitline)構造を用いている。すなわち、蓄積ノードSNをビット線BL上部に設ける。このことによって、プレート電極PLはアレイ中でビット線BLと上記アドレス選択MOSFETの接続部BLCTにより分断されることなく、1枚の平面状に形成することができるため、プレート電極PLの抵抗を低減することが可能である。この実施例とは逆にCUB(Capacitor under Bitline)構造を採用した場合には、ビット線BLがプレート電極PLの上に存在することになる。この構成ではアレイ中でプレート電極PLに孔をあけて、ビット線BLとアドレス選択MOSFETのソース,ドレインとを接続するために、かかる接続部BLCTを活性化領域ACTへ落とす必要がある。

# [0049]

プレート電極 P L を P L ( D )と P L ( U )のような積層構造とし、かかるプレート電極 P L のシート抵抗値を下げるようにしてもよい。一例として、記憶キャパシタの容量絶縁膜 C P に B S T や T a 2 O 5 のような高誘電体膜を用いた場合、下部電極(蓄積ノード) S N 及び上部電極下層 P L ( D )には R u を用いると、記憶キャパシタ C S の容量を高めることができる。 R u は従来用いられていたポリ S i に比べるとシート抵抗値が低いため、プレート電極 P L の抵抗値を下げることが出来る。

## [0050]

さらに、この構造にプレート電極PL(U)としてWを積層すると、プレート電極PLの抵抗値をさらに下げることができる。このようにして、プレート電極PL自体の抵抗値を下げると、プレート電極PLにのったノイズが打ち消される速度が高速化され、プレート電極PLノイズが低減される。また、プレート電極PL(D)としてはTiNを用いてもよい。この場合も上記と同様の効果が得られる。

#### [0051]

上記のようなメモリセルの構造では、図6(a)から明らかなようにビット線BLに隣接して蓄積ノードSNとMOSFETのソース,ドレイン拡散層とを接続する接続部SNCTが設けられる。つまり、断面の縦方向においてメモリセルの蓄積ノードとビット線BLとの間において寄生容量が存在するものとなる。この寄生容量は、前記図10の寄生容量CBLSNを構成するので、この発明のようなプレート電極PLをそれ自身を利用した配線によって相互に接続し、上記のように隣接した2つのマットで1つのバンクを構成し、かつあるバンクを活性化した後、そのバンクをプリチャージするまでは隣接バンクの活性化を禁止することが有益なものとなる。

#### [0052]

図7には、この発明に係る1交点アレイ従属バンクDRAMの動作の一例を説明するための波形図が示されている。アドレスADD端子からバンク(Bank)0に対するバンクアドレス、行(ROW) a に対する行アドレスが入力され、活性化コマンドACTが入力される。バンク0ではプリチャージ信号PCが非活性化され、ビット線BLのプリチャージが終了し、ワード線WLaが活性化される。そしてビット線BLT/Bにメモリセルからの微小信号が発生した後、センスアンプ起動信号SAN/Pを駆動してセンスアンプSAでの増幅を開始する。この状態でバンク0のセンスアンプSAにはワード線WLaの情報が保持される。

10

20

30

20

30

40

50

#### [0053]

マルチバンクDRAMではバンク0に情報を保持した状態で、バンク2も活性化できる。 先程と同様にして、アドレスADD端子からバンク(Bank)2に対するバンクアドレス、 行(ROW)bに対する行アドレスが入力され、活性化コマンドACTが入力されと、ワード線、センスアンプが活性化され、Bank2のセンスアンプにはワード線WLbの情報が 保持される。

#### [0054]

この状態から、バンク 0、バンク 2 のセンスアンプS A 中のデータを短時間で読み出すことが可能である。つまりバンク(Bank) 0、列(COL)×に対して読み出しコマンドRE A D が入力されると Y S × が活性化され、バンク 0 のセンスアンプS A からメイン入出力線 M I O T / Bを介して、バンク(Bank) 0、行 a、列×のデータが入出力端子 D Q へ読み出される。同様に、バンク(Bank) 2、列(COL)yに対して読み出しコマンドRE A D が入力されると Y S y が活性化され、バンク 2 のセンスアンプS A からメイン入出力線 M I Oを介して、バンク(Bank) 2、行 b、列 y のデータが入出力端子 D Q へ読み出される。多バンク構成 D R A M では、前記のように複数のバンクをアクティブにして置くことにより、センスアンプを記憶回路(メモリセル)とするようなスタティック型 R A M と同様な高速読み出しが可能になるものである。

## [0055]

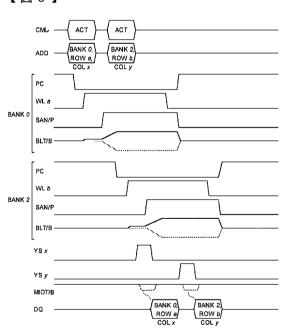

図8には、この発明に係る1交点アレイ従属バンクDRAMの動作の他の一例を説明するための波形図が示されている。前記図7では行アドレスと列アドレスが時間を分けて入力される場合を示したが、これらを同時に入力することもできる。つまり、同図のように最初のACTコマンド入力時にアドレスADD端子からバンク(Bank)0に対するバンクアドレス、行(ROW)aに対する行アドレスと列アドレスCOLxを入力しており、次のACTコマンド入力時にアドレスADD端子からバンク(Bank)2に対するバンクアドレス、行(ROW)bに対する行アドレスと列アドレスCOLyを入力している。上記一つのコマンドでそれぞれ出力データを読み出している。

#### [0056]

この実施例では、上記バンク(Bank) 0のデータがデータ端子DQから出力されるとすぐにバンク 0のビット線をプリチャージしている。このようにしておくと、バンク 0にa以外の行アドレスが続けて入力される場合に、上記プリチャージを終了させて別の行アドレスに対応したワード線の選択ができるからアクセスを早くすることが出来る。先ほどと同様に、マルチバンク構成なのでバンク 0とバンク 2で同時にセンスアンプ中にデータを保持しておくことが出来る。

# [0057]

図12には、本発明に係る1交点アレイ従属バンクDRAMの他の一実施例のメモリアレイ構成図が示されている。この実施例は、前記図1の実施例と異なる点は、1マットを1バンクに割り当てる点のみが異なる。この場合でも、連続するバンクのアクセスにルールを設けることでノイズによる信号減少を抑制することができる。その第一の構成はあるバンクを活性化した場合、そのバンクをプリチャージするまでは隣接およびその外側バンクの活性化を禁止することである。このようにすると、連続して活性化されるバンクの間には少なくとも2個のマット(バンク)が入る。これにより、前記図2で示したのと同様に、連続して活性化される参照ビット線BLが異なるマットに存在することとなるため、後に活性化される参照ビット線BLにノイズが加わらず、読み出しマージンを拡大することができる。

#### [0058]

第二の構成はあるバンクを活性化した後、そのバンクをプリチャージするまでは隣接バンクの活性化を禁止し、なおかつ、あるバンクを活性化またはプリチャージをした後、一定の期間は隣接及びさらに1つ外側のバンクの活性化を禁止するようなスペック化を行うことである。あるマットを活性化した後、それによって隣接マットに生ずる非選択ワード線WL、プレートPL、基板SUBに生ずるノイズが減衰するのを待つてから、さらにその

20

30

40

50

一つ隣のマットの活性化を行うと、ノイズによる信号減少を抑制でき読み出しマージンを 拡大することができる。

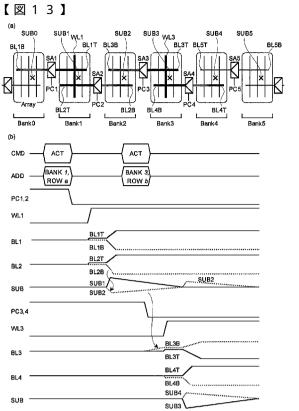

# [0059]

この実施例において、上記のような第一あるいは第二の構成に違反して、バンク(Bank)1を活性化中に、1つのバンク2を挟んで隣接するバンク3を活性化すると次のような問題が生じる。図13には、その動作を説明するための構成図が示されている。図13において、バンク(Bank)1に活性化コマンドACTが入力され、それに対応したワード線WL1を活性化したあと、かかるバンク1の両側に設けられたセンスアンプSA1とSA2を起動する。

# [0060]

ワーストケースとして、バンク(Bank) 1 のビット線 B L 1 , B L 2 T 等は全てハイレベル(H)のデータを読み出したとする。 ビット線 B L 2 T に対応した参照ビット線 B L 2 B をはじめとするバンク(B ank) 2 中の参照ビット線 B L D と D と D と D と D では D と D を D に D と D と D に D と D に D と D に D と D に D と D に D と D に D と D に D と D に D と D に D と D に D と D に D と D に D と D に D と D に D と D に D と D に D と D に D と D に D と D に D と D に D と D に D と D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D に D

# [0061]

すると、バンク3のビット線BL3Tに対応したバンク2の参照ビット線BL3Bはマット2の基板SUB2、ワード線WL、プレートPLからノイズを受け、ハーフプリチャージ電位であるべき電位が上昇する。この状態でバンク3のワード線WL3が活性化され、ビット線BL3Tに高レベルの信号が読み出されても、上記参照ビット線線BL3Bのハーフプリチャージ電位がノイズによって高くなって、相対的に信号量が減少し、誤つて上記ビット線BL対の電位関係が反転してしまう。

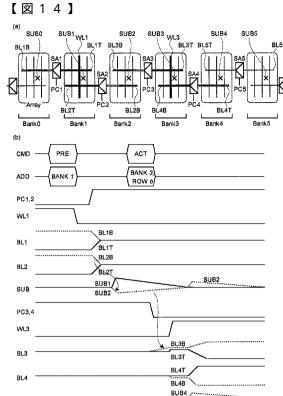

#### [0062]

また、バンク(Bank) 1をプリチャージしたあとに,すぐにバンク(Bank) 3を活性化する場合にも同様の信号量減少が生ずる。この問題を図 1 4を用いて説明する。バンク(Bank) 1 の前サイクルでのビット線全てロウレベル(L)の読み出しだったと仮定すると、バンク(Bank) 2 中の参照ビット線(BL2B等)は全て高レベル電位 V DLに増幅されている。上記バンク(Bank) 1 がプリチヤージコマンド P REによりプリチャージされると、ビット線 P BLのロウレベルが一斉に参照電位 P BLRへ戻るため、バンク(Bank) 2の基板 P SUB P 2 には負のノイズが発生する。

#### [0063]

続いて、バンク(Bank)3を活性化するために、SA3のプリチヤージが切れると、ビット線BL3Tの参照ビット線BL3Bはマット2の基板SUB2、ワード線、プレートPLからノイズを受けて電位が上昇する。この状態でバンク3のワード線WL3が活性化され、ビット線BL3Tに高レベルの信号が読み出されると、相対的に信号量が減少し、誤つてBL対の電位関係が反転してしまう。

# [0064]

また、バンク1がプリチャージされた後は隣接するバンク2の活性化が可能となるが、図14に示すように、あるマットがプリチャージされると、その隣接マットにもノイズが生ずる。したがつて、前記図1のように2マットを1バンクに割り当てた場合でも、バンク1のプリチャージ後、すぐにバンク1やバンク2の活性化を行うと、バンク2の読み出し時に信号が滅少してしまう。そこで、バンク1のプリチャージによりバンク1やバンク2の非選択ワード線WL、プレートPL、基板SUBに生ずるノイズが減衰する一定期間待つてから活性化するようにスペック化を行うと、ノイズによる信号減少を抑制でき、読み出しマージンが拡大される。

# [0065]

つまり、前記図1の2マットで1バンクを構成する場合、及び1マットで1バンクを構成する場合において、前記のように非選択ワード線WL、プレートPL、基板SUBに生ず

るノイズが減衰する一定期間をおいて隣接マットを活性化するような条件を加えるようにすることにより、ノイズによる信号減少を抑制でき、読み出しマージンが拡大することができる。

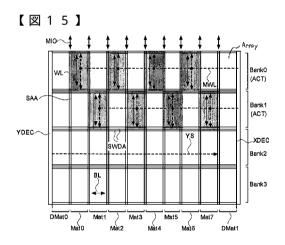

# [0066]

図15には、本発明に係る1交点独立バンクDRAMの一実施例の構成図が示されている。この実施例では、行デコーダ(XDEC)から出力されるメインワード線MWLがビット線BLと同方向に配線され、サブワードドライバ列SWDAに入力する点に特徴がある。列デコーダ(YDEC)から出力されるカラム選択線(YS)はビット線BLと同方向に配線され、センスアンプ列SAAに入力する。

## [0067]

この実施例でも、センスアンプ列SAAとサブワードドライバ列SWDAにより囲まれた 領域をアレイ(Array)と呼ぶことにする。この実施例の1交点独立バンクDRAMでは ビット線BL方向に並んだ横1列のアレイ(Array)で1つのバンクを構成する。バンク の境界にはSWDAを2列配置する。

#### [0068]

1本のメインワード線MWLは少なくとも1個のアレイ間においてサブワードドライバ列SWDAに入力し、すくなくとも間に1個以上のアレイをはさんでセンスアンプSAを活性化する。このようにすると、各バンクはセンスアンプSA、サブワードドライバSWDを独立に持つことが出来るので、ワード線WLの活性化、センスアンプSAの情報保持を完全に独立に行うことが出来る。さらに、参照用のビット線BL専用のダミーマツトDMatは最も外側のマットのみに必要となるので、チップ面積を低減できる。

#### [0069]

図16には、本発明に係る1交点独立バンクDRAMの一実施例のワード線構成図が示されている。前記図5の実施例と異なる点は、アレイ(Array)の境界でサブワードドライバ列SWDAが2列あること、各サブワードドライバSWDは片側のアレイ(Array)のワード線WLのみを駆動すること、メインワード線MWLがビット線BL方向に配線されることである。つまり、アレイ毎にバンクが構成され、アレイ毎にサブワードドライバSWDが設けられることにより、隣接するアレイ(バンク)を独立にアクセスすることができる。言い換えるならば、互いに隣接するバンク0のワード線とバンク1のワード線を同時に選択することも可能となるため、独立バンクDRAMとすることができる。

## [0070]

この実施例ではメインワード線MWLはアレイ(Array)1個おきにサブワードドライバSWDに入力しているが、2個以上間をおいても構わない。このようにすると活性化されるアレイの距離が離れるために、ビット線BLを増幅する際のアレイノイズを低減できるため、読み出しマージンが向上する利点がある。入出力線(LIO-MIO)の構成については図3または図4の実施例と同様にすることができる。

# [0071]

この実施例では、ビット線が1交点により構成する例が示されているが、2交点により構成されるものであってもよい。2交点方式では、センスアンプSAが同じアレイに設けられた相補ビット線の電圧差を増幅するものであるので、例えば図21に示したようにセンスアンプSAをバンクの境界で2組設けることによって独立バンクにすることが考えられる。しかしながら、上記センスアンプSAは、前記図3に示したように多くの回路素子を必要とし、そのために比較的大きな占有面積及び消費電流を必要とする。これに対して、サブワードドライバSWDは、前記図5に示したように3個のような少ない素子数により構成でき、しか消費電流が小さいから、上記2交点方式のアレイにおいても、独立バンク構成をほうる場合には、この実施例のようなバンク構成を採用することにより、高集積化と低消費電力化が可能になるものである。

# [0072]

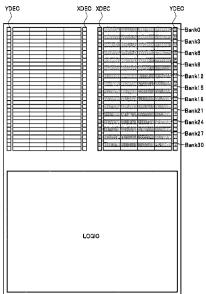

図17には、この発明が適用された論理混載DRAMのチップ構成図が示されている。この実施例の半導体集積回路装置は、論理回路部LOGICと、メモリ部DRAMから構成

10

20

30

40

20

30

40

50

される。 DRAM部は、大きく2組のメモリ部からなり、それぞれのメモリ部は、バンク0~31の32バンクからなるような多バンク構成とされる。同図の右側のメモリ部には、独立にアクセス可能なバンクをハッチングを付した偶数バンクと、白抜きの奇数バンクとに分けて表している。各バンクは、例えば前記図1のように2つのアレイにより1つのバンクが構成される。

# [0073]

上記バンク数が32とされた1つのメモリ部は、各バンクに対応して行デコーダXDECと列デコーダYDECをそれぞれ独立に持つ、また、バンクの境界部でセンスアンプは両方のバンクに対応したアレイのビット線に共用されるために、前記1交点アレイ従属バンクDRAMとされる。そして、あるバンクを活性化した後、そのバンクをプリチャージするまでは隣接バンクの活性化を禁止するようにされることよって、動作マージンを確保するものである。

# [0074]

図18には、この発明に係る従属バンクDRAMのチップ全体構成図が示されている。バンク数は32バンクであり、これら32バンクのメモリ部が全体で4組設けられる。各バンクは行デコーダXDECを独立に持つが、列デコーダYDEC、アドレスバッファ(ADB)、入出力バッファ(DIB,DOB)は共有化される。他の構成は、前記図17と同様であるので、その説明を省略する。

# [0075]

# [0076]

YCNTは、Yカウンタであり、列パケットデコーダYPCKTDECから入力された初期アドレスを基にクロックによりYアドレスを歩進させる。これにより、バーストモードでのメモリアクセスが可能にされる。REFCNTは、自動リフレッシュ回路であり、リフレッシュアドレスを生成して上記行パケットデコーダXPCKTDECを介して、各バンクのワード線を順次に選択してメモリセルのリフレッシュ動作を行なわせる。

# [0077]

この発明に係る多バンク構成 DRAMは、前記のような非選択ワード線、プレートあるいは基板を介したノイズ対策に止まらず、DRAMの特徴である高集積化にも充分な配慮が成されているものである。例えば、図20に示すように1交点アレイを用い、独立バンク構成とした場合には、3つのアレイを用いて1つのバンクを構成することができる。

# [0078]

つまり、1交点アレイでは隣接マット中のビット線を参照ビット線に用いる必要があるため、正規マツトのとなりに参照マツトが必要となる。各バンクの動作を完全に独立化するためには、参照マットも独立化する必要があるため、正規マット(Mat0)のとなりの参照マット(DLMat0、DRMat0)を含めた最低3マットで1バンクを構成する必要がある。一方、参照マット中のビット線のうち半分はVBLRへ固定され、センスアンプに接続されないダミービット線となるので、参照マットは半分の面積が無駄になる。したがって、32バンクのようにバンク数が増えるとダミーマットが増えて、無駄な面積が大幅に増加して、DRAMを用いることの意味がなくなってしまう。

#### [0079]

これに対して、本願発明では1交点アレイでは前記のような従属バンクDRAMとし、そのバンクの選択動作を一部制限するという簡単な構成によって、高集積化と動作マージン

20

30

40

50

の確保を行なうようにすることができるものである。本願において、バンクという概念は、シンクロナスDRAM等において広く用いられるものであり、それと同様な意味で用いている。

# [0800]

DRAMにおいては、記憶キャパシタに電荷が有るか無いかで2値情報の1と0に対応させている。したがって、ワード線を選択すると、ビット線のプリチャージ電荷との電荷結合によって元の蓄積電荷の状態が失われてしまうので、センスアンプによって上記ビット線の読み出し信号を増幅してもとの電荷の状態に戻すというリフレッシュ又はリライト動作を必須とするものである。したがって、DRAMにおいては、ワード線の選択動作が常にセンスアンプの動作と密接に関連するものである。このことから、ワード線の選択タイミングあるいはワード線の選択アドレスを独立に設定できるということは、前記バンクという概念を用いなくともDRAMの動作上は実質的には同じ意義を有するものとなる。

## [0081]

以上説明した本願において、用語「MOS」は、本来はメタル・オキサイド・セミコンダクタ構成を簡略的に呼称するようになったものと理解される。しかし、近年の一般的呼称でのMOSは、半導体装置の本質部分のうちのメタルをポリシリコンのような金属でない電気導電体に換えたり、オキサイドを他の絶縁体に換えたりするものもの含んでいる。CMOSもまた、上のようなMOSに付いての捉え方の変化に応じた広い技術的意味合いを持つと理解されるようになってきている。MOSFETもまた同様に狭い意味で理解されているのではなく、実質上は絶縁ゲート電界効果トランジスタとして捉えられるような広義の構成をも含めての意味となってきている。本発明のCMOS、MOSFET等は一般的呼称に習っている。

## [0082]

上記の実施例から得られる作用効果は、下記の通りである。

(1) 第1方向に沿って配置された複数のメモリアレイ領域と交互に配置された複数のセンスアンプ領域を設け、上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のビット線と、上記第1方向と直交する第2方向に沿って設けられた複数のワード線と、上記複数のビット線と上記複数のワード線との交差部に対応して設けられた複数のメモリセルを設け、各センスアンプ領域に隣接する両側のメモリアレイ領域のうちの一方に延びるビット線と他方に延びるビット線とから一対の信号を受けるセンスアンプを設け、メモリアレイ領域を2つ以上間に挟んで離れた2つのメモリアレイ領域に対するそれぞれのワード線選択タイミングを独立に制御することにより、高集積化と動作の安定化を実現した半導体記憶装置を実現できるとうい効果が得られる。

# [0083]

(2) 上記に加えて、上記メモリアレイ領域を1つ間に挾んで離れた2つのメモリアレイ領域に対するそれぞれのワード線選択タイミングを一定期間ずれて制御することにより、ワード線の選択タイミングに対応して発生するノイズの影響を無くすことができるから動作の安定化と使い勝手を良くした半導体記憶装置を実現できるとうい効果が得られる。

# [0084]

(3) 上記に加えて、メモリセルをMOSFETとキャパシタとからなり、上記MOSFETのゲートが選択端子とされ、一方のソース,ドレインが入出力端子とされ、他方のソース,ドレインが上記キャパシタの一方の電極である蓄積ノードと接続されてなるダイナミック型メモリセルとし、かかるメモリアレイに設けられるキャパシタの他方の電極を一体化されたプレート電極により構成することにより、高集積化を実現できるという効果が得られる。

# [0085]

(4) 第1方向に沿って配置された複数のメモリアレイ領域と交互に配置された複数のセンスアンプ領域を設け、上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のビット線と、上記第1方向と直交する第2方向に沿って設けられた複数のワード線と、上記複数のビット線と上記複数のワード線との交差部に対応して設け

20

30

40

50

られた複数のメモリセルを設け、各センスアンプ領域に隣接する両側のメモリアレイ領域のうちの一方に延びるビット線と他方に延びるビット線とから一対の信号を受けるセンスアンプを設け、メモリアレイ領域を2つ以上間に挾んで離れた2つのメモリアレイ領域に対するそれぞれのワード線選択アドレスを独立に制御することにより、高集積化と動作の安定化を実現した半導体記憶装置を実現できるとうい効果が得られる。

## [0086]

(5) 上記に加えて、メモリセルをMOSFETとキャパシタとからなり、上記MOSFETのゲートが選択端子とされ、一方のソース,ドレインが入出力端子とされ、他方のソース,ドレインが上記キャパシタの一方の電極である蓄積ノードと接続されてなるダイナミック型メモリセルとし、かかるメモリアレイに設けられるキャパシタの他方の電極を一体化されたプレート電極により構成することにより、高集積化を実現できるという効果が得られる。

#### [0087]

(6) 第1方向に沿って配置された複数のメモリアレイ領域と交互に配置された複数のセンスアンプ領域を設け、上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のビット線と、上記第1方向と直交する第2方向に沿って設けられた複数のワード線と、上記複数のワード線との交差部に対応して設けられた複数のメモリセルを設け、各センスアンプ領域に隣接する両側のメモリアレイ領域のうちの一方に延びるビット線と他方に延びるビット線とから一対の信号を受けるセンスアンプを設け、隣接して設けられた2つのメモリアレイ領域により1つのバンクを構成し、かかるバンクの複数個のうち1のバンクを挾んで離れた2つのバンクに対するそれぞれのワード線選択タイミングを独立に制御することにより、高集積化と動作の安定化を実現したマルチバンク構成の半導体記憶装置を実現できるとうい効果が得られる。

#### [0088]

(7) 上記に加えて、上記複数のバンクのうち互いに隣接する2つのバンクに対するそれぞれのワード線選択タイミングを一定期間ずれて制御することにより、ワード線の選択タイミングに対応して発生するノイズの影響を無くすことができるから動作の安定化と使い勝手を良くしたマルチバンク構成の半導体記憶装置を実現できるとうい効果が得られる

# [0089]

(8) 上記に加えて、メモリセルをMOSFETとキャパシタとからなり、上20OSFETのゲートが選択端子とされ、一方のソース,ドレインが入出力端子とされ、他方のソース,ドレインが上記キャパシタの一方の電極である蓄積ノードと接続されてなるダイナミック型メモリセルとし、かかるメモリアレイに設けられるキャパシタの他方の電極を一体化されたプレート電極により構成することにより、高集積化を実現できるという効果が得られる。

# [0090]

(9) 第1方向に沿って配置された複数のメモリアレイ領域と交互に配置された複数のセンスアンプ領域を設け、上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のビット線と、上記第1方向と直交する第2方向に沿って設けられた複数のワード線と、上記複数のビット線と上記複数のワード線との交差部に対応して設けられた複数のメモリセルを設け、各センスアンプ領域に隣接する両側のメモリアレイ領域のうちの一方に延びるビット線と他方に延びるビット線とから一対の信号を受けるセンスアンプが上記各センスアンプ領域内に設け、隣接して設けられた2つのメモリアレイ領域により1つのバンクを構成し、かかるバンクの複数個のうち1のバンクを挟んで離れた2つのバンクに対するそれぞれのワード線選択アドレスを独立に設定することにより、高集積化と動作の安定化を実現したマルチバンク構成の半導体記憶装置を実現できるとうい効果が得られる。

# [0091]

(10) 上記に加えて、メモリセルをMOSFETとキャパシタとからなり、上記MO

SFETのゲートが選択端子とされ、一方のソース,ドレインが入出力端子とされ、他方のソース,ドレインが上記キャパシタの一方の電極である蓄積ノードと接続されてなるダイナミック型メモリセルとし、かかるメモリアレイに設けられるキャパシタの他方の電極を一体化されたプレート電極により構成することにより、高集積化を実現できるという効果が得られる。

# [0092]

(11) 第1方向に沿って配置された複数のメモリアレイ領域と交互に配置された複数のセンスアンプ領域を設け、上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のビット線と、上記第1方向と直交する第2方向に沿って設けられた複数のワード線と、上記複数のビット線と上記複数のワード線との交差部に対応して設けられた複数のメモリセルを設け、各センスアンプ領域に隣接する両側のメモリアレイ領域のうちの一方に延びるビット線と他方に延びるビット線とから一対の信号を受けるセンスアンプを設け、上記1つのメモリアレイ領域により1つのバンクを構成し、かかるバンクの複数個のうち2のバンクを挟んで離れた2つのバンクに対するそれぞれのワード線選択アドレスを独立に設定することにより、高集積化と動作の安定化を実現したマルチバンク構成の半導体記憶装置を実現できるとうい効果が得られる。

## [0093]

(12) 上記に加えて、1つのバンクを挟んで離れた2つのバンクをセンスアンプによる微小信号増幅期間にはバンクの活性化を禁止することにより、動作の安定化を図りつつ、使い勝手を良くすることができるという効果が得られる。

#### [0094]

(13) 上記に加えて、1つのバンクを挟んで離された2つのバンクは、一方のバンクが活性化された時には、他方のバンクは所定時間遅れて活性化を許可することにより、動作の安定化を図りつつ、使い勝手を良くすることができるという効果が得られる。

#### [0095]

(14) 上記に加えて、メモリセルをMOSFETとキャパシタとからなり、上記MOSFETのゲートが選択端子とされ、一方のソース,ドレインが入出力端子とされ、他方のソース,ドレインが上記キャパシタの一方の電極である蓄積ノードと接続されてなるダイナミック型メモリセルとし、かかるメモリアレイに設けられるキャパシタの他方の電極を一体化されたプレート電極により構成することにより、高集積化を実現できるという効果が得られる。

# [0096]

(15) 第1方向に沿って配置された複数のメモリアレイ領域とと交互に配置された複数のワード選択領域を設け、上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のワード線と、上記第1方向と直交する第2方向に沿って設けられた複数のビット線と、上記複数のワード線と上記複数のビット線との交差部に対応して設けられた複数のメモリセルを設け、各ワード線選択領域に隣接する両側のメモリアレイ領域のうちの一方に延びるワード線及び他方に延びるワード線のそれぞれに対応してワード線選択回路を上記各ワード線選択領域内に設け、各メモリアレイ領域に対するそれぞれのワード線選択タイミングを独立に制御することにより、高集積化と動作の安定化を実現した半導体記憶装置を実現できるとうい効果が得られる。

#### [0097]

(16) 上記に加えて、上記ワード線選択回路は、上記メモリアレイに設けられるサブワード線を選択するものとし、上記ワード線選択回路に選択信号を伝えるメインワード線を上記第2方向に延長させることにより、メモリアレイ領域に対するそれぞれのワード線選択タイミングを独立に制御することができるという効果が得られる。

#### [0098]

(17) 上記に加えて、上記メモリアレイに設けられるビット線を、相補のビット線対が平行に延長されるものとすることにより、高集積化を図ることができるという効果が得られる。

10

20

30

20

30

40

50

## [0099]

(18) 上記に加えて、上記第2方向にも複数のメモリアレイを設け、かかる複数のメモリアレイ領域と交互に配置された複数のセンスアンプ領域を更に設け、各センスアンプ領域に隣接する両側のメモリアレイ領域のうちの一方に延びるビット線と他方に延びるビット線とから一対の信号を受けるセンスアンプが上記センスアンプ領域内に設けられるようにすることにより、高集積化を図ることができるという効果が得られる。

#### [0100]

(19) 上記に加えて、メモリセルをMOSFETとキャパシタとからなり、上記MOSFETのゲートが選択端子とされ、一方のソース,ドレインが入出力端子とされ、他方のソース,ドレインが上記キャパシタの一方の電極である蓄積ノードと接続されてなるダイナミック型メモリセルとし、かかるメモリアレイに設けられるキャパシタの他方の電極を一体化されたプレート電極により構成することにより、高集積化を実現できるという効果が得られる。

# [0101]

複数の第1ビット線と、複数の第1ワード線と、上記複数の第1ビット線と上 記複数の第1ワード線に結合された複数の第1メモリセルを含む第1メモリマットと、複 数の第2ビット線と、複数の第2ワード線と、上記複数の第2ビット線と上記複数の第2 ワード線との交点に結合された複数の第2メモリセルを含む第2メモリマットと、上記第 1 メモリマットと上記第 2 メモリマットとの問の領域に複数センスアンプを設け、上記複 数のセンスアンプの各々は、上記複数の第1ビット線のうちの対応する1つと上記複数の 第2ビット線のうちの対応する1つに結合し、上記複数の第1メモリセルの各々は、第1 及び第2電極を有する第1容量と、上記複数の第1ワード線のうちの対応する1つに結合 されたゲートと、その一方が上記複数の第1ビット線のうちの対応する1つに結合されそ の他方が上記第1容量の上記第1電極に緯合されたソース・ドレイン経路とを有する第1 トランジスタで構成し、上記複数の第2メモリセルの各々は、第3及び第4電極を有する 第2容量と、上記複数の第2ワード線のうちの対応する1つに結合されたゲートと、その 方が上記複数の第2ビット線のうちの対応する1つに結合されその他方が上記第2容量 の上記第4電極に綜合されたソース・ドレイン径路とを有する第2トランジスタで構成し 上記複数の第1メモリセルの上記第1容量の上記第2電極の各々及び上記複数の第2メ モリセルの上記第2容量の上記第4電極の各々は、上記第1メモリマット、上記第2メモ リマット及び上記複数のセンスアンプの上に配置された1つの導電層に結合し、上記メモ リマットを2つ以上間に挾んで離れた2つのメモリマットに対するそれぞれのワード線選 択アドレスを独立に設定することにより、高集積化と動作の安定化を実現した半導体記憶 装置を実現できるとうい効果が得られる。

# [0102]

モリセルの上記第2容量の上記第4電極の各々は、上記第1メモリマット、上記第2メモリマット及び上記複数のセンスアンプの上に配置された1つの導電層に結合し、隣接して設けられた2つのマットにより1つのバンクを構成し、かかるバンクの複数個のうち1のバンクを挟んで離れた2つのバンクに対するそれぞれのワード線選択アドレスを独立に設定することにより、高集積化と動作の安定化を実現したマルチバンク構成の半導体記憶装置を実現できるとうい効果が得られる。

#### [0103]

以上本発明者よりなされた発明を実施例に基づき具体的に説明したが、本願発明は前記実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。例えば、メモリセルは、前記のようなダイナミック型メモリセルの他に、記憶手段として強誘電体キャパシタを用いて不揮発化するものであってもよい。強誘電体キャパシタは、その誘電体膜に加える電圧の大きさによって、不揮発性モードと前記ダイナミック型メモリセルと同様な揮発性モードの両方に用いるようにするものであってもよい。ダイナミック型RAMの入出力インターフェイスは、ランバス構成あるいはシンクロナスDRAM等に適合可能にするもの、あるいは前記論理回路に搭載されるもの等種々の実施形態を採ることができる。

## [0104]

#### 【発明の効果】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。第1方向に沿って配置された複数のメモリアレイ領域と交互に配置された複数のセンスアンプ領域を設け、上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のビット線と、上記第1方向と直交する第2方向に沿って設けられた複数のワード線と、上記複数のビット線と上記複数のワード線との交差部に対応して設けられた複数のメモリセルを設け、各センスアンプ領域に隣接する両側のメモリアレイ領域のうちの一方に延びるビット線と他方に延びるビット線とから一対の信号を受けるセンスアンプを設け、メモリアレイ領域を2つ以上間に挟んで離れた2つのメモリアレイ領域に対するそれぞれのワード線選択タイミング又はアドレスを独立に設定することにより、高集積化と動作の安定化を実現した半導体記憶装置を実現することができる

# [0105]

第1方向に沿って配置された複数のメモリアレイ領域と交互に配置された複数のセンスアンプ領域を設け、上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のビット線と、上記第1方向と直交する第2方向に沿って設けられた複数のワード線と、上記複数のビット線と上記複数のワード線との交差部に対応して設けられた複数のメモリセルを設け、各センスアンプ領域に隣接する両側のメモリアレイ領域のうちの一方に延びるビット線と他方に延びるビット線とから一対の信号を受けるセンスアンプを設け、隣接して設けられた2つのメモリアレイ領域により1つのバンクを構成し、かかるバンクの複数個のうち1のバンクを挟んで離れた2つのバンクに対するそれぞれのワード線選択アドレスを独立に設定することにより高集積化と動作の安定化を実現したマルチバンク構成の半導体記憶装置を実現できる。

# 【図面の簡単な説明】

【図1】この発明に係るDRAMの一実施例を示す概略構成図である。

【図2】この発明に係るDRAMの動作の一例の説明図である。

【図3】この発明に係る1交点アレイ従属バンクDRAMにおけるデータの入出力経路の一実施例を説明するためのブロック図である。

【図4】この発明に係る1交点アレイ従属バンクDRAMにおけるデータの入出力経路の他の一実施例を説明するためのブロック図である。

【図 5 】この発明に係る 1 交点アレイ従属バンク D R A M におけるワード線の選択回路の一実施例を説明するためのブロック図である。

【図6】この発明に係る1交点アレイDRAMにおけるメモリセルの構造の説明図である

10

20

30

40

- 【図7】この発明に係る1交点アレイ従属バンクDRAMの動作の一例を説明するための 波形図である。

- 【図8】この発明に係る1交点アレイ従属バンクDRAMの動作の他の一例を説明するための波形図である。

- 【図9】1交点アレイでの非選択ワード線ノイズの発生原理の説明図である。

- 【図10】1交点アレイでのプレートノイズの発生原理の説明図である。

- 【図11】1交点アレイでの基板ノイズの発生原理の説明図である。

- 【図12】本発明に係る1交点アレイ従属バンクDRAMの他の一実施例を示すメモリアレイ構成図である。

- 【図13】1交点アレイ従属バンクDRAMでのバンク選択動作の悪い例を説明するための構成図である。

- 【図14】1交点アレイ従属バンクDRAMでのバンク選択動作の悪い他の例を説明するための構成図である。

- 【図15】本発明に係る1交点独立バンクDRAMの一実施例を示す構成図である。

- 【図16】本発明に係る1交点独立バンクDRAMの一実施例を示すワード線構成図である。

- 【図17】この発明が適用された論理混載DRAMのチップ構成図である。

- 【図18】この発明に係る従属バンクDRAMのチップ全体構成図である。

- 【図19】この発明に係る従属バンクDRAMの一実施例のブロック図である。

- 【図20】この発明に先立って検討された1交点独立バンクDRAMの構成図である。

- 【図21】この発明に先立って検討された2交点独立バンクDRAMの構成図である。

# 【符号の説明】

バンク… B ank 、 X D E C … 行デコーダ、 Y D E C … 列デコーダ、 S A A … センスアンプ列 (領域)、 S W D A … サブワードドライバ列 (領域)、 A rray … アレイ、 Mat … マット、 S A … センスアンプ、 S W D … サブワードドライバ、 P L … プレート電極、 M W L … メインワード線、 W L … サブワード線、 B L … ビット線、 A C T … 活性領域、 S N … 蓄積 ノード、 C P … 容量絶縁膜、 B L C T … コンタクト部、 S N C T … コンタクト部、 M 1 ~ M 3 … 金属配線層、 S U B … 基板 (ウェル領域)、

Q1~Q13...MOSFET、

ABD…アドレスバッファ、DIB…データ入力回路、DOB…データ出力回路、XPCKTDEC…Xパケットデコーダ、YPCKTDEC…Yパケットデコーダ、YCND…Yカウンタ、REFCNT…リフレッシュ制御回路。Demux…デマルチプレクサ、Mux…マルチプレクサ。

20

10

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

# (a) WLO CS PL BLOT BLOT BLOB BLOB BLIT BLIB WLO SAO BLOB, BL2B BLOB, BL2B BLOB, BL2B

BLOT, BL2T

BL1T

WL2

BL1T

BL1B

SUB

【図17】

【図18】

【図19】

【図20】

# 【図21】

# フロントページの続き

(72)発明者 梶谷 一彦 東京都青梅市新町六丁目 1 6 番地の 3 株式会社 日立製作所 デバイス開発センタ内

審査官 堀江 義隆

(56)参考文献 特開平11-317072(JP,A) 特開平06-037279(JP,A) 特開平4-6692(JP,A)

(58)調査した分野(Int.CI., DB名) G11C 11/40-11/4099