## (10) **DE 10 2019 116 700 B4** 2021.03.04

(12)

## **Patentschrift**

(21) Aktenzeichen: 10 2019 116 700.0

(22) Anmeldetag: 19.06.2019(43) Offenlegungstag: 16.01.2020

(45) Veröffentlichungstag

der Patenterteilung: 04.03.2021

(51) Int Cl.: **G05F 1/563** (2006.01)

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(66) Innere Priorität:

(73) Patentinhaber:

10 2018 116 668.0 10.07.2018

Elmos Semiconductor SE, 44227 Dortmund, DE

(72) Erfinder:

Kapoor, Niron, 45357 Essen, DE

(56) Ermittelter Stand der Technik:

siehe Folgeseiten

# (54) Bezeichnung: Stützkondensatorfreier Low-Drop-Spannungsregler mit großem Spannungsbereich mit einem DIMOS Transistor und Verfahren zu dessen Betrieb

- (57) Hauptanspruch: Low-Drop-Spannungsregler zur Erzeugung einer Ausgangsspannung an seinem Ausgang  $(V_{\text{OUTa}})$

- mit einem selbstleitenden NMOS-Transistor (M<sub>1a</sub>) und

- mit einem nicht selbstleitenden DIMOS-Transistor ( $\mathrm{M}_{\mathrm{2a}}$ ) und

- wobei der selbstleitende NMOS-Transistor ( $\rm M_{1a}$ ) als ein erster Regeltransistor des Low- Drop-Spannungsreglers verwendet wird und

- wobei der nicht selbstleitende DIMOS-Transistor ( $\rm M_{2a}$ ) als ein zweiter Regeltransistor des Low- Drop-Spannungsreglers verwendet wird und

- wobei die Regelung der Ausgangsspannung ( $V_{OUTa}$ ) über den selbstleitenden NMOS-Transistor ( $M_{1a}$ ) mit einer ersten Zeitkonstante ( $\tau_{1a}$ ) erfolgt und

- wobei die Regelung der Ausgangsspannung ( $V_{OUTa}$ ) über den nicht selbstleitenden DIMOS-Transistor ( $M_{2a}$ ) mit einer zweiten Zeitkonstante ( $\tau_{2a}$ ) erfolgt und

- wobei die Regelung über den nicht selbstleitenden DIMOS-Transistor ( $\rm M_{2a}$ ) das Einspeisen eines zweiten Stroms ( $\rm I_{2a}$ ) in den Knoten des Ausgangs des Spannungsreglers ( $\rm HV\_LDO_a$ ) mit Hilfe dieses selbstleitenden DIMOS-Transistors ( $\rm M_{2a}$ ) umfasst, wobei der Wert des zweiten Stromes ( $\rm I_{2a}$ ) von einem Bias-Strom ( $\rm I_{Ba}$ ) abhängt, und

- wobei die Regelung über den nicht selbstleitenden DI-MOS-Transistor ( $M_{2a}$ ) das Einspeisen eines vierten Stroms ( $I_{4a}$ ) in den Knoten des Ausgangs des Spannungsreglers ( $HV_LDO_a$ ) umfasst, wobei der Wert des vierten Stromes ( $I_{4a}$ ) ebenfalls von dem Bias-Strom ( $I_{Ba}$ ) abhängt, und

- wobei die Regelung über den nicht selbstleitenden DI-MOS-Transistor ( $\rm M_{2a}$ ) das Entnehmen eines achten Stromes ( $\rm I_{8a}$ ) ...

# (10) **DE 10 2019 116 700 B4** 2021.03.04

#### (56) Ermittelter Stand der Technik:

| DE | 101 10 273       | C2         |

|----|------------------|------------|

| DE | 35 38 584        | <b>A1</b>  |

| DE | 603 11 098       | T2         |

| US | 2014 / 0 028 274 | <b>A1</b>  |

| US | 4 683 382        | Α          |

| WO | 2017/ 102 251    | <b>A</b> 1 |

PLUMMER, J.D.; MEINDL, J.D.: A monolithic 200-V CMOS analog switch. In: IEEE Journal of Solid-State Circuits - Dec. 1976, Bd. 11, H. 6, S. 809 - 817. - ISSN 0018-9200 (P), 1558-173X (E). DOI: 10.1109/JSSC.1976.1050822. URL: https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=1050822 [abgerufen am 2019-09-06].

TIHANYI, J.; WIDMANN, D.: DIMOS - A novel IC technology with submicron effective channel MOSFET. In: International Electron Devices Meeting - 5-7 Dec. 1977 - Washington, DC, USA, S. 399-401. DOI: 10.1109/IEDM.1977.189270. URL: https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=1479350 [abgerufen am 2019-09-05].

#### **Beschreibung**

### Oberbegriff

**[0001]** Die Erfindung richtet sich auf einen mikrointegrierbaren Low-Drop-Spannungsregler mit voller Ausnutzung des Versorgungsspannungsbereiches und schneller Ausregelung von dynamischen Lastsprüngen des Laststromes (IL<sub>a</sub>), sodass er keine Stützkapazität extern seiner mikrointegrierten Schaltung benötigt.

Allgemeine Einleitung und Stand der Technik

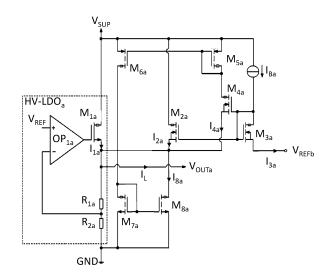

[0002] Mit den wachsenden Anforderungen hinsichtlich eines immer größeren, notwendigen Betriebsspannungsbereichs für die elektronischen Schaltungen -vor allem im Automobilbereich- wird der Einsatz von in der integrierten Schaltung (IC) eingebauten sogenannten Hochvolt-Low-Drop-Reglern -in weiterem HV-LDO genannt- im Gegensatz zu kostenintensiven DC-DC-Konvertern bzw. Schaltregler stetig beliebter und notwendiger. Die integrierte Schaltung (IC) ist dabei in ein Gehäuse mit Gehäuseanschlüssen eingebaut. Diese Spannungsreglertypen müssen bei maximaler Versorgung sowohl einen größeren Spannungsabfall über ihren jeweiligen Ausgangstreibertransistor standhalten können, als auch bei minimaler Versorgungsspannung, die nahe der Regler-Ausgangsspannung selbst liegen kann, die nominale Ausgangsspannung  $V_{\text{OUTa}}$  am ersten Ausgang des ersten Hochvolt-Low-Drop-Reglers (HV-LDO<sub>a</sub>) bereitstellen können. Der Ausgangstreibertransistor (MDRV) ist typischerweise ein MOS-Transistor mit Drain-, Source- und Gate-Anschluss. Um die Bereitstellung der nominalen Ausgangsspannung V<sub>OUTa</sub> erreichen zu können, benötigt der Ausgangstreibertransistor ( $\mathbf{M}_{\mathbf{DRV}}$ ) dieses Hochvolt-Low-Drop-Reglers (HV-LDO<sub>a</sub>) eine ausreichende Gate-Source-Spannung, weshalb die Hochvolt-Low-Drop-Regler (HV-LDO<sub>a</sub>) nach Stand der Technik bevorzugt mit einem p-leitenden Transistor als Ausgangstreibertransistor (M<sub>DRV</sub>) (siehe Fig. 1) konstruiert werden, dessen Gate-Potenzial auf Werte bis zur negativen Versorgungspannung des Bezugspotenzials (GND) angesteuert werden kann. Damit kann die absolute Gate-Source-Spannung  $V_{GS}$  des Ausgangstreibertransistors ( $M_{DRV}$ ), der typischerweise im Stand der Technik ein PMOS-Transistor ist, nahezu den gesamten verfügbaren Spannungsbereich von positiver Versorgungsspannung (V<sub>SUP</sub>) bis zur negativen Versorgungsspannung des Bezugspotenzials (GND) ausnutzen und somit mit einem kleinen R<sub>DSON MDRV</sub>, einen minimalen Spannungsabfall über den Ausgangstreibertransistor gewährleisten. Diese Art der Hochvolt-Low-Drop-Regler (HV-LDO<sub>a</sub>) müssen aber unter anderem aus Stabilitätsgründen entweder mit sehr großem Schaltungsaufwand intern phasenkompensiert werden oder/und benötigen in der Regel einen zusätzlichen Gehäuse-Anschluss eine große, typischerweise nicht integrierbare externe Kapazität ( $\mathbf{C}_{\text{buffer}}$ ) an ihrem Ausgang ( $V_{\text{OUT}}$ ).

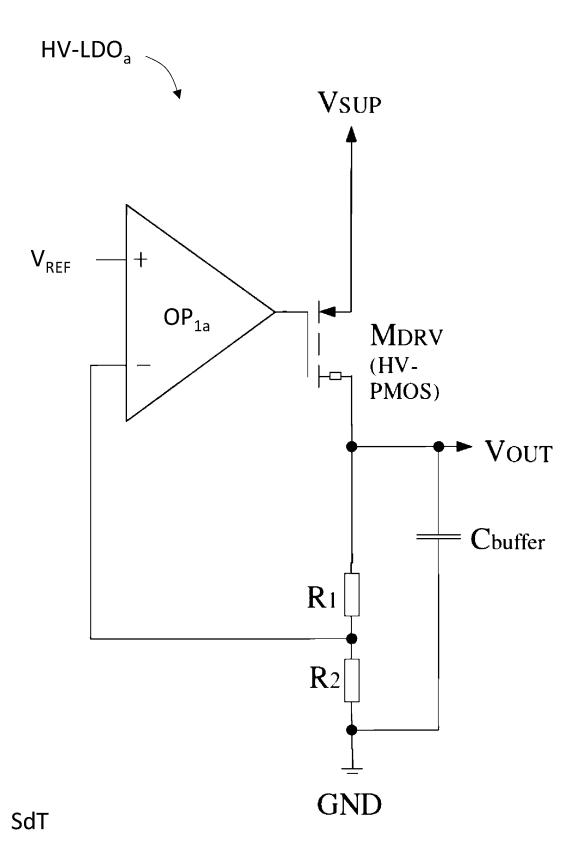

[0003] Bevorzugt wird daher die Möglichkeit, einen selbstleitenden Hoch-Volt-NMOS-Transistor (HV-NMOS) als Treiber ( $M_{1a}$ ) zu verwenden (siehe **Fig. 2**). Ganz besonders handelt es sich dabei um einen NMOS-Transistor mit einem nur schwach oder nicht dotierten Kanal. Ein solcher erster Transistor (M<sub>1a</sub>) wird im Folgenden als "natural NMOS-Transistor" bezeichnet. Wegen einer unzureichenden, wirksamen Gate-Source-Spannung  $V_{GSeff}$  und damit einem zu großen Einschaltwiderstand  $R_{DSON1a}$  des Ausgangstreibertransistors (M<sub>1a</sub>), muss aber der Natural-NMOS-Transistor, der hier beispielhaft als Ausgangstransistor eingesetzt wird, für eine größere Gleichstromlast sehr großflächig gewählt werden, weshalb sein Einsatz nur auf Anwendungen mit kleineren Gleichstromlastströmen begrenzt ist. Außerdem hat solch ein natural NMOS-Transistor (M<sub>1a</sub>) aufgrund seiner deutlich größeren Kanallänge eine relativ große Gate-Kapazität und reagiert somit sehr langsam mit einer ersten Zeitkonstante (T1a) auf dynamische Lastsprünge des Laststromes (ILa), was wiederum ohne externe Pufferkapazität Spannungseinbrüche zur Folge hat.

[0004] Aus der US 2014 / 0 028 274 A1 ist beispielsweise ein Spannungsregler zur Abgabe eines Laststroms (ILa) mit einer Referenzspannung, mit einem Differenzverstärker, mit einem ersten Transistor, mit einer Rückkoppelschaltung, und mit einem Reglerausgang bekannt. Dabei weist der Differenzverstärker der US 2014 / 0 028 274 A1 einen negativen Eingang und einen positiven Eingang und einen Ausgang auf. Der Reglerausgang der US 2014 / 0 028 274 A1 ist über die Rückkoppelschaltung auf den negativen Eingang des Differenzverstärkers der US 2014 / 0 028 274 A1zurückgekoppelt. Der positive Eingang des Differenzverstärkers der US 2014 / 0 028 274 A1 ist mit der Referenzspannung der US 2014 / 0 028 274 A1 verbunden. Der erste Transistor der US 2014 / 0 028 274 A1 bestromt in Abhängigkeit von dem Ausgangssignal des Differenzverstärkers der US 2014 / 0 028 274 A1 den Ausgang des Spannungsreglers der US 2014 / 0 028 274 A1 mit einem ersten Strom (I<sub>1a</sub>). Der Spannungsregler der US 2014 / 0 028 274 A1 führt dabei ein Verfahren zur Stabilisierung einer Ausgangsspannung des Ausgangs eines Spannungsreglers aus, dass das Ausregeln der Ausgangsspannung (VOUTa) mit Hilfe eines ersten Transistors umfasst, der einen ersten Strom in den Knoten des Ausgangs des Spannungsreglers in Abhängigkeit von einer Referenzspannung (V<sub>RFF</sub>) einspeist.

**[0005]** Aus der WO 2017/ 102 251 A1 ist ein solcher Spannungsregler bekannt, wobei in der technischen Lehre der WO 2017/ 102 251 A1 eine zweite Referenzspannung und ein zweiter Transistor sowie eine

Bias-Stromguelle vorgesehen sind. Gemäß der technischen Lehre der WO 2017/ 102 251 A1 bestromt der zweite Transistor der WO 2017/ 102 251 A1 den Ausgang des Spannungsreglers der WO 2017/ 102 251 A1 mit einem zweiten Strom in Abhängigkeit von der zweiten Referenzspannung der WO 2017/ 102 251 A1 Dabei hängt der zweite Strom der WO 2017/ 102 251 A1 von der Spannungsdifferenz zwischen der zweiten Referenzspannung der WO 2017/ 102 251 A1 und der WO 2017/ 102 251 A1 Spannung am Ausgang des Spannungsreglers der WO 2017/ 102 251 A1 und dem Bias-Strom der WO 2017/ 102 251 A1 ab. Aus der ist dabei ein Verfahrensschritt bekannt, der sas Einspeisen eines zweiten Stroms in den Knoten des Ausgangs des Spannungsreglers mit Hilfe eines zweiten Transistors umfasst, wobei der Wert des zweiten Stromes von einer zweiten Referenzspannung und von einem Bias-Strom abhängt.

[0006] Aus der DE 603 11 098 T2 ist ein Multimodusspannungsregler mit einer Niederstromdurchlasseinrichtung und einer Hochstromdurchlasseinrichtung bekannt, die jeweils zum Anschluss zwischen einer Stromversorgung und einer Last ausgeführt sind. Eine Vorrichtung gemäß der technischen Lehre der DE 603 11 098 T2 umfasst einen Feldverstärker mit einer Ausgangsleitung, der auf die Differenz zwischen einer Referenzspannung und einer Funktion der Spannung an der Last anspricht, um ein Fehlersignal auf der Ausgangsleitung der Vorrichtung gemäß der technischen Lehre der DE 603 11 098 T2 zu erzeugen. Eine Vorrichtung gemäß der technischen Lehre der DE 603 11 098 T2 zeichnet sich durch einen Kleinleistungstreiber aus, der einen niedrigen Vorstrom hat und in einem Niederlastmodus aus das Fehlersignal auf der Ausgangsleitung anspricht, um die Niederstromdurchlasseinrichtung zu aktivieren und so der Last eine niedrigere Leistung bereitzustellen. Des Weiteren zeichnet sich eine Vorrichtung gemäß der technischen Lehre der DE 603 11 098 T2 dadurch aus, dass sie einen Hochleistungstreiber umfasst, der einen höheren Vorstrom hat und in einem Hochleistungsmodus auf das Fehlersignal auf der Ausgangsleitung anspricht, um die Hochstromdurchlasseinrichtung zu aktivieren und so der Last (57) eine hohe Leistung bereitzustellen, damit der Wirkungsgrad über die Hoch- und Niederleistungssignal aufrechterhalten wird.

[0007] Aus der US 4 683 382 A ist eine Halbleiteranordnung bekannt. Die Vorrichtung gemäß der US 4 683 382 A zeigt ein Bereitschaftsintervall zur Verringerung der Leistungsaufnahme und mit einem externen Anschluss, an dem eine externe Stromversorgungsspannung zugespeist wird. Die Vorrichtung der US 4 683 382 A umfasst darüber hinaus eine interne Stromversorgungsleitung, an welcher eine Spannung, die niedriger ist als die externe Stromversorgungsspannung, zugespeist wird.

[0008] Die Vorrichtung der US 4 683 382 A umfasst darüber hinaus einen internen Schaltkreis, der ein Bereitschaftsintervall zur Verringerung der Leistungsaufnahme aufweist und mittels der Spannung von der internen Stromversorgungsleitung als Betriebsspannung betrieben wird. Außerdem weist die Vorrichtung der US 4 683 382 A eine zumindest im Bereitschaftsintervall wirksame erste Spannungsabsenkeinheit auf, um aus der externen Stromversorgungsspannung eine erste Spannung mit einer kleineren Größe als derjenigen der externen Stromversorgungsspannung für die Zuspeisung der ersten Spannung zur internen Stromversorgungsleitung zu erzeugen. Ebenso weist die Vorrichtung der US 4 683 382 A eine in einem vom Bereitschaftsintervall verschiedenen Intervall wirksame zweite Spannungsabsenkeinheit auf, um aus der externen Stromversorgungsspannung eine zweite Spannung, welche die gleiche Größe wie die erste Spannung (Vin1), aber eine kleinere Größe als die externe Stromversorgungsspannung aufweist, für die Zuspeisung der zweiten Spannung zur internen Stromversorgungsleitung (12) zu erzeugen. Die technische Lehre der US 4 683 382 A zeichnet sich dadurch aus, dass die Leistungsaufnahme der ersten Stromabsenkeinheit in deren wirksamen Zustand niedriger ist als diejenige der zweiten Stromabsenkeinheit in deren wirksamen Zustand, wobei die Leistungsaufnahme der zweiten Spannungsabsenkeinheit, wenn diese unwirksam bzw. außer Betrieb ist, praktisch null beträgt.

[0009] Aus der DE 101 10 273 C2 ist ein Spannungsgenerator zur Erzeugung einer an einem Ausgangsanschluss anliegenden Ausgangsspannung bekannt. Die Vorrichtung gemäß der technischen Lehre der DE 101 10 273 C2 umfasst einen ersten Spannungsregler mit einer Vergleichsstufe und einer von der Vergleichsstufe ansteuerbaren Ausgangsstufe, bei dem die Ausgangsstufe ausgangsseitig mit dem Ausgangsanschluss verbunden ist und die Vergleichsstufe eingangsseitig einen Anschluss für ein erstes Referenzpotential aufweist. Die Vorrichtung gemäß der technischen Lehre der DE 101 10 273 C2 umfasst des Weiteren einen Anschluss, der mit der Ausgangsstufe verbunden ist, sowie einen zweiten Spannungsregler mit einer Vergleichsstufe und einer von der Vergleichsstufe ansteuerbaren Ausgangsstufe und einen Schalter, bei der die Ausgangsstufe ausgangsseitig mit dem Ausgangsanschluss verbunden ist und die Vergleichsstufe eingangsseitig mit dem Anschluss für das erste Referenzpotential und mit der Ausgangsstufe verbunden ist, wobei der zweite Spannungsregler durch den Schalter ein- und ausschaltbar ist. Die Vorrichtung gemäß der technischen Lehre der DE 101 10 273 C2 umfasst ebenso eine weitere Vergleichsstufe, die eingangsseitig mit einem Anschluss für ein vom ersten Referenzpotential (VREF) durch einen Spannungsteiler abgeleitetes verschiedenes weiteres Referenzpotential und mit dem Ausgangsanschluss verbunden ist und die ausgangsseitig einen Anschluss aufweist, über den der Schalter des zweiten Spannungsreglers steuerbar ist.

**[0010]** Aus der DE 35 38 584 A1 ist eine aus mehreren parallel arbeitenden Feldeffekttransistoren bestehende Anordnung bekannt. Die Vorrichtung der DE 35 38 584 A1 ist gekennzeichnet da durch, dass zum Ersten nur einer der Feldeffekttransistoren an seinem Gate-Anschluss von einem externen Steuersignal gesteuert wird und zum Zweiten die weiteren Feldeffekttransistoren über eine eigene Regelung in dem Sinne nachgeführt werden, dass sie jeweils auf einen zuvor gesteuerten Feldeffekttransistor nachgeführte parallele Stromquellen darstellen.

#### Aufgabe der Erfindung

**[0011]** Der Erfindung liegt daher die Aufgabe zugrunde, eine Lösung zu schaffen, die die obigen Nachteile des Stands der Technik nicht aufweist und weitere Vorteile aufweist.

**[0012]** Die Kern-Aufgabe dieser Erfindung ist somit die Realisierung einer chip-flächen- und damit kostengünstigen Schaltung zur Vermeidung der besagten Spannungseinbrüche auf dem Ausgang (**V**<sub>OUTa</sub>) des Spannungsreglers infolge großer dynamischen Lastströme (**I**<sub>La</sub>) am Ausgang (**V**<sub>OUTa</sub>) eines Hochvolt-Low-Drop-Reglers (**HV-LDO**<sub>a</sub>) ohne Verwendung einer externen Puffer-Kapazität (**C**<sub>buffer</sub>).

**[0013]** Diese Aufgabe wird durch eine Vorrichtung nach Anspruch 1 und ein Verfahren nach Anspruch 2 gelöst.

Lösung der erfindungsgemäßen Aufgabe

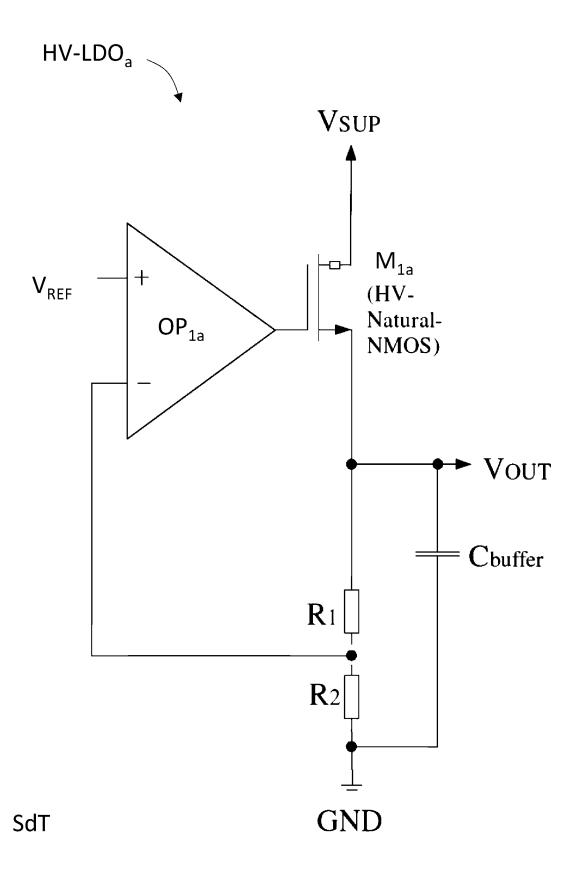

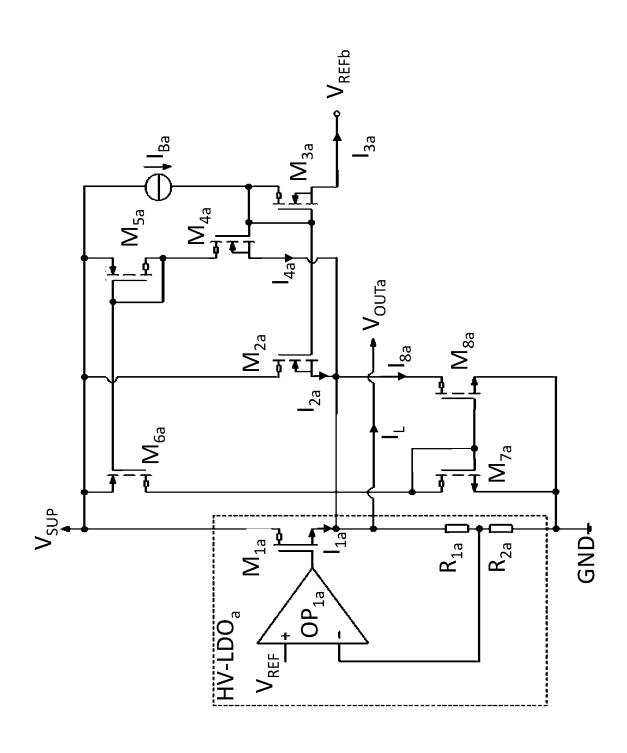

[0014] Die Erfindung wird mit Hilfe der Fig. 3 bis Fig. 6 in verschiedenen Varianten erläutert.

#### Variante A

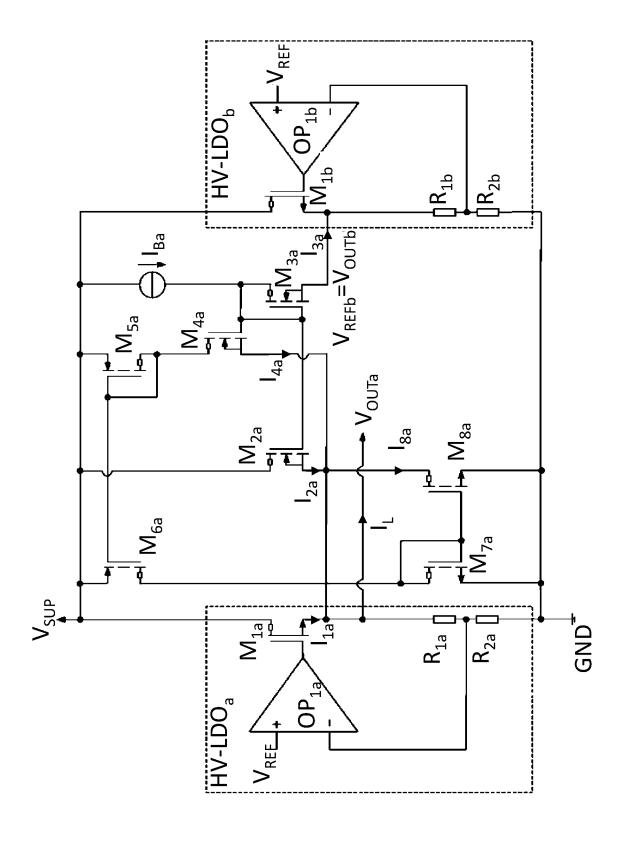

[0015] Die Fig. 3 zeigt das vereinfachte Prinzipschaltbild der Schaltung dieser Erfindung.

[0016] Die Grundidee der erfindungsgemäßen Schaltung ist die Überlagerung der Ausgangsstufe eines vorhandenen ersten Hochvolt-Low-Drop-Reglers ( $HV\text{-}LDO_a$ ) aus einem ersten, relativ hochohmigen, selbstleitenden HV-Natural-Transistor ( $M_{1a}$ ), der vorzugsweise ein NMOS-Transistor ist, mit geringer Treibfähigkeit mit einem zusätzlichen niederohmigen Treiber aus einem zweiten DIMOS-Treiber-Transistor ( $M_{2a}$ ). Unter einem DIMOS Transistor im Sinne dieser Offenlegung ist hier und im folgenden Text ein "double implanted metal-oxide semiconductor" beispielsweise entsprechend J. Tihanyi and D. Widmann, "DI-MOS - A novel IC technology with submicron effective channel MOSFETs," 1977 International Electron

Devices Meeting, Washington, DC, USA, 1977, pp. 399-401 oder ein DMOS-Transistor entsprechend J. D. Plummer and J. D. Meindl, "A monolithic 200-V CMOS analog switch," in IEEE Journal of Solid-State Circuits, vol. 11, no. 6, pp. 809-817, Dec. 1976 zu verstehen.

[0017] Entsprechend der Fig. 3 ist der erste Hochvolt-Low-Drop-Regler (HV\_LDO<sub>a</sub>) ein Low-Drop-Spannungsregler bestehend aus einem ersten Operationsverstärker (OP1a), dem ersten Ausgangstreibertransistor (M<sub>1a</sub>), der typischerweise ein relativ hochohmiger, selbstleitender HV-Natural-Transistor NMOS-Transistor ist, und einem ersten Spannungsteiler bestehend aus einem ersten oberen Spannungsteilerwiderstand (R<sub>1a</sub>) und einem ersten unteren Spannungsteilerwiderstand (R<sub>2a</sub>), der über die Referenzspannung VREF eine geregelte erste Ausgangsspannung (Vouta) erzeugt. Natürlich kann die Rückkopplung auch über komplexere Schaltungen erfolgen. Der erste Ausgangstreibertransistor (M<sub>1a</sub>), dieses ersten Hochvolt-Low-Drop-Reglers (HV\_LDO<sub>a</sub>) ist ein relativ hochohmiger, selbstleitender N-Kanal-HV-Natural-Transistor mit geringer Treibfähigkeit. Wegen der relativ großen Kompensationskapazität und Gate-Kapazität, die auf die große Kanallänge des ersten Ausgangstreibertransistors (M<sub>1a</sub>) wegen seiner bevorzugten Ausführung als ein relativ hochohmiger, selbstleitender N-Kanal-HV-Natural-Transistor zurück zu führen ist, ist die erste Zeitkonstante (T<sub>1a</sub>) dieses ersten Hochvolt-Low-Drop-Reglers (HV\_LDO<sub>a</sub>) relativ groß, was wiederum eine relativ langsame Regelungsgeschwindigkeit seiner Ausgangsspannung an seinem Ausgang (Vouta) zufolge hat. Damit kann er den großen dynamischen Umladeströmen bzw. Lastströmen (I<sub>La</sub>), die ggf. seinem Ausgang (V<sub>OUTa</sub>) entnommen werden, u.a. auch wegen der fehlenden externen Puffer-Kapazität (C<sub>buf-</sub> fer), nicht schnell genug entgegenwirken.

[0018] Diese Funktion übernimmt hier entsprechend der erfindungsgemäßen Idee nun der zum bestehenden ersten Ausgangstreibertransistor ( $\mathbf{M_{1a}}$ ) parallel geschaltete, flächensparsame und niederohmige zusätzliche zweite DIMOS-Treiber-Transistor ( $\mathbf{M_{2a}}$ ), der aufgrund seiner sehr kleinen Kanallänge, einerseits ein sehr kleines  $\mathbf{R_{DSON2a}}$  und damit eine große Treibfähigkeit besitzt und anderseits eine relativ kleine Gate-Kapazität aufweist.

[0019] Der Gleichspannungs- und Gleichstrom-Arbeitspunkt des zweiten DIMOS-Treiber-Transistors ( $\mathbf{M_{2a}}$ ) wird nach dem Konzept der Erfindung so gewählt, dass der zweite DIMOS-Treiber-Transistor ( $\mathbf{M_{2a}}$ ) leicht leitend ist bzw. die Gate-Source-Spannung des zweiten DIMOS-Treiber-Transistors ( $\mathbf{M_{2a}}$ ) leicht oberhalb der Schwellspannung des zweiten DIMOS-Treiber-Transistors ( $\mathbf{M_{2a}}$ ) liegt. Dies minimiert die Umladezeiten der parasitären Kapazitäten des zweiten DIMOS-Treiber-Transistors ( $\mathbf{M_{2a}}$ ) und damit

seine Reaktionszeit auf die dynamischen Laststromänderungen des ersten Laststroms ( $I_{La}$ ). Folglich werden durch die dynamischen Laststromänderungen des ersten Laststroms ( $I_{La}$ ) verursachten Spannungseinbrüche der ersten Ausgangsspannung ( $V_{OUTa}$ ) des Ausgangs des ersten Hochvolt-Low-Drop-Reglers ( $HV-LDO_a$ ) soweit minimiert, dass der Einsatz einer externen Puffer-Kapazität ( $C_{buffer}$ ) nicht mehr notwendig ist.

**[0020]** Für die Einstellung dieses Arbeitspunkts wird entsprechend der **Fig. 3** eine zweite Referenzspannung ( $\mathbf{V}_{\mathsf{REFb}}$ ) mit dem gleichen Spannungswert wie die erste Ausgangsspannung ( $\mathbf{V}_{\mathsf{OUTa}}$ ) des Reglerausgangs verwendet. Der verwendete Referenzgenerator zur Erzeugung dieser zweiten Referenzspannung ( $\mathbf{V}_{\mathsf{REFb}}$ ) kann z.B. ein kleiner Buffer oder selbst wieder ein Spannungsregler sein. Hierzu später mehr.

[0021] In den meisten Anwendungsschaltungen der integrierten Schaltung (IC) wird in der Regel mehr als ein Spannungsregler z.B. für die Trennung der Versorgungen des Digital- und Analogteils benötigt. In solchen Fällen wird, wie in der Fig. 4 entsprechend dem erfindungsgemäßen Konzept dargestellt, die geregelte zweite Ausgangsspannung Voutb des Ausgangs des zweiten Hochvolt-Low-Drop-Reglers (HV\_ LDO<sub>b</sub>), bestehend aus einem zweiten Operationsverstärker (OP<sub>1b</sub>), einem zweiten Ausgangs-Treiber-Transistor (M<sub>1b</sub>) und einem zweiten oberen Spannungsteilerwiderstand (R<sub>1b</sub>) und einem zweiten unteren Spannungsteilerwiderstand (R<sub>2b</sub>), als Referenzspannung verwendet. In der Regel kann diese zweite Referenzspannung (V<sub>REFb</sub>) aber beliebig generiert werden.

[0022] Die statische Gate-Spannung des zweiten DI-MOS-Treiber-Transistors  $(\mathbf{M}_{2a})$  wird über einen kleinen, zum zweiten DIMOS-Treiber-Transistor  $(\mathbf{M}_{2a})$  matchenden dritten Sense-Transistor  $(\mathbf{M}_{3a})$  eingestellt. Dieser dritte Sense-Transistor  $(\mathbf{M}_{3a})$  ist mit seinem Source-Anschluss an der zweiten Referenzspannung  $(\mathbf{V}_{\text{REFb}} = \mathbf{V}_{\text{OUTb}})$  angehängt und wird highside-seitig mit einem kleinen ersten Bias-Strom  $(\mathbf{I}_{Ba})$  bestromt. Damit stellt sich die Gate-Source-Spannung des dritten Sense-Transistors  $(\mathbf{M}_{3a})$  leicht oberhalb der Schwellspannung des dritten Sense-Transistors  $(\mathbf{M}_{3a})$  ein.

**[0023]** Somit ist auch der zweite DIMOS-Treiber-Transistor ( $\mathbf{M_{2a}}$ ) leicht leitend, wobei mit  $\mathbf{V_{OUTa}} = \mathbf{V_{OUTb}}$  die Ausgangsspannung ( $\mathbf{V_{OUTa}}$ ) des ersten Reglers in etwa der Ausgangsspannung ( $\mathbf{V_{OUTb}}$ ) des zweiten Reglers entspricht.

**[0024]** Um zu verhindern, dass der gespiegelte Strom über den Stromspiegel ( $\mathbf{M_{2a}}$ ,  $\mathbf{M_{3a}}$ ) im statischen Fall die Regler-Ausgangsspannung ( $\mathbf{V_{OUTa}}$ ) beeinflusst, wird ein gleichgroßer Strom aus dem Reglerausgang entnommen. Zu diesem Zweck dienen der

vierte Transistor ( $\mathbf{M}_{4a}$ ), der fünfte Transistor ( $\mathbf{M}_{5a}$ ), der sechste Transistor ( $\mathbf{M}_{6a}$ ), der siebte Transistor ( $\mathbf{M}_{7a}$ ) und der achte Transistor ( $\mathbf{M}_{8a}$ ).

**[0025]** Der Sense-Transistor ( $\mathbf{M_{3a}}$ ), der vierte Transistor ( $\mathbf{M_{4a}}$ ), der fünfte Transistor ( $\mathbf{M_{5a}}$ ), der sechste Transistor ( $\mathbf{M_{6a}}$ ) und der siebte Transistor ( $\mathbf{M_{7a}}$ ) sowie der achte Transistor ( $\mathbf{M_{8a}}$ ) sind Stromspiegelpaare mit einem Gesamtspiegelverhältnis von:

1:(m+1) wobei gilt:

$$m \times (W/L)[\mathbf{M}_{3a}] = (W/L)[\mathbf{M}_{2a}]$$

[0026] Hierbei bezeichnet (W/L)[ $\mathbf{M}_{3a}$ ] das Längenzu-Weiten-Verhältnis des Kanals des dritten Sense-Transistors ( $\mathbf{M}_{3a}$ ) und (W/L)[ $\mathbf{M}_{2a}$ ] das Längen-zu-Weiten-Verhältnis des Kanals des zweiten DIMOS-Treiber-Transistors ( $\mathbf{M}_{2a}$ ). m repräsentiert eine positive Zahl. Bevorzugt handelt es sich um eine ganze Zahl.

[0027] Folgende (W/L)-Verhältnisse können als Beispiel verwendet werden:

Bei einem guten Matching der Transistoren gilt für die Gleichstromwerte der Ströme:

$$I_{2a} + I_{4a} = I_{8a}$$

Hiermit kompensieren sich die high-side- und low-side-seitigen Zusatzströme am ersten Regler-Ausgang des ersten Reglers mit der ersten Ausgangsspannung ( $\mathbf{V}_{\text{OUTa}}$ ). Damit wird die erste Ausgangsspannung ( $\mathbf{V}_{\text{OUTa}}$ ) des ersten Hochvolt-Low-Drop-Reglers ( $\mathbf{HV}$ -LDO $_{\mathbf{a}}$ ) und andere statische Eigenschaften des ursprünglichen ersten Hochvolt-Low-Drop-Reglers ( $\mathbf{HV}$ -LDO $_{\mathbf{a}}$ ) von der zusätzlichen Schaltung an seinem Regler-Ausgang nicht beeinflusst.

[0028] Bei einem dynamischen Laststromwechsel des Laststroms ( $I_{La}$ ) aus dem Ausgang ( $V_{OUTa}$ ) des ersten Hochvolt-Low-Drop-Reglers ( $HV\text{-}LDO_a$ ) heraus, steigt auch die Gate-Source-Spannung des zweiten DIMOS-Treiber-Transistors ( $M_{2a}$ ) und versetzt ihn in die Lage, den benötigten zusätzlichen Stromanteil des Laststroms ( $I_{La}$ ) zu liefern. Damit wird der Einbruch der Ausgangsspannung ( $V_{OUTa}$ ) stark reduziert.

#### Variante B

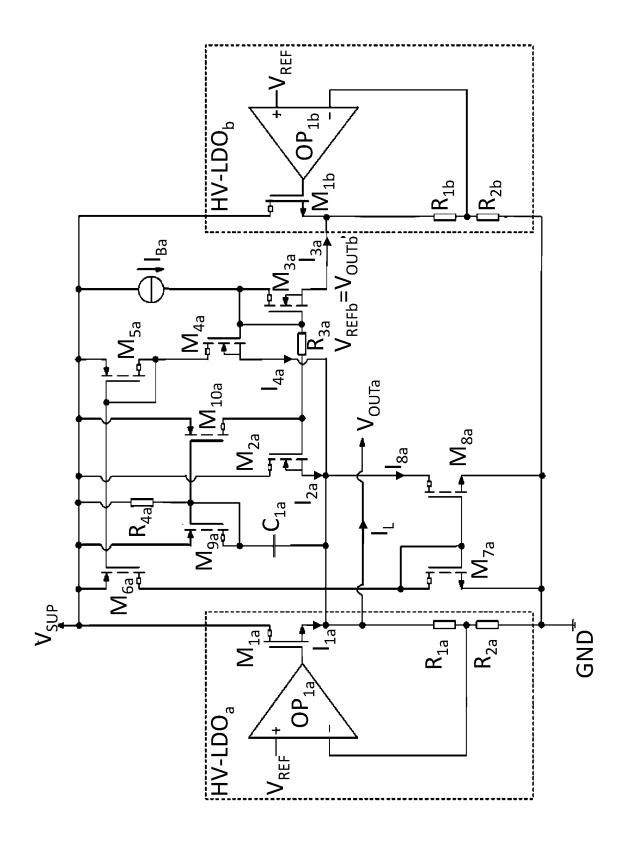

[0029] Die Reaktionszeit des Reglers auf dynamische Laststromwechsel des Laststroms (I<sub>La</sub>) kann mit einer zusätzlichen sogenannten dynamischen Gegenkopplung -wie in **Fig. 5** dargestellt- weiterhin

durch eine kleinere zweite Zeitkonstante ( $\tau_{2a}$ ) eines zweiten parallelen Regelkreises reduziert werden.

[0030] Der neunte Transistor ( $M_{9a}$ ), der zehnte Transistor (M<sub>10a</sub>) und die Kapazität (C<sub>1a</sub>) stellen hier eine Gegenkopplung, die als Reaktion zu den dynamischen Laststromwechseln des Laststroms (I<sub>1 a</sub>) die Gate-Spannung des DIMOS-Treiber-Transistors (M<sub>2a</sub>) weiter erhöhen. Dadurch steigt die Effektivität der Schaltung gegen die Spannungseinbrüche. Der Pullup-Widerstand (R<sub>4a</sub>) schaltet den neunten Transistor (M<sub>9a</sub>) und den zehnten Transistor (M<sub>10a</sub>) im statischen Fall aus. Der dritte Widerstand (R<sub>3a</sub>) wird mit einem relativ großen Widerstandswert gewählt und sorgt dafür, dass das Gate des zweiten DIMOS-Treiber-Transistors (M<sub>2a</sub>) im dynamischen Fall durch die relativ niederohmige Referenz nicht an dieser Spannung festgehalten wird und über die oben genannte zusätzliche Gegenkopplungsschaltung dynamisch weiter hochgezogen werden kann.

#### Variante C

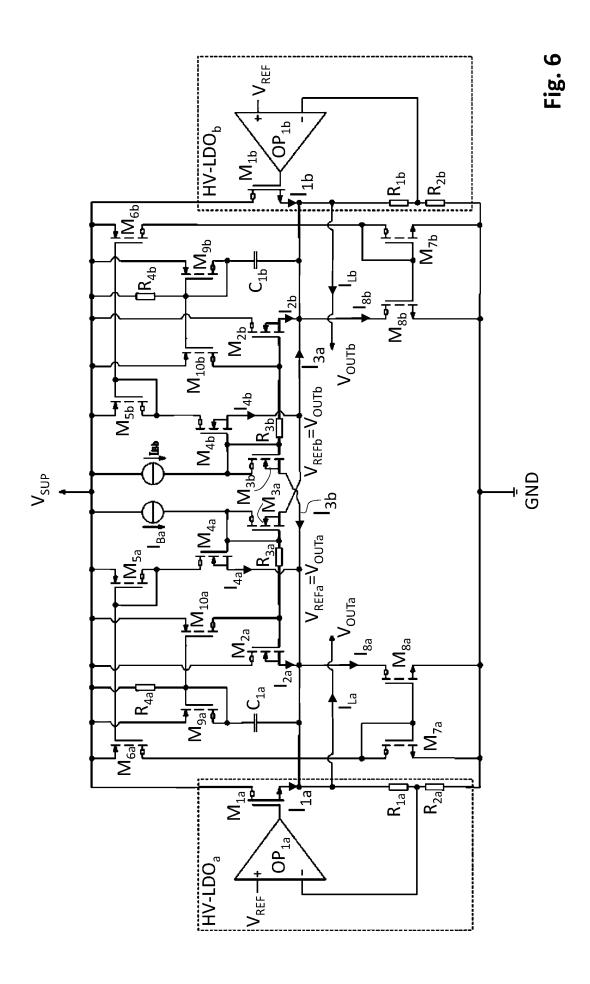

[0031] Entsprechend der erfindungsgemäßen Idee können auch zwei Hochvolt-Low-Drop-Regler ( $HV\text{-}LDO_a$ ,  $HV\text{-}LDO_b$ ) sich gegenseitig gegen dynamische Laststromwechsel ihrer Lastströme ( $I_{La}$ ,  $I_{Lb}$ ) stabilisieren. Damit kann dann bei beiden auf externe Kapazitäten ( $C_{buffer}$ ) verzichtet werden, was ggf. eine doppelte Ersparnis zur Folge hat. Hierfür wird die Schaltung der **Fig. 5** entsprechend der **Fig. 6** ergänzt.

[0032] Hier dient die erste Ausgangsspannung ( $V_{OU-Ta}$ ) des ersten Hochvolt-Low-Drop-Regler ( $HV-LDO_a$ ) als Referenzspannung ( $V_{REFb}$ ) für den zweiten Hochvolt-Low-Drop-Regler ( $HV_LDO_b$ ) und die zweite Ausgangsspannung ( $V_{OUTb}$ ) des zweiten Hochvolt-Low-Drop-Reglers ( $HV_LDO_b$ ) als Referenzspannung ( $V_{REFa}$ ) für den ersten Hochvolt-Low-Drop-Regler ( $HV-LDO_a$ ).

[0033] Ansonsten wird die zweite Ausgangsspannung ( $V_{OUTb}$ ) des zweiten Hochvolt-Low-Drop-Reglers ( $HV_LDO_b$ ) in gleicher Weise wie oben für den ersten Hochvolt-Low-Drop-Regler ( $HV_LDO_a$ ) beschrieben gegenüber Lastströmen stabilisiert und so die Spannungseinbrüche ohne zusätzliche externe Kapazität minimiert.

### Grundlegende Vorrichtung

**[0034]** Der vorgeschlagene Spannungsregler zur Abgabe eines Laststroms ( $I_{La}$ ) umfasst daher typischerweise zumindest einen Knoten für eine Referenzspannung ( $V_{REF}$ ), einen Knoten für eine zweite Referenzspannung ( $V_{REF}$ ), einen Differenzverstärker ( $OP_{1a}$ ) oder andere Verstärker äquivalenter Funktion, einen ersten Transistor ( $M_{1a}$ ), einen zweiten Transistor ( $M_{2a}$ ), einen vierten Transistor ( $M_{4a}$ ), einen achten Transistor ( $M_{8a}$ ), eine Bias-Stromquelle ( $I_{Ba}$ ),

eine Rückkoppelschaltung ( $R_{1a}$ ,  $R_{2a}$ ) und einen Knoten für den Reglerausgang (V<sub>OUT</sub>), an dem der Laststrom (I<sub>1 a</sub>) entnommen wird und an dem die durch die Referenzspannung (V<sub>REF</sub>) eingestellte Ausgangsspannung (V<sub>OUTa</sub>) abgenommen werden kann. Der Differenzverstärker (OP<sub>1a</sub>) weist, typischerweise einen negativen Eingang (-) und einen positiven Eingang (+) und einen Ausgang auf. Der Reglerausgang  $(V_{OUTa})$  wird über die Rückkoppelschaltung  $(R_{1a}, R_{2a})$ , hier ein Spannungsteiler aus einem ersten oberen Spannungsteilerwiderstand (R<sub>1a</sub>) und einem unteren ersten Spannungsteilerwiderstand (R2a) auf den negativen Eingang (-) des Differenzverstärkers (OP<sub>1a</sub>) zurückgekoppelt. Der positive Eingang (+) des Differenzverstärkers (OP<sub>1a</sub>) ist mit der besagten Referenzspannung (V<sub>REF</sub>) bevorzugt verbunden. Der erste Transistor (M<sub>1a</sub>), der bevorzugt ein selbstleitender NMOS-Transistor ist, bestromt nun in Abhängigkeit von dem Ausgangssignal des Differenzverstärkers (**OP**<sub>1a</sub>) den Ausgang (**V**<sub>OUT</sub>) des Spannungsreglers mit einem ersten Strom (I<sub>1a</sub>), den er in den Knoten des Ausgangs (Vouta) des ersten Spannungsreglers (HV-LDO<sub>a</sub>) einspeist. Dies stellt den ersten Regelkreis dar. Wird ein selbstleitender NMOS-Transistor als erster Transistor (M<sub>1a</sub>) verwendet, so weist dieser typischerweise einen relativ langen Kanal auf, was die notwendige Spannungsfestigkeit ergibt, um als positive Versorgungsspannung (V<sub>SUP</sub>) typische automobile Kfz-Board-Netzspannungen verwenden zu können. Da es sich um einen selbstleitenden NMOS-Transistor handelt, kann der Ausgang (Vouta) des ersten Hochvolt-Low-Drop-Reglers (HV-LDO<sub>a</sub>) bis nahezu an die positive Versorgungsspannung gebracht werden. Der Nachteil dieses selbstleitenden NMOS-Transistors (M<sub>1a</sub>) ist, dass er einen relativ hohen ersten Einschaltwiderstand (R<sub>DSON1a</sub>) besitzt. Hierdurch hat die zuvor beschriebene erste Regelschleife eine relativ hohe erste Zeitkonstante ( $\tau_{1a}$ ), was die besagte Empfindlichkeit gegenüber dynamischen Laststromwechseln des Laststroms (ILa) zur Folge hat. Daher wird der zweite Transistor (M<sub>2a</sub>), der bevorzugt ein nicht selbstleitender DIMOS-Transistor ist, vorgesehen, der parallel zu dem ersten Transistor  $(\mathbf{M_{1a}})$  den Ausgang  $(\mathbf{V_{OUTa}})$  des ersten Hochvolt-Low-Drop-Reglers (HV-LDO<sub>a</sub>) ebenfalls, nun aber mit einem zweiten Strom (I<sub>2a</sub>), in Abhängigkeit von der zweiten Referenzspannung ( $V_{\text{REFb}}$ ) bestromt und über eine zweite Regelschleife gesteuert wird. Die mit diesem zweiten Transistor (M2a) verbundene zweite Zeitkonstante (T2a) dieser parallelen zweiten Regelschleife ist erheblich geringer, da der nicht selbstleitende zweite DIMOS-Transistor (M2a) einen erheblich geringeren Einschaltwiderstand (R<sub>DSON2a</sub>) als der selbstleitende erste NMOS-Transistor (M<sub>1a</sub>) aufweist. Dies ist ein wesentlicher Vorteil gegenüber dem Stand der Technik. Ein vierter Transistor (M<sub>4a</sub>) bestromt den Ausgang (V<sub>OUTa</sub>) des ersten Hochvolt-Low-Drop-Regler (HV-LDO<sub>a</sub>) ebenfalls parallel mit einem vierten Strom (I<sub>4a</sub>). Ein achter Transistor (M<sub>8a</sub>) entnimmt dem Ausgang (Vout) des Hochvolt-Low-

Drop-Reglers (HV-LDO<sub>a</sub>) einen achten Strom (I<sub>8a</sub>). Der vierte Strom (I4a) hängt dabei von der Spannungsdifferenz zwischen der zweiten Referenzspannung ( $V_{REFb}$ ) und der Spannung am Ausgang ( $V_{OU}$ -Ta) des Hochvolt-Low-Drop-Reglers (HV-LDOa) und dem Bias-Strom (IBa) ab. Durch den dritten Transistor  $(\mathbf{M}_{3a})$  fließt ein dritter Strom  $(\mathbf{I}_{3a})$  der dem Strom  $(\mathbf{I}_{Ba})$ der betreffenden Stromquelle entspricht. Dieser dritte Strom (I<sub>3a</sub>) wird durch ein Stromspiegelverhältnis m in den zweiten Strom (I<sub>2a</sub>) durch den zweiten Transistor (M<sub>2a</sub>) als Teil eines Stromspiegels umgesetzt. Der achte Strom (I8a) entspricht entsprechend der Konstruktion betragsmäßig dem vierten Strom (I4a) entsprechend einem Stromspiegelverhältnis (1:(m+1)) einer Stromspiegelschaltung (M<sub>5a</sub>, M<sub>6a</sub>, M<sub>7a</sub>, M<sub>8a</sub>), deren Teil der achte Transistor (M8a) ist. Im ausgeregelten Zustand ist der achte Strom (I<sub>8a</sub>) betragsmäßig gleich dem Betrag der Summe aus zweiten Strom  $(I_{2a})$  und vierten Strom  $(I_{4a})$ . Der erste Strom  $(I_{1a})$  ist im ausgeregelten Zustand betragsmäßig gleich dem Betrag der Summe aus dem Strom in den Spannungsteiler (R<sub>1a</sub>, R<sub>2a</sub>) und dem Laststrom (I<sub>L</sub>) aus der Vorrichtung heraus. Der zweite Strom (I2a) hängt von der Spannungsdifferenz zwischen der zweiten Referenzspannung (V<sub>REFb</sub>) und der Spannung am Ausgang (V<sub>OUTa</sub>) des ersten Hochvolt-Low-Drop-Reglers (HV-LDO<sub>a</sub>) und dem Bias-Strom (I<sub>Ba</sub>) ab. Dieses Szenario entspricht der Fig. 3.

[0035] Vorteile dieser Grundversion der Vorrichtung sind zum Ersten, dass durch den selbstleitenden ersten NMOS-Transistor ( $\mathbf{M_{1a}}$ ) der maximale am Ausgang ( $\mathbf{V_{OUT}}$ ) des Hochvolt-Low-Drop-Reglers ( $\mathbf{HV-LDO_a}$ ) ggf. zur Verfügung stellbare Spannungspegel nahezu dem Pegel der Versorgungsspannung ( $\mathbf{V_{SUP}}$ ) entspricht, und zum Zweiten, dass durch die schnelle Nachregelung mittels des nicht selbstleitenden zweiten DIMOS-Transistors ( $\mathbf{M_{2a}}$ ) schnelle dynamische Änderungen des Laststroms ( $\mathbf{I_{La}}$ ) ausgeglichen werden können, sodass keine externe Kapazität ( $\mathbf{C_{buffer}}$ ) mehr notwendig ist. Außerdem ist der zweite Transistor ( $\mathbf{M_{2a}}$ ), wenn er als nicht selbstleitender DIMOS-Transistor realisiert wird, nicht besonders flächenintensiv.

#### Erste Variante der Vorrichtung

**[0036] Fig. 4** zeigt eine erste Variante, bei der die zweite Referenzspannung ( $V_{REFb}$ ) durch einen zusätzlichen zweiten Spannungsregler (HVLDO<sub>b</sub>) gebildet wird.

#### Zweite Variante der Vorrichtung

**[0037]** Bei einer zweiten Variante der Vorrichtung weist die Vorrichtung zusätzlich eine Schaltung zum Starten der Regelung auf. Dabei ist eine erste Kapazität ( $\mathbf{C}_{1a}$ ) mit einem ersten Anschluss mit dem Ausgang ( $\mathbf{V}_{OUTa}$ ) des Hochvolt-Low-Drop-Reglers ( $\mathbf{HV-LDO}_a$ ) verbunden. Die erste Kapazität ( $\mathbf{C}_{1a}$ ) ist

mit dem zweiten Anschluss über die MOS-Diode (M<sub>9a</sub>) eines Stromspiegels (M<sub>9a</sub>, M<sub>10a</sub>) mit der positiven Versorgungsspannung (V<sub>SUP</sub>) verbunden. Die Stromspiegel interne Referenzleitung dieses Stromspeigels (M<sub>9a</sub>, M<sub>10a</sub>) ist mit dem zweiten Knoten der Kapazität (C<sub>1a</sub>) verbunden und über einen vierten Widerstand (R<sub>4a</sub>) mit der positiven Versorgungsspannung  $(V_{SUP})$  verbunden. Der zweite Stromspiegeltransistor  $(M_{10a})$  des Stromspiegels  $(M_{9a}, M_{10a})$  kann bei einem geeigneten Potenzial an seinem Steueranschluss den Steueranschluss des zweiten Transistors (M<sub>2a</sub>) mit der positiven Versorgungsspannung (V<sub>SUP</sub>) verbinden. Der Steueranschluss des zweiten Stromspiegeltransistors (M<sub>10a</sub>) des Stromspiegels (M<sub>9a</sub>, M<sub>10a</sub>) ist mit dem zweiten Knoten der Kapazität (C<sub>1a</sub>) verbunden. Der Ausgang der Bias-Stromquelle  $(I_{Ba})$  ist über einen dritten Widerstand  $(R_{3a})$  mit dem Steueranschluss des zweiten Transistors (M<sub>2a</sub>) verbunden.

**[0038]** Vorteil dieser Variante ist, dass sie im Einschaltvorgang definiert durch diese Zusatzschaltung ( $\mathbf{R_{3a}}$ ,  $\mathbf{M_{10a}}$ ,  $\mathbf{R_{4a}}$ ,  $\mathbf{M_{9a}}$ ) in den Fangbereich der Regelung gebracht wird.

#### Dritte Variante der Vorrichtung

**[0039]** In einer dritten Variante der Vorrichtung ist ein zusätzlicher Sense-Transistor ( $\mathbf{M_{3a}}$ ) als MOS-Diode zwischen den Ausgang der Bias-Stromquelle ( $\mathbf{I_{Ba}}$ ) und die zweite Referenzspannung ( $\mathbf{V_{REFb}}$ ) geschaltet.

**[0040]** Diese MOS-Diode ( $\mathbf{M}_{3a}$ ) hat den Vorteil, dass sie einen Vergleich der zweiten Referenzspannung ( $\mathbf{V}_{\text{REFb}}$ ) mit der Ausgangsspannung ( $\mathbf{V}_{\text{OUTa}}$ ) ermöglicht

#### Vierte Variante der Vorrichtung

**[0041]** In einer vierten Variante der Vorrichtung ist der Steueranschluss des vierten Transistors ( $\mathbf{M_{4a}}$ ) mit dem Ausgang der Bias-Stromquelle ( $\mathbf{I_{Ba}}$ ) verbunden.

### Spannungsreglersystem

[0042] Des Weiteren wird hier ein Spannungsreglersystem aus einem ersten Spannungsregler ( $HV\text{-}LDO_a$ ) entsprechend dem unmittelbar zuvor beschriebenen Spannungsregler oder seinen Varianten und aus einem zweiten Spannungsregler ( $HV\text{-}LD\text{-}O_b$ ) entsprechend dem unmittelbar zuvor beschriebenen Spannungsregler oder seinen Varianten offengelegt. Der Ausgang ( $V_{OUTa}$ ) des ersten Spannungsreglers ( $HV\text{-}LDO_a$ ) ist dabei bevorzugt mit der zweiten Referenzspannung ( $V_{REFb}$ ) des zweiten Spannungsreglers ( $HV\text{-}LDO_b$ ) verbunden und der der Ausgang ( $V_{OUTb}$ ) des zweiten Spannungsreglers ( $HV\text{-}LDO_b$ ) ist bevorzugt mit der zweiten Referenzspannung ( $V_{REFa}$ ) des ersten Spannungsreglers ( $HV\text{-}LDO_a$ ) ver-

bunden. Natürlich sind auch komplexere Verkettungen mit mehr als zwei solchen Spannungsreglern (HV-LDO<sub>a</sub>, HV-LDO<sub>b</sub>) denkbar und werden hier ausdrücklich beansprucht.

**[0043]** Vorteil dieser ersten Variante ist, dass beide Spannungsregler ( $HV-LDO_a$ ,  $HV-LDO_b$ ) sich gegenseitig absichern können und hierdurch mehrere externe Kondensatoren ( $C_{buffer}$ ) eingespart werden können.

# Verfahren zum Betreiben eines solchen Spannungsreglers

**[0044]** Die zuvor beschriebenen Spannungsregler basieren auf einem Verfahren zur Stabilisierung einer Ausgangsspannung ( $V_{OUT}$ ) des Ausgangs eines solchen Spannungsreglers ( $HV_LDO_a$ ) umfassend die Schritte

- 1. Ausregeln der Ausgangsspannung ( $V_{OUT}$ ) mit Hilfe eines ersten Transistors ( $M_{1a}$ ), der einen ersten Strom ( $I_{1a}$ ) in den Knoten des Ausgangs des Spannungsreglers ( $HV_LDO_a$ ) einspeist in Abhängigkeit von einer Referenzspannung ( $V_{REF}$ );

- 2. Einspeisen eines zweiten Stroms ( $I_{2a}$ ) in den Knoten des Ausgangs des Spannungsreglers ( $HV\_LDO_a$ ) mit Hilfe eines zweiten Transistors ( $M_{2a}$ ), wobei der Wert des zweiten Stromes ( $I_{2a}$ ) von einer zweiten Referenzspannung ( $V_{REFb}$ ) und von einem Bias-Strom ( $I_{Ba}$ ) abhängt;

- 3. Einspeisen eines vierten Stroms ( $I_{4a}$ ) in den Knoten des Ausgangs des Spannungsreglers ( $HV_LDO_a$ ) mit Hilfe eines vierten Transistors ( $M_{4a}$ ), wobei der Wert des vierten Stromes ( $I_{4a}$ ) von einer zweiten Referenzspannung ( $V_{REFb}$ ) und von einem Bias-Strom ( $I_{Ba}$ ) abhängt;

- 4. Entnehmen eines achten Stromes ( $I_{8a}$ ) aus dem Knoten des Ausgangs des Spannungsreglers ( $HV_LDO_a$ ) mit Hilfe eines vierten Transistors ( $M_{4a}$ ), wobei der betragsmäßige Wert des achten Stromes ( $I_{8a}$ ) dem betragsmäßigen Wert des vierten Stromes ( $I_{4a}$ ) multipliziert mit einem Stromspiegelfaktor (1:(m+1)) entspricht.

# Grundidee der Vorrichtung der hier vorgelegten Offenlegung

[0045] Die Grundidee der hier vorgelegten Offenlegung stellt ein Low-Drop-Spannungsregler zur Erzeugung einer Ausgangsspannung an seinem Ausgang ( $V_{OUTa}$ ) dar, der einen ersten selbstleitenden NMOS-Transistor ( $M_{1a}$ ) und einen zweiten nicht selbstleitenden DIMOS-Transistor ( $M_{2a}$ ) umfasst. Der erste, selbstleitende NMOS-Transistor ( $M_{1a}$ ) wird als ein erster Regeltransistor des Low- Drop-Spannungsreglers verwendet und der zweite, nicht selbstleitende DIMOS-Transistor ( $M_{2a}$ ) wird als ein zweiter Regelt-

ransistor des Low- Drop-Spannungsreglers verwendet. Die Regelung der Ausgangsspannung ( $V_{OUTa}$ ) erfolgt über den ersten, selbstleitenden NMOS-Transistor ( $M_{1a}$ ) mit einer ersten Zeitkonstante ( $\tau_{1a}$ ) und die Regelung der Ausgangsspannung ( $V_{OUTa}$ ) über den zweiten, nicht selbstleitenden DIMOS-Transistor ( $M_{2a}$ ) mit einer zweiten Zeitkonstante ( $\tau_{2a}$ ). Die Konstruktion des zweiten, nicht selbstleitenden DI-MOS-Transistors ( $M_{2a}$ ) und des ersten, selbstleitenden NMOS-Transistor ( $M_{1a}$ ) ist bevorzugt so gewählt, dass die erste Zeitkonstante ( $\tau_{1a}$ ) länger als die zweite Zeitkonstante ( $\tau_{1a}$ ) ist.

### Grundidee des Verfahrens der hier vorgelegten Offenlegung

**[0046]** Die Grundidee des Verfahrens der hier vorgelegten Offenlegung ist ein Verfahren zum Betreiben eines Low-Drop-Spannungsregler zur Erzeugung einer Ausgangsspannung an seinem Ausgang (**V**<sub>OUTa</sub>) mit den Schritten:

- 1. Ausregelung der Ausgangsspannung ( $V_{OUTa}$ ) über einen ersten, selbstleitenden NMOS-Transistor ( $M_{1a}$ ) als ersten Regeltransistor einer ersten Regelschleife des Low- Drop-Spannungsreglers mit einer ersten Zeitkonstante ( $\tau_{1a}$ ) und

- 2. parallele Ausregelung der Ausgangsspannung ( $V_{OUTa}$ ) über einen zweiten, nicht selbstleitenden DIMOS-Transistor ( $M_{2a}$ ) als zweiten Regeltransistor einer zweiten parallelen Regelschleife des Low- Drop-Spannungsreglers mit einer zweiten Zeitkonstante ( $\tau_{2a}$ ).

[0047] Die Konstruktion des zweiten, nicht selbstleitenden DIMOS-Transistors ( $\mathbf{M_{2a}}$ ) und des ersten, selbstleitenden NMOS-Transistors ( $\mathbf{M_{1a}}$ ) ist dabei jeweils so gewählt, dass die erste Zeitkonstante ( $\mathbf{\tau_{1a}}$ ) länger als die zweite Zeitkonstante ( $\mathbf{\tau_{2a}}$ ) ist.

#### Vorteil der Erfindung

**[0048]** Die erfindungsgemäße Vorrichtung weist viele Vorteile gegenüber dem Stand der Technik auf:

- Es handelt sich um ein relativ flächen- und damit kostengünstiges Konzept eines Hochvolt-Low-Drop-Reglers (HV-LDO<sub>a</sub>, HV-LDO<sub>b</sub>) mit relativ großer Treibfähigkeit;

- 2. Es erfolgt eine Minimierung der Spannungseinbrüche infolge von dynamischem Laststromwechseln des Laststroms (I<sub>La</sub>, I<sub>Lb</sub>) ohne externe Komponente (C<sub>buffer</sub>) oder aufwendige interne Filter- und/oder kompensations- Schaltungen;

- 3. Es handelt sich um eine einfache Erweiterung der bestehenden LDO-Konzepte mit Natural-HV-NMOS-Treiber-Transistoren ( $\mathbf{M_{1a}}$ ,  $\mathbf{M_{1b}}$ ) auf größerer Treibfähigkeit;

4. Es erfolgt eine gegenseitige Stabilisierung mehrerer Hochvolt-Low-Drop-Regler (HV-LDO<sub>a</sub>, HV-LDO<sub>h</sub>) innerhalb einer integrierten Schaltung und damit die Erzielung einer mehrfachen Ersparnis von externen Gehäuseanschlüssen und Pufferkapazitäten (Cbuffer).

[0049] Die Vorteile sind hierauf aber nicht beschränkt.

#### Figurenliste

Fig. 1 zeigt einen Hochvolt-LDO für größere dynamische Lastströme nach dem Stand der Technik mit einem HV-PMOS-Treiber.

Fig. 2 zeigt einen Hochvolt-LDO für größere dynamische Lastströme nach dem Stand der Technik mit einem HV-Natural-NMOS-Treiber.

Fig. 3 zeigt eine vereinfachte Darstellung der erfindungsgemäßen Schaltung (Variante A).

Fig. 4 zeigt das Erfindungskonzept mit einem zusätzlichen Spannungsregler als Referenzgenerator (Variante A).

Fig. 5 zeigt das Erfindungskonzept mit einer zusätzlichen dynamischen Gegenkopplung (Variante B).

Fig. 6 zeigt die gegenseitige Stabilisierung zweier LDOs gegenüber Stromlasten nach dem Erfindungsprinzip (Variante C).

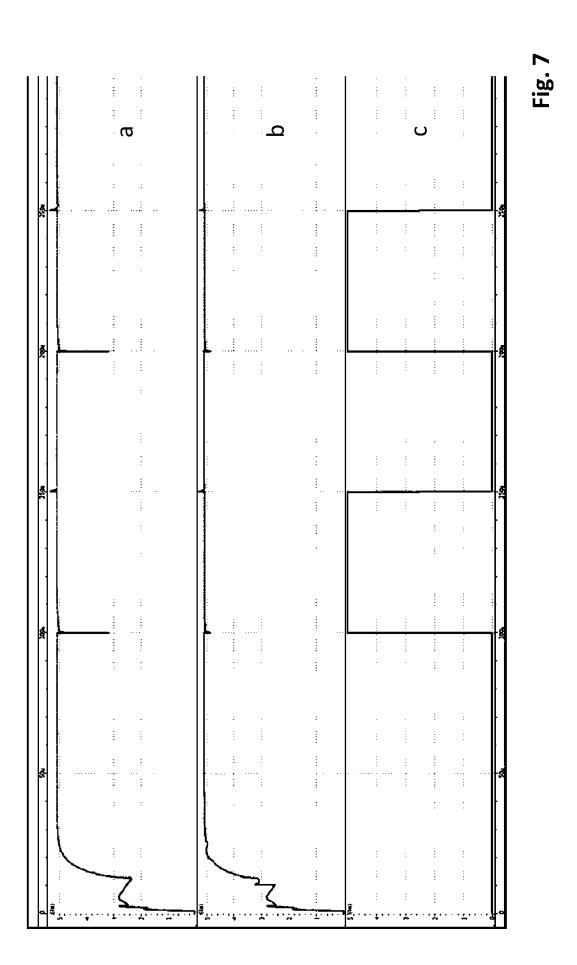

Fig. 7 zeigt in Fig. 7a die mit einem Oszilloskop aufgenommene Ausgangsspannung am Ausgang (Vouta) eines Spannungsreglers ohne die erfindungsgemäße Vorrichtung und ohne das erfindungsgemäße Verfahren und ohne Stützkapazität (Cbuffer) mit Spannungseinbrüchen bei PWM-förmigen dynamischen Belastungen und in Fig. 7b die mit dem betreffenden Oszilloskop aufgenommene Ausgangsspannung am Ausgang (V<sub>OUTa</sub>) eines solchen Spannungsreglers mit der erfindungsgemäßen Vorrichtung und mit dem erfindungsgemäßen Verfahren und ohne Stützkapazität (C<sub>buffer</sub>), ohne dass Spannungseinbrüche bei einer PWMförmigen dynamischen Belastungen auftreten, und in Fig. 7c den Verlauf der PWM-förmigen Belastung.

## Bezugszeichenliste

C<sub>1a</sub> erste Kapazität des ersten Hochvolt-Low-Drop-Reglers (HV-LDO<sub>a</sub>); C<sub>1b</sub> erste Kapazität des zweiten

Hochvolt-Low-Drop-Reglers

(HV-LDO<sub>b</sub>);

externe Kapazität, die als C<sub>buffer</sub> Stützkapazität dient und bevorzugt außerhalb des Gehäuses der integrierten Schal-

tung angeordnet wird;

**GND** Bezugspotenzial, hier auch negative Versorgungsspan-

nung;

HV-LDO<sub>a</sub> erster Hochvolt-Low-Drop-

Regler;

HV-LDO<sub>b</sub> zweiter Hochvolt-Low-Drop-

Regler;

erster Strom durch den ersten  $I_{1a}$

Transistor (M<sub>1a</sub>) des ersten Hochvolt-Low-Drop-Reglers (HV-LDO<sub>a</sub>) in den Ausgangsknoten des ersten Ausgangs (VOLTA) des ersten Hochvolt-Low-Drop-Reglers (HV-LDO<sub>a</sub>)

hinein:

erster Strom durch den ersten  $I_{1b}$ Transistor (M<sub>1b</sub>) des zweiten Hochvolt-Low-Drop-Reglers (HV-LDO<sub>b</sub>) in den Ausgangsknoten des zweiten Ausgangs

(Vouth) des zweiten Hochvolt-Low-Drop-Reglers (HV-LDO<sub>b</sub>)

hinein;

zweiter Strom durch den zweiten Transistor (M2a) des ersten Hochvolt-Low-Drop-Reglers (HV-LDO<sub>a</sub>) in den Ausgangsknoten des ersten Ausgangs (V<sub>OUTa</sub>) des ersten Hochvolt-Low-Drop-Reglers

(HV-LDO<sub>a</sub>) hinein;

zweiter Strom durch den zweiten Transistor (M<sub>2b</sub>) des zweiten Hochvolt-Low-Drop-Reglers (**HV-LDO**<sub>b</sub>) in den Ausgangsknoten des zweiten Ausgangs (Vouth) des zweiten Hochvolt-Low-Drop-Reg-

lers (HV-LDO<sub>b</sub>) hinein;

dritter Strom durch den dritten Transistor (M<sub>3a</sub>) des ersten Hochvolt-Low-Drop-Reglers  $(\mathbf{HV\text{-}LDO_a})$  aus dem Anschluss der zweiten Referenzspannung (V<sub>REFb</sub>) des ersten Hochvolt-Low-Drop-Reglers (HV-LDO<sub>a</sub>) heraus. Der dritte Strom entspricht dem Strom der Stromquelle des ersten Bias-Stroms (I<sub>Ba</sub>) der ersten

$I_{2a}$

$I_{2b}$

$I_{3a}$

# DE 10 2019 116 700 B4 2021.03.04

|                 | Bias-Stromquelle des ersten Reglers;                                                                                                                                                                                                                                                                                                    |                 | ten Hochvolt-Low-Drop-Reglers ( <b>HV-LDO</b> <sub>a</sub> ) heraus;                                                                                |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| I <sub>3b</sub> | dritter Strom durch den dritten Transistor (M <sub>3b</sub> ) des zweiten Hochvolt-Low-Drop-Reglers (HV-LDO <sub>b</sub> ) aus dem An-                                                                                                                                                                                                  | I <sub>Lb</sub> | zweiter Laststrom aus dem zweiten Ausgang ( <b>V</b> <sub>OUTb</sub> ) des zweiten Hochvolt-Low-Drop-Reglers ( <b>HV-LDO</b> <sub>b</sub> ) heraus; |  |

|                 | schluss der zweiten Referenz- spannung (V <sub>REFa</sub> ) des zweiten Hochvolt-Low-Drop-Reglers (HV-LDO <sub>b</sub> ) heraus. Der dritte Strom entspricht dem Strom der Stromquelle des zweiten Bias-Stroms (I <sub>Bb</sub> ) der zweiten Bias-Stromquelle des zweiten Reglers;                                                     | M <sub>1a</sub> | Ausgangstreibertransistor, relativ hochohmiger HV-Natural-<br>Transistor (selbstleitend) des ersten Reglers;                                        |  |

|                 |                                                                                                                                                                                                                                                                                                                                         | M <sub>1b</sub> | Ausgangstreibertransistor, relativ hochohmiger HV-Natural-<br>Transistor (selbstleitend) des zweiten Reglers;                                       |  |

| l <sub>4a</sub> | ten Transistor ( <b>M</b> <sub>4a</sub> ) des ersten Hochvolt-Low-Drop-Reglers ( <b>HV-LDO</b> <sub>a</sub> ) in den Ausgangsknoten des ersten Aus-                                                                                                                                                                                     | M <sub>2a</sub> | DIMOS-Treiber-Transistor des ersten Reglers;                                                                                                        |  |

|                 |                                                                                                                                                                                                                                                                                                                                         | M <sub>2b</sub> | DIMOS-Treiber-Transistor des zweiten Reglers;                                                                                                       |  |

|                 |                                                                                                                                                                                                                                                                                                                                         | M <sub>3a</sub> | Sense-Transistor des ersten Reglers, der zum DI-<br>MOS-Treiber-Transistor ( <b>M</b> <sub>2a</sub> )<br>matchend ausgeführt werden                 |  |

| l <sub>4b</sub> | vierter Strom durch den vierten Transistor (M <sub>4b</sub> ) des zweiten Hochvolt-Low-Drop-Reglers (HV-LDO <sub>b</sub> ) in den Ausgangsknoten des zweiten Ausgangs (V <sub>OUTb</sub> ) des zweiten Hochvolt-Low-Drop-Reg-                                                                                                           |                 | sollte;                                                                                                                                             |  |

|                 |                                                                                                                                                                                                                                                                                                                                         | М <sub>Зь</sub> | Sense-Transistor des zweiten Reglers, der zum DI-<br>MOS-Treiber-Transistor ( <b>M</b> <sub>2b</sub> )<br>matchend ausgeführt werden<br>sollte;     |  |

| l <sub>8a</sub> | lers ( <b>HV-LDO</b> <sub>b</sub> ) hinein; achter Strom durch den achten Transistor ( <b>M</b> <sub>8a</sub> ) des ersten Hochvolt-Low-Drop-Reglers ( <b>HV-LDO</b> <sub>a</sub> ) aus dem Ausgangsknoten des ersten Ausgangs ( <b>V</b> <sub>OUTa</sub> ) des ersten Hochvolt-Low-Drop-Reglers ( <b>HV-LDO</b> <sub>a</sub> ) heraus; | M <sub>4a</sub> | vierter Transistor des ersten<br>Reglers;                                                                                                           |  |

|                 |                                                                                                                                                                                                                                                                                                                                         | $M_{4b}$        | vierter Transistor des zweiten<br>Reglers;                                                                                                          |  |

|                 |                                                                                                                                                                                                                                                                                                                                         | M <sub>5a</sub> | fünfter Transistor des ersten<br>Reglers;                                                                                                           |  |

|                 |                                                                                                                                                                                                                                                                                                                                         | M <sub>5b</sub> | fünfter Transistor des zweiten<br>Reglers;                                                                                                          |  |

| I <sub>8b</sub> | achter Strom durch den ach-<br>ten Transistor ( <b>M<sub>8b</sub>)</b> des zwei-<br>ten Hochvolt-Low-Drop-Reg-                                                                                                                                                                                                                          | M <sub>6a</sub> | sechster Transistor des ersten Reglers;                                                                                                             |  |

|                 | lers ( <b>HV-LDO</b> <sub>b</sub> ) aus dem Ausgangsknoten des zweiten Ausgangs ( <b>V</b> <sub>OUTb</sub> ) des zweiten Hochvolt-Low-Drop-Reglers ( <b>HV-LDO</b> <sub>b</sub> ) heraus;                                                                                                                                               | M <sub>6b</sub> | sechster Transistor des zweiten Reglers;                                                                                                            |  |

|                 |                                                                                                                                                                                                                                                                                                                                         | M <sub>7a</sub> | siebter Transistor des ersten<br>Reglers;                                                                                                           |  |

| l <sub>Ba</sub> | erster Bias-Strom der ersten Bias-Stromquelle des ersten Reglers; zweiter Bias-Strom der zwei-                                                                                                                                                                                                                                          | M <sub>7b</sub> | siebter Transistor des zweiten<br>Reglers;                                                                                                          |  |

|                 |                                                                                                                                                                                                                                                                                                                                         | M <sub>8a</sub> | achter Transistor des ersten<br>Reglers;                                                                                                            |  |

| I <sub>Bb</sub> | ten Bias-Stromquelle des zweiten Reglers;                                                                                                                                                                                                                                                                                               | M <sub>8b</sub> | achter Transistor des zweiten<br>Reglers;                                                                                                           |  |

| IC              | integrierte Schaltung;                                                                                                                                                                                                                                                                                                                  | M <sub>9a</sub> | neunter Transistor des ersten Reglers;                                                                                                              |  |

| l <sub>La</sub> | erster Laststrom aus dem ersten Ausgang (V <sub>OUTa</sub> ) des ers-                                                                                                                                                                                                                                                                   |                 | . (09,010,                                                                                                                                          |  |

# DE 10 2019 116 700 B4 2021.03.04

| M <sub>9b</sub>        | neunter Transistor des zweiten Reglers;                                                                                                                                                                                                                                                                               | R <sub>DSON1b</sub>                                                                                   | Einschaltwiderstand des ersten Transistors (M <sub>1b</sub> ) des zweiten Hochvolt-Low-Drop-Reglers (HV-LDO <sub>b</sub> ) zwischen dessen Source-Anschluss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| M <sub>10a</sub>       | zehnter Transistor des ersten<br>Reglers;                                                                                                                                                                                                                                                                             |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| M <sub>10b</sub>       | zehnter Transistor des zweiten Reglers;                                                                                                                                                                                                                                                                               |                                                                                                       | und dessen Drain-Anschluss,<br>wenn der erste Transistor<br>( <b>M</b> <sub>1b</sub> ) des zweiten Hochvolt-<br>Low-Drop-Reglers ( <b>HV-LDO</b> <sub>b</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| $\mathbf{M}_{DRV}$     | Ausgangstreibertransistor                                                                                                                                                                                                                                                                                             |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| OP <sub>1a</sub>       | erster Operationsverstärker des ersten Reglers;                                                                                                                                                                                                                                                                       |                                                                                                       | sich im eingeschalteten Zu-<br>stand befindet (siehe auch<br>Fig. 6);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| OP <sub>1b</sub>       | zweiter Operationsverstärker des zweiten Reglers;                                                                                                                                                                                                                                                                     | R <sub>DSON2a</sub>                                                                                   | Einschaltwiderstand des zweiten DIMOS-Treiber-Tran-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| R <sub>1a</sub>        | erster oberer Spannungsteilerwiderstand;                                                                                                                                                                                                                                                                              |                                                                                                       | sistors (M <sub>2a</sub> ), des ersten<br>Hochvolt-Low-Drop-Reglers<br>(HV-LDO <sub>a</sub> ) zwischen dessen<br>Source-Anschluss und des-<br>sen Drain-Anschluss, wenn<br>der zweite DIMOS-Treiber-<br>Transistor (M <sub>2a</sub> ) sich im einge-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| $R_{2a}$               | erster unterer Spannungstei-<br>lerwiderstand;                                                                                                                                                                                                                                                                        |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| R <sub>1b</sub>        | zweiter oberer Spannungsteilerwiderstand;                                                                                                                                                                                                                                                                             |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| R <sub>2b</sub>        | zweiter unterer Spannungstei-<br>lerwiderstand;                                                                                                                                                                                                                                                                       | R <sub>DSON2b</sub>                                                                                   | schalteten Zustand befindet; Einschaltwiderstand des zwei-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| R <sub>3a</sub>        | dritter Widerstand des ersten<br>Hochvolt-Low-Drop-Reglers<br>( <b>HV-LDO</b> <sub>a</sub> );                                                                                                                                                                                                                         | ten DIMOS-Treiber-Tran-<br>sistors ( <b>M<sub>2b</sub>), des zweiten</b><br>Hochvolt-Low-Drop-Reglers |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| R <sub>3b</sub>        | dritter Widerstand des zweiten<br>Hochvolt-Low-Drop-Reglers<br>( <b>HV-LDO</b> <sub>b</sub> );                                                                                                                                                                                                                        |                                                                                                       | (HV-LDO <sub>b</sub> ) zwischen dessen<br>Source-Anschluss und des-<br>sen Drain-Anschluss, wenn<br>der zweite DIMOS-Treiber-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| R <sub>4a</sub>        | Pullup-Widerstand des ersten Hochvolt-Low-Drop-Reglers (HV-LDO <sub>a</sub> );                                                                                                                                                                                                                                        | SdT                                                                                                   | Transistor (M <sub>2b</sub> ) sich im einge-<br>schalteten Zustand befindet;<br>Stand der Technik;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| R <sub>4b</sub>        | Pullup-Widerstand des zweiten Hochvolt-Low-Drop-Reglers ( <b>HV-LDO</b> <sub>b</sub> );                                                                                                                                                                                                                               | T <sub>1a</sub>                                                                                       | erste Zeitkonstante der ersten Regelschleife des ersten Hochvolt-Low-Drop-Reglers (HV-LDO <sub>a</sub> ) zur Regelung des ersten Transistors (M <sub>1a</sub> ) des ersten Hochvolt-Low-Drop-Reglers (HV-LDO <sub>a</sub> ), die niedriger ist als die zweite Zeitkonstante (τ <sub>2a</sub> ) der zweiten Regelschleife des ersten Hochvolt-Low-Drop-Reglers (HV-LDO <sub>a</sub> ); zweite Zeitkonstante der zweiten Regelschleife des ersten Hochvolt-Low-Drop-Reglers (HV-LDO <sub>a</sub> ) zur Regelung des zweiten Transistors (M <sub>2a</sub> ) des ersten Hochvolt-Low-Drop-Reglers (HV-LDO <sub>a</sub> ), die höher ist als die erste Zeitkonstante (τ <sub>1a</sub> ) der ersten Regelschleife des ersten Hochvolt-Low-Drop-Reglers (HV-LDO <sub>a</sub> ); |  |

| R <sub>DSON:MDRV</sub> | Einschaltwiderstand des Ausgangstreibertransistors (M <sub>DRV</sub> ) des Hochvolt-Low-Drop-Reglers (HV-LDO <sub>a</sub> ) zwischen dessen Source-Anschluss und dessen Drain-Anschluss, wenn der Ausgangstreibertransistor (M <sub>DRV</sub> ) sich im eingeschalteten Zustand befindet (siehe auch <b>Fig. 1</b> ); |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| R <sub>DSON1a</sub>    | Einschaltwiderstand des ersten Transistors (M <sub>1a</sub> ) des ersten Hochvolt-Low-Drop-Reglers (HV-LDO <sub>a</sub> ) zwischen dessen Source-Anschluss und dessen Drain-Anschluss, wenn der erste Transistor (M <sub>1a</sub> ) sich im eingeschalteten Zustand befindet (siehe auch Fig. 2);                     |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

T<sub>1b</sub>