## (19)中华人民共和国国家知识产权局

# (12)发明专利

(10)授权公告号 CN 107316899 B (45)授权公告日 2020.08.28

*H01L* 29/78(2006.01) *H01L* 21/336(2006.01)

审查员 卢振宇

(21)申请号 201710576671.6

(22)申请日 2017.07.14

(65)同一申请的已公布的文献号 申请公布号 CN 107316899 A

(43)申请公布日 2017.11.03

(73)专利权人 南京溧水高新创业投资管理有限 公司

地址 210000 江苏省南京市溧水经济开发 区柘塘街道福田路科创大厦

(72)发明人 何春晖

(74)专利代理机构 深圳峰诚志合知识产权代理 有限公司 44525

代理人 李明香

(51) Int.CI.

H01L 29/06(2006.01)

#### (54)发明名称

半超结器件及其制造方法

#### (57)摘要

本发明提供了一种半超结器件及其制造方 法。所述半超结器件包括N型衬底、形成于N型衬 底表面的三层N型外延、贯穿所述第三层N型外延 且延伸至所述第二层N型外延中的第一、第二P型 注入区域、形成于所述第一P、第二P型注入区域 表面的沟槽、形成于所述第一P、第二P型注入区 域的沟槽中的第一氧化层、形成于所述第一P、第 二P型注入区域的沟槽中第一氧化层表面的第一 多晶硅、形成于所述第三层N型外延表面的第三、 第四及第五P型注入区域、形成于所述第三、第四 及第五P型注入区域表面的第一、第二及第三N型 注入区域、第二氧化层、第二多晶硅、介质层、形 四 成于所述介质层上的第一金属层;及形成于所述 N型衬底远离所述第一层N型外延下表面的第二 金属层。

权利要求书3页 说明书6页 附图8页

107316899 S

1.一种半超结器件,其特征在于,所述半超结器件包括:

N型衬底:

设置于所述N型衬底表面的第一层N型外延;

设置于所述第一层N型外延表面的第二层N型外延;

设置于所述第二层N型外延表面的第三层N型外延;

贯穿所述第三层N型外延且延伸至所述第二层N型外延中的第一P型注入区域;

贯穿所述第三层N型外延且延伸至所述第二层N型外延中的第二P型注入区域;

形成于所述第一P、第二P型注入区域表面的沟槽:

形成于所述第一P、第二P型注入区域的沟槽中的第一氧化层;

形成于所述第一P、第二P型注入区域的沟槽中第一氧化层表面的第一多晶硅;

形成于所述第三层N型外延、所述第一至第二P型注入区域上的第二氧化层;

形成于所述第二氧化层上的第二多晶硅;

形成于所述第二多晶硅上的介质层;

形成于所述介质层上的第一金属层:及

形成于所述N型衬底远离所述第一层N型外延的第二金属层;

所述半超结器件还包括:

形成于所述第三层N型外延表面的第三、第四及第五P型注入区域:

形成于所述第三P型注入区域表面的第一N型注入区域;

形成于所述第四P型注入区域表面的第二N型注入区域;及

形成于所述第五P型注入区域表面的第三N型注入区域:

其中,所述第一P型注入区域位于所述第三P型注入区域与所述第四P型注入区域之间, 所述第二P型注入区域位于所述第四P型注入区域与所述第五P型注入区域之间:

所述介质层包括第一通孔、第二通孔、第三通孔,所述第一金属层通过所述第一通孔连接所述第三P型注入区域,所述第一金属层通过所述第二通孔连接所述第四P型注入区域, 所述第一金属层通过所述第三通孔连接所述第五P型注入区域;

所述第二N型注入区域的数量为两个,所述第二通孔中的第一金属层对应并接触所述两个第二N型注入区域之间的第四P型注入区域,所述第二通孔中的第一金属层还部分接触所述两个第二N型注入区域;所述第三N型注入区域的数量为两个,所述第三通孔中的第一金属层对应并接触所述两个第三N型注入区域之间的第五P型注入区域,所述第三通孔中的第一金属层还部分接触所述两个第三N型注入区域。

- 2.如权利要求1所述的半超结器件,其特征在于,所述第一通孔中的第一金属层与所述第一N型注入区域部分接触,所述第三P型注入区域与所述第一P型注入区域之间的第二氧化层与所述第一N型注入区域部分接触。

- 3.一种半超结器件的制造方法,其包括如下步骤:

提供N型衬底,所述N型衬底表面依序形成有第一层N型外延与第二层N型外延,使用第一光刻胶作为掩膜,形成第一注入窗口与第二注入窗口,通过所述第一注入窗口与所述第二注入窗口进行P型注入形成位于所述第二层N型外延表面的第一P型注入区域与第二P型注入区域;

去除所述第一光刻胶,在所述第二层N型外延表面形成第三层N型外延;

在所述第三层N型外延表面形成氧化硅层,使用第二光刻胶作为掩膜,干法刻蚀所述氧化硅层形成第三注入窗口与第四注入窗口,其中所述第三注入窗口对应所述第二层N型外延表面的第一P型注入区域,所述第四注入窗口对应所述第二层N型外延表面的第二P型注入区域:

去除所述第二光刻胶,干法刻蚀所述第三层N型外延从而在所述第三层N型外延表面形成分别对应所述第一与所述第二P型注入区域的两个沟槽;

利用所述两个沟槽进行垂直与倾斜P型离子注入,使得所述两个沟槽壁具有P型离子; 在所述两个沟槽表面形成第一氧化层;

通过进行热退火使得所述两个沟槽壁的P型离子被激活与推进,进而形成贯穿所述第三层N型外延且与所述两个沟槽对应得第一P型注入区域与第二P型注入区域,其中,所述贯穿所述第三层N型外延的第一P型注入区域与所述第二层N型外延表面的第一P型注入区域相接,所述贯穿所述第三层N型外延的第二P型注入区域与所述第二层N型外延表面的第二P型注入区域相接;

在所述氧化硅层及所述沟槽中的第一氧化层表面形成第一多晶硅;

干法刻蚀去除所述第三层N型外延上的第一多晶硅,所述两个沟槽中的第一多晶硅被保留:

湿法刻蚀去除所述氧化硅层,在所述第三层N型外延、所述第一、第二P型注入区域、所述第一氧化层及所述第一多晶硅上依序形成第二氧化层与第二多晶硅;

在所述第一及第二氧化层、所述第二多晶硅上形成介质层;

在所述介质层上形成第一金属层:及

在所述N型衬底远离所述第一层N型外延的表面形成第二金属层;

使用第三光刻胶作为掩膜,干法刻蚀所述第二氧化层和第二多晶硅形成贯穿所述第二氧化层与第二多晶硅的第一至第五开口,其中,所述第一开口与所述第二开口分别对应所述第一P型注入区域与所述第二P型注入区域,所述第一开口位于所述第三开口与所述第四开口之间,所述第二开口位于所述第四开口与所述第五开口之间;

去除第三光刻胶,通过所述第三、第四及第五开口对所述第三层N型外延进行P型离子注入,进行热退火对经由所述第三至第五开口注入所述第三层N型外延的P型离子注入进行激活与推进,进而形成第三P型注入区域、第四P型注入区域与第五P型注入区域;及

使用第四光刻胶作为掩膜,对所述第三至第五P型注入区域进行N型离子注入,从而在所述第三P型注入区域表面形成第一N型注入区域,在所述第四P型注入区域表面形成第二N型注入区域,在所述第五P型注入区域表面形成第三N型注入区域;

其中,所述第一P型注入区域位于所述第三P型注入区域与所述第四P型注入区域之间, 所述第二P型注入区域位于所述第四P型注入区域与所述第五P型注入区域之间。

- 4.如权利要求3所述的半超结器件的制造方法,其特征在于,所述方法还包括在所述介质层中形成第一通孔、第二通孔、第三通孔,所述第一金属层通过所述第一通孔连接所述第三P型注入区域,所述第一金属层通过所述第二通孔连接所述第四P型注入区域,所述第一金属层通过所述第三通孔连接所述第五P型注入区域。

- 5.如权利要求4所述的半超结器件的制造方法,其特征在于,所述第一通孔中的第一金属层与所述第一N型注入区域部分接触,所述第三P型注入区域与所述第一P型注入区域之

间的第二氧化层与所述第一N型注入区域部分接触。

6.如权利要求5所述的半超结器件的制造方法,其特征在于,所述第二N型注入区域的数量为两个,所述第二通孔中的第一金属层对应并接触所述两个第二N型注入区域之间的第四P型注入区域,所述第二通孔中的第一金属层还部分接触所述两个第二N型注入区域;所述第三N型注入区域的数量为两个,所述第三通孔中的第一金属层对应并接触所述两个第三N型注入区域之间的第五P型注入区域,所述第三通孔中的第一金属层还部分接触所述两个第三N型注入区域。

1/6 页

# 半超结器件及其制造方法

#### 【技术领域】

[0001] 本发明涉及半导体器件技术领域,特别地,涉及一种半超结器件及其制造方法。

#### 【背景技术】

[0002] 超结/半超结器件,如沟槽型垂直双扩散场效应晶体管(VDMOS)的漏源两极分别在器件的两侧,使电流在器件内部垂直流通,增加了电流密度,改善了额定电流,单位面积的导通电阻也较小,是一种用途非常广泛的功率器件。

[0003] 传统功率MOSFET通常采用VDMOS结构,为了承受高耐压,需降低漂移区掺杂浓度或者增加漂移区厚度,这带来的直接后果是导通电阻急剧增大。一般传统功率MOSFET的导通电阻与击穿电压呈2.5次方关系,这个关系被称为"硅极限"。"超结"VDMOS基于电荷补偿原理,使器件的导通电阻与击穿电压呈1.32次方关系,很好地解决了导通电阻和击穿电压之间的矛盾。和传统功率VDMOS结构相比,超结MOSFET采用交替的P-N-结构替代传统功率器件中低掺杂漂移层作为电压维持层。超结MOSFET的本质是利用在漂移区中插入的P区(对N沟器件而言)所产生的电场对N区进行电荷补偿,达到提高击穿电压并降低导通电阻的目的。

[0004] 超结MOSFET的是利用复合缓冲层里面交替的N柱和P柱进行电荷补偿,使P区和N区相互耗尽,形成理想的平顶电场分布和均匀的电势分布,从而达到提高击穿电压并降低导通电阻的目的。要达到理想的效果,其前提条件就是电荷平衡。因此,超结技术从诞生开始,它的制造工艺就是围绕如何制造电荷平衡的N柱和P柱进行的。目前使用的制造技术主要有:多次外延和注入技术,深槽刻蚀和填槽技术。然而,如何降低超结/半超结器件的制造成本是业界的一个重要课题。

#### 【发明内容】

[0005] 本发明的其中一个目的在于为解决上述问题而提供一种半超结器件及其制造方法。

[0006] 一种半超结器件,其包括:

[0007] N型衬底;

[0008] 设置于所述N型衬底表面的第一层N型外延;

[0009] 设置于所述第一层N型外延表面的第二层N型外延;

[0010] 设置于所述第二层N型外延表面的第三层N型外延;

[0011] 贯穿所述第三层N型外延且延伸至所述第二层N型外延中的第一P型注入区域;

[0012] 贯穿所述第三层N型外延且延伸至所述第二层N型外延中的第二P型注入区域:

[0013] 形成于所述第一P、第二P型注入区域表面的沟槽;

[0014] 形成于所述第一P、第二P型注入区域的沟槽中的第一氧化层;

[0015] 形成于所述第一P、第二P型注入区域的沟槽中第一氧化层表面的第一多晶硅;

[0016] 形成于所述第三层N型外延、所述第一至第二P型注入区域上的第二氧化层;

[0017] 形成于所述第二氧化层上的第二多晶硅;

- [0018] 形成于所述第二多晶硅上的介质层;

- [0019] 形成于所述介质层上的第一金属层:及

- [0020] 形成于所述N型衬底远离所述第一层N型外延的第二金属层。

- [0021] 在一种实施方式中,所述半超结器件还包括:

- [0022] 形成于所述第三层N型外延表面的第三、第四及第五P型注入区域;

- [0023] 形成于所述第三P型注入区域表面的第一N型注入区域;

- [0024] 形成于所述第四P型注入区域表面的第二N型注入区域:及

- [0025] 形成于所述第五P型注入区域表面的第三N型注入区域;

[0026] 其中,所述第一P型注入区域位于所述第三P型注入区域与所述第四P型注入区域 之间,所述第二P型注入区域位于所述第四P型注入区域与所述第五P型注入区域之间。

[0027] 在一种实施方式中,所述介质层包括第一通孔、第二通孔、第三通孔,所述第一金属层通过所述第一通孔连接所述第三P型注入区域,所述第一金属层通过所述第二通孔连接所述第四P型注入区域,所述第一金属层通过所述第三通孔连接所述第五P型注入区域。

[0028] 在一种实施方式中,所述第一通孔中的第一金属层与所述第一N型注入区域部分接触,所述第三P型注入区域与所述第一P型注入区域之间的第二氧化层与所述第一N型注入区域部分接触。

[0029] 在一种实施方式中,所述第二N型注入区域的数量为两个,所述第二通孔中的第一金属层对应并接触所述两个第二N型注入区域之间的第四P型注入区域,所述第二通孔中的第一金属层还部分接触所述两个第二N型注入区域;所述第三N型注入区域的数量为两个,所述第三通孔中的第一金属层对应并接触所述两个第三N型注入区域之间的第五P型注入区域,所述第三通孔中的第一金属层还部分接触所述两个第三N型注入区域。

[0030] 一种半超结器件的制造方法,其包括如下步骤:

[0031] 提供N型衬底,所述N型衬底表面依序形成有第一层N型外延与第二层N型外延,使用第一光刻胶作为掩膜,形成第一注入窗口与第二注入窗口,通过所述第一注入窗口与所述第二注入窗口进行P型注入形成位于所述第二层N型外延表面的第一P型注入区域与第二P型注入区域;

[0032] 去除所述第一光刻胶,在所述第二层N型外延表面形成第三层N型外延;

[0033] 在所述第三层N型外延表面形成氧化硅层,使用第二光刻胶作为掩膜,干法刻蚀所述氧化硅层形成第三注入窗口与第四注入窗口,其中所述第三注入窗口对应所述第二层N型外延表面的第一P型注入区域,所述第四注入窗口对应所述第二层N型外延表面的第二P型注入区域;

[0034] 去除所述第二光刻胶,干法刻蚀所述第三层N型外延从而在所述第三层N型外延表面形成分别对应所述第一与所述第二P型注入区域的两个沟槽;

[0035] 利用所述两个沟槽进行垂直与倾斜P型离子注入,使得所述两个沟槽壁具有P型离子;

[0036] 在所述两个沟槽表面形成第一氧化层;

[0037] 通过进行热退火使得所述两个沟槽壁的P型离子被激活与推进,进而形成贯穿所述第三层N型外延且与所述两个沟槽对应得第一P型注入区域与第二P型注入区域,其中,所述贯穿所述第三层N型外延的第一P型注入区域与所述第二层N型外延表面的第一P型注入

区域相接,所述贯穿所述第三层N型外延的第二P型注入区域与所述第二层N型外延表面的第二P型注入区域相接:

[0038] 在所述氧化硅层及所述沟槽中的第一氧化层表面形成第一多晶硅;

[0039] 干法刻蚀去除所述第三层N型外延上的第一多晶硅,所述两个沟槽中的第一多晶硅被保留;

[0040] 湿法刻蚀去除所述氧化硅层,在所述第三层N型外延、所述第一、第二P型注入区域、所述第一氧化层及所述第一多晶硅上依序形成第二氧化层与第二多晶硅;

[0041] 在所述第一及第二氧化层、所述第二多晶硅上形成介质层;

[0042] 在所述介质层上形成第一金属层;及

[0043] 在所述N型衬底远离所述第一层N型外延的表面形成第二金属层。

[0044] 在一种实施方式中,所述方法还包括以下步骤:

[0045] 使用第三光刻胶作为掩膜,干法刻蚀所述第二氧化层和第二多晶硅形成贯穿所述第二氧化层与第二多晶硅的第一至第五开口,其中,所述第一开口与所述第二开口分别对应所述第一P型注入区域与所述第二P型注入区域,所述第一开口位于所述第三开口与所述第四开口之间,所述第二开口位于所述第四开口与所述第五开口之间;

[0046] 去除第三光刻胶,通过所述第三、第四及第五开口对所述第三层N型外延进行P型离子注入,进行热退火对经由所述第三至第五开口注入所述第三层N型外延的P型离子注入进行激活与推进,进而形成所述第三P型注入区域、第四P型注入区域与第五P型注入区域;及

[0047] 使用第四光刻胶作为掩膜,对所述第三至第五P型注入区域进行N型离子注入,从而在所述第三P型注入区域表面形成第一N型注入区域,在所述第四P型注入区域表面形成第二N型注入区域,在所述第五P型注入区域表面形成第三N型注入区域;

[0048] 其中,所述第一P型注入区域位于所述第三P型注入区域与所述第四P型注入区域 之间,所述第二P型注入区域位于所述第四P型注入区域与所述第五P型注入区域之间。

[0049] 在一种实施方式中,所述方法还包括在所述介质层中形成第一通孔、第二通孔、第三通孔,所述第一金属层通过所述第一通孔连接所述第三P型注入区域,所述第一金属层通过所述第二通孔连接所述第四P型注入区域,所述第一金属层通过所述第三通孔连接所述第五P型注入区域。

[0050] 在一种实施方式中,所述第一通孔中的第一金属层与所述第一N型注入区域部分接触,所述第三P型注入区域与所述第一P型注入区域之间的第二氧化层与所述第一N型注入区域部分接触。

[0051] 在一种实施方式中,所述第二N型注入区域的数量为两个,所述第二通孔中的第一金属层对应并接触所述两个第二N型注入区域之间的第四P型注入区域,所述第二通孔中的第一金属层还部分接触所述两个第二N型注入区域;所述第三N型注入区域的数量为两个,所述第三通孔中的第一金属层对应并接触所述两个第三N型注入区域之间的第五P型注入区域,所述第三通孔中的第一金属层还部分接触所述两个第三N型注入区域。

[0052] 本发明使用双层外延,进行P型注入形成埋层,进行第三层N型外延,再进行一次沟槽刻蚀,在沟槽下部形成第一及第二P型注入区域,然后在沟槽中形成第一氧化层作为隔离,并在沟槽上部填充第一多晶硅形成沟道,工艺简单,降低了器件制造成本。

### 【附图说明】

[0053] 为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图,其中:

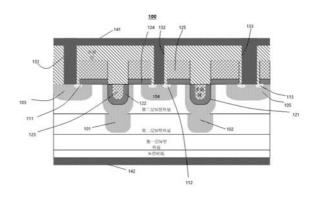

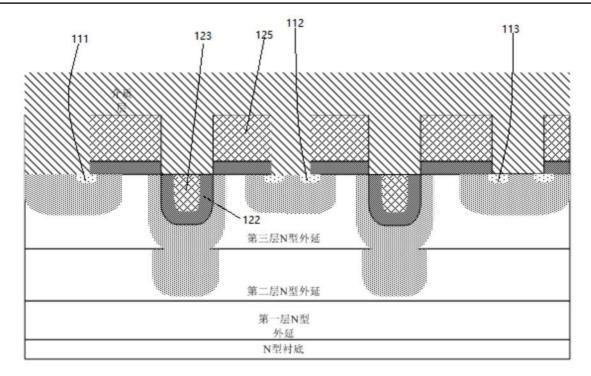

[0054] 图1为本发明一较佳实施方式的半超结器件的剖面结构示意图。

[0055] 图2至图16是图1所示半超结器件的制造方法的各步骤的结构示意图。

[0056] 主要元件符号说明

[0057] 第一P型注入区域101;第二P型注入区域102;第三P型注入区域103;第四P型注入区域104;第五P型注入区域105;第一N型注入区域111;第二N型注入区域112;第三N型注入区域113;沟槽121;第一氧化层122;第一多晶硅123;第二氧化层124;第二多晶硅125;第一金属层141;第二金属层142;第一通孔131;第二通孔132;第三通孔133;

#### 【具体实施方式】

[0058] 下面将对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

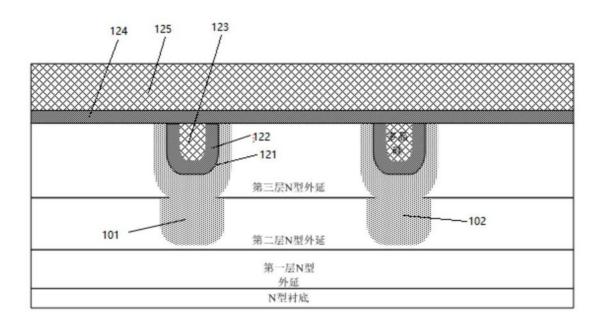

[0059] 请参阅图1,图1是本发明一较佳实施方式的半超结器件的结构示意图。所述半超结器件100包括:N型衬底;设置于所述N型衬底表面的第一层N型外延;设置于所述第一层N型外延表面的第三层N型外延;设置于所述第一层N型外延表面的第三层N型外延;贯穿所述第三层N型外延电的第一P型注入区域101;贯穿所述第三层N型外延且延伸至所述第二层N型外延中的第一P型注入区域101;贯穿所述第三层N型外延上延伸至所述第二层N型外延中的第一P型注入区域102;形成于所述第一P、第二P型注入区域101、102表面的沟槽121;形成于所述第一P、第二P型注入区域101、102的沟槽121中第一氧化层122表面的第一多晶硅123;形成于所述第三层N型外延表面的第三、第四及第五P型注入区域103、104、105;形成于所述第三P型注入区域111表面的第一N型注入区域111;形成于所述第四P型注入区域104表面的第二N型注入区域112;形成于所述第五P型注入区域105表面的第三N型注入区域104表面的第三N型注入区域112;形成于所述第一至第五P型注入区域101-105上的第二氧化层124;形成于所述第二氧化层124上的第二多晶硅125;形成于所述第二多晶硅上的介质层;形成于所述介质层上的第一金属层141;及形成于所述N型衬底远离所述第一层N型外延的第二金属层142。

[0060] 具体地,所述第一P型注入区域101位于所述第三P型注入区域103与所述第四P型注入区域104之间,所述第二P型注入区域102位于所述第四P型注入区域104与所述第五P型注入区域105之间。

[0061] 进一步地,所述介质层包括第一通孔131、第二通孔132、第三通孔131,所述第一金属层141通过所述第一通孔131连接所述第三P型注入区域103,所述第一金属层141通过所述第二通孔132连接所述第四P型注入区域104,所述第一金属层141通过所述第三通孔131连接所述第五P型注入区域105。

[0062] 其中,所述第一通孔131中的第一金属层141与所述第一N型注入区域111部分接触,所述第三P型注入区域103与所述第一P型注入区域101之间的第二氧化层124与所述第一N型注入区域111部分接触。

[0063] 所述第二N型注入区域112的数量为两个,所述第二通孔132中的第一金属层141对应并接触所述两个第二N型注入区域112之间的第四P型注入区域104,所述第二通孔132中的第一金属层141还部分接触所述两个第二N型注入区域112。

[0064] 所述第三N型注入区域113的数量为两个,所述第三通孔131中的第一金属层141对应并接触所述两个第三N型注入区域113之间的第五P型注入区域105,所述第三通孔131中的第一金属层141还部分接触所述两个第三N型注入区域113。

[0065] 请参阅图2至图16,其是图1所示半超结器件100的制造方法的各步骤的结构示意图。所述半超结器件100的制造方法如下步骤S1至S16。

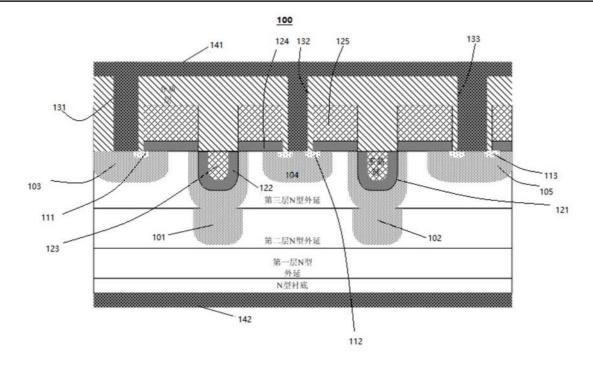

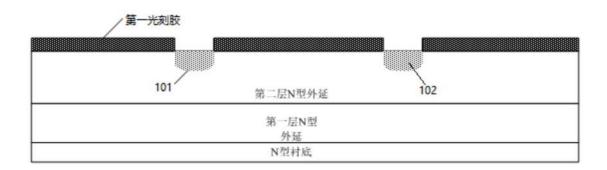

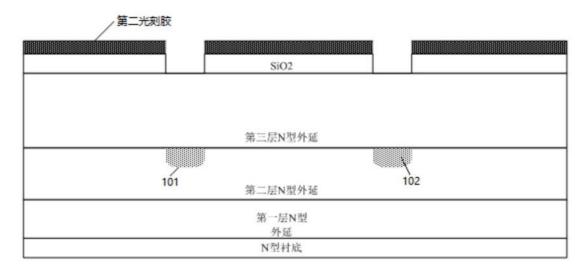

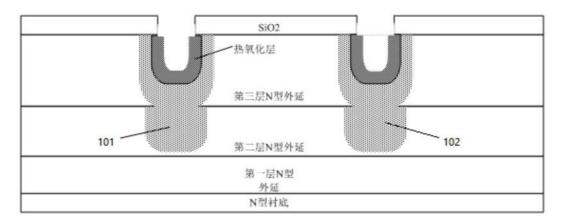

[0066] 步骤S1,请参阅图2,提供N型衬底,所述N型衬底表面依序形成有第一层N型外延与第二层N型外延,使用第一光刻胶作为掩膜,形成第一注入窗口与第二注入窗口,通过所述第一注入窗口与所述第二注入窗口进行P型注入形成位于所述第二层N型外延表面的第一P型注入区域101与第二P型注入区域102。

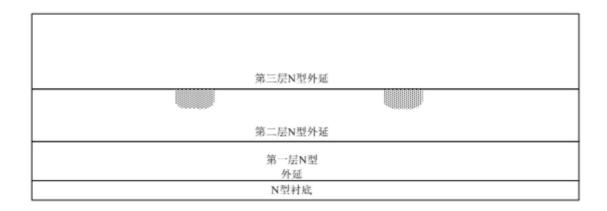

[0067] 步骤S2,请参阅图3,去除所述第一光刻胶,在所述第二层N型外延表面形成第三层N型外延。

[0068] 步骤S3,请参阅图4,在所述第三层N型外延表面形成氧化硅层,使用第二光刻胶作为掩膜,干法刻蚀所述氧化硅层形成第三注入窗口与第四注入窗口,其中所述第三注入窗口对应所述第二层N型外延表面的第一P型注入区域101,所述第四注入窗口对应所述第二层N型外延表面的第二P型注入区域102。

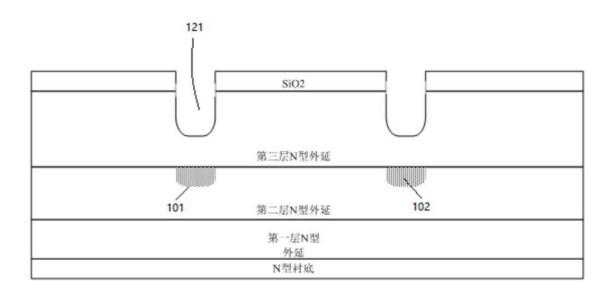

[0069] 步骤S4,请参阅图5,去除所述第二光刻胶,干法刻蚀所述第三层N型外延从而在所述第三层N型外延表面形成分别对应所述第一与所述第二P型注入区域101、102的两个沟槽121。

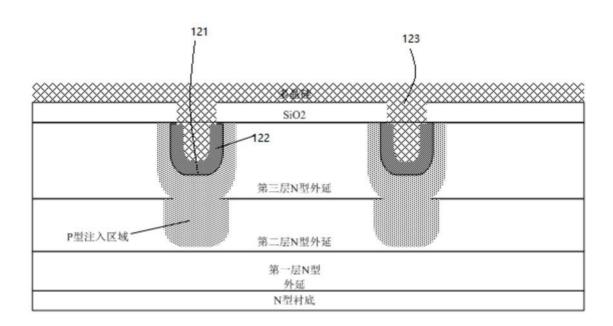

[0070] 步骤S5,请参阅图6,利用所述两个沟槽121进行垂直与倾斜P型离子注入,使得所述两个沟槽壁具有P型离子。

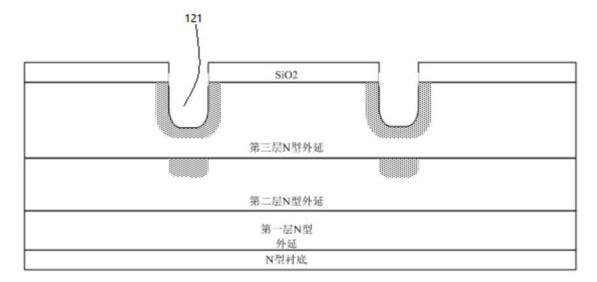

[0071] 步骤S6,请参阅图7,通过热氧化,在所述两个沟槽121表面形成第一氧化层122。

[0072] 步骤S7,请参阅图8,通过进行热退火使得所述两个沟槽壁的P型离子被激活与推进,进而形成贯穿所述第三层N型外延且与所述两个沟槽对应得第一P型注入区域101与第二P型注入区域102,其中,所述贯穿所述第三层N型外延的第一P型注入区域101与所述第二层N型外延表面的第一P型注入区域101相接,所述贯穿所述第三层N型外延的第二P型注入区域102与所述第二层N型外延表面的第二P型注入区域102相接。

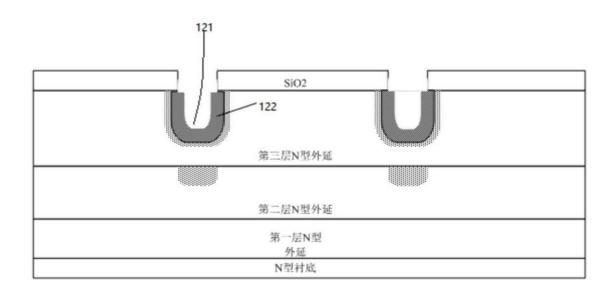

[0073] 步骤S8,请参阅图9,在所述氧化硅层及所述沟槽121中的第一氧化层122表面形成第一多晶硅123。

[0074] 步骤S9,请参阅图10,干法刻蚀去除所述第三层N型外延上的第一多晶硅123,所述两个沟槽121中的第一多晶硅123被保留。

[0075] 步骤S10,请参阅图11,湿法刻蚀去除所述氧化硅层,在所述第三层N型外延、所述第一、第二P型注入区域101、102、所述第一氧化层122及所述第一多晶硅123上依序形成第二氧化层124与第二多晶硅125。

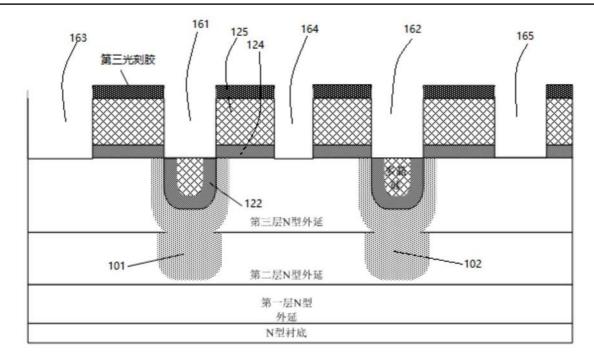

[0076] 步骤S11,请参阅图12,使用第三光刻胶作为掩膜,干法刻蚀所述第二氧化层124和第二多晶硅125形成贯穿所述第二氧化层124与第二多晶硅125的第一至第五开口161-165,其中,所述第一开口161与所述第二开口162分别对应所述第一P型注入区域101与所述第二P型注入区域102,所述第一开口161位于所述第三开口163与所述第四开口164之间,所述第二开口162位于所述第四开口164与所述第五开口165之间。

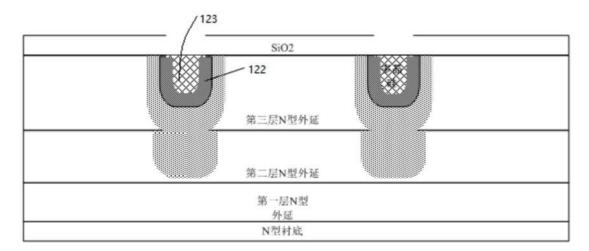

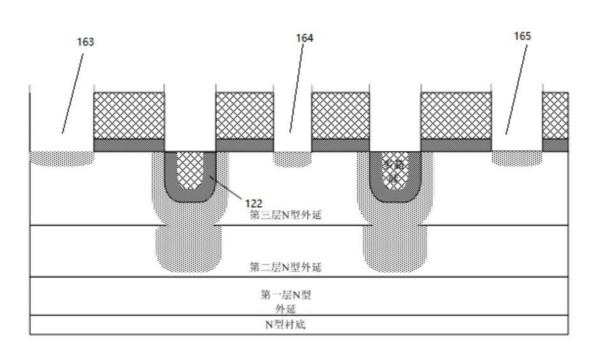

[0077] 步骤S12,请参阅图13及图14,去除第三光刻胶,通过所述第三、第四及第五开口163-165对所述第三层N型外延进行P型离子注入,进行热退火对经由所述第三至第五开口163-165注入所述第三层N型外延的P型离子注入进行激活与推进,进而形成所述第三P型注入区域103、第四P型注入区域104与第五P型注入区域105。

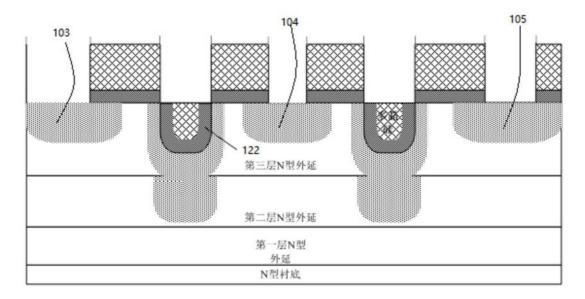

[0078] 步骤S13,请参阅图15,使用第四光刻胶作为掩膜,对所述第三至第五P型注入区域103、104、105进行N型离子注入,从而在所述第三P型注入区域103表面形成第一N型注入区域111,在所述第四P型注入区域104表面形成第二N型注入区域112,在所述第五P型注入区域105表面形成第三N型注入区域113。

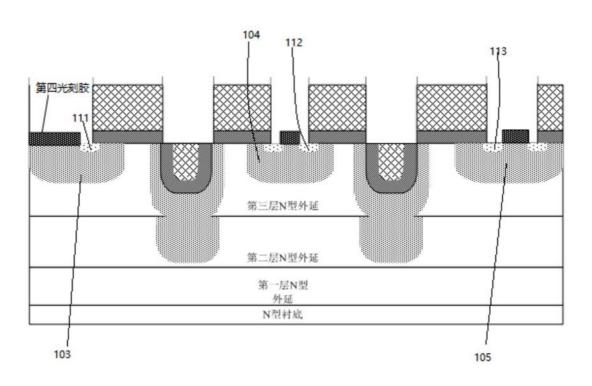

[0079] 步骤S14,请参阅图16及图1,在所述第一、第二及第三N型注入区域111、112、113、所述第一氧化层122、所述第一、第二多晶硅123、125上形成介质层。进一步地,在所述介质层中形成贯通的第一通孔161、第二通孔162及第三通孔163。

[0080] 步骤S15,请参阅图1,在所述介质层上形成第一金属层141。

[0081] 步骤S16,请参阅图1,在所述N型衬底远离所述第一层N型外延的表面形成第二金属层142。

[0082] 本发明使用双层外延,进行P型注入形成埋层,进行第三层N型外延,再进行一次沟槽121刻蚀,在沟槽121下部形成第一及第二P型注入区域101与102,然后在沟槽121中形成第一氧化层122作为隔离,并在沟槽121上部填充第一多晶硅123形成沟道,工艺简单,降低了器件制造成本。

[0083] 以上所述的仅是本发明的实施方式,在此应当指出,对于本领域的普通技术人员来说,在不脱离本发明创造构思的前提下,还可以做出改进,但这些均属于本发明的保护范围。

图1

图2

图3

图4

图5

图6

图7

# 图8

图9

图10

图11

图12

图13

图14

图15

图16