### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4482996号 (P4482996)

(45) 発行日 平成22年6月16日(2010.6.16)

(24) 登録日 平成22年4月2日(2010.4.2)

| (51) Int.Cl. |       |           | F 1  |       |      |

|--------------|-------|-----------|------|-------|------|

| G06T         | 11/00 | (2006.01) | GO6T | 11/00 | 100A |

| G06F         | 5/16  | (2006.01) | GO6F | 5/16  |      |

| G06T         | 1/60  | (2006.01) | GO6T | 1/60  | 450F |

| G09G         | 5/00  | (2006.01) | GO9G | 5/00  | 550M |

請求項の数 8 (全 21 頁)

(21) 出願番号 特願2000-21836 (P2000-21836) (22) 出願日 平成12年1月26日 (2000.1.26) (65) 公開番号 特開2001-209811 (P2001-209811A) (43) 公開日 平成13年8月3日 (2001.8.3) 審查請求日 平成18年11月15日 (2006.11.15)

(73)特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74)代理人 100094053

弁理士 佐藤 隆久

|(72)発明者 猿谷 武司

神奈川県横浜市保土ヶ谷区神戸町134番地 ソニー・エルエスアイ・デザイン株式

会社内

(72) 発明者 成田 篤史

東京都品川区北品川6丁目7番35号 ソ

二一株式会社内

審査官 伊知地 和之

最終頁に続く

# (54) 【発明の名称】データ記憶装置とその方法および画像処理装置

# (57)【特許請求の範囲】

### 【請求項1】

入力される複数系統のデータを順に記憶するデータ記憶手段と、

前記データ記憶手段に記憶されたデータの記憶順序を前記系統ごとに管理する記憶順序管理手段と、

各系統ごとのデータの出力要求に応じて、前記記憶順序管理手段に管理されている前記 系統ごとのデータの記憶順序に基づいて、当該要求された系統の前記記憶されているデー タを前記入力された順に読み出し出力する出力手段と

#### を有し、

前記記憶順序管理手段は、

前記データ記憶手段の未だ読み出されていないデータが記憶されている領域以外の空き領域の任意のアドレスを、入力されるデータを記憶する記憶アドレスとして生成する記憶アドレス生成手段と、

前記各系統ごとに、最後に入力され記憶されたデータに対する前記記憶アドレスを記憶するアドレス記憶手段と、

前記データ記憶手段のアドレス空間に対応したアドレス空間を有し、各アドレスのデータとして、前記データ記憶手段の対応するアドレスに記憶されているデータと同一の系統の前記入力されるデータで、当該アドレスのデータの次に入力され記憶されたデータが記憶されている前記データ記憶手段のアドレスを記憶するテーブルと、

入力される任意の系統のデータが前記データ記憶手段の前記生成された記憶アドレス

に記憶された際に、前記テーブルの前記アドレス記憶手段に記憶されているアドレスに、 前記生成された記憶アドレスを記憶するテーブル更新手段と、

を有し、

前記記憶アドレス生成手段は、

前記データ記憶手段の各アドレスごとの当該アドレスに未だ読み出されていないデータが記憶されているか否かを示すフラグを記憶するフラグ記憶手段と、

前記記憶されているフラグに基づいて、前記データ記憶手段の前記空き領域を検出し、当該空き領域のいずれか1の領域のアドレスを前記記憶アドレスとして選択する記憶アドレス選択手段と、

新たに入力されるデータの記憶および前記出力手段による記憶されたデータの読み出 しに基づいて、前記フラグを更新するフラグ更新手段とを有し、

前記データ記憶手段は、前記記憶アドレス生成手段により生成されたアドレスに、前記入力される任意の系統のデータを記憶する

データ記憶装置。

# 【請求項2】

前記出力手段は、

前記各系統ごとに、前記データ記憶手段より最後にデータを読み出したアドレスの、 前記テーブルに記憶されている前記記憶アドレスを、読み出しアドレスとして記憶する読 み出しアドレス記憶手段と、

任意の前記系統のデータの出力要求があった場合に、前記データ記憶手段の前記読み出しアドレス記憶手段に記憶されている当該系統の前記読み出しアドレスのデータを読み出し出力するデータ読み出し手段と、

を有する請求項1に記載のデータ記憶装置。

#### 【請求項3】

前記データ記憶手段、前記記憶順序管理手段および前記出力手段は、半導体集積回路と して構成されている

請求項1に記載のデータ記憶装置。

#### 【請求項4】

前記データ記憶手段は、データの記憶と読み出しを同サイクル中に行うことができるデュアルポートメモリを有する

請求項3に記載のデータ記憶装置。

#### 【請求項5】

データ記憶手段と、記憶順序管理手段と、出力手段とを有するデータ記憶装置のデータ記憶方法であって、

入力される複数系統のデータをメモリに記憶する第1の工程と、

前記記憶されたデータの記憶順序を前記系統ごとに管理する第2の工程と、

各系統ごとのデータの出力要求に応じて、前記管理されている前記系統ごとのデータの記憶順序に基づいて、当該要求された系統の前記記憶されているデータを前記入力された順に読み出し出力する第3の工程と、

を有し、

前記第2の工程は、

前記各系統ごとに、最後に入力され記憶されたデータに対する前記記憶アドレスを記憶しておく第4の工程と、

任意の系統のデータが入力された場合に、前記メモリの未だ読み出されていないデータが記憶されている領域以外の空き領域の任意のアドレスを、入力されるデータを記憶する記憶アドレスとして生成する第5の工程と、

前記データ記憶手段のアドレス空間に対応したアドレス空間を有し、各アドレスのデータとして、前記データ記憶手段の対応するアドレスに記憶されているデータと同一の系統の前記入力されるデータで、当該アドレスのデータの次に入力され記憶されたデータが記憶されている前記データ記憶手段のアドレスを記憶するテーブルの、前記記憶されてい

10

20

30

40

る当該系統の最後に入力され記憶されたデータに対する記憶アドレスに、<u>当該入力されるデータが前記メモリの前記生成された記憶アドレスに記憶された際に、</u>当該生成された記憶アドレスを記憶する第6の工程と、

を有し、

前記第4の工程は、

前記メモリの各アドレスに未だ読み出されていないデータが記憶されているか否か を示すフラグを設定しておく第7の工程と、

前記記憶されているフラグに基づいて前記メモリの前記空き領域を検出する第8の 工程と、

当該空き領域のいずれか1の領域のアドレスを前記記憶アドレスとして選択する第9の工程と、

を有するデータ記憶方法。

#### 【請求項6】

任意の表示用画像データを生成する画像生成手段と、

前記生成された表示用画像データを記憶する画像メモリと、

前記記憶された表示用画像データより所望の領域のデータを読み出し表示用画面データとして出力する出力手段と

を有し、

前記画像メモリは、

入力される複数系統のデータを順に記憶するデータ記憶手段と、

前記データ記憶手段に記憶されたデータの記憶順序を前記系統ごとに管理する記憶順序管理手段と、

各系統ごとのデータの出力要求に応じて、前記記憶順序管理手段に管理されている前記系統ごとのデータの記憶順序に基づいて、当該要求された系統の前記記憶されているデータを前記入力された順に読み出し出力する出力手段と

を有し、

前記記憶順序管理手段は、

前記データ記憶手段の未だ読み出されていないデータが記憶されている領域以外の空き領域の任意のアドレスを、入力されるデータを記憶する記憶アドレスとして生成する記憶アドレス生成手段と、

前記各系統ごとに、最後に入力され記憶されたデータに対する前記記憶アドレスを 記憶するアドレス記憶手段と、

前記データ記憶手段のアドレス空間に対応したアドレス空間を有し、各アドレスのデータとして、前記データ記憶手段の対応するアドレスに記憶されているデータと同一の系統の前記入力されるデータで、当該アドレスのデータの次に入力され記憶されたデータが記憶されている前記データ記憶手段のアドレスを記憶するテーブルと、

入力される任意の系統のデータが前記データ記憶手段の前記生成された記憶アドレスに記憶された際に、前記テーブルの前記アドレス記憶手段に記憶されているアドレスに、前記生成された記憶アドレスを記憶するテーブル更新手段と、

を有し、

前記記憶アドレス生成手段は、

前記データ記憶手段の各アドレスごとの当該アドレスに未だ読み出されていないデータが記憶されているか否かを示すフラグを記憶するフラグ記憶手段と、

前記記憶されているフラグに基づいて、前記データ記憶手段の前記空き領域を検出し、当該空き領域のいずれか1の領域のアドレスを前記記憶アドレスとして選択する記憶アドレス選択手段と、

新たに入力されるデータの記憶および前記出力手段による記憶されたデータの読み出しに基づいて、前記フラグを更新するフラグ更新手段とを有し、

前記データ記憶手段は、前記記憶アドレス生成手段により生成されたアドレスに、前記入力される任意の系統のデータを記憶する

10

20

30

40

画像処理装置。

### 【請求項7】

前記画像生成手段は、

任意の3次元立体モデルが、少なくとも3次元位置情報を有する頂点によって示される基本多角形の集合として示されている3次元画像データの、当該基本多角形の前記頂点に対して所定の座標変換を行う座標変換手段と、

前記基本多角形の頂点のデータに基づいて、当該基本多角形の画素データを生成する 画素データ生成手段と、

前記生成された画素データに対して、所望のテクスチャパタンを用いてテクスチャマッピングし、表示用3次元画像データを前記表示用画像データとして生成するテクスチャマッピング手段と

を有する請求項6に記載の画像処理装置。

### 【請求項8】

前記出力手段は、

前記各系統ごとに、前記データ記憶手段より最後にデータを読み出したアドレスの、前記テーブルに記憶されている前記記憶アドレスを、読み出しアドレスとして記憶する読み出しアドレス記憶手段と、

任意の前記系統のデータの出力要求があった場合に、前記データ記憶手段の前記読み出しアドレス記憶手段に記憶されている当該系統の前記読み出しアドレスのデータを読み出し出力するデータ読み出し手段と、

を有する請求項7に記載の画像処理装置。

### 【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は、複数系統のデータに対する先入れ先出し形式(以降、FIFO(First In First Out)形式と言う。)のデータ記憶装置とデータ記憶方法、および、そのデータ記憶装置を用いて表示用画像の生成を効率よく行うことのできる画像処理装置に関する。

[00002]

# 【従来の技術】

入力したデータを入力した順に読み出すいわゆるFIFOメモリは、種々の電子回路において広く使用されている。特に近年、あらゆる電子機器において処理速度の向上が図られているため、結果的に各処理部間でのデータの処理速度に差異が生じたり、適切に同期をとってデータを転送することが難しくなるなどの問題が生じており、これを解決するために、各処理部間に緩衝手段としてFIFOメモリを設けることが多くなっている。

たとえば、CAD装置やゲーム機器などに用いられる3次元画像を生成する画像処理装置などは、座標変換やテクスチャマッピング、各画素に対する特殊効果処理、生成した画像の高速表示など、多数の画素に対して高速に処理を行う各種の処理部が順次接続されて構成されている。そして、これらの各処理部の間におけるデータ転送を高速かつ適切に行うために、FIFOメモリが多数使用されている。

### [0003]

【発明が解決しようとする課題】

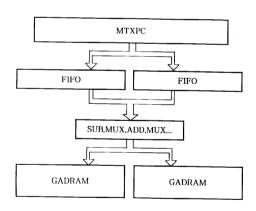

ところで、たとえばそのような画像処理装置の各構成部間においては、複数種類のデータが必要に応じて転送される場合が多い。特に、画像データのみならず制御データまでをも含めると、特定の1種類のデータのみが転送されるということは稀と考えられる。そのような場合に、これまでは、たとえば図7に示すように、そのデータの種類(データの系統と言う場合もある。)に応じて複数系統のFIFOメモリが並列に設けられていた。

しかし、そのように複数のFIFOメモリを並列に設けると、各系統ごとにマージンを確保しなければならなかったり、共通的な信号処理が多いにも係わらず制御部を独立して設けることになるなど、回路を効率よく利用することができない、すなわち、必要以上に回路規模が大きくなるという問題がある。

10

20

30

40

20

30

40

50

特に、このような回路は、半導体集積回路として実現する場合が多いため、回路規模、換言すれば回路のゲート規模を少しでも小さくしたいという要望もある。

#### [0004]

したがって本発明の目的は、より小さい回路規模で複数系統のデータに対して適切にFIFO機能を提供できるデータ記憶装置とその方法を提供することにある。

また、本発明の他の目的は、より小さい回路規模で各処理手段でのデータの転送が適切に行え、これにより所望の画像処理を効率よく行えるような画像処理装置を提供することにある。

### [0005]

前記課題を解決するために、本発明のデータ記憶装置は、入力される複数系統のデータ を順に記憶するデータ記憶手段と、前記データ記憶手段に記憶されたデータの記憶順序を 前記系統ごとに管理する記憶順序管理手段と、各系統ごとのデータの出力要求に応じて、 前記記憶順序管理手段に管理されている前記系統ごとのデータの記憶順序に基づいて、当 該要求された系統の前記記憶されているデータを前記入力された順に読み出し出力する出 力手段とを有し、前記記憶順序管理手段は、前記データ記憶手段の未だ読み出されていな いデータが記憶されている領域以外の空き領域の任意のアドレスを、入力されるデータを 記憶する記憶アドレスとして生成する記憶アドレス生成手段と、前記各系統ごとに、最後 に入力され記憶されたデータに対する前記記憶アドレスを記憶するアドレス記憶手段と、 前記データ記憶手段のアドレス空間に対応したアドレス空間を有し、各アドレスのデータ として、前記データ記憶手段の対応するアドレスに記憶されているデータと同一の系統の 前記入力されるデータで、当該アドレスのデータの次に入力され記憶されたデータが記憶 されている前記データ記憶手段のアドレスを記憶するテーブルと、入力される任意の系統 のデータが前記データ記憶手段の前記生成された記憶アドレスに記憶された際に、前記テ ーブルの前記アドレス記憶手段に記憶されているアドレスに、前記生成された記憶アドレ スを記憶するテーブル更新手段と、を有し、前記記憶アドレス生成手段は、前記データ記 憶手段の各アドレスごとの当該アドレスに未だ読み出されていないデータが記憶されてい るか否かを示すフラグを記憶するフラグ記憶手段と、前記記憶されているフラグに基づい て、前記データ記憶手段の前記空き領域を検出し、当該空き領域のいずれか1の領域のア ドレスを前記記憶アドレスとして選択する記憶アドレス選択手段と、新たに入力されるデ ータの記憶および前記出力手段による記憶されたデータの読み出しに基づいて、前記フラ グを更新するフラグ更新手段とを有し、前記データ記憶手段は、前記記憶アドレス生成手 段により生成されたアドレスに、前記入力される任意の系統のデータを記憶する。

#### [0006]

第2の発明のデータ記憶方法は、データ記憶手段と、記憶順序管理手段と、出力手段と を有するデータ記憶装置のデータ記憶方法であって、入力される複数系統のデータをメモ リに記憶する第1の工程と、前記記憶されたデータの記憶順序を前記系統ごとに管理する 第2の工程と、各系統ごとのデータの出力要求に応じて、前記管理されている前記系統ご とのデータの記憶順序に基づいて、当該要求された系統の前記記憶されているデータを前 記入力された順に読み出し出力する第3の工程と、を有し、前記第2の工程は、前記各系 統ごとに、最後に入力され記憶されたデータに対する前記記憶アドレスを記憶しておく第 4の工程と、任意の系統のデータが入力された場合に、前記メモリの未だ読み出されてい ないデータが記憶されている領域以外の空き領域の任意のアドレスを、入力されるデータ を記憶する記憶アドレスとして生成する第5の工程と、前記データ記憶手段のアドレス空 間に対応したアドレス空間を有し、各アドレスのデータとして、前記データ記憶手段の対 応するアドレスに記憶されているデータと同一の系統の前記入力されるデータで、当該ア ドレスのデータの次に入力され記憶されたデータが記憶されている前記データ記憶手段の アドレスを記憶するテーブルの、前記記憶されている当該系統の最後に入力され記憶され たデータに対する記憶アドレスに、当該入力されるデータが前記メモリの前記生成された 記憶アドレスに記憶された際に、当該生成された記憶アドレスを記憶する第6の工程と、 を有し、前記第4の工程は、前記メモリの各アドレスに未だ読み出されていないデータが 記憶されているか否かを示すフラグを設定しておく第7の工程と、前記記憶されているフラグに基づいて前記メモリの前記空き領域を検出する第8の工程と、当該空き領域のいずれか1の領域のアドレスを前記記憶アドレスとして選択する第9の工程と、を有す<u>る。</u>

第3の発明の画像処理装置は、任意の表示用画像データを生成する画像生成手段と、前 記生成された表示用画像データを記憶する画像メモリと、前記記憶された表示用画像デー タより所望の領域のデータを読み出し表示用画面データとして出力する出力手段とを有し 、前記画像メモリは、入力される複数系統のデータを順に記憶するデータ記憶手段と、前 記データ記憶手段に記憶されたデータの記憶順序を前記系統ごとに管理する記憶順序管理 手段と、各系統ごとのデータの出力要求に応じて、前記記憶順序管理手段に管理されてい る前記系統ごとのデータの記憶順序に基づいて、当該要求された系統の前記記憶されてい るデータを前記入力された順に読み出し出力する出力手段とを有し、前記記憶順序管理手 段は、前記データ記憶手段の未だ読み出されていないデータが記憶されている領域以外の 空き領域の任意のアドレスを、入力されるデータを記憶する記憶アドレスとして生成する 記憶アドレス生成手段と、前記各系統ごとに、最後に入力され記憶されたデータに対する 前記記憶アドレスを記憶するアドレス記憶手段と、前記データ記憶手段のアドレス空間に 対応したアドレス空間を有し、各アドレスのデータとして、前記データ記憶手段の対応す るアドレスに記憶されているデータと同一の系統の前記入力されるデータで、当該アドレ スのデータの次に入力され記憶されたデータが記憶されている前記データ記憶手段のアド レスを記憶するテーブルと、入力される任意の系統のデータが前記データ記憶手段の前記 生成された記憶アドレスに記憶された際に、前記テーブルの前記アドレス記憶手段に記憶 されているアドレスに、前記生成された記憶アドレスを記憶するテーブル更新手段と、を 有し、前記記憶アドレス生成手段は、前記データ記憶手段の各アドレスごとの当該アドレ スに未だ読み出されていないデータが記憶されているか否かを示すフラグを記憶するフラ グ記憶手段と、前記記憶されているフラグに基づいて、前記データ記憶手段の前記空き領 域を検出し、当該空き領域のいずれか1の領域のアドレスを前記記憶アドレスとして選択 する記憶アドレス選択手段と、新たに入力されるデータの記憶および前記出力手段による 記憶されたデータの読み出しに基づいて、前記フラグを更新するフラグ更新手段とを有し 、前記データ記憶手段は、前記記憶アドレス生成手段により生成されたアドレスに、前記 入力される任意の系統のデータを記憶する。

[0013]

【発明の実施の形態】

本発明の一実施の形態について図1~図6を参照して説明する。

本実施の形態においては、家庭用ゲーム機などに適用され、任意の3次元物体モデルの 所望の3次元画像をディスプレイ上に高速に表示する3次元コンピュータグラフィックス システムを例示して、本発明を説明する。

[0014]

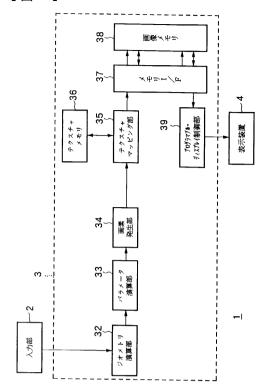

まず、その3次元コンピュータグラフィックスシステムの全体の構成および動作について図1を参照して説明する。

<u>この3次元コンピュータグラフィックスシステムは、立体モデルを単位図形である三角形(ポリゴン)の張り合わせとして表現しておき、このポリゴンを描画することで表示画面の各画素の色を決定しディスプレイに表示するポリゴンレンダリング処理を行うシステムである。</u>

また、3次元コンピュータグラフィックスシステム1においては、平面を表わす(x、y)座標のほかに、奥行きを表わすz座標を用いて3次元物体を表わし、またこのx、y、zの3つの座標で3次元空間内の任意の1点を特定する。

[0015]

<u>図1は、その3次元コンピュータグラフィックスシステム1の構成を示すブロック図で</u>ある。

3次元コンピュータグラフィックスシステム1は、入力部2、3次元画像生成装置3お

10

20

30

40

### よび表示装置4を有する。

また、3次元画像生成装置3は、ジオメトリ演算部32、パラメータ演算部33、画素発生部34、テクスチャマッピング部35、テクスチャメモリ36、メモリインターフェイス(I/F)37、画像メモリ38およびプログラマブル・ディスプレイ制御部39を有する。

# [0016]

まず、各部の構成・機能について説明する。

入力部2は、3次元画像生成装置3に対して、表示対象の立体モデルのデータを入力する。本実施の形態においては、3次元コンピュータグラフィックスシステム1は家庭用ゲーム機に適用されているので、入力部2は、その家庭用ゲーム機のゲーム自体を制御する主制御装置などに接続される。その主制御装置においては、ゲームの進行状況などに基づいて表示する画面を決定し、その画面表示に必要な立体モデルを選択し、その表示方法の情報を生成する。したがって入力部2は、これらの情報を、家庭用ゲーム機の主制御装置より受け取り、3次元画像生成装置3へ入力するのに適した形態に変換するなどして3次元画像生成装置3に入力する。

具体的には、入力部 2 は、前述したような表示する立体モデルのポリゴンデータを 3 次元画像生成装置 3 のジオメトリ演算部 3 2 に入力する。また、その入力されるポリゴンのデータは、各頂点の×, y, z座標データおよびカラー、透明度、テクスチャなどの付随データである。

### [0017]

ジオメトリ演算部 3 2 は、入力部 2 より入力されたポリゴンを、 3 次元空間中の所望の位置に配置させその位置におけるポリゴンデータを生成する。具体的には、ポリゴンの各項点(x、y、z)ごとに、並進変換、平行変換および回転変換などの幾何学的変換処理(ジオメトリ変換処理という場合もある)を行う。ジオメトリ変換処理を行ったポリゴンデータは、パラメータ演算部 3 3 に出力される。

### [0018]

パラメータ演算部 3 3 は、ジオメトリ演算部 3 2 から入力されたポリゴンのデータ、すなわち、ポリゴンの各頂点のデータに基づいて、画素発生部 3 4 においてポリゴン内部の画素データを発生するために必要なパラメータを求め、画素発生部 3 4 に出力する。具体的にはたとえば、カラー、奥行きおよびテクスチャの傾きの情報などを求める。

### [0019]

画素発生部34は、ジオメトリ演算部32でジオメトリ変換処理が行われたポリゴンデータ、および、パラメータ演算部33で求められたパラメータに基づいて、ポリゴンの各頂点間を線型補間してポリゴン内部およびエッジ部分の画素データを発生する。また画素発生回路34は、画素データの表示に対応した所定の2次元平面上でのアドレスの生成を行う。生成された画素データおよびアドレスは順次テクスチャマッピング部35に出力される。

### [0020]

テクスチャマッピング部35は、画素発生部34で生成された画素データに対して、テクスチャメモリ36に格納されているテクスチャデータを用いて、テクスチャマッピング処理を行う。テクスチャマッピング処理を行った画素データおよびアドレスは、メモリインターフェイス37に出力する。

#### [0021]

テクスチャメモリ 3 6 は、テクスチャマッピング部 3 5 でテクスチャマッピングする際に 用いるテクスチャパタンを記憶しておくメモリである。

# [0022]

メモリインターフェイス37は、テクスチャマッピング部35から入力される画素データおよびアドレス、および、既に画像メモリ38に記憶されている対応する画素データに基づいて、新たな画素データを生成し、画像メモリ38に記憶する。すなわち、メモリインターフェイス37は、テクスチャマッピング部35から入力されるアドレスに対応した画

10

20

30

40

素データを画像メモリ38から読み出し、その画素データと、テクスチャマッピング部35から入力された画素データとを用いて、所望の画素演算処理を行い、得られた画素データを画像メモリ38へ書き込む。

またメモリインターフェイス37は、プログラマブル・ディスプレイ制御部39から表示領域が指定された場合には、その表示領域の画素データを、画像メモリ38から読み出し、プログラマブル・ディスプレイ制御部39に出力する。

### [0023]

画像メモリ38は、表示用の画像データを記録するメモリであり、同時にアクセスすることができる2つのメモリバッファ、フレームバッファとZバッファを有する。フレームバッファには、各画素のカラー情報であるフレームデータが格納される。また、Zバッファには、各画素の奥行き情報(Z値)であるZデータが格納される。

画像メモリ38については、後に詳細に説明する。

#### [0024]

プログラマブル・ディスプレイ制御部39は、メモリインターフェイス37を介して画像メモリ38より読み出した表示領域の画素データを、表示装置4により表示可能なたとえば所定のアナログ信号に変換し、表示装置4に出力する。この時の出力信号の形式およびそれに基づく変換条件などは、接続される表示装置4の信号特性などに基づいて、プログラムすることにより任意に設定可能である。

なお、プログラマブル・ディスプレイ制御部39は、メモリインターフェイス37に対して表示すべき表示領域の画素データの要求を行い、これにより画像メモリ38より所望の表示領域の画素データを読み出す。

#### [0025]

表示装置4は、本実施の形態においては、通常家庭などで用いられているビデオ入力端子などを有するテレビジョン受信機である。3次元画像生成装置3のプログラマブル・ディスプレイ制御部39からは、ビデオ信号入力端子を介してアナログビデオ信号が入力され、その信号に基づいて3次元映像を画面上に表示する。

### [0026]

次に、この3次元コンピュータグラフィックスシステム1の動作について説明する。 まず、家庭用ゲーム機のゲーム自体を制御する主制御装置などにおいて、表示する3次元 画像が決定されると、その画面表示に必要な立体モデルの情報が入力部2に入力される。 入力部2はこの情報に基づいて、その画像を表示するための立体モデルのポリゴンデータ を3次元画像生成装置3に入力する。

3次元画像生成装置3に入力された各ポリゴンデータは、まず、ジオメトリ演算部32において、画面表示のために3次元空間中の所望の位置に配置されるように、並進変換、平行変換および回転変換などのジオメトリ変換処理が行われる。

#### [0027]

次に、座標変換の行われたポリゴンデータに対して、パラメータ演算部33においてポリゴン内部の画素データを発生するために必要なパラメータが求められ、画素発生部34において、実際にポリゴンの各頂点間を線型補間してポリゴン内部およびエッジ部分の画素データが発生される。

発生された画素データは順次テクスチャマッピング部35に入力され、テクスチャマッピング部35において、テクスチャメモリ36に記録されているテクスチャパタンデータを参照して、テクスチャマッピング処理が行われ、生成された画素データがメモリインターフェイス37を介して画像メモリ38に記憶される。

### [0028]

画像メモリ38に記憶された画素データは、同様の経路により入力される他の画素データ や任意の制御データに基づいて適宜所望の処理が行われる。

これにより画像メモリ38には常に最新の画像データが格納され、画面表示に供される。 すなわち、表示装置4に表示するための所定の領域のデータの出力の要求がプログラマブ ル・ディスプレイ制御部39からメモリインターフェイス37に対して行われ、その領域 10

20

30

40

の画素データが適宜画像メモリ38から読み出され、プログラマブル・ディスプレイ制御部39において画面表示用の所定の信号に変換され、表示装置4に出力される。

これにより、表示装置4には、所望の画像が画面に表示される。

#### [0029]

次に、このような3次元コンピュータグラフィックスシステム1の、本発明に係わる画像 メモリ38の周辺回路について詳細に説明する。

3次元コンピュータグラフィックスシステム1においては、テクスチャマッピング部35、メモリインターフェイス37およびプログラマブル・ディスプレイ制御部39が、実質的に画像メモリ38に対してアクセスを行なう構成部である。以下の説明においては、本発明の係わる特徴が明らかになるように、これらの処理部を画像メモリ38に対する1つの信号処理部とみなして説明を行なう。

なお、実際の回路は、図1に示したように各構成部が独立した構成でもよいし、後述するように、たとえば汎用のシグナルプロセッサなどを用いて一体的に構成したものであって もよい。

### [0030]

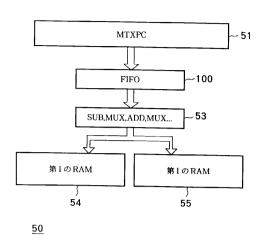

図 2 は、その画像メモリ 3 8 の周辺回路(以後、これをメモリ装置 5 0 として示す)を論理的に示す図であり、図 1 に示したテクスチャマッピング部 3 5 ~ プログラマブル・ディスプレイ制御部 3 9 の構成を、別の観点から示した図である。

なお、このメモリ装置 5 0 は、前述したように、たとえば各画素のカラー情報であるフレームデータと、各画素の奥行き情報( Z 値)である Z データの 2 系統のデータを順次バッファリングする機能を有するものとする。

#### [0031]

M T X P C 5 1 は、 3 次元コンピュータグラフィックスシステム 1 におけるメモリインターフェイス ( M e m o r y interface ) 3 7、マッピング ( T e X t u r e M a p p i n g ) 部 3 5 およびプログラマブル・ディスプレイ制御部 ( P r o g r a m m a b l e C r t c o n t r o l l e r ) 3 9 が一体化された信号処理部である。 M T X P C 5 1 で生成された画像データは、 F I F O メモリ 1 0 0 に入力される。

FIFOメモリ100は、MTXPC51より入力された画像データを、その系統(種類)は問わずに順次記憶し、バッファリングして信号処理部53に出力する。

# [0032]

信号処理部53は、FIFOメモリ100より読み出した画像データに任意の処理を施し、再び画像メモリ38に記憶する。前述したように、信号処理部53では、たとえば、既に画像メモリ38に記憶されている対応する画素データと、テクスチャマッピングされた画素データとを用いて所望の画素演算処理を行う。そして、得られた画素データは再び画像メモリ38へ書き込まれる。

第1のRAM54および第2のRAM55は、各々特定の系統のデータを記憶する2バンクのFIFOメモリであり、信号処理部53より入力されるデータを各々順次記憶する。また、図示しないが、たとえばMTXPC51からの読み出し要求に応じて、記憶したデータを記憶した順に出力する。

なお、第1のRAM54(バンクA)および第2のRAM55(バンクB)は、各々27 5ビット幅で、合わせて16ワードの記憶容量を有する。

#### [0033]

メモリ装置 5 0 (画像メモリ 3 8 の周辺回路)は、論理的にはこのようにその構成を示すことができるが、以下、本発明に係わる F I F O メモリ 1 0 0 について、図 3 ~ 図 6 を参照して説明する。

前述したように、このFIFOメモリ100は、図1における画像メモリ38として描画データをバッファリングするメモリであり、275ビット×16ワードの容量を有する。また、共有データバッファにより2系統のデータに対応し、書き込みから読み出しまでのレイタンシー3、読み出しレイタンシー2のFIFOメモリである。

# [0034]

40

30

10

20

20

30

40

50

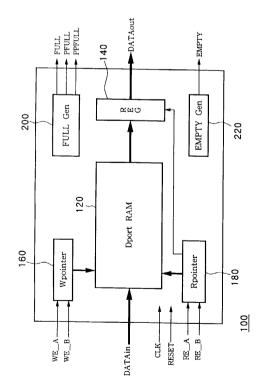

まず、そのFIFOメモリ100の構成の概略について、図3を参照して、データの流れを中心にして説明する。

図3は、FIFOメモリ100におけるデータの流れを示すのに好適な、FIFOメモリ100の主要な構成を模式的に示すブロック図である。

図 3 に示すように、F I F O メモリ 1 0 0 は、デュアルポート R A M ( D p o r t R A M ) 1 2 0、出力レジスタ( R E G ) 1 4 0、ライトポインタ部( W p o i n t e r ) 1 6 0、リードポインタ部( R p o i n t e r ) 1 8 0、フル信号生成部( F u l l G e n ) 2 0 0 およびエンプティ信号生成部( E M P T Y

Gen)220を有する。

# [0035]

デュアルポートRAM120は、275ビット×16ワード構成の同時に書き込みおよび 読み出しが可能なメモリである。

デュアルポートRAM120は、データ入力端子に入力データDATAinが印加されており、ライトポインタ部160からのライト制御信号に基づいてこれを順に記憶する。また、デュアルポートRAM120に記憶されたデータは、リードポインタ部180からのリード制御信号に基づいて記憶された順番に読み出され、出力レジスタ140に出力される。

# [0036]

出力レジスタ140は、リードポインタ部180より出力されるリード制御信号に基づいてデュアルポートRAM120より読み出されたデータRAMoutを記憶し、FIFOメモリ100より出力する。

[0037]

ライトポインタ部 1 6 0 は、FIFOメモリ 1 0 0 に入力されるバンク A、バンク B のそれぞれのライトイネーブル信号W E \_ A、W E \_ B に基づいて、デュアルポートR A M 1 2 0 に対する記憶制御信号を生成しデュアルポートR A M 1 2 0 に印加することにより、デュアルポートR A M 1 2 0 へのデータの記憶を制御する。

[0038]

リードポインタ部 1 8 0 は、FIFOメモリ 1 0 0 に入力されるバンク A、バンク B のそれぞれのリードイネーブル信号 R E \_ A , R E \_ B に基づいて、デュアルポート R A M 1 2 0 に対するリード制御信号を生成しデュアルポート R A M 1 2 0 に印加することにより、デュアルポート R A M 1 2 0 からのデータの読み出しを制御する。

[0039]

フル信号生成部200は、図示せぬFIFOメモリ100内の種々の制御信号および状態信号に基づいて、デュアルポートRAM120へ格納されたデータの合計がそれぞれ16、15、14以上であることを示すフル信号FULL、プレ・フル信号PFULL、および、プレ・プレ・フル信号PPFULL、換言すれば、デュアルポートRAM120の記憶領域が満杯の状態を示すプレ信号FULL、あと1ワードで満杯となる状態を示すプレ・フル信号PFULL、および、あと1ワードでプレ・フルとなる状態を示すプレ・プレ・フル信号PPFULLを生成し、3次元コンピュータグラフィックスシステム1のメモリインターフェイス37に相当する図示せぬ制御部に出力する。

[0040]

エンプティ信号生成部 2 2 0 は、図示せぬ F I F O メモリ 1 0 0 内の種々の制御信号および状態信号に基づいて、デュアルポート R A M 1 2 0 へ格納されたデータが無い状態、すなわちエンプティな状態を示す信号 E M P T Y を生成し、 3 次元コンピュータグラフィックスシステム 1 のメモリインターフェイス 3 7 に相当する図示せぬ制御部に出力する。図示せぬ制御部は、これら信号 F U L L , P F U L L , P P F U L L および E M P T Y に基づいて、画像メモリ 3 8 ( F I F O メモリ 1 0 0 ) へのデータの書き込みおよび読み出しを制御する。

#### [0041]

次に、FIFOメモリ100のより詳細な構成について、図4および図5を参照して説明

20

30

40

50

する。

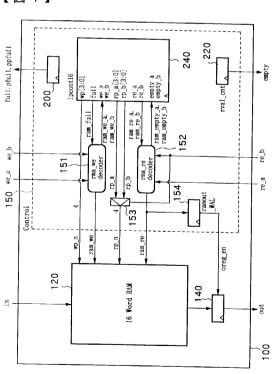

図4は、FIFOメモリ100の詳細の構成を示す回路図である。

FIFOメモリ100は、デュアルポートRAM120、出力レジスタ140および制御 部150を有する。

また、制御部 1 5 0 は、ライトイネーブルデコーダ 1 5 1、リードイネーブルデコーダ 1 5 2、セレクタ 1 5 3、レジスタ 1 5 4、フル信号生成部 2 0 0、エンプティ信号生成部 2 2 0 およびアドレス制御部 2 4 0 を有する。

[0042]

デュアルポートRAM120は、前述したように275ビット×16ワード構成の同時に書き込みおよび読み出しが可能なメモリである。デュアルポートRAM120は、制御部150のアドレス制御部240より入力される書き込みアドレスwp\_mおよびライトイネーブルデコーダ151より入力されるライトイネーブル信号ram\_weに基づいて、印加されるデータinを記憶する。また、制御部150のセレクタ153より入力される読み出しアドレスrp\_mおよびリードイネーブルデコーダ152より入力されるリードイネーブル信号ram\_reに基づいて、データを読み出し出力レジスタ140に出力する。

[0043]

出力レジスタ140は、制御部150のレジスタ154より入力されるイネーブル信号 oreg\_enに基づいて、デュアルポートRAM120より読み出されたデータを一旦記憶し、出力信号 outとしてFIFOメモリ100より出力する。

[0044]

制御部150のライトイネーブルデコーダ151は、外部よりFIFOメモリ100に入力される2つのバンクA,B各々に対するライトイネーブル信号we\_a,we\_bおよびアドレス制御部240より入力されるデュアルポートRAM120がフルであることを示す信号ram\_fu11に基づいて、デュアルポートRAM120に対するライトイネーブル信号ram\_we、および、各バンクのデータの書き込みを示す信号ram\_we\_a,ram\_we\_bを生成し、各々、デュアルポートRAM120おいアドレス制御部240に出力する。

[0045]

具体的には、ライトイネーブルデコーダ151は、デュアルポートRAM120がフルでない場合には、ライトイネーブル信号we\_a,we\_bのいずれかが入力された場合に、デュアルポートRAM120に対するライトイネーブル信号ram\_weをアクティブにする。また、ライトイネーブル信号we\_a,we\_bに応じて、データの書き込みを示す信号ram\_we\_a,ram\_we\_bのいずれかをアクティブにする。デュアルポートRAM120がフルであることを示す信号ram\_fu11がアクティブの時には、ライトイネーブルデコーダ151はいずれの信号もアクティブにしない。

[0046]

リードイネーブルデコーダ 1 5 2 は、外部よりFIFOメモリ 1 0 0 に入力される 2 つのバンク A , B 各々に対するリード信号 r e \_ a , r e \_ b およびアドレス制御部 2 4 0 より入力される各バンクの記憶データがエンプティであることを示す信号 r a m \_ e m p t y \_ a , r a m \_ e m p t y \_ b に基づいて、デュアルポート R A M 1 2 0 に対するリードイネーブル信号 r a m \_ r e 、 および、各バンクのデータの読み出しを示す信号 r a m \_ r e \_ a , r a m \_ r e \_ b を生成し、各々、デュアルポート R A M 1 2 0 おいアドレス制御部 2 4 0 に出力する。

[0047]

具体的には、リードイネーブルデコーダ152は、バンクAまたはバンクBのいずれかに対するリード信号re\_a,re\_bのいずれかが入力された場合であって、そのバンクがエンプティでない場合には、デュアルポートRAM120に対するリードイネーブル信号ram\_reをアクティブにし、そのバンクのデータの読み出しを示す信号ram\_re\_a,ram\_re\_bをアクティブにする。そのバンクがエンプティであることを示

す信号 $ram\_empty\_a$ または $ram\_empty\_b$ がアクティブの時には、リードイネーブルデコーダ 1 5 1 はいずれの信号もアクティブにしない。

### [0048]

セレクタ153は、アドレス制御部240より入力される、デュアルポートRAM120に記憶されている各バンクの先頭データのアドレスrp\_a,rp\_bのいずれかを、選択し、デュアルポートRAM120に印加する。本実施の形態においては、FIFOメモリ100に入力されるバンクBのリード信号re\_bがアクテオィブの時にバンクBの記憶データの先頭アドレスrp\_bを選択し、そうでない時にバンクAの記憶データの先頭アドレスrp\_aを選択する。

# [0049]

レジスタ154は、リードイネーブルデコーダ152よりデュアルポートRAM120に 出力されるリードイネーブル信号 r a m\_\_ r e を1クロックラッチし、デュアルポートRAM120より出力されるデータを出力レジスタ140が記憶するためのイネーブル信号 or e g\_\_ e n として、出力レジスタ140に出力する。

### [0050]

フル信号生成部200は、後述するアドレス制御部240において生成されるフル信号 fullに基づいて、さらに、あと1ワードでフルとなる状態を示す信号 PFULL、および、あと1ワードで PFULLとなる状態を示す信号 PPFULLを各々生成し出力する

# [0051]

エンプティ信号生成部 2 2 0 は、後述するアドレス制御部 2 4 0 において生成される各バンクのデータがエンプティであることを示す信号 e m p t y \_ a , e m p t y \_ b に基づいて、デュアルポート R A M 1 2 0 へ格納されたデータが無い状態、すなわちエンプティな状態を示す信号 E M P T Y を生成し出力する。

#### [0052]

アドレス制御部240は、前述したようなデュアルポートRAM120および外部に対する種々の制御信号を生成するとともに、デュアルポートRAM120に記憶したデータの順序などを管理する。

アドレス制御部240の構成について、図5を参照して詳細に説明する。

図5は、アドレス制御部240の構成を示す回路図である。

アドレス制御部240は、RAM使用領域フラグ241、フラグ更新部242、書き込みアドレスデコーダ243、バンクA書き込みアドレス記憶部244、バンクB書き込みアドレス記憶部245、セレクタ246、ネクストポインタ247、バンクAリードアドレス選択部248、バンクAリードアドレスレジスタ249、バンクBリードアドレス選択部250、バンクBリードアドレスレジスファ251、バンクAエンプティ検出カウンタ252およびバンクBエンプティ検出カウンタ253を有する。

# [0053]

R A M 使用領域フラグ 2 4 1 は、デュアルポート R A M 1 2 0 の各アドレスに未だ読み出されていないデータが記憶せているか否を示すフラグを記憶し、デュアルポート R A M 1 2 0 の各アドレスに 1 ビットが対応した 1 6 ビットのレジスタである。

R A M 使用領域フラグ 2 4 1 は、ライトイネーブルデコーダ 1 5 1 よりいずれかのバンクの書き込みを示す信号 r a m \_ w e \_ a (アドレス制御部 2 4 0 内部ではw e \_ a。以下同じ),r a m \_ w e \_ b (w e \_ b)が入力された場合、または、リードイネーブルデコーダ 1 5 2 よりいずれかのバンクの読み出しを示す信号 r a m \_ r e \_ a (r e \_ a),r a m \_ r e \_ b (r e \_ b)が入力された場合に、フラグ更新部 2 4 2 から印加される新たなフラグデータにより更新される。

# [0054]

フラグ更新部242は、デュアルポートRAM120に対してデータの書き込みおよび読み出しが行なわれた場合、すなわち、いずれかのバンクの書き込みを示す信号ram\_w

10

20

30

40

e\_a(we\_a),ram\_we\_b(we\_b)およびいずれかのバンクの読み出しを示す信号ram\_re\_a(re\_a),ram\_re\_b(re\_b)のいずれかが入力された場合に、RAM使用領域フラグ241の更新データを生成し、RAM使用領域フラグ241に印加する。

### [0055]

書き込みアドレスデコーダ 2 4 3 は、RAM使用領域フラグ 2 4 1 に記憶されているデュアルポートRAM120の記憶領域の使用フラグに基づいて、次にデータを記憶するアドレスを生成し、バンクA書き込みアドレス記憶部 2 4 4、バンクB書き込みアドレス記憶部 2 4 5 およびネクストポインタ 2 4 7 に出力するとともに、アドレス制御部 2 4 0 より出力してデュアルポートRAM120 に印加する。

なお、バンク A またはバンク B がエンプティの状態でデュアルポート R A M 1 2 0 にデータを記憶した場合には、このアドレスw p は、ネクストポインタ 2 4 7 は介さずに直接バンク A リードアドレス選択部 2 4 8 またはバンク B リードアドレス選択部 2 5 0 に入力され、データの読み出しに用いられる。

### [0056]

なお、書き込みアドレスデコーダ243は、この時、デュアルポートRAM120の空き領域のうち、アドレスの大きい方から順に記憶領域を選択し、そのアドレスを出力する。また、書き込みアドレスデコーダ243は、RAM使用領域フラグ241に記憶されているデュアルポートRAM120の使用フラグに基づいて、デュアルポートRAM120の全ての記憶領域に未だ読み出されていないデータが記憶されているか否か、すなわち、デュアルポートRAM120がフルであるか否かを検出し、フルである場合にはフル信号 fullを出力する。

### [0057]

バンク A 書き込みアドレス記憶部 2 4 4 は、バンク A の最後にデータを書き込んだデュアルポート R A M 1 2 0 のアドレスを記憶するレジスタである。バンク A 書き込みアドレス記憶部 2 4 4 には、バンク A への書き込みを示す信号 r a m \_ w e \_ a ( w e \_ a ) がアクティブになった時の、書き込みアドレスデコーダ 2 4 3 の出力アドレスが記憶される。

#### [0058]

バンク B 書き込みアドレス記憶部 2 4 5 は、バンク B の最後にデータを書き込んだデュアルポート R A M 1 2 0 のアドレスを記憶するレジスタである。バンク B 書き込みアドレス記憶部 2 4 5 には、バンク B への書き込みを示す信号 r a m \_ w e \_ b ( w e \_ b ) がアクティブになった時の、書き込みアドレスデコーダ 2 4 3 の出力アドレスが記憶される。

#### [0059]

セレクタ246は、データが書き込まれるバンクに応じて、バンクA書き込みアドレス記憶部244またはバンクB書き込みアドレス記憶部245に記憶されているアドレスを選択し、ネクストポインタ247に印加する。

# [0060]

ネクストポインタ 2 4 7 は、各バンクごとのデータの順序を記憶するレジスタである。ネクストポインタ 2 4 7 は、デュアルポート R A M 1 2 0 と同じ 1 6 ワードのアドレス空間を有し、各ワード 4 ビットのレジスタファイルである。

そして、ネクストポインタ 2 4 7 は、新たなデータがデュアルポート R A M 1 2 0 に書き込まれるごとに、セレクタ 2 4 6 により選択され印加されるアドレスに、書き込みアドレスデコーダ 2 4 3 より出力されるアドレスを記憶する。

これにより、新たなデータがデュアルポートRAM120に書き込まれるごとに、ネクストポインタ247の、そのデータと同じバンクに対して書き込まれたそのデータの前のデータが記憶されているアドレスに、そのデータが記憶されたアドレスを記憶することになる。換言すれば、ネクストポインタ247の各アドレスには、そのアドレスに記憶されているデータと同じバンクのデータで、そのデータに続く次のデータが記憶されているアドレスが記憶されることになる。

### [0061]

10

20

30

バンク A リードアドレス選択部 2 4 8 は、ネクストポインタ 2 4 7 の 1 6 ワードのデータよりバンク A のデータを順に選択し、バンク A リードアドレスレジスタ 2 4 9 に出力する。バンク A リードアドレス選択部 2 4 8 は、バンク A のデータが読み出されるごとに、自らが選択したアドレスのデータであり、後段のバンク A リードアドレスレジスタ 2 4 9 に記憶されているアドレスのネクストポインタ 2 4 7 のデータを順に選択する。

[0062]

バンク A リードアドレスレジスタ 2 4 9 は、バンク A リードアドレス選択部 2 4 8 により選択されたネクストポインタ 2 4 7 のデータ、すなわち、バンク A のデータとして記憶された次に読み出すデータのアドレス r a m \_ r e \_ a ( r e \_ a ) を記憶するレジスタであり、記憶したアドレスはアドレス制御部 2 4 0 よりリードイネーブルデコーダ 1 5 2 に出力される。

[0063]

バンク B リードアドレス選択部 2 5 0 は、ネクストポインタ 2 4 7 の 1 6 ワードのデータよりバンク B のデータを順に選択し、バンク B リードアドレスレジスタ 2 5 1 に出力する。バンク B リードアドレス選択部 2 5 0 は、バンク B のデータが読み出されるごとに、自らが選択したアドレスのデータであり、後段のバンク B リードアドレスレジスタ 2 5 1 に記憶されているアドレスのネクストポインタ 2 4 7 のデータを順に選択する。

[0064]

バンク B リードアドレスレジスタ 2 5 1 は、バンク B リードアドレス選択部 2 5 0 により選択されたネクストポインタ 2 4 7 のデータ、すなわち、バンク B のデータとして記憶された次に読み出すデータのアドレス r a m \_ r e \_ b ( r e \_ b ) を記憶するレジスタであり、記憶したアドレスはアドレス制御部 2 4 0 よりリードイネーブルデコーダ 1 5 2 に出力される。

[0065]

バンクAエンプティ検出カウンタ252は、バンクAの有効データ数をカウントするカウンタであり、バンクAへの書き込みを示す信号ram\_we\_a(we\_a)が入力されるごとにインクリメントされ、バンクAからの読み出しを示す信号ram\_re\_a(re\_a)が入力されるごとにデクリメントされる。そして、このカウンタ値が0の時、バンクAにはデータが記憶されていないものとして、エンプティ信号ram\_empty\_a(empty\_a)がアクティブにされる。

[0066]

バンク B エンプティ検出カウンタ 2 5 3 は、バンク B の有効データ数をカウントするカウンタであり、バンク B への書き込みを示す信号 r a m \_\_ w e \_\_ b ( w e \_\_ b )が入力されるごとにインクリメントされ、バンク B からの読み出しを示す信号 r a m \_\_ r e \_\_ b ( r e \_\_ b )が入力されるごとにデクリメントされる。そして、このカウンタ値が 0 の時、バンク B にはデータが記憶されていないものとして、エンプティ信号 r a m \_\_ e m p t y \_\_ b ( e m p t y \_\_ b )がアクティブにされる。

[0067]

次に、このような構成のFIFOメモリ100の動作について、図3~図6を参照して説明する。

まず、図4および図5を参照して、FIFOメモリ100におけるアドレスの制御方法を中心として、その動作を詳細に説明する。

[0068]

まず、たとえばバンク A (第 1 の系統)のデータが記憶される時には、デュアルポート R A M 1 2 0 に対して入力データ D A T A i n が印加され、バンク A のライトイネーブル信号 w e a がアクティブにされる。

FIFOメモリ100の制御部150のライトイネーブルデコーダ151がこのライトイネーブル信号we\_aを検出し、デュアルポートRAM120に対するライトイネーブル信号ram\_weをアクティブにするとともに、アドレス制御部240に対してバンクAにデータを書き込む旨の信号ram\_we\_a(we\_a)を入力する。

10

20

30

40

20

30

40

50

アドレス制御部 2 4 0 からは、既に書き込みアドレスデコーダ 2 4 3 において空き領域のアドレスが検出され、デュアルポート R A M 1 2 0 に印加されているので、デュアルポート R A M 1 2 0 においては、このライトイネーブルデコーダ 1 5 1 からのライトイネーブル信号 r a m \_ w e により、書き込みアドレスデコーダ 2 4 3 が指示するアドレス w p にデータが記録される。

# [0069]

そして、アドレス制御部 2 4 0 においては、ライトイネーブルデコーダ 1 5 1 より入力されるバンク A にデータを書き込む旨の信号 r a m \_ w e \_ a (w e \_ a)に基づいて、書き込みアドレスwpがバンク A 書き込みアドレス記憶部 2 4 4 に記憶される。

また、フラグ更新部242により、RAM使用領域フラグ241に記憶されているフラグに対して、アドレスwpのフラグが使用されている状態とされた新たなフラグデータが生成され、これによりRAM使用領域フラグ241の内容が更新される。

そしてまた、バンク A リードアドレス選択部 2 4 8 ではこのアドレスw p が選択されて、バンク A リードアドレスレジスタ 2 4 9 にバンク A の先頭データのアドレスとしてセットされる。

さらに、更新されたRAM使用領域フラグ241のフラグデータに基づいて、書き込みアドレスデコーダ243が、次にデータの書き込みを行なうアドレスを生成し、新たなアドレスwpとして出力する。

# [0070]

次に、たとえばバンク B (第 2 の系統)のデータが記憶されるとすると、デュアルポート R A M 1 2 0 に対して入力データ D A T A i n が印加され、バンク B のライトイネーブル信号 w e \_\_ b を、制御部 1 5 0 のライトイネーブルデコーダ 1 5 1 が検出し、デュアルポート R A M 1 2 0 に対するライトイネーブル信号 r a m \_\_ w e をアクティブにする。これにより、既にアドレス制御部 2 4 0 より出力されデュアルポート R A M 1 2 0 に印加されているアドレス r a m \_\_ w p (w p)に、入力されたデータが書き込まれる。

### [0071]

また、ライトイネーブルデコーダ 1 5 1 からアドレス制御部 2 4 0 に対してバンク B にデータを書き込む旨の信号 r a m \_ w e \_ b ( w e \_ b ) が入力され、これにより、書き込みアドレスw p がバンク B 書き込みアドレス記憶部 2 4 5 に記憶される。

また、フラグ更新部242により、RAM使用領域フラグ241に記憶されているフラグに対して、アドレスwpのフラグが使用されている状態とされた新たなフラグデータが生成され、これによりRAM使用領域フラグ241の内容が更新される。

そしてまた、バンクBリードアドレス選択部250ではこのアドレスwpが選択されて、 バンクBリードアドレスレジスタ251にバンクBの先頭データのアドレスとしてセット される。

さらに、更新されたRAM使用領域フラグ241のフラグデータに基づいて、書き込みアドレスデコーダ243が、次にデータの書き込みを行なうアドレスを生成し、新たなアドレスwpとして出力する。

### [0072]

次に、再びバンクAのデータが記憶されるとすると、デュアルポートRAM120に対して入力データDATAinが印加され、バンクAのライトイネーブル信号we\_aがアクティブにされる。このライトイネーブル信号we\_aをライトイネーブルデコーダ151が検出し、デュアルポートRAM120に対するライトイネーブル信号ram\_weをアクティブにすることにより、アドレス制御部240よりデュアルポートRAM120に印加されているアドレスram\_wp(wp)に、入力されたデータが書き込まれる。

### [0073]

そしてこの時、アドレス制御部240においては、入力されるバンクAにデータを書き込む旨の信号ram\_we\_a(we\_a)に基づいて、セレクタ246において、バンクA書き込みアドレス記憶部244の出力である1回目にバンクAのデータを記録したアド

20

30

40

50

レスが選択され、これがネクストポインタ247に印加され、今回のデータ記録アドレス、すなわち、2回目のバンクAのデータを記録したアドレスが、この1回目のデータ記録アドレスに記憶される。

その後、1回目の時あるいはバンクBに対する書き込みの時と同様に、この記録アドレスがバンクA書き込みアドレス記憶部244に記録され、フラグ更新部242ではRAM使用領域フラグ241に記憶されているフラグの内容が更新され、また、書き込みアドレスデコーダ243では更新されたRAM使用領域フラグ241のフラグデータに基づいて新たな書き込みアドレスが生成される。

なお、既にデータが蓄積されている状態からの追加のデータの記憶の際には、バンク A リードアドレスレジスタ 2 4 9 への書き込みアドレスデコーダ 2 4 3 からのアドレスの書き込みは行なわれない。

[0074]

さて、このようにデータを書き込んだ状態で、バンク A のデータの読み出しが要求された場合には、バンク A のリードイネーブル信号 r e \_ a がアクティブにされる。

FIFOメモリ100の制御部150のリードイネーブルデコーダ152がこのリードイネーブル信号we\_aを検出し、デュアルポートRAM120に対するリードイネーブル信号ram\_reをアクティブにするとともに、アドレス制御部240に対してバンクAのデータを読み出す旨の信号ram\_re\_a(re\_a)を入力する。

[0075]

アドレス制御部240からは、既にバンクAリードアドレスレジスタ249およびバンクBリードアドレスレジスタ251を介して、各バンクの記憶データ先頭アドレスがセレクタ153に出力されている。

そして、セレクタ153においては、バンクBのリードイネーブル信号 r e \_ b がネガティブであることから、バンクAリードアドレスレジスタ249の出力であるバンクAの先頭アドレスが選択されて、デュアルポートRAM120に印加される。

その結果、デュアルポート R A M 1 2 0 からは先に記憶したバンク A の先頭データが読み出され、出力レジスタ 1 4 0 を介して F I F O メモリ 1 0 0 より出力される。

[0076]

また、アドレス制御部 2 4 0 においては、リードイネーブルデコーダ 1 5 2 より入力されるバンク A のデータを読み出す旨の信号 r a m \_ r e \_ a ( r e \_ a ) に基づいて、バンク A リードアドレス選択部 2 4 8 が、ネクストポインタ 2 4 7 より、バンク A リードアドレスレジスタ 2 4 9 に記憶されていた今回データを読み出したアドレスのデータを選択し、バンク A の次のデータのアドレスとしてバンク A リードアドレスレジスタ 2 4 9 にセットする。その結果、アドレス制御部 2 4 0 からは、新たなバンク A の記憶データ先頭アドレスがセレクタ 1 5 3 に出力される。

さらに、アドレス制御部240においては、フラグ更新部242により、RAM使用領域フラグ241に記憶されているフラグに対して、アドレスwpのフラグが未使用の状態とされた新たなフラグデータが生成され、これによりRAM使用領域フラグ241の内容が更新される。

[0077]

このようにして、以下順次各バンクのデータの読み出しおよび書き込みが行なわれる。

[0078]

最後に、FIFOメモリ100の全体の動作について図3および図6を参照して説明する

図 6 は、 F I F O メモリ 1 0 0 の全体の動作を示すタイムチャートであり、 ( A ) F I F O メモリ 1 0 0 の動作クロック C L K を示す図、 ( B ) は F I F O メモリ 1 0 0 への入力 データ D A T A i n を示す図、 ( C ) はデュアルポート R A M 1 2 0 に印加されているデータ F I F O i n を示す図、 ( D ) はバンク A に対するライトイネーブル信号W E \_\_ B、 ( F ) は全体のエンプティ信号 M P T Y、 ( G ) はフル信号 F U L L、 ( H ) はプレ・フル信号 P F U L L、 ( I )

はプレ・プレ・フル信号 P P F U L L 、 ( J ) はバンク B に対するリードイネーブル信号 、 ( K ) はデュアルポート R A M 1 2 0 からの出力データ F I F O o u t である。

### [0079]

まず、図6(B)に示すようにデータを順次FIFOメモリ100に入力し、データD0~D3はバンクAに記憶し、データD4~D7はバンクBに記憶するようにしたい場合、図6(D)および図6(E)に示すようにバンクAおよびバンクBに対する各ライトイネーブル信号をアクティブにすれば、前述したようにFIFOメモリ100内で信号処理が行なわれ、所望の形態でデータが記憶される。

そして、図6(F)に示すようにデータD0を記憶した段階でエンプティ信号はネガティブになり、図6(I)に示すようにデータD5までの6個のデータを記憶した段階でプレ・プレ・フル信号PPFULLがアクティブになり、図6(H)に示すようにデータD6までの7個のデータを記憶した段階でプレ・フル信号PFULLがアクティブになり、さらに、図6(G)に示すようにデータD7までの8個のデータを記憶した段階でフル信号FULLがアクティブになる。

### [0800]

そして、このような状態で、図6(J)に示すように、バンクBのリードイネーブル信号をアクティブにすることにより、図6(K)に示すように、データD4以下のバンクBのデータが順次読み出される。 F

そして、データの読み出しとともに、図6(G)に示すフル信号FULL、図6(H)に示すプレ・フル信号PFULLおよび図6(I)に示すプレ・プレ・フル信号PPFULLが各々ネガティブになっていく。

FIFOメモリ100は、このように動作する。

#### [0081]

このように、本実施の形態のFIFOメモリ100においては、1つのデュアルポートRAM120を用いて、2つの系統のFIFOを実現することができる。これにより、全く独立したFIFOを2系統備える場合に比べて、FIFOのマージンを全体として少なくすることができ、また、制御回路の一部を共通化することができ、その結果、回路規模を大幅に削減することができる。

また、その2つの系統における記憶容量の割り当ては、入力されるデータに基づいてダイナミックに決定すればよく予め固定されるものではない。したがって、全体として、よりフレキシブルなバッファを構成することができる。

# [0082]

そして、このような構成のFIFOメモリ100を、たとえば前述したような3次元コンピュータグラフィックスシステム1の3次元画像生成装置3に適用することにより、各々が複雑で高速な処理を行なう各構成部間のデータの転送を、少ない規模の回路で、効率よく行なうことができ、その結果、効率よく所望の画像の生成ができる。

# [0083]

なお、本発明は前述した実施の形態に限られるものではなく、さらに種々の改変が可能である。

たとえば、本実施の形態においては、2種類(2系統)のデータを処理するFIFOを例示したが、これは2系統に限られるものではなく、任意の数の系統を処理できるようにしてよい。

### [0084]

また、実際にデータを記憶するメモリは、デュアルポートRAMに限られるものではなく、シングルポートRAMを用いてもよい。その場合には、たとえばシングルポートRAMを2つ具備し、1つのシングルポートRAMに対して記憶と読み出しを同時に行わないようにデータの記憶および読み出しを制御することにより、記憶または読み出しを同時に行えないシングルポートRAMを用いて、また動作クロックを早めることなく、本発明と同様の動作を行なうFIFOメモリを構成することができる。

もちろん、メモリの種類は、シングルポートRAM以外の任意のメモリを用いてよい。

10

20

30

50

#### [0085]

また、本実施の形態においては、FIFOメモリ100メモリ100の適用例として、3次元画像生成装置を例示したが、このFIFOメモリ装置は通常のFIFOメモリとして、任意好適な装置に適用可能である。

[0086]

# 【発明の効果】

以上説明したように、本発明によれば、より小さい回路規模で複数系統のデータに対して適切にFIFO機能を提供できるデータ記憶装置とその方法を提供することができる。 また、より小さい回路規模で各処理手段でのデータの転送が適切に行え、これにより所望の画像処理を効率よく行えるような画像処理装置を提供することがにできる。

【図面の簡単な説明】

- 【図1】図1は、本発明の一実施の形態であって、本発明のメモリ装置を適用する3次元コンピュータグラフィックスシステムの構成を示すブロック図である。

- 【図2】図2は、図1に示した3次元コンピュータグラフィックスシステムの画像メモリおよびその周辺回路を含むメモリ装置の構成を論理的に示す図である。

- 【図3】図3は、図2に示したメモリ装置におけるデータの流れを示すのに好適な、メモリ装置のFIFOメモリの構成を模式的に示すブロック図である。

- 【図4】図4は、図3に示したFIFOメモリの詳細な構成を示す回路図である。

- 【図5】図5は、図4に示したFIFOメモリのアドレス制御部の構成を示す回路図である。

- 【図6】図6は、図3に示したFIFOメモリの全体の動作を示すタイムチャートである

- 【図7】図7は、従来の3次元コンピュータグラフィックスシステムの画像メモリおよび その周辺回路を含むメモリ装置の構成を論理的に示す図である。

#### 【符号の説明】

1 … 3 次元コンピュータグラフィックスシステム、 2 …入力部、 3 … 3 次元画像生成装置、 4 …表示装置、 3 2 …ジオメトリ演算部、 3 3 …パラメータ演算部、 3 4 …画素発生部 、 3 5 …テクスチャマッピング部、 3 6 …テクスチャメモリ、 3 7 …メモリインターフェイス、 3 8 …画像メモリ、 3 9 …プログラマブル・ディスプレイ制御部、 5 0 …メモリ装置、 5 1 … M T X P C 、 5 3 …信号処理部、 5 4 …第 1 の R A M 、 5 5 …第 2 の R A M 、 1 0 0 … F I F O メモリ、 1 2 0 …デュアルポート R A M 、 1 4 0 …出力レジスタ、 1 5 0 …制御部、 1 5 1 …ライトイネーブルデコーダ、 1 5 2 …リードイネーブルデコーダ、 1 5 3 …セレクタ、 1 5 4 …レジスタ、 1 6 0 …ライトポインタ部、 1 8 0 …リードポインタ部、 2 0 0 …フル信号生成部、 2 2 0 …エンプティ信号生成部、 2 4 0 …アドレス制御部、 2 4 1 … R A M 使用領域フラグ、 2 4 2 …フラグ更新部、 2 4 3 …書き込みアドレスデコーダ、 2 4 4 …バンク A 書き込みアドレス記憶部、 2 4 5 …バンク B 書き込みアドレス記憶部、 2 4 5 …バンク B 引ードアドレス 選択部、 2 4 9 …バンク A リードアドレスレジスタ、 2 5 0 …バンク B リードアドレス 選択部、 2 5 1 …バンク B リードアドレスレジスファ、 2 5 2 …バンク A エンプティ検出カウンタ、 2 5 3 …バンク B エンプティ検出カウンタ

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】 【図6】 we\_a|we\_b| re\_a|re\_b X D0 X D1 X D2 X D3 X D4 X D5 X D6 X D7 X D8 X D9 X D10 rp\_a next[0] #rite address full we\_b (C) FIF0in (DportRAM in) (B) DATAin (A) CLK (D) WE\_A (E) WE\_B (F) EMPTY PPFULL PFULL FULL we\_a © ± € 5 £ 240

【図7】

# フロントページの続き

# (56)参考文献 特開平11-162157 (JP,A)

特開平11-289438 (JP,A)

特開平09-298651(JP,A)

枝 洋樹 外 1 名 , "低価格W S の 3 次元グラフィックス性能の向上でパソコンの追撃を振り切る 2 部 L S I のサーベイ 市販 L S I の選択肢が広がる ワークステーションとパソコンで共用可能に",日経エレクトロニクス,日本,日経 B P 社 , 1994年10月24日 , 第620号 , p . 83-92

# (58)調査した分野(Int.CI., DB名)

G06T 11/00 - 17/50

A63F 13/00

G06T 1/60

G09G 5/00 - 5/40

CSDB(日本国特許庁)