(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

HO1L 21/88

HO1L 23/52

(11)特許番号

特許第5175476号 (P5175476)

(45) 発行日 平成25年4月3日(2013.4.3)

(24) 登録日 平成25年1月11日(2013.1.11)

(51) Int.Cl. F 1

HO1L 21/3205 (2006.01) HO1L 21/768 (2006.01)

HO1L 23/522 (2006.01) HO1L 23/52 (2006.01) T

С

請求項の数 4 (全 13 頁)

(21) 出願番号 特願2007-50757 (P2007-50757) (22) 出願日 平成19年2月28日 (2007. 2. 28)

(65) 公開番号 (43) 公開日

審查請求日

特開2008-218529 (P2008-218529A) 平成20年9月18日 (2008.9.18) 平成22年2月24日 (2010.2.24) (73) 特許権者 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

|(74)代理人 100105924

弁理士 森下 賢樹

|(72)発明者 中里 真弓

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72)発明者 水原 秀樹

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72) 発明者 臼井 良輔

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

最終頁に続く

(54) 【発明の名称】回路装置の製造方法

# (57)【特許請求の範囲】

# 【請求項1】

絶縁層の一方の面上に導体部を形成する第1の工程と、

回路素子が形成された基板の表面に第1の配線層を形成する第2の工程と、

前記第1の配線層と前記導体部とを接触させた状態で前記基板と前記絶縁層とを圧着して前記導体部を前記絶縁層に埋め込む第3の工程と、

前記絶縁層の他方の面から前記導体部を露出させる第4の工程と、

前記導体部の露出した箇所および前記絶縁層の上に第2の配線層を設ける第5の工程と 、を含み、

前記導体部を、前記第1の配線層と前記第2の配線層との導通方向の結晶粒のサイズより、前記基板の表面と平行な方向の結晶粒のサイズが大きくなるように形成することを特徴とする回路装置の製造方法。

10

### 【請求項2】

前記第1の工程において、前記導体部を、結晶粒のサイズの異方性が圧延により形成された圧延材料を用いて形成することを特徴とする請求項1に記載の回路装置の製造方法。

# 【請求項3】

前記第1の工程において、前記導体部を、前記絶縁層の表面と接する面と鋭角をなす側面部を有するように形成することを特徴とする<u>請求項1または2</u>に記載の回路装置の製造方法。

【請求項4】

回路素子が形成された基板の表面に設けられた第1の配線層と絶縁層の一方の面上に形成された導体部とを接触させた状態で、前記基板と前記絶縁層とを圧着して前記導体部を前記絶縁層に埋め込む埋め込み工程と、

前記絶縁層の他方の面から前記導体部を露出させる露出工程と、

前記導体部の露出した箇所および前記絶縁層の上に第2の配線層を設ける配線工程と、 を含み、

前記導体部を、前記第1の配線層と前記第2の配線層との導通方向の結晶粒のサイズより、前記基板の表面と平行な方向の結晶粒のサイズが大きくなるように形成することを特徴とする回路装置の製造方法。

【発明の詳細な説明】

10

# 【技術分野】

[0001]

本発明は、回路装置の製造方法に関する。

【背景技術】

[0002]

近年、電子機器の小型化・高機能化に伴い、電子機器に使用される回路装置の小型化が求められている。そのための一つの方策として、回路装置の外部接続電極間のピッチを狭くすることが考えられるが、電極として用いられるはんだバンプ自体の大きさやはんだ付け時のブリッジの発生により、外部接続電極間のピッチを狭くすることによる小型化には限界があった。そこで、更なる回路装置の小型化を図るために、回路装置に再配線を形成することによる外部接続電極の再配置を行う技術が考案されている。

20

#### [0003]

このような技術としては、ウエハ状態で銅の再配線、電極端子形成と樹脂封止が行われ、その後にチップ化されたウエハ・レベル・パッケージ(Wafer-Level Packaging:以下、「WLP」という)も実現されている。例えば、特許文献1には、素子電極用メタルポストを銅や金等の導電性金属による電気めっきで形成するWLPの製造方法が開示されている。

【特許文献1】特開2004-193297号公報

【発明の開示】

【発明が解決しようとする課題】

30

## [0004]

上述のような電気めっきの一つである銅電解めっきは、一般的には硫酸銅浴によって行われ、アノードとして可溶性の含リン銅が使用されている。含リン銅アノードを使用した場合、電解によりアノード表面にリン化銅や塩化銅等からなるブラックフィルムが形成され、一価の銅の不均化反応による金属銅や酸化銅の生成を抑え、パーティクルの発生を抑制することができる。

[0005]

しかしながら、含リン銅アノードが溶解する際、液中に銅と同時にリンも溶出するため、めっき液がリンで汚染され、めっき皮膜中にリンが共析する。そのため、電解めっきによって形成された銅ポストは、不純物としてリンを含有するため硬度が高くなり、応力がかかった際の接続信頼性に問題がある。

40

# [0006]

本発明はこうした状況に鑑みてなされたものであり、その目的とするところは、回路装置における配線の接続信頼性を向上する技術を提供することにある。

【課題を解決するための手段】

# [0012]

上記課題を解決するために、本発明のある態様の回路装置の製造方法は、絶縁層の一方の面上に導体部を形成する第1の工程と、回路素子が形成された基板の表面に第1の配線層を形成する第2の工程と、第1の配線層と導体部とを接触させた状態で基板と絶縁層とを圧着して導体部を絶縁層に埋め込む第3の工程と、絶縁層の他方の面から導体部を露出

20

30

40

させる第4の工程と、導体部の露出した箇所および絶縁層の上に第2の配線層を設ける第5の工程と、を含む。また、この方法は、導体部を、第1の配線層と第2の配線層との導通方向の結晶粒のサイズより、基板の表面と平行な方向の結晶粒のサイズが大きくなるように形成する。

# [0013]

この態様によると、導体部は、導通方向の結晶粒のサイズより基板の表面と平行な方向 の結晶粒のサイズが大きくなるように形成されているため、基板の表面と平行な方向の結 晶粒のサイズが導通方向の結晶粒のサイズと同じあるいは小さい場合と比較して、第2の 配線層と接触する面における結晶粒界の合計長さが短くなる。換言すれば、導体部が第2 の配線層と接触する面における結晶粒界が占める割合は小さくなる。そのため、例えば、 第2の配線層を導体部の上面に形成する際に不純物などが結晶粒界から導体部の内部に侵 入することを抑制することができる。その結果、導体部が不純物などで浸食されにくくな り導体部と第2の配線層との接続信頼性が向上した回路装置を製造することができる。ま た、導体部や第1の配線層を介して回路素子内部に不純物などが到達しにくくなるため、 回路素子の誤作動が防止される。また、導通方向の結晶粒のサイズより基板の表面と平行 な方向の結晶粒のサイズが大きいため、導電部と第1の配線層との接触面においても導電 部の結晶粒界の合計長さが短くなる。換言すれば、導体部が第1の配線層と接触する面に おける結晶粒界が占める割合は小さくなる。そのため、導体部は、結晶粒界より抵抗が比 較的低い結晶部分が第1の配線層と接触する面積が増え、導体部と第1の配線との接触抵 抗を小さくすることができる。その結果、無駄な発熱が抑えられ、回路装置の低消費電力 化を達成することができる。

#### [0014]

第1の工程において、導体部を、結晶粒のサイズの異方性が圧延により形成された圧延 材料を用いて形成してもよい。これにより、めっきにより導体部を形成する場合と比較し て簡易に低コストで導体部を形成することができる。

### [0015]

第1の工程において、導体部を、前記絶縁層の表面と接する面と鋭角をなす側面部を有するように形成してもよい。あるいは、第1の工程において、導体部を、絶縁層の表面から該表面と垂直な方向に向かって、絶縁層の表面と平行な断面の面積が小さくなるように形成してもよい。これにより、第3の工程で絶縁層に埋め込まれた導体部は、第1の配線層と接触している面の面積より絶縁層の他方の面と対向する部分の面積の方が大きくなる。その結果、例えば、導体部を絶縁層の他方の面から露出させるためにビアを形成する際の位置合わせが容易となり、製造コストを低減することができる。

### [0016]

本発明の更に別の態様は、回路装置の製造方法である。この方法は、回路素子が形成された基板の表面に設けられた第1の配線層と絶縁層の一方の面上に形成された導体部とを接触させた状態で、前記基板と前記絶縁層とを圧着して前記導体部を前記絶縁層に埋め込む埋め込み工程と、前記絶縁層の他方の面から前記導体部を露出させる露出工程と、前記導体部の露出した箇所および前記絶縁層の上に第2の配線層を設ける配線工程と、を含む。また、この方法は、導体部を、第1の配線層と第2の配線層との導通方向の結晶粒のサイズより、基板の表面と平行な方向の結晶粒のサイズが大きくなるように形成する。

#### 【発明の効果】

# [0017]

本発明によれば、回路装置における配線の接続信頼性を向上することができる。

# 【発明を実施するための最良の形態】

# [0018]

以下、本発明の実施の形態を図面を参照して説明する。なお、図面の説明において同一の要素には同一の符号を付し、重複する説明を適宜省略する。また、以下に述べる構成は例示であり、本発明の範囲を何ら限定するものではない。

# [0019]

20

30

40

50

#### (第1の実施の形態)

# 「回路装置の構造 ]

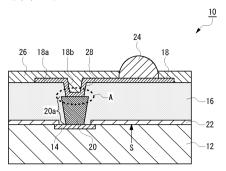

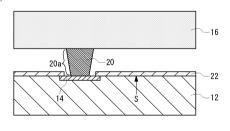

図1は、第1の実施の形態に係る回路装置の構成を示す概略断面図である。図1に示すように、第1の実施の形態に係る回路装置10は、表面S(上面側)に周知の技術により所定の電気回路などの回路素子(不図示)が形成された半導体基板12と、半導体基板12の実装面となる表面S(特に周辺部)に形成された第1の配線層の一部である回路素子の電極14と、電極14の上に設けられた絶縁層16と、絶縁層16の上に設けられた第2の配線層18と、絶縁層16を貫通して電極14および第2の配線層18を電気的に接続する導体部としての導電性バンプ20と、を備える。

# [0020]

半導体基板 1 2 の表面上には、電極 1 4 の所定の領域が露出するように保護膜 2 2 が形成されている。また、隣接する電極 1 4 同士のピッチをより広くするために、電極 1 4 および保護膜 2 2 の上に設けられた絶縁層 1 6 の上に再配線パターン 1 8 a が形成されている。電極 1 4 と再配線パターン 1 8 a との接続は、電極 1 4 の露出面に接続する導電性バンプ 2 0 とこの導電性バンプ 2 0 に接続するビアコンタクト 1 8 b を介してなされている。再配線パターン 1 8 a の所定の領域には外部接続電極としてのはんだバンプ 2 4 が設けられており、はんだバンプ 2 4 が設けられている領域以外はソルダーレジスト層 2 6 により覆われている。

### [0021]

より具体的には、絶縁層16は、半導体基板12の表面Sの上方に形成されており、その厚さは、例えば、約80μmである。絶縁層16は、加圧したときに塑性流動を引き起こす材料により形成されている。加圧したときに塑性流動を引き起こす材料の一例としては、エポキシ系熱硬化型樹脂が挙げられる。絶縁層16を形成するためにより好ましいエポキシ系熱硬化型樹脂としては、例えば、温度160 、圧力8MPaの条件下で、粘度が1kPa・s程度の特性を有する材料であるとよい。また、この材料を、温度160の条件下で15MPaで加圧した場合、加圧しない場合と比較して、樹脂の粘度が約1/8に低下する。

### [0022]

なお、エポキシ系熱硬化形樹脂としては、編み込まれたガラス繊維に樹脂を含侵させたタイプの膜であってもよい。あるいは、絶縁層内に  $2~\mu$  m  $\sim 1~0~\mu$  m 程度の直径を有するフィラーが添加された膜であってもよい。このフィラーとしては、アルミナ(A 1~2~O~3)、シリカ(S i~O~2)、窒化アルミニウム(A 1~N)、窒化シリコン(S i~N)および窒化ホウ素(B N)などが好適である。また、フィラーの重量充填率としては、 3~0~%  $\sim 8~0~\%$  程度が好ましい。

# [0023]

導電性バンプ20としては、銅(Cu)やアルミニウム(Al)などの金属を採用することができるが、本実施の形態に係る回路装置10では、圧延により形成された銅箔が用いられている。そのため、導電性バンプ20は、材料の銅の結晶粒のサイズに異方性を有する。具体的には、導電性バンプ20は、電極14と第2の配線層18との導通方向(表面Sに垂直な方向)の結晶粒のサイズより、半導体基板12の表面Sと平行な方向の結晶粒のサイズが大きい。例えば、圧延により形成された銅箔は、結晶粒の長手方向の平均的なサイズが約80~100 $\mu$ m、結晶粒の短手方向の平均的なサイズが約15 $\mu$ m程度である。

# [0024]

導電性バンプ20の高さは、例えば、約50 $\mu$ mである。本実施の形態に係る導電性バンプ20は、円錐台(断面形状が台形状)形状に設けられており、電極14の接触面と平行な先端部と、この先端部に近づくにつれて径(寸法)が細くなるように形成された側面部20aとを備えている。つまり、導電性バンプ20は、半導体基板12の表面Sと接する面と鈍角をなす側面部20aを有している。換言すると、導電性バンプ20は、半導体基板12の表面Sと平行な断面の面積が電極14側から第2の配線層18側に向かって大

20

30

40

50

きくなるように形成されている。 導電性バンプ 2 0 の先端の径および第 2 の配線層 1 8 と接する面の径は、それぞれ約 8 0  $\mu$  m および約 1 0 0  $\mu$  m である。また、導電性バンプ 2 0 は、電極 1 4 と対応する位置に設けられている。そして、導電性バンプ 2 0 の先端部は、電極 1 4 と直に接するように形成されている。

### [0025]

再配線パターン 1 8 a は、絶縁層 1 6 の上に形成され、その厚さは、例えば、約 2 0  $\mu$  mである。再配線パターン 1 8 a は、例えば、銅(C u)などの金属が採用され、絶縁層 1 6 の開口部 2 8 内に設けたビアコンタクト 1 8 b を介して導電性バンプ 2 0 と電気的に接続されている。ここで、開口部 2 8 の開口幅は約 1 0 0  $\mu$  mである。ビアコンタクト 1 8 b は、開口部 2 8 の内面を被覆するように設けられており、再配線パターン 1 8 a と一体的に形成されている。なお、電極 1 4 の上には導電性バンプ 2 0 が介在するので、ビアコンタクト 1 8 b (開口部 2 8)の深さは約 3 0  $\mu$  mであり、電極 1 4 に直接ビアコンタクト (開口部 )を形成する場合に比べてその深さを浅くすることができる。

# [0026]

以上のように、本実施の形態に係る回路装置10は、半導体基板12の表面Sに形成された電極14に対して、導電性バンプ20およびビアコンタクト18bを介して再配線パターン18aが形成されているので、外部接続電極であるはんだバンプ24の再配置を行うことができる。

### [0027]

# (導電性バンプ)

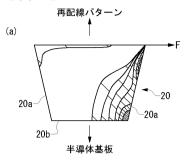

次に、銅箔を用いて形成された導電性バンプ20について詳述する。図2は、図1に示す導電性バンプ20とビアコンタクト18bとの界面領域Aにおける結晶粒を模式的に示した図である。図2に示すように、導電性バンプ20は、電極14と第2の配線層18との導通方向Zの結晶粒30のサイズL1より、半導体基板12の表面Sと平行な方向Xまたは方向Yの結晶粒のサイズL2が大きい。

### [0028]

したがって、導電性バンプ20は、半導体基板の表面と平行な方向の結晶粒のサイズ L2が図2に示す結晶粒30の導通方向Zの結晶粒のサイズ L1と同じあるいはサイズ L1より小さい場合と比較して、ビアコンタクト18bと接触する面における各結晶粒界30aの合計長さが短くなる。換言すれば、導電性バンプ20がビアコンタクト18bと接触する面における結晶粒界30aが占める面積の割合は小さくなる。そのため、例えば、ビアコンタクト18bを導電性バンプ20の内部に侵入することを抑制することができる。その結果、導電性バンプ20が不純物などで浸食されにくくなり導電性バンプ20とビアコンタクト18bとの接続信頼性を向上することができる。

# [0029]

また、導電性バンプ20や電極14を介して半導体基板12に形成されている回路素子内部に不純物などが到達しにくくなるため、回路素子の誤作動が防止される。また、導電性バンプ20は、導通方向Zの結晶粒30のサイズL1より半導体基板12の表面Sと平行な方向Xまたは方向Yの結晶粒30のサイズL2が大きいため、半導体基板12の表面Sと平行な方向Xまたは方向Yの結晶粒のサイズL2が導通方向Zの結晶粒のサイズL1と同じあるいはサイズL1より小さい場合と比較して、電極14と接触する面における各結晶粒界30aの合計長さが短くなる。換言すれば、導電性バンプ20が電極14と接触する面における結晶粒界30aが占める面積の割合は小さくなる。そのため、導電性バンプ20は、結晶粒界より抵抗が比較的低い結晶部分が電極14と接触する面積が増え、導電性バンプ20と電極14との接触抵抗を小さくすることができる。その結果、無駄な発熱が抑えられ、回路装置10の低消費電力化を達成することができる。

### [0030]

また、導電性バンプ20は、結晶粒30のサイズの異方性が圧延により形成された圧延 材料の場合、破断強度が向上されているため、めっきなどで導電性バンプ20を形成した

20

30

40

50

場合と比較して応力がかかった際に導電性バンプ 2 0 が破断しにくくなり、配線の接続信頼性を向上することができる。

### [0031]

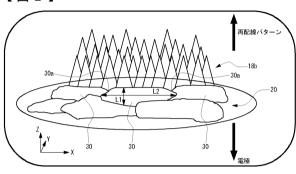

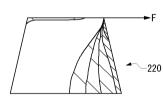

次に、導電性バンプに応力がかかる場合について説明する。図3(a)~図3(c)は、再配線パターン18aを含む第2の配線層18を介して導電性バンプ20のX方向に応力がかかった場合の応力分布を導電性バンプ20の形状ごとにシミュレーションにより算出した模式図である。

# [0032]

再配線パターン18aの材料である銅と回路素子を含む半導体基板12の材料であるシリコンとは熱膨張係数が異なるため、熱衝撃や回路素子における発熱などにより第2の配線層18を介して導電性バンプ20には、半導体基板12の表面Sと平行な方向に応力が発生する。

### [0033]

例えば、導電性バンプ20とビアコンタクト18bとの接続部において半導体基板12の表面Sと平行な方向Xに応力Fがかかった場合、導電性バンプ20の形状によって導電性バンプ20内部のZ方向の応力分布は異なる。図3(a)に示す本実施の形態に係る導電性バンプ20は、半導体基板12の表面Sと平行な断面の面積が電極14から第2の配線層18に向かって大きくなるように形成されている。換言すると、導電性バンプ20は、半導体基板12の表面Sとの接触面20bと鈍角をなす側面部20aを有していることになる。図3(b)に示す導電性バンプ120は、半導体基板12の表面Sと平行な断面の面積が電極14から第2の配線層18に向かって同じとなるように形成されている。図3(c)に示す導電性バンプ220は、半導体基板12の表面Sと平行な断面の面積が電極14から第2の配線層18に向かって小さくなるように形成されている。

#### [0034]

図3(a)~図3(c)を比較すると、導電性バンプ20の電極14と接する部分近傍の応力分布は、図3(a)に示す形状の場合に最も大きくかつ広範囲に分布していることがわかる。なお、濃い部分ほど応力は大きい。したがって、熱による応力が発生した場合であっても、このような形状の導電性バンプ20は、電極14により大きな力で押し付けられることとなる。そのため、導電性バンプ20と電極14とがより密着することになり、接続信頼性が向上する。

### [0035]

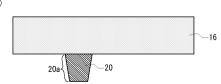

# (回路装置の製造方法)

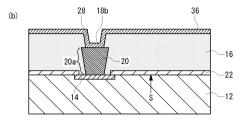

次に、図4~図6を参照して第1の実施の形態に係る回路装置の製造方法について説明する。図4(a)~図4(c)は、第1の実施の形態に係る回路装置の製造方法における第1の工程を説明するための概略断面図である。図5(a)~図5(c)は、第1の実施の形態に係る回路装置の製造方法における第2の工程および第3の工程を説明するための概略断面図である。図6(a)~図6(b)は、第1の実施の形態に係る回路装置の製造方法における第4の工程および第5の工程を説明するための概略断面図である。

# [0036]

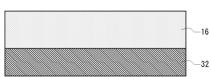

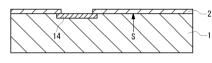

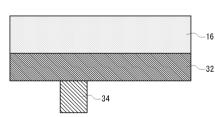

まず、図4(a)に示すように、エポキシ系熱硬化型樹脂からなる厚さ約80μmの絶縁層16の一方の面上に厚さ約50μmの銅箔32を接合する。ここで、銅箔32としては、結晶粒のサイズの異方性が圧延により形成された圧延材料を用いる。これにより、めっきにより導電性バンプ20を形成する場合と比較して簡易に低コストで導電性バンプ20を形成することができる。次に、図4(b)に示すように、通常のリソグラフィ法を用いて銅箔32上の導電性バンプ形成領域にレジストマスク34を形成する。ここで、導電性バンプ形成領域は、図1に示す半導体基板12の電極14の位置に対応する。

### [0037]

そして、図4(c)に示すように、レジストマスク34をマスクとして薬液を用いたウェットエッチング処理により、所定の円錐台形状を有する導電性バンプ20が形成され、その後にレジストマスク34が除去される。この際、導電性バンプ20は、先端部に近づ

20

30

40

50

くにつれて径(寸法)が細くなる側面部20aを有するように形成される。つまり、導電性バンプ20は、絶縁層16の表面と接する面と鋭角をなす側面部20aが形成される。換言すると、導電性バンプ20は、絶縁層16の表面からその表面と垂直な方向に向かって、絶縁層16の表面と平行な断面の面積が小さくなるように形成されている。以上、図4(a)~図4(c)に示した本実施の形態に係る第1の工程により、絶縁層16の一方の面上に導電性バンプ20を形成することができる。

### [0038]

なお、本実施の形態に係る回路装置 100 製造方法では、導電性バンプ 200 の高さを約  $50\mu$  m、導電性バンプ 200 の先端の径を約  $80\mu$  m 、導電性バンプ 200 が絶縁層 160 と接している面の径を約  $100\mu$  m としている。また、上述の各工程では、エポキシ系熱硬化型樹脂からなる絶縁層 160 が完全に熱硬化されないように、熱硬化温度まで加熱しないようにして、絶縁層 160 が半硬化の状態(流動しやすい状態)で維持されている。

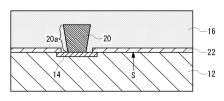

### [0039]

次に、回路素子が形成された半導体基板12の表面Sに第1の配線層として電極14を 形成する第2の工程と、電極14と導電性バンプ20とを接触させた状態で半導体基板1 2と絶縁層16とを圧着して導電性バンプ20を絶縁層16に埋め込む第3の工程とを説 明する。

# [0040]

まず、図5(a)に示すように、P型シリコン基板などの半導体基板12に対して、その表面S近傍の領域に周知の技術により、所定の電気回路などの回路素子(図示せず)およびその周辺部若しくは上部に電極14を形成する。電極14の材料としては、一般的にアルミニウムなどの金属が用いられる。そして、電極14の所定部分が露出するように、半導体基板12の表面S上の領域に、半導体基板12を保護するための絶縁性の保護膜22が形成される。保護膜22としては、シリコン酸化膜(SiO2)やシリコン窒化膜(SiN)などが用いられる。このように、図5(a)で示した本実施の形態に係る第2の工程により、回路素子が形成された半導体基板12の表面Sに第1の配線層としての電極14を形成することができる。

#### [0041]

次に、図5(b)に示すように、電極14と導電性バンプ20の先端とが接触するような状態に半導体基板12と絶縁層16とを配置する。そして、この状態でプレス装置を用いて加圧成型することにより、図5(c)に示すように、導電性バンプ20が絶縁層16に埋め込まれながら半導体基板12、導電性バンプ20および絶縁層16が一体化される(埋め込み工程)。

# [0042]

ここで、プレス装置を用いた加圧成形時の圧力は約 5 M P a 、温度は約 2 0 0 である。このプレス加工により絶縁層 1 6 の粘度が低下し、絶縁層 1 6 は塑性流動を起こす。そのため、導電性バンプ 2 0 は電極 1 4 と接触した状態で絶縁層 1 6 の内部に自己整合的に埋設される。なお、本実施の形態では、絶縁層 1 6 の厚さが約 8 0  $\mu$  m、導電性バンプ 2 0 の高さが約 5 0  $\mu$  mであるため、加圧成形の際に導電性バンプ 2 0 は絶縁層 1 6 を貫通することなく埋め込まれる。

# [0043]

導電性バンプ20が絶縁層16に埋め込まれた後も、引き続き、絶縁層16に熱処理(150、30分)を加えることにより、絶縁層16を完全に硬化させる。この結果、半導体基板12の上に絶縁層16が圧着され固定されるとともに、導電性バンプ20が電極14に接触し押し付けられた状態で絶縁層16内に固定される。このように、図5(b)および図5(c)で示した本実施の形態に係る第3の工程により、電極14と導電性バンプ20とを接触させた状態で半導体基板12と絶縁層16とを圧着して導電性バンプ20を絶縁層16に埋め込むことができる。

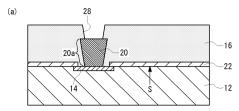

### [0044]

次に、絶縁層16の他方の面から導電性バンプ20を露出させる第4の工程と、導電性

バンプ 2 0 の露出した箇所および絶縁層 1 6 の上に第 2 の配線層 1 8 を設ける第 5 の工程とを説明する。

# [0045]

図6(a)に示すように、絶縁層16の上面からレーザを照射して導電性バンプ20が露出するように開口部28を形成する。ここで、レーザ照射には、例えば、炭酸ガスレーザを用いることができる。レーザ照射は、所定の条件である第1の照射条件と第1の照射条件におけるパルス幅を変更した第2の照射条件の二段階で行われる。具体的には、0.25msのパルス周期で、1.0Wの出力のレーザを用い、第1の照射条件としては、例えば、パルス幅が8~10μs、ショット数を1とすることができる。また、第2の照射条件としては、例えば、パルス幅が3~5μs、パルス間隔が25ms、ショット数を3とすることができる。これにより、絶縁層16の表面から導電性バンプ20に近づくにつれて径が縮小するテーパ形状の側壁を有する開口部28を形成することができる。

### [0046]

なお、上述の第1の工程において、導電性バンプ20は、絶縁層16の表面からその表面と垂直な方向に向かって、絶縁層16の表面と平行な断面の面積が小さくなるように形成されているため、上述の第3の工程で絶縁層16に埋め込まれた導電性バンプ20は、電極14と接触している面の面積より絶縁層16の他方の面と対向する部分の面積の方が大きくなる。その結果、導電性バンプ20を絶縁層16の他方の面から露出させるためにレーザでビアを形成する際の位置合わせが容易となり、製造コストを低減することができる。このように、図6(a)で示した本実施の形態に係る第4の工程(露出工程)により絶縁層16の他方の面から導電性バンプ20を露出させることができる。

#### [0047]

次に、図6(b)に示すように、無電解めっき法および電解めっき法を用いて絶縁層16の上面および開口部28の内面上に銅を約20μmの厚さでめっきする。この結果、絶縁層16上に約20μmの厚みを有する銅めっき層36が形成されるとともに、開口部28の内部にビアコンタクト18bが形成される。なお、導電性バンプ20の上にめっきにより銅を成長させると、図2に示すように、2方向に結晶が成長して柱状の結晶粒からなるビアコンタクト18bが形成される。

# [0048]

その後、図1に示したように、通常のリソグラフィ技術およびエッチング技術を用いて 銅めっき層36(図6(b)参照)を加工することにより、所定のライン / スペースパターンを有する再配線パターン18aが形成される。そして、再配線パターン18aの電極パッド形成領域に開口部が形成されるように絶縁層16および再配線パターン18aをソルダーレジスト層26により覆う。ソルダーレジスト層26は、再配線パターン18aの保護膜として機能し、エポキシ樹脂などを用いることができる。本実施の形態に係るソルダーレジスト層26の厚さは、例えば、約40μmである。

# [0049]

そして、はんだ印刷法を用いて、ソルダーレジスト層26の開口部から露出する部分の再配線パターン18aに対して外部接続端子として機能するはんだバンプ24を形成する。このように、図6(b)で示した本実施の形態に係る第5の工程(配線工程)により導電性バンプ20の露出した箇所および絶縁層16の上に第2の配線層18を設けることができる。

# [0050]

以上、上述の各工程により図1に示される回路装置10が製造される。本実施の形態に係る回路装置の製造方法によれば、導電性バンプ20を、電極14と第2の配線層18との導通方向の結晶粒のサイズより、半導体基板12の表面Sと平行な方向の結晶粒のサイズが大きくなるように形成することができる。そのため、導電性バンプ20は、半導体基板12の表面Sと平行な方向の結晶粒のサイズが導通方向の結晶粒のサイズと同じあるいは小さい場合と比較して、第2の配線層18と接触する面における結晶粒界の合計長さが短くなる。換言すれば、導体部が第2の配線層と接触する面における結晶粒界が占める割

10

20

30

40

20

30

40

50

合は小さくなる。その結果、例えば、第2の配線層18を導電性バンプ20の上面に形成する際に不純物などが結晶粒界から導電性バンプ20の内部に侵入することを抑制することができる。

### [0051]

また、導電性バンプ20が不純物などで浸食されにくくなり導電性バンプ20と第2の配線層18との接続信頼性が向上した回路装置を製造することができる。また、導電性バンプ20や電極14を介して回路素子内部に不純物などが到達しにくくなるため、回路素子の誤作動が防止される。また、導通方向の結晶粒のサイズより半導体基板12の表面と平行な方向の結晶粒のサイズが大きいため、導電性バンプ20と電極14との接触面においても導電性バンプ20の結晶粒界の合計長さが短くなる。換言すれば、導電性バンプ20が電極14と接触する面における結晶粒界が占める割合は小さくなる。そのため、導電性バンプ20は、結晶粒界より抵抗が比較的低い結晶部分が電極14と接触する面積が増え、導電性バンプ20と電極14との接触抵抗を小さくすることができる。その結果、無駄な発熱が抑えられ、回路装置の低消費電力化を達成することができる。

### [0052]

### (第2の実施の形態)

図7は、第2の実施の形態に係る半導体モジュールの構成を示す概略断面図である。本実施の形態に係る半導体モジュール100は、上述した回路装置10を複数内蔵している。また、半導体モジュール100は、回路装置10のそれぞれを外部接続端子(不図示)と電気的に導通する配線構造130を備えている。なお、第1の実施の形態で説明した内容と同じものについては同じ符号を付して説明を省略する。本実施の形態に係る半導体モジュール100によれば、第1の実施の形態で説明した効果と同様の効果を得ることができる。

#### [0053]

以上、本発明を上述の各実施の形態を参照して説明したが、本発明は上述の各実施の形態に限定されるものではなく、各実施の形態の構成を適宜組み合わせたものや置換したものについても本発明に含まれるものである。また、当業者の知識に基づいて各実施の形態における回路装置の製造方法の順番を適宜組み替えることや、回路装置において各種の設計変更等の変形を各実施の形態に対して加えることも可能であり、そのような変形が加えられた実施の形態も本発明の範囲に含まれうる。

### [0054]

上述の実施の形態では、開口部28内を被覆するようにビアコンタクト18bを設けた例を示したが、例えば、開口部28の開口寸法を狭くして、ビアコンタクト18bを含む再配線パターン18aを形成する際、めっき液中に抑制剤および促進剤を添加することによって、開口部28内を銅めっきで完全に埋め込むようにビアコンタクト18bを形成するようにしてもよい。これにより、ビアコンタクト部(導電性バンプ20およびビアコンタクト18b)を低抵抗化することができる。

### [0055]

また、上述の実施の形態では、半導体基板12の電極14と再配線パターン18aとの間を接続するビアコンタクト部を設けた例を示したが、例えば、多層配線基板内における下層配線層と上層配線層との間を接続するためにビアコンタクト部を適用してもよい。これにより、多層配線基板の製造安定性を良好にすることができ、多層配線基板を低コストで製造することができる。

# [0056]

また、上述の実施の形態では、回路素子が形成された基板の表面に第1の配線層を形成する第2の工程を含む製造工程の例について説明しているが、例えば、第2の工程の代わりに、回路素子に接続された第1の配線層である電極14が形成された半導体基板12を準備する準備工程を採用してもよい。そして、この準備工程により半導体基板12を準備した後、半導体基板12の表面に設けられた電極14と絶縁層16の一方の面上に形成された導電性バンプ20とを接触させた状態で、半導体基板12と絶縁層16とを圧着して

導電性バンプ20を絶縁層16に埋め込む埋め込み工程と、絶縁層16の他方の面から導 電性バンプ20を露出させる露出工程と、導電性バンプ20の露出した箇所および絶縁層 16の上に第2の配線層18を設ける配線工程とを行うことで、上述の実施の形態に係る 回路装置を製造してもよい。なお、上述の埋め込み工程では、第1の工程で作製した絶縁 層16の代わりに、予め導電性バンプ20が一方の面上に形成された絶縁層を準備しそれ を用いてもよい。

#### 【図面の簡単な説明】

### [0057]

- 【図1】第1の実施の形態に係る回路装置の構成を示す概略断面図である。

- 【図2】図1に示す導電性バンプとビアコンタクトとの界面領域における結晶粒を模式的 に示した図である。

- 【図3】再配線パターンを含む第2の配線層を介して導電性バンプのX方向に応力がかか った場合の応力分布を導電性バンプの形状ごとにシミュレーションにより算出した模式図 である。

- 【図4】第1の実施の形態に係る回路装置の製造方法における第1の工程を説明するため の概略断面図である。

- 【図5】第1の実施の形態に係る回路装置の製造方法における第2の工程および第3の工 程を説明するための概略断面図である。

- 【図6】第1の実施の形態に係る回路装置の製造方法における第4の工程および第5の工 程を説明するための概略断面図である。

- 【図7】第2の実施の形態に係る半導体モジュールの構成を示す概略断面図である。

#### 【符号の説明】

### [0058]

10 回路装置、 12 半導体基板、 14 16 絶縁層、 電極、 18 第2 18a 再配線パターン、 18b ビアコンタクト、 20 導電性バン の配線層、 プ、 20a 側面部、 22 保護膜、 24 はんだバンプ、 26 ソルダーレジ スト層、 28 開口部、 30 結晶粒、 3 0 a 結晶粒界、 3 2 銅箔、 レジストマスク、 36 銅めっき層、 100 半導体モジュール、 130 配線 構造。

10

# 【図1】

# 【図3】

【図2】

(c)

# 【図4】

(b)

(b)

(c)

(c)

【図6】

【図7】

# フロントページの続き

# 審査官 大嶋 洋一

(56)参考文献 特開2004-349361(JP,A) 国際公開第2005/027223(WO,A1)

# (58)調査した分野(Int.CI., DB名)

H 0 1 L 2 1 / 3 2 0 5 H 0 1 L 2 1 / 7 6 8 H 0 1 L 2 3 / 5 2 H 0 1 L 2 3 / 5 2 2