#### (19)**日本国特許庁(JP)**

# (12) 公開特許公報(A)

(11)公開番号 特開2024-57500 (P2024-57500A)

(43)公開日 令和6年4月24日(2024.4.24)

| (51)国際特許分類 |                 | FΙ      |       | テーマコード(参考) |           |

|------------|-----------------|---------|-------|------------|-----------|

| H 0 1 L    | 23/29 (2006.01) | H 0 1 L | 23/36 | Α          | 5 F 1 3 6 |

| H 0 1 L    | 25/07 (2006.01) | H 0 1 L | 25/04 | C          |           |

| H 0 1 L    | 23/48 (2006.01) | H 0 1 L | 23/48 | G          |           |

|                     | 審查                                                    | 請求              | 未請求        | 請求項の数                                        | 7   | O L    | (全12頁)    |  |

|---------------------|-------------------------------------------------------|-----------------|------------|----------------------------------------------|-----|--------|-----------|--|

| (21)出願番号<br>(22)出願日 | 特願2022-164293(P2022-164293)<br>令和4年10月12日(2022.10.12) | (71)出           | <b>は願人</b> | 000004260<br>株式会社デンソー<br>愛知県刈谷市昭和町 1 丁目 1 番地 |     |        |           |  |

|                     |                                                       | (74)代理人         |            |                                              |     |        |           |  |

|                     |                                                       |                 |            | 矢作 和行                                        |     |        |           |  |

|                     |                                                       | (74)代理人         | 100121991  |                                              |     |        |           |  |

|                     |                                                       |                 | 弁理士 野々部 泰平 |                                              |     |        |           |  |

|                     |                                                       | (74)代理人         |            | 100145595<br>弁理士 久保 貴則                       |     |        |           |  |

|                     |                                                       |                 |            |                                              |     |        |           |  |

|                     |                                                       | (72)発明者         | 下妻 彩子      |                                              |     |        |           |  |

|                     |                                                       | 愛知県刈谷市昭和町1丁目1番地 |            | 番地 株式                                        |     |        |           |  |

|                     |                                                       |                 |            | 会社デンソー内                                      |     |        |           |  |

|                     |                                                       | F ターム (参考)      |            | ) 5F136                                      | BC0 | 3 DA07 | DA27 FA03 |  |

|                     |                                                       |                 |            |                                              |     |        |           |  |

|                     |                                                       |                 |            |                                              |     |        |           |  |

|                     |                                                       |                 |            |                                              |     |        |           |  |

## (54)【発明の名称】 半導体装置

### (57)【要約】

【課題】放熱性を向上させつつ、低コスト化が可能な半 導体装置を提供すること。

【解決手段】半導体装置101は、一面に設けられたド レイン電極11a,12aと、反対面に設けられたソー ス電極11b,12bと有した二つ以上の電位が異なる 半導体チップ11,12を備えている。また、半導体装 置101は、各半導体チップが個別に実装された第1基 板20と第2基板30と、各半導体チップを電気的に接 続する第3基板50と、半導体チップと各基板を一体的 に封止する封止樹脂部90とを備えている。第1基板と 第2基板は、半導体チップが実装される実装銅21,3 1と、半導体チップからの熱を放熱する放熱銅22,3 2と、実装銅と放熱銅を絶縁する絶縁層23,33とを 有している。そして、放熱銅は、絶縁層との対向面の反 対面が封止樹脂部から露出している。実装銅は、放熱銅 よりも板厚が厚い。

【選択図】図1

図

#### 【特許請求の範囲】

#### 【請求項1】

一面に設けられた第1電極(11a,12a)と、前記一面の反対面に設けられた第2電極(11b,12b)と有し、二つ以上の電位が異なる半導体素子(11,12)と、 各半導体素子が個別に実装された二つ以上の配線基板(20,30)と、

各半導体素子を電気的に接続する配線部材(50)と、

前記半導体素子と前記配線基板と前記配線部材を一体的に封止する封止樹脂部(90)と、を備え、

各配線基板は、各半導体素子の実装部位であり前記第1電極と接続された実装金属板(21,31)と、前記半導体素子から発せられた熱を放熱する放熱金属板(22,332)と、前記実装金属板と前記放熱金属板との間に配置され前記実装金属板と前記放熱金属板とを電気的に絶縁する絶縁層(23,33)とを有し、

前記放熱金属板は、前記絶縁層との対向面の反対面が前記封止樹脂部から露出し、前記実装金属板は、前記放熱金属板よりも板厚が厚い半導体装置。

#### 【請求項2】

前記放熱金属板は、前記絶縁層の縁部を除く部位に設けられている、請求項1に記載の半導体装置。

#### 【請求項3】

前記配線部材は、各半導体素子の前記第2電極と対向して配置されており、一つの前記半導体素子の前記第2電極と接続された第1配線板(51a)と、他の前記半導体素子の前記第2電極と接続された第2配線板(51b)とが一つの基板として設けられており、さらに、前記第1配線板と接続されている前記半導体素子が実装された前記実装金属板

さらに、前記第1配線板と接続されている前記半導体素子が実装された前記実装金属板に接続された第1主端子(41)と、前記第2配線板に接続された第2主端子(42)と、を備え、

前記第1主端子と前記第2主端子は、前記封止樹脂部に対して同一方向に突出している 、請求項1に記載の半導体装置。

#### 【請求項4】

前記第1配線板および前記第2配線板は、前記第2電極に対向して配置された導電性のターミナル(61,62)とはんだ(73,76)を介して接続されており、かつ、前記ターミナルの対向領域の周辺に、前記対向領域から溢れた前記はんだを収容可能な凹部(55)が設けられている、請求項3に記載の半導体装置。

#### 【請求項5】

前記実装金属板は、側面が凸形状を有しており、前記凸形状の頂点が前記絶縁層との接触面側よりも前記半導体素子の実装面側に位置している、請求項1~3のいずれか1項に記載の半導体装置。

## 【請求項6】

前記実装金属板と前記第1主端子は、超音波接合によって接続されている、請求項3に記載の半導体装置。

### 【請求項7】

前記放熱金属板は、前記実装金属板と前記第1主端子との接続部の対向領域の周辺に設けられている、請求項6に記載の半導体装置。

【発明の詳細な説明】

### 【技術分野】

## [0001]

本開示は、半導体装置に関する。

## 【背景技術】

#### [00002]

特許文献 1 には、絶縁層を介して銅坂が積層された放熱回路基板と、放熱回路基板に実装された複数の半導体素子を備えた半導体装置が開示されている。放熱回路基板は、半導体素子が実装される実装面である銅板と、冷却器と熱接触する放熱面である銅板とが絶縁

20

10

30

00

層を介して積層されている。また、放熱回路基板は、半導体素子が実装される実装面である銅板の厚さが、冷却器と熱接触する放熱面である銅板の厚さと同一又はより厚くなっている。

【先行技術文献】

【特許文献】

[0003]

【特許文献1】特開2019-204869号公報

【発明の概要】

【発明が解決しようとする課題】

[0004]

ところで、半導体装置は、同電位ではない二つの半導体素子を備えた構成もある。この場合、特許文献 1 の半導体装置では、放熱回路基板を切削やエッチングなどで加工する必要があるため高コストになってしまうという問題がある。

[00005]

開示される一つの目的は、放熱性を向上させつつ、低コスト化が可能な半導体装置を提供することである。

【課題を解決するための手段】

[0006]

ここに開示された半導体装置は、

一面に設けられた第1電極(11a,12a)と、一面の反対面に設けられた第2電極(11b,12b)と有し、二つ以上の電位が異なる半導体素子(11,12)と、

各半導体素子が個別に実装された二つ以上の配線基板(20,30)と、

各半導体素子を電気的に接続する配線部材(50)と、

半導体素子と配線基板と配線部材を一体的に封止する封止樹脂部(90)と、を備え、 各配線基板は、各半導体素子の実装部位であり第1電極と接続された実装金属板(21 ,31)と、半導体素子から発せられた熱を放熱する放熱金属板(22,32)と、実装 金属板と放熱金属板との間に配置され実装金属板と放熱金属板とを電気的に絶縁する絶縁 層(23,33)とを有し、

放熱金属板は、絶縁層との対向面の反対面が封止樹脂部から露出し、

実装金属板は、放熱金属板よりも板厚が厚いことを特徴とする。

[0007]

このように、半導体装置は、各半導体素子が個別に実装された配線基板を備えているため、電位が異なる半導体素子を実装するために切削などによって配線基板を加工する必要がない。よって、半導体装置は、低コスト化することができる。

[00008]

また、配線基板は、絶縁層よりも半導体素子側に配置されている実装金属板の板厚が、 放熱金属板の板厚よりも厚くなっている。このため、半導体装置は、放熱金属板が実装金 属板よりも板厚が厚い構成よりも、半導体素子から発せられた熱の放熱性を向上できる。

[ 0 0 0 9 ]

この明細書において開示された複数の態様は、それぞれの目的を達成するために、互いに異なる技術的手段を採用する。請求の範囲およびこの項に記載した括弧内の符号は、後述する実施形態の部分との対応関係を例示的に示すものであって、技術的範囲を限定することを意図するものではない。この明細書に開示される目的、特徴、および効果は、後続の詳細な説明、および添付の図面を参照することによってより明確になる。

【図面の簡単な説明】

[0010]

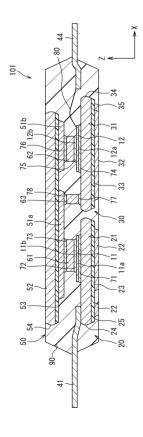

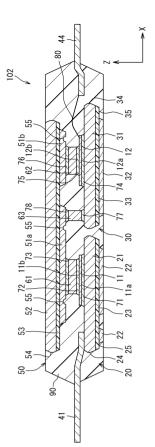

- 【図1】実施形態における半導体装置の概略構成を示す断面図である。

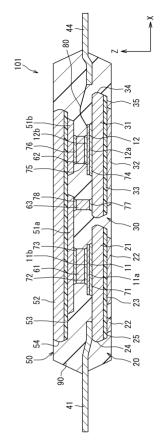

- 【図2】実施形態におけるリードフレームの概略構成を示す平面図である。

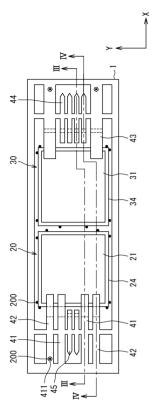

- 【図3】図2のII II線に沿う断面図である。

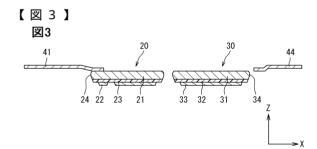

- 【図4】図2のIV IV線に沿う断面図である。

10

20

30

50

【図5】実施形態における半導体装置の概略構成を示す透視図である。

- 【図6】変形例1における半導体装置の概略構成を示す断面図である。

- 【図7】変形例2における半導体装置の概略構成を示す断面図である。

【発明を実施するための形態】

[0011]

以下において、図面を参照しながら、本開示を実施するための複数の形態を説明する。各形態において、先行する形態で説明した事項に対応する部分には同一の参照符号を付して重複する説明を省略する場合がある。各形態において、構成の一部のみを説明している場合は、構成の他の部分については先行して説明した他の形態を参照し適用することができる。

[0012]

なお、以下においては、互いに直交する3方向をX方向、Y方向、Z方向と示す。また、X方向とY方向とによって規定される平面をXY平面と示す。また、Z方向からみることを平面視とも称する。よって、平面視は、Z方向から見た場合の平面図とみなすことができる。

[0013]

(実施形態)

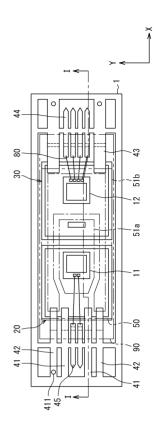

図1~図5を用いて、第1実施形態の半導体装置101に関して説明する。図1、図2などに示すように、半導体装置101は、半導体チップ11,12、第1基板20、第2基板30、端子41~45、第3基板50、ターミナル61~63、はんだ71~78、ボンディングワイヤ80、封止樹脂部90を備えている。半導体装置101は、たとえば、電力変換装置におけるインバータなどに適用することができる。インバータは、三相分の上下アーム回路を備えて構成されている。なお、インバータの回路構成は、たとえば、特開2022-126905号公報などを適用できる。また、図1は、図5のII線に沿う断面図に相当する。

[0014]

半導体装置101は、たとえば一相分の上下アーム回路を構成する。本実施形態では、一つのハイサイドスイッチ11と一つのローサイドスイッチ12が直接接続された例を採用する。しかしながら、本開示は、複数のハイサイドスイッチ11が並列接続され、複数のローサイドスイッチ12が並列接続された構成であっても採用できる。

[0015]

なお、図2は、リードフレーム1の一部である正極端子41、負極端子42、出力端子43、信号端子44、ゲート端子45が分割される前の状態を示している。また、図5は、封止樹脂部90が設けられ、かつ、リードフレーム1が分割される前の状態を示している。

[0016]

< 半 導 体 チ ッ プ 1 1 , 1 2 >

図1に示すように、半導体装置101は、半導体チップ11,12として、ハイサイドスイッチ11とローサイドスイッチ12とを備えている。つまり、半導体装置101は、二つ以上の電位が異なる半導体チップ11,12を備えているといえる。ハイサイドスイッチ11とローサイドスイッチ12は、同一の構成を有している。そのため、ハイサイドスイッチ11とローサイドスイッチ12を区別する必要がない場合は、ハイサイドスイッチ11を用いて説明する。ハイサイドスイッチ11、ローサイドスイッチ12は、半導体素子に相当する。

[0017]

ハイサイドスイッチ11は、シリコン(Si)、シリコンよりもバンドギャップが広いワイドバンドギャップ半導体などを材料とする半導体基板に、素子が形成されてなる。ワイドバンドギャップ半導体としては、たとえばシリコンカーバイド(SiC)、窒化ガリウム(GaN)、酸化ガリウム(Ga2O3)、ダイヤモンドがある。ハイサイドスイッチ11は、半導体素子と称されることがある。

10

20

30

40

. .

10

20

30

40

50

[0018]

ハイサイドスイッチ11は、板厚方向が2方向と一致している。ハイサイドスイッチ11に形成された素子は、2方向に主電流が流れるように縦型構造をなしている。縦型素子として、IGBT、MOSFET、ダイオードなどを採用することができる。本実施形態では、縦型素子として、一つのアームを構成するMOSFETが形成されている。ハイサイドスイッチ11は、図示しないゲート電極を有している。

[ 0 0 1 9 ]

ハイサイドスイッチ11は、自身の板厚方向、すなわち2方向における両面に、素子の主電極を有している。具体的には、主電極として、一面側にドレイン電極11aを有し、一面の反対面側にソース電極11bを有している。一方、ローサイドスイッチ12は、主電極として、一面側にドレイン電極12aを有し、反対面側にソース電極12bを有している。ドレイン電極11a,12aは、第1電極に相当する。ソース電極11b,12bは、第2電極に相当する。

[0020]

ハイサイドスイッチ11は、平面略矩形状をなしている。ハイサイドスイッチ11は、反対面においてソース電極11bとは異なる位置に形成された複数のパッドを有している。ソース電極11bおよびパッドは、半導体基板の反対面の図示しない保護膜からそれぞれ露出している。ソース電極11bは、ハイサイドスイッチ11の反対面の一部分に形成されている。ドレイン電極11aは、一面のほぼ全面に形成されている。

[0021]

パッドは、信号用の電極である。パッドは、ソース電極11bと電気的に分離されている。パッドは、たとえば、Y方向において、ソース電極11bの形成領域とは反対側の端部に形成されている。パッドは、少なくともゲート電極用のゲートパッドを含む。また、電流センス用、半導体チップ11,12のいずれか(ここでは、ローサイドスイッチ12)の温度を検出する感温ダイオード用の信号パッドなどを含んでいてもよい。なお、図1に示すように、ローサイドスイッチ12は、信号パッドと信号端子44とがボンディングワイヤ80を介して接続されている。ハイサイドスイッチ11およびローサイドスイッチ12は、ゲートパッドとゲート端子45とがボンディングワイヤ80を介して接続されている。

[0022]

< ターミナル 6 1 ~ 6 3 >

第1ターミナル61と第2ターミナル62と継手ターミナル63は、金属を主成分とする導電性のブロック体である。これらのターミナル61~63は、半導体装置101の配線の一部である。

[0023]

第1ターミナル61は、ハイサイドスイッチ11のソース電極11b上に配置されている。第1ターミナル61は、一方の端部がはんだ72によってソース電極11bと接続されている。第1ターミナル61は、他方の端部がはんだ73によって第1実装銅51aと接続されている。

[0024]

第2ターミナル62は、ローサイドスイッチ12のソース電極12b上に配置されている。第2ターミナル62は、一方の端部がはんだ75によってソース電極12bと接続されている。第2ターミナル62は、他方の端部がはんだ76によって第2実装銅51bと接続されている。

[ 0 0 2 5 ]

継手ターミナル 6 3 は、一方の端部がはんだ 7 7 によって実装銅 3 1 と接続されている。継手ターミナル 6 3 は、他方の端部がはんだ 7 8 によって第 1 実装銅 5 1 a と接続されている。なお、実装銅 3 1、第 1 実装銅 5 1 a 、第 2 実装銅 5 1 b は、後ほど説明する。

[0026]

<第1基板20、第2基板30>

10

20

30

40

50

図1に示すように、第1基板20は、ハイサイドスイッチ11が実装される配線基板である。第1基板20は、実装銅21、放熱銅22、絶縁層23を備えている。第1基板20は、実装銅21、絶縁層23、放熱銅22が、この順番で積層されている。また、実装銅21は、絶縁層23と対向する面において絶縁層23と接している。 縁層23と対向する面において絶縁層23と接している。

#### [0027]

実装銅21は、銅を主成分として構成された配線の一部である。実装銅21は、表面にめっき膜が設けられていてもよい。実装銅21は、薄膜とは異なり、板状の部材である。よって、実装銅21は、金属板や銅板ともいえる。実装銅21は、ハイサイドスイッチ11の実装部位でありドレイン電極11aと接続されている。実装銅21は、はんだ71によってドレイン電極11aと接続されている。実装銅21は、主端子の一つである正極端子41と接続されている。実装銅21は、放熱銅22よりも板厚が厚い。実装銅21は、たとえば、板厚が0.8mm以上である。なお、板厚は、2方向に沿う長さともいえる。正極端子41は、第1主端子に相当する。正極端子41は、後ほど説明する第1実装銅51aと接続されているハイサイドスイッチ11が実装された実装銅21に接続されているといえる。

#### [0028]

放熱銅22は、実装銅21と同様の材料によって構成されている。放熱銅22は、絶縁層23との対向面の反対面が封止樹脂部90から露出している。放熱銅22は、ハイサイドスイッチ11から発せられた熱を放熱する部材である。つまり、放熱銅22は、ハイサイドスイッチ11から絶縁層23を介して熱が伝達され、その熱を封止樹脂部90の外部に放熱する。放熱銅22は、放熱金属板に相当する。なお、実装銅21と放熱銅22は、銅以外の金属を主成分としたものであっても採用できる。

## [0029]

絶縁層23は、実装銅21と放熱銅22との間に配置され、実装銅21と放熱銅22と を電気的に絶縁する部材である。

#### [0030]

第2基板30は、ローサイドスイッチ12が実装される配線基板である。第2基板30は、実装銅31、放熱銅32、絶縁層33を有し、第1基板20と同様に構成されている。実装銅31は、実装銅21と同様の構成を有している。放熱銅32は、放熱銅22と同様の構成を有している。絶縁層33は、絶縁層23と同様の構成を有している。

#### [0031]

実装銅31は、はんだ74によってドレイン電極12aと接続されている。実装銅31 は、はんだ77によって継手ターミナル63と接続されている。さらに、実装銅31は、 主端子の一つである出力端子43と接続されている。

## [0032]

図1に示すように、実装銅21,31の側面には、凸形状であるVカット部24,34が設けられている。つまり、実装銅21,31は、側面がV字形状をなしているといえる。また、実装銅21,31は、側面がVカットされているといえる。さらに、実装銅21,31は、Z方向において、凸形状の頂点が絶縁層23,33との接触面側よりも半導体チップ11,12の実装面側に位置している。Vカット部24,34は、実装銅21,31の側面の全周にわたって設けられている。

### [0033]

これによって、半導体装置101は、半導体チップ11、12の周辺における封止樹脂部90の剥離や、はんだ71,74へかかるストレスを低減できる。なお、実装銅21,31は、絶縁層23,33側から半導体チップ11,12側にいくにつれて、XY平面に沿う断面積が広くなる形状を有していてもよい。これによっても、半導体装置101は、同様の効果を奏することができる。

#### [0034]

図1に示すように、放熱銅22,32は、絶縁層23,33の縁部を除く部位に設けら

(7)

れている。つまり、放熱銅22は、Z方向からの平面視において、絶縁層23の一部に設けられている。さらに、放熱銅22は、絶縁層23の環状の外周部を除く位置に設けられている。絶縁層23は、放熱銅22を囲う部位が沿面部25として設けられているといえる。沿面部25は、実装銅21と放熱銅22との絶縁性を確保するための部位である。言い換えると、沿面部25は、実装銅21と放熱銅22と沿面距離を確保するための部位である。

### [0035]

同様に、放熱銅32は、絶縁層33の環状の外周部を除く位置に設けられている。よって、絶縁層33は、放熱銅32を囲う部位が沿面部35として設けられているといえる。 沿面部35は、実装銅31と放熱銅32との絶縁性を確保するための部位である。

10

## [0036]

< 第 3 基 板 >

図 1 に示すように、第 3 基板 5 0 は、半導体チップ 1 1 , 1 2 上に配置されている。第 3 基板 5 0 は、ソース電極 1 1 b , 1 2 bと対向して配置されている。第 3 基板 5 0 は、ハイサイドスイッチ 1 1 とローサイドスイッチ 1 2 とを電気的に接続する配線部材である

[0037]

第3基板50は、第1実装銅51aと、第2実装銅51bと、放熱銅52と、絶縁層53を備えている。第1実装銅51aと第2実装銅51bは、絶縁層53と対向する面において絶縁層53と接している。放熱銅52は、絶縁層53と対向する面において絶縁層53と接している。よって、第3基板50は、第1実装銅51a(第2実装銅51b)、絶縁層53、放熱銅52が、この順番で積層されている。

20

#### [0038]

図1に示すように、第1実装銅51aと第2実装銅51bは、絶縁層53の同一面に設けられている。しかしながら、図5に示すように、第1実装銅51aと第2実装銅51bは、接しておらず、距離を置いて配置されている。このように、第3基板50は、第1実装銅51aと第2実装銅51bが一つの基板として設けられている。なお、第1実装銅51aと第2実装銅51bは、実装銅21と同様の材料によって構成されている。

[0039]

第1実装銅51aは、平面視において、矩形形状を有している。第1実装銅51aは、 ソース電極11bの対向領域から、実装銅31の対向領域にわたって設けられている。

30

## [0040]

第1実装銅51aは、ハイサイドスイッチ11のソース電極11bと接続されている。 詳述すると、第1実装銅51aは、はんだ73によって第1ターミナル61と接続されている。そして、第1ターミナル61は、ソース電極11bと接続されている。よって、第1実装銅51aは、第1ターミナル61を介して、ソース電極11bと接続されている。

[0041]

また、第1実装銅51aは、実装銅31と接続されている。詳述すると、第1実装銅5 1aは、はんだ78によって継手ターミナル63と接続されている。そして、継手ターミナル63は、実装銅31と接続されている。よって、第1実装銅51aは、継手ターミナル63を介して、実装銅31と接続されている。なお、ハイサイドスイッチ11は、一つの半導体素子に相当する。第1実装銅51aは、第1配線板に相当する。

40

### [0042]

第2実装銅51bは、平面視において、第1実装銅51aを部分的に囲う形状を有している。第2実装銅51bは、X方向において第1実装銅51aと隣り合う部分と、Y方向において第1実装銅51aと隣り合う二つの部分とが一体的に設けられていう。よって、第2実装銅51bは、電気的な経路として環状の一部が分断された形状を有している。

[0043]

第2実装銅51bは、ローサイドスイッチ12のソース電極12bと接続されている。 詳述すると、第2実装銅51bは、はんだ76によって第2ターミナル62と接続されて

いる。そして、第2ターミナル62は、ソース電極12bと接続されている。よって、第2実装銅51bは、第2ターミナル62を介して、ソース電極12bと接続されている。なお、第2実装銅51bは、X方向において第1実装銅51aと隣り合う部分に第2ターミナル62が接続されている。また、第2実装銅51bは、Y方向において第1実装銅51aと隣り合う二つの部分に負極端子42が接続されている。

#### [0044]

なお、ローサイドスイッチ 1 2 は、他の半導体素子に相当する。第 2 実装銅 5 1 b は、第 2 配線板に相当する。負極端子 4 2 は、第 2 主端子に相当する。

#### [0045]

放熱銅52は、実装銅21と同様の材料によって構成されている。放熱銅52は、絶縁層53との対向面の反対面が封止樹脂部90から露出している。放熱銅52は、半導体チップ11,12から発せられた熱を放熱する部材である。つまり、放熱銅52は、半導体チップ11,12から絶縁層53を介して熱が伝達され、その熱を封止樹脂部90の外部に放熱する。放熱銅52は、実装銅21,31と同様、側面にVカット部54が設けられている。

#### [0046]

なお、実装銅 5 1 a , 5 1 b と放熱銅 5 2 は、銅以外の金属を主成分としたものであっても採用できる。第 3 基板 5 0 では、放熱銅 5 2 の方が実装銅 5 1 a , 5 1 b よりも板厚が厚くなっている。しかしながら、放熱銅 5 2 と実装銅 5 1 a , 5 1 b は、同等の板厚であってもよい。さらに、実装銅 5 1 a , 5 1 b は、放熱銅 5 2 よりも板厚が厚くてもよい

[0047]

絶縁層53は、実装銅51a,51bと放熱銅52との間に配置され、実装銅51a, 51bと放熱銅52とを電気的に絶縁する部材である。

#### [0048]

< 封止樹脂部 9 0 >

封止樹脂部 9 0 は、半導体チップ 1 1 , 1 2 、第 1 基板 2 0 、第 2 基板 3 0 、端子 4 1 ~ 4 5 、第 3 基板 5 0 、ターミナル 6 1 ~ 6 3 、はんだ 7 1 ~ 7 8 、ボンディングワイヤ 8 0 を一体的に覆っている。これによって、半導体装置 1 0 1 は、半導体チップ 1 1 , 1 2 などを外部環境から保護することができる。

[0049]

また、各放熱銅22,32,52は、各絶縁層23,33,53との対向面の反対面が 封止樹脂部90から露出している。これによって、半導体装置101は、放熱性を向上で きる。

[0050]

図5に示すように、端子41~45は、一部が封止樹脂部90から露出した状態で、残りの部分が封止樹脂部90に覆われている。正極端子41と負極端子42とハイサイドスイッチ11側のゲート端子45は、封止樹脂部90から同一方向に突出している。出力端子43とローサイドスイッチ12側のゲート端子45と信号端子44は、封止樹脂部90から同一方向に突出している。そして、正極端子41と出力端子43は、封止樹脂部90に対して逆方向に突出している。

[0051]

以上のように、半導体装置101は、第1基板20および第2基板30と、第3基板50とによって半導体チップ11,12を挟み込む構成を有している。よって、半導体装置101は、両面放熱構造をなしている。

## [0052]

< 製造方法 >

図2、図3、図4、図5を用いて、半導体装置101の製造方法に関して説明する。まず、図2に示すように、各端子41~45が一体的に設けられたリードフレーム1と、第1基板20、第2基板30を用意する。リードフレーム1は、第1基板20、第2基板3

20

10

30

40

0 とともに台座に置かれる。このとき、リードフレーム 1 は、位置決めピン 2 0 0 によって位置決めされる。また、リードフレーム 1 は、基準穴として貫通穴 4 1 1 が設けられている。位置決めピン 2 0 0 は、その貫通穴 4 1 1 にも通される。これによって、リードフレーム 1 は、第 1 基板 2 0 、第 2 基板 3 0 に対して位置決めされる。

#### [ 0 0 5 3 ]

このとき、図3に示すように、リードフレーム1は、正極端子41の一端が実装銅21上に配置される。また、リードフレーム1は、出力端子43の一端が実装銅31上に配置される。なお、負極端子42は、第1実装銅51aと接続される。このため、図4に示すように、負極端子42は、実装銅21から離れた状態となっている。

#### [0054]

リードフレーム1は、上記のように位置決めされた状態で、正極端子41の一端と実装銅21が超音波接合によって接続される。同様に、リードフレーム1は、出力端子43の一端と実装銅31が超音波接合によって接続される。

#### [0055]

その後、負極端子42は、第1実装銅51aと接続される。また、信号端子44とゲート端子45は、ボンディングワイヤ80を介して、半導体チップ11,12のパッドと接続される。そして、図5に示すように、半導体チップ11,12、第1基板20、第2基板30、端子41~45、第3基板50、ターミナル61~63、はんだ71~78、ボンディングワイヤ80を一体的に覆うように封止樹脂部90が形成される。なお、各端子41~45は、封止樹脂部90が形成された、リードフレームの枠部から分割される。

#### [0056]

< 効果 >

半導体装置101は、配線基板として、各半導体チップ11,12が個別に実装された第1基板20と第2基板30を備えている。このため、半導体装置101は、電位が異なる半導体チップ11,12を実装するために切削などによって配線基板を加工する必要がない。よって、半導体装置101は、低コスト化することができる。

#### [0057]

また、第1基板20と第2基板30は、実装銅21,31の板厚が、放熱銅22,32 の板厚よりも厚くなっている。このため、半導体装置101は、放熱銅22,32が実装銅21,31よりも板厚が厚い構成よりも、半導体チップ11,12から発せられた熱の放熱性を向上できる。

#### [0058]

[0059]

半導体装置101は、ソース電極11b,12b側の第3基板50が上記のような一体物として構成されている。よって、半導体装置101は、正極端子41から出力端子43までの配線と、出力端子43から負極端子42までの配線とを対向させることができる。また、半導体装置101は、正極端子41から負極端子42までのループを小さくすることができる。よって、半導体装置101は、低インダクタンスを実現することができる。

以上、本開示の好ましい実施形態について説明した。しかしながら、本開示は、上記実施形態に何ら制限されることはなく、本開示の趣旨を逸脱しない範囲において、種々の変形が可能である。以下に、本開示のその他の形態として、変形例 1 、 2 に関して説明する。上記実施形態および変形例 1 、 2 は、それぞれ単独で実施することも可能であるが、適宜組み合わせて実施することも可能である。本開示は、実施形態において示された組み合わせに限定されることなく、種々の組み合わせによって実施可能である。

#### [0060]

(変形例1)

図 6 を介して、変形例 1 の半導体装置 1 0 2 に関して説明する。ここでは、主に、半導体装置 1 0 2 における半導体装置 1 0 1 との相違点に関して説明する。半導体装置 1 0 2 は、第 1 実装銅 5 1 a と第 2 実装銅 5 1 b の構成が半導体装置 1 0 1 と異なる。

#### [0061]

10

20

30

第1実装銅51 a は、第1ターミナル61や継手ターミナル63の対向領域から溢れたはんだ73,78を収容可能なはんだ吸収溝55が設けられている。第2実装銅51 b は、第2ターミナル62の対向領域から溢れたはんだ76を収容可能なはんだ吸収溝55が設けられている。はんだ吸収溝55 は、周辺よりも窪んだ部位である。はんだ吸収溝55 は、凹部に相当する。

#### [0062]

(変形例2)

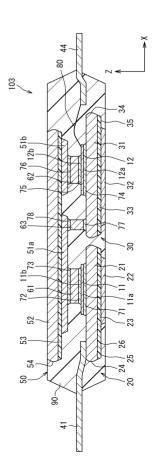

図 7 を介して、変形例 2 の半導体装置 1 0 3 に関して説明する。ここでは、主に、半導体装置 1 0 3 における半導体装置 1 0 1 との相違点に関して説明する。半導体装置 1 0 3 は、第 1 基板 2 0 の構成が半導体装置 1 0 1 と異なる。

[0063]

放熱銅22は、実装銅21と正極端子41との接続部の対向領域の周辺に設けられている。つまり、絶縁層23は、対向領域に放熱銅22が形成された非形成部26が設けられている。

[0064]

第1基板20は、正極端子41と実装銅21とを超音波接合する際に、絶縁層23にクラックが入る可能性がある。第1基板20は、絶縁層23にクラックが入ったとしても、 実装銅21と放熱銅22との絶縁性を確保することができる。

[0065]

本開示は、実施形態に準拠して記述されたが、本開示は当該実施形態や構造に限定されるものではないと理解される。本開示は、様々な変形例や均等範囲内の変形をも包含する。加えて、様々な組み合わせや形態が本開示に示されているが、それらに一要素のみ、それ以上、あるいはそれ以下、を含む他の組み合わせや形態をも、本開示の範畴や思想範囲に入るものである。

#### 【符号の説明】

[0066]

1 1 ... ハイサイドスイッチ、 1 1 a ... ドレイン電極、 1 1 b ... ソース電極、 1 2 ... ローサイドスイッチ、 1 2 a ... ドレイン電極、 1 2 b ... ソース電極、 2 0 ... 第 1 基板、 2 1 ... 実装銅、 2 2 ... 放熱銅、 2 3 ... 絶縁層、 2 4 ... Vカット部、 2 5 ... 沿面部、 2 6 ... 非形成部、 3 0 ... 第 2 基板、 3 1 ... 実装銅、 3 2 ... 放熱銅、 3 3 ... 絶縁層、 3 4 ... Vカット部、 3 5 ... 沿面部、 4 1 ... 正極端子、 4 2 ... 負極端子、 4 3 ... 出力端子、 4 4 ... 信号端子、 4 5 ... ゲート端子、 4 1 1 ... 貫通穴、 5 0 ... 第 3 基板、 5 1 a ... 第 1 実装銅、 5 1 b ... 第 2 実装銅、 5 2 ... 放熱銅、 5 3 ... 絶縁層、 5 4 ... Vカット部、 5 5 ... はんだ吸収溝、 6 1 ... 第 1 ターミナル、 6 2 ... 第 2 ターミナル、 6 3 ... 継手、 7 1 ~ 7 8 ... はんだ、 8 0 ... ボンディングワイヤ、 9 0 ... 封止樹脂部、 1 0 1 ~ 1 0 3 ... 半導体装置、 2 0 0 ... 位置決めピン

40

10

20

【図面】

【図1】

<u>×</u>

【図2】 図

10

20

【図4】 図4

30

【図5】 SS 図

【図6】

<u>₩</u>

10

20

【図7】

<u>⊠</u>

30