## (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 110224789 B (45) 授权公告日 2021. 09. 07

**G05B** 19/05 (2006.01) **G06F** 12/0846 (2016.01)

(56) 对比文件

CN 105302753 A,2016.02.03

CN 101867452 A, 2010.10.20

CN 105612705 A.2016.05.25

US 2004143710 A1,2004.07.22

李晓娟;黄翌."基于FPGA的HDLC设计实现". 《现代电子技术》.2007,

Jun Wang; Wenhao Zhang. "Design and implementation of HDLC procedures based on FPGA". 《2009 3rd International Conference on Anti-counterfeiting, Security, and Identification in Communication》. 2009,

审查员 曹洪菠

权利要求书3页 说明书8页 附图2页

(21) 申请号 201910497885.3

(22) 申请日 2019.06.10

(65) 同一申请的已公布的文献号 申请公布号 CN 110224789 A

(43) 申请公布日 2019.09.10

(73) 专利权人 哈尔滨工业大学 地址 150001 黑龙江省哈尔滨市南岗区西 大直街92号

(72) **发明人** 梁军 崔秀海 赵金帅 彭宇 彭喜元

(74) 专利代理机构 哈尔滨市松花江专利商标事 务所 23109

代理人 董玉娇

(51) Int.CI.

H04L 1/00 (2006.01)

#### (54) 发明名称

一种基于FPGA的多模式HDLC控制器

#### (57) 摘要

一种基于FPGA的多模式HDLC控制器,涉及数据通信领域。解决了传统使用FPGA实现的HDLC控制器中每个模块都单纯通过HDL逐句描述,导致设计复杂、调试繁琐及功能单一的问题。本发明FPGA包括HDLC协议传输单元、数据缓存单元和主控单元;HDLC协议传输单元包括HDLC数据发送模块和HDLC数据接收模块;当控制器用于向与其通信的装置发送HDLC数据时,HDLC数据发送模块将写入的并行数据转化为串行数据,并将串行数据编码成HDLC帧,当控制器用于接收与其通信的装置发送来的HDLC数据时,HDLC数据接收模块将接收的串行数据转化为并行数据,并对并行数据进行解码。本发明主要用于数据通信。

CN 110224789 B

1.一种基于FPGA的多模式HDLC控制器,其特征在于,该控制器采用FPGA实现,FPGA包括HDLC协议传输单元(100)、数据缓存单元(200)和主控单元(300);

HDLC协议传输单元 (100) 包括HDLC数据发送模块 (110) 和HDLC数据接收模块 (120);

(一) 当控制器用于向与其通信的装置发送HDLC数据时,

主控单元 (300) 解析从控制总线下发的控制指令,根据预设的传输模式将解析完成的控制指令控制数据缓存单元 (200) 将其内部存储的待发送并行数据写入HDLC数据发送模块 (110),HDLC数据发送模块 (110)根据主控单元 (300)下发的配置指令,将写入的并行数据转化为串行数据,并将串行数据编码成HDLC帧后,发送至与控制器通信的装置,同时,当串行数据编码成HDLC帧后,HDLC数据发送模块 (110)还用于发送配置完成使能信号至主控单元 (300);

HDLC数据发送模块 (110) 还向与控制器通信的装置发送同步时钟信号,从而完成控制器向与其通信的装置发送HDLC数据;

(二) 当控制器用于接收与其通信的装置发送来的HDLC数据时,

HDLC数据接收模块(120),用于接收同步时钟信号和编码成HDLC帧的串行数据,将接收的串行数据转化为并行数据,并对并行数据进行解码,解码完成后的并行数据缓存至数据缓存单元(200),同时,HDLC数据接收模块(120),还用于向主控单元(300)实时发送数据传输状态信息;

数据缓存单元(200)将并行数据缓存完成的使能信息发送至主控单元(300),主控单元(300)根据接收到使能信息向数据缓存单元(200)发送控制指令,从而从数据缓存单元(200)内读取并行数据,并将读取的并行数据发送至数据总线,完成控制器对与其通信的装置发送来的HDLC数据的接收:

主控单元 (300) 包括顶层控制模块 (340)、标准传输模式控制模块 (310)、定时传输模式控制模块 (320) 和响应传输模式控制模块 (330);

数据缓存单元 (200) 包括标准传输模式数据缓存模块 (210)、定时传输模式数据缓存模块 (220) 和响应传输模式数据缓存模块 (230):

顶层控制模块(340),用于同时与控制总线和数据总线进行通信,还用于同时与标准传输模式控制模块(310)、定时传输模式控制模块(320)和响应传输模式控制模块(330)进行通信,并对三种传输模式控制模块进行切换;

标准传输模式控制模块(310),用于向标准传输模式数据缓存模块(210)发送数据发送指令或从标准传输模式数据缓存模块(210)接收与控制器通信的装置发送过来的数据,

标准传输模式数据缓存模块 (210) 的并行数据输入端用于接收从HDLC数据接收模块 (120) 发出的并行数据,标准传输模式数据缓存模块 (210) 的并行数据输出端通过信号多路 复用模块 (400) 将其输出的并行数据发送至HDLC数据发送模块 (110);

定时传输模式控制模块(320),用于定时向定时传输模式数据缓存模块(220)发送数据发送指令,定时传输模式数据缓存模块(220)根据接收的数据发送指令,通过信号多路复用模块(400)向HDLC数据发送模块(110)发送并行数据;

响应传输模式控制模块(330),用于向响应传输模式数据缓存模块(230)发送数据发送指令,响应传输模式数据缓存模块(230)根据接收的数据发送指令,进行相应的响应后,通过信号多路复用模块(400)向HDLC数据发送模块(110)发送并行数据;

信号多路复用模块(400),用于对数据传输通路进行切换。

2.根据权利要求1所述的一种基于FPGA的多模式HDLC控制器,其特征在于,HDLC数据发送模块(110)包括发送数据FIF0缓存模块(111)、CRC生成模块(112)、数据与CRC缓存模块(113)和插"0"数据缓存模块(114);

发送数据FIF0缓存模块(111),用于缓存接收的并行数据,并将并行数据转化为串行数据,再根据主控单元(300)下发的配置指令对串行数据中每一帧数据的帧头、帧尾个数及波特率进行配置,配置完成后,发送配置完成的数据帧至CRC生成模块(112),同时,还发送配置完成使能信号至主控单元(300);其中,配置完成的数据帧中的每一帧数据包括帧头、有效数据和帧尾;

发送数据FIF0缓存模块(111)在发送数据帧的同时,还用于发送同步时钟信号;

CRC生成模块(112),用于对接收的每一帧数据生成CRC校验码,并将生成CRC校验码后的数据帧发送至数据与CRC缓存模块(113),CRC校验码位于每一帧数据中有效数据与帧尾之间:

数据与CRC缓存模块(113),用于对生成CRC校验码后的数据帧进行缓存,缓存完成后发送至插"0"数据缓存模块(114);

插"0"数据缓存模块(114),用于对接收的数据帧进行插"0"操作,插"0"操作完成后再次进行缓存,缓存完成后的数据帧为HDLC帧。

3.根据权利要求2所述的一种基于FPGA的多模式HDLC控制器,其特征在于,发送数据 FIF0缓存模块(111)包括1号FIF0缓存器和参数设置模块;

1号FIF0缓存器,用于缓存接收的并行数据,并将并行数据转化为串行数据;

参数设置模块,用于根据主控单元(300)下发的配置指令对1号FIF0缓存器中的串行数据中每一帧数据的帧头、帧尾个数及波特率进行配置,还用于发送同步时钟信号;

1号FIFO缓存器,还用于发送配置完成的数据帧至CRC生成模块(112)。

- 4.根据权利要求2所述的一种基于FPGA的多模式HDLC控制器,其特征在于,数据与CRC 缓存模块(113)采用FIF0缓存器实现,该FIF0缓存器命名为2号FIF0缓存器。

- 5.根据权利要求2所述的一种基于FPGA的多模式HDLC控制器,其特征在于,插"0"数据 缓存模块(114)包括插"0"处理模块和3号FIF0缓存器:

插"0"处理模块,用于对接收的数据帧中每一帧数据的有效数据和CRC校验码进行插"0"操作,插"0"操作完成后通过3号FIF0缓存器进行缓存,缓存完成后的数据帧作为HDLC帧发送至与控制器通信的装置。

6.根据权利要求1所述的一种基于FPGA的多模式HDLC控制器,其特征在于,HDLC数据接收模块(120)包括标志字检测模块(121)、删"0"数据缓存模块(122)和解析帧数据缓存模块(123);

标志字检测模块(121),用于接收编码成HDLC帧的串行数据,并将串行数据转换成并行数据后,同时,根据接收的同步时钟信号提取并行数据中每一帧数据中的有效数据和CRC校验码,并将提取完成的有效数据和CRC校验码发送至删"0"数据缓存模块(122);

删"0"数据缓存模块(122),用于对每一帧数据中的有效数据和CRC校验码进行删"0"操作,再对删"0"后的有效数据所对应的CRC校验码进行校验,并将校验成功的CRC校验码所对应的删"0"后的有效数据发送至解析帧数据缓存模块(123);

解析帧数据缓存模块(123),用于对删"0"后的有效数据进行缓存,缓存后的数据以并行传输方式发送至数据缓存单元(200)。

7.根据权利要求6所述的一种基于FPGA的多模式HDLC控制器,其特征在于,删"0"数据缓存模块(122)包括FIFO使能模块、4号FIFO缓存器和CRC校验模块;

FIFO使能模块,用于对每一帧数据中的有效数据和CRC校验码进行删"0"操作,并将删"0"后的有效数据发送至4号FIFO缓存器,同时,将该删"0"后的有效数据和删"0"后的CRC校验码同时发送至CRC校验模块;

CRC校验模块,根据接收的删"0"后的有效数据生成CRC匹配码,该CRC匹配码用于对删"0"后的有效数据所对应CRC校验码进行校验,当CRC匹配码和CRC校验码匹配成功,则,发送匹配成功使能信号至4号FIF0缓存器;

4号FIF0缓存器,根据接收的匹配成功使能信号,发送与匹配成功的CRC校验码所对应的删"0"后的有效数据至解析帧数据缓存模块(123)。

- 8.根据权利要求6或7所述的一种基于FPGA的多模式HDLC控制器,其特征在于,解析帧数据缓存模块(123)采用FIF0缓存器实现,该FIF0缓存器命名为5号FIF0缓存器。

- 9.根据权利要求1所述的一种基于FPGA的多模式HDLC控制器,其特征在于,标准传输模式数据缓存模块(210)采用一个FIF0缓存器实现;

定时传输模式数据缓存模块(220)采用一个FIF0缓存器实现;

响应传输模式数据缓存模块 (230) 采用多个FIF0缓存器实现,且响应传输模式数据缓存模块 (230) 根据接收的数据发送指令,使相应的某个FIF0缓存器进行响应,并从该FIF0缓存器中发出并行数据。

# 一种基于FPGA的多模式HDLC控制器

#### 技术领域

[0001] 本发明涉及数据通信领域,具体涉及一种基于FPGA的多模式HDLC控制器。

[0002] FPGA的英文全称为:Field Programmable Gate Array,FPGA,中文翻译为:现场可编辑门阵列,HDLC的英文全称为:High-level Data Link Control,中文翻译为:高级数据链路控制。

#### 背景技术

[0003] HDLC是面向比特的数据链路控制协议的典型协议,该协议不依赖于任何一种字符编码集。HDLC协议具有错误检测能力强大、同步传输速率高效等特性,在通信领域有着十分广泛的应用。

[0004] 传统实现HDLC协议的方式主要有软件实现和硬件实现两种方法。软件方法主要是通过CPU (Central Processing Unit,CPU)或DSP (Digital Signal Processing,DSP)方式实现,但由于CPU或DSP是基于8位或16位进行处理,而HDLC协议是基于比特处理,因而实现HDLC协议时会增加CPU或DSP的负荷,使性能低下;硬件方法主要是通过专用的HDLC协议处理芯片实现HDLC协议的解析与生成,处理速度较快,但专用芯片存在包含的接口控制寄存器较多、专用性太强和不支持灵活配置等缺点。FPGA具有丰富的系统门、逻辑单元、块RAM和I/0管脚等硬件资源,采用硬件技术处理信号,既可以通过软件反复编程使用,又能够兼顾速度和灵活性,并能并行处理多路信号,在数据通信领域得到广泛的应用。

[0005] 传统使用FPGA设计的HDLC控制器具有良好的可移植性,可以根据需求在不同型号的FPGA上进行移植。但由于HDLC协议的实现包括很多功能模块,如果每个模块都是通过硬件描述语言HDL逐句描述,则会导致HDLC控制器设计复杂、调试繁琐,工作量较大。且设计的HDLC控制器多为针对特定需要而研制的,功能单一,在不同平台进行移植时要进行较大改动。因此,以上问题亟需解决。

## 发明内容

[0006] 本发明是为了解决传统使用FPGA实现的HDLC控制器中每个模块都单纯通过HDL逐句描述,导致设计复杂、调试繁琐及功能单一的问题,本发明提供了一种基于FPGA的多模式HDLC控制器。

[0007] 本发明的一种基于FPGA的多模式HDLC控制器,该控制器采用FPGA实现,FPGA包括HDLC协议传输单元、数据缓存单元和主控单元;

[0008] HDLC协议传输单元包括HDLC数据发送模块和HDLC数据接收模块:

[0009] (一) 当控制器用于向与其通信的装置发送HDLC数据时,

[0010] 主控单元解析从控制总线下发的控制指令,根据预设的传输模式将解析完成的控制指令控制数据缓存单元将其内部存储的待发送并行数据写入HDLC数据发送模块,HDLC数据发送模块根据主控单元下发的配置指令,将写入的并行数据转化为串行数据,并将串行数据编码成HDLC帧后,发送至与控制器通信的装置,同时,当串行数据编码成HDLC帧后,

HDLC数据发送模块还用于发送配置完成使能信号至主控单元;

[0011] HDLC数据发送模块还向与控制器通信的装置发送同步时钟信号,从而完成控制器向与其通信的装置发送HDLC数据:

[0012] (二) 当控制器用于接收与其通信的装置发送来的HDLC数据时,

[0013] HDLC数据接收模块,用于接收同步时钟信号和编码成HDLC帧的串行数据,将接收的串行数据转化为并行数据,并对并行数据进行解码,解码完成后的并行数据缓存至数据缓存单元,同时,HDLC数据接收模块,还用于向主控单元实时发送数据传输状态信息;

[0014] 数据缓存单元将并行数据缓存完成的使能信息发送至主控单元,主控单元根据接收到使能信息向数据缓存单元发送控制指令,从而从数据缓存单元内读取并行数据,并将读取的并行数据发送至数据总线,完成控制器对与其通信的装置发送来的HDLC数据的接收。

[0015] 作为优选,HDLC数据发送模块包括发送数据FIF0缓存模块、CRC生成模块、数据与CRC缓存模块和插"0"数据缓存模块;

[0016] 发送数据FIF0缓存模块,用于缓存接收的并行数据,并将并行数据转化为串行数据,再根据主控单元下发的配置指令对串行数据中每一帧数据的帧头、帧尾个数及波特率进行配置,配置完成后,发送配置完成的数据帧至CRC生成模块,同时,还发送配置完成使能信号至主控单元;其中,配置完成的数据帧中的每一帧数据包括帧头、有效数据和帧尾;

[0017] 发送数据FIF0缓存模块在发送数据帧的同时,还用于发送同步时钟信号:

[0018] CRC生成模块,用于对接收的每一帧数据生成CRC校验码,并将生成CRC校验码后的数据帧发送至数据与CRC缓存模块,CRC校验码位于每一帧数据中有效数据与帧尾之间:

[0019] 数据与CRC缓存模块,用于对生成CRC校验码后的数据帧进行缓存,缓存完成后发送至插"0"数据缓存模块;

[0020] 插"0"数据缓存模块,用于对接收的数据帧进行插"0"操作,插"0"操作完成后再次进行缓存,缓存完成后的数据帧为HDLC帧。

[0021] 作为优选,发送数据FIF0缓存模块包括1号FIF0缓存器和参数设置模块;

[0022] 1号FIF0缓存器,用干缓存接收的并行数据,并将并行数据转化为串行数据:

[0023] 参数设置模块,用于根据主控单元下发的配置指令对1号FIF0缓存器中的串行数据中每一帧数据的帧头、帧尾个数及波特率进行配置,还用于发送同步时钟信号;

[0024] 1号FIF0缓存器,还用于发送配置完成的数据帧至CRC生成模块。

[0025] 作为优选,数据与CRC缓存模块采用FIF0缓存器实现,该FIF0缓存器命名为2号FIF0缓存器。

[0026] 作为优选,插"0"数据缓存模块包括插"0"处理模块和3号FIF0缓存器;

[0027] 插"0"处理模块,用于对接收的数据帧中每一帧数据的有效数据和CRC校验码进行插"0"操作,插"0"操作完成后通过3号FIF0缓存器进行缓存,缓存完成后的数据帧作为HDLC帧发送至与控制器通信的装置。

[0028] 作为优选, HDLC数据接收模块包括标志字检测模块、删"0"数据缓存模块和解析帧数据缓存模块:

[0029] 标志字检测模块,用于接收编码成HDLC帧的串行数据,并将串行数据转换成并行数据后,同时,根据接收的同步时钟信号提取并行数据中每一帧数据中的有效数据和CRC校

验码,并将提取完成的有效数据和CRC校验码发送至删"0"数据缓存模块;

[0030] 删"0"数据缓存模块,用于对每一帧数据中的有效数据和CRC校验码进行删"0"操作,再对删"0"后的有效数据所对应的CRC校验码进行校验,并将校验成功的CRC校验码所对应的删"0"后的有效数据发送至解析帧数据缓存模块;

[0031] 解析帧数据缓存模块,用于对删"0"后的有效数据进行缓存,缓存后的数据以并行传输方式发送至数据缓存单元。

[0032] 作为优选,删"0"数据缓存模块包括FIF0使能模块、4号FIF0缓存器和CRC校验模块;

[0033] FIF0使能模块,用于对每一帧数据中的有效数据和CRC校验码进行删"0"操作,并将删"0"后的有效数据发送至4号FIF0缓存器,同时,将该删"0"后的有效数据和删"0"后的CRC校验码同时发送至CRC校验模块:

[0034] CRC校验模块,根据接收的删"0"后的有效数据生成CRC匹配码,该CRC匹配码用于对删"0"后的有效数据所对应CRC校验码进行校验,当CRC匹配码和CRC校验码匹配成功,则,发送匹配成功使能信号至4号FIF0缓存器;

[0035] 4号FIF0缓存器,根据接收的匹配成功使能信号,发送与匹配成功的CRC校验码所对应的删"0"后的有效数据至解析帧数据缓存模块。

[0036] 作为优选,解析帧数据缓存模块采用FIF0缓存器实现,该FIF0缓存器命名为5号FIF0缓存器。

[0037] 作为优选,主控单元包括顶层控制模块、标准传输模式控制模块、定时传输模式控制模块和响应传输模式控制模块:

[0038] 数据缓存单元包括标准传输模式数据缓存模块、定时传输模式数据缓存模块和响应传输模式数据缓存模块;

[0039] 顶层控制模块,用于同时与控制总线和数据总线进行通信,还用于同时与标准传输模式控制模块、定时传输模式控制模块和响应传输模式控制模块进行通信,并对三种传输模式控制模块进行切换:

[0040] 标准传输模式控制模块,用于向标准传输模式数据缓存模块发送数据发送指令或 从标准传输模式数据缓存模块接收与控制器通信的装置发送过来的数据,

[0041] 标准传输模式数据缓存模块的并行数据输入端用于接收从HDLC数据接收模块发出的并行数据,标准传输模式数据缓存模块的并行数据输出端通过信号多路复用模块将其输出的并行数据发送至HDLC数据发送模块;

[0042] 定时传输模式控制模块,用于定时向定时传输模式数据缓存模块发送数据发送指令,定时传输模式数据缓存模块根据接收的数据发送指令,通过信号多路复用模块向HDLC数据发送模块发送并行数据:

[0043] 响应传输模式控制模块,用于向响应传输模式数据缓存模块发送数据发送指令,响应传输模式数据缓存模块根据接收的数据发送指令,进行相应的响应后,通过信号多路 复用模块向HDLC数据发送模块发送并行数据;

[0044] 信号多路复用模块,用于对数据传输通路进行切换。

[0045] 作为优选,标准传输模式数据缓存模块采用一个FIF0缓存器实现:

[0046] 定时传输模式数据缓存模块采用一个FIF0缓存器实现;

[0047] 响应传输模式数据缓存模块采用多个FIF0缓存器实现,且响应传输模式数据缓存模块根据接收的数据发送指令,使相应的某个FIF0缓存器进行响应,并从该FIF0缓存器中发出并行数据。

[0048] 本发明带来的有益效果是,

[0049] (1) 本发明所述基于FPGA的多模式HDLC控制器无需对每个模块通过HDL逐句描,通过各功能模块的功能及连接关系,可实现串/并数据间协议的转化,控制器设计简单,调试时只需校验各模块端口的信号,则可完成对控制器的调试。

[0050] (2) 本发明设计的HDLC协议传输模块充分利用FIF0性质,以多级FIF0 IP核串行连接为设计主体,并通过HDL设计中间控制电路,进而完成HDLC协议的解帧与生成功能,降低了HDLC控制器设计复杂度,减少设计代码量,具有方便调试、易于维护的特点;由于HDLC协议实现的过程中,HDLC协议解析与生成以串行顺序过程为主,而FIF0恰具有"先进先出"按顺序执行的特点,本发明通过FPGA设计平台的提供FIF0模块,充分利用FIF0该特点进行设计,减少代码设计量,降低设计复杂度;

[0051] (3) 本发明包含标准传输、响应传输和定时传输三种工作模式,可根据设计需求进行相应的功能的增减,具有方便灵活、易于功能剪裁等特点,且适用性强;

[0052] (4) 本发明充分利用FPGA拥有丰富硬件资源的特点,无需额外专用芯片即可实现 多模式HDLC控制器设计,有利于节约硬件电路板面积和成本;

[0053] (5) 发送数据时, 帧头和帧尾个数可以灵活设置, 避免只能发送单一数量的不足; 接收数据时, 无需发送与接收双方约定好帧头与帧尾个数, 通过标志字检测模块可以自动准确的去除任意数量的帧头和帧尾。

## 附图说明

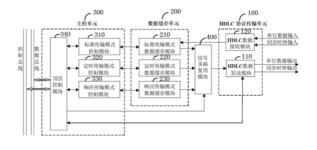

[0054] 图1为本发明所述一种基于FPGA的多模式HDLC控制器的原理示意图:

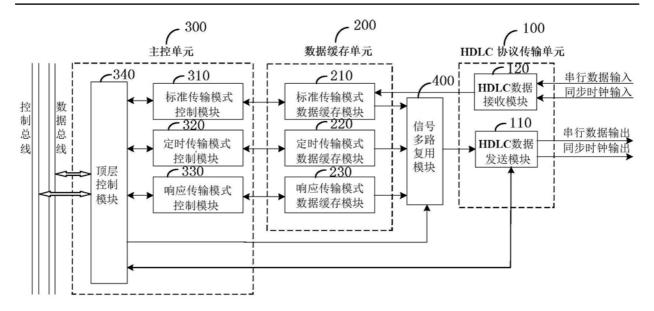

[0055] 图2为HDLC数据发送模块的原理示意图:

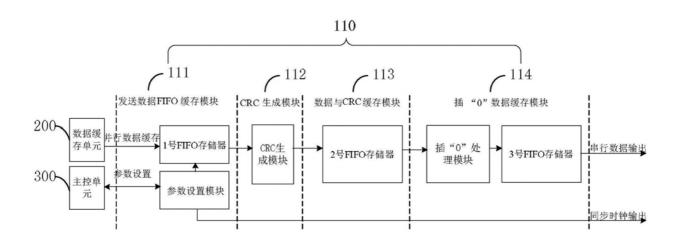

[0056] 图3为HDLC数据接收模块的原理示意图

#### 具体实施方式

[0057] 下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动的前提下所获得的所有其它实施例,都属于本发明保护的范围。

[0058] 需要说明的是,在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。

[0059] 下面结合附图和具体实施例对本发明作进一步说明,但不作为本发明的限定。

[0060] 参见图1说明本实施方式,本实施方式所述的一种基于FPGA的多模式HDLC控制器,该控制器采用FPGA实现,FPGA包括HDLC协议传输单元、数据缓存单元和主控单元;

[0061] HDLC协议传输单元包括HDLC数据发送模块和HDLC数据接收模块:

[0062] (二) 当控制器用于向与其通信的装置发送HDLC数据时,

[0063] 主控单元解析从控制总线下发的控制指令,根据预设的传输模式将解析完成的控

制指令控制数据缓存单元将其内部存储的待发送并行数据写入HDLC数据发送模块,HDLC数据发送模块根据主控单元下发的配置指令,将写入的并行数据转化为串行数据,并将串行数据编码成HDLC帧后,发送至与控制器通信的装置,同时,当串行数据编码成HDLC帧后,HDLC数据发送模块还用于发送配置完成使能信号至主控单元;

[0064] HDLC数据发送模块还向与控制器通信的装置发送同步时钟信号,从而完成控制器向与其通信的装置发送HDLC数据;

[0065] (二) 当控制器用于接收与其通信的装置发送来的HDLC数据时,

[0066] HDLC数据接收模块,用于接收同步时钟信号和编码成HDLC帧的串行数据,将接收的串行数据转化为并行数据,并对并行数据进行解码,解码完成后的并行数据缓存至数据缓存单元,同时,HDLC数据接收模块,还用于向主控单元实时发送数据传输状态信息;

[0067] 数据缓存单元将并行数据缓存完成的使能信息发送至主控单元,主控单元根据接收到使能信息向数据缓存单元发送控制指令,从而从数据缓存单元内读取并行数据,并将读取的并行数据发送至数据总线,完成控制器对与其通信的装置发送来的HDLC数据的接收。

[0068] 本实施方式中,本发明HDLC控制器通过各功能模块的功能及连接关系,可实现串/并数据间协议的转化,控制器设计简单,调试时只需校验各模块端口的信号,则可完成对控制器的调试。HDLC协议传输单元实现了HDLC协议的解析与生成

[0069] HDLC控制器的结构简单、降低设计复杂度,并能灵活配置控制器的各参数,提高了系统的灵活性和设计效率,具有重要的实际应用价值。

[0070] 参见图2说明本优选实施方式,本优选实施方式中,HDLC数据发送模块包括发送数据FIF0缓存模块、CRC生成模块、数据与CRC缓存模块和插"0"数据缓存模块:

[0071] 发送数据FIF0缓存模块,用于缓存接收的并行数据,并将并行数据转化为串行数据,再根据主控单元下发的配置指令对串行数据中每一帧数据的帧头、帧尾个数及波特率进行配置,配置完成后,发送配置完成的数据帧至CRC生成模块,同时,还发送配置完成使能信号至主控单元;其中,配置完成的数据帧中的每一帧数据包括帧头、有效数据和帧尾;

[0072] 发送数据FIF0缓存模块在发送数据帧的同时,还用于发送同步时钟信号:

[0073] CRC生成模块,用于对接收的每一帧数据生成CRC校验码,并将生成CRC校验码后的数据帧发送至数据与CRC缓存模块,CRC校验码位于每一帧数据中有效数据与帧尾之间;

[0074] 数据与CRC缓存模块,用于对生成CRC校验码后的数据帧进行缓存,缓存完成后发送至插"0"数据缓存模块;

[0075] 插"0"数据缓存模块,用于对接收的数据帧进行插"0"操作,插"0"操作完成后再次进行缓存,缓存完成后的数据帧为HDLC帧。

[0076] 本优选实施方式中,通过发送数据FIF0缓存模块对有效数据添加帧头及帧尾个数,再通过CRC生成模块生成CRC校验码,并将CRC校验码插入在有效数据和帧尾之间,然后,再对有效数据和CRC校验码进行插"0"操作,从而完成对待发送的串行数据的编码,整个编码过程的编码程度高,在数据发送时,首先根据配置的发送帧头与帧尾个数发送相应个数的帧头,再依次发送有效数据和CRC校验码,最后发送相应个数的帧尾。

[0077] HDLC数据发送模块发送数据时,帧头和帧尾个数可以灵活设置,避免只能发送单一数量的不足。

[0078] 本实施方式中,可选择CCITT-16的校验方式,实际应用中也可以根据不同需求替换为其他校验方式。

[0079] 参见图2说明本优选实施方式,本优选实施方式中,发送数据FIF0缓存模块包括1号FIF0缓存器和参数设置模块;

[0080] 1号FIF0缓存器,用于缓存接收的并行数据,并将并行数据转化为串行数据;

[0081] 参数设置模块,用于根据主控单元下发的配置指令对1号FIF0缓存器中的串行数据中每一帧数据的帧头、帧尾个数及波特率进行配置,还用于发送同步时钟信号;

[0082] 1号FIF0缓存器,还用于发送配置完成的数据帧至CRC生成模块。

[0083] 数据与CRC缓存模块采用FIF0缓存器实现,该FIF0缓存器命名为2号FIF0缓存器。

[0084] 插"0"数据缓存模块包括插"0"处理模块和3号FIF0缓存器;

[0085] 插"0"处理模块,用于对接收的数据帧中每一帧数据的有效数据和CRC校验码进行插"0"操作,插"0"操作完成后通过3号FIF0缓存器进行缓存,缓存完成后的数据帧作为HDLC帧发送至与控制器通信的装置。

[0086] 本优选实施方式中,以多级FIF0(First Input First Output,FIF0)IP (Intellectual Property,IP)核串行连接为设计主体,并通过硬件描述语言设计中间控制电路,降低HDLC控制器设计复杂度。

[0087] 参见图3说明本优选实施方式,本优选实施方式中,HDLC数据接收模块包括标志字检测模块、删"0"数据缓存模块和解析帧数据缓存模块;

[0088] 标志字检测模块,用于接收编码成HDLC帧的串行数据,并将串行数据转换成并行数据后,同时,根据接收的同步时钟信号提取并行数据中每一帧数据中的有效数据和CRC校验码,并将提取完成的有效数据和CRC校验码发送至删"0"数据缓存模块;

[0089] 删"0"数据缓存模块,用于对每一帧数据中的有效数据和CRC校验码进行删"0"操作后,再对删"0"后的有效数据所对应的CRC校验码进行校验,并将校验成功的CRC校验码所对应的删"0"后的有效数据发送至解析帧数据缓存模块:

[0090] 解析帧数据缓存模块,用于对删"0"后的有效数据进行缓存,缓存后的数据以并行传输方式发送至数据缓存单元。

[0091] 本优选实施方式中,HDLC数据接收模块接收数据时,无需发送与接收双方约定好帧头与帧尾个数,通过标志字检测模块可以自动准确的去除任意数量的帧头和帧尾,提高数据接收速度。

[0092] 参见图3说明本优选实施方式,本优选实施方式中,删"0"数据缓存模块包括FIF0 使能模块、4号FIF0缓存器和CRC校验模块:

[0093] FIFO使能模块,用于对每一帧数据中的有效数据和CRC校验码进行删"0"操作,并将删"0"后的有效数据发送至4号FIFO缓存器,同时,将该删"0"后的有效数据和删"0"后的CRC校验码同时发送至CRC校验模块;

[0094] CRC校验模块,根据接收的删"0"后的有效数据生成CRC匹配码,该CRC匹配码用于对删"0"后的有效数据所对应CRC校验码进行校验,当CRC匹配码和CRC校验码匹配成功,则,发送匹配成功使能信号;

[0095] 4号FIF0缓存器,根据接收的匹配成功使能信号,发送与匹配成功的CRC校验码所对应的删"0"后的有效数据至解析帧数据缓存模块。

[0096] 本优选实施方式中,删"0"数据缓存模块包括两个功能模块,结构简单,可自动准确的去除任意数量的帧头和帧尾,直接获得删"0"后的有效数据和删"0"后的CRC校验码,信息提取过程直接、简单。

[0097] 参见图3说明本优选实施方式,本优选实施方式中,解析帧数据缓存模块采用FIF0 缓存器实现,该FIF0缓存器命名为5号FIF0缓存器。

[0098] 本优选实施方式中,解析帧数据缓存模块采用FIF0缓存器实现,便于实现及产业化应用。

[0099] 参见图1说明本优选实施方式,本优选实施方式中,主控单元包括顶层控制模块、标准传输模式控制模块、定时传输模式控制模块和响应传输模式控制模块;

[0100] 数据缓存单元包括标准传输模式数据缓存模块、定时传输模式数据缓存模块和响应传输模式数据缓存模块;

[0101] 顶层控制模块,用于同时与控制总线和数据总线进行通信,还用于同时与标准传输模式控制模块、定时传输模式控制模块和响应传输模式控制模块进行通信,并对三种传输模式控制模块进行切换;

[0102] 标准传输模式控制模块,用于向标准传输模式数据缓存模块发送数据发送指令或 从标准传输模式数据缓存模块接收与控制器通信的装置发送过来的数据,

[0103] 标准传输模式数据缓存模块的并行数据输入端用于接收从HDLC数据接收模块发出的并行数据,标准传输模式数据缓存模块的并行数据输出端通过信号多路复用模块将其输出的并行数据发送至HDLC数据发送模块:

[0104] 定时传输模式控制模块,用于定时向定时传输模式数据缓存模块发送数据发送指令,定时传输模式数据缓存模块根据接收的数据发送指令,通过信号多路复用模块向HDLC数据发送模块发送并行数据;

[0105] 响应传输模式控制模块,用于向响应传输模式数据缓存模块发送数据发送指令,响应传输模式数据缓存模块根据接收的数据发送指令,进行相应的响应后,通过信号多路 复用模块向HDLC数据发送模块发送并行数据:

[0106] 信号多路复用模块,用于对数据传输通路进行切换。

[0107] 本优选实施方式中,主控单元可实现传输模式选择、参数配置和信号控制等功能,实现对不同模式的调控;HDLC协议传输单元包括HDLC数据发送模块和HDLC数据接收模块,实现HDLC协议的解析与生成;为实现在标准传输模式、定时传输模式和响应传输模式下对数据缓存的需求,数据缓存模块针对不同传输模式分别设计数据缓存子模块,完成基于FPGA实现多模式HDLC控制器的设计。

[0108] 标准传输模式控制模块为标准的数据发送与接收模式;该种模式下,当发送数据时,主控单元的顶层控制模块与标准传输模式控制模块将从数据总线接收的数据存入标准传输模式数据缓存模块作为发送的数据源;由由顶层控制模块按照从控制总线接收的指令配置HDLC协议传输单元的波特率、帧长、发送帧头与帧尾个数等参数;当接收数据时,把HDLC数据接收模块接收到的数据缓存到标准传输模式控制模块中备用。

[0109] 定时传输模式控制模块为只能进行发送数据的模式;此模式下每间隔一定时间会自动发送一帧数据。

[0110] 当发送数据时,主控单元的顶层控制模块与定时传输模式控制模块将从数据总线

接收的数据存入定时传输模式数据缓存模块作为发送的数据源;由顶层控制模块按照从控制总线接收的指令配置HDLC协议传输单元的波特率、定时周期、帧长、发送帧头与帧尾个数等参数;每到设置的定时周期,如定时周期设置为2.5ms,则每间隔2.5ms,会产生一个发送使能,若定时传输模式数据缓存模块的数据个数不为0,则按照配置参数自动发送一帧,不断循环,直至退出此模式或缓存个数为0。

[0111] 响应传输模式控制模块为只能进行发送数据的模式。

[0112] 参见图1和图3说明本优选实施方式,本优选实施方式中,

[0113] 标准传输模式数据缓存模块采用一个FIF0缓存器实现:

[0114] 定时传输模式数据缓存模块采用一个FIF0缓存器实现;

[0115] 响应传输模式数据缓存模块采用多个FIF0缓存器实现,且响应传输模式数据缓存模块根据接收的数据发送指令,使相应的某个FIF0缓存器进行响应,并从该FIF0缓存器中发出并行数据。

[0116] 本优选实施方式中,以多级FIF0(First Input First Output,FIF0)IP (Intellectual Property,IP)核串行连接为设计主体,并通过硬件描述语言设计中间控制电路,降低HDLC控制器设计复杂度。

[0117] 当发送数据时,主控单元的顶层控制模块与响应传输模式控制模块将从数据总线接收的数据存入响应传输模式数据缓存模块作为发送的数据源;由顶层控制模块按照从控制总线接收的指令配置HDLC协议传输单元的波特率、数据源所在FIF0(respond\_FIF0n,n为1~5)、帧长、发送帧头与帧尾个数等参数。

[0118] 虽然在本文中参照了特定的实施方式来描述本发明,但是应该理解的是,这些实施例仅仅是本发明的原理和应用的示例。因此应该理解的是,可以对示例性的实施例进行许多修改,并且可以设计出其它的布置,只要不偏离所附权利要求所限定的本发明的精神和范围。应该理解的是,可以通过不同于原始权利要求所描述的方式来结合不同的从属权利要求和本文中所述的特征。还可以理解的是,结合单独实施例所描述的特征可以使用在其它所述实施例。

图1

图2

图3