### (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 106919240 B (45) 授权公告日 2022. 12. 09

- (21)申请号 201511001586.4

- (22) 申请日 2015.12.28

- (65) 同一申请的已公布的文献号 申请公布号 CN 106919240 A

- (43) 申请公布日 2017.07.04

- (73) 专利权人 伊姆西IP控股有限责任公司 地址 美国马萨诸塞州

- (72) 发明人 陈警 杨涛 崔希志

- (74) **专利代理机构** 北京市金杜律师事务所 11256

专利代理师 王茂华

(51) Int.CI.

G06F 1/26 (2006.01)

#### (56) 对比文件

- CN 103576814 A, 2014.02.12

- CN 105159428 A, 2015.12.16

- CN 104977959 A, 2015.10.14

- US 2013339757 A1,2013.12.19

- US 2014229748 A1,2014.08.14

- US 2005162019 A1,2005.07.28

审查员 罗煜川

权利要求书2页 说明书9页 附图4页

#### (54) 发明名称

用于向处理器供电的方法和设备

#### (57) 摘要

本公开的实施例提供了一种用于向处理器 供电的方法、装置、附加电源和主板系统。该方法 包括:响应于接收到来自为处理器供电的供电单 元的第一信号,确定附加电源是否能够提供所要 求的额外功率,其中第一信号指示该处理器要求 的功率超过供电单元能够提供的最大功率;以及 响应于确定附加电源能够提供额外功率,至少利 用附加电源向该处理器供电。本公开的实施例能 够通过从附加电源向处理器提供所需要的额外 功率,优化处于加速模式中的处理器的性能。

1.一种用于向处理器供电的方法,包括:

在包括在总线上电池内的微处理器处,响应于接收到来自为CPU供电的供电单元的第一信号,在所述微处理器处确定附加电源是否能够提供所述CPU所要求的额外功率,定义CPU加速模式的所述第一信号指示所述CPU所要求的功率超过所述供电单元能够提供的最大功率,其中在所述CPU要求的功率超过所述供电单元的峰值功率时,所述供电单元将作为逻辑信号的所述第一信号传输给所述总线上电池而不是给所述CPU;以及

响应于确定所述附加电源能够提供所述额外功率,至少利用作为所述附加电源的所述总线上电池向所述CPU供电。

2.根据权利要求1所述的方法,还包括:

响应于未接收到来自所述供电单元的所述第一信号,停止利用所述附加电源向所述 CPU供电。

3.根据权利要求1所述的方法,还包括:

响应于所述供电单元掉电,利用所述附加电源向所述CPU供电。

4.一种用于控制向CPU供电的装置,包括:

包括微处理器的总线上电池,所述微处理器被配置为:响应于接收到来自为所述CPU供电的供电单元的第一信号,确定附加电源是否能够提供所述CPU所要求的额外功率,定义CPU加速模式的所述第一信号指示所述CPU要求的功率超过所述供电单元能够提供的最大功率,其中在所述CPU要求的功率超过所述供电单元的峰值功率时,所述总线上电池接收作为逻辑信号的所述第一信号,并且其中所述总线上电池被配置为响应于确定所述附加电源能够提供所述额外功率,使得至少利用作为所述附加电源的所述总线上电池向所述CPU供电。

5.根据权利要求4所述的装置,还包括:

第二信号发送模块,被配置为响应于确定所述附加电源不能够提供所述额外功率,向所述CPU发送第二信号,以降低所述CPU的时钟频率。

- 6.根据权利要求5所述的装置,其中所述第二信号经由所述装置的第二保留引脚被发送。

- 7.根据权利要求4所述的装置,

其中响应于未接收到来自所述供电单元的所述第一信号,所述微处理器还被配置为使得停止利用所述附加电源向所述CPU供电。

8.根据权利要求4所述的装置,

其中响应于所述供电单元掉电,所述微处理器还被配置为使得利用所述附加电源向所述CPU供电。

9. 一种用于向CPU供电的附加电源,包括:

用于控制向所述CPU供电的装置,所述装置包括总线上电池,所述总线上电池包括微处理器,所述微处理器被配置为:

响应于接收到来自为所述CPU供电的供电单元的第一信号,确定所述附加电源是否能够提供所述CPU所要求的额外功率,定义CPU加速模式的所述第一信号指示所述CPU要求的功率超过所述供电单元能够提供的最大功率,其中在所述CPU要求的功率超过所述供电单元的峰值功率时,所述总线上电池接收作为逻辑信号的所述第一信号;以及

响应于确定所述附加电源能够提供所述额外功率,使得至少利用作为所述附加电源的所述总线上电池向所述CPU供电。

10.根据权利要求9所述的附加电源,其中所述装置还被配置为:

响应于确定所述附加电源不能够提供所述额外功率,向所述CPU发送第二信号,以降低所述CPU的时钟频率。

- 11.根据权利要求10所述的附加电源,其中所述第二信号经由所述装置的第二保留引脚被发送。

- 12.根据权利要求9所述的附加电源,其中所述装置还被配置为:

响应于未接收到来自所述供电单元的所述第一信号,使得停止利用所述附加电源向所述CPU供电。

13.根据权利要求9所述的附加电源,其中所述装置还被配置为:

响应于所述供电单元掉电,使得利用所述附加电源向所述CPU供电。

14.一种主板系统,包括:

CPU:

用于向所述CPU供电的供电单元;

附加电源:以及

控制装置,所述控制装置被配置为:

在包括在总线上电池内的微处理器处,响应于接收到来自所述供电单元的第一信号,确定所述附加电源是否能够提供所述CPU所要求的额外功率,定义CPU加速模式的所述第一信号指示所述CPU要求的功率超过所述供电单元能够提供的最大功率,其中在所述CPU要求的功率超过所述供电单元的峰值功率时,所述供电单元将作为逻辑信号的所述第一信号传输给所述总线上电池而不是给所述CPU;

响应于确定所述附加电源能够提供所述额外功率,使得至少利用作为所述附加电源的所述总线上电池向所述CPU供电。

15.根据权利要求14所述的主板系统,其中所述控制装置还被配置为:

响应于确定所述附加电源不能够提供所述额外功率,向所述CPU发送第二信号,以降低所述CPU的时钟频率。

- 16.根据权利要求14所述的主板系统,其中所述控制装置经由第二保留引脚向所述CPU 发送第二信号。

- 17.根据权利要求14所述的主板系统,其中所述控制装置还被配置为:

响应于未接收到来自所述供电单元的所述第一信号,使得停止利用所述附加电源向所述CPU供电。

- 18.根据权利要求14所述的主板系统,其中所述控制装置还被配置为:

- 响应于所述供电单元掉电,使得利用所述附加电源向所述CPU供电。

- 19.根据权利要求14所述的主板系统,其中所述控制装置位于所述附加电源中。

## 用于向处理器供电的方法和设备

#### 技术领域

[0001] 本公开的实施例总体涉及处理器领域,具体涉及一种用于向处理器供电的方法、装置、附加电源和主板系统。

#### 背景技术

[0002] 在计算机系统中,系统的整体性能由平台的中央处理单元 (CPU) 主导。通常,更高性能的CPU将从系统的供电单元 (PSU) 获取更多的功率。具有加速模式的CPU可以通过在短时期内增加时钟频率来提升CPU性能,例如英特尔<sup>TM</sup>公司设计的具有睿频 (TurboBoost <sup>TM</sup>) 模式的CPU。然而,这要求从PSU获取更多的额外功率。当处理器上的工作负载要求更高的性能并且该处理器处于其功率、电流和发热量的极限之下时,该处理器的时钟将增加工作频率以满足要求。例如,针对酷睿 (Core <sup>TM</sup>) i7-920XM处理器,正常工作频率为2.0GHz。当处于加速模式中时,单个核的最大频率将增加至3.2GHz。

[0003] 然而,在当前的系统架构中,由于所要求的额外功率上的限制,CPU加速模式可能不能够被彻底实现。一旦CPU要求的功率超过PSU的峰值功率,PSU将向CPU发送PROCHOT#信号以迫使CPU降低其时钟频率,而降低时钟频率意味着降低CPU的计算性能。

[0004] 因此,本领域需要一种方法以解决上述的问题,以优化CPU的性能。

#### 发明内容

[0005] 本公开的实施例旨在提供一种用于向处理器供电的方法、装置、附加电源和主板系统。

[0006] 根据本公开的第一方面,提供了一种用于向处理器供电的方法。该方法包括响应于接收到来自为处理器供电的供电单元的第一信号,确定附加电源是否能够提供所要求的额外功率,其中第一信号指示该处理器要求的功率超过供电单元能够提供的最大功率。该方法还包括响应于确定附加电源能够提供额外功率,至少利用附加电源向该处理器供电。

[0007] 在一些实施例中,该方法还包括响应于确定附加电源不能够提供额外功率,向该处理器发送第二信号,以降低该处理器的时钟频率。

[0008] 在一些实施例中,该方法还包括响应于未接收到来自供电单元的第一信号,停止利用附加电源向该处理器供电。

[0009] 在一些实施例中,该方法还包括响应于供电单元掉电,利用附加电源向该处理器供电。

[0010] 根据本公开的第二方面,提供了一种用于控制向处理器供电的装置。该装置包括功率确定模块,被配置为响应于接收到来自为处理器供电的供电单元的第一信号,确定附加电源是否能够提供所要求的额外功率,其中第一信号指示该处理器要求的功率超过供电单元能够提供的最大功率。该装置还包括第一控制模块,被配置为响应于确定附加电源能够提供额外功率,使得至少利用附加电源向该处理器供电。

[0011] 在一些实施例中,第一信号经由该装置的第一保留引脚被接收。

[0012] 在一些实施例中,该装置还包括第二信号发送模块,被配置为响应于确定附加电源不能够提供额外功率,向该处理器发送第二信号,以降低该处理器的时钟频率。

[0013] 在一些实施例中,第二信号经由该装置的第二保留引脚被发送。

[0014] 在一些实施例中,该装置还包括第二控制模块,被配置为响应于未接收到来自供电单元的第一信号,使得停止利用附加电源向该处理器供电。

[0015] 在一些实施例中,该装置还包括第三控制模块,被配置为响应于供电单元掉电,使得利用附加电源向该处理器供电。

[0016] 根据本公开的第三方面,提供了一种用于向处理器供电的附加电源。该附加电源包括用于控制向处理器供电的装置。该装置被配置为响应于接收到来自为处理器供电的供电单元的第一信号,确定该附加电源是否能够提供所要求的额外功率,其中第一信号指示该处理器要求的功率超过供电单元能够提供的最大功率。该装置还被配置为响应于确定该附加电源能够提供额外功率,使得至少利用该附加电源向该处理器供电。

[0017] 在一些实施例中,第一信号经由该装置的第一保留引脚被接收。

[0018] 在一些实施例中,该装置还被配置为响应于确定该附加电源不能够提供额外功率,由该附加电源向该处理器发送第二信号,以降低该处理器的时钟频率。

[0019] 在一些实施例中,第二信号经由该装置的第二保留引脚被发送。

[0020] 在一些实施例中,该装置还被配置为响应于未接收到来自供电单元的第一信号,使得停止利用该附加电源向该处理器供电。

[0021] 在一些实施例中,该装置还被配置为响应于供电单元掉电,使得利用该附加电源向该处理器供电。

[0022] 根据本公开的第四方面,提供了一种主板系统。该主板系统包括处理器、用于向所述处理器供电的供电单元、附加电源以及控制装置。该控制装置被配置为响应于接收到来自供电单元的第一信号,确定附加电源是否能够提供所要求的额外功率,其中第一信号指示处理器要求的功率超过供电单元能够提供的最大功率。该控制装置还被配置为响应于确定附加电源能够提供额外功率,使得至少利用附加电源向处理器供电。

[0023] 在一些实施例中,控制装置经由第一保留引脚从供电单元接收第一信号。

[0024] 在一些实施例中,控制装置还被配置为响应于确定附加电源不能够提供额外功率,向处理器发送第二信号,以降低处理器的时钟频率。

[0025] 在一些实施例中,控制装置经由第二保留引脚向处理器发送第二信号。

[0026] 在一些实施例中,控制装置还被配置为响应于未接收到来自供电单元的第一信号,使得停止利用附加电源向处理器供电。

[0027] 在一些实施例中,控制装置还被配置为响应于供电单元掉电,使得利用附加电源向处理器供电。

[0028] 在一些实施例中,控制装置位于附加电源中。

[0029] 根据本公开的第五方面,提供了一种用于向处理器供电的计算机程序产品,所述计算机程序产品被有形地存储在非瞬态计算机可读介质上并且包括计算机可执行指令,所述计算机可执行指令在被执行时使得计算机执行所述方法的任意步骤。

[0030] 根据本公开的实施例的用于向处理器供电的方法、装置、附加电源和主板系统,能够通过从附加电源向处理器提供所需要的额外功率,优化处于加速模式中的处理器的性

能。

#### 附图说明

[0031] 在此所述的附图用来提供对本公开的进一步理解,构成本公开的一部分,本公开的示意性实施例及其说明用于解释本公开,并不构成对本公开的不当限定。在附图中:

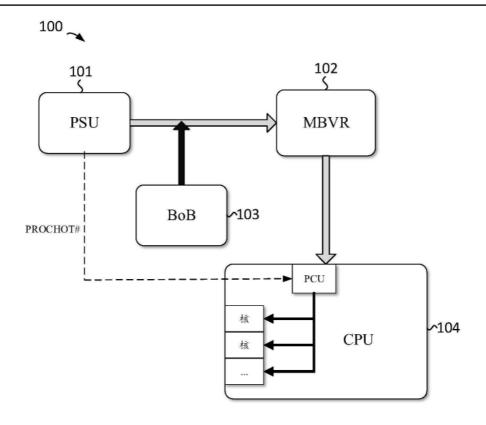

[0032] 图1图示了现有主板系统架构100的示例性框图;

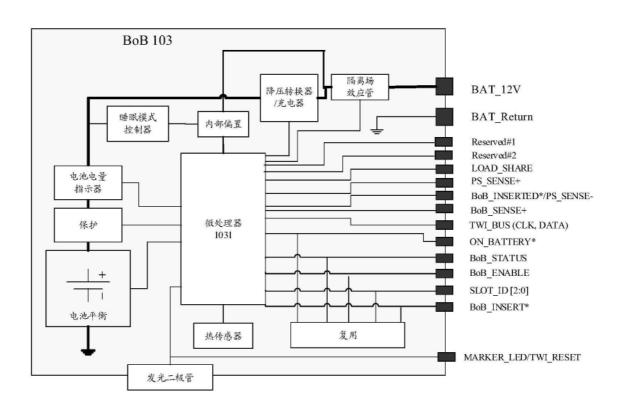

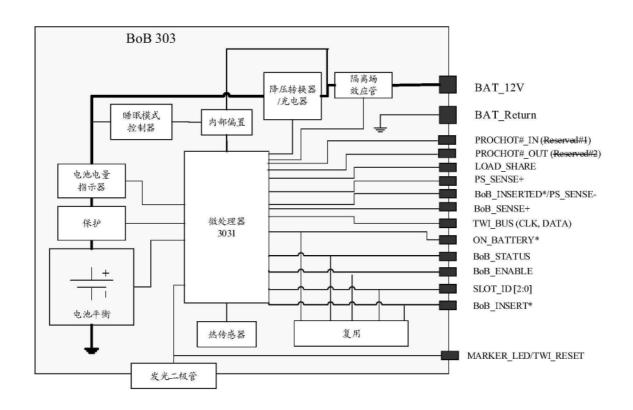

[0033] 图2图示了现有主板系统架构100中的电池模块的结构框图:

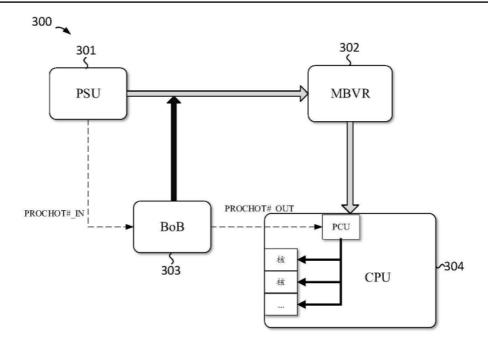

[0034] 图3图示了根据本公开的实施例的主板系统架构300的示例性框图;

[0035] 图4图示了根据本公开的实施例的主板系统架构300中的电池模块的结构框图;

[0036] 图5图示了根据本公开的实施例的主板系统架构300中各部件状态和各信号的时序关系图:

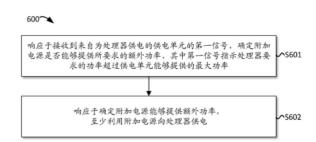

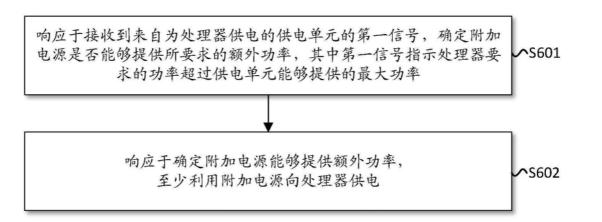

[0037] 图6图示了根据本公开的实施例的用于向处理器供电的方法600的流程图;

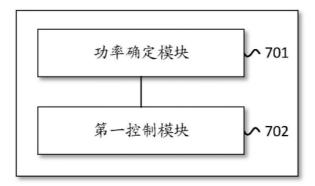

[0038] 图7图示了根据本公开的实施例的用于控制向处理器供电的装置700的框图;

[0039] 图8图示了根据本公开的实施例的用于向处理器供电的附加电源800的框图;以及

[0040] 图9图示了根据本公开的实施例的主板系统900的框图。

[0041] 在各个附图中,相同或对应的标号表示相同或对应的部分。

#### 具体实施方式

[0042] 在下文中,将参考附图详细描述本公开的各个示例性实施例。应当注意,这些附图和描述涉及的仅仅是作为示例性的实施例。应该指出的是,根据随后描述,很容易设想出此处公开的结构和方法的替换实施例,并且可以在不脱离本公开要求保护的原理的情况下使用这些替代实施例。

[0043] 应当理解,给出这些示例性实施例仅仅是为了使本领域技术人员能够更好地理解 进而实现本公开,而并非以任何方式限制本公开的范围。

[0044] 在此使用的术语"包括"、"包含"及类似术语应该被理解为是开放性的术语,即"包括/包含但不限于"。术语"基于"是"至少部分地基于"。术语"一个实施例"表示"至少一个实施例";术语"另一实施例"表示"至少一个另外的实施例"。其他术语的相关定义将在下文描述中给出。

[0045] 在下文中,将参考附图来详细描述根据本公开的实施例的用于向处理器供电的技术方案。

[0046] 图1图示了现有主板系统架构100的示例性框图。该系统架构100例如包括PSU 101、母板电压调节器 (MBVR) 102、总线上电池 (BoB,以下也称为电池模块) 103和CPU 104, MBVR 102可以用于驱动CPU 104。应当理解,图1所示出的系统架构仅为示例性的,其中仅示出了现有系统架构中与本公开的实施例有关的部件,而非现有系统架构中的全部部件。CPU 104可以是具有单个核的处理器或者可以是如图1所示的具有多个核的处理器,其中具有功率控制单元 (PCU)。当PSU 101上电时,BoB 103处于充电状态,MBVR 102可以由PSU 101供电。在加速模式期间,当CPU 104获取的功率超过PSU 101的峰值功率时,PSU 101可以向CPU 104发送PROCHOT#信号以迫使CPU 104降低其时钟频率。仅当PSU 101掉电时,BoB 103可以通过MBVR102向CPU 104提供功率,因此,在如图1所示的现有系统架构中,BoB 103的能量不

能够被用于在加速模式期间向CPU 104提供额外的功率。

[0047] 以下将结合图2进一步详细描述系统架构100中的BoB 103的结构。

[0048] 图2示例性图示了现有处理器系统架构100中的电池模块的结构框图。在一个示例中,图2中所示的电池模块可以是图1中的BoB 103。如图2所示,在BoB 103的一个示例性结构中,核心部件为微处理器1031,其可以操作用于进行电池管理系统(BMS)和通信及降压控制。如图2所示,在与微处理器1031相连的输入输出接口中,包括两个保留的引脚:Reserved#1和Reserved#2。BoB 103中的微处理器1031中还包含有固件,当固件由微处理器1031执行时,例如,可以使得BoB 103执行如下操作:当如图1中所示的PSU 101上电时,BoB 103处于充电状态,其不能够向CPU 104提供功率;而当PSU 101掉电时,该BoB 103进入放电状态,从而向CPU 104提供功率。因此,如图2所示的现有处理器系统架构中的电池模块不能够被用于在加速模式期间向CPU 104提供额外的功率。

[0049] 为了解决上述问题,本公开的实施例可以提供一种用于向处理器供电的方案。例如,图3图示了根据本公开的实施例的主板系统架构300的示例性框图,以下将对比图1来详细描述根据本公开的实施例的主板系统架构与现有主板系统架构之间的不同。与图1中相同的是,图3中图示的根据本公开的实施例的系统架构300也包括PSU 301、MBVR 302、BoB 303和CPU 304,MBVR 302可以用于驱动CPU 304。CPU 304可以是具有单个核的处理器或者可以是如图3所示的具有多个核的处理器,其中具有PCU。当PSU上电时,BoB 303可以处于充电状态,MBVR 302可以由PSU 301供电。然而,与图1中不同的是,在加速模式期间,当CPU 304要求的功率超过PSU 301的峰值功率时,PSU 301可以首先向BoB 303而非CPU 304发送PROCHOT#\_IN信号。当BoB 303能够提供所要求的额外功率时,其可以进入放电状态以向CPU 304供电,使得CPU 304能够保持运行在加速模式下。当BoB 303要使用的功率超过其能够提供的额外功率时,BoB 303可以向CPU 304发送PROCHOT#\_OUT信号,从而防止系统意外关闭。PROCHOT# OUT信号可以迫使CPU 304降低其时钟频率,以降低所需要的功率。

为了实现图3中图示的系统架构300,本公开的实施例可以提供一种新的电池模 [0050] 块。例如,图4示例性图示了根据本公开的实施例的主板系统架构300中的电池模块的结构 框图。例如,图4中所示的电池模块可以是图3中的BoB 303。如图4所示,在BoB 303的一个示 例性结构中,微处理器3031可以操作用于进行电池管理和通信及降压控制。与图2所示的现 有的电池模块不同的是,在与微处理器3031相连的输入输出接口中,保留引脚Reserved#1 (例如,图2中所示的保留引脚Reserved#1)可以被连接至如图3所示的PSU 301,以便于从 PSU 301接收PROCHOT#\_IN信号;而保留引脚Reserved#2(例如,图2中所示的保留引脚 Reserved#2)可以被连接至如图3所示的CPU 304中的PCU,以便于向PCU输出PROCHOT# OUT 信号。此外,如以下将进一步详细描述的,微处理器3031中的固件当由微处理器3031执行 时,可以使得BoB 303执行如下操作:当处于加速模式的如图3所示的CPU 304要求的功率超 过PSU 301的峰值功率时,BoB 303可以接收来自PSU 301的PROCHOT# IN信号;响应于接收 到的PROCHOT# IN信号, 当BoB 303能够提供所要求的额外功率时, 其可以进入放电状态以 向CPU 304供电,使得CPU 304能够保持运行在加速模式下;当BoB 303使用的能量超过其能 够提供的额外功率时,BoB 303可以向CPU 304发送PROCHOT# OUT信号,从而防止系统意外 关闭,其中PROCHOT# OUT信号可以迫使CPU 304降低其时钟频率,以降低所需要的功率。

[0051] 图5图示了根据本公开的实施例的主板系统架构300中各部件状态和各信号的时

序关系图。在图5中,横坐标轴代表时间,其中T0至T6分别代表7个不同时刻;图中的五条折线从上到下依次表示CPU状态、PSU状态、PROCHOT#\_IN信号、BoB状态和PROCHOT#\_OUT信号随时间的变化。

如图5所示,在T0至T1期间,CPU处于正常工作模式,其要求的功率小于1倍的热设 [0052] 计功率(TDP),因此仅由PSU供电;在T1处,CPU进入加速模式;在T1至T2期间,处于加速模式 的CPU要求1.2倍的TDP,由于未超过PSU的峰值功率,其仍然仅由PSU供电;在T2处,CPU要求2 倍的TDP,超过了PSU的峰值功率,因此PSU向BoB发送PROCHOT# IN信号;在T2至T3期间,BoB 处于放电状态,以向CPU提供其所要求的超过PSU峰值功率的额外功率;在T3处,CPU要求1.2 倍的TDP,由于未超过PSU的峰值功率,因此PSU不向BoB发送PROCHOT# IN信号,使得BoB退出 放电状态不再向CPU供电;在T3至T4期间,CPU要求1.2倍的TDP,因此CPU仅由PSU供电,该时 间段可以被称为保持时间(Thold);在T4处,CPU要求2倍的TDP,超过了PSU的峰值功率,因此 PSU向BoB发送PROCHOT# IN信号;在T4至T5期间,BoB处于放电状态,以向CPU提供其所要求 的超过PSU峰值功率的额外功率;在T5处,CPU要求1.2倍的TDP,由于未超过PSU的峰值功率, 因此PSU不向BoB发送PROCHOT#\_IN信号,使得BoB退出放电状态不再向CPU供电;在T5至T6期 间,CPU要求1.2倍的TDP,因此CPU仅由PSU供电;在T6处,CPU回到正常工作模式并且仅由PSU 供电。从图6中可以看出,根据本公开的实施例,在CPU要求的功率超过PSU的峰值功率时, PSU可以向BoB发送PROCHOT# IN信号,使得BoB开始放电以向CPU提供额外的功率。此时,BoB 和PSU可以以并行的模式来工作,其中仍然主要由PSU向CPU提供功率,而由BoB向CPU提供额 外的功率。当CPU要求的功率降低至PSU的峰值功率以下时,BoB可以退出放电状态,并且如 通常情况那样,CPU要求的所有功率可以仅由PSU提供。

[0053] 由此可见,根据本公开的实施例,在CPU处于加速模式期间,当CPU要求的功率超过PSU能够提供的上限时,CPU能够不被迫使通过降低其时钟频率来保证系统正常运行,而是能够由BoB来提供其所要求的超过PSU峰值功率的额外功率,从而使得CPU能够获得尽可能高的性能。

[0054] 图6图示了根据本公开的实施例的用于向处理器供电的方法600的流程图。以下将结合图3来详细描述方法600。例如,方法600可以被实施在图3(和图4)中所示的BoB 303上(诸如,可以以固件的方式被实施在BoB 303内的微处理器3031中)或者也可以被实施在其他单独的设备上。方法600可以包括步骤S601至S602。

[0055] 在步骤S601,响应于接收到来自为处理器供电的供电单元的第一信号,确定附加电源是否能够提供所要求的额外功率,其中第一信号指示该处理器要求的功率超过供电单元能够提供的最大功率。例如,在此所述的附加电源可以是如图3所示的BoB 303。如图3所示,当处于加速模式的CPU 304要求的功率超过PSU的峰值功率时,PSU 301可以向BoB 303发送PROCHOT#\_IN信号。响应于接收到来自PSU 301的PROCHOT#\_IN信号,BoB 303可以确定自身是否能够提供所要求的额外功率。

[0056] 返回图6,方法600进行至步骤S602。在步骤S602,响应于确定附加电源能够提供额外功率,至少利用附加电源向该处理器供电。例如,如图3所示,当BoB 303确定其自身能够提供所要求的额外功率是,BoB303可以进入放电模式以与PSU 301一同向CPU 304供电。因此,在CPU 304处于加速模式期间,当CPU 304要求的功率超过PSU能够提供的上限时,CPU 304能够不被迫使通过降低其时钟频率来保证系统正常运行,而是能够由BoB 303来提供其

所要求的超过PSU 301峰值功率的额外功率,从而使得CPU 304能够获得尽可能高的性能。 [0057] 根据本公开的实施例,方法600可以包括如下的可选步骤:响应于确定附加电源不能够提供额外功率,向该处理器发送第二信号,以降低该处理器的时钟频率。例如,如图3所示,当BoB 303确定其自身不能够提供所要求的额外功率时,BoB 303可以向CPU 304发送PROCHOT#\_OUT信号,从而防止系统意外关闭,其中PROCHOT#\_OUT信号可以迫使CPU 304降低

[0058] 根据本公开的实施例,方法600还可以包括如下的可选步骤:响应于未接收到来自供电单元的第一信号,停止利用附加电源向该处理器供电。例如,如图3所示,当CPU 304要求的功率不超过PSU 301的峰值功率时,PSU 301可以不向BoB 303发送PROCHOT#\_IN信号,使得BoB 303退出放电模式,从而不向CPU 304供电。

[0059] 根据本公开的实施例,方法600还可以包括如下的可选步骤:响应于供电单元掉电,利用附加电源向该处理器供电。例如,如图3所示,当PSU 301掉电时,BoB 303可以进入放电模块,以单独地向CPU 304供电。

[0060] 至此,方法600结束。

其时钟频率,以降低所需要的功率。

[0061] 出于清楚的目的,在图6没有示出方法600的某些可选步骤。然而,应当理解,上文参考图3-5所描述的各个特征同样适用于方法600。特别地,根据本公开的实施例,参考图6描述的方法600可以被实现为计算机软件程序。例如,本公开的实施例包括一种计算机程序产品,所述计算机程序产品被有形地存储在非瞬态计算机可读介质上并且包括计算机可执行指令,所述计算机可执行指令在被执行时使得计算机执行方法600的任意步骤。

[0062] 图7图示了根据本公开的实施例的用于控制向处理器供电的装置700的框图。例如,装置700可以被实施在图4中所示的BoB 303上的微处理器3031中或者也可以被实施在其他单独的控制装置上。装置700可以包括功率确定模块701,被配置为响应于接收到来自为处理器供电的供电单元的第一信号,确定附加电源是否能够提供所要求的额外功率,其中第一信号指示该处理器要求的功率超过供电单元能够提供的最大功率。装置700还可以包括第一控制模块702,被配置为响应于确定附加电源能够提供额外功率,使得至少利用附加电源向该处理器供电。

[0063] 根据本公开的实施例,第一信号可以经由装置700的第一保留引脚被接收。例如,第一信号可以经由图4中所示的BoB 303中的微处理器3031的第一保留引脚(即Reserved#1)被接收。

[0064] 根据本公开的实施例,装置700还可以包括第二信号发送模块,被配置为响应于确定附加电源不能够提供额外功率,向该处理器发送第二信号,以降低该处理器的时钟频率。

[0065] 根据本公开的实施例,第二信号可以经由装置700的第二保留引脚被发送。例如,第二信号可以经由图4中所示的BoB 303中的微处理器3031的第二保留引脚(即Reserved#2)被发送。

[0066] 根据本公开的实施例,装置700还可以包括第二控制模块,被配置为响应于未接收到来自供电单元的第一信号,使得停止利用附加电源向该处理器供电。

[0067] 根据本公开的实施例,装置700还可以包括第三控制模块,被配置为响应于供电单元掉电,使得利用附加电源向该处理器供电。

[0068] 出于清楚的目的,在图7中没有示出装置700的某些可选模块。然而,应当理解,上

文参考本公开的方法所描述的各个特征同样适用于装置700。而且,装置700中的各个模块可以是硬件模块,也可以是软件模块。例如,在某些实施例中,装置700可以部分或者全部利用软件和/或固件来实现,例如被实现为包含在计算机可读介质上的计算机程序产品。备选地或附加地,装置700可以部分或者全部基于硬件来实现,例如被实现为集成电路(IC)、专用集成电路(ASIC)、片上系统(SOC)、现场可编程门阵列(FPGA)等。本公开的范围在此方面不受限制。

[0069] 图8图示了根据本公开的实施例的用于向处理器供电的附加电源800的框图。例如,附加电源800可以被实施在图3和图4中所示的BoB 303中。根据本公开的实施例,附加电源800可以包括用于控制向所述处理器供电的装置801。例如,装置801可以被实施为图4中所示的BoB 303上的微处理器3031。

[0070] 根据本公开的实施例,装置801被配置为响应于接收到来自为处理器供电的供电单元的第一信号,确定附加电源800是否能够提供所要求的额外功率,其中第一信号指示该处理器要求的功率超过供电单元能够提供的最大功率。例如,第一信号可以经由装置801的第一保留引脚被接收(诸如,第一信号可以经由图4中所示的BoB 303上的微处理器3031的引脚Reserved#1被接收)。装置801还可以被配置为响应于确定附加电源800能够提供额外功率,使得至少利用附加电源800向该处理器供电。

[0071] 根据本公开的实施例,装置801还可以被配置为响应于确定附加电源800不能够提供额外功率,由附加电源800向该处理器发送第二信号,以降低该处理器的时钟频率。例如,第二信号可以经由装置801的第二保留引脚被发送(诸如,第二信号可以经由图4中所示的BoB303上的微处理器3031的引脚Reserved#2被发送)。

[0072] 根据本公开的实施例,装置801还可以被配置为响应于未接收到来自供电单元的第一信号,使得停止利用附加电源800向该处理器供电。

[0073] 根据本公开的实施例,装置801还可以被配置为响应于供电单元掉电,使得利用附加电源800向该处理器供电。

[0074] 图9图示了根据本公开的实施例的主板系统900的框图。例如,主板系统900可以被实施为如图3所示的主板系统架构300。主板系统900包括处理器901、用于向所述处理器供电的供电单元902、附加电源903以及控制装置904。根据本公开的实施例,控制装置904可以位于附加电源903中。例如,主板系统900中的处理器901可以被实施为如图3所示的CPU 304,供电单元902可以被实施为如图3所示的PSU 301,附加电源903可以被实施为如图3所示的BoB 303,控制装置可以被实施为BoB 303中的微处理器(例如,如图4所示的微处理器 3031)或者也可以被实施为其他单独的设备。

[0075] 根据本公开的实施例,在主板系统900中,控制装置904被配置为响应于接收到来自供电单元902的第一信号,确定附加电源903是否能够提供所要求的额外功率,其中第一信号指示处理器901要求的功率超过供电单元902能够提供的最大功率。控制装置904还被配置为响应于确定附加电源903能够提供额外功率,使得至少利用附加电源903向处理器901供电。例如,控制装置904可以经由第一保留引脚从供电单元902接收第一信号。

[0076] 根据本公开的实施例,控制装置904还可以被配置为响应于确定附加电源903不能够提供额外功率,向处理器901发送第二信号,以降低处理器901的时钟频率。例如,控制装置904可以经由第二保留引脚向处理器901发送第二信号。

[0077] 根据本公开的实施例,控制装置904还可以被配置为响应于未接收到来自供电单元902的第一信号,使得停止利用附加电源903向处理器901供电。

[0078] 根据本公开的实施例,控制装置904还可以被配置为响应于供电单元902掉电,使得利用附加电源903向处理器901供电。

[0079] 综上所述,根据本公开的实施例,提供了一种用于向处理器供电的方法、装置、附加电源和主板系统。与现有技术相比,本公开的实施例能够通过从附加电源向处理器提供所需要的额外功率,优化处于加速模式中的处理器的性能。

[0080] 一般而言,本发明的各种示例实施例可以在硬件或专用电路、软件、逻辑,或其任何组合中实施。某些方面可以在硬件中实施,而其他方面可以在可以由控制器、微处理器或其他计算设备执行的固件或软件中实施。当本发明的实施例的各方面被图示或描述为框图、流程图或使用某些其他图形表示时,将理解此处描述的方框、装置、系统、技术或方法可以作为非限制性的示例在硬件、软件、固件、专用电路或逻辑、通用硬件或控制器或其他计算设备,或其某些组合中实施。

[0081] 而且,流程图中的各框可以被看作是方法步骤,和/或计算机程序代码的操作生成的操作,和/或理解为执行相关功能的多个耦合的逻辑电路元件。例如,本发明的实施例包括计算机程序产品,该计算机程序产品包括有形地实现在机器可读介质上的计算机程序,该计算机程序包含被配置为实现上文描述方法的程序代码。

[0082] 在公开的上下文内,机器可读介质可以是包含或存储用于或有关于指令执行系统、装置或设备的程序的任何有形介质。机器可读介质可以是机器可读信号介质或机器可读存储介质。机器可读介质可以包括但不限于电子的、磁的、光学的、电磁的、红外的或半导体系统、装置或设备,或其任意合适的组合。机器可读存储介质的更详细示例包括带有一根或多根导线的电气连接、便携式计算机磁盘、硬盘、随机存储存取器(RAM)、只读存储器(ROM)、可擦除可编程只读存储器(EPROM或闪存)、光存储设备、磁存储设备,或其任意合适的组合。

[0083] 用于实现本发明的方法的计算机程序代码可以用一种或多种编程语言编写。这些计算机程序代码可以提供给通用计算机、专用计算机或其他可编程的数据处理装置的处理器,使得程序代码在被计算机或其他可编程的数据处理装置执行的时候,引起在流程图和/或框图中规定的功能/操作被实施。程序代码可以完全在计算机上、部分在计算机上、作为独立的软件包、部分在计算机上且部分在远程计算机上或完全在远程计算机或服务器上执行。

[0084] 另外,尽管操作以特定顺序被描绘,但这并不应该理解为要求此类操作以示出的特定顺序或以相继顺序完成,或者执行所有图示的操作以获取期望结果。在某些情况下,多任务或并行处理会是有益的。同样地,尽管上述讨论包含了某些特定的实施细节,但这并不应解释为限制任何发明或权利要求的范围,而应解释为对可以针对特定发明的特定实施例的描述。本说明书中在分开的实施例的上下文中描述的某些特征也可以整合实施在单个实施例中。相反地,在单个实施例的上下文中描述的各种特征也可以分离地在多个实施例或在任意合适的子组合中实施。

[0085] 针对前述本发明的示例实施例的各种修改、改变将在连同附图查看前述描述时对相关技术领域的技术人员变得明显。任何及所有修改将仍落入非限制的和本发明的示例实

施例范围。此外,前述说明书和附图存在启发的益处,涉及本发明的这些实施例的技术领域的技术人员将会想到此处阐明的本发明的其他实施例。

[0086] 将会理解,本法明的实施例不限于公开的特定实施例,并且修改和其他实施例都应包含于所附的权利要求范围内。尽管此处使用了特定的术语,但是它们仅在通用和描述的意义上使用,而并不用于限制目的。

图1

图2

图3

图4

图5

600

图6

# 700

图7

# 附加电源800~

图8

# 902 供电单元 附加电源 空03 控制装置 904

图9