(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4833652号 (P4833652)

(45) 発行日 平成23年12月7日(2011, 12.7)

(24) 登録日 平成23年9月30日(2011.9.30)

(51) Int.Cl. F 1

**GO5F** 1/56 (2006.01) GO5F 1/56 **B6OR** 16/03 (2006.01) B6OR 16/02

請求項の数 13 (全 20 頁)

(21) 出願番号 特願2005-355150 (P2005-355150) (22) 出願日 平成17年12月8日 (2005.12.8)

(65) 公開番号 特開2007-157071 (P2007-157071A) (43) 公開日 平成19年6月21日 (2007. 6. 21)

審査請求日 平成20年11月17日 (2008.11.17)

(73) 特許権者 000116024

310C

670T

ローム株式会社

京都府京都市右京区西院溝崎町21番地

|(74)代理人 100105924

弁理士 森下 賢樹

|(72)発明者 猪上 浩樹

京都府京都市右京区西院溝崎町21番地

ローム株式会社内

審査官 櫻田 正紀

最終頁に続く

## (54) 【発明の名称】 レギュレータ回路およびそれを搭載した自動車

#### (57)【特許請求の範囲】

### 【請求項1】

<u>入力端子に印加された入力電圧を安定化し、出力端子から出力電圧を出力するレギュレ</u>ータ回路であって、

前記入力端子と前記出力端子の間に設けられた出力トランジスタと、

<u>前記出力電圧に応じた電圧が所定の基準電圧に近づくように、前記出力トランジスタの</u>制御端子の電圧を調節する誤差増幅器と、

<u>前記入力端子から接地端子に至る経路上に設けられ、一端の電位が固定された変動検出</u> キャパシタと、

前記変動検出キャパシタに流れる電流に応じた電流を、前記出力トランジスタの制御端子に供給する電流帰還回路と、

前記出力トランジスタの制御端子の電圧を、前記出力電圧より差分電圧だけ低いクランプ電圧以上となるようにクランプするとともに、前記差分電圧を、前記出力トランジスタに流れる出力電流に応じて大きくするクランプ回路と、

を備えることを特徴とするレギュレータ回路。

#### 【請求項2】

前記クランプ回路は、

前記出力トランジスタに流れる出力電流に応じた検出電流を生成する電流検出回路と、 前記出力電圧より前記検出電流に比例した電圧だけ低いクランプ基準電圧を生成するク ランプ基準電圧生成回路と、

前記クランプ基準電圧生成回路により生成されるクランプ基準電圧よりも、さらに所定の電圧だけ低い電圧を、前記クランプ電圧に設定し、前記出力トランジスタの制御端子の電圧をクランプするクランプ実行回路と、

を含むことを特徴とする請求項1に記載のレギュレータ回路。

#### 【請求項3】

前記クランプ基準電圧生成回路は、

一端が前記出力端子に接続され、前記電流検出回路により生成される検出電流の経路上に設けられた抵抗を含み、当該抵抗の他端に現れる電圧を、前記クランプ基準電圧として出力することを特徴とする請求項2に記載のレギュレータ回路。

#### 【請求項4】

前記クランプ実行回路は、

前記クランプ基準電圧生成回路の出力端子から、前記出力トランジスタの制御端子に至る経路上に、カソード端子が前記出力トランジスタの制御端子側となるように設けられたダイオードを含むことを特徴とする請求項 2 に記載のレギュレータ回路。

### 【請求項5】

前記クランプ実行回路は、

ゲートに前記クランプ基準電圧が印加されたNチャンネル電界効果トランジスタと、 アノードが、前記Nチャンネル電界効果トランジスタのソースに接続され、カソードが 前記出力トランジスタの制御端子に接続されたダイオードと、

を含むことを特徴とする請求項2に記載のレギュレータ回路。

#### 【請求項6】

<u>前</u>記出力トランジスタの制御端子と前記入力端子の電圧差が、所定のクランプ電圧以上となるように、前記出力トランジスタの制御端子の電圧をクランプする<u>第2クランプ回路</u>をさらに備えることを特徴とする請求項1から5のいずれかに記載のレギュレータ回路。

#### 【請求項7】

前記<u>第2</u>クランプ回路は、前記変動検出キャパシタに電流が流れる期間、動作することを特徴とする請求項6に記載のレギュレータ回路。

#### 【請求項8】

前記出力トランジスタは、Pチャンネル電界効果トランジスタであって、前記クランプ電圧は、前記出力トランジスタのしきい値電圧より小さく設定されることを特徴とする請求項<u>6または7</u>に記載のレギュレータ回路。

## 【請求項9】

前記<u>第2</u>クランプ回路は、前記電流帰還回路から前記出力トランジスタの制御端子への電流供給経路上に、カソードが前記出力トランジスタの制御端子側に、アノードが前記電流帰還回路側となるように配置されたダイオードを含むことを特徴とする請求項<u>6 から 8</u>のいずれかに記載のレギュレータ回路。

### 【請求項10】

前記<u>第2</u>クランプ回路は、前記電流帰還回路から前記出力トランジスタの制御端子への電流供給経路上に設けられた抵抗を含むことを特徴とする請求項<u>6 から 8</u> のいずれかに記載のレギュレータ回路。

## 【請求項11】

前記電流帰還回路は、前記入力端子から前記変動検出キャパシタの他端に至る経路上に 設けられた第1トランジスタと、

前記第1トランジスタとカレントミラー回路を構成する第2トランジスタと、

を含み、前記第2トランジスタに流れる電流を、前記クランプ回路を介して前記出力トランジスタの制御端子に供給することを特徴とする請求項<u>9または10</u>に記載のレギュレータ回路。

## 【請求項12】

ひとつの半導体基板上に一体集積化されたことを特徴とする請求項1から<u>11</u>のいずれかに記載のレギュレータ回路。

10

20

30

40

#### 【請求項13】

バッテリと、

前記バッテリの電圧を安定化して負荷に供給する請求項1から<u>12</u>のいずれかに記載の レギュレータ回路と、

を備えることを特徴とする自動車。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、出力電圧を安定化するレギュレータ回路に関する。

【背景技術】

[00002]

電子回路を安定に動作させるために、その電源電圧を一定の値に安定化させたい場合がある。また、各電子回路が必要とする電源電圧は、必ずしも電子回路が搭載される機器に用意されているとは限らない。例えば、車載機器の5Vマイコンなどは、電源電圧として5Vを必要とするが、自動車のバッテリから供給される電圧は12Vであり、なおかつ不安定である。このような場合に、電子回路が必要とする電源電圧を簡易かつ安定に生成するために、レギュレータ回路が広く用いられている。

#### [0003]

このレギュレータ回路は一般的に、誤差増幅器と出力トランジスタとフィードバック抵抗を備えている。誤差増幅器は、フィードバック抵抗により帰還した出力電圧と所望の基準電圧値とを比較し、2つの電圧が近づくように出力トランジスタの制御端子の電圧や負荷が変動した場合には、その変動に応じて出力トランジスタの制御端子の電圧を変化させなければならない。

### [0004]

ここで、出力トランジスタとして低消費電流化のために、MOSFET(Metal Oxide Semiconductor Field Effect Transis tor)を使用する場合がある。MOSFETを使用した場合、電流許容量を大きくとるためにトランジスタサイズを大きくすると、それに伴ってゲート容量が大きくなり、誤差増幅器によって制御されるゲート電圧の応答が、入力電圧あるいは負荷の変動に対して遅れることになる。この遅れは、出力電圧のオーバーシュートやアンダーシュートを引き起こす。また、負荷変動すなわち出力電流が変動する際にも、オーバーシュートやアンダーシュートが発生する。

## [0005]

このような問題を解決するために、出力トランジスタから負荷に流れる電流をモニタし、その電流に応じて誤差増幅器のバイアス電流を増やすことによりレギュレータの応答速度を速める手法が提案されている。

[0006]

【特許文献1】特開2001-34351号公報

【発明の開示】

【発明が解決しようとする課題】

[0007]

上記文献に記載の技術を用いた場合には、負荷に多くの電流が流れる場合には、誤差増幅器にも大きなバイアス電流が流れ応答速度が高速化される。しかしながら、負荷に流れる電流が急激に減少した時には、それに伴い応答速度が遅くなってしまうため、出力電圧が変動するおそれがある。また、入力電圧の変動に起因する出力電圧の変動を抑制することが困難である。

## [0008]

本発明はこうした課題に鑑みてなされたものであり、その目的は、安定状態における消費電力を増加を抑えつつ、入力電圧や出力電流が変動した時の出力電圧の変動を抑制することができるレギュレータ回路の提供にある。

10

20

30

40

### 【課題を解決するための手段】

### [0009]

本発明のある態様は、入力端子に印加された入力電圧を安定化し、出力端子から出力電圧を出力するレギュレータ回路に関する。このレギュレータ回路は、入力端子と出力端子の間に設けられた出力トランジスタと、出力電圧に応じた電圧が所定の基準電圧に近づくように、出力トランジスタの制御端子の電圧を調節する誤差増幅器と、入力端子から接地端子に至る経路上に設けられ、一端の電位が固定された変動検出キャパシタと、変動検出キャパシタに流れる電流に応じた電流を、出力トランジスタの制御端子に供給する電流帰還回路と、出力トランジスタの制御端子の電圧をクランプするクランプ回路と、を備える

10

## [0010]

入力電圧が上昇すると、電圧変動量の時間微分に比例した電流が変動検出キャパシタに流れる。変動検出キャパシタに流れる電流に応じた電流を、出力トランジスタの制御端子に供給することにより、出力トランジスタの制御端子の電圧を強制的に上昇させることができ、オーバーシュートが抑制される。この態様においては、クランプ回路を設けて、出力トランジスタの制御端子をクランプし、出力トランジスタのゲートソース、あるいはベースエミッタ間電圧(以下、ゲートソース間電圧およびベースエミッタ間電圧を、ゲートソース間電圧と総称する)の上限値、あるいは下限値、もしくはその両方を設定することにより、必要以上に、出力トランジスタの制御端子の電圧が変化するのを抑制し、オーバーシュートやアンダーシュートをさらに抑制することができる。

20

#### [0011]

クランプ回路は、出力トランジスタの制御端子と入力端子の電圧差が、所定のクランプ 電圧以上となるように、出力トランジスタの制御端子の電圧をクランプしてもよい。

出力トランジスタの制御端子と入力端子の間の電圧差、すなわち、ゲートソース間電圧に下限値を設定することにより、出力トランジスタが完全にオフするのを防止することができる。この態様によれば、入力電圧が非常に速い速度で変化しても、アンダーシュートを抑制することができる。

[0012]

クランプ回路は、変動検出キャパシタに電流が流れる期間、動作してもよい。この場合、変動検出キャパシタに電流が流れない期間、すなわち、回路が定常状態にある期間は、クランプ回路が動作しないため、ゲートソース間電圧がクランプされず、出力電圧を基準電圧に一致するように安定化することができる。

30

## [0013]

出力トランジスタは、Pチャンネル電界効果トランジスタであって、クランプ電圧は、 出力トランジスタのしきい値電圧より小さく設定されてもよい。

[0014]

クランプ回路は、電流帰還回路から出力トランジスタの制御端子への電流供給経路上に、カソードが出力トランジスタの制御端子側に、アノードが電流帰還回路側となるように配置されたダイオードを含んでもよい。この場合、クランプ回路を、ダイオードに電流が流れる期間、すなわち、変動検出キャパシタに電流が流れる期間、アクティブとすることができ、さらに、出力トランジスタのゲートソース間電圧を、少なくとも、ダイオードの順方向電圧以上にクランプすることができる。

40

### [0015]

クランプ回路は、電流帰還回路から出力トランジスタの制御端子への電流供給経路上に設けられた抵抗を含んでもよい。この場合、クランプ回路を、抵抗に電流が流れる期間、すなわち、変動検出キャパシタに電流が流れる期間、アクティブとすることができ、さらに、出力トランジスタのゲートソース間電圧を、少なくとも、抵抗に発生する電圧降下以上にクランプすることができる。

#### [0016]

電流帰還回路は、入力端子から変動検出キャパシタの他端に至る経路上に設けられた第

20

30

40

50

1トランジスタと、第1トランジスタとカレントミラー回路を構成する第2トランジスタと、を含み、第2トランジスタに流れる電流を、クランプ回路を介して出力トランジスタの制御端子に供給してもよい。

#### [0017]

クランプ回路は、出力電圧より差分電圧だけ低い電圧を、クランプ電圧に設定し、出力 トランジスタの制御端子の電圧を、クランプ電圧以上となるようにクランプしてもよい。

入力電圧が変動し、出力電圧の目標値である基準電圧に近接し、あるいはそれより低くなると(以下、本明細書において、入力電圧低下状態という)、誤差増幅器は、出力トランジスタがフルオンするように、出力トランジスタの制御端子の電圧を低下させて、ゲートソース間電圧を増大させる。この態様では、出力トランジスタの制御端子の電圧に、下限値を設定することにより、出力トランジスタのゲートソース間電圧がある電圧でクランプされるため、入力電圧低下状態から、入力電圧が急激に上昇した場合において、出力電圧がオーバーシュートするのを抑制することができる。

## [0018]

クランプ回路は、出力トランジスタに流れる出力電流に応じて大きくなる電圧を差分電 圧として、クランプ電圧を設定してもよい。

差分電圧を、出力電流に応じて増大させることにより、重負荷となるに従って、出力トランジスタの制御端子の下限値は低くなる。その結果、負荷電流に応じて、出力トランジスタのオンの程度の上限を設定することができ、より好適に出力電圧のオーバーシュートを抑制することができる。

#### [0019]

クランプ回路は、出力トランジスタに流れる出力電流に応じた検出電流を生成する電流 検出回路と、出力電圧より検出電流に比例した電圧だけ低いクランプ基準電圧を生成する クランプ基準電圧生成回路と、クランプ基準電圧生成回路により生成されるクランプ基準 電圧よりも、さらに所定の電圧だけ低い電圧を、クランプ電圧に設定し、出力トランジス タの制御端子の電圧をクランプするクランプ実行回路と、を含んでもよい。

この場合、出力トランジスタに流れる出力電流に比例した電圧と、所定の電圧の和を、 差分電圧として設定することができる。

### [0020]

クランプ基準電圧生成回路は、一端が出力端子に接続され、電流検出回路により生成される検出電流の経路上に設けられた抵抗を含み、当該抵抗の他端に現れる電圧を、クランプ基準電圧として出力してもよい。

#### [0021]

クランプ実行回路は、クランプ基準電圧生成回路の出力端子から、出力トランジスタの 制御端子に至る経路上に、カソード端子が出力トランジスタの制御端子側となるように設 けられたダイオードを含んでもよい。

## [0022]

クランプ実行回路は、ゲートにクランプ基準電圧が印加されたNチャンネル電界効果トランジスタと、アノードが、Nチャンネル電界効果トランジスタのソースに接続され、カソードが出力トランジスタの制御端子に接続されたダイオードと、を含んでもよい。

## [0023]

レギュレータ回路は、ひとつの半導体基板上に一体集積化されてもよい。「一体集積化」とは、回路の構成要素のすべてが半導体基板上に形成される場合や、回路の主要構成要素が一体集積化される場合が含まれ、回路定数の調節用に一部の抵抗やキャパシタなどが 半導体基板の外部に設けられていてもよい。

## [0024]

本発明の別の態様は、自動車である。この自動車は、バッテリと、バッテリの電圧を安定化して負荷に供給する上述のレギュレータ回路と、を備える。

#### [0025]

この態様によると、バッテリの電圧が変動しても、負荷に供給される電圧のオーバーシ

ュートやアンダーシュートを抑制することができ、負荷を安定に駆動することができる。

### [0026]

なお、以上の構成要素の任意の組合せや、本発明の構成要素や表現を、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

## 【発明の効果】

## [0027]

本発明に係るレギュレータ回路によれば、安定状態における消費電力の増加を抑えつつ 、入力電圧の変動にともなうアンダーシュートを抑制することができる。

### 【発明を実施するための最良の形態】

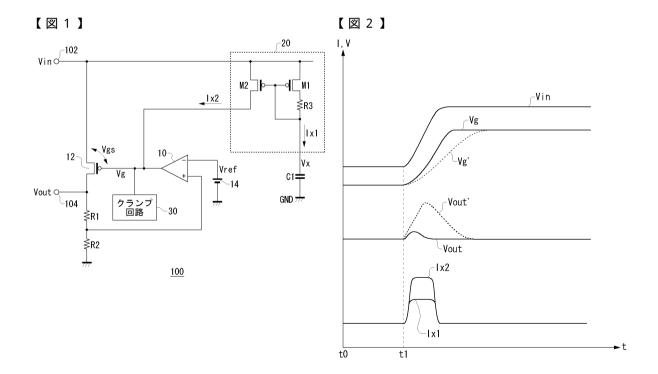

#### [0028]

(本発明の実施の形態の概要)

はじめに、本発明の実施の形態に係るレギュレータ回路100の構成および動作の概略を、図1の回路図をもとに説明する。図1は、本実施の形態に係るレギュレータ回路100の構成を示すブロック図である。以降の図において、同一の構成要素には同一の符号を付し、適宜説明を省略する。以下の説明において、電圧信号、電流信号あるいは抵抗、容量などに付された符号は、必要に応じてそれぞれの電圧値、電流値あるいは抵抗値、容量値を表すものとして用いることとする。

#### [0029]

本実施の形態にかかるレギュレータ回路100は、入力端子102に印加された入力電圧Vinを安定化し、出力端子104から出力電圧Voutを出力する。このレギュレータ回路100は、誤差増幅器10、出力トランジスタ12、第1抵抗R1、第2抵抗R2、基準電圧源14に加えて、変動検出キャパシタC1、電流帰還回路20、クランプ回路30を備える。

#### [0030]

誤差増幅器10、出力トランジスタ12、第1抵抗R1、第2抵抗R2は一般的なリニアレギュレータを構成する。出力トランジスタ12は、入力端子102と出力端子104間に設けられており、出力電圧Voutが所望の電圧となるように入力電圧Vinを電圧降下させる。本実施の形態において出力トランジスタ12はPチャンネルMOSFETであって、そのソースがレギュレータ回路100の入力端子102に接続され、ドレインがレギュレータ回路100の出力端子104に接続される。また、制御端子であるゲートには、誤差増幅器10の出力が接続され、この誤差増幅器10によってゲート電圧Vgが制御される。

#### [0031]

誤差増幅器10は、反転入力端子・に基準電圧源14から出力される基準電圧Vrefが入力されている。誤差増幅器10の非反転入力端子+には、出力電圧Voutが第1抵抗R1、第2抵抗R2により抵抗分割され、R2/(R1+R2)倍して帰還入力される。誤差増幅器10は、反転、非反転入力端子の電圧が等しくなるように出力トランジスタ12のゲート電圧Vgを調節する。その結果、出力電圧Voutは、入力電圧Vinの値に関わらず、Vout=(R1+R2)/R2×Vrefが成り立つように安定化される

## [0032]

変動検出キャパシタ C 1 は、入力端子 1 0 2 から接地端子 G N D に至る経路上に設けられ、一端が接地されて電位が固定される。電流帰還回路 2 0 は、変動検出キャパシタ C 1 に流れる電流 I X 1 に応じた電流 I X 2 を、出力トランジスタ 1 2 のゲートに供給する。変動検出キャパシタ C 1 および電流帰還回路 C 0 は、入力端子 C 1 0 2 に印加される入力電圧 C 1 n が急激に変動した場合において、出力電圧 C 0 u t がオーバーシュートするのを抑制するものである。

## [0033]

電流帰還回路20は、入力端子102から変動検出キャパシタC1の他端に電流が流れ込むとき、出力トランジスタ12のゲート電圧Vgを強制的に上昇せしめる。電流帰還回

10

20

30

40

路20は、入力端子102から変動検出キャパシタC1の他端に流れ込む電流I×1に応じた電流I×2を、出力トランジスタ12のゲートに供給する。

#### [0034]

電流帰還回路20は、たとえばカレントミラー回路を用いて構成することができる。本実施の形態において、電流帰還回路20は、第1トランジスタM1、第2トランジスタM2、利得調整抵抗R3を含む。第1トランジスタM1および利得調整抵抗R3は、入力端子102から変動検出キャパシタC1の他端に至る経路上に直列に接続される。第1トランジスタM1は、PチャンネルMOSFETであって、ソースが入力端子102に接続され、ドレインが利得調整抵抗R3に接続される。第2トランジスタM2も、PチャンネルMOSFETであって、ソースが入力端子102に接続され、ゲートが第3トランジスタM3のゲートに接続される。第2トランジスタM2は、第1トランジスタM1とともにカレントミラー回路を構成する。第1トランジスタM1、第2トランジスタM2は、入力端子102から変動検出キャパシタC1に流れ込む電流I×1を定数倍した電流I×2を、出力トランジスタ12のゲートに供給し、ゲート電圧Vgを強制的に上昇せしめる。

#### [0035]

回路が安定状態にある場合には、第1トランジスタM1にはほとんど電流は流れず、そのドレインソース間の電位差はほぼ0Vとなり、さらに、利得調整抵抗R3での電圧降下もほぼ0Vとなる。したがって、変動検出キャパシタC1の一端には、入力電圧Vinがほぼそのまま入力され、Vx Vinが成り立っている。また、第1トランジスタM1のドレインソース間電圧および利得調整抵抗R3での電圧降下の和電圧は、第2トランジスタM2のゲートソース間電圧に相当するが、上述のようにいずれの電圧も非常に小さいため、第2トランジスタM2はオフ状態となる。

#### [0036]

入力端子102に印加されている入力電圧Vinが上昇すると、変動検出キャパシタC1の高電位側の電圧が入力電圧Vinに伴って上昇する。この結果、変動検出キャパシタC1を充電するために、第1トランジスタM1および利得調整抵抗R3を介して、過渡的に電流I×1が流れる。

#### [0037]

電流帰還回路20は、この電流I×1を増幅して電流I×2として出力トランジスタ12の制御端子であるゲートに帰還する。ここでの増幅には、利得が1より低い場合も含まれる。電流I×1と電流I×2の比は、第1トランジスタM1、第2トランジスタM2のサイズ比および利得調整抵抗R3によって調節することができる。すなわち電流利得を大きくするには、サイズ比を大きく、あるいは利得調整抵抗R3を大きく設定すればよい。

## [0038]

クランプ回路30は、出力トランジスタ12の制御端子の電圧、すなわちゲート電圧Vgをクランプする。クランプ回路30は、出力トランジスタ12のゲート電圧Vgをクランプすることにより、出力トランジスタ12のゲートソース間電圧Vgsの上限値、あるいは下限値、もしくはその両方を設定する。

### [0039]

次に、図1のレギュレータ回路100の動作のオーバーシュート抑制機能について図2をもとに説明する。図2は、入力電圧Vinが急激に上昇したときのレギュレータ回路100の動作波形図である。以降の図において、縦軸および横軸は、見やすさおよび理解の容易化のために、適宜拡大、縮小されており、実際のスケールとは異なって示されている

#### [0040]

本実施の形態にかかるレギュレータ回路100のオーバーシュートの抑制機能をより理解するため、はじめに、変動検出キャパシタC1および電流帰還回路20を使用しない場合の動作について説明する。図2に破線で示されるゲート電圧Vg′および出力電圧Vout′がこのときの電圧波形を示している。

## [0041]

50

10

20

30

#### [0042]

ゲート電圧 Vg 'は、ゲート容量によって形成される時定数回路によって応答が遅れ、 ソース電圧である入力電圧 Vinの急激な上昇に追従できない。したがって、出力トラン ジスタ12のゲートソース間電圧は一時的に大きくなる。その結果、ドレイン電圧である 出力電圧 Vout'は一時的に上昇し、オーバーシュートが発生してしまう。

#### [0043]

次に、本発明の実施形態にかかるレギュレータ回路100について、オーバーシュートを防止するために変動検出キャパシタC1、電流帰還回路20を動作させた場合の動作について図2に、実線で示される電圧波形Vg、Voutをもとに説明する。

#### [0044]

時刻 t 0 ~ t 1 において回路は安定状態にあり、時刻 t 1 に入力電圧 V i n が上昇する。入力電圧 V i n が上昇すると、入力端子 1 0 2 から変動検出キャパシタ C 1 に電流 I × 1 が流れることになる。電流 I × 1 は、変動検出キャパシタ C 1 の容量値を用いて、 I × 1 C 1 × d V i n / d t で与えられる。従って、図 2 において、電流 I × 1 は、入力電圧 V i n を時間微分した波形にほぼ比例し、入力電圧 V i n が変化したときに流れる。

#### [0045]

電流  $I \times 1$  は、電流帰還回路  $I \times 2$  のによって増幅され、電流  $I \times 2$  が生成される。この増幅率は先述のように第  $I \times 2$  が  $I \times 2$  が  $I \times 3$  により決定される。電流帰還回路  $I \times 3$  によって増幅された電流  $I \times 2$  は、出力トランジスタ  $I \times 3$  2 のゲートに供給され、出力トランジスタ  $I \times 3$  2 のゲートに供給され、出力トランジスタ  $I \times 4$  2 のゲート容量  $I \times 5$  2 によって充電される。これは  $I \times 5$  3 の関係において、充電電流  $I \times 5$  2 によって充電される。これは  $I \times 5$  4 は  $I \times 5$  5 に  $I \times 5$  6 において、  $I \times 5$  6 によってゲート電圧  $I \times 5$  7 の時間変化率が大きくなることを意味する。その結果、ゲート電圧  $I \times 5$  8 は、図 2 に実線で示すように破線で示した  $I \times 5$  8 ま早く立ち上がることになる。

#### [0046]

その結果、出力トランジスタ12のゲートソース間電圧Vgsは、ソース電圧である入力電圧Vinが変動した場合でも適切な値に調節され、出力電圧Voutは実線で示すようにオーバーシュートが抑制されて、安定化することができる。

## [0047]

このように、本実施形態にかかるレギュレータ回路100では、電流帰還回路20によって入力電圧Vinが変動する期間に過渡的に流れる電流Ix1を検出し、その電流を増幅して出力トランジスタ12のゲート端子に供給することによりゲート電圧Vgを強制的に上昇させてオーバーシュートを防止することができる。

## [0048]

また、このオーバーシュート抑制機能によって、通常、出力端子 1 0 4 と接地端子間に設けられるキャパシタ(図示せず)の容量値を小さくすることができる。

#### [0049]

さらに、電流 I × 1、 I × 2 は、上述のように入力電圧 V i n の時間微分に比例するため、入力電圧 V i n が時間的に変動した期間にのみ流れる。従って、本実施形態に係るレギュレータ回路 1 0 0 は、安定状態にあるときの消費電流を増やすことなく、出力電圧 V o u t のオーバーシュートを抑制することができる。

#### [0050]

このように、本実施の形態に係るレギュレータ回路100は、変動検出キャパシタ C 1 および電流帰還回路20によって、入力電圧 V i n の変動時に、出力トランジスタ12のゲート電圧 V g を強制的に変化させ、オーバーシュートを抑制する。クランプ回路30は、上述のように、出力トランジスタ12のゲートソース間電圧 V g s の上限値、あるいは下限値、もしくはその両方を設定するものである。以下、ゲートソース間電圧 V g s の下

10

20

30

40

限値を設定する場合、上限値を設定する場合それぞれについて、第 1 、第 2 の実施の形態 にもとづいて、順に説明する。

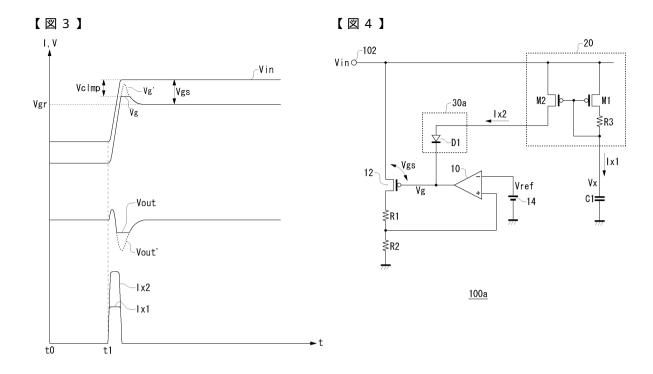

#### [0051]

(第1の実施の形態)

第1の実施の形態では、図1のクランプ回路30によって、出力トランジスタ12のゲートソース間電圧Vgsの下限値を設定する場合について説明する。はじめにその動作について説明し、次いでその具体的な構成例について説明する。

### [0052]

上述のように、電流帰還回路 2 0 により出力トランジスタ 1 2 のゲートに供給される電流は、入力電圧 V i n の時間変化率に比例する。したがって、入力電圧 V i n がきわめて速い速度で変動すると、過剰な電流が出力トランジスタ 1 2 のゲートに供給されることになる。その結果、出力トランジスタ 1 2 のゲートソース間電圧が小さくなり過ぎ、ひいては、ドレインソース間電圧 V d s が大きくなり過ぎて、アンダーシュートが発生する場合があった。本実施の形態において、図 1 のクランプ回路 3 0 は、以下のように、このアンダーシュートを抑制する機能を果たす。

#### [0053]

図3は、出力トランジスタ12のゲートソース間電圧Vgsの下限値を設定した場合の、図1のレギュレータ回路100の動作波形図である。はじめに、クランプ回路30の効果をより明確とするため、クランプ回路30を設けない場合の動作について説明する。図3に破線で示されるゲート電圧Vg′および出力電圧Vout′がこのときの電圧波形を示している。

#### [0054]

時刻 t  $0 \sim t$  1 においては、入力電圧 V i n i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d i d

#### [0055]

このとき、変動検出キャパシタC1には、入力電圧Vinの時間変化率dVin/dtに比例した電流I×1が流れる。その結果、出力トランジスタ12のゲートに供給される電流I×2は、図2の場合に比べて非常に大きくなる。出力トランジスタ12のゲート容量に、過剰な電流が供給されると、ゲート電圧Vgは、所望の出力電圧を与える安定すべき電圧Vgrを超えて上昇する。その結果、出力トランジスタ12のゲートソース間電圧Vgsが非常に小さくなり、出力トランジスタ12のドレインソース間電圧Vdsが大きくなるため、出力電圧Voutが、破線で示すようにアンダーシュートする。

## [0056]

次に、本発明の実施形態にかかるレギュレータ回路100について、クランプ回路30を設けて、出力トランジスタ12のゲートソース間電圧Vgsの下限値(以下、クランプ電圧Vc1mpという)を設定した場合の動作について、図3に、実線で示される電圧波形Vg、Voutをもとに説明する。

#### [0057]

時刻 t 1 に、入力電圧 V i n が急激に上昇し、その時間変化率に比例した電流 I x 2 が、出力トランジスタ 1 2 のゲートに供給され、ゲート電圧 V g が急速に上昇する。時刻 t 1 に、ゲートソース間電圧 V g が、クランプ電圧 V c 1 m p まで小さくなると、クランプ回路 3 0 によってゲート電圧 V g がクランプされる。このとき、出力トランジスタ 1 2 は完全にオフせず、したがって、ドレインソース間電圧 V d s が必要以上に大きくなならないため、出力電圧 V o u t のアンダーシュートを抑制することができる。

#### [0058]

次に、クランプ回路 3 0 の構成例について説明する。図 4 は、本実施の形態に係るレギュレータ回路 1 0 0 a の構成例を示す回路図である。本実施の形態に係るレギュレータ回路 1 0 0 a のクランプ回路 3 0 a は、第 1 ダイオード D 1 を含む。第 1 ダイオード D 1 は

10

20

30

40

、電流帰還回路20から出力トランジスタ12のゲートへの電流供給経路上に、カソードが出力トランジスタ12のゲート側に、アノードが電流帰還回路20側となるように配置される。この第1ダイオードD1は、PN接合を有するダイオード素子、ベースコレクタ間を接続したバイポーラトランジスタ、あるいはMOSFETのボディダイオードなどを利用して形成してもよい。

#### [0059]

本実施の形態に係るレギュレータ回路 100aのクランプ回路 30aは、出力トランジスタ 12のゲートと、入力端子 102の電圧差、すなわち、出力トランジスタ 12のゲートソース間電圧 Vgsが、第 1 ダイオード D1 の順方向電圧 Vf(0.7V) 以上となるようにクランプすることができる。より厳密には、本実施の形態に係るレギュレータ回路 100a では、出力トランジスタ 120 のゲートソース間電圧 Vgs は、ダイオードの順方向電圧 Vf と、第 2 トランジスタ 120 のドレインソース間電圧 Vds の和電圧以上となるようにクランプされる。

## [0060]

なお、クランプ回路 3 0 a は、第 1 ダイオード D 1 を抵抗に置換して構成しても良い。この場合、この抵抗には、電流 I  $\times$  2 に、抵抗値を乗じた電圧降下をクランプ電圧 V c 1 m p に設定することができる。この場合、抵抗値の選択によって、クランプ電圧 V c 1 m p を調節することができる。また、クランプ回路 3 0 a は、ダイオードと抵抗を直列に接続して構成してもよい。

## [0061]

## [0062]

このように、クランプ回路30aを入力電圧Vinの変動時のみ動作させることにより、定常状態においては、出力トランジスタ12のゲートソース間電圧Vgsはクランプされないため、出力トランジスタ12のオン抵抗を、クランプ回路30aによって制約を受けることなく自由に制御し、出力電圧Voutを所望の電圧に安定化することができる。

## [0063]

さらに、出力トランジスタ12のゲートソースしきい値電圧Vthは、プロセスにも依存するが、典型的には1V~2Vの範囲である。一方、本実施の形態に係るレギュレータ回路100aにおいて、クランプ電圧Vc1mp 0.7Vである。このように、クランプ電圧Vc1mpを、出力トランジスタ12のしきい値電圧Vthより小さく設定することにより、変動検出キャパシタC1および電流帰還回路20によるオーバーシュート抑制機能と、クランプ回路30によるアンダーシュート抑制機能をバランス良く実現することができる。

#### [0064]

(第2の実施の形態)

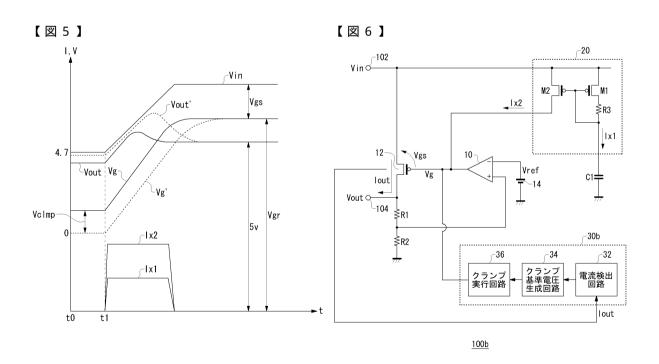

第2の実施の形態では、クランプ回路30によって、出力トランジスタ12のゲートソース間電圧Vgsの上限値を設定する場合について説明する。はじめにその動作について説明し、次いでその具体的な構成例について説明する。

#### [0065]

本実施の形態において、クランプ回路30は、出力トランジスタ12のゲート電圧Vgを、クランプ電圧Vclmp以上となるようにクランプする。

#### [0066]

図5は、第2の実施の形態に係るレギュレータ回路100の動作波形図である。はじめに、クランプ回路30の効果をより明確とするため、クランプ回路30を機能させない場

10

20

30

40

20

30

40

50

合の動作について説明する。図 5 に破線で示されるゲート電圧 V g 'および出力電圧 V o u t 'がこのときの電圧波形を示している。

#### [0067]

### [0068]

### [0069]

次に、本発明の実施形態にかかるレギュレータ回路100について、クランプ回路30を機能させた場合の動作について、図5に、実線で示される電圧波形Vg、Voutをもとに説明する。

## [0070]

時刻 t 0 ~ t 1 の入力電圧低下状態において、出力トランジスタ 1 2 のゲート電圧 V g は、クランプ回路 3 0 によってクランプ電圧 V c 1 m p 以上となるようにクランプされる。ゲート電圧 V g の下限値が設定されることは、出力トランジスタ 1 2 のゲートソース間電圧 V g s に上限値が設定されることと等価である。ゲートソース間電圧 V g s に上限値が設定されると、出力トランジスタ 1 2 はフルオンしなくなるため、時刻 t 0 ~ t 1 の間の出力電圧 V o u t は、破線の出力電圧 V o u t 'よりも低くなる。

### [0071]

時刻 t 1 に、入力電圧 V i n が上昇すると、電流 I x 2 によって出力トランジスタ 1 2 のゲート容量が充電され、ゲート電圧 V g が上昇する。このときの出力トランジスタ 1 2 のゲートソース間電圧 V g s は、クランプ回路 3 0 を機能させない場合のゲートソース間電圧 V g s に比べて、概ねクランプ電圧 V c 1 m p 分だけ小さくなる。その結果、出力トランジスタ 1 2 はフルオンせず、ドレインソース間電圧 V d s をある程度以上の値に保ちつつ、入力電圧 V i n が上昇ことになる。その結果、出力電圧 V o u t が、入力電圧 V i n に追従して上昇するのを防止し、オーバーシュートを抑制することができる。

## [0072]

図6は、第2の実施の形態に係るレギュレータ回路100bの構成例を示す回路図である。このレギュレータ回路100bのクランプ回路30bは、出力電圧Voutより差分電圧 Vだけ低い電圧を、クランプ電圧Vc1mpに設定し、出力トランジスタ12のゲート電圧Vgを、クランプ電圧Vc1mp以上となるようにクランプする。本実施の形態において、差分電圧 Vは、出力トランジスタ12に流れる出力電流Ioutに応じて大きくなる電圧である。差分電圧 Vは、出力トランジスタ12に流れる出力電流Ioutに比例して大きくなる成分 V1と、所定の固定電圧 V2の和となるように設定してもよい。

## [0073]

クランプ回路30 b は、電流検出回路32、クランプ基準電圧生成回路34、クランプ 実行回路36を含む。電流検出回路32は、出力トランジスタ12に流れる出力電流Io utに応じた検出電流Idetを生成する。クランプ基準電圧生成回路34は、出力電圧 Voutよりも、検出電流Idetに比例した電圧 V1だけ低いクランプ基準電圧Vc

20

30

40

50

lmprefを生成する。Vclmpref=Vout- V1が成り立つ。

### [0074]

クランプ実行回路36は、クランプ基準電圧生成回路34により生成されるクランプ基準電圧Vclmprefよりも、さらに所定の電圧 V2だけ低い電圧を、クランプ電圧 Vclmpに設定し、出力トランジスタ12のゲート電圧Vgをクランプする。

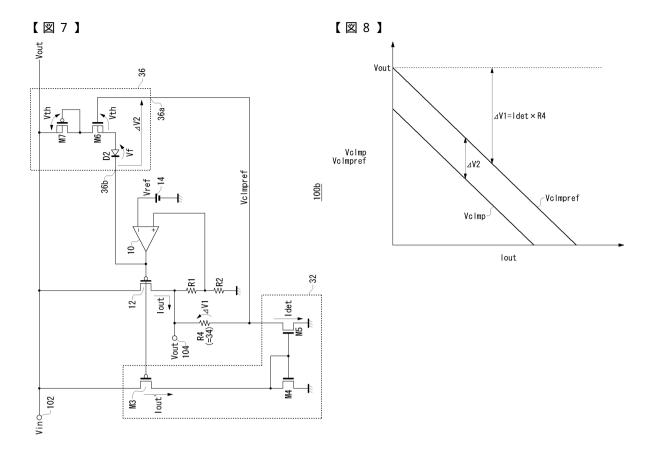

## [0075]

図7は、図6のレギュレータ回路100bのより詳細な回路図である。図7において、変動検出キャパシタC1および電流帰還回路20は省略している。

### [0076]

電流検出回路32は、トランジスタM3、M4、M5を含む。トランジスタM3は、出力トランジスタ12とゲート、ソースが共通に接続されたPチャンネルMOSFETである。出力トランジスタ12およびトランジスタM3のサイズ比は、たとえば1000:1程度に設定する。トランジスタM3には、出力トランジスタ12に流れる出力電流Ioutに比例した電流Iout、が流れる。トランジスタM4は、NチャンネルMOSFETであって、電流Iout、の経路上に設けられる。トランジスタM5は、トランジスタM4とともにカレントミラー回路を構成しており、電流Iout、を定数倍した検出電流Idetを生成する。

## [0077]

本実施の形態において、クランプ基準電圧生成回路34は抵抗R4を含んで構成される。この抵抗R4は、一端が出力端子104に接続され、電流検出回路32により生成される検出電流Idetの経路上に設けられる。この抵抗R4には、検出電流Idetに、抵抗値R4を乗じた電圧降下 V1が発生する。すなわち、抵抗R4の他端の電圧には、出力電圧Voutより検出電流Idetに比例した電圧 V1だけ低いクランプ基準電圧Vclmpref(=Vout・ V1=Vout-Idet×R4)が現れる。

#### [0078]

クランプ実行回路36には、クランプ基準電圧Vc1mprefおよび出力電圧Voutが入力される。図7のクランプ実行回路36は、トランジスタM6、M7、第2ダイオードD2を含む。トランジスタM6は、NチャンネルMOSFETであって、ゲートにクランプ基準電圧Vc1mprefが印加される。第2ダイオードD2は、アノードがトランジスタM6のソースに接続され、カソードが出力トランジスタ12のゲートに接続される。また、トランジスタM6のドレインには、ドレインソースが接続されたPチャンネルMOSFETであるトランジスタM7が接続される。トランジスタM7のソースは、出力端子104と接続され、出力電圧Voutが印加される。トランジスタM7は、出力トランジスタ12とペアリングして構成することが望ましい。

#### [0079]

第2ダイオードD2は、クランプ基準電圧生成回路34の出力端子から、出力トランジスタ12のゲートに至る経路上に、カソード端子が出力トランジスタ12のゲート側となるように設けられる。

## [0800]

このように構成したクランプ実行回路36は、クランプ基準電圧Vc1mprefよりも、電圧 V2だけ低い電圧をクランプ電圧Vc1mpに設定する。ここで電圧 V2は、トランジスタM6のゲートソースしきい値電圧Vthと、第2ダイオードD2の順方向電圧Vfの和となる。また、トランジスタM7は、出力トランジスタ12とペアリングして形成されるため、2つのトランジスタのゲートソースしきい値電圧Vthはほぼ等しくなる。したがって、トランジスタM6のゲートソースしきい値電圧Vthがばらついた場合においても、電圧 V2は、トランジスタM7のゲートソースしきい値電圧Vthと、第2ダイオードD2の順方向電圧Vfの和に設定される。

#### [0081]

以上のように構成されたレギュレータ回路100bによれば、出力電圧Voutが低下するに従って、クランプ電圧Vclmpを低下させることができる。その結果、入力電圧

Vinが出力電圧Voutの目標値を下回るような場合、入力電圧Vinに応じてクランプ電圧Vclmpを設定することができ、幅広い入力電圧Vinの範囲において、より好適にオーバーシュートを抑制することができる。

#### [0082]

図8は、本実施の形態に係るレギュレータ回路100bの、出力電流Ioutと、クランプ電圧Vc1mpならびにクランプ基準電圧Vc1mprefの関係を示す。上述のようにクランプ基準電圧Vc1mprefは、出力電圧Voutから、差分電圧 V1だけ低い値に設定される。ここで、 V1=Idet×R4であるから、出力電流Ioutが増加するにしたがい、クランプ基準電圧Vc1mprefは低下する。

## [0083]

クランプ電圧 V c l m p は、クランプ基準電圧 V c l m p r e f よりも、差分電圧 V 2 だけ低い電圧に設定される。ここで、差分電圧 V 2 は、 V 2 = V t h + V f である。本実施の形態に係るレギュレータ回路 1 0 0 b では、負荷に流れる出力電流 I o u t が大きくなるに従って、クランプ電圧 V c l m p が低く設定される。

#### [0084]

あるドレインソース間電圧Vdsを得るために必要なゲートソース間電圧Vgsは、出力電流Ioutが大きいほど大きくなる。本実施の形態に係るレギュレータ回路100によれば、軽負荷時には、ゲート電圧Vgの下限値を高く(すなわちゲートソース間電圧Vgsの上限値を低く)設定し、重負荷となるに従って、ゲート電圧Vgの下限値を低く(すなわちゲートソース間電圧Vgsの上限値を高く)設定することができる。その結果、負荷の状態に応じて、より好適にオーバーシュートを抑制することができる。

#### [0085]

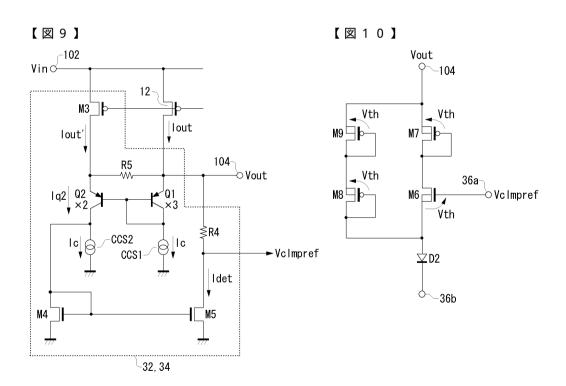

図9は、本実施の形態に係るレギュレータ回路の電流検出回路32、クランプ基準電圧 生成回路34の変形例である。図9の電流検出回路32は、トランジスタM3~M5、抵抗R5、トランジスタQ1、Q2、定電流源CCS1、CCS2、を含む。

#### [0086]

トランジスタM3は、出力トランジスタ12とゲートおよびソースが共通に接続されており、カレントミラー回路を構成する。出力トランジスタ12およびトランジスタM3のそれぞれのドレイン間には、抵抗R5が設けられる。トランジスタQ1およびQ2は、サイズの異なるPNP型のバイポーラトランジスタである。たとえば、トランジスタQ1と2のサイズ比を、3:2に設定する。トランジスタQ1、Q2のベースは共通に接続され、トランジスタQ1のベースとコレクタは接続される。トランジスタQ1のエミッタは、トランジスタM3のドレインに接続され、トランジスタQ2のエミッタは、トランジスタM3のドレインに接続される。トランジスタQ1、Q2のコレクタには、それぞれ定電流源CCS1、CCS2が負荷として接続される。定電流源CCS1、CCS2は、等しい定電流Icを生成する。この定電流Icは、数十nAから数μAの非常に低い電流値に設定することが望ましい。

#### [0087]

このように構成された電流検出回路 3 2 の動作について説明する。はじめに、出力トランジスタ 1 2 に流れる出力電流 I o u t が流れないあるいは非常に小さい無負荷状態について説明する。トランジスタ Q 1 と、 Q 2 には、等しい定電流 I c が流れるが、そのサイズ比が異なっているため、それぞれのエミッタ間、すなわち抵抗 R 5 の両端には電位差が生ずる。出力電流 I o u t が流れないとき、トランジスタ Q 2 には、定電流源 C C S 2 により生成される定電流 I c のみが流れる。その結果、トランジスタ M 4 には電流が流れず、検出電流 I d e t は I A となる。

## [0088]

レギュレータ回路100bから負荷に出力電流Ioutが流れ始めると、トランジスタM3にも、出力電流Ioutに比例した電流Iout'が流れる。この電流Iout'は、その一部が、抵抗R5を介して負荷に供給され、その残りがトランジスタQ2に供給される。トランジスタQ2の経路に流れる電流をIQ2とすると、トランジスタM4には、

10

20

30

40

20

30

40

50

電流(I q 2 - I c )が流れることになる。上述のように定電流 I c の値を非常に小さく設定しておけば、トランジスタ M 4 に流れる電流は、出力電流 I o u t にほぼ比例した電流とみなすことができる。トランジスタ M 4 に流れる電流は、トランジスタ M 5 により複製され、抵抗 R 4 によって電圧変換される。

### [0089]

図9の電流検出回路32によれば、第3トランジスタM3に流れる電流の大部分は負荷に供給され、定電流源CCS2およびトランジスタM4を介して接地に流れる電流は、非常に小さくなる。その結果、検出電流Idetを低減することができ、回路の消費電流を低減することができる。

### [0090]

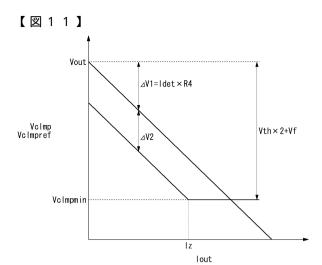

図10は、クランプ実行回路36の別の変形例を示す回路図である。図10のクランプ実行回路36は、図7のクランプ実行回路36に加えて、さらにトランジスタM8、M9を備える。トランジスタM8、M9は、いずれも、ゲートドレインを接続したPチャンネルMOSFETであり、第2ダイオードD2のアノードと出力端子104との間に、直列に接続される。すなわち、トランジスタM8のドレインは、第2ダイオードD2のアノードに接続され、そのソースは、トランジスタM9のドレインに接続される。トランジスタM9のソースは、出力端子104と接続され、出力電圧Voutが印加される。

## [0091]

図11は、図10のクランプ実行回路36における、出力電流Ioutと、クランプ電圧Vc1mpの関係を示す図である。図8と同様に、クランプ基準電圧Vc1mprefは、出力電流Ioutの増加にともない、低下していく。クランプ電圧Vc1mpは、クランプ基準電圧Vc1mprefよりも、差分電圧 V2低い電圧に設定されるため、出力電流Ioutの増加にともない、一定の傾きで低下する。出力電流Ioutが、所定レベル(図11のIz)まで増加すると、トランジスタM8、M9および第2ダイオードD2によってゲート電圧Vgがクランプされる。その結果、クランプ電圧Vc1mpmは、最低クランプ電圧Vc1mpminは、出力電圧Voutから、トランジスタM8、M9のゲートソースしきい値電圧Vthおよび第2ダイオードD2の順方向電圧Vfだけ低下した電圧Vout・(Vth×2+Vf)に設定される。

### [0092]

このように、図10のクランプ実行回路36を用いることにより、クランプ電圧Vclmpに、出力電圧Voutに応じた下限値を設定することができる。

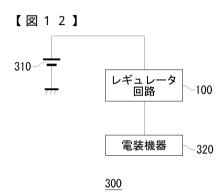

#### [0093]

最後に、上述のレギュレータ回路100の用途について説明する。レギュレータ回路100は、たとえば、自動車に搭載される。図12は、レギュレータ回路100を搭載した自動車300の電気系統のブロック図である。自動車300は、バッテリ310、レギュレータ回路100、電装機器320を備える。バッテリ310は、13V程度のバッテリ電圧Vbatを出力する。このバッテリ電圧Vbatは、リレーを介して出力されるため、時間的に変動が大きい。一方、電装機器320は、たとえば、カーステレオやカーナビゲーションシステム、インテリアパネルの照明用LEDなどであって、時間的に変動しない安定した電源電圧を必要とする負荷である。レギュレータ回路100は、バッテリ電圧Vbatを所定の電圧に降圧して電装機器320に出力する。

### [0094]

上述したように、実施形態で説明したレギュレータ回路100は、入力電圧Vinや出力電圧Voutの急峻な変動に対して、高速に追従し、出力電圧Voutのアンダーシュート、オーバーシュートを小さく抑えることができる。したがって、自動車に搭載されるバッテリなどのように、電圧が大きく変動するような電源を安定化する用途に好適に用いることができる。

#### [0095]

もっとも、実施形態で説明したレギュレータ回路100は、車載用途に限らず、入力電

圧を安定化して負荷に供給するさまざまな用途に用いることができる。

#### [0096]

上述の実施の形態は例示であり、それらの各構成要素や各処理プロセスの組合せにいるいるな変形例が可能なこと、またそうした変形例も本発明の範囲にあることは当業者に理解されるところである。

#### [0097]

各実施の形態に係るレギュレータ回路100の各構成要素は、単独で用いた場合には、上述の作用および効果を有するが、任意に組み合わせてもよい。この場合、より好適にアンダーシュートやオーバーシュートを好適に抑圧することができる。たとえば、図1のクランプ回路30が、図4のクランプ回路30aと、図6あるいは図7に示されるクランプ回路30bの両方を含む構成となっていてもよい。

[0098]

実施の形態において、クランプ回路 3 0、さらには電流検出回路 3 2、クランプ基準電圧生成回路 3 4、クランプ実行回路 3 6の構成について、好ましい形態について例示したが、本発明はこれらに限定されるものではない。たとえば、クランプ実行回路 3 6 については、ある電圧を基準として対象電圧をクランプする回路を用いることができる。

#### [0099]

実施の形態においてMOSFETとして例示されたトランジスタは、バイポーラトランジスタで構成してもよく、また、バイポーラトランジスタで例示されたトランジスタは、MOSFETで構成してもよい。また、天地反転にともなうPチャンネルとNチャンネル、PNP型とNPN型の置換や、抵抗の挿入などによる回路の変形例は、当然に本発明の技術的範囲に含まれる。いずれのトランジスタを用いるかは、レギュレータ回路に要求される設計仕様、使用する半導体製造プロセスなどによって決めればよい。

#### [0100]

実施の形態において、レギュレータ回路100を構成する素子はすべて一体集積化されていてもよく、その一部がディスクリート部品で構成されていてもよい。どの部分を集積化するかは、コストや占有面積などによって決めればよい。

【図面の簡単な説明】

[0101]

【図1】実施の形態に係るレギュレータ回路の構成を示すブロック図である。

【図2】入力電圧が急激に上昇したときの、図1のレギュレータ回路の動作波形図である

【図3】第1の実施の形態に係るレギュレータ回路の動作波形図である。

【図4】第1の実施の形態に係るレギュレータ回路の構成例を示す回路図である。

【図5】第2の実施の形態に係るレギュレータ回路の動作波形図である。

【図6】第2の実施の形態に係るレギュレータ回路の構成例を示す回路図である。

【図7】図6のレギュレータ回路のより詳細な回路図である。

【図8】本実施の形態に係るレギュレータ回路の、出力電流と、クランプ電圧ならびにクランプ基準電圧の関係を示す図である。

【図9】レギュレータ回路の電流検出回路、クランプ基準電圧生成回路の変形例を示す回 40 路図である。

【図10】クランプ実行回路の別の変形例を示す回路図である。

【図11】図10のクランプ実行回路における、出力電流と、クランプ電圧ならびにクランプ基準電圧の関係を示す図である。

【図12】レギュレータ回路を搭載した自動車の電気系統のブロック図である。

## 【符号の説明】

#### [0102]

100 レギュレータ回路、 102 入力端子、 104 出力端子、 10 誤差 増幅器、 12 出力トランジスタ、 14 基準電圧源、 R1 第1抵抗、 R2 第2抵抗、 R3 利得調整抵抗、 C1 変動検出キャパシタ、 D1 第1ダイオー 10

20

30

30

ド、 20 電流帰還回路、 30 クランプ回路、 32 電流検出回路、 34 クランプ基準電圧生成回路、 36 クランプ実行回路、 D2 第2ダイオード、 50 オーバーシュート抑制回路、 M1 第1トランジスタ、 M2 第2トランジスタ。

## フロントページの続き

## (56)参考文献 特開2002-189522(JP,A)

特開昭53-067848(JP,A)

特開2002-343874(JP,A)

特開平08-190437(JP,A)

米国特許出願公開第2004/0263137(US,A1)

特開2002-222929(JP,A)

特開2001-337729(JP,A)

特開2003-044150(JP,A)

特開2000-022456(JP,A)

特開2006-065836(JP,A)

## (58)調査した分野(Int.CI., DB名)

G05F 1/445,1/56,1/613,1/618

B60R 16/03