(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2023/103900 A1

- (51) International Patent Classification: *H02M 3/156* (2006.01) *H02M 3/157* (2006.01)

- (21) International Application Number:

PCT/CN2022/136160

(22) International Filing Date:

02 December 2022 (02.12.2022)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

21213515.6

09 December 2021 (09.12.2021) EP

- (71) Applicant: GOODIX TECHNOLOGY (HK) COMPANY LIMITED [CN/CN]; Room 2113, Level 21, Landmark North, 39 Lung Sum Avenue, Sheung Shui, Hong Kong (CN).

- (72) Inventors: KRABBENBORG, Bernardus Henricus; 6537 TL Nijmegen (NL). SEGUNDO BABARRO, Jokin;

6537 TL Nijmegen (NL). **BERKHOUT, Marco**; 6537 TL Nijmegen (NL).

- (74) **Agent: LONGSUN LEAD IP LTD.**; Room 801-1, Floor 8, Building 3, Block 2, No. 81 Beiqing Road, Haidian District, Beijing 100094 (CN).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CV, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IQ, IR, IS, IT, JM, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, WS, ZA, ZM, ZW.

(54) Title: FEEDBACK CIRCUIT WITH ADJUSTABLE LOOP GAIN FOR BOOST CONVERTER

Fig. 4

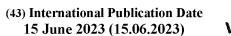

(57) Abstract: A feedback circuit for a boost converter wherein the feedback circuit comprises a measurement resistance  $R_M$  configured to receive a current  $I_{COIL}$  from the boost converter, a feedback resistance  $R_{SH}$ , a gain circuit  $g_M$  comprising a gain output and configured to receive a sensed voltage associated to the measurement resistance, and to provide, at the gain output, a gain signal generated based on the sensed voltage; and a comparison circuit comprising a comparison output, and configured to generate a comparison signal, at the comparison output, wherein the comparison signal is generated based on the gain signal, a voltage drop across the feedback resistance  $R_{SH}$  and a reference signal  $V_{REF}$ .

#

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, CV, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, ME, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### **Published:**

— with international search report (Art. 21(3))

### FEEDBACK CIRCUIT WITH ADJUSTABLE LOOP GAIN FOR BOOST CONVERTER

#### CROSS-REFERENCE TO RELATED APPLICATIONS

5 **[0001]** This patent document claims the priority to and benefits of EP Patent Application No. 21213515.6 entitled "Feedback circuit with adjustable loop gain for a boost converter" filed on December 9, 2021. The entire content of the aforementioned patent applications are incorporated by reference as part of the disclosure of this patent document.

#### **TECHNICAL FIELD**

10 **[0002]** The invention relates to a feedback circuit for a boost converter with adjustable loop gain. The invention further relates to a boost converter circuit comprising the feedback circuit with adjustable loop gain and to a method of operating the feedback circuit with adjustable loop gain.

15

20

25

#### **BACKGROUND**

- [0003] Energy harvesting is the process by which energy is derived from external sources, captured, and stored for small, wireless autonomous devices, like those used in wearable electronics and wireless sensor networks. A direct current to direct current 'DC-to-DC' converter circuits, such as boost converter circuits, are electronic circuits that convert a source of direct current (DC) from one voltage level to another voltage by first charging an energy storage element using an input voltage and then discharging the energy storage element to provide the energy at the output of the DC-to-DC converter. DC-to-DC converters can be used to increase the amount of energy harvested from an energy source. Constant-On-Time (COT) boost converters are popular for its simplicity and high performance in both continuous conduction mode (CCM) and discontinuous conduction mode (DCM). COT boost converters use feedback circuits to control the switching of the boost circuit. These feedback circuits need to comply with certain stability requirements in order to work properly. As the stability criteria depends on the value of some of the components of the boost converter circuit for a given target output voltage, the stability criteria is met at the price of efficiency and/or costs.

- 30 [0004] Xiaoru Xu, Xiaobo Wu, Xiaolang Yan, " A Quasi Fixed Frequency Constant On Time Controlled Boost Converter," *IEEE International Symposium on Circuits and Systems*,

ISCAS 2008, discloses a COT boost converter circuit wherein, for a given battery voltage  $V_{BAT}$  as input, a given inductor  $L_{BST}$  and a given target current  $I_{LOAD}$ , a requirement for stability contradicts with requirements for cost, i.e. a low value of the capacitor  $C_{BST}$  at the output, and efficiency, i.e. a low value of the measurement resistor  $R_M$ ). I.e., stability can only be reached at expenses of efficiency or cost. An obvious way to prevent the contradictory requirements is the use a different kind of converter topology, but that eliminates all the simplicity and performance advantages of the COT topology.

[0005] Jinping Wang, Liangkui Hou, Liang Zhang, Sheng Xiang, and Yigang He, "Analysis of the Low-frequency Oscillation Phenomenon in Constant-on-time Controlled Boost Converter", *IEEE Energy Conversion Congress and Exposition*, ECCE 2015 discloses a method that consists on relocating the measurement resistance R<sub>M</sub> of the feedback circuit in series with the output capacitor C<sub>BST</sub>. In this way, the dissipation is moved to the output capacitor C<sub>BST</sub>. However, this does not improve efficiency and makes the stability dependent on the parasitic of an external component, i.e. on the output capacitor C<sub>BST</sub>. Moreover, the stability requirements still depend on the measurement value of the resistance R<sub>M</sub>. Furthermore, this configuration also introduces a high unwanted ripple on the output voltage V<sub>BST</sub>.

[0006] It would be advantageous to implement a low cost efficient feedback circuit for a boost converter circuit that still meets the required stability criteria.

20 SUMMARY

5

10

15

25

30

[0007] An object of the invention is to implement a stable boost converter circuit in an efficient and cost-effective way.

**[0008]** The invention relates to a feedback circuit for a boost converter circuit wherein the feedback circuit comprises a measurement resistance  $R_M$  configured to receive a current  $I_{COIL}$  from the boost converter, a feedback resistance  $R_{SH}$ , a gain circuit  $g_M$  comprising a gain output and configured to receive a sensed voltage associated to the measurement resistance, and to provide, at the gain output, a gain signal  $I_M$  generated based on the sensed voltage; and a comparison circuit comprising a comparison output, and configured to generate a comparison signal, at the comparison output, wherein the comparison signal is generated based on the gain signal, a voltage drop across the feedback resistance  $R_{SH}$  and a reference signal  $V_{REF}$ . In this way, the gain circuit introduces a gain at the comparison circuit which allows to meet the required stability criteria in an efficient and simple way.

This allows to extend the load current range for a constant-on-time boost converter circuit beyond the limits normally dominated by external components, battery voltage and switch resistance. This means that the maximum load current can be increased to levels where a conventional converter would not be stable, or would need a higher measurement resistance value by choosing a high Effective Series Resistance (ESR) in the output capacitance, resulting in power loss and high ripple voltage, or a high switch resistance resulting in high power losses, or would need a higher output capacitance value, or would need a lower inductor value resulting in higher ripple current amplitude. Furthermore, the gain setting can be used to optimize the balance between cost (external capacitance), efficiency (measurement resistance, ESR), performance (output resistance, ripple voltage, ripple current) and for a given use case (load current, battery voltage). Also the use of capacitor in the feedback circuit is prevented such that the feedback circuit can be smaller compared to a feedback circuit using a capacitor suited for the whole voltage range.

5

10

15

20

25

30

**[0009]** The measurement resistance  $R_M$  may comprise a first end and a second end, the gain circuit may comprise a first gain input and a second gain input and wherein the gain circuit may be configured to receive, at the first gain input, a first voltage sensed at the first end of the measurement resistance, to receive, at the second gain input, a second voltage sensed at the second end of the measurement resistance, and to provide, at the gain output, the gain signal  $I_M$  generated based on the first sensed voltage and the second sensed voltage. This is a suitable way to connect the gain circuit such that the gain can be provided at the inputs of the comparison circuit in an efficient way.

**[0010]** The feedback resistance  $R_{SH}$  may comprise a first end and a second end and wherein the first end of the feedback resistance  $R_{SH}$  may be coupled to the second end of the measurement resistance, the second end of the feedback resistance ( $R_{SH}$ ) may be coupled to the comparison circuit and the gain output may be coupled to the comparison circuit. Again, this allows for providing the gain at the inputs of the comparison circuit in an efficient way.

[0011] The comparison circuit may comprise a first comparison input, a second comparison input and a comparison output, wherein the comparison circuit may be configured to receive the reference voltage at the first input, to receive a feedback signal at the second input, and to generate the comparison signal by comparing the feedback signal and the reference signal, wherein the feedback signal may be based on the gain signal and

the voltage drop across the feedback resistance. This provides the gain at the input of the comparison circuit in a suitable and efficient manner, thereby saving in resources.

[0012] The gain output may be coupled to the second end of the feedback resistance and to the second comparison input. This is a suitable manner of connecting the gain output to provide the gain at the input of the comparison circuit.

5

10

15

20

25

30

[0013] The feedback circuit may comprise another feedback resistance configured to receive the gain signal wherein the comparison circuit may comprise a first comparison input, a second comparison input and a comparison output, wherein the comparison circuit is configured to receive, at the first comparison input, the sum of the reference voltage and a further voltage drop caused by the gain signal across the another feedback resistance, to receive the voltage drop across the feedback resistance R<sub>SH</sub> at the second comparison input and to generate the comparison signal by comparing the sum of the reference voltage and the further voltage drop with the voltage drop across the feedback resistance R<sub>SH</sub>. This allows to provide the gain to the circuit independently of the value of R<sub>SH</sub>.

[0014] The another feedback resistance may comprise a first and a second end wherein the first comparison input may be coupled to the first end of the another feedback resistance and to the gain output and wherein the second end of the another feedback resistance may be coupled to the reference voltage.

[0015] The gain circuit may comprise a voltage controlled current source. This is a suitable implementation of the gain circuit.

[0016] The first end of the feedback resistance  $R_{SH}$  may be coupled to an output terminal  $V_{BST}$  of the boost converter.

[0017] The feedback circuit may further comprise a measurement switch  $S_M$  wherein the measurement switch  $S_M$  and the measurement resistance  $R_M$  may be coupled in series, wherein the measurement switch  $S_M$  and the measurement resistance  $R_M$  may be coupled in parallel with a first switch  $S_H$  of the boost converter, wherein the first switch  $S_H$  comprises an on-resistance  $R_H$  when the first switch  $S_H$  is closed, and wherein the feedback switch  $S_M$  and the first switch  $S_H$  of the boost converter circuit may be configured to open and close at the same time. This allows to reduce dissipation at the output because prevents energy loss at the measurement resistance by re-using the on-resistance  $R_H$  of the switch  $S_H$  which is present anyway. The measurement  $R_M$  is no longer in the high current path, and with an

additional switch  $S_M$ , that switches simultaneously with switch  $S_H$ , the voltage across the switch  $S_H$  and the on-resistance  $R_H$  is sensed when both switches  $S_H$  and  $S_M$  are closed. The measurement resistance  $R_M$  can now be chosen much larger so that the power loss in the measurement resistance  $R_M$  can be neglected.

- 5 [0018] The feedback circuit may further comprise an adjustable current source coupled to the second end of the feedback resistance and to the second comparison input of the comparison circuit. This is a suitable way of adjusting the voltage at the output to the required value. Alternatively, the feedback circuit may comprise a current DAC controlled by a digital word or a voltage controlled current source controlled by a control voltage or a current controlled current source controlled with a control current.

- [0019] The invention also relates to a boost converter circuit comprising a feedback circuit.

- [0020] The invention relates as well to a method of operating a feedback circuit for a boost converter circuit.

- 15 **[0021]** The person skilled in the art will understand that the features described above may be combined in any way deemed useful. Moreover, modifications and variations described in respect of the system may likewise be applied to a method.

#### BRIEF DESCRIPTION OF THE DRAWINGS

- [0022] In the following, aspects of the invention will be elucidated by means of examples, with reference to the drawings. The drawings are diagrammatic and are not drawn to scale.

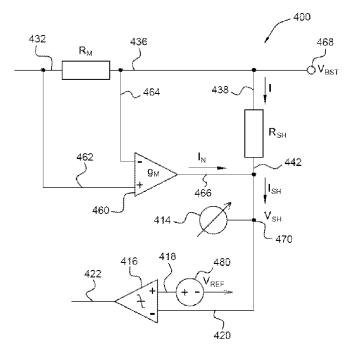

- [0023] Fig. 1 shows a known boost converter circuit.

20

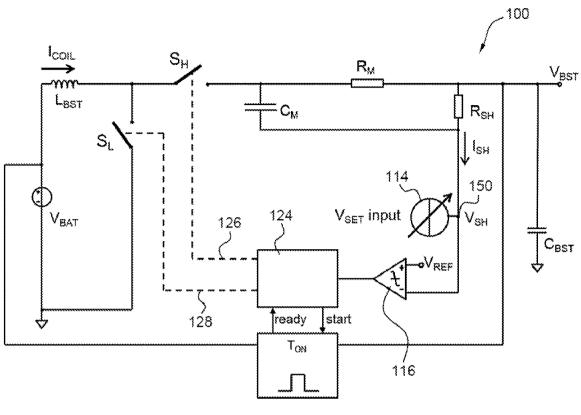

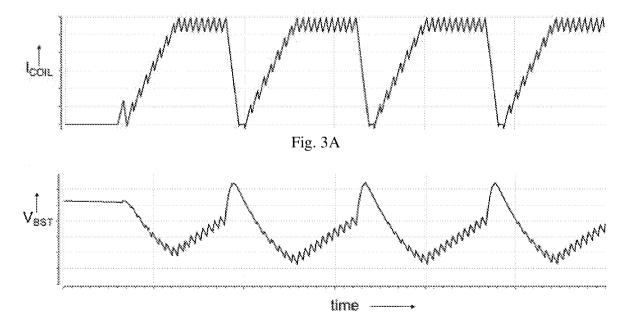

- [0024] Figs. 2A-B and 3A-B show diagrams of time waveforms of several signals of the boost converter circuit of Fig. 1 during operation.

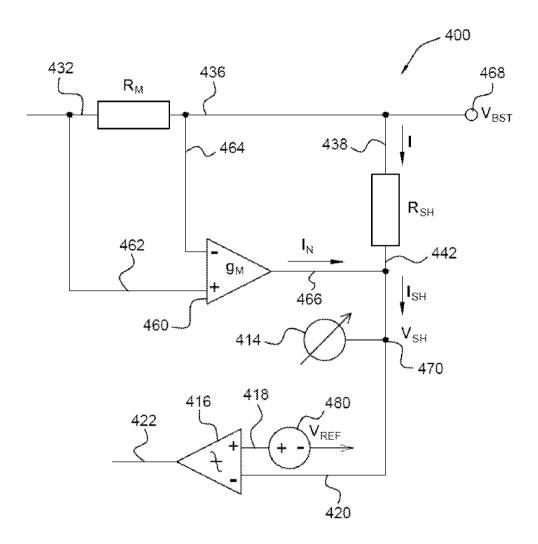

- [0025] Fig. 4 shows a feedback circuit according to an embodiment of the invention.

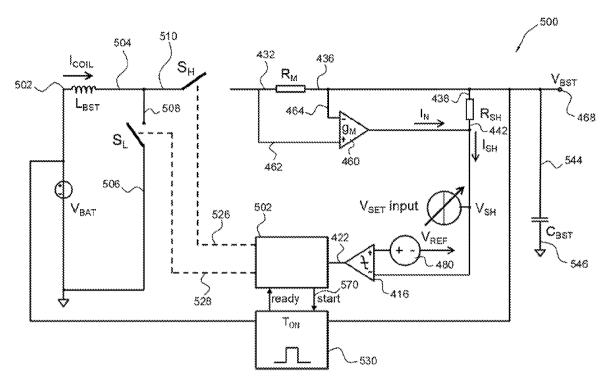

- 25 [0026] Fig. 5 shows a boost converter circuit comprising the feedback circuit of fig. 4.

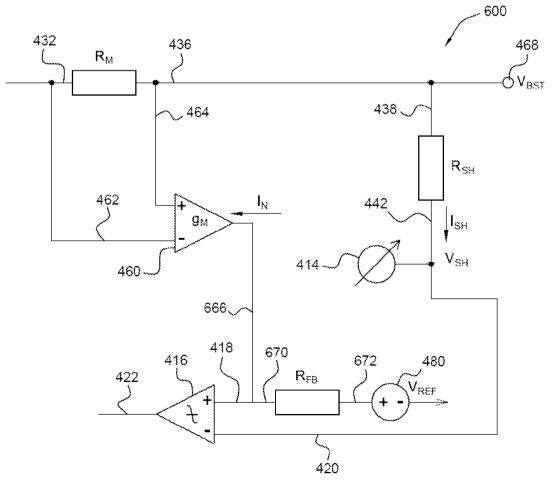

- [0027] Fig. 6 shows another feedback circuit according to another embodiment of the invention.

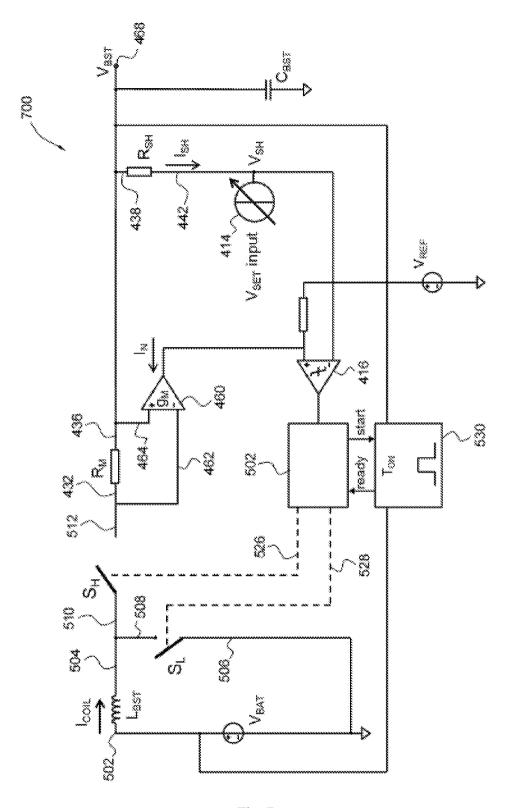

- [0028] Fig. 7 shows a boost converter circuit comprising the feedback of fig. 6.

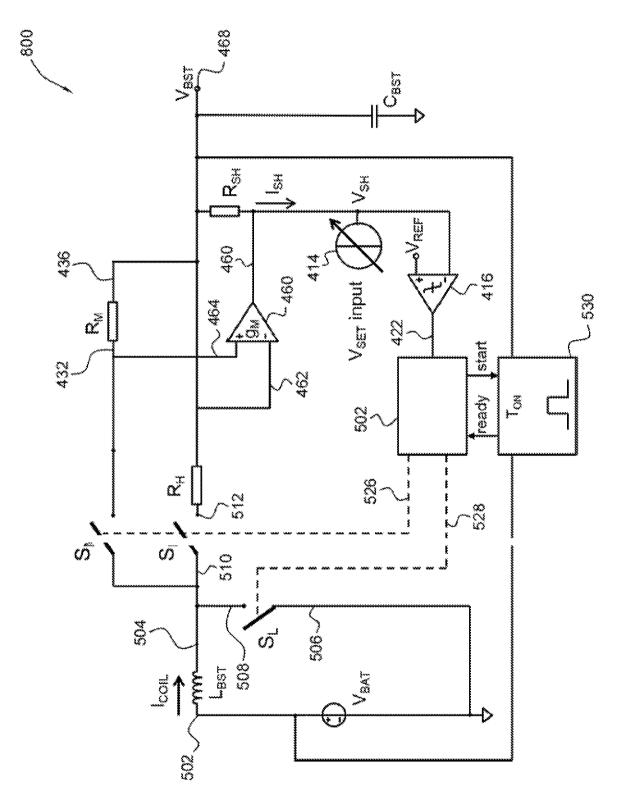

[0029] Fig. 8 shows a boost converter circuit comprising a feedback circuit according to another embodiment of the invention.

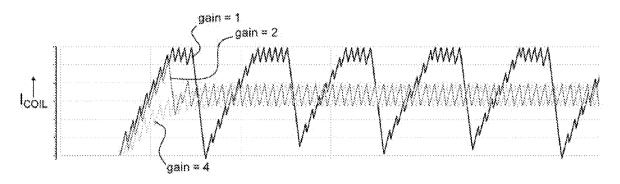

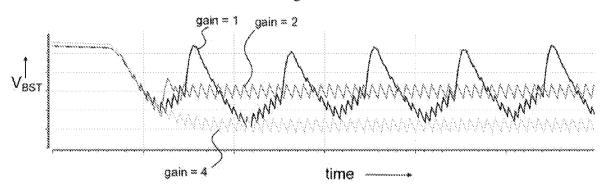

[0030] Figs. 9A-B show time diagrams of the waveforms of several signals of the boost converter circuit 800 of fig. 8 during operation.

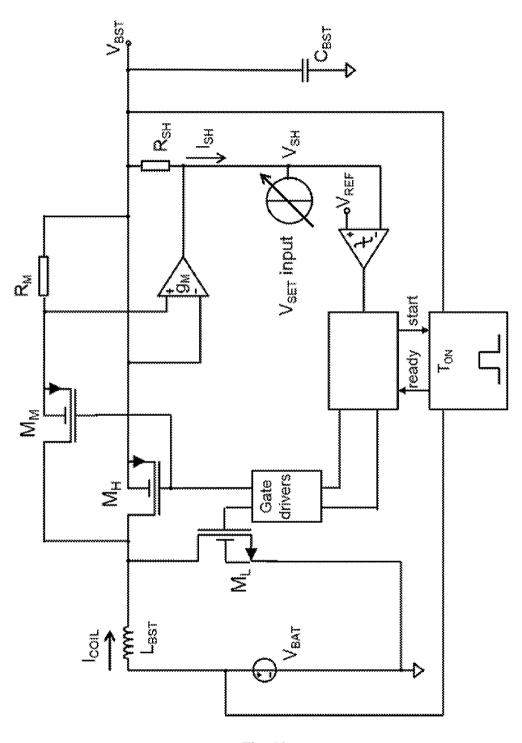

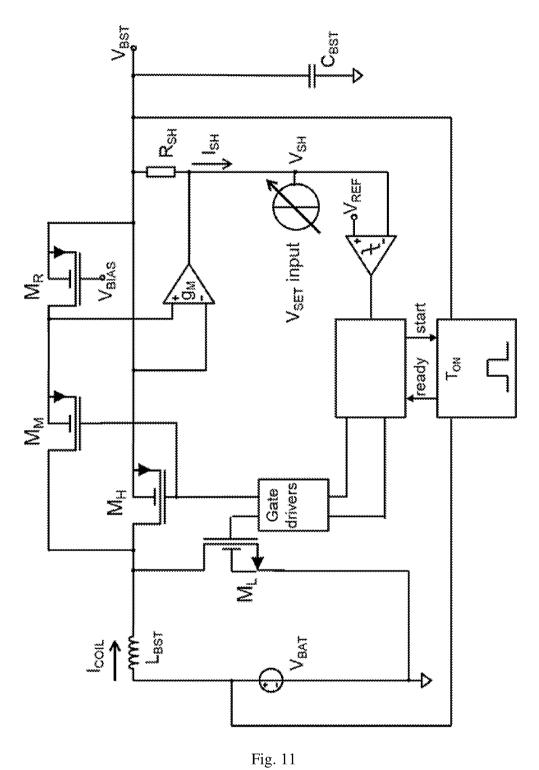

[0031] Figs. 10 and 11 show examples of implementations of the boost converter circuit of fig. 8.

5

10

15

20

25

30

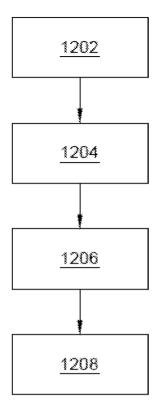

[0032] Fig. 12 shows a flowchart of a method of operating the feedback circuit for a boost converter circuit of fig. 6.

#### **DETAILED DESCRIPTION**

[0033] In the figures, the same reference numbers indicate elements that are similar in structure and function.

Fig. 1 shows a known boost converter circuit 100. Figs. 2A-B and 3A-B show diagrams of time waveforms of several signals of the boost converter circuit of fig. 1 during operation. The operation of a boost converter circuit will be now explained with reference to Fig. 1, 2A-B, and 3A-B. Figs. 2A-B illustrates the ideal values of V<sub>SH</sub>, and I<sub>COIL</sub> as a function of time for the different operation states of the boost converter circuit of fig. 1. Figs. 3A-B illustrate the real values of V<sub>BST</sub>, and I<sub>COIL</sub> as a function of time for the different operation states of the boost converter circuit of fig. 1. The I<sub>COIL</sub> is the current through the inductor L<sub>BST</sub>. As it can be seen in figs. 2A-B, during the time interval 200 the switch S<sub>L</sub> is close and the switch SH is open in order to connect the inductor LBST to the ground as it can be seen in fig. 1. When the inductor L<sub>BST</sub> is connected to ground, the boost converter circuit enters into a charging state in which current flows through the inductor L<sub>BST</sub> and the inductor L<sub>BST</sub> stores some energy by generating a magnetic field. The current I<sub>COIL</sub> in the inductor L<sub>BST</sub> increases during the time interval 200 as it can be seen in fig. 2A. A control unit 124 sends a control signal 128 to open the switch S<sub>L</sub> in order to disconnect the inductor L<sub>BST</sub> from the ground, and a control signal 126 to close the switch S<sub>H</sub> in order to connect the inductor L<sub>BST</sub> to the output V<sub>BST</sub> via a measurement resistor R<sub>M</sub> as it can be seen in fig. 1 and the boost converter circuit enters into a discharging state in which, during the time interval 210, the energy previously accumulated in the inductor L<sub>BST</sub> is transferred to the output V<sub>BST</sub> therefore charging the capacitor C<sub>BST</sub> and the current I<sub>COIL</sub> in the inductor L<sub>BST</sub>

starts decreasing, as it can be seen in fig. 2A. Time intervals 200 and 210 define in this case a continuous mode event wherein a completed switching cycle has been performed by the circuit. A new continuous mode event starts with time interval 220.

[0035] Although the above example has considered that the DCDC circuit worked in a in a continuous mode wherein the current at the inductor  $L_{\rm BST}$  does not discharge to zero after each charging period, but it does discharge to a lower energy threshold, the circuit may be working in a DCM mode.

5

10

15

20

[0036] A target output boost voltage  $V_{BST}$  for the boost converter circuit of fig. 1 is set by choosing an appropriate value for the current  $I_{SH}$  using the adjustable current source 114 as follows:

$$I_{SH} = \frac{V_{BST,TARGET} - V_{REF}}{R_{SH}}$$

**[0037]** In the boost converter circuit of fig. 1, the switch  $S_L$  is closed with a frequency f and a duty cycle D that depends on the output voltage  $V_{BST}$  and on the input voltage  $V_{BAT}$  in a periodic steady state condition with constant load as follows:

$$D = \frac{V_{BST} - V_{BAT}}{V_{BST}}$$

[0038] The on-time  $T_{ON}$  of the boost converter circuit of fig. 1, i.e., the period of time 200, is related to the frequency f and the duty cycle D in the following way:

$$f = \frac{D}{T_{ON}}$$

**[0039]** This means that, for a fixed value of the on-time  $T_{ON}$ , the frequency f would depend on the duty cycle D, and therefore on both the input voltage  $V_{BAT}$  and the output voltage  $V_{BST}$ , which is generally not desirable. Therefore, the on-time  $T_{ON}$  is usually chosen to depend on the input voltage  $V_{BAT}$ , the output voltage  $V_{BST}$  and the intended switching frequency  $f_{TARGET}$  as indicated below:

$$T_{ON} = \frac{V_{BST} - V_{BAT}}{f_{TARGET} V_{BST}}$$

25 [0040] The actual switching frequency f will be equal to the intended frequency  $f_{TARGET}$ , and independent of the input voltage  $V_{BAT}$  and the output voltage  $V_{BST}$  as follows:

$$f = \frac{D}{T_{ON}} = \frac{\frac{V_{BST} - V_{BAT}}{V_{BST}}}{T_{ON}} = \frac{\frac{V_{BST} - V_{BAT}}{V_{BST}}}{\frac{V_{BST} - V_{BAT}}{f_{TARGET} V_{BST}}} = f_{TARGET}$$

**[0041]** As it can be seen in figs. 2A-B and 3A-B, in a (periodic) steady state under constant load conditions, a step  $\Delta V_{SH2}$  in a control voltage  $V_{HS}$  at a control node 150 when the switch  $S_H$  is switched on or close must be high enough to bring a voltage  $V_{SH}$  above the chosen reference voltage  $V_{REF}$ . Otherwise the comparator 116 will not toggle and the boost converter circuit stops switching, as illustrated in figs. 3A-B. This will occur for high load currents with a large difference  $\Delta V_{BST}$  between the highest and the lowest value output voltage  $V_{BST}$ . In this way, the boost converter circuit must satisfy the following stability condition:

$$\Delta V_{RST} < \Delta V_{SH2} - \Delta V_{SH1}$$

5

15

20

**[0042]**  $\Delta V_{SH1}$  represents a step in the control voltage V<sub>HS</sub> at the control node 150 when the switch S<sub>H</sub> is switched off or open. If we called I<sub>COIL,MIN</sub> to the minimum current in the inductor L<sub>BST</sub>, I<sub>COIL,MAX</sub> to the maximum current in the inductor L<sub>BST</sub>, and  $\Delta I$  to the peakpeak ripple amplitude, i.e. to the difference between the minimum current I<sub>COIL,MIN</sub> and the maximum current I<sub>COIL,MAX</sub>, then the step  $\Delta V_{SH1}$  and the step  $\Delta V_{SH2}$  can be defined as follows:

$$\Delta V_{SH1} = I_{COII,MIN}R_M$$

$$\Delta V_{SH2} = I_{COII,MAX} R_M$$

[0043] Wherein the above definitions of  $\Delta V_{SH1}$  and  $\Delta V_{SH2}$  leads to:

$$\Delta V_{SH2} - \Delta V_{SH1} = \Delta I R_M$$

**[0044]** The peak-peak ripple amplitude  $\Delta l$  can be written as a function of the on-time  $T_{ON}$ , the input voltage  $V_{BAT}$  and the inductor  $L_{BST}$  as follows:

$$\Delta I = \frac{V_{BAT}}{L_{BST}} T_{ON}$$

[0045] A load current  $I_{LOAD}$  and an output capacitance  $C_{BST}$  determine the voltage drop  $V_{BST}$  of the output voltage  $V_{BST}$  during the on-time  $T_{ON}$  in the following way:

WO 2023/103900 9 PCT/CN2022/136160

$$\Delta V_{BST} = \frac{T_{ON}I_{LOAD}}{C_{BST}}$$

[0046] In this way, the stability condition can be rewritten as:

5

10

15

20

25

30

$$\frac{R_M C_{BST} V_{BAT}}{L_{BST}} > I_{LOAD}$$

**[0047]** It can be seen and already said, in the boost converter circuit shown in fig. 1, for a given inductor  $L_{BST}$  and a given input voltage  $V_{BAT}$ , the above stability criteria depends on the values of the measurement resistance  $R_M$  and the output capacitor  $C_{BST}$ . However, high values of the measurement resistance  $R_M$  implies high energy dissipation and therefore to an inefficient boost converter circuit, and output capacitor  $C_{BST}$  with a high value are expensive.

[0048] Fig. 4 shows a feedback circuit 400 according to an embodiment of the invention. The feedback circuit of fig. 4 comprises a measurement resistance  $R_{M}$ , a feedback resistor  $R_{SH}$ , and an adjustable current source 414 configured to receive as an input a voltage  $V_{SET}$  and to provide as output a current  $I_{SH}$  such that a voltage  $V_{SH}$  is adjusted to the required value  $V_{SET}$ . The feedback circuit of fig. 4 further comprises a comparison circuit 416 comprising a first comparison input 418, a second comparison input 420 and an comparison output 422 wherein the comparison circuit 416 is configured to receive from a voltage source 480 a reference voltage  $V_{REF}$  at the first comparison input 418, the voltage  $V_{SH}$  at the second comparison input 420 and to generate a comparison result at the comparison output 422 based on comparing the first comparison input 418 and the second comparison input 420. The feedback circuit of fig. 4 may be further configured to send the comparison output 422 to a control circuit of a boost converter circuit (not shown in fig. 4) such that the control circuit generates a control signal based on the comparison circuit in order to control the switching of the boost converter circuit.

[0049] The feedback circuit of fig. 4 comprises also a gain circuit having a g<sub>M</sub> stage and comprising a voltage controlled current source 460 comprising a first gain input 462 connected at a first end 432 of the measurement resistance, a second gain input 464 connected at a second end 436 of the measurement resistance and a gain output 466 configured to provide a current IM based on voltage sensed at the first and second gain inputs. Furthermore, the feedback resistance R<sub>SH</sub> comprises a first end 438 connected to the second end 436 of the measurement resistance and a second end 442 connected to the gain output 466, to the adjustable current source 414, and to the second comparison input 420.

[0050] In fig. 4, the programmable current  $I_{SH}$  defines a target boost voltage at the output terminal 468 of the boost converter circuit. The target boost voltage is defined by:

$$V_{BST,TARGET} = V_{REF} + I_{SH} R_{SH}$$

[0051] The voltage  $V_{SH}$  at the feedback node 470 relates to the output voltage  $V_{BST}$  as follows:

$$V_{SH} = V_{BST} - I_{SH} R_{SH} + I_{M} R_{SH}$$

**[0052]** When the boost converter circuit is in a charging state wherein an inductor is storing energy, the current  $I_M$  at the gain output 466 is zero and therefore the voltage  $V_{SH}$  is close to the reference voltage  $V_{REF}$  when the system is in control.

**[0053]** When the boost converter circuit is in a discharging state wherein an inductor is releasing energy, an inductor current  $I_{COIL}$  will flow through the measurement resistance  $R_M$  and a current  $I_M$  at the gain output 466 is not equal to zero. The product  $I_M$   $R_{SH}$  acts as a feedback signal  $V_{FB}$  that can be defined as:

$$V_{SH} = V_{BST} - I_{SH} R_{SH} + g_M R_M I_{COIL} R_{SH} = V_{BST} - I_{SH} R_{SH} + V_{FB}$$

[0054] The feedback signal  $V_{FB}$  is the variation on the voltage  $V_{SH}$  generated by the  $g_M$  stage of the gain circuit 460 in combination with the feedback resistance  $R_{SH}$  such that:

$$V_{FB} = I_M R_{SH} = g_M R_M I_{COIL} R_{SH}$$

[0055] The feedback signal in the known boost converter circuit shown in fig. 1 can be expressed as:

$$V_{FB} = R_M I_{COIL}$$

5

10

15

25

30

[0056] In this way, the feedback circuit of fig. 4 has introduced a gain compared to the known boost converter circuit shown of fig. 1 equal to:

$$gain = g_M R_{SH}$$

[0057] The voltage controlled current source  $g_M$  in combination with the feedback resistance  $R_{SH}$  required to program the target output voltage creates the gain factor.

[0058] Fig. 5 shows a boost converter circuit 500 comprising the feedback circuit of fig. 4.

**[0059]** The boost converter circuit 500 of fig. 5 comprises an inductor  $L_{BST}$  connected to an input terminal receiving an input voltage  $V_{BAT}$ , which may correspond, for instance, to battery, such that an output voltage  $V_{BST}$  is provided at the output terminal 468 of the boost converter circuit based on the input voltage  $V_{BAT}$ , wherein typically  $V_{BST} \le V_{BAT}$ . The

WO 2023/103900 11 PCT/CN2022/136160

boost converter circuit of fig. 5 further comprises a switching circuit comprising switches  $S_L$  and  $S_H$ . The boost converter circuit of fig. 5 further comprises a control circuit 502 configured to receive the comparison output 422 of the comparison circuit 416 and to generate a first control signal 526 and a second control signal 528 based on the comparison output 422 of the comparison circuit 416. The first control signal 526 is configured to control the switch  $S_L$  to open or close and the second control signal 528 is configured to control the switch  $S_H$  to open or close. Furthermore the boost converter circuit of fig. 5 comprises a pulse signal circuit 530 configured to provide an on-time signal to the boost converter circuit based on a third control signal 570 generated by the control unit 502.

5

10

15

20

25

**[0060]** In the example of fig. 5, the inductor  $L_{BST}$  comprises a first end 502 and a second end 504 such that the first end 502 of the inductor  $L_{BST}$  is connected to the input voltage  $V_{BAT}$  and the second end 504 of the inductor  $L_{BST}$  is connected to the switch  $S_L$  and to the switch  $S_H$ . The switch  $S_L$  comprises a first end 506 and a second end 508. The first end 506 of the switch  $S_L$  is connected to ground and the second end 508 of the switch  $S_L$  is connected to the second end 504 of the inductor  $L_{BST}$ . The switch  $S_H$  comprises a first end 510 and a second end 512. The first end 510 of the switch  $S_H$  is connected to the second end 504 of the inductor  $L_{BST}$  and the second end 512 of the switch  $S_H$  is connected to the first end 432 of the measurement resistor  $R_M$  and to the first gain input 462 of the voltage controlled current source 460. The switches  $S_1$  and  $S_2$  may be implemented with any kind of suitable switching device, for example, a transistor, a diode, etc.

**[0061]** As illustrated in fig. 5, the boost converter circuit may comprise a capacitor  $C_{BST}$  having a first end 544 and a second end 546 wherein the first end 544 of the capacitor  $C_{BST}$  is connected to the output voltage  $V_{BST}$  of the boost circuit and the second end 546 of the capacitor  $C_{BST}$  is connected to ground.

[0062] The control unit 502 is configured to generate the first control signal 526 and/or the second control signal 528 in order to control the switching of S<sub>H</sub> and/or S<sub>L</sub> based on the comparison output 422 generated by the comparison circuit 416. The control unit 502 is also configured to generate the third control signal 570 in order to control the pulse generator circuit 530 based on the comparison output 422 generated by the comparison circuit 416.

30 [0063] Fig. 6 shows a feedback circuit 600 according to another embodiment of the invention.

WO 2023/103900 12 PCT/CN2022/136160

[0064] In fig. 6, the same reference numbers as in fig. 4 have been used to refer to similar elements. Furthermore, the feedback circuit 600 of fig. 6 comprises another feedback resistance R<sub>FB</sub>. The feedback resistance R<sub>FB</sub> comprises a first end 670 and a second end 672 wherein the first end 670 of the feedback resistance R<sub>FB</sub> is connected to the first comparison input 418 of the comparison circuit 416. The gain output 666 of the voltage controlled current source 460 is now also connected to the first comparison input 418 of the comparison circuit 416 such that a current I<sub>N</sub> is provided based on voltage sensed at the first and second gain inputs. Furthermore, the second end 672 of the feedback resistance R<sub>FB</sub> is connected to the voltage source 480.

5

10

15

20

25

30

[0065] In this way, an inverse feedback voltage is added at the first comparison input 418 using the feedback resistance  $R_{FB}$ . If the feedback resistance  $R_{FB}$  has a value identical to the value of the other feedback resistance  $R_{SH}$ , the effect is identical as in the feedback circuit of figure 4. The advantage of the feedback circuit 600 of fig. 6 is that the value  $g_M$  for the  $g_M$  stage of the gain circuit 460 and the value of the feedback resistance  $R_{FB}$  can be chosen independent of the value of the feedback resistance  $R_{SH}$ . However, the voltage source 480 providing  $V_{REF}$  must be able to sink the current  $I_N$ .

[0066] The feedback voltage in fig. 6 can be represented as  $V_{FB} = g_M R_M I_{COIL} R_{FB}$ .

**[0067]** Fig. 7 shows a boost converter circuit 700 similar to the boost converter circuit 500 of fig. 5 but comprising the feedback circuit 600 of fig. 6. The boost converter circuit 700 of fig. 7 also operates similar to the boost converter circuit 500 of fig. 5 but with a feedback voltage  $V_{FB} = g_M R_M I_{COIL} R_{FB}$ .

**[0068]** Fig. 8 shows a boost converter circuit 800 according to another embodiment of the invention. The boost converter circuit 800 further comprises a measurement switch  $S_M$  in series with the measurement resistance  $R_M$ . Furthermore, the measurement switch  $S_M$  and the measurement resistance  $R_M$  are connected in parallel with the switch  $S_H$  of the boost converter circuit 800. The switch  $S_H$  comprises an on-resistance  $R_H$  when the first switch  $S_H$  is closed, such that the measurement switch  $S_M$  and the switch  $S_H$  of the boost converter circuit 800 are configured to open and close at the same time. In this way, measurement resistance  $R_M$  is located out of the high current path avoding loss of energy at said measurement resistance  $R_M$ . The on-resistance  $R_H$  of the switch  $S_H$  which is reused. The measurement switch  $S_M$  switches simultaneously with switch  $S_H$  such that the voltage across the switch  $S_H$  and the on-resistance  $R_H$  is sensed when both switches  $S_H$  and  $S_M$  are closed.

WO 2023/103900 13 PCT/CN2022/136160

The measurement resistance  $R_M$  can be chosen much larger so that the power loss in the measurement resistance  $R_M$  can be neglected. For instance, for a boost converter circuit 800 with a switch resistance  $R_H$  in the range of 10-100 miliohms, the measurement resistance  $R_M$  can be chosen in the kiloohms range. When both switches  $S_H$  and  $S_M$  are closed the voltage across the measurement resistance  $R_M$  is equal to

$$V_{R_M} = I_{COIL}R_H$$

5

10

15

20

25

**[0069]** When both switches  $S_H$  and  $S_M$  are open,  $V_{BST}$  is sensed, so the voltage across the measurement resistance  $R_M$  is zero:

$$V_{R_M}=0$$

[0070] The boost converter circuit 800 of fig. 8 further comprises a feedback circuit as the one shown in fig. 5 wherein the first gain input 462 and the second gain input 464 of the gain circuit 460 are respectively connected to the second end 436 of the measurement resistance  $R_M$  and to the first end 432 of the measurement resistance  $R_M$ . The value of  $g_M$  can now be chosen in such a way that the output current of the  $g_M$  stage is higher than the current through the original capacitor  $C_M$  that was replaced. Therefore, the voltage step  $\Delta V$  at the feedback node  $V_{SH}$  can be scaled:

$$\Delta V = I_{COIL} R_H g_M R_{SH}$$

[0071] For  $g_M = 1/R_{SH}$ , a gain of 1 is achieved compared to the situation with the use of the capacitor. For higher values of  $g_M$ , the feedback current is higher and has the same effect as a higher measurement resistance. The feedback gain can be defined as:

$$gain = g_M R_{SH}$$

[0072] The stability requirement now includes the gain such that:

$$gain \ \frac{R_{SH}C_{BST}V_{BAT}}{L_{BST}} > I_{LOAD}$$

[0073] Figs. 9A-B show time diagrams of the waveforms of several signals of the boost converter circuit 800 of fig. 8 during operation. Specifically, figs. 9A-B show the values of the inductor current  $I_{COIL}$  and the output voltage  $V_{BST}$  of the boost converter circuit 800 of fig. 8 as a function of time for three different gains, namely for gain 1, 2 and 4. For reference, the case with gain =1 is added. This resembles the prior art situation using a

WO 2023/103900 14 PCT/CN2022/136160

capacitor that hits the maximum current limit. Clearly, the feedback gain can now be used to stabilize the boost converter circuit for operating conditions that would not be possible without it. Note that the higher feedback gain setting results also in a higher output resistance in the same way as a higher measurement resistance would do because it increases the ripple voltage amplitude on the feedback node  $V_{SH}$ .

5

10

15

20

25

30

[0074] Figs. 10 and 11 show possible implementations of the boost converter circuit 800 of fig. 8. The switches in the boost converter circuit may be implemented with transistors. An example of a complementary power stage using NMOS and PMOS transistors can be seen in figure 9A where the switch  $S_L$  is implemented with NMOS transistor  $M_L$ , switch  $S_H$  is implemented with PMOS transistor  $M_H$  and switch  $S_M$  is implemented with a transistor  $M_M$  that can be the same type of PMOS transistor as  $M_H$  so that the gate drive of  $M_H$  and  $M_M$  can be combined. Since  $M_M$  has a certain on-resistance, the voltage at the input of the  $g_M$  stage is a fraction of the drain-source voltage of  $M_H$  determined by the resistive divider formed by  $M_M$  and  $R_M$ .

[0075]  $R_M$  can also be implemented with a PMOS transistor  $M_R$  as can be seen in figure 11. When  $V_{BIAS}$  is equal to the gate voltage of  $M_H$  in on-state,  $M_M$  and  $M_R$  again form a resistive divider that determines the fraction of the voltage across  $M_H$  that is driving the gm stage. The advantage of this method is that this fraction is independent of process variation and temperature since the same type of components are used for switch and resistance. The same method can be used for an implementation where  $M_H$ ,  $M_M$  and  $M_R$  are NMOS transistors (in a full NMOS power stage).

[0076] Fig. 12 shows a flowchart of a method of operating the feedback circuit for a boost converter circuit of fig. 6. The method of fig. 6 comprises a step 1202 of receiving, at the measurement resistance R<sub>M</sub>, the current I<sub>COIL</sub>. At step 2004, the method receives, at the gain circuit 460, a sensed voltage associated to the measurement resistance and proceeds to step 1206. Step 1206 comprises providing, at the gain output 466 of the gain circuit, a gain signal generated based on the sensed voltage. Finally, the method of fig. 12 comprises a step 1208 of generating, at the comparison output 422 of the comparison circuit 416, a comparison signal, wherein the comparison signal is generated based on the gain signal, a voltage drop across the feedback resistance (R<sub>SH</sub>) and a reference signal (V<sub>REF</sub>).

[0077] The examples and embodiments described herein serve to illustrate rather than limit the invention. The person skilled in the art will be able to design alternative

# WO 2023/103900 15 PCT/CN2022/136160

embodiments without departing from the scope of the claims. Reference signs placed in parentheses in the claims shall not be interpreted to limit the scope of the claims. Items described as separate entities in the claims or the description may be implemented as a single hardware or software item combining the features of the items described.

#### **CLAIMS**

- 1. A feedback circuit for a boost converter circuit wherein the feedback circuit comprises:

- a measurement resistance ( $R_{\rm M}$ ) configured to receive a current ( $I_{\rm COIL}$ );

- a feedback resistance (R<sub>SH</sub>);

- a gain circuit (460) comprising a gain output (466) and configured to receive a sensed voltage associated to the measurement resistance, and to provide, at the gain output (466; 666), a gain signal generated based on the sensed voltage; and

- a comparison circuit (416) comprising a comparison output (422), and configured to generate a comparison signal, at the comparison output (422), wherein the comparison signal is generated based on the gain signal, a voltage drop across the feedback resistance ( $R_{SH}$ ) and a reference signal ( $V_{REF}$ ).

- 2. The feedback circuit according to claim 1, wherein the measurement resistance (R<sub>M</sub>) comprises a first end (432) and a second end (436), the gain circuit (460) comprises a first gain input (462) and a second gain input (464) and wherein the gain circuit (460) is configured to receive, at the first gain input (462), a first voltage sensed at the first end (432) of the measurement resistance, to receive, at the second gain input (464), a second voltage sensed at the second end (436) of the measurement resistance, and to provide, at the gain output (466), the sensed voltage generated based on the first sensed voltage and the second sensed voltage.

- 3. The feedback circuit according to claim 2, wherein the feedback resistance R<sub>SH</sub> comprises a first end (438) and a second end (442) and wherein the first end (438) of the feedback resistance (R<sub>SH</sub>) is coupled to the second end (436) of the measurement resistance, the second end (442) of the feedback resistance (R<sub>SH</sub>) is coupled to the comparison circuit (426) and the gain output (466) is coupled to the comparison circuit.

- 4. The feedback circuit according to any of the previous claims, wherein the comparison circuit (416) comprises a first comparison input (418), a second comparison input (420) and a comparison output (422), wherein the comparison circuit is configured to receive the reference voltage at the first input, to receive a feedback signal at the second

WO 2023/103900 17 PCT/CN2022/136160

input, and to generate the comparison signal by comparing the feedback signal and the reference signal ( $V_{REF}$ ), wherein the feedback signal is based on the gain signal and the voltage drop across the feedback resistance ( $R_{SH}$ ).

5. The feedback circuit according to claim 5, wherein the gain output (466) is coupled to the second end (442) of the feedback resistance (R<sub>SH</sub>) and to the second comparison input (420).

5

10

15

20

25

30

- 6. The feedback circuit according to any of claims 1-3, further comprising another feedback resistance ( $R_{FB}$ ) configured to receive the gain signal wherein the comparison circuit (416) comprises a first comparison input (418), a second comparison input (420) and a comparison output (422), wherein the comparison circuit (416) is configured to receive, at the first comparison input (418), the sum of the reference voltage ( $V_{REF}$ ) and a further voltage drop caused by the gain signal across the another feedback resistance ( $R_{FB}$ ), to receive the voltage drop across the feedback resistance ( $R_{SH}$ ) at the second comparison input (420) and to generate the comparison signal by comparing the sum of the reference voltage and the further voltage drop with the voltage drop across the feedback resistance ( $R_{SH}$ ).

- 7. The feedback circuit according to claim 6, wherein the another feedback resistance ( $R_{FB}$ ) comprises a first end (670) and a second end (672) wherein the first comparison input (418) is coupled to the first end (670) of the another feedback resistance ( $R_{FB}$ ) and to the gain output (666) and wherein the second end (672) of the another feedback resistance ( $R_{FB}$ ) is coupled to the reference voltage ( $V_{REF}$ ).

- 8. The feedback circuit according to any of the previous claims, wherein the gain circuit (460) comprises a voltage controlled current source.

- 9. The feedback circuit according to any of the previous claims, wherein the first end (438) of the feedback resistance ( $R_{SH}$ ) is coupled to an output terminal ( $V_{BST}$ ) of the boost converter.

- 10. The feedback circuit according to any of the previous claims, further comprising a measurement switch  $(S_M)$  wherein the measurement switch  $(S_M)$  and the measurement resistance  $(R_M)$  are coupled in series, wherein the measurement switch  $(S_M)$  and the measurement resistance  $(R_M)$  are coupled in parallel with a first switch  $(S_H)$  of the boost converter, wherein the first switch  $(S_H)$  comprises an on-resistance  $(R_H)$  when the first

WO 2023/103900 18 PCT/CN2022/136160

switch  $(S_H)$  is closed, and wherein the feedback switch  $(S_M)$  and the first switch  $(S_H)$  of the boost converter circuit are configured to open and close at the same time.

- 11. The feedback circuit according to any of the previous claims further comprising an adjustable current source (414) coupled to the second end (442) of the feedback resistance (R<sub>SH</sub>) and to the second comparison input (420) of the comparison circuit (416).

- 12. A boost converter circuit comprising:

5

10

15

20

25

30

```

the feedback circuit according to any of claims 1-11; an inductor (L_{BST}); an input terminal configured to receive an input voltage (V_{BAT}); an output terminal configured to provide an output voltage (V_{BST});

```

- a control circuit (502) configured to switch the circuit to perform cycles wherein each cycle comprises an energy discharging state in which the inductor provides energy to the output terminal and an energy charging state in which the inductor stores energy provided by the input voltage; wherein the control circuit is configured to switch the boost converter circuit based on the comparison signal.

- 13. The boost converter circuit of claim 12, wherein the inductor  $(L_{BST})$  comprises a first end (502) and a second end (504), wherein the first end (502) is coupled to the input terminal, and wherein the control circuit (502) comprises a first switch  $(S_L)$  comprising a first end (508) connected to the second end (504) of the inductor  $(L_{BST})$  and a second end (510) connected to ground and wherein the first switch  $(S_L)$  is configured to connect the inductor  $(L_{BST})$  to the ground such that the inductor  $(L_{BST})$  enters into a charging state, and to disconnect the inductor from the ground.

- 14. The boost converter circuit according to claim 13, wherein the switching circuit further comprises a second switch  $(S_H)$  having a first end (510) coupled to the second end (504) of the inductor  $(L_{BST})$ , and having a second end (512) coupled to the output terminal and wherein the second switch  $(S_H)$  is configured to couple the inductor  $(L_{BST})$  to the output terminal such that the energy storage element  $(L_{BST})$  enters into a discharging state.

- 15. A method of operating a feedback circuit for a boost converter circuit, the method comprising the steps of

- receiving, at a measurement resistance (R<sub>M</sub>), a current (I<sub>COIL</sub>);

WO 2023/103900 19 PCT/CN2022/136160

receiving, at a gain circuit (460), a sensed voltage associated to the measurement resistance;

providing, at a gain output (466; 666) of the gain circuit, a gain signal generated based on the sensed voltage; and

5

generating, at a comparison output (422) of a comparison circuit (416), a comparison signal, wherein the comparison signal is generated based on the gain signal, a voltage drop across the feedback resistance ( $R_{SH}$ ) and a reference signal ( $V_{REF}$ ).

Fig. 1

Fig. 2B

Fig. 3B

WO 2023/103900 3/10 PCT/CN2022/136160

Fig. 4

Fig. 5

Fig.6

Fig. 7

Fig. 8

Fig. 9A

Fig. 9B

Fig. 10

Fig. 12

#### INTERNATIONAL SEARCH REPORT

International application No.

#### PCT/CN2022/136160

#### A. CLASSIFICATION OF SUBJECT MATTER

H02M3/156(2006.01)i;H02M3/157(2006.01)i

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC: H02M

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

CNABS, CNTXT, VEN, ENTXTC, CNKI: boost, DC 1W DC, feedback, resistor, measure+, detect+, sampl+, gain, gm, amplifier, VCCS, COT, constant, on-time

#### C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                           | Relevant to claim No. |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| PX        | CN 114726209 A (GOODIX TECHNOLOGY (HK) CO., LTD.) 08 July 2022 (2022-07-08) description, paragraphs [0034]-[0098] and figures 4-12           | 1-15                  |

| Y         | US 2014253084 A1 (RICHTEK TECHNOLOGY CORPORATION) 11 September 2014 (2014-09-11) description, paragraphs [0021]-[0076] and figures 7-10      | 1-15                  |

| Y         | CN 205356148 U (WUXI SILICON POWER MICROELECTRONICS CO., LTD. ) 29 June 2016 (2016-06-29) description, paragraphs [0004]-[0006] and figure 1 | 1-15                  |

| A         | CN 102957321 A (FUJITSU SEMICONDUCTOR LIMITED) 06 March 2013 (2013-03-06) the whole document                                                 | 1-15                  |

| Α         | CN 105375782 A (CHENGDU MONOLITHIC POWER SYSTEMS CO., LTD.) 02 March 2016 (2016-03-02) the whole document                                    | 1-15                  |

| A         | CN 109478846 A (SILANNA ASIA PTE LTD.) 15 March 2019 (2019-03-15) the whole document                                                         | 1-15                  |

| CHINA NATIONAL INTELLECTUAL PROPERTY<br>ADMINISTRATION<br>6, Xitucheng Rd., Jimen Bridge, Haidian District, Beijing<br>100088, China                                                                                                                                        | HUANG,Shan                                                                                                                                                                                                                                       |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name and mailing address of the ISA/CN                                                                                                                                                                                                                                      | Authorized officer                                                                                                                                                                                                                               |  |  |  |

| 20 February 2023                                                                                                                                                                                                                                                            | 28 February 2023                                                                                                                                                                                                                                 |  |  |  |

| the priority date claimed  Date of the actual completion of the international search                                                                                                                                                                                        | Date of mailing of the international search report                                                                                                                                                                                               |  |  |  |

| means "P" document published prior to the international filing date but later than                                                                                                                                                                                          | "&" document member of the same patent family                                                                                                                                                                                                    |  |  |  |

| <ul> <li>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)</li> <li>"O" document referring to an oral disclosure, use, exhibition or other</li> </ul> | "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |  |  |  |

| "D" document cited by the applicant in the international application "E" earlier application or patent but published on or after the international filing date                                                                                                              | "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone                                                                     |  |  |  |

| <ul> <li>* Special categories of cited documents:</li> <li>"A" document defining the general state of the art which is not considered to be of particular relevance</li> </ul>                                                                                              | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                              |  |  |  |

| Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                  | See patent family annex.                                                                                                                                                                                                                         |  |  |  |

| uic whole decument                                                                                                                                                                                                                                                          | I                                                                                                                                                                                                                                                |  |  |  |

| i the whole document                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                  |  |  |  |

Telephone No. (+86) 010-53961235

Facsimile No. (86-10)62019451

### INTERNATIONAL SEARCH REPORT

International application No.

# PCT/CN2022/136160

| ategory* | Citation of document, with indication, where appropriate, of the relevant passages                       | Relevant to claim No |

|----------|----------------------------------------------------------------------------------------------------------|----------------------|

| A        | US 2014292300 A1 (VIRGINIA TECH INTELLECTUAL PROPERTIES) 02 October 2014 (2014-10-02) the whole document | 1-15                 |

|          | tne whole document                                                                                       |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

|          |                                                                                                          |                      |

# INTERNATIONAL SEARCH REPORT Information on patent family members

International application No.

# PCT/CN2022/136160

|    |                                  |            |                                   |      | -                 |               |                                   |

|----|----------------------------------|------------|-----------------------------------|------|-------------------|---------------|-----------------------------------|

|    | ent document<br>in search report |            | Publication date (day/month/year) | Pate | ent family member | r(s)          | Publication date (day/month/year) |

| CN | 114726209                        | Α          | 08 July 2022                      | •    | None              | '             |                                   |

| US | 2014253084                       | <b>A</b> 1 | 11 September 2014                 | TW   | 201436454         | A             | 16 September 2014                 |

|    |                                  |            |                                   | TWI  | 531156            | В             | 21 April 2016                     |

|    |                                  |            |                                   | US   | 9287774           | B2            | 15 March 2016                     |

| CN | 205356148                        | U          | 29 June 2016                      |      | None              |               |                                   |

| CN | 102957321                        | A          | 06 March 2013                     | US   | 2013049725        | A1            | 28 February 2013                  |

|    |                                  |            |                                   | US   | 9083238           | B2            | 14 July 2015                      |

|    |                                  |            |                                   | JP   | 2013046496        | Α             | 04 March 2013                     |

| CN | 105375782                        | A          | 02 March 2016                     |      | None              |               |                                   |

| CN | 109478846                        | A          | 15 March 2019                     | WO   | 2017195066        | <b>A</b> 1    | 16 November 2017                  |

|    |                                  |            |                                   | TW   | 201813268         | Α             | 01 April 2018                     |

|    |                                  |            |                                   | TWI  | 772298            | В             | 01 August 2022                    |

|    |                                  |            |                                   | US   | 2017331370        | $\mathbf{A}1$ | 16 November 2017                  |

|    |                                  |            |                                   | US   | 9882473           | B2            | 30 January 2018                   |

|    |                                  |            |                                   | KR   | 20180136472       | A             | 24 December 2018                  |

|    |                                  |            |                                   | KR   | 102390302         | B1            | 25 April 2022                     |

|    |                                  |            |                                   | US   | 2018145590        | $\mathbf{A}1$ | 24 May 2018                       |

|    |                                  |            |                                   | US   | 10630177          | В2            | 21 April 2020                     |

| US | 2014292300                       | <b>A</b> 1 | 02 October 2014                   | US   | 9601997           | B2            | 21 March 2017                     |