(19) 日本国特許庁(JP)

# (12) 特許公報(B2)

(11)特許番号

特許第3925615号 (P3925615)

(45) 発行日 平成19年6月6日(2007.6.6)

(24) 登録日 平成19年3月9日(2007.3.9)

(51) Int.C1.

$\mathbf{F} \mathbf{I}$

HO1L 25/00

(2006, 01)

HO1L 25/00

Α

請求項の数3 (全 10 頁)

(21) 出願番号 (22) 出願日

特願2001-203077 (P2001-203077) 平成13年7月4日(2001.7.4)

(65) 公開番号 (43) 公開日

審査請求日

特開2003-17649 (P2003-17649A) 平成15年1月17日 (2003.1.17) 平成15年1月10日 (2003.1.10)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

||(74)代理人 100078145

弁理士 松村 修

(72) 発明者 深澤 博之

東京都品川区北品川6丁目7番35号ソニ

一株式会社内

審査官 酒井 英夫

最終頁に続く

(54) 【発明の名称】半導体モジュール

### (57)【特許請求の範囲】

#### 【請求項1】

表裏両面の外周側縁部に他の半導体装置の外部接続用電極と当接して接続される平坦な 外部接続用電極が形成されており、表裏の配線あるいは表裏の配線と中間層の配線とを接 続するバイアホールが厚さ方向に貫通して形成されており、かつ絶縁材料から成るプリン ト配線基板の一方の表面のほぼ中央部に半導体集積回路チップが搭載されており、該半導 体集積回路チップが封止材で封止されている半導体装置を複数個組合わせて構成され、

一の前記半導体装置のプリント配線基板の表側にお<u>いて一側面に沿って</u>形成されている 外部接続用電極が他の前記半導体装置のプリント配線基板の裏側において前記一側面と対 向する側面に沿って形成されている外部接続用電極と互いに接続され、これによって前記 プリント配線基板の厚さ方向における各半導体装置の上部または下部に少なくとも前記プ リント配線基板の厚さとほぼ等しい空間が形成され、該空間に前記半導体集積回路チップ が位置していることを特徴とする半導体モジュール。

#### 【請求項2】

隣接する前記半導体装置の一方の半導体装置のプリント配線基板の表面に形成されてい る前記外部接続用電極と、他方の半導体装置のプリント配線基板の裏面に形成されている 前記外部接続用電極とが互いに接続されていることを特徴とする請求項1に記載の半導体 モジュール。

#### 【請求項3】

複数の前記半導体装置が前記外部接続用電極を介して平面的広がりを以て互いに接続さ

れていることを特徴とする請求項1に記載の半導体モジュール。

【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は、複数個の半導体装置を組込んだ半導体モジュールの構造、構成に関するものである。

[00002]

【従来の技術】

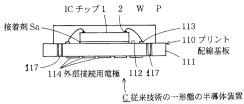

先ず、図10乃至図13を参照しながら、従来技術の半導体装置及び半導体モジュールの 構成、構造を説明する。

[0003]

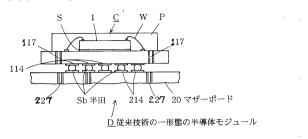

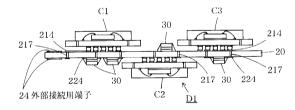

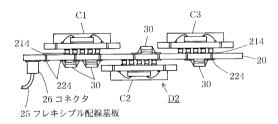

図10は従来技術の一形態の半導体装置の断面図、図11は図10に示した半導体装置をマザーボードに搭載した構造の断面図、図12は図10に示した半導体装置を複数個、マザーボードに搭載した半導体モジュールの断面図、そして図13は図10に示した半導体装置を複数個、マザーボードに搭載した他の形態の半導体モジュールの断面図である。

[0004]

先ず、図10を用いて従来技術の一形態の半導体装置の構成、構造を説明する。

[00005]

この半導体装置 C は半導体集積回路チップ(以下、単に「ICチップ」と記す)1とプリント配線基板 1 1 0 とから構成されている。ICチップ 1 の表面には、所定の配列で形成されている電極の表面に金、半田などの複数のバンプ 2 が形成されており、プリント配線基板 1 1 0 の電気絶縁基板 1 1 1 の表面には、ICチップ 1 を搭載する表面側の載置部 1 1 2 の周辺部に前記バンプ 2 に対応した複数のランド 1 1 3 が、裏面側に周辺配列或いは格子配列で複数の外部接続用電極 1 1 4 とを電気的に接続する複数のヴァイアホール 1 1 7 が形成されている。

[0006]

ICチップ1はプリント配線基板110の中央部に接着剤Saなどを用いて搭載されており、そしてそれぞれのバンプ2がそれらに対応するランド113に金などの金属細線Wを用いて電気的に接続されている。そしてこの半導体装置Cは金属細線Wとランド113との接続部分を含むICチップ1全体がエポキシ樹脂のような絶縁封止材Pで封止された構造で構成されている。

[0007]

図11乃至図13に示した半導体モジュール D はこのような構造の複数の半導体装置 C をマザーボード 2 0 に搭載したものである。マザーボード 2 0 の表面には前記外部接続用電極 1 1 4 に対応した位置に複数のランド 2 1 4 が、裏面もランド 2 2 4 (図 1 2)が、そして必要に応じて、その裏面に通じるヴァイアホール 2 2 7 などが形成されていて、図 1 1 には拡大して、このような構造のマザーボード 2 0 の表面のランド 2 1 4 に 1 個の I C チップ 1 を、例えば、半田付けなどの方法を用いて電気的に接続した状態を示したものである。符号 S b は半田を指す。

[0008]

図12及び図13に示した半導体モジュールD1及びD2は、図10に示したICチップ Cが2個、マザーボード20の表面のランド214に、<u>また1</u>個、その裏面のランド224にそれぞれ半田付け方法で搭載され、この他、抵抗、コンデンサなどのチップ部品30が複数個、搭載されて構成されているもので、図12に示した半導体モジュールD1はマザーボード20の一端にランド214、224に連結され、他の電気回路基板のソケット(不図示)に挿入、接続するための外部接続用端子24が設けられたものであり、図13に示した半導体モジュールD2はマザーボード20の一端にランド224に連結され、他の電気回路基板にフレキシブルケーブル配線基板25を用いて接続するためのコネクタ26などが設けられている。

[0009]

50

40

10

20

前記のような構造、構成の半導体装置 C 及び半導体モジュール D は、米国特許第 5 , 2 1 6 , 2 7 8 号や、A S I C & E D A 1 9 9 3 年 3 月号の 9 ~ 1 5 頁に開示されているものであり、また、M o t o r o l a 社の "OMPAC"等の形状で封入された周知のものである。

#### [0010]

【発明が解決しようとする課題】

しかし、このような半導体装置 C 及び半導体モジュール D の構造であると、多くのプリント配線基板 1 1 0 及びマザーボード 2 0 を使う必要があり、コストが嵩み、そしてコンパクトに構成できないという課題がある。

#### [0011]

本発明は、このような課題を解決しようとするものであって、コンパクトな構造で安価 に構成することができる半導体モジュールを得ることを目的とするものである。

#### [0013]

【課題を解決するための手段】

それ故、本発明の半導体装置は、表裏両面の外周部に外部接続用電極が形成されており かつ絶縁材料から成るプリント配線基板の一方の表面のほぼ中央部に半導体集積回路チップが搭載されており、該半導体集積回路チップが封止材で封止されている。

#### [0014]

本発明の半導体モジュールは、表裏両面の外周側<u>縁</u>部に他の半導体装置の外部接続用電極と当接して接続される平坦な外部接続用電極が形成されており、表裏の配線あるいは表裏の配線と中間層の配線とを接続するバイアホールが厚さ方向に貫通して形成されており、かつ絶縁材料から成るプリント配線基板の一方の表面のほぼ中央部に半導体集積回路チップが搭載されており、該半導体集積回路チップが封止材で封止されている半導体装置を複数個組合わせて構成され、

一の前記半導体装置のプリント配線基板の表側において一側面に沿って形成されている外部接続用電極が他の前記半導体装置のプリント配線基板の裏側において前記一側面と対向する側面に沿って形成されている外部接続用電極と互いに接続され、これによって前記プリント配線基板の厚さ方向における各半導体装置の上部または下部に少なくとも前記プリント配線基板の厚さとほぼ等しい空間が形成され、該空間に前記半導体集積回路チップが位置していることを特徴とする。

#### [0015]

その半導体モジュールの或るものは、隣接する前記半導体装置の一方の半導体装置のプリント配線基板の表面に形成されている前記外部接続用電極と、他方の半導体装置のプリント配線基板の裏面に形成されている前記外部接続用電極とを互いに接続して構成してもよく、また、他のものは隣接する前記半導体装置のプリント配線基板の表面或いは裏面に形成されている前記外部接続用電極同士を互いに接続して構成してもよい。

# [0016]

更に、それらの半導体モジュールは隣接する前記半導体装置の前記両外部接続用電極が中継基板を介して互いに接続された構造で構成してもよい。

#### [0017]

更にまた、それらの半導体モジュールは、複数の前記半導体装置を前記外部接続用電極を 介して平面的広がりを以て互いに接続した構造で構成してもよい。

#### [0018]

従って、本発明の半導体装置は中央部にICチップを搭載したプリント配線基板の周辺部に外部接続用電極を形成した単純な構造で2次元的にも3次元的にも広がりを持った構造で半導体モジュールを構成できる。

#### [0019]

また、本発明の半導体モジュールは、前記半導体装置のプリント配線基板同士を直接、或 いはチップ部品や中継基板を介して接続する構造を採っているため、大きな面積を占めて いたマザーボードを使う必要がなくなり、コンパクトに、しかも安価に構成することがで 10

20

30

40

きる。

### [0020]

#### 【発明の実施の形態】

以下、図1乃至図9を用いて、本発明の実施形態の半導体装置及び半導体モジュールの構成、構造を説明する。

### [0021]

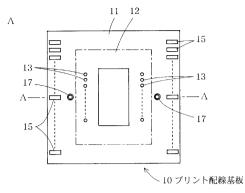

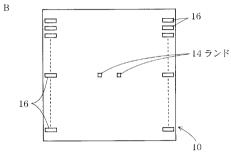

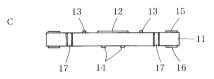

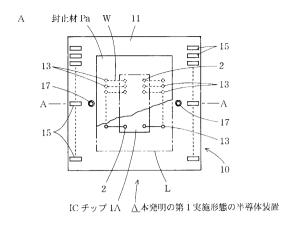

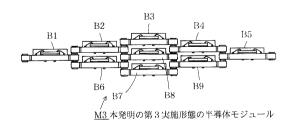

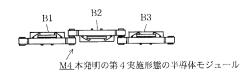

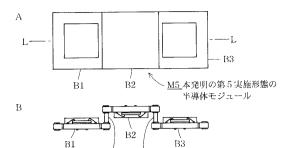

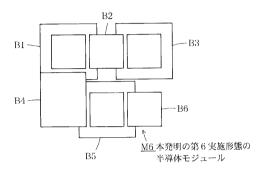

図1は本発明の半導体装置に用いて好適な一実施形態のプリント配線基板を示していて、同図Aはその表面側の平面図、同図Bはその裏面側の平面図、同図Cは同図AのA・A線上における断面図、図2は本発明の第1実施形態の半導体装置を示していて、同図Aはその平面図、同図Bは同図AのA・A線上における断面図、図3は第1半導体装置の断面図、図4は図2に示した半導体装置を複数個用いて構成されている本発明の第1実施形態の半導体モジュールの断面図、図5は同じく第2実施形態の半導体<u>モジュール</u>の断面図、図6は同じく本発明の第3実施形態の半導体<u>モジュール</u>の断面図、図7は図3に示した半導体装置を複数個用いて構成されている本発明の第4実施形態の半導体モジュールの断面図、図8は同じく本発明の第5実施形態の半導体<u>モジュール</u>を示していて、同図Aはその平面図、同図Bは同図AのL・L線上における断面図、そして図9は本発明の第6実施形態の半導体モジュールの平面図である。

#### [0022]

なお、従来技術の半導体装置の構成部分と同一の構成部分には同一の符号を付して説明する。

#### [0023]

先ず、図1を用いて、本発明の半導体装置に用いて好適なプリント配線基板の構造を説明 する。

#### [0024]

符号10は全体としてプリント配線基板を指す。このプリント配線基板10は単層または多層の配線基板であって、ガラスエポキシ樹脂などの電気絶縁材基板11の表面のほぼ中央部にICチップを載置する載置部12と、この載置部12の長辺の両周辺部に、搭載しようとするICチップの複数の電極に対応して配列されているランド13と、絶縁基板11の両側縁に前記ランド13に対応して配列されている外部接続用裏面電極15がそれぞれ銅などの導電性部材で形成されている。また、プリント配線基板10の裏面側には後記するチップ部品を接続するためのランド14と絶縁基板11の両側縁に複数の外部接続用裏面電極16がそれぞれ銅などの導電性部材で形成されている。また、必要に応じて少なくとも1以上のヴァイアホール17が形成されており、プリント配線基板10の表裏の配線、或いは表裏の配線と中間層の配線とを接続する。一点鎖線Lは封止材Paを封止する範囲を示したものである。

#### [0025]

載置部12は搭載しようとするICチップを接地する必要がある場合に導電性部材で形成する必要があるが、その必要性が無い場合には敢えて導電性部材で形成する必要は無い。ICチップを載置する部分が判ればよい。また、裏面のランド14も、チップ部品を接続する必要が無い場合には、省略される。

### [0026]

また、外部接続用電極15、16のそれぞれの上下の位置は必ずしも一致して形成する必要は無く、接続しようとする相手側のプリント配線基板の機能などに対応した数、配列などを考慮して形成されるものである。

#### [0027]

更にまた、図示のプリント配線基板10は、搭載しようとするICチップに形成されている複数の電極がデュアルインラインで形成されているものに用いる基板として描かれているものであって、複数の電極がICチップの4辺に沿って形成されている場合には、ランド13は載置部12の4辺の周りに沿ってに形成してもよく、外部接続用電極15、16もプリント配線基板10の4辺の周りに沿って形成するようにしても、2辺のみ或いは3

20

30

辺のみの側縁に沿って形成するようにしてもよい。

#### [0028]

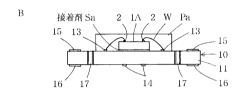

次に、図2を用いて、本発明の第1実施例の半導体装置の構造を説明する。

#### [0029]

図 2 において、符号 A は本発明の第 1 の実施例の半導体装置を指す。この半導体装置 A は、従来技術の半導体装置 C と同様に、ICチップ 1 A (ICチップ 1 と同一である)とプリント配線基板 1 0 とから構成されている。ICチップ 1 の表面には、所定の配列で形成されている電極の表面に金、半田などの複数のバンプ 2 が形成されている。

#### [0030]

このICチップ1Aは、図1に示したプリント配線基板10の載置部12に、例えば、導電性接着剤Saを介して接着、固定する。そしてそれぞれのバンプ2がそれらに対応するランド13に金などの金属細線Wを用いて電気的に接続されている。そしてこの半導体装置Aも金属細線Wとランド13との接続部分を含むICチップ1全体がエポキシ樹脂のような絶縁封止材Paで封止された構造で構成されている。

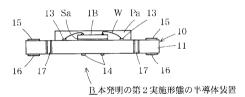

#### [0031]

図3に示した本発明の第2実施形態の半導体装置 B は、前記の構造のプリント配線基板10を用い、そのプリント配線基板10の中央部に I C チップ1 A の厚みより薄い厚みの I C チップ1 B が搭載されており、そしてバンプ2とランド13との接続部分を含むその I C チップ1 B を前記プリント配線基板10の厚みより薄い厚みの封止材 P b で封止された構造のものである。

#### [0032]

このような外部接続用電極 1 5 、 1 6 を備えた半導体装置 A 及び半導体装置 B であると、従来技術の半導体装置 C のように裏面に外部接続用電極 1 1 4 が形成されているのではなく、プリント配線基板 1 0 の外周部分に外部接続用電極 1 5 、 1 6 が形成されているので、これら外部接続用電極 1 5 、 1 6 の接続を組み合わせることで半導体装置 A 及び又は半導体装置 B 同士を 2 次元的に、或いは 3 次元的に電気的に接続して、所望の構成、構造の半導体モジュールを得ることが可能となる。

#### [0033]

半導体装置 A に寸法は、一例であるが、プリント配線基板 1 0 は、その外部接続用電極 1 5、16の厚みも含めて厚みが 0.4 mm程度、封止材 P a の厚みが 0.6 mm程度であり、半導体装置 B はプリント配線基板 1 0 が半導体装置 A の場合と同一であり、封止材 P a の厚みが 0.3 mm程度である。

#### [0034]

次に、図4乃至図9を用いて、本発明の各実施形態の半導体モジュールについて説明する

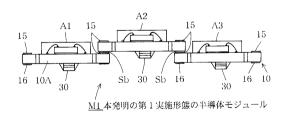

#### [0035]

先ず、図4を用いて、本発明の第1実施形態の半導体モジュールの構成、構造を説明する。この半導体モジュールM1は、3個の半導体装置A1、A2、A3(何れも半導体装置Aであって、説明の便宜上A1、A2、A3と符号を付して区別した)から構成されていて、半田Sbを介して半導体装置A1、A3の外部接続用電極15と半導体装置A2の外部接続用電極16とが電気的に接続された構造のものである。

#### [0036]

この半導体モジュール M 1 の製作方法は、先ず、これら半導体装置 A 1 、 A 3 の外部接続用電極 1 5 に半田ペースト(不図示)を印刷等の従来技術で塗布しておき、これらの半導体装置 A 1 、 A 3 を、治具(不図示)の上に載置する等の方法で、予め、定められている位置に載置し、それら半導体装置 A 1 、 A 3 の外部接続用電極 1 5 の上に、残りの半導体装置 A 2 の裏面の外部接続用電極 1 6 を位置決めして載置する。その後、リフロー等の方法を用いて前記半田ペーストを溶融し、冷却して接続することにより前記半導体モジュール M 1 が得られる。半導体装置 A 1 、 A 2 、 A 3 の裏面のランド 1 4 には必要に応じてチップ部品 3 0 を接続する。

20

40

30

#### [0037]

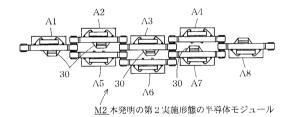

次に、図5を用いて、本発明の第2実施形態の半導体モジュールM2の構成、構造を説明 する。この半導体モジュール M 2 は 3 個のチップ部品 3 0 を含む 8 個の半導体装置 A 1 ~ A 8 から構成されている。半導体装置 A 1 ~ A 4 及び半導体装置 A 5 ~ A 8 は、半導体モ ジュールM1の接続構造と同様に、表面の外部接続用電極15と隣接する半導体装置Aの 裏面の外部接続用電極16とが接続されており、半導体装置A2とA5とは半導体装置A 1とA3との外部接続用電極15、16を介して裏面の外部接続用電極16同士が接続さ れており、同様に半導体装置A3とA6とは半導体装置A5とA7との外部接続用電極1 5、16を介して裏面の外部接続用電極16同士が、半導体装置A4とA7とは半導体装 置A3とA8との外部接続用電極15、16を介して裏面の外部接続用電極16同士が接 続された構造で構成された半導体モジュールである。半導体装置A2~A4の裏面にはチ ップ部品30が搭載されている。

#### [0038]

図6に示した第3実施形態の半導体モジュールM3は、第2実施形態の半導体装置Bを8 個用いて構成されたものであって、全ての半導体装置B1~B8が隣接する半導体装置B の表面の外部接続用電極15と裏面の外部接続用電極16とで接続されている。

#### [0039]

この半導体モジュールM3は、半導体装置B3、B8、B7が三重に重なった部分があり 、このように半導体装置を多段に積層する構造の半導体モジュールを必要とする場合には 、厚みの薄い半導体装置Bを用いることが望ましい。

#### [0040]

図7は本発明の第4実施形態の半導体モジュールM4を示していて、この半導体モジュー ルM4は3個の半導体装置Bから構成されている例である。この半導体モジュールM4は 半導体モジュールの全体厚さが薄いものが望まれる場合に好適な構造のものである。即ち 、治具などの載置台(不図示)に半導体装置B1及びB3を所定の間隔を開けて載置し、 後から搭載する半導体装置B2を表裏反転させて、前記と同様な半田付け方法により接続 した構造のものである。このような構造で構成すると、全体としてほぼ均一な厚みの半導 体モジュールが得られる。

### [0041]

図8は本発明の第5実施形態の半導体モジュールM5を示していて、この半導体モジュー ルM5は3個の半導体装置B1~B3の内、所定の間隔を開けて配列されている半導体装 置 B 1 と B 3 との表面の外部接続用電極 1 5 に半導体装置 B 2 の裏面の外部接続用電極 1 6 を、一方はチップ部品30を介して、他方は中継基板40を介して接続した構造の半導 体モジュールである。

# [0042]

この実施形態の半導体モジュールM5は、同図Aから明らかなように、3個の半導体装置 B1~B3を同一方向の側面のみを接続して構成された構造のものであるが、図9に示し た本発明の第6実施形態の半導体モジュールM6のように、複数個の半導体装置B1、B 2、B3・・・を平面的な広がりをもった接続構造、即ち、2次元的な接続構造で構成す ることもできる。そして2次元的な接続構造に、図5及び図6に示した厚み方向にも接続 する構造を取り入れば、半導体モジュールを3次元に広がる接続構造でも構成することも できる。

#### [0043]

### 【発明の効果】

以上説明したように、本発明の半導体装置によれば、隣接する半導体装置のプリント配 線基板の表裏両面の外周部に外部接続用電極が形成されるとともに、半導体集積回路チッ プが封止材で封止されているので、隣接する半導体装置のそれら外部接続用電極を互いに 接続することにより各種構造の本発明の半導体モジュールを簡単に構成することができる

[0044]

50

20

30

20

30

また、本発明の半導体モジュールは、半導体装置のプリント配線基板同士を直接接続する構造を採っているので、大きな面積を占めていたマザーボードを使う必要がなくなり、従来技術の半導体モジュールよりも遙かに廉価なコストで製作することができ、しかも2次元にも3次元にも広がりをもって、そして必要に応じて厚みの薄い構造で半導体モジュールを構成することができるなど、数々の優れた効果が得られる。

#### 【図面の簡単な説明】

- 【図1】 本発明の半導体装置に用いて好適な一実施形態のプリント配線基板を示していて、同図Aはその表面側の平面図、同図Bはその裏面側の平面図、同図Cは同図AのA-A線上における断面図である。

- 【図2】 本発明の第1実施形態の半導体装置を示していて、同図Aはその平面図、同図Bは同図AのA-A線上における断面図である。

- 【図3】 第1半導体装置の断面図である。

- 【図4】 図2に示した半導体装置を複数個用いて構成されている本発明の第1実施形態の半導体モジュールの断面図である。

- 【図5】 第2実施形態の半導体モジュールの断面図である。

- 【図6】 本発明の第3実施形態の半導体モジュールの断面図である。

- 【図7】 図3に示した半導体装置を複数個用いて構成されている本発明の第4実施形態の半導体モジュールの断面図Fらる。

- 【図8】 本発明の第5実施形態の半導体モジュールを示していて、同図Aはその平面図、同図Bは同図AのL-L線上における断面図である。

- 【図9】 本発明の第6実施形態の半導体モジュールの平面図である。

- 【図10】 従来技術の一形態の半導体装置の断面図である。

- 【図11】 図10に示した半導体装置をマザーボードに搭載した構造の断面図である。

- 【図12】 図10に示した半導体装置を複数個、マザーボードに搭載した半導体モジュールの断面図である。

- 【図13】 図10に示した半導体装置を複数個、マザーボードに搭載した他の形態の半 導体モジュールの断面図である。

#### 【符号の説明】

1 A , 1 B … 半導体集積回路チップ(ICチップ)、2 … バンプ、1 0 A … 本発明の半導体装置に用いて好適なプリント配線基板、1 0 … 本発明の半導体装置に用いて好適なプリント配線基板、1 1 … 絶縁基板、1 2 … 載置部、1 3 , 1 4 … ランド、1 5 , 1 6 … 外部接続用電極、1 7 … ヴァイアホール、3 0 … チップ部品、4 0 … 中継基板、A , A 1 ~ A 8 … 本発明の第1実施形態の半導体装置、B , B 1 ~ B 9 … 本発明の第2実施形態の半導体装置、M 1 … 本発明の第1実施形態の半導体モジュール、M 2 … 本発明の第2実施形態の半導体モジュール、M 4 … 本発明の第4実施形態の半導体モジュール、 M 5 … 本発明の第4実施形態の半導体モジュール、 M 5 … 本発明の第6実施形態の半導体モジュール、 P a … 封止材、S a …接着剤、W … 金属ワイヤ

# 【図1】

# 【図2】

# 【図3】

# 【図4】

# 【図5】

# 【図6】

# 【図7】

# 【図8】

40 中継基板

## 【図9】

チップ部品 30

【図10】

# 【図11】

# 【図12】

# 【図13】

# フロントページの続き

(56)参考文献 特開2001-110979(JP,A)

特開平07-183426(JP,A)

実開昭64-018752(JP,U)

特開平04-212440(JP,A)

実開平01-143168(JP,U)

(58)調査した分野(Int.CI., DB名)

H01L 23/12,25/00-25/18,

H05K 1/14