## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2010-21234 (P2010-21234A)

(43) 公開日 平成22年1月28日(2010.1.28)

| (51) Int.Cl. |      |            | F 1  |      |     | テーマコード (参考) |

|--------------|------|------------|------|------|-----|-------------|

| HO1G         | 7/06 | (2006.01)  | HO1G | 7/06 |     | 5 E O O 1   |

| HO1G         | 4/33 | (2006.01)  | HO1G | 4/06 | 102 | 5E082       |

| HO1G         | 4/12 | (2006, 01) | HO1G | 4/12 | 394 |             |

#### 審査請求 未請求 請求項の数 3 〇1 (全 16 百)

|                       |                                                      | 田旦明小     | 不明小 明小項の数 3 〇七 (主 10 貝)                                       |  |  |

|-----------------------|------------------------------------------------------|----------|---------------------------------------------------------------|--|--|

| (21) 出願番号<br>(22) 出願日 | 特願2008-178793 (P2008-178793)<br>平成20年7月9日 (2008.7.9) | (71) 出願人 | 000006231<br>株式会社村田製作所<br>京都府長岡京市東神足1丁目1〇番1号                  |  |  |

|                       |                                                      | (74)代理人  | 100114502<br>弁理士 山本 俊則                                        |  |  |

|                       |                                                      | (72) 発明者 | 中磯 俊幸 京都府長岡京市東神足1丁目10番1号 株式会社は日制作売中                           |  |  |

|                       |                                                      | (72) 発明者 | 株式会社村田製作所内<br>竹島 裕<br>京都府長岡京市東神足1丁目1〇番1号                      |  |  |

|                       |                                                      | Fターム (参  | 株式会社村田製作所内<br>考) 5E001 AB06<br>5E082 AA20 BC40 EE05 FF05 FG03 |  |  |

|                       |                                                      |          | 2232 11125 2215 2230 1100 1000                                |  |  |

## (54) 【発明の名称】 コンデンサ

## (57)【要約】

【課題】等価直列抵抗ESR(Equivalent Series Resistance)を低減すること ができるコンデンサを提供する。

【解決手段】コンデンサは、(a)一対の電極層15,17と、(b)一対の電極層15,17の間に配置された誘電体層16と、(c)一対の電極層15,17にそれぞれ接続された一対の引き出し電極30s,32;30t,34とを備える。一方の電極層15は、電極層15,17及び誘電体層16が積層された方向から透視したとき、(i)一対の電極層15,17が誘電体層16を介して対向する容量発生部に重なる中心部15pと、(ii)中心部から外側に延在し、かつ中心部を全周に渡って連続的に取り囲む外周部15qとを有する。一方の引き出し電極30sは、一方の電極層15の外周部15sに1箇所で接続され、当該接続面は中心部15pを全周に渡って連続的に取り囲む。

## 【選択図】図1

#### 【特許請求の範囲】

## 【請求項1】

一対の電極層と、

該一対の電極層の間に配置された誘電体層と、

前記電極層にそれぞれ接続された一対の引き出し電極と、

を備えたコンデンサであって、

一方の前記電極層は、前記電極層及び前記誘電体層の積層方向から透視したとき、前記一対の電極層が前記誘電体層を介して対向する容量発生部に重なる中心部と、該中心部から外側に延在し、かつ前記中心部を全周に渡って連続的に取り囲む外周部とを有し、

一方の前記引き出し電極は、前記一方の電極層の前記外周部に1箇所で接続され、当該接続面は前記中心部を全周に渡って連続的に取り囲むことを特徴とする、コンデンサ。

## 【請求項2】

一対の電極層と、

該一対の電極層の間に配置された誘電体層と、

前記電極層にそれぞれ接続された一対の引き出し電極と、

を備えたコンデンサであって、

一方の前記電極層は、前記電極層及び前記誘電体層の積層方向から透視したとき、前記一対の電極層が前記誘電体層を介して対向する容量発生部に重なる中心部と、該中心部から外側に延在し、かつ前記中心部を全周に渡って連続的に取り囲む外周部とを有し、

一方の前記引き出し電極は、前記一方の電極層の前記外周部に 2 か所以上で接続され、 当該接続面は前記中心部の周囲に等間隔に配置されていることを特徴とする、コンデンサ

## 【請求項3】

他方の前記電極層と前記容量発生部とが、複数に分割され、

前記積層方向から透視したとき、前記容量発生部と前記接続面とが、格子状又は千鳥状に交互に配置されていることを特徴とする、請求項2に記載のコンデンサ。

【発明の詳細な説明】

## 【技術分野】

[0001]

本発明はコンデンサに関し、特に可変コンデンサに好適な、コンデンサの構造に関する

## 【背景技術】

[0002]

従来、一対の電極層の間に誘電体層が配置された構造のコンデンサが種々提案されている。

## [0003]

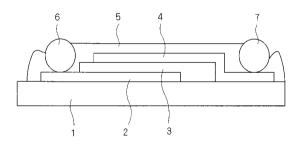

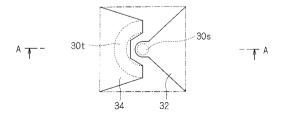

例えば図20の断面図に示す可変コンデンサは、支持基板1上に、下部電極層2、誘電体層3、上部電極層4及び保護層5が積層され、下部電極層2及び上部電極層4の間に誘電体層3が配置された平行平板型の可変コンデンサである。誘電体層3には、(Ba,Sr)Ti〇₃などの容量変化率の高い強誘電体系薄膜材料が用いられる。下部電極層2及び上部電極層4には、誘電体層3の誘電体薄膜形成時の高温酸化雰囲気に対する耐性はあるが比抵抗の高いPtなどが用いられる。下部電極層2及び上部電極層4は、それぞれ、保護層5に形成された単一のスルーホール(貫通孔)に配置された半田ボールや金属バンプなどの外部端子6,7を介して、外部回路に接続される(例えば、特許文献1参照)。

【特許文献1】特開2002-329641号公報

#### 【発明の開示】

【発明が解決しようとする課題】

## [0004]

理想的なコンデンサならば、周波数が高くなるとインピーダンスは低くなる。しかし、 実際のコンデンサでは、ある周波数までは、周波数が高くなるにつれてインピーダンスが 10

20

30

40

次第に低くなるものの、ある周波数を越えると、周波数が高くなるにつれてインピーダンスが次第に高くなる。インピーダンスの最下点は、等価直列抵抗(Equivalent Series Resistance、以下「ESR」と言う。)と呼ばれている。

[0005]

例えば、高周波用可変コンデンサに、図20のように下部電極層2から外部端子6で引き出す構造を採用すると、ESRが大きくなり、ESRの影響により高周波帯での損失が増大する問題点がある。

[0006]

すなわち、高周波用可変コンデンサは、容量密度が高ければ高いほどよい一般の薄膜コンデンサとは異なり、数 p F から十数 p F の容量値が 1 0 V 以下の制御電圧で数十%の可変率を有することが要求される。必要な容量発生部の面積は、 3 0 μ m x 3 0 μ m より小さく、数十から数百 μ m <sup>2</sup> であり、高い加工精度が要求される。

[00007]

下部電極層を外部接続端子と接続するための引き出し電極用スルーホールは、従来は、 後述する比較例の図17~図19、特に図17(c)及び図19(b)において符号22 qで示すように、容量発生部よりも下部電極用外部接続端子に近い方にのみ形成されている。

[0008]

可変コンデンサの高周波での損失は、誘電ロス以外に、導電ロスにも強く影響を受ける。特に、低容量素子になると容量発生部が小さくなる影響で、引き出し電極と上下の電極層との接続部の面積が狭くなるなどして配線抵抗が増大するため、特性劣化(高周波での損失増大)が起こる。

[0009]

上下の電極層、特に下部電極材料は誘電体薄膜形成時の高温酸化雰囲気での耐性がある PtやPdなどを用いるが、これらは比抵抗の高い材料である。

[0010]

以上の観点から、導電ロスが少なくなるような素子構造が求められる。

[0011]

本発明は、かかる実情に鑑み、ESRを低減することができるコンデンサを提供しようとするものである。

【課題を解決するための手段】

[0012]

本発明は、上記課題を解決するために、以下のように構成したコンデンサを提供する。

[0013]

コンデンサは、(a)一対の電極層と、(b)該一対の電極層の間に配置された誘電体層と、(c)前記電極層にそれぞれ接続された一対の引き出し電極とを備える。一方の前記電極層は、前記電極層及び前記誘電体層の積層方向から透視したとき、(i)前記一対の電極層が前記誘電体層を介して対向する容量発生部に重なる中心部と、(ii)該中心部から外側に延在し、かつ前記中心部を全周に渡って連続的に取り囲む外周部とを有する。一方の前記引き出し電極は、前記一方の電極層の前記外周部に1箇所で接続され、当該接続面は前記中心部を全周に渡って連続的に取り囲む。

[0014]

上記構成によれば、コンデンサの一対の電極層の間に高周波電圧が印加されると、一方の電極層において、電流は、外周部に形成された一方の引き出し電極との接続面と中心部との間を、放射状にかつ均等に流れる。一方の電極層において、中心部と一方の引き出し電極との接続面との間の電流パスが増え、導電ロスが小さくなるため、ESRを低減し、高周波帯での損失が低減することができる。

[0015]

また、本発明は、上記課題を解決するために、以下のように構成した他のコンデンサを 提供する。 10

20

30

40

#### [0016]

コンデンサは、(a)一対の電極層と、(b)該一対の電極層の間に配置された誘電体層と、(c)前記電極層にそれぞれ接続された一対の引き出し電極とを備える。一方の前記電極層は、前記電極層及び前記誘電体層の積層方向から透視したとき、(i)前記一対の電極層が前記誘電体層を介して対向する容量発生部に重なる中心部と、(ii)該中心部から外側に延在し、かつ前記中心部を全周に渡って連続的に取り囲む外周部とを有する。一方の前記引き出し電極は、前記一方の電極層の前記外周部に2か所以上で接続され、当該接続面は前記中心部の周囲に等間隔に配置されている。

## [0017]

上記構成によれば、コンデンサの一対の電極層の間に高周波電圧が印加されると、一方の電極層において、電流は、外周部に形成された一方の引き出し電極との接続面と中心部との間を、略放射状にかつ略均等に流れる。一方の電極層において、中心部と一方の引き出し電極との接続面との間の電流パスが増え、導電ロスが小さくなるため、ESRを低減し、高周波帯での損失が低減することができる。

### [0018]

好ましくは、他方の前記電極層と前記容量発生部とが、複数に分割される。前記積層方向から透視したとき、前記容量発生部と前記接続面とが、格子状又は千鳥状に交互に配置されている。

## [0019]

この場合、他方の電極層と容量発生部とを複数に分割することにより、他方の電極層と容量発生部とが 1 だけの場合よりも、電流パスが増え、導電ロスが小さくなるため、さらに ESRが低減でき、高周波帯での損失が一層低減できる。

## 【発明の効果】

[0020]

本発明のコンデンサは、ESRを低減することができる。

【発明を実施するための最良の形態】

#### [0021]

以下、本発明の実施の形態について、図1~図19を参照しながら説明する。

## [0022]

#### [0023]

まず、実施例1の可変コンデンサ10の概要を説明する。

## [0024]

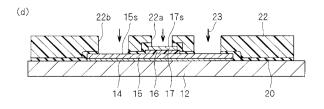

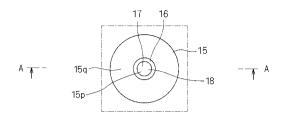

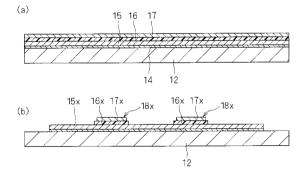

図2(h)の断面図に示すように、実施例1の可変コンデンサ10は、基板12上に、上部電極層17と下部電極層15との間に誘電体層16が挟まれたキャパシタ構造を有し、上部電極層17と下部電極層15とは、それぞれ、引き出し電極30a,32;30b,34を介して、外部電極32s,34sに電気的に接続されている。

#### [0025]

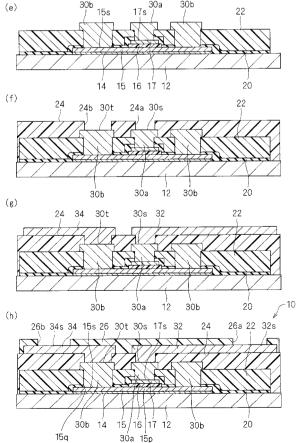

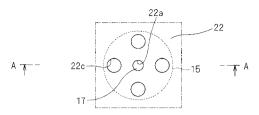

積層方向から透視すると、図3の平面図に示すように、下部電極層15は、上部電極層17と下部電極層15とが誘電体層16を介して対向する容量発生部18に重なる中心部15pと、中心部15pから外側に延在し、中心部15pを全周に渡って連続的に取り囲む外周部15qとを有している。積層方向から透視すると、下部電極層15の中心部15pは上部電極層17に重なる部分であり、下部電極層15の外周部15qは、円形の下部電極層15のうち円形の中心部15p以外のドーナツ状の部分である。

#### [0026]

そして、図2(h)の断面図と図4の要部平面図とに示すように、下部電極層15の外周部15qに、下部電極層15と外部電極34sとの間を接続する引き出し電極30bが1箇所で接続され、引き出し電極30bとの接続面15sは、中心部15pの外側を全周

10

20

30

40

に渡って連続的に取り囲むように延在している。

#### [0027]

これにより、コンデンサの一対の電極層15,17の間に高周波電圧が印加されると、下部電極層15において、電流は、外周部15qに形成された引き出し電極30bとの接続面15sと中心部15pとの間を、放射状にかつ均等に流れる。

## [0028]

また、変形例1として、図4の代わりに、図5の要部平面図に示すように、積層方向から透視したときに、下部電極層15の外周部15qに、下部電極層15と外部電極34sとの間を接続する引き出し電極が4か所以上(図5では4か所)に分割して接続され、接続面15kは、中心部15pを中心に、中心部15pのまわりに等間隔に(図5では90度ごとに)配置されている。

[0029]

この変形例1において、電極層15,17の間に高周波電圧が印加されると、下部電極層15において、電流は、外周部15qに形成された引き出し電極との接続面と中心部15pとの間を、略放射状にかつ略均等に流れる。

#### [0030]

このように、下部電極層 1 5 の外周部 1 5 q に、引き出し電極とを接続する接続面 1 5 s , 1 5 k を、中心部 1 5 p の周りに、ドーナツ状に配置し、あるいは 4 以上の等間隔に分割して配置することにより、キャパシタ構造と外部電極との間の相対的に比抵抗の高い下部電極層 1 5 における電流パスを増加させて電流を分散させ、導電ロスを小さくすることで、 E S R を低減でき、高周波帯での損失を低減できる。

【0031】

次に、実施例1の可変コンデンサ10の製造工程及び作製例について、説明する。

[ 0 0 3 2 ]

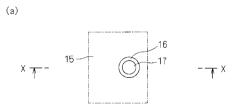

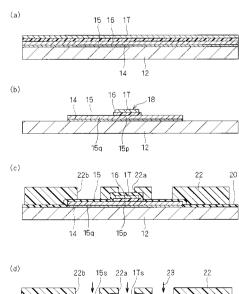

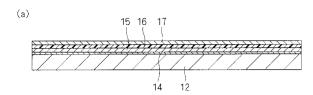

(1)まず、図1(a)に示すように、基板12上に、密着層14、下部電極層15、 誘電体層16、上部電極層17を積層する。

[0033]

作製例では、表面にSiO₂膜が形成されたSiO₂/Si基板12上に、化学溶液堆積(CSD)法により、密着層14として、Ba<sub>0.7</sub>Sr<sub>0.3</sub>TiO₃(BST)薄膜を形成した。具体的には、化学量論組成のBST原料溶液を基板12のSiO₂膜上に塗布し、乾燥させ、650、30minの熱処理により結晶化させて、BST薄膜を得た。次いで、密着層14のBST薄膜上にスパッタリング法により膜厚300nmのPt膜を成膜し、下部電極層15とした。次いで、下部電極層15上に、誘電体層16として、密着層14のBST薄膜と同様にCSD法によりBST薄膜を形成した。すなわち、原料溶液を下部電極層15のPt膜上に塗布し、300~400 で乾燥させ、650 、30minの熱処理により結晶化させてBST薄膜を得た。次いで、誘電体層16のBST薄膜上に、スパッタリング法で膜厚300nmのPt膜を成膜し、上部電極層17とした。

[0034]

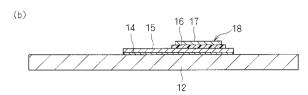

(2)次に、図1(b)に示すように、各層14~17をパターニングして、容量発生部18を形成する。このとき、図3の要部平面図に示すように、積層方向から見ると、上部電極層17よりも大きく誘電体層16が形成され、誘電体層16よりも大きく下部電極層15が形成されている。容量発生部18は、上部電極層17と下部電極層15とが誘電体層16を介して対向する部分、すなわち、図3において上部電極層17に重なる部分である。下部電極層15は、積層方向から見ると、容量発生部18、すなわち上部電極層17に重なる中心部15pと、中心部15pから外側に延在し、かつ中心部15pを全周に渡って連続的に取り囲む外周部15qとを有している。

[0035]

作製例では、レジストマスクを形成した後、イオンミリング法により上部電極層17と その下の誘電体層16、下部電極層15を順次ドライエッチングした。これを、キャパシ 10

20

30

40

(6)

タ構造とする。次いで、上記のキャパシタ構造を800 、30minの条件で熱処理した。

## [0036]

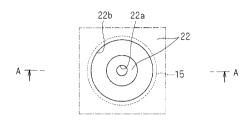

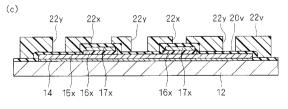

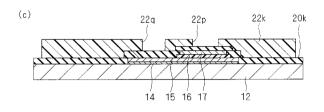

(3)次に、図1(c)に示すように、絶縁保護膜20と、1層目の有機保護膜22とを形成する。1層目の有機保護膜22には、上部電極層17の上に貫通孔22aを形成し、下部電極層15の外周部15qの上に貫通孔22bを形成する。

#### [0037]

図4の要部平面図に示すように、積層方向から見たとき、貫通孔22bは、貫通孔22 aの周囲を全周に渡って連続的に取り囲み、貫通孔22aを中心に点対称(回転対称)となるように、ドーナツ状に形成する。

[0038]

変形例1では、図5の要部平面図に示すように、下部電極層15の外周部15qの上に形成する貫通孔22cを、貫通孔22aを中心に4箇所又はそれ以上に分割し、貫通孔22aを中心に等間隔に形成する。

### [0039]

作製例では、キャパシタ構造の上面及び側面を覆うように、スパッタリング法により膜厚300nmの窒化シリコン( $SiN_X$ )膜を成膜し、無機の絶縁保護膜20とした。次いで、絶縁保護膜20の $SiN_X$ 膜上に、感光性樹脂材料をスピンコートで塗布し、乾燥後、露光、現像工程を経てキュアを行い、貫通孔22a,22bを有する第1の有機保護膜22として、膜厚2 $\mu$ mのポリイミド膜を得た。

[0040]

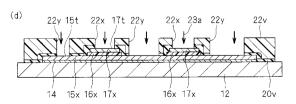

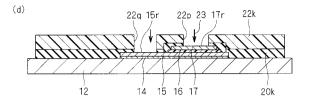

(4)次に、図1(d)に示すように、1層目の有機保護膜22の貫通孔22a,22 bの底面に露出している部分の絶縁保護膜20を除去し、その下の部分の上部電極層17 及び下部電極層15の一部17s,15sを露出させる。

#### [0041]

作製例では、1層目の有機保護膜22であるポリイミド膜をマスクとして、CHF  $_3$  ガスを用いて、矢印23で示すように貫通孔22a,22bを介して絶縁保護膜20のSiN  $_X$  膜をドライエッチングし、上部電極層17及び下部電極層15のPt膜の一部17s,15sを露出させる。

[ 0 0 4 2 ]

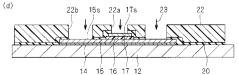

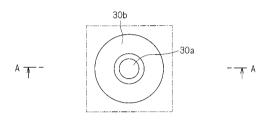

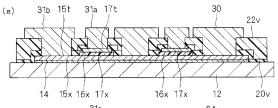

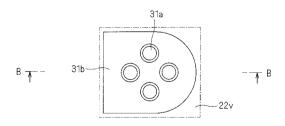

(5)次いで、図2(e)に示すように、上下電極引き出し用スルーホール埋め込み用電極膜30a,30bを形成する。このとき、図6の要部平面図に示すように、積層方向から見ると、上部電極層17に接続された電極膜30aの周りに、下部電極層15に接続された電極膜30bがドーナツ状に形成される。

[0043]

変形例1では、図示していないが、積層方向から見ると、上部電極層17に接続された電極膜の周りに、下部電極層15bに接続された4つ又はそれ以上の電極膜が等間隔(例えば90度ごと)に配置される。

[0044]

作製例では、スパッタリング法によりTi(膜厚100nm)、Cu(膜厚2000nm)を順次成膜した。次いで、フォトリソグラフィ法によってレジストマスクを形成し、表面に露出した部分のCu/Ti構造をイオンミリング法によりエッチングして、Cu/Tiからなる埋め込み用電極膜30a,30bを形成した。

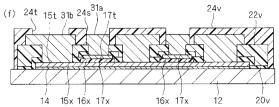

[0045]

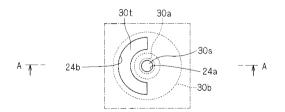

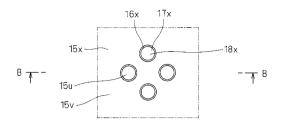

(6)次に、図2(f)に示すように、2層目の有機保護膜24を形成する。このとき、図7の要部平面図に示すように、第2の有機保護膜24には、上部電極層17に接続された引き出し用電極膜30 aの一部30 s が露出する貫通孔24 a と、下部電極層15に接続された引き出し用電極膜30 bの一部30 t が露出する半月状の貫通孔24 b とを形成する。

## [0046]

10

20

30

作製例では、感光性樹脂原料をスピンコートで塗布し、乾燥後、露光、現像工程を経てキュアを行い、貫通孔 2 4 a , 2 4 b を有する 2 層目の有機保護膜 2 4 として、膜厚 2 μ m のポリイミド膜を得た。

(7)

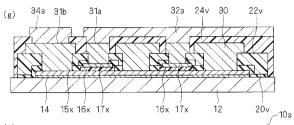

## [0047]

(7)次に、図2(g)に示すように、上下電極の引き出し電極膜32,34を形成する。このとき、図8の平面図に示すように、電極膜32,34が、それぞれ、電極膜30a,30bの露出面30s,30tに接続されるように形成する。

## [0048]

作製例では、スパッタリング法によりTi(膜厚100nm)、Cu(膜厚2000nm)を順次成膜した。次いで、フォトリソグラフィ法によってレジストマスクを形成し、表面に露出した部分のCu/Ti構造をイオンミリング法により除去して、Cu/Tiからなる引き出し電極膜32,34を形成した。

#### [0049]

(8)次に、図2(h)に示すように、3層目の有機保護膜26を形成する。第3の有機保護膜26には、上下電極引き出し電極膜32,34の一部32s,34sが外部電極として露出する貫通孔26a,26bを形成する。

## [0050]

作製例では、感光性樹脂原料をスピンコートで塗布し、乾燥後、露光、現像工程を経てキュアを行い、貫通孔 2 6 a , 2 6 b を有する有機保護膜 2 6 として、膜厚 2 μ m のポリイミド膜を得た。

#### [0051]

以上の工程で製造された可変コンデンサ10は、例えば、外部電極32g,34gに半田ボールや金属バンプなどの外部端子が形成され、回路基板などに実装される。

#### [0052]

## [0053]

まず、実施例2の可変コンデンサ10aの概要を説明する。実施例2の可変コンデンサ10aは、実施例1の可変コンデンサ10と略同様に構成されている。

## [0054]

すなわち、図10(h)の断面図に示すように、基板12上に、上部電極層17×と下部電極層15×との間に誘電体層16×が挟まれたキャパシタ構造を有し、上部電極層17×と下部電極層15×とは、それぞれ、引き出し電極を介して、外部電極32t,34tに電気的に接続されている。

## [0055]

実施例2の可変コンデンサ10aは、実施例1の可変コンデンサ10と異なり、容量発生部18×が複数に分割されている。

## [0056]

すなわち、積層方向から見ると、図11の要部平面図に示すように、上部電極層17×及び誘電体層16×は4つに分割されている。下部電極層15×は、上部電極層17×と下部電極層15×とが誘電体層16×を介して対向する4か所の容量発生部18×に重なる中心部15uと、中心部15uの外側に外周部15vとを有する。外周部15vは、下部電極層15×のうち、中心部15uを除く部分であり、各中心部15uについて見ると、各中心部15uの周囲を全周に渡って連続的に取り囲む。

#### [0057]

そして、下部電極層 1 5 x の外周部 1 5 v には、下部電極層 1 5 x と外部電極との間を接続する引き出し電極との接続面が複数個所に形成され、積層方向から透視すると、引き出し電極との接続面と容量発生部 1 8 x に重なる中心部 1 5 u とは、千鳥状に交互に配置

10

20

30

40

されている。

## [0058]

このように、下部電極層と引き出し電極とを接続する接続面と、容量発生部とを格子状又は千鳥状に交互に配置することにより、容量発生部と外部電極との間の相対的に比抵抗の高い下部電極層 1 5 における電流パスを増加させて電流を分散させ、導電ロスを小さくして、ESRが低減でき、高周波帯での損失を低減できる。

#### [0059]

次に、実施例2の可変コンデンサ10aの製造工程及び作製例について説明する。

#### [0060]

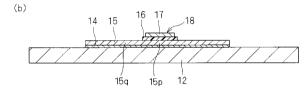

(1)まず、図9(a)に示すように、基板12上に、密着層14、下部電極層15、 誘電体層16、上部電極層17を積層する。

## [0061]

作製例では、表面にSiO₂膜が形成されたSiO₂/Si基板12上に、化学溶液堆積(CSD)法により、密着層14として、Ba<sub>0.7</sub>Sr<sub>0.3</sub>TiO₃(BST)薄膜を形成した。具体的には、化学量論組成のBST原料溶液を基板12のSiO₂膜上に塗布し、乾燥させ、650、30minの熱処理により結晶化させて、BST薄膜を得た。次いで、密着層14のBST薄膜上にスパッタリング法により膜厚300nmのPt膜を成膜し、下部電極層15とした。次いで、下部電極層15上に、誘電体層16として、密着層14のBST薄膜と同様にCSD法によりBST薄膜を形成した。すなわち、原料溶液を下部電極層15のPt膜上に塗布し、300~400 で乾燥させ、650 、30minの熱処理により結晶化させてBST薄膜を得た。次いで、誘電体層16のBST薄膜上に、スパッタリング法で膜厚300nmのPt膜を成膜し、上部電極層17とした。

## [0062]

(2)次に、図9(b)に示すように、各層14~17をパターニングして、複数の容量発生部18×を形成する。このとき、図11の平面図に示すように、積層方向から見ると、下部電極層15×は、複数に分割された上部電極層17×全体を含むように形成され、複数に分割された上部電極層17×のそれぞれについて、全周に渡って取り囲む。

## [0063]

作製例では、レジストマスクを形成した後、イオンミリング法により上部電極層17xとその下の誘電体層16x、下部電極層15xを順次ドライエッチングした。これを、キャパシタ構造とする。次いで、上記のキャパシタ構造を800 、30minの条件で熱処理した。

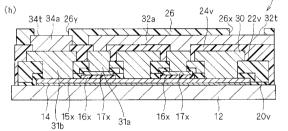

## [0064]

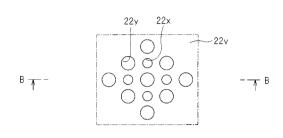

(3)次に、図9(c)に示すように、絶縁保護膜20vと、1層目の有機保護膜22 vとを形成する。このとき、1層目の有機保護膜22vには、上部電極層17xの上に貫通孔22xを形成し、下部電極層15xの外側領域の上に貫通孔22yを形成する。

## [0065]

このとき図12の要部平面図に示すように、貫通孔22xと貫通孔22yとは、交互に、千鳥状に形成する。

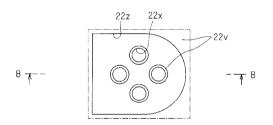

## [0066]

変形例2では、図12の代わりに、図13の要部平面図に示すように、複数の貫通孔22×と1つの貫通孔22zとが形成され、各貫通孔22×の周りが貫通孔22zで囲まれる。

## [0067]

10

20

30

### [0068]

(4)次に、図9(d)に示すように、1層目の有機保護膜22∨の貫通孔22×,2 2 yの底面に露出する部分の絶縁保護膜20∨を除去し、その下の部分の上部電極層17 ×及び下部電極層15×の一部17t,15tを露出させる。

## [0069]

作製例では、1層目の有機保護膜22∨であるポリイミド膜をマスクとして、CHF<sub>3</sub>ガスを用いて、矢印23aで示すように貫通孔22×,22yを介して絶縁保護膜20∨のSiN<sub>×</sub>膜をドライエッチングし、有機保護膜22∨の貫通孔22×,22zの底面に、上部電極層17×及び下部電極層15×のPt膜の一部17t,15tを露出させる。

## [0070]

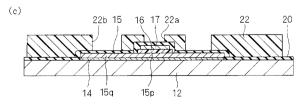

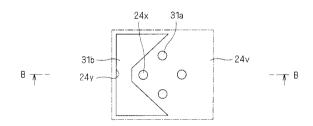

(5)次いで、図10(e)に示すように、上下電極引き出し用スルーホール埋め込み用電極膜31a,31bを形成する。このとき、図14の平面図に示すように、上部電極層17xに接続された電極膜31aの周りを取り囲むように、下部電極層15xに接続された電極膜31bが形成される。

### [0071]

作製例では、スパッタリング法によりTi(膜厚100nm)、Cu(膜厚2000nm)を順次成膜した。次いで、フォトリソグラフィ法によってレジストマスクを形成し、表面に露出した部分のCu/Ti構造をイオンミリング法によりエッチングして、Cu/Tiからなる埋め込み配線膜を形成した。

## [ 0 0 7 2 ]

(6)次に、図10(f)に示すように、第2の有機保護膜24vを形成する。このとき、図15の平面図に示すように、第2の有機保護膜24には、下部電極引き出し電極膜31bの一部31tが露出する1つの貫通孔24yと、上部電極膜31aの一部31sが露出する4つの貫通孔24xとを形成する。

#### [0073]

作製例では、感光性樹脂原料をスピンコートで塗布し、乾燥後、露光、現像工程を経てキュアを行い、貫通孔 2 4 x , 2 4 y を有する 2 層目の有機保護膜 2 4 v として、膜厚 2 μ m のポリイミド膜を得た。

## [0074]

(7)次に、図10(g)に示すように、上下電極の引き出し電極膜32a、34aを 形成する。このとき、図16の平面図に示すように、電極膜32a,34aが、それぞれ 、電極膜31a,31bの露出面に接続されるように形成する。

#### [0075]

作製例では、スパッタリング法によりTi(膜厚100nm)、Cu(膜厚2000nm)を順次成膜した。次いで、フォトリソグラフィ法によってレジストマスクを形成し、表面に露出した部分のCu/Ti構造をイオンミリング法により除去して、Cu/Tiからなる引き出し電極膜31a,31bを形成した。

## [0076]

(7)次に、図10(h)に示すように、上下電極引き出し電極膜31a,31bの一部32t,34tが露出する貫通孔26x,26yを有する第3の有機保護膜26を形成する。上下電極引き出し電極膜のうち、貫通孔26x,26yから露出する部分32s,34sは、外部電極になる。

## [0077]

作製例では、感光性樹脂原料をスピンコートで塗布し、乾燥後、露光、現像工程を経て キュアを行い、膜厚 2 μmのポリイミド膜を得た。

## [ 0 0 7 8 ]

以上の工程で製造された可変コンデンサ10aは、例えば、外部電極32t,34tに 半田ボールや金属バンプなどの外部端子が形成され、回路基板などに実装される。

## [0079]

<比較例> 従来の構造を有する比較例の可変コンデンサの製造工程及び作製例につい

10

20

30

40

て、図17~図19を参照しながら説明する。図17及び図18は、製造工程を示す断面図である。図19は、製造途中の要部平面図である。図17及び図18は、図19の線X-Xに沿って切断した断面図である。

[0800]

比較例の可変コンデンサは、実施例1略同様に製造される。

[0081]

(1)まず、図17(a)に示すように、基板12上に、密着層14、下部電極層15、誘電体層16、上部電極層17を積層する。

[0082]

作製例では、表面にSiO₂膜が形成されたSiO₂/Si基板12上に、化学溶液堆積(CSD)法により密着層14としてBa<sub>0.7</sub>Sr<sub>0.3</sub>TiO<sub>3</sub>(BST)薄膜を形成した。具体的には、化学量論組成のBSR原料溶液を基板12のSiO₂膜上に塗布し、乾燥させ、650、30minの熱処理により結晶化させてBST薄膜を得た。次いで、密着層14のBST薄膜上にスパッタリング法により膜厚300nmのPt膜を成膜し、下部電極層15とした。次いで、上記下部電極層15上に、誘電体層16として、密着層14のBST薄膜と同様にCSD法によりBST薄膜を形成した。すなわち、原料溶液を下部電極層15のPt膜上に塗布し、乾燥させ、650、30minの熱処理により結晶化させて、BST薄膜を得た。次いで、BST薄膜上にスパッタリング法で膜厚300nmのPt膜を成膜し、上部電極層17とした。

[0083]

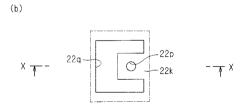

(2)次に、図17(b)に示すように、容量発生部18を形成する。このとき、図19(a)の要部平面図に示すように、積層方向から見ると、下部電極層15は、上部電極層17より大きく、上部電極層17を全周に渡って取り囲む。

[0084]

作製例では、フォトリソグラフィ法によってレジストマスクを形成した後、イオンミリング法により上部電極層17とその下の誘電体層16、下部電極層15を順次ドライエッチングした。これをキャパシタ構造とする。このキャパシタ構造を、800 、30minで熱処理した。

[0085]

(3)次に、図17(c)に示すように、無機の絶縁保護膜20kと、1層目の有機保護膜22kとを形成する。このとき、1層目の有機保護膜22kには、上部電極層17の上に貫通孔22pを形成し、下部電極層15の上に貫通孔22pを形成する。このとき、図19(b)の要部平面図に示すように、貫通孔22pは、貫通孔22pの片側を取り囲むように、略C字状に形成する。

[0086]

作製例では、キャパシタ構造の上面及び側面を覆うように、スパッタリング法により膜厚400nmの窒化シリコン(SiN<sub>x</sub>)膜を成膜し、絶縁保護膜20とした。

[0087]

次 N で、 絶 縁 保 護 膜 2 0 の S i N  $_{\chi}$  膜 上 に 感 光 性 樹 脂 原 料 を ス ピ ン コ ー ト で 塗 布 し 、 乾 燥 後 、 露 光 、 現 像 工 程 を 経 て キ ュ ア を 行 い 、 貫 通 孔 2 2 p , 2 2 q を 有 す る 1 層 目 の 有 機 保 護 膜 2 2 と し て 、 膜 厚 2  $\mu$  m の ポ リ イ ミ ド 膜 を 得 た 。

[0088]

(4)次に、図18(d)に示すように、1層目の有機保護膜22kの貫通孔22p, 22qの底面に露出している部分の絶縁保護膜20kを除去し、その下の部分の上部電極層17及び下部電極層15の一部17r,15rを露出させる。

[0089]

作製例では、 1 層目の有機保護膜 2 2 k のポリイミド膜をマスクとして、 C H F  $_3$  ガスを用いて、 矢印 2 3 で示すように絶縁保護膜 2 0 の S i N  $_X$  をドライエッチングし、上部電極層 1 7 及び下部電極層 1 5 の P t 膜の一部 1 7 r , 1 5 r を露出させた。

[0090]

50

10

20

30

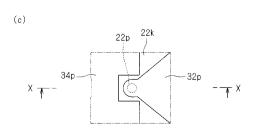

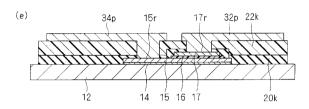

(5)次に、図18(e)に示すように、上部電極層17及び下部電極層15からの引き出し電極膜32p,34pを形成する。このとき、図19(c)の平面図に示すように、電極膜32p,34pは、それぞれ、電極層17,15の露出面17r,15r全体に接続され、1層目の有機保護膜22k上では互いに逆方向に、それぞれ大きく形成される

#### [0091]

作製例では、スパッタリング法によりTi(膜厚100nm)、Cu(膜厚2000nm)を順次成膜した。次にフォトリソグラフィ法によってレジストマスクを形成し、表面に露出した部分のCu/Ti構造をイオンミリング法により除去してCu/Tiからなる引き出し電極32p,34pを形成した。

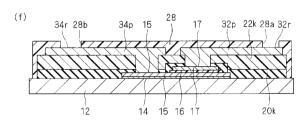

[0092]

(6)次に、図18(f)に示すように、2層目の有機保護膜28を形成する。2層目の有機保護膜28には、引き出し電極膜32p,34pの一部が露出する貫通孔28a, 28bを形成する。

#### [0093]

作製例では、感光性樹脂原料をスピンコートで塗布し、乾燥後、露光、現像工程を経てキュアを行い、貫通孔 2 8 a , 2 8 b を有する 2 層目の有機保護膜 2 8 として、膜厚 2 μmのポリイミド膜を得た。

## [0094]

く検討> 上部電極層17の合計面積を225μm²と同じにした、実施例1、実施例 2及び比較例のそれぞれの作製例について、有限要素法によりESRを計算した。計算条件は次の通りである。

素子サイズ 0.5×0.2mm

メッシュサイズ 10μm

計算周波数 2 G H z

ESRの測定 素子長手方向の両端で計算

引き出し電極間の距離 図2(h)の30aと30bの距離

3 4 の長手方向の長さ

3 4 の上下方向の長さ

は各条件で一定にして計算。

### [0095]

計算結果を、次の表1に示す。

## 【表1】

## 表 1 有限要素法による各構造の ESR 計算結果

|     | 実施例1     | 実施例2     | 比較例      |

|-----|----------|----------|----------|

| ESR | 0. 055 Ω | 0. 036 Ω | 0. 102 Ω |

## [0096]

この表1から、次のことが分かる。

## [0097]

下部電極層と引き出し電極との接続面の形状がドーナツ状である実施例1の構造と、下部電極層と引き出し電極との接続面を容量発生部の周りに等間隔で4箇所形成した実施例2の構造とは、いずれも、下部電極層と引き出し電極との接続面が容量発生部の片側1か所のみに形成されている比較例に比べて、ESRが低減できる。

## [0098]

また、上部電極及び容量発生部を複数に分割している実施例2の方が、上部電極及び容量発生部が1か所のみである実施例1と比べると、よりESRを低減できる。これは、実施例2の方が、実施例1よりも電流パスが増加して電流がより分散されるためである。

10

20

30

40

[0099]

[0100]

また、より薄い下部電極膜厚で同等の導電ロスの素子を得ることができる。

[ 0 1 0 1 ]

なお、本発明は、上記実施の形態に限定されるものではなく、種々変更を加えて実施することが可能である。

[0102]

例えば、本発明は、可変コンデンサ以外の種々のタイプのコンデンサに適用することができる。

[ 0 1 0 3 ]

また、下部電極引き出し部を分割する場合には、2箇所以上に分割し、均等に配置すればよい。例えば2箇所に分割する場合は、それぞれの下部電極引き出し部を略C字状に形成してもよい。3箇所に分割する場合には、下部電極引き出し部を120度ごとに配置すればよい。

【図面の簡単な説明】

- [0104]

- 【図1】可変コンデンサの製造工程を示す断面図である。(実施例1)

- 【図2】可変コンデンサの製造工程を示す断面図である。(実施例1)

- 【図3】可変コンデンサの製造途中の要部平面図である。(実施例1)

- 【図4】可変コンデンサの製造途中の要部平面図である。(実施例1)

- 【図5】可変コンデンサの製造途中の要部平面図である。(変形例1)

- 【図6】可変コンデンサの製造途中の要部平面図である。(実施例1)

- 【図7】可変コンデンサの製造途中の要部平面図である。(実施例1)

- 【図8】可変コンデンサの製造途中の要部平面図である。(実施例1)

- 【図9】可変コンデンサの製造工程を示す断面図である。(実施例2)

- 【図10】可変コンデンサの製造工程を示す断面図である。(実施例2)

- 【図11】可変コンデンサの製造途中の要部平面図である。(実施例2)

- 【図12】可変コンデンサの製造途中の要部平面図である。(実施例2)

- 【図13】可変コンデンサの製造途中の要部平面図である。(実施例2)

- 【図14】可変コンデンサの製造途中の要部平面図である。(実施例2)

- 【図15】可変コンデンサの製造途中の要部平面図である。(変形例2)

- 【図16】可変コンデンサの製造途中の要部平面図である。(実施例2)

- 【図17】可変コンデンサの製造工程を示す断面図である。(比較例) 【図18】可変コンデンサの製造工程を示す断面図である。(比較例)

- 【図19】可変コンデンサの製造途中の要部平面図である。(比較例)

- 【図20】可変コンデンサの断面図である。(従来例)

【符号の説明】

- [0105]

- 12 基板

- 15,15x 下部電極層

- 15p 中心部

- 15q 外周部

- 15s,15t 接続面

- 15 u 中心部

30

10

20

40

10

- 15 v 外周部

- 16,16x 誘電体層

- 17,17x 上部電極層

- 18,18z 容量発生部

- 2 0 絶縁保護膜

- 2 2 , 2 2 v 有機保護膜

- 24,24 > 有機保護膜

- 2 6 有機保護膜

- 30a,30b 電極膜(引き出し電極)

- 3 1 a , 3 1 b 電極膜(引き出し電極)

- 3 2 , 3 2 a 電極膜(引き出し電極)

- 3 2 s , 3 2 t 外部電極

- 34,34a 電極膜(引き出し電極)

- 3 4 s , 3 4 t 外部電極

## 【図1】

## 【図2】

# 【図3】

# 【図5】

# 【図4】

# 【図6】

# 【図7】

【図8】

# 【図9】

# 【図10】

【図13】

# 【図14】

# 【図11】

# 【図12】

# 【図15】

# 【図16】

# 【図17】

# 【図18】

# 【図19】

【図20】