#### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2010-258254 (P2010-258254A)

(43) 公開日 平成22年11月11日(2010.11.11)

| (51) Int.Cl.                           | F I                                                    |                                              | テーマコード(参考)                                                                                                                                                              |

|----------------------------------------|--------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HO1L 25/10<br>HO1L 25/11               | <b>(2006.01)</b> HO11                                  | 25/14<br>25/08                               | Z<br>Z                                                                                                                                                                  |

| HO1L 25/18<br>HO1L 25/06<br>HO1L 25/07 | 5 (2006.01)                                            | 安本護状                                         | : 未請求 - 請求項の数 16 - O L - (全 19 頁)                                                                                                                                       |

| (21) 出願番号 (22) 出願日                     | 特願2009-107380 (P2009-107380)<br>平成21年4月27日 (2009.4.27) | (71) 出願人<br>(74) 代理人<br>(72) 発明者<br>(72) 発明者 | ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部1753番地<br>100080001<br>弁理士 筒井 大和<br>早坂 隆<br>東京都千代田区大手町二丁目6番2号 株<br>式会社ルネサステクノロジ内<br>・<br>杉田 憲彦<br>東京都千代田区大手町二丁目6番2号 株<br>式会社ルネサステクノロジ内 |

|                                        |                                                        |                                              | 式会社ルネサステクノロジ内<br>最終頁に続く                                                                                                                                                 |

# (54) 【発明の名称】半導体装置

# (57)【要約】

【課題】積層型の半導体装置の信頼性の向上を図る。 【解決手段】下段の第1配線基板3にフリップチップ接

続されたSOC1と、上段の第2配線基板4にフリップ チップ接続されたSDRAM2と、第1配線基板3と第 2配線基板4とを接続する複数の第2ボール電極6と、 第1配線基板3の第1下面3bに接続された複数の第1 ボール電極5とからなり、第2配線基板4の内部には、 第2メタル層4cとこの第2メタル層4c上に配置され た第2絶縁層4dとが設けられ、上段のSDRAM2が 第2配線基板4の第2絶縁層4dより上に配置されてい るため、下段のSOC1と上段のSDRAM2の放熱経 路12a,12bを切り分けることができ、下段のSO C 1の熱を実装基板 1 1 に逃がすことができる。これに より、積層型のSIP7の信頼性の向上を図ることがで きる。

【選択図】図2

- 2d: 第2パンプ電極 3: 第1配線基板

- 3a:第1上面 3b:第1下面 3d:第1絕緣層 4:第2配線基板

#### 【特許請求の範囲】

#### 【請求項1】

複数の第1ボール電極、またはランド電極を介して実装基板に接続し得る半導体装置であって、

第1上面とその反対側の第1下面とを有し、第1絶縁層を備えた第1配線基板と、

前記第1配線基板の前記第1上面上に搭載された第1半導体チップと、

第2上面とその反対側の第2下面とを有し、前記第1半導体チップ上に配置され、前記 第1配線基板と複数の第2ボール電極を介して電気的に接続された第2配線基板と、

前記第2配線基板の前記第2上面上に搭載された第2半導体チップと、

前記第1配線基板の前記第1下面に設けられた前記複数の第1ボール電極と、

を有し、

前記第1半導体チップは、前記第2半導体チップより発熱量が多く、

前記第2配線基板は、メタル層と前記メタル層上に配置された第2絶縁層とを備えるとともに、前記メタル層の一部は、前記複数の第2ボール電極のうちの何れかを介して前記第1配線基板に電気的に接続され、

前記第2配線基板の前記第2絶縁層上に前記第2半導体チップが搭載されていることを特徴とする半導体装置。

#### 【請求項2】

請求項1記載の半導体装置において、前記第1半導体チップは、前記第2半導体チップ より消費電力が大きいことを特徴とする半導体装置。

【請求項3】

請求項2記載の半導体装置において、前記第2半導体チップは、前記第1半導体チップより温度耐性が低いことを特徴とする半導体装置。

#### 【請求項4】

請求項3記載の半導体装置において、前記第1半導体チップの単位時間に動作している 回路の数は、前記第2半導体チップより多いことを特徴とする半導体装置。

#### 【請求頃5】

請求項4記載の半導体装置において、前記第1半導体チップのパッド数は、前記第2半導体チップのパッド数より多いことを特徴とする半導体装置。

# 【請求項6】

請求項5記載の半導体装置において、前記第1半導体チップは、その動作がプログラムによって制御される回路を有するシステムオンチップであり、前記第2半導体チップは、 メモリチップであることを特徴とする半導体装置。

# 【請求項7】

請求項1記載の半導体装置において、前記第1半導体チップは、複数の第1バンプ電極を介して前記第1配線基板の前記第1上面上に搭載され、前記第2半導体チップは、複数の第2バンプ電極を介して前記第2配線基板の前記第2上面上に搭載されていることを特徴とする半導体装置。

#### 【請求項8】

請求項7記載の半導体装置において、前記第2配線基板の前記メタル層は、前記第1半導体チップの第1裏面に接続されていることを特徴とする半導体装置。

#### 【請求項9】

請求項8記載の半導体装置において、前記第2配線基板の前記第2下面に、前記第1半導体チップの前記第1裏面に接続するメタルプレーン層が設けられ、前記メタル層と前記メタルプレーン層が接続されていることを特徴とする半導体装置。

# 【請求項10】

請求項9記載の半導体装置において、前記メタルプレーン層と前記第1半導体チップの前記第1裏面との間にフィルム状接着材またはペースト材が介在されていることを特徴とする半導体装置。

### 【請求項11】

10

20

30

請求項10記載の半導体装置において、前記第2半導体チップの第2裏面にヒートスプレッダが設けられていることを特徴とする半導体装置。

#### 【請求項12】

請求項11記載の半導体装置において、前記第2配線基板の前記第2絶縁層の熱伝導率は、前記第1配線基板の前記第1絶縁層の熱伝導率より小さいことを特徴とする半導体装置。

#### 【請求項13】

請求項1記載の半導体装置において、前記第1配線基板は、ビルドアップ基板であり、前記第2配線基板は、ビア用の貫通孔がドリルによって形成された基板であることを特徴とする半導体装置。

【請求項14】

請求項1記載の半導体装置において、前記第1配線基板、及び前記第2配線基板では、前記第1半導体チップの電源端子と前記第2半導体チップの電源端子とが電気的に分離されていることを特徴とする半導体装置。

#### 【請求項15】

請求項1記載の半導体装置において、前記第2配線基板の前記メタル層と、前記第1半導体チップのGND端子に電気的に接続される前記第2ボール電極とが、前記第2配線基板において電気的に接続されていることを特徴とする半導体装置。

#### 【請求項16】

請求項1記載の半導体装置において、前記第2配線基板の前記メタル層と繋がるアウタリードが前記第2配線基板の側部から露出して設けられていることを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

[00001]

本発明は、半導体装置に関し、特に、積層型の半導体装置に適用して有効な技術に関する。

【背景技術】

[0002]

半導体チップをモジュール基板上にフリップチップ実装したモジュールを積層して成る 積層型半導体装置の放熱構造において、モジュール基板及びマザーボードに、これらを厚 み方向に貫通する放熱用ビアが、半導体チップまたは熱伝導材に接触するように形成され た構造が記載されている(例えば、特許文献1参照)。

[0003]

また、積層型半導体装置において、半導体基板の裏面に放熱用の金属パターンを形成し、さらに半導体基板の厚み方向に貫通する貫通ビアを形成し、半導体装置の金属パターンに伝達された熱を、この金属パターンが設けられた半導体装置の裏面側に隣り合う半導体装置の貫通ビアに伝達する技術が記載されている(例えば、特許文献2参照)。

【先行技術文献】

【特許文献】

[0004]

【特許文献1】特開2000-12765号公報

【特許文献2】特開2006-295119号公報

【発明の概要】

【発明が解決しようとする課題】

[0005]

複数の半導体チップ(IC(Integrated Circuit))を積層したSIP(System In Package)や半導体パッケージを積層したPOP(Package On Package)等の半導体装置において、下段側の半導体チップとして、消費電力が大きくて発熱量が多いシステムオンチップ(以降、単にSOC(System On Chip)とも言う)やマイコンチップを搭載し、上段側の

10

20

30

00

40

半導体チップとして、消費電力が小さくて発熱量が少ないDRAM(Dynamic Random Access Memory)等のメモリチップやアナログICを搭載した積層型の半導体装置が知られている。

[0006]

前述のような積層型の半導体装置では、メモリチップやアナログIC等の制御を行うSOCやマイコンチップが、外部装置との信号のやり取りも行う。したがって、配線基板における配線パターンの引き回しを少しでも容易にするために、SOCやマイコンチップは、下段側に搭載されることが多い。

[0007]

今後、SOCやマイコンチップの高性能化や高集積化が進んでいくと、発熱量がさらに 多くなるため、放熱対策が必須となる。

[0008]

例えば、下段にSOCが搭載され、上段にDRAMが搭載される半導体装置では、SOCとDRAMとで、温度耐性が異なっている。SOCの温度耐性は、ジャンクション温度丁 j 換算で約125 であるのに対して、DRAMの温度耐性は、雰囲気温度Ta=70~85 、ケース温度Tc=85 ~95 、ジャンクション温度T j 換算でおおよそ100 未満である。DRAMでは、記憶が失われないように電荷を補充するリフレッシュと呼ばれる動作があり、このリフレッシュ動作を満足させるための温度が規格によって雰囲気温度Ta=70 ~85 、ケース温度Tc=85 ~95 と定められている。

[0009]

したがって、今後、SOCの発熱量がさらに多くなると、SOCから発せられる熱が上段のDRAMに伝わってDRAMが動作不良に至り、半導体装置が不良となることが問題である。

[ 0 0 1 0 ]

なお、前記特許文献1(特開2000-12765号公報)には、半導体チップの表面側に半導体チップと接する埋め込み導体を設け、バンプ電極を介して実装基板側に熱を逃がす構造が記載されており、また、前記特許文献2(特開2006-295119号公報)には、同様に、半導体チップの表面側に半導体チップと接する導電パターンを設け、バンプ電極を介して実装基板側に熱を逃がす構造が記載されている。

[0011]

しかしながら、前記特許文献1や2の半導体装置においては、下段の半導体チップから発せられる熱が上段の半導体チップに伝わらないような構造に形成されていないため、前述のような下段にSOCが搭載され、上段にDRAMが搭載される場合には、下段のSOCの熱が上段のDRAMに伝わってDRAMが動作不良を引き起し、半導体装置が不良となる。

[0012]

すなわち、下段の半導体チップの放熱経路と上段の半導体チップの放熱経路が切り分けられていないため、SOCの熱がDRAMに伝わり、DRAMの温度が許容範囲を越えて動作不良を引き起し、その結果、半導体装置不良に至る。

[0013]

本発明は、上記課題に鑑みてなされたものであり、その目的は、積層型の半導体装置の信頼性の向上を図ることができる技術を提供することにある。

[0014]

また、本発明の他の目的は、発熱量が多い半導体チップの放熱効果を高めることができる技術を提供することにある。

[0015]

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

- 【課題を解決するための手段】

- [0016]

20

10

30

40

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下の とおりである。

[0017]

すなわち、本発明は、複数の第1ボール電極、またはランド電極を介して実装基板に接 続し得るものであり、第1上面とその反対側の第1下面とを有し、第1絶縁層を備えた第 1 配線基板と、前記第 1 配線基板の前記第 1 上面上に搭載された第 1 半導体チップと、第 2上面とその反対側の第2下面とを有し、前記第1半導体チップ上に配置され、前記第1 配線基板と複数の第2ボール電極を介して電気的に接続された第2配線基板と、前記第2 配線基板の前記第2上面上に搭載された第2半導体チップと、前記第1配線基板の前記第 1下面に設けられた前記複数の第1ボール電極と、を有し、前記第1半導体チップは、前 記 第 2 半 導 体 チ ッ プ よ り 発 熱 量 が 多 く 、 前 記 第 2 配 線 基 板 は 、 メ タ ル 層 と 前 記 メ タ ル 層 上 に配置された第2絶縁層とを備えるとともに、前記メタル層の一部は、前記複数の第2ボ ール電極のうちの何れかを介して前記第1配線基板に電気的に接続され、前記第2配線基 板の前記第2絶縁層上に前記第2半導体チップが搭載されているものである。

【発明の効果】

[ 0 0 1 8 ]

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明 すれば、以下のとおりである。

[0019]

チップ積層型の半導体装置において、下段の半導体チップと上段の半導体チップの放熱 経路を切り分けることで、下段の半導体チップの熱が上段の半導体チップに伝わらないた め、半導体装置の信頼性の向上を図ることができる。

[0020]

また、発熱量の異なる半導体チップを積層する際に、発熱量が多い半導体チップの放熱 効果を高めることができる。

【図面の簡単な説明】

[0021]

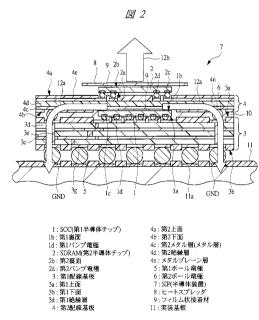

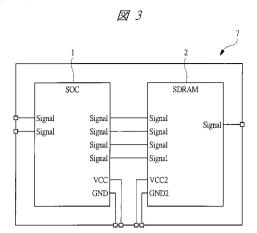

- 【図1】本発明の実施の形態の半導体装置の構造の一例を示す断面図である。

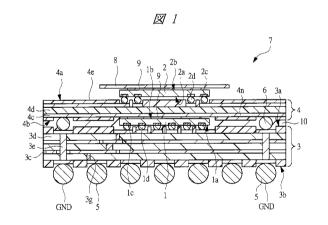

- 【図2】図1に示す半導体装置の実装構造と放熱経路の一例を示す部分断面図である。

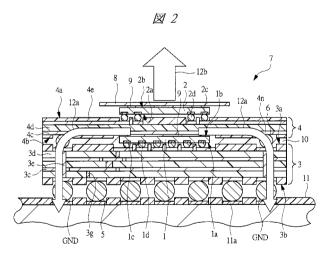

- 【 図 3 】 図 1 に 示 す 半 導 体 装 置 の 回 路 構 造 の 一 例 を 示 す ブ ロ ッ ク 図 で あ る 。

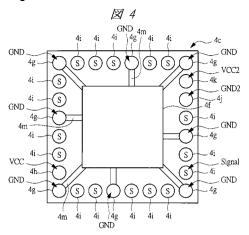

【 図 4 】 図 1 に 示 す 半 導 体 装 置 に 組 み 込 ま れ る メ タ ル 層 に お け る 配 線 パ タ ー ン の 一 例 を 示 す平面図である。

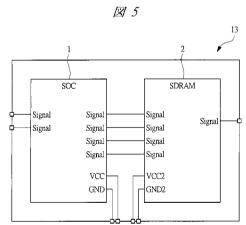

【図5】本発明の実施の形態の第1変形例の半導体装置の回路構造を示すブロック図であ る。

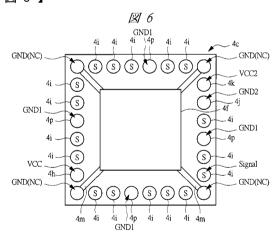

【 図 6 】 図 5 に示す半導体装置に組み込まれるメタル層における配線パターンの一例を示 す平面図である。

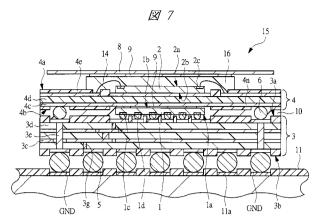

【 図 7 】 本 発 明 の 実 施 の 形 態 に お け る 第 2 変 形 例 の 半 導 体 装 置 の 構 造 を 示 す 断 面 図 で あ る

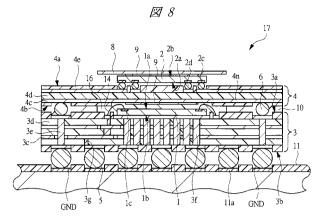

【図8】本発明の実施の形態における第3変形例の半導体装置の構造を示す断面図である

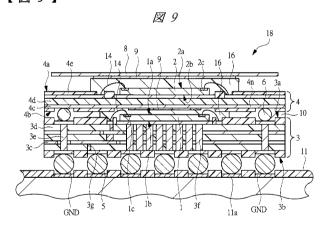

【図9】本発明の実施の形態における第4変形例の半導体装置の構造を示す断面図である

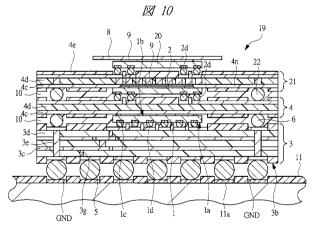

【図10】本発明の実施の形態における第5変形例の半導体装置の構造を示す断面図であ る。

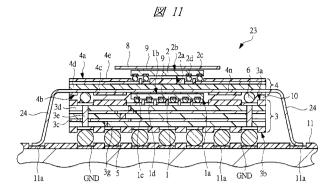

【図11】本発明の実施の形態における第6変形例の半導体装置の構造を示す断面図であ

【発明を実施するための形態】

[0022]

以下の実施の形態では特に必要なとき以外は同一または同様な部分の説明を原則として 繰り返さない。

10

20

30

40

#### [0023]

さらに、以下の実施の形態では便宜上その必要があるときは、複数のセクションまたは 実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係な ものではなく、一方は他方の一部または全部の変形例、詳細、補足説明などの関係にある

# [0024]

また、以下の実施の形態において、要素の数など(個数、数値、量、範囲などを含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合などを除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良いものとする。

# [0025]

また、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。

#### [0026]

また、以下の実施の形態において、構成要素等について、「Aからなる」、「Aよりなる」、「Aを有する」、「Aを含む」と言うときは、特にその要素のみである旨明示した場合等を除き、それ以外の要素を排除するものでないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

# [0027]

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

# [0028]

#### (実施の形態)

図1は本発明の実施の形態の半導体装置の構造の一例を示す断面図、図2は図1に示す 半導体装置の実装構造と放熱経路の一例を示す部分断面図、図3は図1に示す半導体装置 の回路構造の一例を示すブロック図、図4は図1に示す半導体装置に組み込まれるメタル 層における配線パターンの一例を示す平面図である。

#### [0029]

本実施の形態の半導体装置は、複数の半導体チップがそれぞれ配線基板を介して積層されて成る半導体パッケージであり、本実施の形態では、前記半導体装置の一例として、SIP7を取り上げて説明する。

# [0030]

なお、SIP7は、図1に示すように、配線基板上に下段の半導体チップが搭載され、さらにこのチップ上に上段の半導体チップが配線基板を介して搭載されており、下段の半導体チップの方が上段の半導体チップより発熱量が多いものである。つまり、下段には、SOC1やマイコンチップ等の発熱量の多い半導体チップが搭載され、上段には、DRAMやSDRAM(Synchronous DRAM)2またはアナログIC等の発熱量の少ない半導体チップが搭載されている。本実施の形態では、下段の半導体チップの一例としてSOC1を取り上げ、上段の半導体チップの一例としてSDRAM2を取り上げて説明するが、各半導体チップはこれらに限定されるものではない。

# [0031]

SIP7の詳細構造について説明すると、第1上面3aとその反対側の第1下面3bとを有し、かつ第1絶縁層3dを備えた下段側の第1配線基板3と、第1配線基板3の第1上面3a上に搭載された下段側の第1半導体チップであるSOC1と、第2上面4aとその反対側の第2下面4bとを有するとともに、SOC1上に配置され、かつ第1配線基板

10

20

30

40

3 と複数の第 2 ボール電極 6 を介して電気的に接続された上段側の第 2 配線基板 4 と、第 2 配線基板 4 の第 2 上面 4 a 上に搭載された上段側の第 2 半導体チップである S D R A M 2 とを備えている。

#### [0032]

さらに、第2配線基板4は、第2メタル層(メタル層)4cと第2メタル層4c上に配置された断熱層でもある第2絶縁層4dとを備えるとともに、第2メタル層4cの一部は、複数の第2ボール電極6のうちの何れかを介して第1配線基板3に電気的に接続されている。また、第2配線基板4の第2絶縁層4d上にSDRAM2が搭載されている。第2配線基板4の表面には、ソルダーレジスト4eが形成されている。

#### [0033]

また、第1配線基板3の第1下面3bにはSIP7の外部接続端子となる複数の第1ボール電極5が、例えば、格子状配列で設けられており、SIP7は、図2に示すように、複数の第1ボール電極5を介して実装基板11に接続(実装)することが可能な半導体装置である。

#### [0034]

また、下段の第1半導体チップであるSOC1は、第1配線基板3の第1上面3aの中央部にその第1主面1aを下に向けてフリップチップ接続で実装されている。すなわち、SOC1は、複数の第1バンプ電極1dを介して第1配線基板3の第1上面3a上に搭載されている。一方、上段の第2半導体チップであるSDRAM2も、同様に、第2配線基板4の第2上面4aの中央部にその第2主面2aを下に向けてフリップチップ接続で実装されている。つまり、SDRAM2は、複数の第2バンプ電極2dを介して第2配線基板4の第2上面4a上に搭載されている。

#### [ 0 0 3 5 ]

また、下段の第1配線基板3と上段の第2配線基板4とを電気的に接続する複数の第2ボール電極6は、SOC1の外側の領域において、第1配線基板3の周縁部に配置されている。

#### [0036]

また、第1配線基板3には、複数の第2ボール電極6のうちの複数のGND端子同士を電気的に接続する第1メタル層3cが形成されており、さらに第1メタル層3cの表裏両面側には第1絶縁層3dが形成されている。

#### [0037]

一方、第2配線基板4には、複数の第2ボール電極6のうちの前記複数のGND端子同士を電気的に接続する第2メタル層4cが形成されており、さらに第2メタル層4cの上層には断熱層となる第2絶縁層4dが形成されている。したがって、SDRAM2は、第2絶縁層4dより上方の位置、すなわち第2絶縁層4dより上層の位置の第2上面4a上にフリップチップ接続されている。

# [0038]

また、第1配線基板3では、内部に層間配線である複数のビア3eが設けられており、例えば、GND用の第2ボール電極6と第1メタル層3cとが複数のビア3eを介して電気的に接続されている。一部にはレーザービア3gも形成されている。第1配線基板3は、例えば、フォトリソ技術等によって形成された多層配線を有するビルドアップ基板である。

#### [0039]

一方、第2配線基板4は、例えば、ビア用の貫通孔がドリル加工によって形成された貫通基板である。

# [0040]

このように上段の第2配線基板4に高価なビルドアップ基板ではなく、安価な前記貫通 基板を用いることにより、SIP7の製造コストを低減することができる。

#### [0041]

また、第1配線基板3と第2配線基板4の間には封止用の樹脂であるレジン10が充填

10

20

30

40

されており、SOC1の周囲やSOC1のフリップチップ接続部、さらには複数の第2ボール電極6の周囲にレジン10が埋め込まれて、SOC1や第2ボール電極6が封止されて保護されている。なお、レジン10は、例えば、エポキシ系の樹脂である。

#### [0042]

また、SDRAM2の上方を向いた第2裏面2bにはヒートスプレッダ8が設けられている。ヒートスプレッダ8は、熱伝導率の高い金属製の材質から形成されていることが好ましく、SDRAM2から発せられる熱を上方の外部に放出する構造となっている。

#### [0043]

なお、第1ボール電極 5 や第 2 ボール電極 6 は、例えば、半田ボール電極であり、また、第 1 バンプ電極 1 d や第 2 バンプ電極 2 d は、例えば、半田バンプ電極もしくは金バンプ電極である。

#### [0044]

本実施の形態のSIP7では、下段に配置された第1半導体チップであるSOC1は、上段に配置された第2半導体チップであるSDRAM2より発熱量が多い。これは、SOC1は、CPU(Central Processing Unit)を有するとともに、その動作がプログラムによって制御される回路を有するシステムオンチップであり、一方、SDRAM2は、単にメモリ回路を備えたメモリチップであるためである。

# [0045]

つまり、SOC1は、例えば、SDRAM2を制御するコントロール機能、通信機能及びグラフィック機能等を備えており、したがって、内部に組み込まれているトランジスタの数も多いため、SDRAM2等のメモリチップに比べて発熱量が遥かに多い。

#### [0046]

別の言い方をすると、SOC1の単位時間に動作している回路の数は、SDRAM2より多い。また、SOC1のパッド数(第1パッド1cの数)は、SDRAM2のパッド数(第2パッド2cの数)より多い。

#### [0047]

したがって、SOC1は、SDRAM2より消費電力が大きく、発熱量が多い。

#### [0048]

すなわち、SIP7では、下段のSOC1の方が、上段のSDRAM2に比べて発熱量が遥かに多い。SOC1の発熱量は、例えば、約5W(ワット)であり、一方、SDRAM2の発熱量は、例えば、0.5W程度である。つまり、SOC1とSDRAM2とでは、SOC1の方が約10倍発熱量が大きい。

#### [0049]

なお、SOC1は複数の電源レベルを持つが、その中でSDRAM2と接続される信号用の電源とSDRAM2とで実動作時の電源レベルは同じであり、動作電圧は、例えば、3Vである。

## [0050]

一方で、SIP7では、SDRAM2は、SOC1より温度耐性が低い。SDRAM2 の温度耐性は、例えば、雰囲気温度 Ta=70 ~85 、ジャンクション温度 Tj換算で100 未満程度であり、一方、SOC1の温度耐性は、例えば、ジャンクション温度 Tj換算で125 程度である。

#### [0051]

したがって、仮にジャンクション温度 T j 換算で 1 0 0 の温度雰囲気の場合には、 S O C 1 は温度が許容範囲内であるため、その機能に支障を来すことはないが、 S D R A M 2 では温度が許容範囲を越えているため、不具合が出る可能性がある。

# [0052]

そこで、SOC1から発せられる熱をSDRAM2に伝えないようにする必要があるが、本実施の形態のSIP7では、この対策として、SOC1とSDRAM2とで放熱経路を切り分けており、これにより、SOC1から発せられる熱がSDRAM2に伝わらない構造となっている。

10

20

30

40

#### [0053]

すなわち、図2に示すようにSIP7では、上段の半導体チップの放熱経路12bと下段の半導体チップの放熱経路12aを切り分け、一方の半導体チップから発せられる熱が他方の半導体チップに影響しないような構造となっている。具体的には、発熱量が多い下段のSOC1から発せられる熱は、図2の放熱経路12aに示すように第1ボール電極5や第2ボール電極6等を介して実装基板11に逃がす。

#### [0.054]

これに対して、上段のSDRAM2では、図2の放熱経路12bに示すようにSDRA M2の第2裏面2bに設けられたヒートスプレッダ8を介して外部に熱を放す。

#### [0.055]

つまり、SIP7おいては、下段のSOC1は下方の実装基板11に熱を逃がし、一方、上段のSDRAM2は、上方に熱を逃がす構造となっており、それぞれの半導体チップの放熱経路12a,12bを切り分けた構造となっている。

## [0056]

なお、図2のSIP7の実装構造に示すように、SIP7の外部接続端子である複数の 第1ボール電極5とこれらに対応する実装基板11の電極11aとが半田接続されている

# [0057]

また、本実施の形態のSIP7では、上段の第2配線基板4内に、第2メタル層(メタル層)4cが設けられており、この第2メタル層4cは、下段のSOC1の第1裏面1bと接続されている。これによって、SOC1から発せられる熱をその第1裏面1b側から第2メタル層4c、第2ボール電極6及び第1ボール電極5を介して実装基板11に伝えて逃がすことができ、SOC1の放熱性を向上することができる。

#### [0058]

ここで、図4を用いて、上段の第2配線基板4内に設けられた第2メタル層4cの構造について説明する。第2メタル層4cには、その略中央部に、放熱を兼ねた四角形の広域面積のベタパターンである共通パターン4fが設けられている。さらに共通パターン4fの周囲には各ランドが配置されている。前記各ランドには、SOC用GNDランド4g、SOC用電源ランド4h、SOC用やSDRAM用の信号ランド4i、メモリ用GNDランド4j及びメモリ用電源ランド4kが含まれており、これらランドのうち、複数のSOC用GNDランド4gのそれぞれは、配線部4mを介して中央部の共通パターン4fと接続されている。なお、放熱効果を向上させるため、配線部4mはスペースの許す限り太くすることが望ましいことは言うまでもない。

# [0059]

なお、前記複数のSOC用GNDランド4gのそれぞれには、図2に示すようにGND用の第2ボール電極6が接続されており、さらにこれらのGNDの第2ボール電極6が第1配線基板3のビア3eやGNDの第1ボール電極5を介して実装基板11のGNDの電極11aに接続され、この経路が放熱を兼ねた放熱経路12aとなっている。すなわち、下段のSOC1の放熱経路12aは、実装基板11のGNDの電極11aに接続された経路となっている。

# [0060]

言い換えると、第2配線基板4の第2メタル層4cの共通パターン4fと、SOC1のGND端子に電気的に接続される第2ボール電極6とが、第2配線基板4においてSOC用GNDランド4gや配線部4mを介して電気的に接続されている。さらに、言い換えると、上段の第2配線基板4内の第2メタル層4cにおいては、共通パターン4fをSOC1のGNDと共通化している。

#### [0061]

また、図3は、SIP7の回路ブロックを示す図である。図2~図4に示すように、SOC1のSignal(S)とSDRAM2のSignal(S)とが信号の第2ボール電極6を介してそれぞれ接続されている。本実施の形態のSIP7では、上段の第2配線基板4におい

10

20

30

40

20

30

40

50

ては、図 4 に示すように、少なくとも S D R A M 2 の電源端子 ( V C C 2 ) と S D R A M 2 の Signal ( S ) は、第 2 メタル層 4 c とは分離されている。

[0062]

さらに、SOC1の電源端子(VCC)とSDRAM2の電源端子(VCC2)とは電気的に分離されているが、実装基板11上では、SOC1の電源(VCC)とSDRAM2の電源(VCC2)とが接続されている。なお、SOC1の電源(VCC)、およびSDRAM2の電源(VCC2)については放熱経路を担っていないため、第1配線基板3もしくは第2配線基板4上で電気的に接続してもSOC1とSDRAM2の放熱経路を分離できることは言うまでもない。

[0063]

また、図2に示すように、上段の第2配線基板4の第2下面4bには、下段のSOC1の第1裏面1bに接続するメタルプレーン層4nが設けられており、第2メタル層4cとメタルプレーン層4nとが接続されている。

[0064]

また、上段の第2配線基板4においては、第2メタル層4cに形成されたランドに第2ボール電極6が接続されている。

[0065]

さらに、上段の第2配線基板4のメタルプレーン層4nと下段のSOC1の第1裏面1 b との間には、フィルム状接着材9が介在されており、SOC1の第1裏面1 b がフィルム状接着材9によってメタルプレーン層4nに接合されている。したがって、フィルム状接着材9は、例えば、高熱伝導性のものが好ましい。なお、フィルム状接着材9の代わりとして、高熱伝導性のペースト材等を用いてもよい。第2配線基板4のメタルプレーン層4nとSOC1の第1裏面1 b との間に高熱伝導性のフィルム状接着材9を介在させたことで、SOC1から発せられる熱をフィルム状接着材9、メタルプレーン層4nを介して第2メタル層4cに確実に伝えることができ、SOC1の放熱性を高めることができる。さらに、フィルム状接着材9によって、フリップチップ接続されたSOC1の高さ調整を行うこともできる。

[0066]

以上により、下段のSOC1の放熱経路12aは、SOC1の第1裏面1b、フィルム 状接着材9、上段の第2配線基板4に設けられたメタルプレーン層4n、第2メタル層4 c、上下の基板を接続する複数の第2ボール電極6、下段の第1配線基板3の内部配線、 複数の第1ボール電極5及び実装基板11へと繋がる経路である。

[0067]

一方、上段のSDRAM2の放熱経路12bは、SDRAM2の第2裏面2bもしくは第2裏面2bに取り付けられたヒートスプレッダ8を搭載している場合にはそのヒートスプレッダ8であり、第2裏面2bもしくはヒートスプレッダ8から外部(空気中)に熱を放出する。

[0068]

また、上段の第2配線基板4においては、その内部の第2メタル層4cの上部に断熱層である第2絶縁層4dが設けられている。

[0069]

その際、前記断熱層(第2絶縁層4d)の熱伝導率は、下段の第1配線基板3の第1絶縁層3dの熱伝導率より小さいことが望ましい。つまり、下段のSOC1から発せられる熱を前記断熱層(第2絶縁層4d)によって遮断して、SDRAM2に熱が伝わることを低減することができる。

[0070]

さらに、SOC1の第1裏面1bと熱的に接続するメタルプレーン層4nを、第2メタル層4cより上部に配置しないようにすることで、下段のSOC1の放熱経路12aと、上段のSDRAM2の放熱経路12bとを分けることができる。

[0071]

また、下段の第1配線基板3の内部にも第1メタル層3cが設けられており、この第1メタル層3cの一部をGNDと接続することにより、さらに放熱効率を高めることができる。

[0072]

本実施の形態のSIP(半導体装置)7によれば、下段のSOC1と上段のSDRAM2の放熱経路12a,12bを切り分けることができる。すなわち、図2に示すように、発熱量が多い下段のSOC1と発熱量が少ない上段のSDRAM2とにおいて、発熱量が多いSOC1の放熱経路12aを実装基板11に向けるとともに、発熱量が少ないSDRAM2の放熱経路12bを外部上方に向けることで、両者の放熱経路12a,12bを上方向と下方向(実装基板11側)とに明確に分けることができる。

[0073]

したがって、上段のSDRAM2に対して下段のSOC1の熱が伝わらないようにして 下段のSOC1の熱を実装基板11に逃がすことができる。

[0074]

その結果、下段のSOC1の熱が上段のSDRAM2に伝わらないため、上段のSDRAM2が動作不良を引き起こすことはなく、積層型のSIP7の信頼性の向上を図ることができる。

[0075]

また、上段の第2配線基板4に第2メタル層4cが設けられ、この第2メタル層4c及び複数の第2ボール電極6や複数の第1ボール電極5を介してSOC1から発せられる熱を実装基板11に逃がすことができるため、発熱量が多いSOC1の放熱効果を高めることができる。

[0076]

さらに、SIP7はチップ積層型の半導体装置であるため、搭載IC数を増やすことができる。

[0077]

なお、本実施の形態のSIP7において、図1に示す構造では、第1配線基板3と第2 配線基板4の間にレジン10が充填されている場合を説明したが、レジン10は必ずしも 充填されていなくてもよい。

[0078]

また、第2配線基板4の第2上面4aにフリップチップ接続されたSDRAM2について、図1に示す構造では、フリップチップ接続部にアンダーフィルが充填されていない構造の場合を説明したが、フリップチップ接続部にアンダーフィルが充填されていてもよい。特に、SDRAM2がウェハレベルシーエスピー(WLCSP)に組み込まれた半導体チップである場合には、フリップチップ接続部の各ボールが小さいため、その接続強度を高めるためにもアンダーフィルを充填する方が好ましい。

[0079]

次に、本実施の形態の変形例について説明する。

[0800]

図 5 は本発明の実施の形態の第 1 変形例の半導体装置の回路構造を示すブロック図、図 6 は図 5 に示す半導体装置に組み込まれるメタル層における配線パターンの一例を示す平面図である。

[0081]

図5及び図6に示す第1変形例は、図3及び図4のSIP7と同様の構造のSIP13を示すものであり、第2配線基板4の第2メタル層4cの共通パターン4fが、SOC1のGND1(SOC1用GNDランド4p)と電気的に分離されている場合であり、第2メタル層4cにおける四角形の広域面積の共通パターン4fが配線部4mを介して第1配線基板3のGND端子のみと電気的に接続されているか、もしくは配線部4mを介してNC(Non Connect)端子に接続されている。

[0082]

50

10

20

30

20

30

40

50

この第1変形例のSIP13によっても、SOC1から発せられる図2に示す熱の放熱経路12aと、SDRAM2から発せられる熱の放熱経路12bとを分けることができ、図1~図4に示すSIP7と同様の効果を得ることができる。

#### [0083]

次に、図7は本発明の実施の形態における第2変形例の半導体装置の構造を示す断面図、図8は本発明の実施の形態における第3変形例の半導体装置の構造を示す断面図、図9は本発明の実施の形態における第4変形例の半導体装置の構造を示す断面図である。

#### [0084]

まず、図7に示す第2変形例は、上段の第2配線基板4上に搭載されたSDRAM2の第2配線基板4との電気的接続をワイヤ接続としたSIP15であり、SDRAM2と第2配線基板4とが金線等のワイヤ14によって電気的に接続されている。さらに、SDRAM2がワイヤ接続であるため、SDRAM2の周囲と複数のワイヤ14とが他のレジン16によって封止されている。

# [ 0 0 8 5 ]

この第2変形例のSIP15によっても、SOC1から発せられる図2に示す熱の放熱経路12aと、SDRAM2から発せられる熱の放熱経路12bとを分けることができ、図1~図4に示すSIP7と同様の効果を得ることができる。

#### [0086]

次に、図8に示す第3変形例は、下段の第1配線基板3上に搭載されたSOC1の第1配線基板3との電気的接続をワイヤ接続としたSIP17であり、SOC1と第1配線基板3とが金線等のワイヤ14によって電気的に接続されている。さらに、SOC1がワイヤ接続であるため、SOC1の周囲と複数のワイヤ14とが他のレジン16によって封止されており、この他のレジン16の外側の上下の基板間の領域、すなわち複数の第2ボール電極6がレジン10によって封止されている。

#### [0087]

なお、SOC1がワイヤ接続となったため、SOC1の上方が他のレジン16によって覆われ、その結果、SOC1から上段の第2配線基板4への熱の伝わり方が弱くなることが懸念される。そこで、第1配線基板3のSOC1と対応する領域に複数の放熱用ビア3 f を形成し、この複数の放熱用ビア3 f を介してSOC1から発せられる熱の一部を外部接続端子である第1ボール電極5に伝えて、実装基板11に熱を逃がすことができる。

#### [0088]

したがって、この第3変形例のSIP17によっても、SOC1から発せられる図2に示す熱の放熱経路12aと、SDRAM2から発せられる熱の放熱経路12bとを分けることができ、図1~図4に示すSIP7と同様の効果を得ることができる。

# [0089]

次に、図9に示す第4変形例は、下段の第1配線基板3上に搭載されたSOC1の第1配線基板3との電気的接続をワイヤ接続とするとともに、上段の第2配線基板4上に搭載されたSDRAM2の第2配線基板4との電気的接続もワイヤ接続としたSIP18である。すなわち、下段のSOC1も上段のSDRAM2も両チップともワイヤ接続としたものであり、SOC1と第1配線基板3とが、及びSDRAM2と第2配線基板4とがそれぞれ金線等のワイヤ14によって電気的に接続されている。

#### [0090]

また、SOC1及びSDRAM2がワイヤ接続であるため、SOC1の周囲と複数のワイヤ14とが他のレジン16によって封止されており、この他のレジン16の外側の上下の基板間の領域、すなわち複数の第2ボール電極6がレジン10によって封止されている。同様に、SDRAM2の周囲と複数のワイヤ14とが他のレジン16によって封止されている。

# [0091]

なお、図8のSIP17と同様に、SOC1がワイヤ接続となったため、SOC1の上方が他のレジン16によって覆われ、その結果、SOC1から上段の第2配線基板4への

20

30

40

50

熱の伝わり方が弱くなることが懸念される。そこで、SIP18においても、第1配線基板3のSOC1と対応する領域に複数の放熱用ビア3fを形成し、この複数の放熱用ビア3fを介してSOC1から発せられる熱の一部を外部接続端子である第1ボール電極5に伝えて、実装基板11に熱を逃がすことができる。

[0092]

これにより、この第4変形例のSIP18によっても、SOC1から発せられる図2に示す熱の放熱経路12aと、SDRAM2から発せられる熱の放熱経路12bとを分けることができ、図1~図4に示すSIP7と同様の効果を得ることができる。

[0093]

次に、図10は本発明の実施の形態における第5変形例の半導体装置の構造を示す断面図、図11は本発明の実施の形態における第6変形例の半導体装置の構造を示す断面図である。

[0094]

まず、図10に示す第5変形例は、3つの半導体チップを積層した3段積層型のSIP19である。1段目の第1配線基板3上にSOC1がフリップチップ接続されており、さらに2段目の第2配線基板4上にSDRAM2がフリップチップ接続され、加えて3段目の第3配線基板21上にもう1つのSDRAM(第3半導体チップ)20がフリップチップ接続されている。

[0095]

また、第1配線基板3と第2配線基板4は、複数の第2ボール電極6によって電気的に接続され、さらに第2配線基板4と第3配線基板21は、複数の第3ボール電極22によって電気的に接続されている。3段目にSDRAM20をフリップチップ接続したことで、メモリの容量を増やすことができ、SIP19の性能の向上を図ることができる。

[0096]

さらに、この第5変形例のSIP19によっても、SOC1から発せられる図2に示す 熱の放熱経路12aと、SDRAM2から発せられる熱の放熱経路12bとを分けること ができ、図1~図4に示すSIP7と同様の効果を得ることができる。

[0097]

次に、図11に示す第6変形例は、図2に示す半導体装置において、第2配線基板4の 第2メタル層4cと繋がるアウタリード24が第2配線基板4の側部から露出して設けら れたSIP23である。

[0098]

すなわち、図2に示すSOC1の放熱経路12aに介在する第2配線基板4の第2メタル層4cを第2配線基板4の側部からアウタリード24として延在させて露出させ、ガルウィング状に曲げて実装基板11の電極11aに半田接続させるものである。

[0099]

これにより、SIP23において、SOC1の図2に示す放熱経路12aに加えて、SOC1から発せられる熱の一部をアウタリード24を介して実装基板11に逃がすことができ、発熱量の多いSOC1の放熱効果をさらに向上させることができる。

[0100]

また、この第6変形例のSIP23によっても、SOC1から発せられる図2に示す熱の放熱経路12aと、SDRAM2から発せられる熱の放熱経路12bとを分けることができ、図1~図4に示すSIP7と同様の効果を得ることができる。

[0101]

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記発明の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

[0102]

例えば、前記実施の形態では、半導体装置において、上段や下段の基板上に半導体チップが搭載される場合を一例として説明したが、前記半導体装置は、POP (Package On P

ackage) 等であってもよい。すなわち、基板上にBGA(Ball Grid Array)等の半導体パ ッケージを搭載し、このような半導体パッケージを搭載した基板を積層するPOP型の半 導体装置であっても適用可能である。

#### 【産業上の利用可能性】

[0103]

本発明は、複数の半導体チップが積層して成る電子装置に好適である。

#### 【符号の説明】

- [0104]

- 1 SOC(第1半導体チップ)

- 1 a 第1主面

- 1 b 第1裏面

- 1 c 第1パッド

- 1 d 第 1 バンプ電極

- 2 S D R A M (第2半導体チップ)

- 2 a 第 2 主 面

- 2 b 第 2 裏 面

- 2 c 第 2 パッド

- 2 d 第 2 バンプ電極

- 3 第1配線基板

- 3 a 第1上面

- 3 b 第1下面

- 3 c 第 1 メタル層

- 3 d 第 1 絶 縁 層

- 3 e ビア

- 3 f 放熱用ビア

- 3 g レーザービア

- 4 第2配線基板

- 4 a 第 2 上 面

- 4 b 第 2 下 面

- 4 c 第 2 メタル層 (メタル層)

- 4 d 第 2 絶 縁 層

- ソルダーレジスト 4 e

- 4 f 共通パターン

- 4g SOC用GNDランド

- 4 h SOC用電源ランド

- 4 i 信号ランド

- 4 j メモリ用GNDランド

- 4 k メモリ用電源ランド

- 4 m 配線部

- 4 n メタルプレーン層

- 4 p SOC用GNDランド

- 第 1 ボール電極 5

- 第2ボール電極

- 7 SIP(半導体装置)

- ヒートスプレッダ 8

- フィルム状接着材 9

- 10 レジン

- 1 1 実装基板

- 1 1 a 電 極

- 1 2 a , 1 2 b 放熱経路

20

10

30

40

- 1 3 SIP(半導体装置)

- 1 4 ワイヤ

- 1 5 S I P (半導体装置)

- 他のレジン 1 6

- 17,18,19 SIP(半導体装置)

- S D R A M (第3半導体チップ)

- 2 1 第3配線基板

- 2 2 第3ボール電極

- 2 3 S I P (半導体装置)

- アウタリード 2 4

【図1】 【図2】

- 1: SOC(第1半導体チップ) lb: 第1裏面 ld: 第1バンプ電極 2: SDRAM(第2半導体チップ)

- 2: SDRAM(第2半4 2b: 第2惠面 2d: 第2バンプ電極 3: 第1配線基板 3a: 第1上面 3b: 第1下面 3d: 第1絶縁層 4: 第2配線基板

- 4a:第2上面

- 4a:第2上面 4b:第2下面 4c:第2×タル層(メタル層) 4d:第2総縁層 4n:メタルプレーン層 5:第1ボール電極 6:第2ボール電極 7:SI7(半導体装置) 8:ヒートスプレッダ 9:フィルム状接着材 11:実装基板

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

# 【図11】

# フロントページの続き

# (72)発明者 諏訪 真人

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内