## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-33594 (P2008-33594A)

(43) 公開日 平成20年2月14日(2008.2.14)

| (51) Int.Cl. |       |           | F I    |       |         |    | テーマコート   | 、 (参考) |

|--------------|-------|-----------|--------|-------|---------|----|----------|--------|

| G06K         | 17/00 | (2006.01) | GO6K   | 17/00 | F       |    | 5BO11    |        |

| G06F         | 21/06 | (2006.01) | GO6F   | 12/14 | 560E    |    | 5BO17    |        |

| G06F         | 1/26  | (2006.01) | GO6F   | 1/00  | 335C    |    | 5B018    |        |

| G06F         | 12/16 | (2006.01) | GO6F   | 12/16 | 340M    |    | 5B058    |        |

|              |       |           | GO6K   | 17/00 | E       |    |          |        |

|              |       |           | 審査請求 未 | 請求    | 請求項の数 7 | ΟL | (全 23 頁) | 最終頁に続く |

(21) 出願番号 (22) 出願日 特願2006-205714 (P2006-205714) 平成18年7月28日 (2006.7.28)

(71) 出願人 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74)代理人 100082131

弁理士 稲本 義雄

(72) 発明者 村岡 如竹

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

Fターム(参考) 5B011 DA06 EA06 GG02 JB01

5B017 AA07 BB03 CA14

5B018 GA07 LA01 MA24 QA12

5B058 CA15 CA22 CA27 KA27 KA31

(54) 【発明の名称】データ記憶装置、電力制御方法、並びに、通信装置

# (57)【要約】

【課題】耐タンパ性を物理的に向上させる。

【解決手段】主電源14がオフされている場合に、電池351が電池ソケット352から取り外されたとき、主電源14または電池351によりコンデンサ355に蓄積されている電力が、タンパ監視回路105-1乃至105-6、電池電圧検知器358は、入力端子T11への入力電圧が所定の閾値以下になった状態が所定の時間継続した場合、出力端子T12からの出力電圧をHighからLowレベルに変化させ、スイッチ359をオフし、記憶部103への電力の供給を停止させる。これにより、記憶部103のRAMのデータが消去される。本発明は、リーダライタに適用できる。

【選択図】図10

#### 【特許請求の範囲】

## 【請求項1】

メモリ、および、前記メモリに格納されているデータに対する不正行為を監視する監視 手段を有するデータ記憶装置において、

前記監視手段に電力を供給する第1の電源と、

前記第1の電源から前記監視手段に電力が供給されている場合に充電され、前記第1の 電源から前記監視手段への電力の供給が停止された場合、前記監視手段に電力を供給する 蓄電手段と

を含むデータ記憶装置。

## 【請求項2】

前記メモリは、揮発性であり、

前記第1の電源は、さらに、前記メモリに電力を供給する

請求項1に記載のデータ記憶装置。

# 【請求項3】

前記蓄電手段は、さらに、前記第1の電源から前記メモリへの電力の供給が停止された 場合、前記メモリに電力を供給し、

前 記 第 1 の 電 源 か ら 前 記 メ モ リ へ の 電 力 の 供 給 が 停 止 さ れ て か ら 所 定 の 時 間 が 経 過 し た 場合、前記蓄電手段からの前記メモリへの電力の供給を停止させる電力供給制御手段を さらに含む請求項2に記載のデータ記憶装置。

## 【請求項4】

前記第1の電源は、前記監視手段に電力を供給する第2の電源がオフされた場合に前記 監視手段に電力を供給するバックアップ電源であり、

前記蓄電手段は、前記第1の電源または前記第2の電源により充電される 請求項1に記載のデータ記憶装置。

#### 【請求項5】

前記第1の電源は電池であり、前記蓄電手段はコンデンサである 請求項1に記載のデータ記憶装置。

#### 【請求項6】

メモリ、および、前記メモリに格納されているデータに対する不正行為を監視する監視 手段を有するデータ記憶装置の電力制御方法において、

電源から前記監視手段に電力が供給されている場合に蓄電手段を充電し、

前記電源から前記監視手段への電力の供給が停止された場合、前記蓄電手段から前記監 視手段に電力を供給する

電力制御方法。

## 【請求項7】

非接触ICカード機能を有する装置と通信を行う通信装置であって、前記非接触ICカード 機 能 を 有 す る 装 置 か ら 読 み 出 し た デ ー タ を 格 納 す る メ モ リ 、 お よ び 、 前 記 メ モ リ に 格 納 さ れているデータに対する不正行為を監視する監視手段を有する通信装置において、

前記監視手段に電力を供給する電源と、

前記電源から前記監視手段に電力が供給されている場合に充電され、前記電源から前記 監視手段への電力の供給が停止された場合、前記監視手段に電力を供給する蓄電手段と を含む通信装置。

【発明の詳細な説明】

#### 【技術分野】

# [ 0 0 0 1 ]

本発明は、データ記憶装置、電力制御方法、および、通信装置に関し、特に、耐タンパ 性 を 物 理 的 に 向 上 さ せ る よ う に し た デ ー タ 記 憶 装 置 、 電 力 制 御 方 法 、 お よ び 、 通 信 装 置 に 関する。

## 【背景技術】

[0002]

10

20

30

40

(3)

近年、筐体の開放や破壊などのタンパ行為を監視する監視回路を設け、メモリに記憶されているデータを保護する装置が普及してきている(例えば、特許文献1参照)。

### [0003]

そのような装置においては、主電源がオフの状態においても、タンパ行為の監視が行われるように、監視回路用にバッテリなどのバックアップ電源が設けられる場合がある。

#### [0004]

【 特 許 文 献 1 】 特 開 2 0 0 5 - 5 6 4 3 9 号 公 報

## 【発明の開示】

【発明が解決しようとする課題】

## [0005]

しかしながら、監視回路用にバックアップ電源を設けた場合、バックアップ電源が取り 外され、監視回路の動作を停止させられた上で、データの盗聴や改ざんが行われる恐れが ある。

# [0006]

本発明は、このような状況に鑑みてなされたものであり、耐タンパ性を物理的に向上させるようにするものである。

## 【課題を解決するための手段】

#### [0007]

本発明の第1の側面のデータ記憶装置は、メモリ、および、前記メモリに格納されているデータに対する不正行為を監視する監視手段を有するデータ記憶装置であって、前記監視手段に電力を供給する第1の電源と、前記第1の電源から前記監視手段に電力が供給されている場合に充電され、前記第1の電源から前記監視手段への電力の供給が停止された場合、前記監視手段に電力を供給する蓄電手段とが設けられている。

#### [00008]

前記メモリは、揮発性であり、前記第1の電源には、さらに、前記メモリに電力を供給させるようにすることができる。

#### [0009]

前記蓄電手段には、さらに、前記第1の電源から前記メモリへの電力の供給が停止された場合、前記メモリに電力を供給させ、前記第1の電源から前記メモリへの電力の供給が停止されてから所定の時間が経過した場合、前記蓄電手段からの前記メモリへの電力の供給を停止させる電力供給制御手段をさらに設けることができる。

# [0010]

前記第1の電源は、前記監視手段に電力を供給する第2の電源がオフされた場合に前記監視手段に電力を供給するバックアップ電源であり、前記蓄電手段は、前記第1の電源または前記第2の電源により充電されるようにすることができる。

#### [0011]

前記第1の電源は電池であり、前記蓄電手段はコンデンサであるようにすることができる。

## [0012]

本発明の第1の電力制御方法は、メモリ、および、前記メモリに格納されているデータに対する不正行為を監視する監視手段を有するデータ記憶装置の電力制御方法であって、電源から前記監視手段に電力が供給されている場合に蓄電手段を充電し、前記電源から前記監視手段への電力の供給が停止された場合、前記蓄電手段から前記監視手段に電力を供給する。

## [0013]

本発明の第2の側面の通信装置は、非接触ICカード機能を有する装置と通信を行う通信装置であって、前記非接触ICカード機能を有する装置から読み出したデータを格納するメモリ、および、前記メモリに格納されているデータに対する不正行為を監視する監視手段を有する通信装置において、前記監視手段に電力を供給する電源と、前記電源から前記監視手段に電力が供給されている場合に充電され、前記電源から前記監視手段への電力の供

10

20

30

00

40

給が停止された場合、前記監視手段に電力を供給する蓄電手段とが設けられている。

## [0014]

本発明の第1の側面においては、電源から監視手段に電力が供給されている場合に蓄電手段が充電され、前記電源から前記監視手段への電力の供給が停止された場合、前記蓄電手段から前記監視手段に電力が供給される。

## [0015]

本発明の第2の側面においては、電源から監視手段に電力が供給されている場合に蓄電手段が充電され、前記電源から前記監視手段への電力の供給が停止された場合、前記蓄電手段から前記監視手段に電力が供給される。

# 【発明の効果】

[0016]

本発明の第1の側面または第2の側面によれば、メモリに格納されているデータに対する不正行為を監視する監視手段に電力を供給することができる。また、本発明の第1の側面または第2の側面によれば、耐タンパ性を物理的に向上させることができる。

【発明を実施するための最良の形態】

#### [0017]

以下に本発明の実施の形態を説明するが、本発明の構成要件と、明細書または図面に記載の実施の形態との対応関係を例示すると、次のようになる。この記載は、本発明をサポートする実施の形態が、発明の詳細な説明に記載されていることを確認するためのものである。従って、発明の詳細な説明中には記載されているが、本発明の構成要件に対応する実施の形態として、ここには記載されていない実施の形態があったとしても、そのことは、その実施の形態が、その構成要件に対応するものではないことを意味するものではない。逆に、実施の形態が構成要件に対応するものとしてここに記載されていたとしても、そのことは、その実施の形態が、その構成要件以外の構成要件には対応しないものであることを意味するものでもない。

## [0018]

本発明の第1の側面のデータ記憶装置(例えば、図1の制御モジュール13)は、第1に、メモリ(例えば、図5のRAM171)、および、前記メモリに格納されているデータに対する不正行為を監視する監視手段(例えば、図5のタンパ監視回路105-1乃至105-6)を有するデータ記憶装置であって、前記監視手段に電力を供給する第1の電源(例えば、図10の電池351)と、前記第1の電源から前記監視手段に電力が供給されている場合に充電され、前記第1の電源から前記監視手段への電力の供給が停止された場合、前記監視手段に電力を供給する蓄電手段(例えば、図10のコンデンサ355)とを備える。

# [0019]

本発明の第1の側面のデータ記憶装置は、第2に、前記蓄電手段は、さらに、前記第1の電源から前記メモリへの電力の供給が停止された場合、前記メモリに電力を供給し、前記第1の電源から前記メモリへの電力の供給が停止されてから所定の時間が経過した場合、前記蓄電手段からの前記メモリへの電力の供給を停止させる電力供給制御手段(例えば、図10の電池電圧検知器358)をさらに備える。

# [0020]

本発明の第2の側面のデータ記憶装置は、第3に、前記第1の電源は、前記監視手段に電力を供給する第2の電源(例えば、図1の主電源14)がオフされた場合に前記監視手段に電力を供給するバックアップ電源であり、前記蓄電手段は、前記第1の電源または前記第2の電源により充電される。

# [0021]

本発明の第1の側面の電力制御方法は、メモリ(例えば、図5のRAM171)、および、前記メモリに格納されているデータに対する不正行為を監視する監視手段(例えば、図5のタンパ監視回路105-105-6)を有するデータ記憶装置(例えば、図1の制御モジュール13)の電力制御方法において、電源(例えば、図10の電池351)

10

20

30

40

から前記監視手段に電力が供給されている場合に蓄電手段(例えば、図10のコンデンサ355)を充電し、前記電源から前記監視手段への電力の供給が停止された場合、前記蓄電手段から前記監視手段に電力を供給する。

#### [0022]

本発明の第2の通信装置(例えば、図1のリーダライタ1)は、非接触ICカード機能を有する装置(例えば、図1のICカード2)と通信を行う通信装置であって、前記非接触ICカード機能を有する装置から読み出したデータを格納するメモリ(例えば、図5のRAM171)、および、前記メモリに格納されているデータに対する不正行為を監視する監視手段(例えば、図5のタンパ監視回路105・1乃至105・6)を有する通信装置において、前記監視手段に電力を供給する電源(例えば、図10の電池351)と、前記電源から前記監視手段に電力が供給されている場合に充電され、前記電源から前記監視手段への電力の供給が停止された場合、前記監視手段に電力を供給する蓄電手段(例えば、図10のコンデンサ355)とを備える。

[0023]

以下、図を参照して、本発明の実施の形態について説明する。

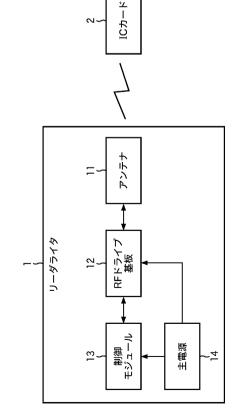

#### [0024]

図1は、本発明を適用したリーダライタの一実施の形態を示すブロック図である。本発明を適用したリーダライタ1は、アンテナ11、RFドライブ基板12、制御モジュール13、および、主電源14を含むように構成される。

## [ 0 0 2 5 ]

RFドライブ基板 1 2 は、アンテナ 1 1 を介して、非接触式のICカード 2 との間で、単一の周波数の搬送波を使用した、電磁誘導による近接通信を行う。RFドライブ基板 1 2 が使用する搬送波の周波数としては、例えば、ISM(Industrial Scientific Medical)バンドの13.56MHzなどを採用することができる。また、近接通信とは、通信する装置どうしの距離が、数10cm以内となって可能となる通信を意味し、通信する装置(の筐体)同士が接触して行う通信も含まれる。

# [0026]

制御モジュール13は、ICカード2を利用したサービスを実現するための処理を実行し、適宜、サービスで使用されるデータを、アンテナ11およびRFドライブ基板12を介して、ICカード2に書き込んだり、ICカード2から読み出したりする。また、制御モジュール13は、複数の種類のサービスの処理を並行して実行することが可能である。すなわち、例えば、電子マネーサービス、プリペイドカードサービス、各種の交通機関の乗車カードサービスなど、非接触式のICカードを利用した複数のサービスを、1台のリーダライタ1により提供することができる。

[0027]

主電源14は、RFドライブ基板12および制御モジュール13の動作に必要な電力を供給する。

[0028]

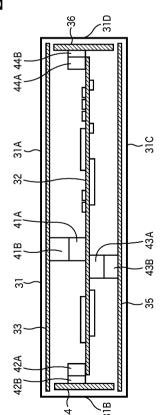

図2は、制御モジュール13の外観の構成の例を示す断面図である。

#### [0029]

制御モジュール13においては、直方体の筐体31内に、メイン基板32、および、保護基板33乃至36が設けられている。メイン基板32は、筐体31の高さ方向のほぼ中央付近に配置されている。保護基板33乃至36は、それぞれ、筐体31の面31A乃至面31Dの内面とほぼ同じ形状および面積の基板であり、筐体31の面31A乃至面31Dの内面に取り付けられている。また、図示されていないが、筐体31の残りの2面にも、保護基板33乃至36と同様に、各面の内面とほぼ同じ形状および面積の保護基板が取り付けられている。すなわち、保護基板33乃至36および図示せぬ2枚の保護基板の合計6枚の保護基板が筐体31の内面のほぼ全面を覆うように、かつ、メイン基板32を囲むように配置されている。なお、図2においては、筐体13の内面と各保護基板との間に所定の間隔が設けられているが、各保護基板を筐体31内の内面に接するように配置する

10

20

30

40

ようにしてもよい。

## [0030]

メイン基板 3 2 は、CPU (Central Processing Unit) 1 0 1 (図 5 )、RAM 1 7 1 (図 5 )などの制御モジュール 1 3 の処理を行うための各部品が搭載されている。

### [0031]

6 枚の保護基板は、図 8 などを参照して後述するように、メイン基板 3 2 上に設けられているRAM 1 7 1 に格納されているデータに対して盗聴や改ざんなどの不正行為を行うために、筐体 3 1 を開放したり、破壊するなどのタンパ行為を検出するために設けられている基板である。

#### [0032]

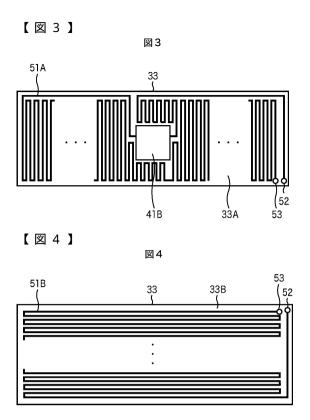

図3および図4は、保護基板33の構成の例を示している。図3は、図2においてメイン基板32側となる保護基板33の面33Aの構成の例を示し、図4は、図2において筐体31側となる保護基板33の面33Aの構成の例を示している。

## [0033]

保護基板33の形状は、上述したように、筐体31の面31Aの内面とほぼ同じ大きさおよび形状の長方形である。保護基板33の面33Aのほぼ中央には、コネクタ41Bが設けられている。また、面33Aのコネクタ41B以外の部分において、面33Aの長さまたは幅に対して十分細い電線51Aが、面33Aの長さまたは幅に対して十分狭い間隔で、長さ方向が面33Aの縦方向とほぼ平行となり、面33Aのほぼ全面を覆うように配線51Bが、面33Bの長さまたは幅に対して十分狭い間隔で、長さ方向が面33A電線51Aの長さ方向とほぼ直交する面33Bの横方向とほぼ平行となり、面33Bのほぼ全面を覆うように配線されている。また、電線51Aと電線51Bとは、貫通ビア52および53により接続されることにより、1本の電線を構成している。すなわち、面33Aとで33Bの両面を合わせて、保護基板33のほぼ全面にほぼ格子状に1本の電線が配線されている。

# [0034]

なお、以下、適宜、電線51Aと電線51Bとを合わせて、電線51と称する。

## [0035]

図示および詳細な説明は省略するが、保護基板33以外の他の5枚の保護基板についても、保護基板33と同様に、各基板の両面を合わせて、各基板のほぼ全面にほぼ格子状に1本の電線が配線されている。すなわち、筐体31の各面の長さまたは幅に対して十分独い電線が、筐体31の各面の長さまたは幅に対して十分狭い間隔で筐体31のほぼ全面を覆うように配線されている。従って、筐体31に穴を開けるなどの破壊行為が行われた場合、筐体31のほぼ全面を覆っている電線の一部がほぼ確実に断線される。

## [0036]

なお、各保護基板において、電線をできる限り細くし、隣接する電線の間隔をできる限り狭くするようにすることが望ましい。

## [0037]

図2に戻り、メイン基板32と保護基板33とは、コネクタ41Aおよび41Bにより電気的に接続されており、メイン基板32と保護基板34とは、コネクタ42Aおよび42Bにより電気的に接続されており、メイン基板32と保護基板35とは、コネクタ43Aおよび43Bにより電気的に接続されており、メイン基板32と保護基板36とは、コネクタ44Aおよび44Bにより電気的に接続されている。また、図示されていない2枚の保護基板についても、図示せぬコネクタを用いて、メイン基板32と電気的に接続されている。すなわち、筐体31の各面を開放しようとした場合、筐体31の内面に取り付けられている保護基板とメイン基板32とが電気的に切断されるようになされている。

# [0038]

なお、制御モジュール 1 3 には、図示した以外にも、RFドライブ基板 1 2 および主電源 1 4 と電気的に接続するためのコネクタなどが設けられる。

10

20

30

40

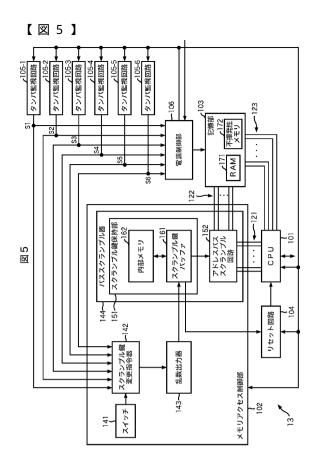

#### [0039]

図5は、図1の制御モジュール13の機能的構成を示すブロック図である。制御モジュール13は、CPU101、メモリアクセス制御部102、記憶部103、リセット回路104、タンパ監視回路105-1万至105-6、および、電源制御部106を含むように構成される。また、メモリアクセス制御部102は、スイッチ141、スクランブル鍵変更指令器142、乱数出力器143、および、バススクランブル器144を含むように構成される。さらに、バススクランブル器144は、スクランブル鍵保持部151、および、アドレスバススクランブル回路152を含むように構成される。また、スクランブル鍵保持部151は、スクランブル鍵パッファ161、および、内部メモリ162を含むように構成される。さらに、記憶部103は、RAM(Random Access Memory)171および不揮発性メモリ172を含むように構成される。

[0040]

CPU 1 0 1 とアドレスバススクランブル回路 1 5 2 とは、バス幅が n ビットのアドレスバス 1 2 1 を介して相互に接続され、アドレスバススクランブル回路 1 5 2 と記憶部 1 0 3 とは、アドレスバス 1 2 2 を介して相互に接続されている。また、CPU 1 0 1 と記憶部 1 0 3 は、バス幅がmビットのデータバス 1 2 3 を介して、相互に接続されている。

## [0041]

CPU 1 0 1 は、所定のプログラムを実行することにより、ICカード 2 を利用したサービスを実現するための処理を実行する。また、CPU 1 0 1 は、各サービスに対応したプログラムを並行して実行することができる。換言すれば、CPU 1 0 1 は、複数のサービスの処理を並行して実行することができる。

[0042]

CPU 1 0 1 は、各サービスで使用するデータを、記憶部 1 0 3 のRAM 1 7 1 または不揮発性メモリ 1 7 2 に書き込んだり、記憶部 1 0 3 のRAM 1 7 1 または不揮発性メモリ 1 7 2 から読み出したりする。なお、以下、適宜、記憶部 1 0 3 のRAM 1 7 1 または不揮発性メモリ 1 7 2 にデータを書き込むことを、単に、記憶部 1 0 3 にデータを書き込むと表現し、記憶部 1 0 3 のRAM 1 7 1 または不揮発性メモリ 1 7 2 からデータを読み出すことを、単に、記憶部 1 0 3 からデータを読み出すと表現する。

[0043]

CPU 1 0 1 は、記憶部 1 0 3 にデータを書き込む場合、データの論理的な書き込み位置を表す論理アドレスを示す論理アドレス信号を、アドレスバス 1 2 1 を介してアドレスバススクランブル回路 1 5 2 に供給するとともに、書き込むデータを含み、データの書き込みの指令を示す書き込み信号を、データバス 1 2 3 を介して記憶部 1 0 3 に供給する。また、CPU 1 0 1 は、記憶部 1 0 3 からデータを読み出す場合、データの論理的な読み出し位置を表す論理アドレスを示す論理アドレス信号を、アドレスバス 1 2 1 を介してアドレスバススクランブル回路 1 5 2 に供給するとともに、データの読み出しの指令を示す読み出し信号を、データバス 1 2 3 を介して記憶部 1 0 3 に供給する。

[0044]

メモリアクセス制御部 1 0 2 は、CPU 1 0 1 の記憶部 1 0 3 へのアクセスを制御する。

[ 0 0 4 5 ]

メモリアクセス制御部102に含まれる個々の構成要素のうち、スイッチ141は、ユーザがスクランブル鍵の変更を指令する場合に押下される。スイッチ141は、ユーザにより押下された場合、押下されたことを示す信号をスクランブル鍵変更指令器142に供給する。

# [0046]

スクランブル鍵変更指令器142は、スイッチ141が押下された場合、スクランブル鍵の変更の指令を乱数出力器143に供給する。また、スクランブル鍵変更指令器142は、タンパ監視回路105-1乃至105-6から出力される監視信号に基づいて、筐体31の破壊や開放などのタンパ行為を検出した場合、スクランブル鍵の変更の指令を乱数

10

20

30

40

出力器143に供給する。

## [0047]

乱数出力器143は、スクランブル鍵変更指令器142からスクランブル鍵の変更の指令を示す信号が供給された場合、 n ビットのビット列からなる疑似乱数を生成し、生成した疑似乱数をスクランブル鍵としてスクランブル鍵バッファ161に出力する。

# [0048]

バススクランブル器 1 4 4 は、CPU 1 0 1 から供給される論理アドレス信号により示される論理アドレスを、記憶部 1 0 3 に実際にアクセスする物理アドレスに変換する処理を行う。

## [0049]

バススクランブル器144に含まれる個々の構成要素のうち、スクランブル鍵保持部151は、乱数出力器143から供給された疑似乱数をスクランブル鍵として保持する。具体的には、スクランブル鍵保持部151のスクランブル鍵バッファ161が、乱数出力器143から供給された疑似乱数をスクランブル鍵として保持するととともに、スクランブル鍵を内部メモリ162に供給し、記憶させる。内部メモリ162は、フラッシュメモリなどの不揮発性メモリ、または、電池などによりバックアップされたRAMなどにより構成され、主電源14がオフされた状態においても、スクランブル鍵を保持し続ける。また、スクランブル鍵バッファ161は、主電源14がオフされた状態からオンされた場合、内部メモリ162に記憶されているスクランブル鍵を読み出し、保持する。さらに、スクランブル鍵パッファ161は、主電源14がオンされてから、内部メモリ162からのスクランブル鍵の読み出しが完了するまでの間、リセット指令信号をリセット回路104に供給する。

# [0050]

アドレスバススクランブル回路152は、スクランブル鍵バッファ161に保持されている鍵を用いて、CPU101から供給された論理アドレス信号により示される論理アドレスにスクランブルをかけることにより、論理アドレスを実際に記憶部103にアクセスする物理アドレスに変換する。換言すれば、アドレススバスクランブル回路152は、入力された論理アドレスにスクランブルをかけることにより、その論理アドレスに対して、物理アドレスを割り当てる。アドレスバススクランブル回路152は、アドレスバス122を介して、変換後の物理アドレスを示す物理アドレス信号を記憶部103に供給する。

# [0051]

記憶部103に含まれる個々の構成要素のうち、RAM171は、各サービスのデータや個人情報などの機密性の高いデータを格納する。RAM171に格納されているデータは、電源制御部106からの電力により保持され、電源制御部106からの電力の供給が停止された場合、消去される。

# [0052]

不揮発性メモリ172は、例えば、フラッシュメモリ、EEPROM(Electrically Erasable and Programmable Read Only Memory)、HDD(Hard Disk Drive)、MRAM(Magnetoresistive Random Access Memory,磁気抵抗メモリ)、FeRAM(Ferroelectric Random Access Memory,強誘電体メモリ)、または、OUM(Ovonic Unified Memory)などにより構成され、機密性の低いデータが格納される。

#### [0053]

RAM 1 7 1 および不揮発性メモリ 1 7 2 は、CPU 1 0 1 から書き込み信号が供給された場合、アドレスバススクランブル回路 1 5 2 から供給された物理アドレス信号により示されるRAM 1 7 1 または不揮発性メモリ 1 7 2 上の物理アドレスに、書き込み信号に含まれるデータを書き込む。また、RAM 1 7 1 および不揮発性メモリ 1 7 2 は、CPU 1 0 1 から読み出し信号が供給された場合、アドレスバススクランブル回路 1 5 2 から供給された物理アドレス信号により示されるRAM 1 7 1 または不揮発性メモリ 1 7 2 上の物理アドレスからデータを読み出し、読み出したデータを、データバス 1 2 3 を介して、CPU 1 0 1 に供給する。

10

20

30

#### [0054]

リセット回路 1 0 4 は、スクランブル鍵バッファ 1 6 1 からリセット指令信号が供給されている間、CPU 1 0 1 にリセット信号を供給し、CPU 1 0 1 の状態を初期化する。

#### [0055]

タンパ監視回路105-1乃至105-6は、図8などを参照して後述するように、筐体31の破壊や開放などのタンパ行為を監視し、監視結果を示す監視信号を電源制御部106およびスクランブル鍵変更指令器142に供給する。

## [0056]

なお、以下、タンパ監視回路 1 0 5 - 1 乃至 1 0 5 - 6 を個々に区別する必要がない場合、単に、タンパ監視回路 1 0 5 と称する。

# [0057]

電源制御部106は、図10などを参照して後述するように、主電源14からの電力の供給を受け、制御モジュール13の各部への電力の供給を制御する。また、電源制御部106は、制御モジュール13に対するタンパ行為が検出された場合、記憶部103への電力の供給を停止することにより、RAM171のデータを消去させる。

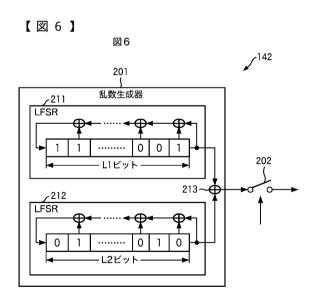

#### [0058]

図 6 は、 乱数出力器 1 4 3 の機能的構成を示すブロック図である。 乱数出力器 1 4 3 は、 乱数生成器 2 0 1 、および、スイッチ 2 0 2 を含むように構成される。

## [0059]

乱数生成器 2 0 1 は、L 1 ビットのシフトレジスタを有するLFSR(Linear Feedback Shift Register,リニアフィードバックシフトレジスタ)型乱数発生器 2 1 1、L 2 ビットのシフトレジスタを有するLFSR型乱数発生器 2 1 2、および、EXOR回路 2 1 3 を含むように構成される。

## [0060]

LFSR型乱数発生器 2 1 1 , 2 1 2 は、シフトレジスタの所定のビットの値の排他的論理和をフィードバック値としてシフトレジスタに入力する周知のLFSRの原理により構成される。乱数生成器 2 0 1 は、LFSR型乱数発生器 2 1 1 , 2 1 2 により生成される 2 つの異なるM系列の疑似乱数の排他的論理和をEXOR回路 2 1 3 によりビット毎に取ることにより、Gold系列の疑似乱数を生成する。なお、乱数生成器 2 0 1 が備えるLFSR型乱数発生器 2 1 1 , 2 1 2 の個数は、 2 個に限定されるものではなく、 3 個以上とすることも可能である

# [0061]

スイッチ 2 0 2 は、スクランブル鍵変更指令器 1 4 2 からスクランブル鍵の変更の指令を示す信号が入力された場合、オンとなり、乱数生成器 2 0 1 により生成されたGold系列の疑似乱数を示すビット列が、スイッチ 2 0 2を介してスクランブル鍵バッファ 1 6 1 に出力される。

# [0062]

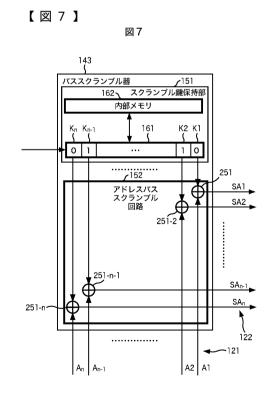

図7は、バススクランブル器144の機能的構成の詳細を示すブロック図である。

#### [0063]

スクランブル鍵バッファ161は、シリアル入力およびパラレル入出力の n ビットのシフトレジスタなどにより構成され、乱数出力器143からシリアル信号により供給された 疑似乱数をスクランブル鍵として保持する。

## [0064]

アドレスバススクランブル回路152は、アドレスバス121を介してCPU101から供給される論理アドレス信号により示されるビットA1乃至Anからなるnビットの論理アドレスと、スクランブル鍵バッファ161に保持されているビットK1乃至Knからなるnビットのスクランブル鍵との排他的論理和を、EXOR回路251-1乃至251-nによりビット毎に取ることにより、論理アドレスをビットSA1乃至SAnからなるnビットの物理アドレスに変換する。アドレスバススクランブル回路152は、アドレスバス122を介して、変換後の物理アドレスを示す物理アドレス信号を記憶部103に供給する。

10

20

30

40

20

30

40

50

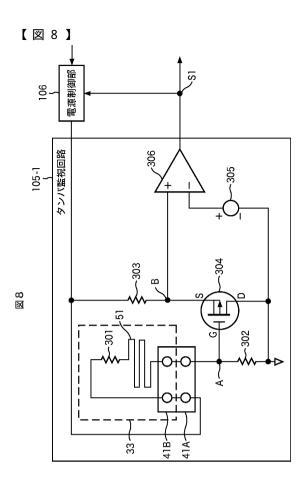

#### [0065]

図 8 は、図 5 のタンパ監視回路 1 0 5 - 1 の回路構成の例を示す図である。タンパ監視回路 1 0 5 - 1 は、保護基板 3 3 上の電線 5 1 および抵抗 3 0 1、抵抗 3 0 2、抵抗 3 0 3、p型のMOSFET (Metal Oxide Semiconductor Field Effect Transistor) 3 0 4、比較電圧源素子 3 0 5、および、電圧比較器 3 0 6 を含むように構成される。

## [0066]

MOSFET 3 0 4 のゲートは、点 A 、コネクタ 4 1 A , 4 1 B 、および、電線 5 1 を介して、抵抗 3 0 1 の一端に接続され、点 A を介して、抵抗 3 0 2 の一端に接続されている。MO SFET 3 0 4 のソースは、点 B を介して、抵抗 3 0 3 の一端、および、電圧比較器 3 0 6 のプラス端子に接続されている。MOSFET 3 0 4 のドレインは、抵抗 3 0 2 の一端であって、MOSFET 3 0 4 のゲートに接続されている一端とは異なる一端、および、比較電圧源素子 3 0 5 のマイナス端子に接続されるとともに、接地されている。すなわち、タンパ監視回路 1 0 5 - 1 は、MOSFET 3 0 4 のドレインが接地されたソースフォロワ回路により構成される。

## [0067]

また、抵抗301の一端であって、電線51に接続されている一端とは異なる一端は、コネクタ41B,41Aを介して、電源制御部106、および、抵抗303の一端であって、点Bに接続されている一端とは異なる一端に接続されている。比較電圧源素子305のプラス端子は、電圧比較器306のマイナス端子に接続されている。電圧比較器306の出力端子は、点S1を介して、図5の電源制御部106およびスクランプル鍵変更指令器142に接続されている。

#### [0068]

抵抗302の値は、抵抗301の値と比較して十分大きな値を持つ。従って、点Aの電圧、すなわち、MOSFET304のゲート電圧は、電源制御部106からの入力電圧とほぼ同じ値まで引き上げられ、MOSFET304のソース電圧は、ゲート電圧とほぼ同じ電圧となるように追従するので、点Aと点Bはほぼ同じ電圧となる。従って、電圧比較器306のプラス端子には、電源制御部106からの入力電圧とほぼ等しい電圧が入力される。比較電圧源素子305は、電源制御部106からの入力電圧の約半分の電圧を電圧比較器306のマイナス端子に入力する。電圧比較器306から出力される監視信号の電圧は、マイナス端子よりプラス端子に入力される電圧の方が高い場合、プラス端子とマイナス端子との電圧の差分を増幅した値となり、プラス端子よりマイナス端子に入力される電圧の方が高い場合、ほぼ0Vとなる。

#### [0069]

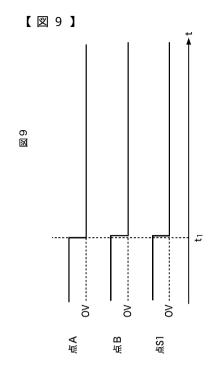

ここで、図9を参照して、タンパ監視回路105-1の動作の例について説明する。図9は、制御モジュール13の筐体31の面31Aに対して、開放や破壊などのタンパ行為が行われた場合の点A、点Bおよび点S1の電圧の変化の例を示す図である。なお、時刻t1は、タンパ行為が行われた時刻を示す。

## [0070]

時刻 t 1 以前の異常が発生していない状態においては、上述したように、点 A と点 B の電圧は、電源制御部 1 0 6 からの入力電圧とほぼ等しくなる。従って、電圧比較器 3 0 6 のプラス端子の電圧、すなわち、点 B の電圧が、マイナス端子の電圧、すなわち、比較電圧源素子 3 0 5 の電圧より高くなるため、電圧比較器 3 0 6 の出力電圧、すなわち、点 S 1 の電圧は、プラス端子とマイナス端子との電圧の差分を増幅した正の値となる。

# [ 0 0 7 1 ]

時刻 t 1 において、制御モジュール 1 3 の筐体 3 1 の面 3 1 A が開放され、コネクタ 4 1 A とコネクタ 4 1 B とが分離されたり、面 3 1 A に対して、穴を開けるなどの破壊行為が行われ、電線 5 1 に断線が生じた場合、電源制御部 1 0 6 とMOSFET 3 0 4 のゲートとの間が断線され、点 A の電圧はほぼ 0 V となる。これに伴い、図 9 に示されるように、点 B の電圧もほぼ 0 V となり、電圧比較器 3 0 6 のマイナス端子の電圧がプラス端子の電圧より高くなるため、電圧比較器 3 0 6 の出力電圧、すなわち、点 S 1 の電圧は、ほぼ 0 V と

なる。

## [0072]

従って、タンパ監視回路105-1から出力される監視信号に基づいて、筐体31の開放や破壊などのタンパ行為を検出することができる。

## [0073]

なお、タンパ監視回路105-2乃至105-6も、タンパ監視回路105-1と同様の構成を有しており、その説明は繰り返しになるので省略するが、タンパ監視回路105-1と同様に、タンパ監視回路105-2乃至105-6からの監視信号に基づいて、筐体31の開放や破壊などのタンパ行為を検出することができる。

## [0074]

従って、タンパ監視回路105-1乃至105-6からの監視信号の電圧を監視することにより、筐体31の全ての面に対する開放や破壊などのタンパ行為を確実に検出することができる。

# [0075]

なお、以下、タンパ監視回路105-2は、保護基板34上の電線を含み、タンパ監視回路105-3は、保護基板35上の電線を含み、タンパ監視回路105-4は、保護基板35上の電線を含み、タンパ監視回路105-5および105-6は、図2に図示されていない筐体31の2面にそれぞれ対応する保護基板上の電線を含むものとする。

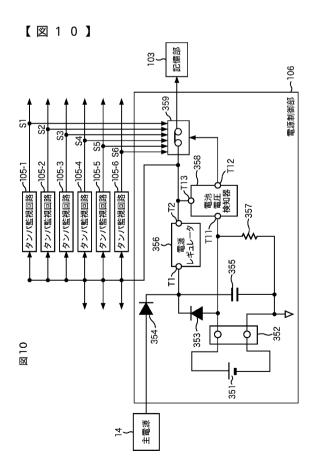

## [0076]

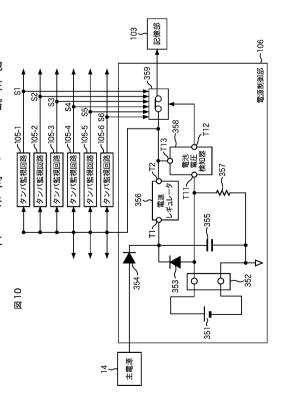

図10は、図5の電源制御部106の回路構成の例を示す図である。電源制御部106は、主電源14のバックアップ電源である電池351、電池ソケット352、ダイオード353,354、コンデンサ355、電源レギュレータ356、抵抗357、電池電圧検知器358、および、スイッチ359を含むように構成される。

#### [0077]

電池351は、電池ソケット352に装着された状態において、正極が、電池ソケット352を介して、逆流防止用のダイオード353のアノード、抵抗357の一端、および、電池電圧検知器358の入力端子T11に接続され、負極が、電池ソケット352を介して、コンデンサ355の一端、および、抵抗357の一端であって、電池351の正極に接続されている一端とは異なる一端に接続されるとともに、接地されている。ダイオード353のカソードは、逆流防止用のダイオード354のカソード、コンデンサ355の一端であって、電池351の負極に接続されている一端とは異なる一端、および、電源レギュレータ356の入力端子T1に接続されている。ダイオード354のアノードは、主電源14に接続されている。

# [0078]

電源レギュレータ356の出力端子T2は、電池電圧検知器358の電源端子T13、スイッチ359の一端、CPU101、メモリアクセス制御部102、リセット回路104、および、タンパ監視回路105-1乃至105-6に接続されている。電池電圧検知器358の出力端子T12は、スイッチ359の図示せぬ電圧検知端子に接続されている。スイッチ359の一端であって、電源レギュレータ356の出力端子T2に接続されている一端とは異なる一端は、記憶部103に接続されている。また、スイッチ359の図示せぬ電圧検知端子が、点S1乃至S6を介して、タンパ監視回路105-1乃至105-6に接続されている。

## [0079]

電源レギュレータ356は、ダイオード354を介して、主電源14から入力される電圧、または、ダイオード353を介して、電池351から入力される電圧を所定の電圧に変換し、ほぼ一定の電圧を出力端子T2から出力する。出力端子T2から出力された電圧は、CPU101、メモリアクセス制御部102、リセット回路104、タンパ監視回路105-1乃至105-6、電池電圧検知器358、および、スイッチ359を介して、記憶部103に供給される。すなわち、主電源14または電池351からの電力が、電源レギュレータ356により、その電圧が安定化されて、CPU101、メモリアクセス制御部

10

20

30

40

20

30

40

50

102、リセット回路104、タンパ監視回路105-1乃至105-6、電池電圧検知器358、および、記憶部103に供給される。従って、主電源14または電池351のいずれか一方からの電力の供給が停止されても、CPU101、メモリアクセス制御部102、リセット回路104、タンパ監視回路105-1乃至105-6、電池電圧検知器358、および、記憶部103に安定化された電力が供給される。

## [0800]

また、コンデンサ355は、主電源14または電池351により電力が供給されている場合、主電源14または電池351により所定の電圧に充電される。そして、主電源14 および電池351からの電力の供給が停止された場合、コンデンサ355に蓄えられた電力が、電源レギュレータ356を介して、CPU101、メモリアクセス制御部102、リセット回路104、タンパ監視回路105-1乃至105-6、電池電圧検知器358、および、スイッチ359を介して、記憶部103に供給される。コンデンサ355は、例えば、スーパーキャパシタ(電気二重層キャパシタ)により構成され、CPU101、メモリアクセス制御部102、リセット回路104、タンパ監視回路105-1乃至105-6、電池電圧検知器358、および、記憶部103に所定の時間(例えば、30~40分)以上の電力の供給が可能な蓄電容量を持つ。

## [0081]

電池電圧検知器 3 5 8 は、入力端子T11 に入力される電圧、すなわち、電池 3 5 1 により抵抗 3 5 7 に印加される電圧を検知することにより、電池 3 5 1 の取り外しを検出する。電池電圧検知器 3 5 8 は、入力端子T11 の電圧が所定の閾値以下になった場合、内部の図示せぬカウンタを用いて時間の計測を開始し、入力端子T11 の電圧が閾値以下の状態が所定の時間継続した場合、出力端子T12 の電圧をHighレベル(例えば、5 V)からLowレベル(例えば、0 V)に変化させる。

#### [0082]

スイッチ359は、タンパ監視回路105-1乃至105-6からの監視信号、および、電池電圧検知器358の出力信号の電圧のうち1つでも所定の閾値以下になった場合、オフされ、電源制御部106から記憶部103への電力の供給が停止される。

#### [0083]

ここで、図11を参照して、電源制御部106の動作の例を説明する。図11は、主電源14がオフされており、かつ、タンパ監視回路105-1乃至105-6によりタンパ行為が検出されていない状態において、電池351が電池ソケット352から取り外された場合の電池電圧検知器358の端子T11,T12、および、電源制御部106から記憶部103への出力電圧の変化の例を示す図である。なお、時刻t11は、電池351が電池ソケット352から取り外された時刻を示す。

# [ 0 0 8 4 ]

時刻 t 1 1 以前の電池 3 5 1 が取り付けられた状態においては、電池 3 5 1 により、電池電圧検知器 3 5 8 の入力端子 T 1 1 に正の電圧が入力され、出力端子 T 1 2 からHighレベルの電圧がスイッチ 3 5 9 に入力される。また、タンパ監視回路 1 0 5 - 1 乃至 1 0 5 - 6 によりタンパ行為が検出されておらず、タンパ監視回路 1 0 5 - 1 乃至 1 0 5 - 6 から正の電圧がスイッチ 3 5 9 に入力されているため、スイッチ 3 5 9 はオンの状態となり、電源レギュレータ 3 5 6 の出力端子 T 2 から出力された電力が、スイッチ 3 5 9を介して、記憶部 1 0 3 に供給される。また、このとき、電源レギュレータ 3 5 6 の出力端子 T 2 から出力された電力は、CPU 1 0 1、メモリアクセス制御部 1 0 2、リセット回路 1 0 4、タンパ監視回路 1 0 5 - 1 乃至 1 0 5 - 6、および、電池電圧検知器 3 5 8 にも供給される。

# [0085]

時刻 t 1 1 において、電池 3 5 1 が電池ソケット 3 5 2 から取り外された場合、電池電圧検知器 3 5 8 の入力端子 T 1 1 に入力される電圧が、ほぼ 0 V となり、電池電圧検知器 3 5 8 は、内部のカウンタを用いて、時間の計測を開始する。また、コンデンサ 3 5 5 が放電を開始し、コンデンサ 3 5 5 に蓄積されている電力が、電源レギュレータ 3 5 6 を介

20

30

40

50

して、CPU 1 0 1、メモリアクセス制御部 1 0 2、リセット回路 1 0 4、タンパ監視回路 1 0 5 - 1 乃至 1 0 5 - 6、および、電池電圧検知器 3 5 8 に供給される。

### [0086]

時刻 t 1 1 において電池電圧検知器 3 5 8 が時間の計測を開始してから、所定の時間 T aが経過した時刻 t 1 2 において、電池電圧検知器 3 5 8 は、出力端子 T 1 2 の電圧をHig hレベルからLowレベルに変化させる。これにより、スイッチ 3 5 9 がオフされ、記憶部 1 0 3 への電力の供給が停止される。これにより、記憶部 1 0 3 のRAM 1 7 1 に記憶されているデータが消去される。

# [0087]

なお、時刻 t 1 2 以降も、CPU 1 0 1、メモリアクセス制御部 1 0 2、リセット回路 1 0 4、タンパ監視回路 1 0 5 - 1 乃至 1 0 5 - 6、および、電池電圧検知器 3 5 8 には、電源レギュレータ 3 5 6 を介して、コンデンサ 3 5 5 から電力が継続して供給される。従って、電池 3 5 1 が取り外されても、タンパ監視回路 1 0 5 - 1 乃至 1 0 5 - 6 によるタンパ行為の監視が継続して行われる。

#### [0088]

なお、電池電圧検知器 3 5 8 は、時間 T a の間に電池 3 5 1 が取り付けられ、入力端子 T 1 1 に入力される電圧が、所定の閾値を超えた場合、内部のカウンタによる時間の計測を停止する。従って、時間 T a を適切に設定することにより、主電源 1 4 をオフした状態においても、RAM 1 7 1 のデータを消去させることなく、電池 3 5 1 を交換することができる。なお、電池 3 5 1 の交換を考慮しなくてもよい場合、時間 T a を設けずに、時刻 t 1 1 において、スイッチ 3 5 9 をオフするようにしてもよい。

#### [ 0 0 8 9 ]

次に、図12乃至図14を参照して、リーダライタ1の処理を説明する。

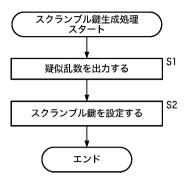

#### [0090]

まず、図12のフローチャートを参照して、リーダライタ1により実行されるスクランブル鍵生成処理について説明する。なお、この処理は、例えば、ユーザが、スイッチ14 1を押下したとき開始される。

#### [0091]

ステップS1において、乱数出力器143は、疑似乱数を出力する。具体的には、スイッチ141は、押下されたことを示す信号をスクランブル鍵変更指令器142に供給する。スクランブル鍵変更指令器142は、スクランブル鍵の変更の指令を示す信号をスイッチ202に供給し、スイッチ202をオンさせる。乱数生成器201は、リーダライタ1の主電源14がオンになっている間、常に疑似乱数を生成しており、スイッチ202がオンされることにより、スイッチ202を介して、乱数生成器201からスクランブル鍵バッファ161への疑似乱数の出力が開始される。スイッチ202は、乱数生成器201から疑似乱数がnビット出力されたとき、オフとなる。

# [0092]

ステップS2において、バススクランブル器144は、スクランブル鍵を設定し、スクランブル鍵生成処理は終了する。具体的には、スクランブル鍵バッファ161は、乱数出力器143から供給されたnビットのビット列からなる疑似乱数をスクランブル鍵として内部のレジスタに保持する。また、スクランブル鍵バッファ161は、内部メモリ162にスクランブル鍵を供給し、記憶させる。すなわち、スクランブル鍵が内部メモリ162にバックアップされる。

# [0093]

これにより、簡単に、各制御モジュール13に対して、それぞれ値が異なり、かつ、予測が困難なスクランブル鍵を設定することができる。なお、このスクランブル鍵設定処理は、例えば、リーダライタ1を工場から出荷する前に行われる。

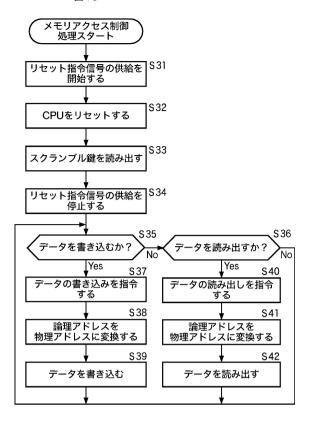

#### [0094]

次に、図13のフローチャートを参照して、リーダライタ1により実行されるメモリアクセス制御処理を説明する。なお、この処理は、例えば、リーダライタ1の主電源14が

オンされたとき開始される。

## [0095]

ステップ S 3 1 において、スクランブル鍵バッファ 1 6 1 は、リーダライタ 1 の主電源 1 4 がオンされることにより、リセット回路 1 0 4 へのリセット指令信号の供給を開始する。

## [0096]

ステップ S 3 2 において、リセット回路 1 0 4 は、CPU 1 0 1 へのリセット信号の供給を開始し、CPU 1 0 1 をリセットする。これにより、CPU 1 0 1 の状態が初期化される。

# [0097]

ステップS33において、スクランブル鍵バッファ161は、内部メモリ162に保持されているスクランブル鍵を読み出す。スクランブル鍵バッファ161は、読み出したスクランブル鍵を内部のレジスタに保持する。

#### [0098]

ステップ S 3 4 において、スクランブル鍵バッファ 1 6 1 は、リセット回路 1 0 4 へのリセット指令信号の供給を停止する。これに伴い、リセット回路 1 0 4 は、CPU 1 0 1 へのリセット信号の供給を停止し、CPU 1 0 1 は、プログラムの実行を開始する。

## [0099]

ステップS35において、CPU101は、データを書き込むかを判定する。CPU101は、実行中のプログラムにおいて、次の処理がデータの書き込みを行う処理でない場合、データを書き込まないと判定し、処理はステップS36に進む。

#### [0100]

ステップS36において、CPU101は、データを読み出すかを判定する。CPU101は、実行中のプログラムにおいて、次の処理がデータの読み出しを行う処理でない場合、データを読み出さないと判定し、処理はステップS35に戻る。

#### [0101]

その後、ステップS35において、データを書き込むと判定されるか、ステップS36においてデータを読み出すと判定されるまで、ステップS35およびS36の処理が繰り返し実行される。

## [0102]

ステップS35においてCPU101は、実行中のプログラムにおいて、次の処理がデータの書き込みを行う処理である場合、データを書き込むと判定し、処理はステップS37に進む。

#### [0103]

ステップS37において、CPU101は、データの書き込みを指令する。具体的には、CPU101は、データの論理的な書き込み位置を表す論理アドレスを示す論理アドレス信号を、アドレスバス121を介してアドレスバススクランブル回路152に供給するとともに、書き込むデータを含み、データの書き込みの指令を示す書き込み信号を、データバス123を介して記憶部103に供給する。

## [0104]

ステップS38において、アドレスバススクランブル回路152は、論理アドレスを物理アドレスに変換する。具体的には、アドレスバススクランブル回路152は、論理アドレス信号により示される論理アドレスとスクランブル鍵バッファ161に保持されているスクランブル鍵との排他的論理和をビット毎に取り、論理アドレスにスクランブルをかけることにより、論理アドレスを物理アドレスに変換する。アドレスバススクランブル回路152は、変換後の物理アドレスを示す物理アドレス信号を、アドレスバス122を介して記憶部103に供給する。

## [0105]

ステップ S 3 9 において、記憶部 1 0 3 は、データを書き込む。具体的には、RAM 1 7 1 または不揮発性メモリ 1 7 2 は、物理アドレス信号に示されるRAM 1 7 1 または不揮発性メモリ 1 7 2 上の物理アドレスに、CPU 1 0 1 から供給された書き込み信号に含まれる

10

20

30

40

20

30

40

50

データを書き込む。これにより、CPU 1 0 1 から連続した論理アドレスへのデータの書き込みが指令されても、実際には、ランダムに配置されるようにRAM 1 7 1 または不揮発性メモリ 1 7 2 に将せまれるため、RAM 1 7 1 または不揮発性メモリ 1 7 2 に格納されているデータの内容を解析したり、改ざんしたりすることが困難となる。

[0106]

その後、処理はステップS35に戻り、ステップS35以降の処理が実行される。

[ 0 1 0 7 ]

ステップS36において、CPU101は、実行中のプログラムにおいて、次の処理がデータの読み出しを行う処理である場合、データを読み出すと判定し、処理はステップS4 0に進む。

[0108]

ステップS40において、CPU101は、データの読み出しを指令する。具体的には、CPU101は、データの論理的な読み出し位置を表す論理アドレスを示す論理アドレス信号を、アドレスバス121を介してアドレスバススクランブル回路152に供給するとともに、データの読み出しの指令を示す読み出し信号を、データバス123を介して記憶部103に供給する。

[0109]

ステップS41において、上述したステップS38の処理と同様に、論理アドレスが物理アドレスに変換され、変換後の物理アドレスを示す物理アドレス信号が、アドレスバス122を介して、アドレスバススクランブル回路152から記憶部103に供給される。

[0110]

ステップS42において、記憶部103は、データを読み出す。具体的には、RAM17 1または不揮発性メモリ172は、物理アドレス信号により示される物理アドレスに記憶されているデータを読み出し、読み出したデータを、データバス123を介して、CPU1 01に供給する。

[0111]

その後、処理はステップS35に戻り、ステップS35以降の処理が実行される。

[0112]

以上のように、各制御モジュール13に異なるスクランブル鍵を簡単に設定することができるため、たとえ、1台の制御モジュール13に設定されているスクランブル鍵が解析されたとしても、そのスクランブル鍵を用いて、他の制御モジュール13のRAM171および不揮発性メモリ172に記憶されているデータの解析や改ざんをすることができない。従って、データの流出や改ざんの被害を最小限に抑えることができる。

[ 0 1 1 3 ]

また、疑似乱数の生成方法およびアドレスのスクランブル方法については、従来の技術をそのまま使用することができ、新たに複雑な回路を設ける必要がなく、スクランブル鍵の変更の指令を入力する以外にユーザの手間も増えないため、簡単にRAM 1 7 1 および不揮発性メモリ 1 7 2 上のデータのセキュリティを向上させることができる。

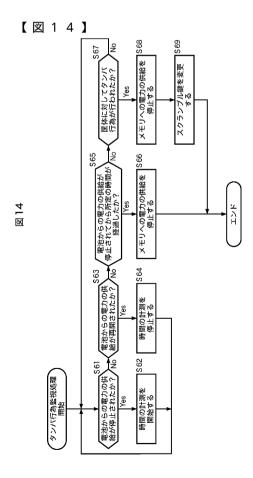

[0114]

次に、図14のフローチャートを参照して、リーダライタ1により実行されるタンパ行 為監視処理を説明する。なお、この処理は、例えば、工場出荷後に、リーダライタ1の使 用が開始されたとき開始される。

[0115]

ステップS61において、電池電圧検知器358は、電池351からの電力の供給が停止されたかを判定する。図10および図11を参照して上述したように、電池電圧検知器358は、例えば、電池351が電池ソケット352から取り外され、入力端子T11の電圧が所定の閾値を超える状態から閾値以下になった場合、電池351からの電力の供給が停止されたと判定し、処理はステップS62に進む。

[0116]

ステップS62において、電池電圧検知器358は、内部の図示せぬカウンタを用いて

20

30

40

50

、時間の計測を開始する。

[0117]

その後、処理はステップS61に戻り、ステップS61以降の処理が実行される。

[0118]

ステップS61において、電池電圧検知器358は、入力端子T11の電圧が閾値を超えている場合、または、入力端子T11の電圧が閾値以下の状態が継続している場合、電池351から電力が供給されている、または、電池351からの電力の供給が停止された状態が継続していると判定し、処理はステップS63に進む。

[0119]

ステップS63において、電池電圧検知器358は、電池351からの電力の供給が再開されたかを判定する。具体的には、電池電圧検知器358は、入力端子T11の電圧が 閾値以下の状態から閾値を超える状態に変化した場合、電池351からの電力の供給が再開されたと判定し、処理はステップS64に進む。

[0120]

ステップS64において、電池電圧検知器358は、内部の図時せぬカウンタによる時間の計測を停止する。

[0121]

その後、処理はステップS61に戻り、ステップS61以降の処理が実行される。

[0122]

ステップS63において、電池電圧検知器358は、入力端子T11の電圧が閾値を超える状態が継続している場合、または、閾値以下の状態が継続している場合、電池351から電力が供給されている状態が継続している、または、電池351からの電力の供給が停止された状態が継続していると判定し、処理はステップS65に進む。

[ 0 1 2 3 ]

ステップS65において、電池電圧検知器358は、電池351からの電力の供給が停止されてから所定の時間が経過したかを判定する。電池電圧検知器358は、内部のカウンタの値が所定の時間以上になっている場合、電池351からの電力の供給が停止されてから所定の時間が経過したと判定し、処理はステップS66に進む。

[0124]

ステップS66において、電源制御部106は、メモリへの電力の供給を停止し、タンパ行為監視処理は終了する。具体的には、電池電圧検知器358は、出力端子T12の電圧をHighレベルからLowレベルに変化させる。これにより、スイッチ359がオフされ、電源レギュレータ356から記憶部103への電力の供給が停止される。これにより、記憶部103のRAM171に記憶されているデータが消去される。

[0125]

ステップS65において、電池電圧検知器358は、内部のカウンタの値が所定の時間未満である場合、電池351からの電力の供給が停止されてから所定の時間が経過していない、または、電池351からの電力の供給が停止されていないと判定し、処理はステップS67に進む。

[0126]

ステップS67において、電源制御部106は、筐体31に対してタンパ行為が行われたかを判定する。具体的には、図8および図9を参照して上述したように、筐体31の開放や破壊などにより、電源制御部106とタンパ監視回路105内のMOSFET(図8のタンパ監視回路105・1の場合、MOSFET304)のゲートとの間が断線された場合、断線されたタンパ監視回路105から出力される監視信号の電圧がほぼ0Vになる。電源制御部106は、タンパ監視回路105・1乃至105・6の監視信号の電圧のうち1つでも所定の閾値以下になった場合、筐体31に対してタンパ行為が行われたと判定し、処理はステップS68に進む。

[ 0 1 2 7 ]

ステップS68において、電源制御部106は、メモリへの電力の供給を停止する。具

20

30

40

50

体的には、タンパ監視回路105-1万至105-6の監視信号の電圧のうち1つでも所定の閾値以下になることにより、スイッチ359がオフされ、電源レギュレータ356から記憶部103への電力の供給が停止される。これにより、記憶部103のRAM171に記憶されているデータが消去される。

## [0128]

ステップS69において、メモリアクセス制御部102は、スクランブル鍵を変更し、タンパ行為監視処理は終了する。具体的には、スクランブル鍵変更指令器142は、タンパ監視回路105・1乃至105・6の監視信号の電圧のうち1つでも所定の閾値以下になった場合、スクランブル鍵の変更の指令を示す信号を乱数出力器143のスイッチ202に供給し、スイッチ202をオンさせる。スイッチ202がオンされることにより、スイッチ202を介して、乱数生成器201からスクランブル鍵バッファ161への疑似乱数の出力が開始される。スイッチ202は、乱数生成器201から疑似乱数がnビット出力されたとき、オフとなる。スクランブル鍵バッファ161は、乱数出力器143から供給されたnビットのビット列からなる疑似乱数を新たなスクランブル鍵として内部のレジスタに保持する。また、スクランブル鍵バッファ161は、内部メモリ162にスクランブル鍵を供給し、記憶させる。

## [0129]

なお、ステップS69において、アドレスのスクランブルが行われないためスクランブル鍵として用いられることがない、全て0からなる値を強制的にスクランブル鍵に設定するようにしてもよい。

#### [ 0 1 3 0 ]

ステップS67において、筐体31に対してタンパ行為が行われていないと判定された 場合、処理はステップS61に戻り、ステップS61以降の処理が実行される。

#### [ 0 1 3 1 ]

このようにして、例えば、タンパ監視回路105-1乃至105-6の動作を停止させる目的で電池351が取り外されても、タンパ監視回路105-1乃至105-6が継続して動作するので、制御モジュール13の耐タンパ性を向上させることができる。また、電池351が取り外されてから所定の時間が経過した場合、RAM171のデータが消去されるので、耐タンパ性をさらに向上させることができる。

## [ 0 1 3 2 ]

さらに、筐体 3 1 の開放や破壊などのタンパ行為が確実に検出され、タンパ行為が検出された場合、RAM 1 7 1 のデータが消去されるため、さらに耐タンパ性を向上させることができる。

# [0133]

また、タンパ行為が検出された場合、スクランブル鍵が変更されるため、たとえRAM 17 1のデータが消去されなくても、ICE(In-Circuit Emulator)などを用いたRAM 17 1上のデータの解析を困難にすることができる。

## [0134]

なお、以上の説明では、揮発性のメモリであるRAM 1 7 1 のデータを保護する例を示したが、例えば、電池 3 5 1 の取り外し、筐体の開放や破壊などが検出された場合に、不揮発性のメモリのデータを消去または破壊することにより、不揮発性のメモリのデータを保護するようにすることも可能である。なお、揮発性メモリのデータを消去する場合、不揮発性メモリのデータを消去する場合と比較して、CPU等のプロセッサを動作させる必要がないため、より少ない電力でデータを消去することができる。従って、コンデンサ 3 5 5 の容量を低く抑えることができる。

# [0135]

また、保護基板を、図3に示されるような単層構造ではなく、多層構造とするようにして、各層に配線のパターンを設けるようにしてもよい。

## [0136]

さらに、保護基板上の電線の配線パターンは、上述した例に限定されるものではなく、

筐体31の面の長さまたは幅に対して十分細い電線が、筐体31の面の長さまたは幅に対して十分狭い間隔で前記筐体のほぼ全面を覆うように配線されるようにすればよい。

### [0137]

また、必ずしも保護基板上に電線を設ける必要はなく、例えば、筐体31の内面上に設けたり、筐体の外面と内面との間に設けるようにしてもよい。

#### [ 0 1 3 8 ]

さらに、本発明の実施の形態においては、制御モジュール13を、主電源14を用いずに電池351のみで動作させるようにすることも可能である。

## [0139]

また、本発明の実施の形態における電池 3 5 1 の取り外しに対する対策は、上述したタンパ監視回路 1 0 5 - 1 乃至 1 0 5 - 6 に限らず、動作させるために電力の供給が必要なタンパ監視回路、例えば、誤動作を目的にした熱による攻撃を監視する温度監視回路などに対して有効である。

# [0140]

さらに、以上の説明では、保護基板ごとにタンパ監視回路105を設けるようにしたが、例えば、複数の保護基板の電線を直列に接続することにより、タンパ監視回路の数を削減するようにしてもよい。

## [0141]

また、電池351の取り外しが検出された場合、タンパ監視回路105によりタンパ行為が検出された場合と同様に、スクランブル鍵を変更するようにしてもよい。

#### [0142]

さらに、以上の説明では、Gold系列の疑似乱数をスクランブル鍵に用いる例を示したが、スクランブル鍵に用いる乱数または疑似乱数は上述した例に限定されるものではなく、例えば、LFSRを1個だけ備えたM系列の疑似乱数を用いたり、熱雑音を利用した物理乱数を用いるようにしてもよい。

# [0143]

また、アドレスにスクランブルをかける方法も上述した例に限定されるものではなく、 乱数または疑似乱数により設定されたスクランブル鍵を用いた他の方法を適用するように してもよい。

# [0144]

さらに、以上の説明では、リーダライタ1と通信する相手としてICカード2を例に挙げたが、もちろん、リーダライタ1は、非接触ICカード機能を有する装置、例えば、非接触ICカード機能を有する携帯電話機、携帯情報端末(Personal Digital Assistants)、時計、コンピュータなどと通信することが可能である。

# [ 0 1 4 5 ]

また、図5のメモリアクセス制御部102を、リーダライタ以外の、メモリのデータを 読み書きする他の装置に適用することも可能である。

## [0146]

さらに、本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能である。

# 【図面の簡単な説明】

#### [0147]

- 【図1】本発明を適用したリーダライタの一実施の形態を示すブロック図である。

- 【図2】図1の制御モジュールの外観の構成の例を示す断面図である。

- 【図3】図2の保護基板の一つの面の構成の例を示す図である。

- 【図4】図2の保護基板の他の面の構成の例を示す図である。

- 【図5】図1の制御モジュールの機能的構成を示すブロック図である。

- 【図6】図5の乱数出力器の機能的構成を示すブロック図である。

- 【 図 7 】 図 5 のバススクランブル器の機能的構成の詳細を示すブロック図である。

- 【図8】図5のタンパ監視回路の構成の例を示す図である。

40

10

20

30

【図9】図5のタンパ監視回路の動作の例を説明するための図である。

【図10】図5の電源制御部の回路の構成の例を示す図である。

【図11】図5の電源制御部の動作の例を説明するための図である。

【図12】図1のリーダライタにより実行されるスクランブル鍵生成処理を説明するためのフローチャートである。

【図13】図1のリーダライタにより実行されるメモリアクセス制御処理を説明するためのフローチャートである。

【図14】図1のリーダライタにより実行されるタンパ行為監視処理を説明するためのフローチャートである。

# 【符号の説明】

# [0148]

1 リーダライタ , 2 ICカード , 1 3 制御モジュール , 1 4 主電源 , 3 1 筐体 , 3 2 メイン基板 , 3 3 乃至 3 6 保護基板 , 4 1 乃至 4 4 コネクタ , 5 1 電線 , 1 0 1 CPU , 1 0 2 メモリアクセス制御部 , 1 0 3 記憶部 , 1 0 5 タンパ監視回路 , 1 0 6 電源制御部 , 1 4 2 スクランブル鍵変更指令器 , 1 4 3 乱数出力器 , 1 4 4 バススクランブル器 , 1 5 1 スクランブル鍵保持部 , 1 5 2 アドレスバススクランブル回路 , 1 6 1 スクランブル鍵バッファ , 1 6 2 内部メモリ , 1 7 1 RAM , 1 7 2 不揮発性メモリ , 2 0 1 乱数生成器 , 2 0 2 スイッチ , 3 0 1 乃至 3 0 3 抵抗 , 3 0 4 MOSFET , 3 0 5 比較電圧源素子 , 3 0 6 電圧比較器 , 3 5 1 電池 , 3 5 2 電池ソケット , 3 5 5 コンデンサ , 3 5 6 電源レギュレータ , 3 5 8 電池電圧検知器 , 3 5 9 スイッチ

【図1】

【図2】

10

【図12】 図12

【図13】 図13

フロントページの続き

(51) Int.CI. F I テーマコード (参考)

G 0 6 K 17/00 S