# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

HO3F 3/45 (2006.01) HO4L 25/03 (2006.01)

(52) CPC특허분류

**HO3F 3/45744** (2013.01) **HO3F 3/45183** (2013.01)

(21) 출원번호 10-2022-0039174

(22) 출원일자2022년03월29일

심사청구일자 없음

(11) 공개번호 10-2023-0140255

(43) 공개일자 2023년10월06일

(71) 출원인

#### 삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

### 서울시립대학교 산학협력단

서울특별시 동대문구 서울시립대로 163 (전농동, 서울시립대학교내)

(72) 발명자

#### 유수환

서울특별시 동대문구 망우로12다길 6, 102호 (휘 경동)

#### 김요한

서울특별시 동대문구 망우로18다길 19, 304호 (휘 경동)

(뒷면에 계속)

(74) 대리인

리앤목특허법인

전체 청구항 수 : 총 12 항

# (54) 발명의 명칭 차동 출력 신호의 오프셋 보상이 가능한 차동 증폭기 및 이를 포함하는 적응형 연속 시간 선형 등화기

#### (57) 요 약

본 발명은 차동 증폭기 및 이를 포함하는 적응형 연속 시간 선형 등화기에 관한 것이다. 본 발명에 따른 연속 시간 선형 등화기는 입력단 및 출력단을 구비한 CTLE 셀, 차동 출력 신호를 각각 로우 패스 필터링하여 얻어진 저대역 차동 신호를 각각 출력하는 로우 패스 필터, 및 저대역 차동 신호 차이를 증폭하여 제어 전압으로 출력하는 오차 증폭기를 포함하되, CTLE 셀은 입력단 및 출력단을 각각 구비한 제1 및 제2 트랜지스터들, 및 제어 전압에 따라 공급 전압원과 출력단 사이의 전위차를 조절하는 오프셋 보상부를 포함하는 것을 특징으로 한다.

#### 대표도

(52) CPC특허분류

**H04L 25/03878** (2013.01)

HO3F 2200/171 (2013.01)

(72) 발명자

# 안현우

서울특별시 동대문구 망우로18라길 40-1, 101호 ( 휘경동)

### 이재걸

서울특별시 광진구 구의강변로 94, 602동 1601호 (구의동,현대아파트)

# 문용삼

경기도 과천시 양지마을3로 1, 201호 (과천동)

# 현지환

경기도 수원시 영통구 삼성로 129 (매탄동, 삼성전 자)

# 최정환

경기도 수원시 영통구 삼성로 129 (매탄동, 삼성전 자)

### 명 세 서

# 청구범위

### 청구항 1

차동 입력 신호를 등화하여 차동 출력 신호를 각각 생성하는 연속 시간 선형 등화기를 구성하는 CTLE 셀에 있어서,

상기 차동 입력 신호가 인가되는 입력단 및 상기 차동 출력 신호를 출력하는 출력단을 구비한 제1 트랜지스터;

상기 차동 입력 신호가 인가되는 입력단 및 상기 차동 출력 신호를 출력하는 출력단을 구비한 제2 트랜지스터; 및

상기 차동 출력 신호를 로우 패스 필터링하여 얻어진 저대역 차동 신호의 차이에 대응하는 제어 전압에 따라 공급 전압원과 상기 출력단 사이의 전위차를 조절하는 오프셋 보상부

를 포함하는 것을 특징으로 하는 CTLE 셀.

#### 청구항 2

제1항에 있어서.

상기 오프셋 보상부는

상기 제어 전압이 인가되는 게이트; 및 상기 공급 전압원에 전기적으로 연결된 소스를 구비한 제3 트랜지스터;

상기 제3 트랜지스터의 드레인과 상기 출력단을 전기적으로 연결하는 저항; 및

상기 제3 트랜지스터의 소스와 상기 출력단을 전기적으로 연결하는 저항

을 포함하는 것을 특징으로 하는 CTLE 셀.

#### 청구항 3

제2항에 있어서,

상기 제3 트랜지스터는 P-MOSFET를 포함하는 것을 특징으로 하는 CTLE 셀.

#### 청구항 4

제2항에 있어서,

상기 제1 트랜지스터는 상기 출력단에 대응하는 드레인; 상기 입력단에 대응되는 게이트를 포함하며,

상기 제2 트랜지스터는 상기 출력단에 대응되는 드레인; 및 상기 입력단에 대응되는 게이트를 포함하는 것을 특징으로 하는 CTLE 셀.

#### 청구항 5

제4항에 있어서,

상기 공급 전압원과 상기 출력단을 전기적으로 연결하는 저항을 더 포함하는 것을 특징으로 하는 CTLE 셀.

#### 청구항 6

제1항에 있어서,

상기 오프셋 보상부는 상기 제어 전압의 평균에 따라 공급 전압원과 상기 출력단 사이의 전위차를 조절하는 것을 특징으로 하는 CTLE 셀.

### 청구항 7

차동 입력 신호를 등화하여 차동 출력 신호를 각각 생성하는 연속 시간 선형 등화기에 있어서,

상기 차동 입력 신호가 각각 인가되는 입력단 및 상기 차동 출력 신호를 각각 출력하는 출력단을 구비한 CTLE 셀;

상기 차동 출력 신호를 각각 로우 패스 필터링하여 얻어진 저대역 차동 신호를 각각 출력하는 로우 패스 필터; 및

상기 저대역 차동 신호의 차이를 증폭하여 제어 전압으로 출력하는 오차 증폭기

를 포함하되,

상기 CTLE 셀은

상기 입력단 및 상기 출력단을 구비한 제1 트랜지스터;

상기 입력단 및 상기 출력단을 구비한 제2 트랜지스터; 및

상기 제어 전압에 따라 공급 전압원과 상기 출력단 사이의 전위차를 조절하는 오프셋 보상부

를 포함하는 것을 특징으로 하는 연속 시간 선형 등화기.

### 청구항 8

제7항에 있어서,

상기 오프셋 보상부는

상기 제어 전압이 인가되는 게이트; 및 상기 공급 전압원에 전기적으로 연결된 소스를 구비한 제3 트랜지스터;

상기 제3 트랜지스터의 드레인과 상기 출력단을 전기적으로 연결하는 저항; 및

상기 제3 트랜지스터의 소스와 상기 출력단을 전기적으로 연결하는 저항

을 포함하는 것을 특징으로 하는 연속 시간 선형 등화기.

#### 청구항 9

제8항에 있어서,

상기 제3 트랜지스터는 P-MOSFET를 포함하는 것을 특징으로 하는 연속 시간 선형 등화기.

# 청구항 10

제8항에 있어서,

상기 제1 트랜지스터는 상기 출력단에 대응하는 드레인; 상기 입력단에 대응되는 게이트를 포함하며,

상기 제2 트랜지스터는 상기 출력단에 대응되는 드레인; 및 상기 입력단에 대응되는 게이트

를 포함하는 것을 특징으로 하는 연속 시간 선형 등화기.

# 청구항 11

제10항에 있어서,

상기 CTLE 셀은

상기 공급 전압원과 상기 출력단을 전기적으로 연결하는 저항을 더 포함하는 것을 특징으로 하는 연속 시간 선형 등화기.

### 청구항 12

제11항에 있어서,

상기 공급 전압원과 상기 오차 증폭기의 출력단 사이에 연결되어 상기 제어 전압의 평균을 생성하는 커패시터를 더 포함하며, 상기 오프셋 보상부는 상기 제어 전압의 평균에 따라 공급 전압원과 상기 출력단 사이의 전위차를 조절하는 것을 특징으로 하는 연속 시간 선형 등화기.

# 발명의 설명

# 기술분야

[0001] 본 발명은 차동 증폭기 및 이를 포함하는 적응형 연속 시간 선형 등화기에 관한 것으로, 특히 적응적으로 차동 출력 신호의 오프셋 보상이 가능한 차동 증폭기 및 이를 포함하는 적응형 연속 시간 선형 등화기에 관한 것이다.

#### 배경기술

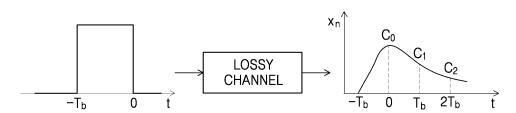

- [0002] 디지털 신호의 전송 속도가 고속화되면, 수신된 디지털 신호의 파형에 왜곡이 발생한다.

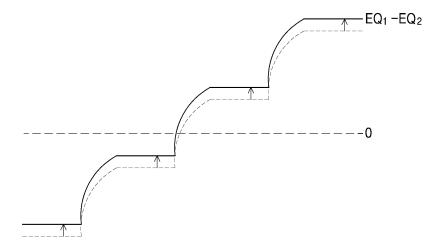

- [0003] 도 1은 파형의 왜곡을 도시한 개략도이다. 도 1을 참조하면, 길이가 T<sub>b</sub>인 펄스를 로시 채널(LOSSY CHANNEL. 예를 들면, 신호 전송 케이블 등)을 통해 전송하면, 수신단에서는 왜곡된 신호(x<sub>n</sub>)가 수신된다. 예를 들어, 수신 된 신호(x<sub>n</sub>)는, 로시 채널의 로우-패스 필터 특성으로 인하여, t=-T<sub>b</sub>에서부터 서서히 상승하여 t=0에서 C<sub>0</sub>(메인 커서: Main Cursor)에 도달한다. 신호(x<sub>n</sub>)는 t=0부터 서서히 하강하여 t=T<sub>b</sub>에서 C<sub>1</sub>(포스트 커서: Post Cursor)에 도달하고, t=2T<sub>b</sub>에서 C<sub>2</sub>(포스트 커서)에 도달한다. 즉, 신호(x<sub>n</sub>)는 t=2T<sub>b</sub>가 되어도 0에 도달하지 못한다.

- [0004] 이러한 파형의 왜곡을 보상하기 위해, 연속 시간 선형 등화기(Continuous-Time Linear Equalizer: CTLE)가 이용된다.

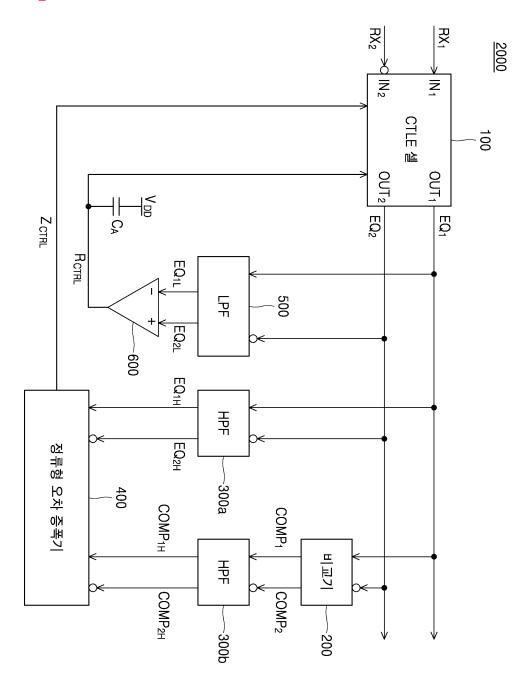

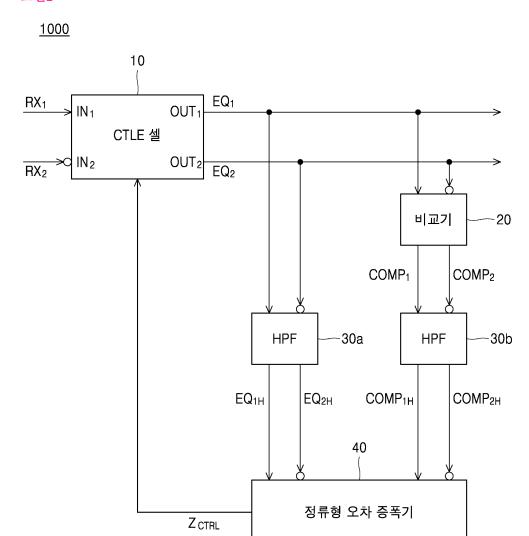

- [0005] 도 2는 종래 기술에 따른 연속 시간 선형 등화기를 도시한 블록도이다.

- [0006] 도 2를 참조하면, 종래 기술에 따른 연속 시간 선형 등화기(1000)는 CTLE 셀(10), 비교기(20), 하이 패스 필터 (HPF)(30a, 30b) 및 정류형 오차 증폭기(40)를 포함한다.

- [0007] CTLE 셀(10)은 차동 입력 신호(RX<sub>1</sub>, RX<sub>2</sub>)를 등화하여 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)를 각각 출력한다.

- [0008] 구체적으로는, CTLE 셀(10)은 차동 입력 신호(RX<sub>1</sub>, RX<sub>2</sub>)가 각각 인가되는 입력단(IN<sub>1</sub>, IN<sub>2</sub>); 및 차동 출력 신호 (EQ<sub>1</sub>, EQ<sub>2</sub>)를 각각 출력하는 출력단(OUT<sub>1</sub>, OUT<sub>2</sub>)을 구비한다.

- [0009] 이하에서는, 도 3을 참조하여 종래 기술에 따른 CTLE 셀(10)에 대해 상세히 설명한다.

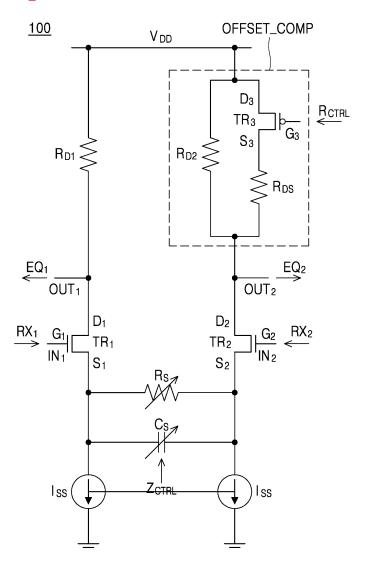

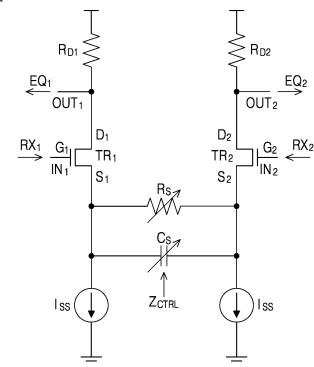

- [0010] 도 3은 종래 기술에 따른 CTLE 셀(10)을 도시한 도면이다. CTLE 셀(10)은 도 3에 도시된 차동 증폭기를 포함한다.

- [0011] 도 3을 참조하면, CTLE 셀(10)을 구성하는 차동 증폭기는 제1 트랜지스터(TR<sub>1</sub>), 제2 트랜지스터(TR<sub>2</sub>), 저항 (R<sub>D1</sub>), 저항(R<sub>D2</sub>), 저항(R<sub>S</sub>) 및 커패시터(C<sub>S</sub>)를 포함한다.

- [0012] 도 3에 도시된 CTLE 셀(10)은 저항(R<sub>s</sub>)의 저항값과 커패시터(C<sub>s</sub>)의 커패시턴스를 조절하여 등화를 수행한다.

- [0013] 구체적으로는, 저항(R<sub>S</sub>)은 CTLE 셀(10)의 저주파 증폭 게인을 조절하며, 커패시터(C<sub>S</sub>)는 CTLE 셀(10)의 고주파 증폭 게인을 조절한다.

- [0014] 저항 $(R_s)$ 은 그 저항값을 조절할 수 있는 가변저항이다.

- [0015] 또한, 커패시터( $C_s$ )의 커패시턴스는 제어 전압( $Z_{CTRL}$ )에 의해 조절된다.

- [0016] 이하에서는, 커패시터(C<sub>s</sub>)의 커패시턴스를 조절하는 방법에 대해 상세히 설명한다.

- [0017] CTLE 셀(10)은 차동 입력 신호(RX<sub>1</sub>, RX<sub>2</sub>)를 등화하여 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)를 각각 출력한다.

- [0018] 차동 출력 신호(EO<sub>1</sub>, EO<sub>2</sub>)는 HPF(30a)에 의해 각각 필터링되어 고대역 차동 출력 신호(EO<sub>1</sub>, EO<sub>2</sub>)로 출력된다.

- [0019] 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)는 비교기(20)에 입력되어 각각 차동 출력 신호(COMP<sub>1</sub>, COMP<sub>2</sub>)로 출력된다.

- [0020] 차동 출력 신호(COMP<sub>1</sub>, COMP<sub>2</sub>)는 HPF(30b)에 의해 각각 필터링되어 고대역 차동 출력 신호(COMP<sub>1H</sub>, COMP<sub>2H</sub>)로 출력되다.

- [0021] 정류형 오차 증폭기(40)는 고대역 차동 출력 신호(EQ<sub>1H</sub>, EQ<sub>2H</sub>) 중 그 크기가 큰 신호;와 고대역 차동 출력 신호 (COMP<sub>1H</sub>, COMP<sub>2H</sub>) 중 그 크기가 큰 신호;의 차이를 증폭하여 제어 전압(Z<sub>CTRL</sub>)으로 출력한다.

- [0022] 제어 전압(Z<sub>CTRL</sub>)을 수식으로 나타내면 아래의 수학식 1과 같다.

# 수학식 1

- $Z_{CTRL} = A_1 \times \left[ \max(EQ_{1H}, EQ_{2H}) \max(COMP_{1H}, COMP_{2H}) \right] + Z_{CTRL,DC}$

- [0024] 여기서, A<sub>1</sub>은 게인(gain)이고 Z<sub>CTRL.DC</sub>는 Z<sub>CTRL</sub>의 DC 바이어스(bias) 값이다. 일반적으로 DC 바이어스 값이란 회로 가 갖는 값의 범위 중에서 중간 값에 해당한다.

- [0025] 예를 들어, EQ<sub>1H</sub>>EQ<sub>2H</sub>이고, COMP<sub>1H</sub><COMP<sub>2H</sub>이면, 정류형 오차 증폭기(40)는 아래의 수학식 2의 제어 전압(Z<sub>CTRL</sub>)을 출력하다.

# 수학식 2

- $Z_{CTRL} = A_1 \times (EQ_{1H} COMP_{2H}) + Z_{CTRL.DC}$

- [0027] 제어 전압(Z<sub>CTRL</sub>)는 CTLE 셀(10)에 피드백되어 커패시터(C<sub>S</sub>)의 커패시턴스를 조절하는데 이용된다. 즉, 제어 전압 (Z<sub>CTRL</sub>)에 따라 커패시터(C<sub>S</sub>)의 커패시턴스를 조절함으로써 CTLE 셀(10)의 고주파 증폭 게인을 조절한다. 이 과정은 max(EQ<sub>1H</sub>, EQ<sub>2H</sub>) ≒ max(COMP<sub>1H</sub>, COMP<sub>2H</sub>)가 될 때까지 반복된다. 이때 A<sub>1</sub>이 크기 때문에 Z<sub>CTRL</sub> ≠ Z<sub>CTRL.DC</sub> 인 것이일반적이다.

- [0028] 종래 기술에 따른 CTLE 셀(10)은 고주파 증폭 게인 및 저주파 증폭 게인을 적응적으로 조절하여 등화를 수행한다. 그러나, 종래 기술에 따른 CTLE 셀(10)은 등화 과정에서 발생할 수 있는 오프셋(offset)을 적응적으로 제거하지 못한다는 문제점이 있다.

- [0029] 이하에서는, 도 4a 내지 도 5b를 참조하여 이에 대해 상세히 설명한다.

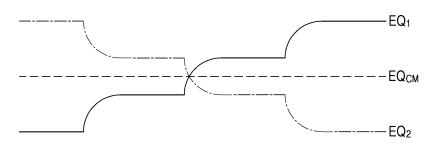

- [0030] 도 4a 및 도 4b는 이상적인 CTLE 셀의 차동 출력 신호와 그 차이를 도시한 파형도이다.

- [0031] 도 4a에 도시된 바와 같이, 이상적(ideal)인 CTLE 셀(10)은 공통 모드(common mode) 전압(EQ<sub>CM</sub>)에 대해 대칭인 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)를 출력한다. 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)가 공통 모드(common mode) 전압(EQ<sub>CM</sub>)에 대해 대칭이면, 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)의 차이(EQ<sub>1</sub>-EQ<sub>2</sub>)는 도 4b에 도시된 바와 같이 0을 기준으로 스윙한다.

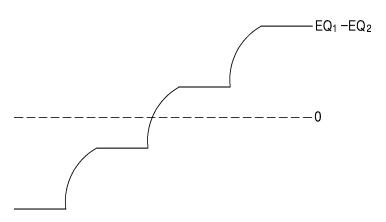

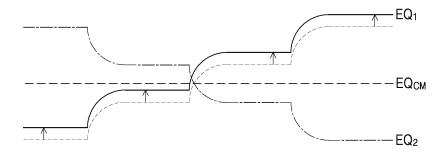

- [0032] CTLE 셀(10)은 도 3에 예시된 바와 같이, 다수의 소자로 구성된다. 그런데, CTLE 셀(10)을 구성하는 소자들은 모두 이상적인 소자가 아니므로, CTLE 셀(10)의 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)에는 도 5a에 도시된 바와 같이 오프셋 (offset)이 존재한다. 또한, 이상적이지 못한 송신 채널 등으로 인하여 오프셋(offset)이 발생할 수도 있다.

- [0033] 도 5a는 오프셋이 발생한 CTLE 셀(10)의 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)를 도시한 파형도로서, 차동 출력 신호(EQ<sub>1</sub>)에 오프셋이 존재하는 경우를 예시한다.

- [0034] 도 5a에 도시된 바와 같이, 차동 출력 신호(EQ<sub>1</sub>)에는 화살표로 표시된 오프셋이 존재한다. 따라서, 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)의 전압은 공통 모드(common mode) 전압(EQ<sub>CM</sub>)에 대해 대칭이 아니다.

- [0035] 차동 출력 신호(EQ<sub>1</sub>)에 오프셋이 존재하는 경우, 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)의 차이(EQ<sub>1</sub>-EQ<sub>2</sub>)가 도 5b에 도시되어 있다.

- [0036] 도 5b를 참조하면, 차동 출력 신호(EQ<sub>1</sub>)에 존재하는 오프셋으로 인하여, 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)의 차이(EQ<sub>1</sub>-EQ<sub>2</sub>)에도 화살표로 표시된 오프셋이 존재한다. 따라서, 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)의 차이(EQ<sub>1</sub>-EQ<sub>2</sub>)는 0을 기준으로 스윙하지 않는다.

- [0037] 오프셋은 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>) 중 어느 하나에만 존재하거나 양자 모두에 존재할 수 있다. 오프셋의 크기는 송신 채널의 특성이나, CTLE 셀(10)을 구성하는 소자들의 미스매치(mismatch) 등에 의해 달라진다.

- [0038] 오프셋이 존재하는 경우, 수신 신호의 레벨을 판정하는데 문제가 발생할 수 있다. 예를 들어, EQ<sub>1</sub>-EQ<sub>2</sub>>0일 때 수신 신호의 레벨을 1이라 판정하고, EQ<sub>1</sub>-EQ<sub>2</sub><0일 때 수신 신호의 레벨을 0이라고 판정한다고 가정하자. 도 5b의 차이(EQ<sub>1</sub>-EQ<sub>2</sub>)는 0보다 위쪽으로 치우쳐 있으므로 수신 신호의 레벨을 1이라고 판정할 확률이 더 높아진다. 즉, 경우에 따라, 수신 신호의 레벨을 정확히 판단하지 못할 수 있다는 문제가 있다.

- [0039] 수신 신호의 레벨을 정확히 판정하기 위해서는 차이(EQ<sub>1</sub>-EQ<sub>2</sub>)가 0을 기준으로 스윙하도록 해야 한다. 따라서, 상술한 오프셋을 보상 또는 제거하는 수단이 필요하다.

### 선행기술문헌

### 특허문헌

[0040] (특허문헌 0001) 미국 특허 공개 제2020-0313638호

#### 비특허문헌

[0041] (비특허문헌 0001) 논문 "A 0.18-/spl mu/m CMOS 3.5-gb/s continuous-time adaptive cable equalizer using enhanced low-frequency gain control method," by Jong-Sang Choi; Moon-Sang Hwang; Deog-Kyoon Jeong, IEEE Journal of Solid-State Circuits, Vol. 39, pp. 419-425, March 3, 2004

#### 발명의 내용

#### 해결하려는 과제

[0042] 본 발명은 차동 출력 신호의 오프셋 보상이 가능한 차동 증폭기 및 이를 포함하는 적응형 연속 시간 선형 등화 기를 제공하는 것을 그 목적으로 한다.

# 과제의 해결 수단

- [0043] 본 발명에 따른 CTLE 셀은, 차동 입력 신호(RX<sub>1</sub>, RX<sub>2</sub>)를 등화하여 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)를 각각 생성하는 연속 시간 선형 등화기를 구성하는 CTLE 셀에 있어서, 상기 차동 입력 신호(RX<sub>1</sub>)가 인가되는 입력단(IN<sub>1</sub>) 및 상기 차동 출력 신호(EQ<sub>1</sub>)를 출력하는 출력단(OUT<sub>1</sub>)을 구비한 제1 트랜지스터; 상기 차동 입력 신호(RX<sub>2</sub>)가 인가되는 입력단(IN<sub>2</sub>) 및 상기 차동 출력 신호(EQ<sub>2</sub>)를 출력하는 출력단(OUT<sub>2</sub>)을 구비한 제2 트랜지스터; 및 상기 차동 출력 신호(EQ<sub>1</sub>)를 로우 패스 필터링하여 얻어진 저대역 차동 신호(EQ<sub>1</sub>L, EQ<sub>2</sub>L)의 차이에 대응하는 제어 전압 (R<sub>CTRL</sub>)에 따라 공급 전압원과 상기 출력단(OUT<sub>2</sub>) 사이의 전위차를 조절하는 오프셋 보상부를 포함하는 것을 특징으로 한다.

- [0044] 상기 오프셋 보상부는 상기 제어 전압(R<sub>CTRL</sub>)이 인가되는 게이트; 및 상기 공급 전압원에 전기적으로 연결된 소스를 구비한 제3 트랜지스터; 상기 제3 트랜지스터의 드레인과 상기 출력단(OUT<sub>2</sub>)을 전기적으로 연결하는 저항

- (R<sub>RS</sub>); 및 상기 제3 트랜지스터의 소스와 상기 출력단(OUT₂)을 전기적으로 연결하는 저항(R<sub>R2</sub>)을 포함할 수 있다.

- [0045] 상기 제3 트랜지스터는 P-MOSFET를 포함하는 것이 바람직하다.

- [0046] 상기 제1 트랜지스터는 상기 출력단(OUT<sub>1</sub>)에 대응하는 드레인; 상기 입력단(IN<sub>1</sub>)에 대응되는 게이트를 포함하며, 상기 제2 트랜지스터는 상기 출력단(OUT<sub>2</sub>)에 대응되는 드레인; 및 상기 입력단(IN<sub>2</sub>)에 대응되는 게이트를 포함할 수 있다.

- [0047] 본 발명에 따른 CTLE 셀은 상기 공급 전압원과 상기 출력단(OUT<sub>1</sub>)을 전기적으로 연결하는 저항 $(R_{D1})$ 을 더 포함할 수 있다.

- [0048] 상기 오프셋 보상부는 상기 제어 전압( $R_{CTRL}$ )의 평균에 따라 공급 전압원과 상기 출력단( $OUT_2$ ) 사이의 전위차를 조절하는 것이 바람직하다.

- [0049] 본 발명에 따른 연속 시간 선형 등화기는 차동 입력 신호(RX<sub>1</sub>, RX<sub>2</sub>)를 등화하여 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)를 각 각 생성하는 연속 시간 선형 등화기에 있어서, 상기 차동 입력 신호(RX<sub>1</sub>, RX<sub>2</sub>)가 각각 인가되는 입력단(IN<sub>1</sub>, IN<sub>2</sub>) 및 상기 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)를 각각 출력하는 출력단(OUT<sub>1</sub>, OUT<sub>2</sub>)을 구비한 CTLE 셀; 상기 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)를 각각 로우 페스 필터링하여 얻어진 저대역 차동 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)를 각각 출력하는 로우 패스 필터; 및 상기 저대역 차동 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)의 차이를 증폭하여 제어 전압(R<sub>CTRL</sub>)으로 출력하는 오차 증폭기를 포함하되, 상기 CTLE 셀은 상기 입력단(IN<sub>1</sub>) 및 상기 출력단(OUT<sub>1</sub>)을 구비한 제1 트랜지스터; 상기 입력단(IN<sub>2</sub>) 및 상기 출력단(OUT<sub>2</sub>)을 구비한 제2 트랜지스터; 및 상기 제어 전압(R<sub>CTRL</sub>)에 따라 공급 전압원과 상기 출력단(OUT<sub>2</sub>) 사이의 전위차를 조절하는 오프셋 보상부를 포함하는 것을 특징으로 한다.

- [0050] 상기 오프셋 보상부는 상기 제어 전압(R<sub>CTRL</sub>)이 인가되는 게이트; 및 상기 공급 전압원에 전기적으로 연결된 소스를 구비한 제3 트랜지스터; 상기 제3 트랜지스터의 드레인과 상기 출력단(OUT<sub>2</sub>)을 전기적으로 연결하는 저항 (R<sub>DS</sub>); 및 상기 제3 트랜지스터의 소스와 상기 출력단(OUT<sub>2</sub>)을 전기적으로 연결하는 저항(R<sub>D2</sub>)을 포함할 수 있다.

- [0051] 상기 제3 트랜지스터는 P-MOSFET를 포함하는 것이 바람직하다.

- [0052] 상기 제1 트랜지스터는 상기 출력단(OUT<sub>1</sub>)에 대응하는 드레인; 상기 입력단(IN<sub>1</sub>)에 대응되는 게이트를 포함하며, 상기 제2 트랜지스터는 상기 출력단(OUT<sub>2</sub>)에 대응되는 드레인; 및 상기 입력단(IN<sub>2</sub>)에 대응되는 게이트를 포함할 수 있다.

- [0053] 본 발명에 따른 연속 시간 선형 등화기는 상기 공급 전압원과 상기 출력단(OUT<sub>1</sub>)을 전기적으로 연결하는 저항  $(R_{D1})$ 을 더 포함할 수 있다.

- [0054] 본 발명에 따른 연속 시간 선형 등화기는 상기 공급 전압원과 상기 오차 증폭기의 출력단 사이에 연결되어 상기 제어 전압(R<sub>CTRL</sub>)의 평균을 생성하는 커패시터(C<sub>A</sub>)를 더 포함하며, 상기 오프셋 보상부는 상기 제어 전압(R<sub>CTRL</sub>)의 평균에 따라 공급 전압원과 상기 출력단(OUT<sub>2</sub>) 사이의 전위차를 조절하는 것이 바람직하다.

#### 발명의 효과

- [0055] 본 발명에 따른 차동 출력 신호의 오프셋 보상이 가능한 차동 증폭기 및 이를 포함하는 적응형 연속 시간 선형 등화기에는 다음과 같은 장점이 있다.

- [0056] (1) 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)에 존재하는 오프셋을 적응적으로 보상하여 정확한 데이터 레벨의 판정이 가능하다.

- [0057] (2) 오프셋을 적응적으로 보상함과 동시에, 적응형 연속 시간 선형 등화기의 저주파 증폭 게인과 고주파 증폭 게인도 적응적으로 조절할 수 있다.

#### 도면의 간단한 설명

[0058] 도 1은 파형의 왜곡을 도시한 개략도.

도 2는 종래 기술에 따른 연속 시간 선형 등화기를 도시한 블록도.

도 3은 도 2의 종래 기술에 따른 연속 시간 선형 등화기를 구성하는 CTLE 셀의 차동 증폭기를 도시한 회로도.

도 4a 및 도 4b는 이상적인 CTLE 셀의 차동 출력 신호와 그 차이를 도시한 파형도.

도 5a 및 도 5b는 오프셋이 발생한 CTLE 셀의 차동 출력 신호와 그 차이를 도시한 파형도.

도 6은 본 발명에 따른 연속 시간 선형 등화기를 도시한 블록도.

도 7은 도 6의 본 발명에 따른 연속 시간 선형 등화기를 구성하는 CTLE 셀의 차동 증폭기를 도시한 회로도.

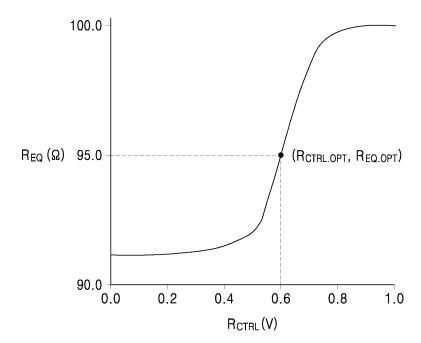

도 8은 제어 전압(RCTRL)에 따른 오프셋 보상부의 저항값을 도시한 그래프.

## 발명을 실시하기 위한 구체적인 내용

- [0059] 이하에서는, 첨부된 도면을 참조하여, 본 발명에 따른 차동 출력 신호의 오프셋 보상이 가능한 차동 증폭기 및 이를 포함하는 적응형 연속 시간 선형 등화기에 대해 상세히 설명한다.

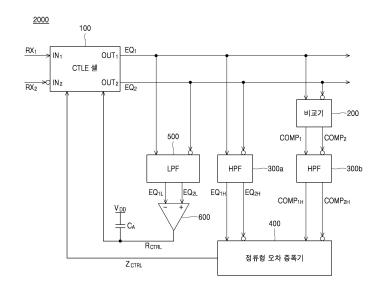

- [0060] 도 6은 본 발명에 따른 연속 시간 선형 등화기를 도시한 블록도이다.

- [0061] 도 6을 참조하면, 본 발명에 따른 연속 시간 선형 등화기(2000)는 CTLE 셀(100), 로우 패스 필터(LPF)(500) 및 오차 증폭기(600)를 포함한다. 또한, 본 발명에 따른 연속 시간 선형 등화기(2000)는 비교기(200), 하이 패스 필터(300a, 300b), 정류형 오차 증폭기(400) 및 커패시터(CA)를 더 포함할 수 있다.

- [0062] CTLE 셀(100)은 차동 입력 신호(RX<sub>1</sub>, RX<sub>2</sub>)를 등화하여 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)를 각각 출력한다.

- [0063] 구체적으로는, CTLE 셀(100)은 차동 입력 신호(RX<sub>1</sub>, RX<sub>2</sub>)가 각각 인가되는 입력단(IN<sub>1</sub>, IN<sub>2</sub>); 및 차동 출력 신호 (EQ<sub>1</sub>, EQ<sub>2</sub>)를 각각 출력하는 출력단(OUT<sub>1</sub>, OUT<sub>2</sub>)을 구비한다.

- [0064] 이하에서는, 도 7을 참조하여 본 발명에 따른 CTLE 셀(100)에 대해 상세히 설명한다.

- [0065] 도 7은 본 발명에 따른 CTLE 셀(100)을 도시한 도면이다. CTLE 셀(100)은 도 7에 도시된 차동 증폭기를 포함한다.

- [0066] 도 7을 참조하면, CTLE 셀(100)을 구성하는 차동 증폭기는 제1 트랜지스터(TR₁), 제2 트랜지스터(TR₂) 및 오프 셋 보상부(OFFSET\_COMP)를 포함한다. 또한, CTLE 셀(100)을 구성하는 차동 증폭기는 저항(R₂), 저항(R₂) 및 커패시터(C₃)를 포함한다.

- [0067] 도 7에 도시된 바와 같이, 저항(R<sub>D1</sub>)과 제1 트랜지스터(TR<sub>1</sub>)는 공급 전압원(V<sub>DD</sub>)과 전류원 사이에 직렬로 연결된다. 즉, 저항(R<sub>D1</sub>)은 공급 전압원(V<sub>DD</sub>)과 제1 트랜지스터(TR<sub>1</sub>)의 드레인(D<sub>1</sub>)을 전기적으로 연결한다.

- [0068] 또한, 오프셋 보상부(OFFSET\_COMP)와 제2 트랜지스터(TR<sub>2</sub>)는 공급 전압원(V<sub>DD</sub>)과 전류원 사이에 직렬로 연결된다. 즉, 오프셋 보상부(OFFSET\_COMP)는 공급 전압원(V<sub>DD</sub>)과 제2 트랜지스터(TR<sub>2</sub>)의 드레인(D<sub>2</sub>)을 전기적으 로 연결한다.

- [0069] 또한, 저항(R<sub>S</sub>) 및 커패시터(C<sub>S</sub>)는 제1 트랜지스터(TR₁)의 소스(S₁)와 제2 트랜지스터(TR₂)의 소스(S₂) 사이에 병렬로 연결된다.

- [0070] 이하에서는, 도 7에 도시된 차동 증폭기의 각 소자에 대하여 보다 상세히 설명한다.

- [0071] 제1 트랜지스터(TR<sub>1</sub>)는 차동 입력 신호(RX<sub>1</sub>)가 인가되는 입력단(IN<sub>1</sub>)에 대응하는 게이트(G<sub>1</sub>)와, 차동 출력 신호 (EQ<sub>1</sub>)를 출력하는 출력단(OUT<sub>1</sub>)에 대응하는 드레인(D<sub>1</sub>)과, 병렬로 연결된 저항(R<sub>S</sub>) 및 커패시터(C<sub>S</sub>)에 전기적으로 연결된 소스(S<sub>1</sub>)를 포함한다. 드레인(D<sub>1</sub>)은 저항(R<sub>D1</sub>)을 통해 공급 전압원(V<sub>DD</sub>)에 전기적으로 연결된다.

- [0072] 제2 트랜지스터(TR2)는 차동 입력 신호(RX2)가 인가되는 입력단(IN2)에 대응하는 게이트(G2)와, 차동 출력 신호

$(EQ_2)$ 를 출력하는 출력단 $(OUT_2)$ 에 대응하는 드레인 $(D_2)$ 과, 병렬로 연결된 저항 $(R_S)$  및 커패시터 $(C_S)$ 에 전기적으로 연결된 소스 $(S_2)$ 를 포함한다. 드레인 $(D_2)$ 은 병렬로 연결된 오프셋 보상부 $(OFFSET\_COMP)$  및 저항 $(R_{D2})$ 을 통해 공급 전압원 $(V_{DD})$ 에 전기적으로 연결된다.

- [0073] 오프셋 보상부(OFFSET\_COMP)는 저대역 차동 신호(EQ<sub>1L</sub>, EQ<sub>2L</sub>)의 차이에 대응하는 제어 전압(R<sub>CTRL</sub>)에 따라 공급 전 압원(V<sub>DD</sub>)과 출력단(OUT<sub>2</sub>) 사이의 전위차를 조절한다. 여기서, 제어 전압(R<sub>CTRL</sub>)은 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)를 로 우 패스 필터링하여 얻어진 저대역 차동 신호(EQ<sub>11</sub>, EQ<sub>21</sub>)의 차이를 증폭한 것이다.

- [0074] 제어 전압(R<sub>CTRI</sub>)은 아래의 수학식 3과 같다.

# 수학식 3

- [0075]  $R_{CTRL} = A_2 \times (EQ_{2L} EQ_{1L}) + R_{CTRL.DC}$

- [0076] 여기서, A<sub>2</sub>는 게인(gain)이고 R<sub>CTRL.DC</sub>는 R<sub>CTRL</sub>의 DC 바이어스(bias) 값이다.

- [0077] 구체적으로는, 오프셋 보상부(OFFSET\_COMP)는 제3 트랜지스터(TR<sub>3</sub>),저항(R<sub>DS</sub>) 및 저항(R<sub>D2</sub>)을 포함한다.

- [0078] 제3 트랜지스터(TR<sub>3</sub>)는 제어 전압(R<sub>CTRL</sub>)이 인가되는 게이트(G<sub>3</sub>) 및 공급 전압원(V<sub>DD</sub>)에 전기적으로 연결된 소스 (S<sub>3</sub>) 및 저항(R<sub>DS</sub>)과 전기적으로 연결된 드레인(D<sub>3</sub>)를 구비한다. 여기서, 제3 트랜지스터(TR<sub>3</sub>)는 P-MOSFET를 포함하는 것이 바람직하다.

- [0079] 저항(R<sub>DS</sub>)은 제3 트랜지스터(TR<sub>3</sub>)의 드레인(D<sub>3</sub>)과 출력단(OUT<sub>2</sub>)을 전기적으로 연결한다.

- [0080] 저항(R<sub>D2</sub>)은 제3 트랜지스터(TR<sub>3</sub>)의 소스(S<sub>3</sub>)와 출력단(OUT<sub>2</sub>)을 전기적으로 연결한다.

- [0081] 저항(R<sub>S</sub>)은 제1 트랜지스터(TR<sub>1</sub>)의 소스(S<sub>1</sub>)와 제2 트랜지스터(TR<sub>2</sub>)의 소스(S<sub>2</sub>)에 전기적으로 연결되며, CTLE 셀 (100)의 저주파 증폭 게인을 조절한다.

- [0082] 커피시터(C<sub>s</sub>)는 저항(R<sub>s</sub>)에 병렬로 연결되어 CTLE 셀(100)의 고주파 증폭 게인을 조절한다.

- [0083] 다시 도 6을 참조하면, 본 발명에 따른 연속 시간 선형 등화기(2000)의 로우 패스 필터(LPF)(500)는 CTLE 셀 (100)이 출력하는 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)를 각각 로우 패스 필터링하여 저대역 차동 신호(EQ<sub>1L</sub>, EQ<sub>2L</sub>)를 각각 출력한다.

- [0084] 오차 증폭기(600)는 로우 패스 필터(LPF)(500)가 출력한 저대역 차동 신호(EQ<sub>IL</sub>, EQ<sub>2L</sub>)의 차이를 증폭하여 제어 전압(R<sub>CTRL</sub>)으로 출력한다. 오차 증폭기(600)가 출력한 제어 전압(R<sub>CTRL</sub>)은 CTLE 셀(100)에 포함된 제3 트랜지스터 (TR<sub>3</sub>)의 게이트(G<sub>3</sub>)에 인가된다.

- [0085] 커페시터(C<sub>A</sub>)는 CTLE 셀(100)에 피드백되는 제어 전압(R<sub>CTRL</sub>)의 평균값을 생성한다. 커페시터(C<sub>A</sub>)는 공급 전압원 (V<sub>DD</sub>)과 오차 증폭기(600)의 출력단 사이에 연결된다. 오프셋 보상부(OFFSET\_COMP)의 저항값은 저대역 차동 신호 (EQ<sub>IL</sub>, EQ<sub>2L</sub>)의 각 펄스마다 얻어진 제어 전압(R<sub>CTRL</sub>)을 이용하여 조절될 수도 있지만, 제어 전압(R<sub>CTRL</sub>)의 평균에 따라 조절될 수도 있다. 이 경우, 오프셋 보상부(OFFSET\_COMP)의 저항값이 상대적으로 더욱 스무스(smooth)하게 조절된다.

- [0086] 비교기(200), 하이 패스 필터(300a, 300b) 및 정류형 오차 증폭기(400)는 도 2를 참조하여 설명한 종래 기술에 따른 연속 시간 선형 등화기의 그것과 동일하므로 상세한 설명은 생략한다.

- [0087] 이하에서는, 도 6 내지 도 8을 참조하여 본 발명에 따른 연속 시간 선형 등화기의 동작에 대해 상세히 설명한다. 다만, 커패시터(Cs) 및 저항(Rs)의 조절은 도 3을 참조하여 설명한 CTLE 셀의 그것과 동일하므로 상세한 설명은 생략한다.

- [0088] 먼저, 입력단(IN<sub>1</sub>, IN<sub>2</sub>)을 통해 차동 입력 신호(RX<sub>1</sub>, RX<sub>2</sub>)가 각각 인가되며, CTLE 셀(100)은 초기값에 따라 차동 입력 신호(RX<sub>1</sub>, RX<sub>2</sub>)를 등화하여 출력단(OUT<sub>1</sub>, OUT<sub>2</sub>)을 통해 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)를 각각 출력한다.

- [0089] CTLE 셀(100)이 출력한 차동 출력 신호(EQ<sub>1</sub>, EQ<sub>2</sub>)는 로우 패스 필터(500)에 의해 필터링된다. 로우 패스 필터 (500)가 출력하는 저대역 차동 신호(EQ<sub>1L</sub>, EQ<sub>2L</sub>)는 오차 증폭기(600)에 인가된다.

- [0090] 오차 증폭기(600)는 저대역 차동 신호(EQ<sub>IL</sub>, EQ<sub>2L</sub>)의 차이를 증폭하여 제어 전압(R<sub>CTRL</sub>)으로 출력하고, 이를 CTLE 셀(100)에 인가한다.

- [0091] 제3 트랜지스터(TR<sub>3</sub>)는 바람직하게는 P-MOSFET이다.

- [0092] 제어 전압(R<sub>CTRL</sub>)이 게이트(G<sub>3</sub>)에 인가되면, 제3 트랜지스터(TR<sub>3</sub>)의 소스(S<sub>3</sub>)와 드레인(D<sub>3</sub>) 사이의 저항값이 변화한다. 예를 들어, 먼저 공급 전압원이 공급하는 전압이 1V라고 가정한다. 제어 전압(R<sub>CTRL</sub>)이 0.8V 이상이면, 제3 트랜지스터(TR<sub>3</sub>)는 완전히 턴 오프(turn off)되므로 소스(S<sub>3</sub>)와 드레인(D<sub>3</sub>) 사이는 실질적으로 오픈 서킷(open circuit)이 된다. 제어 전압(R<sub>CTRL</sub>)이 0.3V 이하이면, 제3 트랜지스터(TR<sub>3</sub>)는 완전히 턴 온(turn on)되므로 소스(S<sub>3</sub>)와 드레인(D<sub>3</sub>) 사이는 실질적으로 쇼트 서킷(short circuit)이 된다. 제어 전압(R<sub>CTRL</sub>)이 0.3V와 0.8V 사이이면, 제어 전압(R<sub>CTRL</sub>)이 증가함에 따라 소스(S<sub>3</sub>)와 드레인(D<sub>3</sub>) 사이의 저항값이 증가한다.

- [0093] 도 8은 제어 전압(R<sub>CTRI</sub>)에 따른 오프셋 보상부(OFFSET\_COMP)의 저항값을 예시한 그래프이다.

- [0094] 도 8을 참조하면, 오프셋 보상부(OFFSET\_COMP)의 저항값(Rea)은 제어 전압(Rctral)에 따라 변화한다.

- [0095] 구체적으로는, 저항값(R<sub>50</sub>)은 제어 전압(R<sub>CTML</sub>)이 커질수록 커지고, 제어 전압(R<sub>CTML</sub>)이 작아질수록 작아진다.

- [0096] 즉, 오프셋 보상부(OFFSET\_COMP)의 저항값(R<sub>EQ</sub>)은 제어 전압(R<sub>CTRL</sub>)이 커질수록 저항(R<sub>D2</sub>)의 저항값에 가까워지며, 제어 전압(R<sub>CTRL</sub>)이 작아질수록 R<sub>D2</sub> Ⅱ R<sub>DS</sub>에 가까워진다.

- [0097] 환언하면, 오프셋 보상부(OFFSET\_COMP)의 저항값( $R_{EQ}$ )의 최대값은  $R_{D2}$ 이고, 최소값은  $R_{D2} \parallel R_{DS}$ (  $= \frac{R_{D2}R_{DS}}{R_{D2}+R_{D9}}$ 이다 이를 수식으로 나타내면 다음의 수학식 4와 같다.

#### 수학식 4

$$\frac{R_{D2}R_{DS}}{R_{D2}+R_{DS}} \leq R_{EQ} \leq R_{D2}$$

- [0099] 수학식 4에 따르면, 오프셋 보상부(OFFSET\_COMP)의 저항값(R<sub>EQ</sub>)은 제어 전압(R<sub>CTRL</sub>)의 변화에 따라 증가 또는 감소한다. 저항값(R<sub>EQ</sub>)이 변하면, 오프셋 보상부(OFFSET\_COMP)에 걸리는 전압이 변하고, 결과적으로 공급 전압원 (V<sub>DD</sub>)과 출력단(OUT<sub>2</sub>) 사이의 전위차, 즉 출력단(OUT<sub>2</sub>)의 전위(또는 전압)가 변하게 된다.

- [0100] 이에 대해 보다 구체적으로 살펴보면 다음과 같다.

- [0101] 먼저, 설명의 편의를 위해, 제어 전압(R<sub>CTRL</sub>)의 최적값을 최적 제어 전압(R<sub>CTRL.0PT</sub>)=0.6V라 하고, 이때의 오프셋 보상부(OFFSET\_COMP)의 저항값(R<sub>EQ</sub>)을 최적 저항값(R<sub>EQ.0PT</sub>)=95Ω이라고 가정하자.

- [0102] 먼저, 제어 전압(R<sub>CTRL</sub>)=0.7V이면, R<sub>EQ</sub> > R<sub>EQ.OPT</sub>이다(도 8 참조).

- [0103] 따라서, 오프셋 보상부(OFFSET\_COMP)에 의한 전압 강하는 최적 제어 전압(R<sub>CTRL.OPT</sub>)=0.6V일 때의 전압 강하보다 크고, 출력단(OUT<sub>2</sub>)의 전위는 최적 제어 전압(R<sub>CTRL.OPT</sub>)일 때의 그것보다 낮다.

- [0104] 따라서, 로우 패스 필터(500)가 출력하는 저대역 차동 신호(EQ<sub>1L</sub>, EQ<sub>2L</sub>) 사이에는 EQ<sub>1L</sub> > EQ<sub>2L</sub>이 성립하고, 오차

증폭기(600)가 출력하는 제어 전압(R<sub>CTRL</sub>)은 감소한다.

- [0105] 두 번째로, 제어 전압(R<sub>CTRL</sub>)=0.5V이면, R<sub>EQ</sub> < R<sub>EQ.OPT</sub>이다(도 8 참조).

- [0106] 따라서, 오프셋 보상부(OFFSET\_COMP)에 의한 전압 강하는 최적 제어 전압(R<sub>CTRL.OPT</sub>)=0.6V일 때의 전압 강하보다 작고, 출력단(OUT<sub>2</sub>)의 전위는 최적 제어 전압(R<sub>CTRL.OPT</sub>)일 때의 그것보다 높다.

- [0107] 따라서, 로우 패스 필터(500)가 출력하는 저대역 차동 신호(EQ<sub>1L</sub>, EQ<sub>2L</sub>) 사이에는 EQ<sub>1L</sub> < EQ<sub>2L</sub>이 성립하고, 오차 증폭기(600)가 출력하는 제어 전압(R<sub>CTRL</sub>)은 증가한다.

- [0108] 상술한 과정은 제어 전압(R<sub>CTRL</sub>)이 최적 제어 전압(R<sub>CTRL.OPT</sub>)에 수렴할 때까지 반복된다. 즉, 제어 전압(R<sub>CTRL</sub>)이 최적 제어 전압(R<sub>CTRL.OPT</sub>)보다 작으면 제어 전압(R<sub>CTRL</sub>)이 증가하는 과정과, 제어 전압(R<sub>CTRL</sub>)이 최적 제어 전압(R<sub>CTRL.OPT</sub>)보다 크면 제어 전압(R<sub>CTRL</sub>)이 감소하는 과정이 반복되어 제어 전압(R<sub>CTRL</sub>)은 최적 제어 전압(R<sub>CTRL.OPT</sub>)에 수렴한다.

#### 도면

# 도면4a

# *도면4b*

# 도면5a

# *도면5b*