(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4854980号 (P4854980)

(45) 発行日 平成24年1月18日(2012.1.18)

(24) 登録日 平成23年11月4日(2011.11.4)

(51) Int.Cl. F 1

HO 1 L

27/095

(2006.01)

HO 1 L

29/80

HO 1 L

21/338

(2006.01)

HO 1 L

29/80

HO1L 29/778 (2006.01) HO1L 29/812 (2006.01)

請求項の数 13 (全 22 頁)

(21) 出願番号 特願2005-96903 (P2005-96903)

(22) 出願日 平成17年3月30日 (2005.3.30) (65) 公開番号 特開2006-278813 (P2006-278813A)

(43) 公開日平成18年10月12日 (2006.10.12)審査請求日平成20年3月12日 (2008.3.12)

||(73)特許権者 000154325

住友電工デバイス・イノベーション株式会

汁

$\mathbf{E}$

Н

神奈川県横浜市栄区金井町1番地

||(74)代理人 100087480

弁理士 片山 修平

|(72)発明者 松田 一

山梨県中巨摩郡昭和町大字紙漉阿原100 〇番地 ユーディナデバイス株式会社内

審査官 行武 哲太郎

最終頁に続く

(54) 【発明の名称】スイッチ回路及び半導体装置の製造方法

#### (57)【特許請求の範囲】

#### 【請求項1】

<u>ソース電極またはドレイン電極の一方が第1の端子に</u>接続され、制御端子に接続された ゲート電極により、<u>前記ソース電極と前記ドレイン電極との</u>導通・非導通が制御される第 1のFETと、

<u>ソース電極またはドレイン電極の一方が</u>前記第1のFET<u>の前記ソース電極またはドレイン電極の他方と直列</u>接続され、前記制御端子に接続されたゲート電極により、<u>前記ソー</u>ス電極と前記ドレイン電極との導通・非導通が制御される第2のFETと、

ソース電極またはドレイン電極の一方が前記第2のFETの前記ソース電極またはドレイン電極の他方と直列接続され、前記ソース電極またはドレイン電極の他方が第2の端子と接続され、前記制御端子に接続されたゲート電極により、前記ソース電極と前記ドレイン電極との導通・非導通が制御される第3のFETとを具備し、

前記第1のFETと前記第2のFETと前記第3のFETとは、そのゲート電極が埋込層内に埋め込まれてなるとともに、前記第1のFETおよび前記第3のFETにおける埋込層に埋め込まれた埋込厚よりも薄いことにより、前記第1のFETのゲート電極に、前記第1のFETのドレイン電極の電圧に対し負の電圧を印加した場合におけるドレイン電極とゲート電極との間の耐圧である前記第1のFETのゲート逆方向耐圧は前記第2のFETのゲート逆方向耐圧よりも大きく、かつ前記第3のFETのゲート逆方向耐圧は前記第2のFETのゲート逆方向耐圧よりも大きいことを特徴とする半導体装置。

#### 【請求項2】

<u>ソース電極またはドレイン電極の一方が第1の端子に</u>接続され、制御端子に接続された ゲート電極により、<u>前記ソース電極と前記ドレイン電極との</u>導通・非導通が制御される第 1のFETと、

ソース電極またはドレイン電極の一方が前記第1のFETの前記ソース電極またはドレイン電極の他方と直列接続され、前記制御端子に接続されたゲート電極により、<u>前記ソー</u>ス電極と前記ドレイン電極との導通・非導通が制御される第2のFETと、

ソース電極またはドレイン電極の一方が前記第2のFETの前記ソース電極またはドレイン電極の他方と直列接続され、前記ソース電極またはドレイン電極の他方が第2の端子と接続され、前記制御端子に接続されたゲート電極により、前記ソース電極と前記ドレイン電極との導通・非導通が制御される第3のFETとを具備し、

前記第1のFETと前記第2のFETと前記第3のFETとは、そのゲート電極が埋込 層内に埋め込まれてなるとともに、前記第1のFETおよび前記第3のFETにおける埋 込層に埋め込まれた埋込厚が前記第2のFETにおける埋込層に埋め込まれた埋込厚より も薄いことにより、前記第1のFETのオフ容量および前記第3のFETのオフ容量は前 記第2のFETのオフ容量よりも小さいことを特徴とするスイッチ回路。

#### 【請求項3】

前記第1の端子は入力端子または出力端子の一方であり、前記第2の端子は前記入力端子または出力端子の他方であることを特徴とする請求項1または2記載のスイッチ回路。

## 【請求項4】

前記第1のFETと前記<u>第3のFET</u>との間には、前記第2のFETが複数直列に設けられてなることを特徴とする請求項1乃至3のいずれか一項記載のスイッチ回路。

#### 【請求項5】

前記制御端子を接地することにより、前記非導通をなすことを特徴とする請求項1乃至4のいずれか一項記載のスイッチ回路。

#### 【請求項6】

請求項1乃至5いずれか一項記載のスイッチ回路である第1スイッチ回路と、請求項1 乃至5いずれか一項記載の別のスイッチ回路である第2スイッチ回路とを含み、前記第1 スイッチ回路と前記第2スイッチ回路とが共通して前記第1の端子に接続されていること を特徴とするスイッチ回路。

#### 【請求項7】

前記第1のFET<u>、</u>前記第2のFET<u>および前記第3のFET</u>は、電子供給層とチャネル層を備えるHEMTであることを特徴とする請求項<u>1乃至6</u>のいずれか一項記載の<u>スイ</u>ッチ回路。

#### 【請求項8】

前記電子供給層は、前記チャネル層の上下に設けられていることを特徴とする請求項<u>7</u> 記載のスイッチ回路。

#### 【請求項9】

前記第1のFET、前記第2のFETおよび前記第3のFET は、GaAs系化合物半導体により構成されてなることを特徴とする請求 項1乃至8のいずれか一項記載のスイッチ回路。

#### 【請求項10】

<u>ソース電極またはドレイン電極の一方が第1の端子に</u>接続され、制御端子に接続された ゲート電極により、<u>前記ソース電極と前記ドレイン電極との</u>導通・非導通が制御される第 1のFETと、

<u>ソース電極またはドレイン電極の一方が</u>前記第1のFET<u>の前記ソース電極またはドレイン電極の他方と直列</u>接続され、前記制御端子に接続されたゲート電極により、<u>前記ソー</u>ス電極と前記ドレイン電極との導通・非導通が制御される第2のFETと、

<u>ソース電極またはドレイン電極の一方が前記第2のFETの前記ソース電極またはドレ</u>イン電極の他方と直列接続され、前記ソース電極またはドレイン電極の他方が第2の端子

10

20

30

40

と接続され、前記制御端子に接続されたゲート電極により、前記ソース電極と前記ドレイン電極との導通・非導通が制御される第3のFETとを具備する半導体装置の製造方法であって、

前記ゲート電極が設けられるショットキ層上に埋込層を形成する工程と、

前記第1のFET<u>および前記第3のFET</u>のゲート電極が形される領域の前記埋込層を露出し、前記第2のFETのゲート電極が形される領域の前記埋込層をマスク層で被覆して、前記第1のFET<u>および前記第3のFET</u>の前記ゲート電極が形される領域の前記埋込層の厚みを選択的に減じる工程と、

前記第1のFET、第2のFET<u>および前記第3のFET</u>それぞれの前記ゲートが形される領域の前記埋込層に前記ショットキ層を露出する開口部を形成する工程と、

前記開口部のそれぞれにゲート電極を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

#### 【請求項11】

前記第1のFET<u>、</u>前記第2のFET<u>および前記第3のFET</u>は、電子供給層とチャネル層を備えるHEMTであることを特徴とする請求項10記載の半導体装置の製造方法。

## 【請求項12】

前記電子供給層は、前記チャネル層の上下に設けられていることを特徴とする請求項<u>1</u> 1記載の半導体装置の製造方法。

## 【請求項13】

前記第1のFET<u>、</u>前記第2のFET<u>および前記第3のFET</u>は、GaAs系化合物半導体により構成されてなることを特徴とする請求項<u>10</u>乃至<u>12</u>記載の半導体装置の製造方法。

#### 【発明の詳細な説明】

#### 【技術分野】

## [0001]

本発明は、高周波(RF)スイッチ回路<u>及び半導体装置</u>の製造方法に関し、特に複数の電界効果トランジスタ(FET)を直列に接続したスタック構成の高周波スイッチ回路<u>及び</u>半導体装置の製造方法に関する。

#### 【背景技術】

## [0002]

近年、複数のキャリア信号を扱う携帯電話端末向けなどに、電界効果型トランジスタ(FET)で構成する多ポートのRFスイッチ(SPNT:Single Pole N-Through: Nはポート数)が用いられるようになってきている。この種のRFスイッチには、送信信号の基本波に対して、低い高調波特性が要求されている。高調波を抑制するためには、オン状態にあるFETのオン抵抗の線形性を良くすることに加え、オフ状態のFETの良好な耐電力特性が必要になる。

## [0003]

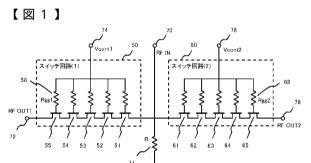

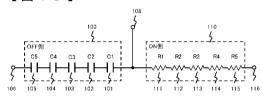

オフ状態の耐電力を向上させる一般的な手法として、特許文献1の図1に開示されているように、FETを多段直列接続する方法が用いられている。図1はRFスイッチとして、SPDT(SP2T)におけるFETを5段直列接続の例(従来例)である。RFの入力端子70は、スイッチ回路(1)50、スイッチ回路(2)60および抵抗71が接続され、抵抗71を介し接地されている。スイッチ回路(1)のFET51、52、53、54、55はソースとドレインが直列に接続され、FET51のソースが入力端子70に接続され、FET55のドレインが出力端子(1)72に接続されている。5つのFETのゲートは、それぞれ抵抗Rgg58を介し、制御端子(1)74に接続され、FET61のソースが入力端子70にFET65のドレインが出力端子(2)76に接続している。5つのFETのゲートは、それぞれ抵抗Rgg68を介し、制御端子(2)78に接続されている。

#### [0004]

50

20

10

30

スイッチ回路(1)50がオフ状態のとき、制御端子(1)74に負の電圧が印加され、FET51、52、53、54、55がオフ状態になる。これにより、入力端子70と出力端子(1)72は電気的に切断される。スイッチ回路(2)60がオン状態のときは、制御端子(2)78に正の電圧が印加され、FET61、62、63、64、65がオン状態になる。これにより、入力端子70から入力したRF信号はスイッチ回路(2)60を通過し出力端子(2)76に出力される。

#### [0005]

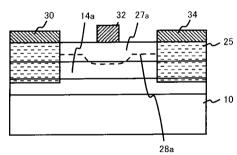

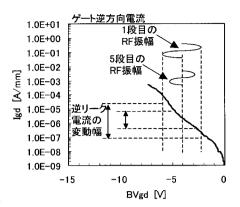

図2(a)および(b)は、オフ状態のスイッチ回路を構成するFETのゲート電圧( Ig) - ゲート電圧(Vg)特性およびオン状態のスイッチ回路を構成するFETのドレイン電流(Ids) - ドレイン電圧(Vds)特性を、それぞれ示す。

[0006]

図 2 ( a )において、オフ状態の耐電力特性を向上させるためには、RF信号の電力振幅(RF振幅)に対しゲート逆方向耐圧(Vgdo)が大きく、ゲート逆方向電流が0に近いことが望ましい。仮に、スイッチ回路(1)50がオフ状態のとき、理想的には、FET51、52、53、54、55の個々に加わるRF振幅は入力信号のRF振幅の1/5である。これは、FETが直列接続されているため、入力端子70と出力端子(1)72の間に加わった電力が均等に分圧されるためである。よって、理想的にはFETを5段直列接続することによって、1つのFETに比べ、耐電力特性を5倍にすることができる

【特許文献1】特開平8-139014号公報 図1

【発明の開示】

【発明が解決しようとする課題】

[0007]

RFスイッチにおいて、挿入損失を小さくすることも重要である。挿入損失はオン抵抗(Ron)が大きいと大きくなる。図2(b)において、オン状態のIds-Vdsの傾きが大きいこと、すなわち、Ronが小さいことが望ましい。しかし、FETが直列に接続されると、Ronが大きくなり、挿入損失が大きくなってしまう。例えば、スイッチ回路(2)のRonはFET61、62、63、64、65のそれぞれのRonの和となる。このように、直列接続の段数を増やし高調波特性を向上させると挿入損失が劣化してしまう。

[0008]

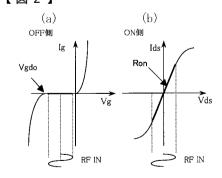

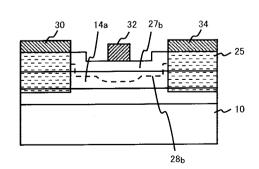

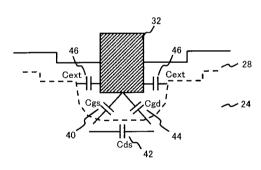

一方、RFスイッチを構成するFET自身のVgdoを向上させることにより耐電力特性を向上させようとすると、Ronが大きくなってしまう。例えば、図3および図4はこの問題を説明するための模式図である。半導体基板10上にチャネル層14a、表面層27a、27b上にソース電極30、ゲート電極32、ドレイン電極34を配置したFETである。ソース電極30およびドレイン電極下にnが領域25が形成されている。図3において、半導体層表面に空乏層28aが形成されている。図3のFETにおけるVgdoを向上させるため、表面層27aの一部を除去し、図4のように表面層27bのようなゲートリセスを形成する。これにより、空乏層28bがチャネル層14aにおよび、Ronが大きくなってしまう。このように、FETのVgdoを向上させようとするとRonが大きくなってしまう。このように、FETのVgdoを向上させようとするとRonが大きくなってしまう。よって、RFスイッチを構成するFET自身の改良によってRFスイッチの高調波特性を向上させると挿入損失の両立を図ることが困難であった。

[0009]

本発明の目的は、上記の問題に鑑み、高調波特性および挿入損失の優れたスイッチ回路及び半導体装置の製造方法を提供することである。

【課題を解決するための手段】

[0010]

20

10

30

本発明は、ソース電極またはドレイン電極の一方が第1の端子に接続され、制御端子に接 続されたゲート電極により、前記ソース電極と前記ドレイン電極との導通・非導通が制御 される第1のFETと、ソース電極またはドレイン電極の一方が前記第1のFETの前記 ソース電極またはドレイン電極の他方と直列接続され、前記制御端子に接続されたゲート 電極により、前記ソース電極と前記ドレイン電極との導通・非導通が制御される第2のF ETと、ソース電極またはドレイン電極の一方が前記第2のFETの前記ソース電極また はドレイン電極の他方と直列接続され、前記ソース電極またはドレイン電極の他方が第2 の端子と接続され、前記制御端子に接続されたゲート電極により、前記ソース電極と前記 ドレイン電極との導通・非導通が制御される第3のFETとを具備し、前記第1のFET と前記第2のFETと前記第3のFETとは、そのゲート電極が埋込層内に埋め込まれて なるとともに、前記第1のFETおよび前記第3のFETにおける埋込層に埋め込まれた 埋込厚が前記第2のFETにおける埋込層に埋め込まれた埋込厚よりも薄いことにより、 前記第1のFETのゲート電極に、前記第1のFETのドレイン電極の電圧に対し負の電 圧を印加した場合におけるドレイン電極とゲート電極との間の耐圧である前記第1のFE Tのゲート逆方向耐圧は前記第2のFETのゲート逆方向耐圧よりも大きく、かつ前記第 3のFETのゲート逆方向耐圧は前記第2のFETのゲート逆方向耐圧よりも大きいスイ ッチ回路である。本発明によれば、RF振幅の大きい信号が入力される1段目FETのV gdoが大きいため、高調波特性の優れたスイッチ回路を提供することができる。

[0011]

本発明は、ソース電極またはドレイン電極の一方が第 <u>1 の端子に</u>接続され、制御端子に 接続されたゲート電極により、前記ソース電極と前記ドレイン電極との導通・非導通が制 御される第1のFETと、ソース電極またはドレイン電極の一方が前記第1のFETの前 記ソース電極またはドレイン電極の他方と直列接続され、前記制御端子に接続されたゲー ト電極により、前記ソース電極と前記ドレイン電極との導通・非導通が制御される第2の FETと、ソース電極またはドレイン電極の一方が前記第2のFETの前記ソース電極ま たはドレイン電極の他方と直列接続され、前記ソース電極またはドレイン電極の他方が第 2 の端子と接続され、前記制御端子に接続されたゲート電極により、前記ソース電極と前 記ドレイン電極との導通・非導通が制御される第3のFETとを具備し、前記第1のFE Tと前記第2のFETと前記第3のFETとは、そのゲート電極が埋込層内に埋め込まれ てなるとともに、前記第1のFETおよび前記第3のFETにおける埋込層に埋め込まれ た埋込厚が前記第2のFETにおける埋込層に埋め込まれた埋込厚よりも薄いことにより 、前記第1のFETのオフ容量および前記第3のFETのオフ容量は前記第2のFETの オフ容量よりも小さいスイッチ回路である。本発明によれば、RF振幅の大きい信号が入 力される1段目FETのCoffが小さいため、高調波特性の優れたスイッチ回路を提供 することができる。

[0012]

本発明は、<u>前記第1の端子は入力端子または出力端子の一方であり、前記第2の端子は</u>前記入力端子または出力端子の他方であるスイッチ回路である。

[0013]

本発明は、前記第1のFETと前記<u>第3のFET</u>との間には、前記第2のFETが複数直列に設けられてなるスイッチ回路である。本発明によれば、FETの段数の多いスイッチ回路においても、高調波特性の優れたスイッチ回路を提供することができる。<u>本発明は、上記のスイッチ回路である第1スイッチ回路と、上記の別のスイッチ回路である第2スイッチ回路とを含み、前記第1スイッチ回路と前記第2スイッチ回路とが共通して前記第</u>1の端子に接続されているスイッチ回路である。

[0014]

本発明は、前記制御端子を接地することにより、前記非導通をなすスイッチ回路である。本発明によれば、制御端子を接地することにより、非導通をなすスイッチ回路において も高調波特性の優れたスイッチ回路を提供することができる。

[0018]

10

20

30

本発明は、前記第1のFET、前記第2のFET および前記第3のFET は、電子供給層とチャネル層を備えるHEMTとした スイッチ回路 である。本発明によれば、更に低雑音特性に優れた スイッチ回路 を提供することができる。本発明は、前記電子供給層が、前記チャネル層の上下に設けられている スイッチ回路 である。本発明によれば、更にドレイン電流を大きく取ることができる スイッチ回路 を提供することができる。本発明は、前記第1のFET、前記第2のFETおよび前記第3のFET は、GaAs系化合物半導体により構成されてなる スイッチ回路 である。本発明によれば、GaAs系化合物半導体を用いた スイッチ回路 において、高調波特性の優れた スイッチ回路 を提供することができる。【0019】

本発明は、ソース電極またはドレイン電極の一方が第1の端子に接続され、制御端子に 接続されたゲート電極により、前記ソース電極と前記ドレイン電極との導通・非導通が制 御される第1のFETと、ソース電極またはドレイン電極の一方が前記第1のFETの前 記ソース電極またはドレイン電極の他方と直列接続され、前記制御端子に接続されたゲー ト電極により、前記ソース電極と前記ドレイン電極との導通・非導通が制御される第2の FETと、ソース電極またはドレイン電極の一方が前記第2のFETの前記ソース電極ま たはドレイン電極の他方と直列接続され、前記ソース電極またはドレイン電極の他方が第 2 の端子と接続され、前記制御端子に接続されたゲート電極により、前記ソース電極と前 記ドレイン電極との導通・非導通が制御される第3のFETとを具備する半導体装置の製 造方法であって、前記ゲート電極が設けられるショットキ層上に埋込層を形成する工程と 、前記第1のFETおよび前記第3のFETのゲート電極が形される領域の前記埋込層を 露出し、前記第2のFETのゲート電極が形される領域の前記埋込層をマスク層で被覆し て、前記第1のFETおよび前記第3のFETの前記ゲート電極が形される領域の前記埋 込層の厚みを選択的に減じる工程と、前記第1のFET、第2のFETおよび前記第3の FETそれぞれの前記ゲートが形される領域の前記埋込層に前記ショットキ層を露出する 開口部を形成する工程と、前記開口部のそれぞれにゲート電極を形成する工程とを有する 半導体装置の製造方法である。本発明によれば、RF振幅の大きい信号が入力される1段 目FETのVgdoが大きいか、あるいはCoffが小さいか、あるいはその両方により 、高調波特性の優れた半導体装置の製造方法を提供することができる。

[0021]

本発明は、前記第1のFET<u>、</u>前記第2のFET<u>および前記第3のFET</u>は、電子供給層とチャネル層を備えるHEMTとした半導体装置の製造方法である。本発明によれば、更に低雑音特性に優れた前記半導体装置の製造方法を提供することができる。

[0022]

本発明は、前記電子供給層が、前記チャネル層の上下に設けられている半導体装置の製造方法である。本発明によれば、更にドレイン電流を大きく取ることができる半導体装置の製造方法を提供することができる。

[0023]

本発明は、前記第1のFET<u>、</u>前記第2のFET<u>および前記第3のFET</u>が、GaAs 系化合物半導体により構成されてなる半導体装置の製造方法である。本発明によれば、G aAs系化合物半導体を用いた半導体装置において、高調波特性の優れた半導体装置の製 造方法を提供することができる。

【発明の効果】

[0024]

<u>本発明</u>によれば、RF振幅の大きい信号が入力する1段目FETのVgdoを大きくし、またはCoffを低減させることにより、高調波特性および挿入損失の優れたスイッチ 回路及び半導体装置の製造方法を提供することができる。

【発明を実施するための最良の形態】

[0025]

従来の認識では、図1のスイッチ回路(1)がオフ状態のとき、入力端子70に入力したRF振幅は理想的には各FET51、52、53、54、55に均等に加わるはずであ

10

20

30

40

る。しかし、本発明者は、実際には1段目のFET51に加わるRF振幅が最も大きく、 5段目のFET55に加わるRF振幅が最も小さいことを見出した。

#### [0026]

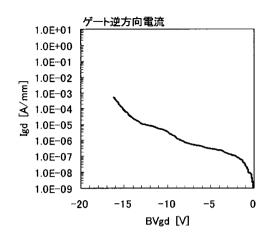

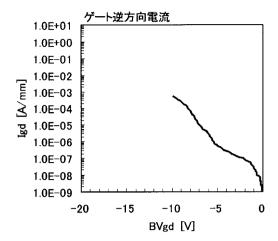

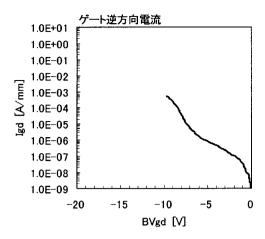

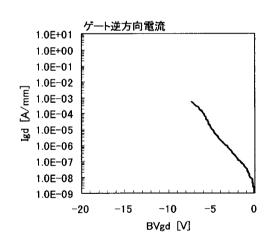

図5はスイッチ回路(1)50を構成する1段のFETのゲート逆方向電流(Igd)-ゲート逆方向電圧(BVgd)を示している。1段目FET51のRF振幅は5段目FET55のRF振幅より大きく、ゲート逆方向電流(Igd)の変動幅も大きい。1段目FET51でゲート逆方向電流が増加すると、オフ状態のスイッチ回路(1)50を通しRF信号が漏れ、RF信号が歪み、高調波特性が劣化する。

#### [0027]

そこで、本発明においては、1段目FET(第1のFET)をVgdoの大きなFETとすることにより、最も大きなRF振幅が加わる1段目FETのゲート逆方向電流を抑制する。さらに、他段のFET(第2のFET)は1段目のFETよりVgdoは小さく、Ronの小さなFETとすることにより、全てのFETをVgdoの大きなFETとした場合に比べ、スイッチ回路全体のRonの劣化は小さくできる。これにより、耐電力特性が良くRonが小さい、すなわち高調波特性が良く、挿入損失の小さなスイッチ回路を実現ですることができる。

#### 【実施例1】

## [0028]

実施例1はFETとして電子供給層とチャネル層を有することで、二次元電子ガスによる低雑音特性に優れた、いわゆるHEMT(High Electron Mobility Transistor)を用いたRFスイッチの例であり、FETを5段直列接続したSPDTの例である。

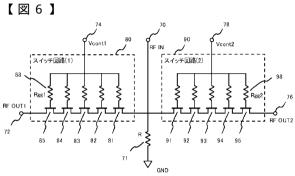

#### [0029]

図6は実施例1の回路構成を示す図である。RFの入力端子70は、スイッチ回路(1)80、スイッチ回路(2)90および抵抗71が接続され、抵抗71を介し接地されている。スイッチ回路(1)80において、1段目FET(第1のFET)81のYースが入力端子70に接続され、ゲートが抵抗Rgg888を介し、制御端子(1)74に接続されている。2段目FET(第2のFET)82のYースは1段目FET(第1のFET)81のFET)81のFレインに接続され、ゲートはゲートが抵抗Rgg888を介し、制御端子(1)74に接続されている。さらに3、4段目FET(第2のFET)83、84はソースとドレインが直列接続され、ゲートが抵抗Rgg888を介し、制御端子(1)74に接続されている。5段目FET(第3のFET)85のソースが、4段目FET(第2のFET)84のドレインに接続され、ゲートが抵抗Rgg888を介し、制御端子(1)74に接続され、ドレインが出力端子(72)に接続されている。

#### [0030]

すなわち、スイッチ回路(1)80は、入力端子70または出力端子72のいずれか一方に接続され、制御端子(1)74に接続されたゲート電極により、導通・非導通が制御される第1のFET<u>81</u>と、入力端子70または出力端子72のいずれか他方と前記第1のFET80との間に接続され、制御端子(1)74に接続されたゲート電極により、導通・非導通が制御される第2のFET82とを具備している。ここで、「入力端子70または出力端子72のいずれか一方に接続され」とは、「第1のFET81のソースまたはドレイン(実施例1ではソース)が入力端子70または出力端子72のいずれか一方(接続されている」ことである。また、「入力端子70またはドレイン(実施例1ではドレイン)が、入力端子70またはのFET82のソースまたはドレイン(実施例1ではドレイン)が、入力端子70またはコカ端子72のうち第1のFET80のソースまたはドレインに接続されていない方の入力端子70または出力端子72(実施例1では出力端子72)に接続されていない方の入力端子70またはドレイン(実施例1ではピース)が第1のFET80の入力端子70に接続

40

10

20

30

10

20

30

40

50

また、スイッチ回路(1)80は入力端子70または出力端子72のいずれか他方に接続され、制御端子(1)74に接続されたゲート電極により、導通・非導通が制御される第3のFET85を備えている。さらに、第1のFET81と入力端子70または出力端子72のいずれか他方との間には、第2のFET82、83、84、が複数直列に設けられている。ここで、「入力端子70または出力端子72のいずれか他方に接続され」とは、「第3のFET85のソースまたはドレイン(実施例1ではドレイン)が入力端子70または出力端子72のうち第1のFET81のソースまたはドレインに接続されていない方の入力端子70または出力端子72(実施例1では出力端子72)に接続されていない方(実施例1ではソース)が第2のFET84のソースまたはドレインのうち第1のFET81に接続されていない方(実施例1ではドレイン)に接続されている」ことである。また、ゲート電極とはゲートのことである。

[0032]

スイッチ回路(2)90においても同様に、1段目FET(第1のFET)91、2から4段目FET(第2のFET)92、93、94、5段目FET(第3のFET)95のソースとドレインが直列に接続され、1段目FET(第1のFET)61のソースが入力端子70に、5段目FET(第3のFET)65のドレインが出力端子(2)76に接続している。FET91、92、93、94、95のゲートは、それぞれ抵抗Rgg988を介し、制御端子(2)78に接続されている。

[0033]

スイッチ回路(1)80がオフ状態のとき、制御端子(1)74に負の電圧が印加され、FET81、82、83、84、85がオフ状態になる。これにより、入力端子70と出力端子(1)72は電気的に切断される。スイッチ回路(2)90がオン状態のとき、制御端子(2)78に正の電圧が印加され、FET91、92、93、94、95がオン状態になる。これにより、入力端子70から入力したRF信号はスイッチ回路(2)90を通過し出力端子(2)76に出力される。「制御端子に接続されたゲート電極により、導通・非導通が制御される」とは「制御端子74に負電圧が印加されたときFETが電気的に切断され、すなわちRF信号が切断され、制御電極が正電圧が印加されたときFETにRF信号が通過する」ことである。

[0034]

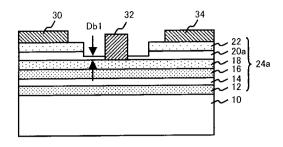

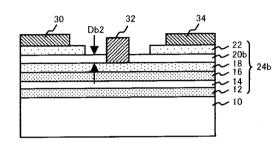

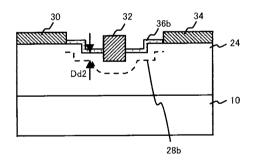

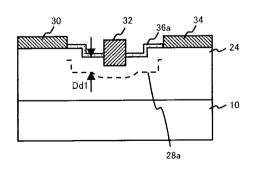

図7および図8は実施例1に係るRFスイッチに用いるFETの断面図である。図7は1段目FET(第1のFET)81、91および5段目FET(第3のFET)85、95の断面図であり、図8は2段目から4段目FET(第2のFET)82、83、84、92、93、94の断面図である。図7および8は、チャネル層14の上下に電子供給層12、16を設けて、2次元電子ガスをチャネル層14の上下に生じさせる構造を持つHEMTについて、説明するものである。この構造のHEMTは、ドレイン電流が大きく取れるため、スイッチ回路に好適である。なお、本発明のFETは、GaAsやAlGaAsなどの化合物半導体によって構成することができ、実施例1においてもGaAs、InGaAs系化合物半導体とは、例えば、GaAs、AlGaAs、InGaAsである。

[0035]

図7および図8において、GaAs半導体基板10上にバッファ層(図示せず)を介し、半導体層24aまたは24bとして、シリコンを添加したN型のAlGaAs電子供給層12、不純物を添加していないInGaAsチャネル層14、シリコンを添加したN型のAlGaAs電子供給層16、不純物を添加しないAlGaAsショットキ層18、不純物を添加しないGaAs埋込層20aまたは20b、シリコンを添加したN型のGaAs高濃度層22が、例えばMOCVD法により成膜されている。高濃度層22上にソース電極30およびドレイン電極34が形成されている。ソース電極30とドレイン電極34の間の高濃度層22が除去され、ゲートリセスが形成されている。ゲート電極32下の埋込層20aまたは20bに埋め込まれている。ここで、埋込厚とは、ゲート電極32が半導体層24aまたは24bに埋め

込まれている厚さとする。

#### [0036]

また、上記HEMTの製造方法は、次のとおりである。まず、GaAs基板10上にバッファ層(図示せず)、電子供給層12、チャネル層14、電子供給層16、ショットキ層18、GaAs埋込層20a,20bおよび高濃度層22を例えばMOCVD法によって成長する。次に、各FETのゲート電極32が形成される領域の高濃度層22を選択的に除去して、埋込層20a,20bを露出する。次に、1段目FET(第1のFET)81,91と、5段目FET(第3のFET)85,95が形成される領域の埋込層20aを露出し、2から4段目FET(第2のFET)82、83、84、92、93、94が形成される領域の埋込層20bを被覆する、たとえばフォトレジストからなるマスク層を形成する。次に、上記マスク層を利用して、露出している埋込層20aをエッチングし、その厚みを減じる。次に、各FETのゲート電極32を形成する領域の埋込層20a,20bにショットキ層18を露出する開口を形成した後、そこにゲート電極32を形成する。最後に、各FETの高濃度層22上にソース電極30およびドレイン電極34を形成することにより、図7および図8のHEMTが完成する。

#### [0037]

図7においては、ゲートリセスが埋込層20aの途中まで形成されており、ゲート電極32は残りの埋込層20aに埋め込まれている。このときの埋込厚をDb1とする。一方、図8においては、ゲートリセスは埋込層20bの表面まで形成されており、ゲート電極32は埋込層20bに埋め込まれている。このときの埋込厚をDb2とする。実施例1においてはDb1<Db2であり、Db1を20nm、Db2を35nmとした。すなわち、1段目FET(第1のFET)81、91および5段目FET(第3のFET)85、95のゲートの埋込厚Db1は、2から4段目FET(第2のFET)82、83,84、92、93、94の埋込厚Db2より薄い。すなわち、1段目FET(第1のFET)81および5段目FET(第2のFET)82、83,84、92、93、94の埋込厚Db2より薄い。すなわち、1段目FET(第1のFET)81および5段目FET(第2のFET)82、83、84、92、93、94とは、そのゲート電極32が埋込層20内に埋め込まれてなるとともに、1段目FET(第1のFET)81における埋込層に埋め込まれた埋込厚Db1は、前記第2のFETにおける埋込層に埋め込まれた埋込厚Db

## [0038]

## [0039]

表1に、各埋込厚を有するFETのゲート幅1mmあたりのRonおよびVgdoを示す。埋込厚35nmのFETのRonは1.73 mmに対し、埋込厚20nmのFETは1.93 mmとRonが大きくなっている。一方、埋込厚35nmのFETのVgdoは-9.8Vに対し、埋込厚20nmのFETでは-16.2Vと大きく改善している

#### [0040]

10

20

30

#### 【表1】

| 埋込厚  | $Ron(\Omegamm)$ | Vgdo(V) |

|------|-----------------|---------|

| 35nm | 1.73            | -9.8    |

| 20nm | 1.93            | -16.2   |

#### [0041]

このように、実施例 1 においては、 1 段目 F E T (第 1 の F E T) 8 1、 9 1 および 5 段目 F E T (第 3 の F E T) 8 5、 9 5 の V g d o を 2 から 4 段目 F E T (第 2 の F E T) 8 2、 8 3、 8 4、 9 2、 9 3、 9 4 に比べ高大きくすることができた。また、 2 から 4 段目 F E T (第 2 の F E T) 8 2、 8 3、 8 4、 9 2、 9 3、 9 4 の R o n は、 1 段目 F E T (第 1 の F E T) 8 1、 9 1 および 5 段目 F E T (第 3 の F E T) 8 5、 9 5 より小さくすることができた。

#### [0042]

これにより、最もRF振幅の大きくなる1段目FET(第1のFET)81,91において、ゲート逆方向電流が小さく、Vgdoが大きいため、大きいRF振幅の信号が入力しても、ゲート逆方向電流の変動幅を小さくでき、良好な耐電力特性を得られる。

#### [0043]

5 段直列接続したSPDTの回路は単純に図13のように表される。オフ状態のスイッチ回路100では容量101、102、103、104、105が直列に接続され、オン状態のスイッチ回路110では抵抗111、112、113、114、115が直列に接続されている。オフ状態のスイッチ回路100においてはCoff(オフ容量)が重要であり、オン状態のスイッチ回路110においてはRonが重要となる。

## [0044]

実施例1においては、1段目FET (第1のFET)81、91および5段目FET(第3のFET)85、95を埋込厚20nm、その他のFET(第2のFET)82、83、84、92、93、94の埋込厚を35nmとしている。そこで、ゲート幅2.4mmの場合のスイッチ回路(1)全体のRonを計算する。1.73 mm/2.8mm×3+1.93 mm/2.8mm×2=3.23 となる。例えば、5段のFET全てが埋込厚35nmまたは20nmの場合は、ぞれぞれ、1.73 mm/2.8mm×5=3.

#### [0045]

5段のFET全てを埋込厚20nmとすると、全てを埋込厚35nmにした場合に比べスイッチ回路全体のRonは約12%大きくなってしまう。しかし、実施例1においては、全てのFETを埋込厚35nmにした場合に比べ、Ron増加を約5%とすることができた。このように、RF振幅が大きい1段目FET(第1のFET)81、91および5段目FET(第3のFET)85、95の埋込厚のみを大きくすることによりRonの増加は少なく、かつ、RF振幅の大きな信号が入力しても、ゲート逆方向電流を抑制し、耐電力特性の高いスイッチ回路を実現できた。

## [0046]

#### [0047]

10

20

30

#### 【表2】

| 埋込厚  | Cgs(pF/mm) | Cgd(pF/mm) | Cds(pF/mm) | Coff(pF/mm) |

|------|------------|------------|------------|-------------|

| 35nm | 0.380      | 0.288      | 0.135      | 0.299       |

| 20nm | 0.352      | 0.253      | 0.134      | 0.281       |

【 0 0 4 8 】 【数 1 】

$$Coff = \frac{Cgs \cdot Cgd}{Cgs + Cgd} + Cds$$

[0049]

図14は、これを説明するためのゲート電極付近の模式図である。半導体層24中に、表面およびゲート電極32下に空乏層28が形成されている。ソースとドレイン間の容量がCds42、ゲート下空乏層のソース側がCgs40、ゲート下空乏層のドレイン側がCgd44である。ゲートが埋め込まれているため、ゲートの埋込部分の側部に外部容量Cext46が形成される。埋込厚が小さいと、Cext46が小さくなりCoffを小さくすることができた。

[0050]

このように、実施例1においては、1段目FET(第1のFET)81、91および5 段目FET(第3のFET)85、95のCoffを2から4段目FET(第2のFET)8 2、83、84、92、93、94に比べ小さくすることができた。

[ 0 0 5 1 ]

1段目FET(第1のFET)81、91のCoffが小さくなることからインピーダンスが小さくなり、2段目から4段目FET(第2のFET)82、83、84、92、93、94に比べ、RF振幅を小さくする方向に働く。これにより、1段目FET(第1のFET)81、91のゲート逆方向電流が流れ難い方向に働き、スイッチ回路の高調波特性がより改善される。

[0052]

以上のように、実施例1においては、最もRF振幅の大きくなる1段目FET(第1のFET)81、91のVgdoを大きくしかつCoffを低減することにより高調波特性を改善し、さらに、2段目から4段目FET(第2のFET)82、83、84、92、93、94のRonは1段目FET(第1のFET)81、91より小さいため、スイッチ回路80、90のRonは、全てのFETのVgdoを向上させかつCoffを削減させた場合より小さくすることができる。

[0053]

すなわち、1段目FET(第1のFET)81,91および5段目FET(第3のFET)85、95は、ゲート逆方向耐圧(Vgdo)が2段目から4段目FET(第2のFET)82、83,84、92、93、94より大きいFETとオフ容量(Coff)が2段目から4段目FET(第2のFET)82、83,84、92、93、94より小さいFETの少なくとも一方である。また、2段目から4段目FET(第2のFET)82、83,84、92、93、94はオン抵抗(Ron)が1段目FET(第1のFET)81、91および5段目FET(第3のFET)85、95より小さいFETである。これにより、高調波特性および挿入損失に優れたスイッチ回路を有する半導体装置を提供することができる。

[0054]

10

20

30

40

なお、実施例1では1段目FET(第1のFET)81、91が、2から4段目FET(第2のFET)82、83,84、92、93,94に比べて、Coffが小さく、かつ、Vgdoが大きくなっている。実施例1では、この両方の効果によって高調波特性が向上している。しかし、1段目FET(第1のFET)81、91のVgdoが大きいことだけ、あるいはCoffが小さいことだけでも、高調波特性が向上できることは言うまでもない。

#### [0055]

たとえば、埋込層20からチャネル層14までの厚みが小さい場合には、図14において説明したCextが、1段目FET(第1のFET)81、91と2から4段目FET(第2のFET)82、83,84、92、93,94とで違っていても、ゲート電極32がチャネル層14に接近しているため、それ以外の容量成分が十分に大きく、Cextの差が特性に殆ど寄与しない。しかし、図3および図4で説明したように、空乏層28aおよび28bのチャネル層14に対する深さの効果は発揮されることから、Vgdoについては有意な差が生じる。その結果、全体の高調波特性が改善される。

#### [0056]

また、たとえば埋込層 2 0 からチャネル層 1 4 までの厚みが大きい場合には、図 3 および図 4 で説明した空乏層 2 8 a および 2 8 b の何れもが、チャネル層 1 4 まで十分に延びないことから、Vgdoについては有意な差が生じない。しかし、ゲート電極 3 2 はチャネル層から離間してゲート電極 3 2 下部の容量成分が小さくなる。このことから、図 1 4 において説明したCextの違いが有意となり、その結果、やはり全体の高調波特性が改善される。

#### [0057]

以上は、1段目FET(第1のFET)81、91と2から4段目FET(第2のFET)82、83,84、92、93、94の関係について説明したが、これは5段目FET(第3のFET)85、95についても同様であることはもちろんである。すなわち、5段目FET(第3のFET)85、95が1段目FET(第1のFET)81、91と異なる構造であっても良い。たとえば、1段目FET(第1のFET)81、91が2から4段目FET(第2のFET)82、83,84、92、93、94に比べて、Vgdoが大きく、かつCoffが小さい場合に、5段目FETはVgdoだけが大きく構成されてもよく、その組み合わせは任意である。

#### [0058]

実施例1においては、1段目FET(第1のFET)81、91および5段目FET(第3のFET)85、95の埋込厚を薄くしているが、これは入力端子70と出力端子72、76の両方からRF振幅の大きな信号が入力されるためである。RF振幅の大きな信号が、入力端子70のみから入力される場合は、1段目FET81、91のみ埋込厚を薄くすれば良い。また、RF振幅の大きな信号が、出力端子72、76のみから入力される場合は、5段目FET85、95のみ埋込厚を薄くすれば良い。

#### 【実施例2】

#### [0059]

実施例2もFETとしてHEMTを用い、FETを5段直列接続したSPDTの例である。回路構成は実施例1と同じである。図15は実施例2の1段目FET(第1のFET)81、91および5段目FET(第3のFET)85、95の断面を示す模式図であり、図16は2段目から4段目FET(第2のFET)82、83、84、92、93、94の断面を示す模式図である。半導体基板10上に半導体層24が積層されている。半導体層24中の各層は実施例1と同様である。半導体層24上にソース電極30、ドレイン電極34が形成されている。ゲート電極32が半導体層24に埋め込まれている。ソース電極30とゲート電極32が半導体層24に埋め込まれている。ソース電極30とゲート電極32の間、並びにゲート電極32とドレイン電極34の間の半導体層24表面には保護膜としてSiNx膜(第1の窒化シリコン膜)36aまたはSiNy膜(第2の窒化シリコン膜)36bが形成されている。

#### [0060]

10

20

30

10

20

30

40

50

以下に、上記HEMTの製造方法について説明する。まず、GaAs基板10上に半導体層24を形成する。半導体層24の詳細は、例えば、図7および図8で説明した、バッファ層(図示せず)、電子供給層12、チャネル層14、電子供給層16、ショットキ層18、GaAs埋込層20a,20bおよび高濃度層22を例えばMOCVD法によって成長することによって実現される。次に、ゲートリセスを形成する。このゲートリセスは、ゲート電極32によって所望の電位が与えられる条件を考慮した深さで形成されるが、たとえば図7および図8で説明した構造であれば、高濃度層22および埋込層20a(20bを含む場合もある)を除去して形成される。

#### [0061]

次に、このゲートリセスが形成された半導体層24上にSiN×膜(第1の窒化シリコン膜)36aを形成する。この場合、SiN×膜36aは各FETを含む基板全面に形成される。この工程により、2から4段目FET(第2のFET)82、83、84、92、93、94のゲート電極とソース電極の間並びにゲート電極とソース電極の間となるべき領域にSiN×膜36が設けられることになる。次に、1段目FET(第1のFET)81、91と、5段目FET(第3のFET)85、95が形成される領域のSiN×膜36aを認出し、上記2から4段目FETが形成される領域のSiN×膜36aを被覆する、たとえばフォトレジストからなるマスク層を形成する。次に、上記マスク層を利用して、露出しているSiN×膜36aを除去する。

#### [0062]

次に、1段目FETと5段目FETが形成される領域に、SiNx膜36よりも窒素組成比が小さいSiNy膜37を形成する。窒素組成比の小さいSiNy膜37は、SiNx膜36に比べて、成膜時に半導体層24に与えるダメージが大きいことから、このSiNy膜をSiNx膜36よりも後に成膜することで、SiNx膜36が残存する領域に与えられるダメージを軽減することができる。この工程により、上記1段目FET(第1のFET)と、5段目FET(第3のFET)のゲート電極とソース電極の間並びにゲート電極とソース電極の間となるべき領域にSiNy37が設けられることになる。次に、各FETのゲート電極32を形成する領域のSiNx膜36,SiNy膜37を露出する開口を形成した後、そこにゲート電極32を形成する。最後に、各FETの高濃度層22上にソース電極30およびドレイン電極34を形成することにより、図15および図16のHEMTが完成する。

#### [0063]

## [0064]

また、図15、図16における、半導体表面からの空乏層28a、28bの空乏層幅をそれぞれDd1、Dd2とすると、Dd1>Dd2となっている。これは、SiNx膜の窒素組成比がSiNy膜比べ大きいことに起因する。SiNx膜およびSiN膜の形成は、例えば、プラズマCVD装置を用いRF周波数を制御することで実現できる。実施例2においては、SiNx膜を形成するときのRF周波数を、SiNy膜形成時より低くすることにより、SiNx膜の窒素組成比をSiNy膜より小さくできた。

## [0065]

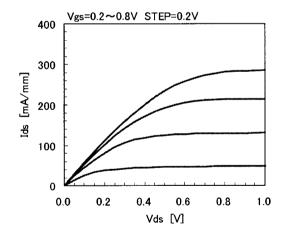

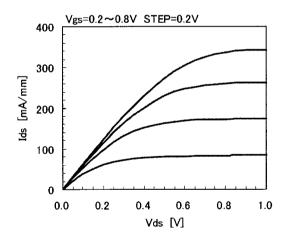

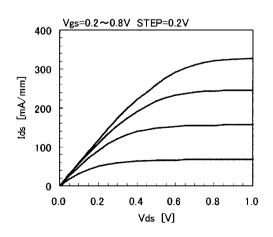

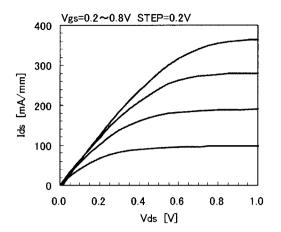

保護膜としてSiNx膜およびSiNy膜を有するFETのドレイン電流(Ids)・ドレイン電圧(Vds)特性をそれぞれ図17および図18に示す。SiNx膜を有するFETのIdsのVdsに対する傾きは、SiNy膜を有するFETより小さい。一方、保護膜としてSiNx膜およびSiNy膜を有するFETのゲート逆方向電流(Igd)・ゲート逆方向電圧(BVgd)特性をそれぞれ図19および図20に示す。SiNx膜を有するFETのゲート逆方向電流は、SiNy膜を有するFETに比べ小さくなってい

る。

#### [0066]

表3に、保護膜としてSiNx膜およびSiNy膜を有するFETのゲート幅1mmあたりのRonおよびVgdoを示す。SiNy膜を有するFETのRonで1.73 mmに対し、SiNx膜を有するFETでは1.76 mmとRonが大きくなっている。一方、SiNy膜を有するFETのVgdoは-7.3Vに対し、SiNx膜を有するFETでは-9.6Vと改善している。

[0067]

【表3】

| 保護膜   | $Ron(\Omegamm)$ | Vgdo(V) |

|-------|-----------------|---------|

| SiNx膜 | 1.81            | -9.6    |

| SiNy膜 | 1.76            | -7.3    |

#### [0068]

実施例1と同様に、最もRF振幅の大きくなる1段目FET(第1のFET)81,91においてSiNx膜を使用しているため、大きいRF振幅の信号が入力しても、ゲート逆方向電流の変動幅を小さくできる。これにより高調波特性を改善できる。

#### [0069]

一方、実施例 2 における、ゲート幅 2 . 4 m m の場合のスイッチ回路(1 ) 全体の R o n は、1 . 7 6 m m / 2 . 8 m m × 3 + 1 . 8 1 m m / 2 . 8 m m × 2 = 3 . 1 8 となる。例えば、5 段の F E T 全てが S i N y 膜を有する F E T の場合は、1 . 7 6 m m / 2 . 8 m m × 5 = 3 . 1 4 となる。

#### [0070]

実施例2の場合は、1段目FET(第1のFET)および5段目FET(第3のFET)にSiNx膜を適用したことによりRonの増加は1.3%であり、実施例1の場合の約5%に比べRonの増加を小さくすることができた。これにより、実施例1に比べ、挿入損失の増加を小さくできる。

## [0071]

また、表 4 に保護膜として SiNx 膜および SiNy 膜を有する FETOCgs、 Cgd、 Cds、 Coff を示す。各容量の求め方は実施例 1 と同様である。SiNy 膜を有する FETOCoff は 0.304 pF/mmに対し、SiNx 膜を有する FET は 0.299 pF/mm と Coff が小さくなっている。このように、SiNx 膜を有する FET は Coff が約 2%減少している。SiNx 膜を使用することにより、表面空乏層幅 Dd は Dd できためである。 Dd 1 の Df 1 の Df 2 の Df 2 の Df 2 の Df 3 の Df 2 の Df 3 の Df 3 の Df 4 の Df 3 の Df 5 の Df 5 の Df 5 の Df 5 の Df 6 の Df 5 の Df 6 の Df 5 の Df 5 の Df 6 の Df 6 の Df 5 の Df 6 の Df 6 の Df 6 の Df 6 の Df 5 の Df 6 の Df 6 の Df 6 の Df 6 の Df 7 の Df 8 の Df 9 の Df 9

[0072]

#### 【表4】

| 保護膜   | Cgs(pF/mm) | Cgd(pF/mm) | Cds(pF/mm) | Coff(pF/mm) |

|-------|------------|------------|------------|-------------|

| SiNx膜 | 0.380      | 0.288      | 0.135      | 0.299       |

| SiNy膜 | 0.389      | 0.300      | 0.135      | 0.304       |

#### [0073]

このように、実施例2においても、スイッチ回路のRonの増加を抑えつつ、Vgdo

10

30

20

40

を大きくしかつ Coffを削減できる。すなわち挿入損出を抑えつつ、高調波特性を改善することができる。

#### 【実施例3】

#### [0074]

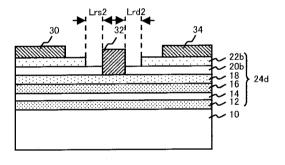

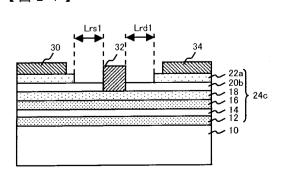

実施例3もFETとしてHEMTを用い、FETを5段直列接続したSPDTの例である。回路構成は実施例1と同じである。図21は実施例3の1段目FET(第1のFET)81、91および5段目FET(第3のFET)85、95の断面を示す模式図であり、図22は2段目から4段目FET(第2のFET)82、83、84、92、93、94の断面を示す模式図である。各FETは、そのゲート電極はゲートリセス内に設けられている。構成は図8とほとんど同じであるがゲートリセス幅が異なっている。ここで、ゲートリセス幅とは、ゲート電極32と高濃度層22a,22bの距離である。

[0075]

1 段目FET(第 1 のFET)および 5 段目FET(第 3 のFET)のソース側のゲートリセス幅Lrs 1 およびドレイン側のゲートリセス幅Lrd 1 とし、 2 段目から 4 段目FET(第 2 のFET)ソース側およびドレイン側のゲートリセス幅をそれぞれLrs 2、Lrd 2 とした。実施例 3 においては、Lrs 1 >Lrs 2 かつLrd 1 >Lrd 2 であり、Lrs 1 =Lrd 1 = 0 .5 μm、Lrs 2 =Lrd 2 = 0 .3 μmとした。すなわち、1 段目FET(第 1 のFET)8 1、9 1 および 5 段目FET(第 3 のFET)8 5、9 5 のゲートリセス幅は、 2 から 4 段目FET(第 2 のFET)8 2、8 3 ,8 4、9 2、9 3、9 4 のゲートリセス幅より広い。

[0076]

1段目および5段目FETにおいては、ゲート電極とn <sup>+</sup> 高濃度層の距離を遠くできるため、Ronは大きくなるものの、Vgdoを大きくできる。また、実施例1および2ほどではないがCoffも小さくできた。これにより、実施例3においても、スイッチ回路のRonの増加を抑えつつ、Vgdoを大きくできる。すなわち挿入損出を抑えつつ、高調波特性を改善することができる。

[0077]

[0078]

なお、実施例3では、1段目FET(第1のFET)81、91および5段目FET(第3のFET)85、95のVgdoとCoffの両方が、2から4段目FET(第2のFET)82、83、84、92、93、94に対して異なっているが、VgdoあるいはCoffの一方のみが異なる場合もある。

[0079]

たとえば、リセス幅を1段目FET(第1のFET)81、91および5段目FET(第3のFET)85、95、と2から4段目FET(第2のFET)82、83、84、92、93、94で異ならせたとしても、そのゲートリセス幅自体がそれぞれのFETで十分に大きい場合、ソース・ドレイン間容量(Cgs)が小さくなる。このことから、何れのFETにおいてもCoffは実質同等となり、Vgdoの差が支配的な効果の差を生じることとなる。

[0080]

また、逆にゲートリセス幅自体がそれぞれ比較的小さい場合には、ソース・ドレイン間容量が大きくなって、Vgdoの差より、Coffの差が支配的な効果の差を生じることとなる。

[0081]

実施例 1 から 3 においては、FETとしてHEMTを用いたが、他のFET、例えばMESFET (Metal Semiconductor Field Effect Transistor) 用いることもできる。また、実施例 1 から 3 においては、FETを 5 段直列接続した SPD Tの例を示したが、 S

10

20

30

40

10

20

30

50

P3T、SP4T、SP5T、SP6T、SP7T、SP8Tのような、より複雑なRFスイッチにも適用できる。さらに、実施例1から3においては、FETの直列接続の段数を5段とした。しかし、RF振幅の大きい信号が入力端子と出力端子のいずれか一方からのみから入力する場合は、この段数は2段以上あればよい。また、RF振幅の大きい信号が入力端子および出力端子の両方から入力する場合は、この段数は3段以上あればよい。

## 【実施例4】

[0082]

実施例4は、携帯電話端末機器に使用されるRFアンテナスイッチモジュール(RFモジュール)である。図23は、本発明の実施例4に係る半導体装置を示すブロック図である。このRFモジュール120は、アンテナANTと複数のRF信号系とを切り替える機能を持つ。RFモジュール120は、半導体チップ122とローパスフィルタ(LPF)128、130とを有する。半導体チップ122には、制御回路124とRFスイッチ126とを有する。RFスイッチ126はいわゆるSP6Tの機能を備え、実施例1、2または3に係るスイッチ回路を有している。

[0083]

図示するRFスイッチ126は、GSM850-R×、GSM900-R×、DCS1800-R×、PCS1900-R×、DCS-T×、GSM-T×の6つのRF信号系を選択的にアンテナANTに接続する。DCS-T×とGSM-T×にはそれぞれLPF128、130が設けられている。制御回路124は、外部からの制御信号CTL1~CLT3信号により、RFスイッチ126内の各スイッチ回路制御端子を通じ、スイッチ回路の切り替えを制御する。チップ122には電源電圧Vddが与えられる。実施例4においても、高調波特性および挿入損失の小さいRFモジュールを提供することができた。

[0084]

以上、発明の好ましい実施形態について詳述したが、本発明は係る特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【図面の簡単な説明】

[0085]

【図1】図1は従来例に係るRFスイッチの回路構成を示す図である。

【図2】図2(a)はオフ状態のスイッチ回路を構成するFETのドレイン電圧(Ig) - ゲート電圧(Vg)特性、図(b)はオン状態のスイッチ回路を構成するFETのドレイン電流(Ids) - ドレイン電圧(Vds)特性を示した図である。

【図3】図3は従来例のFETの断面を表した模式図(その1)であり、従来例の問題を 説明するための図である。

【図4】図4は従来例のFETの断面を表した模式図(その2)であり、従来例の問題を 説明するための図である。

【図 5 】図 5 はスイッチ回路におけるゲート逆方向電流(Igd) - ゲート逆方向電圧( BVgd)を示した図である。

【図6】図6は実施例1に係るRFスイッチの回路構成を示す図である。

【図7】図7は実施例1に係るスイッチ回路の1段目および5段目FETの断面図である 40

【 図 8 】図 8 は実施例 1 に係るスイッチ回路の 2 段目から 4 段目 F E T の断面図である。

【図9】図9は実施例1に係るスイッチ回路の1段目および5段目FET(埋込厚20nm)のドレイン電流(Ids)-ドレイン電圧(Vds)特性を示す図である。

【図10】図10は実施例1に係るスイッチ回路の2段目から4段目FET(埋込厚35nm)のドレイン電流(Ids)-ドレイン電圧(Vds)特性を示す図である。

【図11】図11は実施例1に係るスイッチ回路の1段目および5段目FET(埋込厚20nm)のゲート逆方向電流(Igd)-ゲート逆方向電圧(BVgd)特性を示す図である。

【図12】図12は実施例1に係るスイッチ回路の2段目から4段目FET(埋込厚35

nm)のゲート逆方向電流(Igd)-ゲート逆方向電圧(BVgd)特性を示す図であ る。

【図13】図13は実施例1に係る5段直列接続したSPDTの回路を単純な回路で表し た図である。

【図14】図14は実施例1においてCoffが小さくなることを説明するためのゲート 電極付近の模式図である。

【 図 1 5 】図 1 5 は実施例 2 に係るスイッチ回路の 1 段目および 5 段目 F E T の断面図で ある。

【図16】図16は実施例2に係るスイッチ回路の2段目から4段目FETの断面図であ

【 図 1 7 】図 1 7 は実施例 2 に係るスイッチ回路の 1 段目および 5 段目 F E T ( S i N x 膜)のドレイン電流(Ids)・ドレイン電圧(Vds)特性を示す図である。

【 図 1 8 】図 1 8 は実施例 2 に係るスイッチ回路の 2 段目から 4 段目 F E T ( S i N y 膜 )のドレイン電流(Ids) - ドレイン電圧(Vds)特性を示す図である。

【図19】図19は実施例2に係るスイッチ回路の1段目および5段目FET(SiNx 膜)のゲート逆方向電流(Igd)・ゲート逆方向電圧(BVgd)特性を示す図である

【 図 2 0 】 図 2 0 は実施例 1 に係るスイッチ回路の 2 段目から 4 段目 F E T ( S i N y 膜 )のゲート逆方向電流(Igd)-ゲート逆方向電圧(BVgd)特性を示す図である。

【図21】図21は実施例3に係るスイッチ回路の1段目および5段目FETの断面図で

【 図 2 2 】図 2 2 は実施例 3 に係るスイッチ回路の 2 段目から 4 段目 F E T の断面図であ

【 図 2 3 】 図 2 3 は実 施 例 4 に か かる 携 帯 電 話 端 末 機 器 に 使 用 さ れ る R F ア ン テ ナ ス イ ッ チモジュールのブロック図である。

## 【符号の説明】

## [0086]

1 0 半導体基板 12, 16 電子供給層

14、14a チャネル層

1 8 ショットキ層

20、20a、20b 埋込層

22、22a、22b 高濃度層

24、24a、24b、24c、24d 半導体層

28、28a、28b 空乏層

3 0 ソース電極

3 2 ゲート電極

3 4 ドレイン電極

50.80 スイッチ回路(1)

5 1、6 1、8 1、9 1 1段目 F E T

5 2、6 2、8 2、9 2 2段目 F E T

53、63、83、93 3段目FET

5 4 \ 6 4 \ 8 4 \ 9 4 4 段目 F E T

55、65、85、95 5段目FET 58、68、88、98 抵抗Rgg

60,90 スイッチ回路(2)

7 0 入力端子

7 1 抵抗

7 2 出力端子(1)

7 4 制御端子(1) 10

20

30

40

| 7 | 6   | 出力端子(2) |

|---|-----|---------|

| 7 | 8   | 制御端子(2) |

| 1 | 2 2 | 半導体チップ  |

| 1 | 2 4 | 制御回路    |

| 1 | 2 6 | RFスイッチ  |

【図3】

【図4】

【図5】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図15】

【図17】

【図18】

【図19】

【図20】

【図22】

【図21】

【図23】

# フロントページの続き

(56)参考文献 特開2003-243977(JP,A)

特開平8-139014(JP,A) 特開2003-86767(JP,A) 特開昭61-65480(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 29/80-29/812

H01L 29/778

H01L 21/337-21/338