(19) **日本国特許庁(JP)**

審査請求日

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3665560号 (P3665560)

(45) 発行日 平成17年6月29日(2005.6.29)

(24) 登録日 平成17年4月8日 (2005.4.8)

(51) Int. C1. <sup>7</sup> F 1

HO3K 19/0175 HO3K 19/00 1 O 1 F HO3K 17/16 HO3K 17/16 L HO3K 17/687 F

請求項の数 4 (全 11 頁)

(21) 出願番号 特願2000-362821 (P2000-362821)

(22) 出願日 平成12年11月29日 (2000.11.29) (65) 公開番号 特開2002-164777 (P2002-164777A)

(43) 公開日 平成14年6月7日 (2002.6.7)

平成15年1月28日 (2003.1.28)

|(73)特許権者 000221199

東芝マイクロエレクトロニクス株式会社 神奈川県川崎市川崎区駅前本町25番地1

||(73)特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74)代理人 100058479

弁理士 鈴江 武彦

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100068814

弁理士 坪井 淳

||(74)代理人 100092196

弁理士 橋本 良郎

最終頁に続く

#### (54) 【発明の名称】半導体集積回路

## (57)【特許請求の範囲】

#### 【請求項1】

内部回路から供給される信号が入力する第1制御回路と、

前記第1制御回路の出力信号および前記内部回路から供給される信号が入力し、2つの制御出力ノードの電位を前記第1制御回路に帰還させ、互いの立ち上がりのタイミングおよび立ち下がりのタイミングが異なるとともに同一論理レベルの期間が異なる2つの出力信号を2つの出力ノードから出力する第2制御回路と、

前記第2制御回路の2つの出力信号が対応してゲートに供給される電流吐き出し用のPMOS FETおよび電流吸い込み用のNMOS FETの各ドレインが出力端子に接続された出力バッファ回路とを具備し、

前記第1制御回路は、内部回路から供給される信号の論理レベルと前記第2制御回路の2つの制御出力ノードから帰還する電位の論理レベルが所定の条件を満たした時に出力信号の論理レベルが確定し、

前記第2制御回路の出力信号は前記電流吐き出し用のPMOS FETおよび電流吸い込み用のNM OS FETのうちの一方のオン状態のFET がオフ状態に反転した後に他方のオフ状態のFET がオン状態になるように制御することを特徴とする半導体集積回路。

### 【請求項2】

前記第1制御回路は、

ソースが電源ノードに接続された第 1 の PMOS FETおよびこの第 1 の PMOS FETのドレインに ソースが接続された第 2 の PMOS FETからなる第 1 の PMOS制御回路と、ソースが接地ノード

に接続された第 1 の NMOS FETおよびこの第 1 の NMOS FETのドレインにソースが接続された 第 2 の NMOS FETからなる第 1 の NMOS制御回路とからなり、

前記第1のPMOS FETと前記第1のNMOS FETは各ゲートが共通に接続されており、前記第2のPMOS FETと第2のNMOS FETは各ドレインが共通に接続されて出力ノードになっていることを特徴とする請求項1記載の半導体集積回路。

#### 【請求項3】

前記第2制御回路は、

ソースが電源ノードに接続された第3のPMOS FETと、この第3のPMOS FETとゲート同士、ドレイン同士が接続され、ソースが第1の制御出力ノードとなる第3のNMOS FETと、ドレイン・ソース間が電源ノードと前記第1の制御出力ノードとの間に接続された第4のNMOS FETと、ドレイン・ソース間が前記第1の制御出力ノードと接地ノードとの間に接続された第5のNMOS FETとからなり、前記第3のPMOS FETと第3のNMOS FETの各ゲートに第1制御回路の出力ノードの信号が共通に入力し、前記第1の制御出力ノードの電位が前記第1のNMOS制御回路の第2のNMOS FETのゲートに帰還し、前記第3のPMOS FETと第3のNMOS FETの各ドレイン接続ノードの出力信号が前記出力バッファ回路の電流吐き出し用のPMOS FETのゲートに入力する第2のPMOS制御回路と、

ソースが接地ノードに接続された第6のNMOS FETと、この第6のNMOS FETとゲート同士、ドレイン同士が接続され、ソースが第2の制御出力ノードとなる第6のPMOS FETと、ソース・ドレイン間が電源ノードと前記第2の制御出力ノードとの間に接続された第4のPMOS FETと、ソース・ドレイン間が前記第2の制御出力ノードと接地ノードとの間に接続された第5のPMOS FETとからなり、前記第6のPMOS FETと第6のNMOS FETの各ゲートに第1制御回路の出力ノードの信号が共通に入力し、前記第2の制御出力ノードの電位が前記第1のPMOS制御回路の第2のPMOS FETのゲートに帰還し、前記第6のPMOS FETと第6のNMOS FETの各ドレイン接続ノードの出力信号が前記出力バッファ回路の電流吸い込み用のNMOS FETのゲートに入力する第2のNMOS制御回路と、

前記内部回路から供給される信号が入力し、この入力信号を前記第2のPMOS制御回路の第4のNMOS FETのゲートおよび第2のNMOS制御回路の第5のPMOS FETのゲートに直接に供給するとともに、この入力信号の反転信号を前記第2のPMOS制御回路の第5のNMOS FETのゲートに供給する接続ノード切換制御回路

とを具備することを特徴とする請求項1または2記載の半導体集積回路。

## 【請求項4】

前記入力信号の反転信号は、前記入力信号を1個のインバータ回路で反転させた信号を共通に使用することを特徴とする請求項3記載の半導体集積回路。

【発明の詳細な説明】

[0001]

## 【発明の属する技術分野】

本発明は、半導体集積回路(LSI) に係り、特に出力回路の貫通電流を低減させるように制御する出力制御回路に関するもので、例えばCMOS LSIに使用されるものである。

[0002]

【従来の技術】

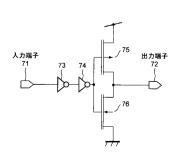

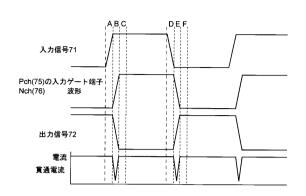

図8は、従来のLSIのCMOS構成の出力回路の一例を示す。

[0003]

LSI 内部回路から入力端子71に供給される入力信号は、2段のCMOSインバータ73,74 を介してCMOSインバータ構成の出力バッファ回路70に入力する。この出力バッファ回路70は、ソース・ドレイン間が電源ノードと出力端子72との間に接続された電流吐き出し用のPMOS FET75と、ドレイン・ソース間が出力端子72と接地ノードとの間に接続された電流吸い込み用のNMOS FET76とからなり、上記したようにドレインが共通に出力端子に接続された2つのFET75,76は、各ゲートが共通に接続されており、プッシュプル駆動される。

[0004]

20

30

このプッシュプル駆動に際して、一方のオン状態のFET がオフ状態に反転する前に他方のオフ状態のFET がオン状態になると、CMOS FETが同時にオン状態の期間が存在し、電源ノードと接地ノードとの間でCMOS FETを貫通する電流が流れる。この点について以下に詳細に説明する。

### [00005]

図9は、図8の出力回路の動作波形の一例を示す。

#### [0006]

入力信号が期間 A に "L" から "H" に変化し、2 段のCMOSインバータの前段の出力信号が期間 B に "H" から "L" に変化し、2 段のCMOSインバータの後段の出力信号(出力バッファ回路の入力信号)が期間 C に "L" から "H" に変化する。これにより、出力バッファ回路のPM OS FETはオン状態からオフ状態に変化し、NMOS FETはオフ状態からオン状態に変化するので、出力端子の出力信号は "H" から "L" に変化する。

#### [0007]

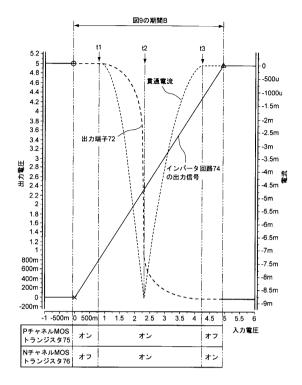

この際、図10に示すように、出力バッファ回路の入力信号の論理レベルが"L" から"H" に遷移(変化)する過程において、NMOS FETの閾値電圧 V thn を越えてNMOS FETがオン状態になった時点 t 1 では、PMOS FETは未だオン状態を維持しているので、貫通電流が流れ始め、時刻 t 2 で貫通電流の値がピークに達する。そして、出力バッファ回路の入力信号がPMOS FETの閾値電圧 V thp を越えた時点 t 3 でPMOS FETがオフ状態になり、貫通電流が流れなくなる。

### [00008]

上記とは逆に、出力回路の入力信号のレベルが"H" から"L" に変化する過程においてPMOS FETの閾値電圧 V thp を越えてPMOS FETがオン状態になった時点では、NMOS FETは未だオン状態を維持しているので、貫通電流が流れ始め、やがて貫通電流の値がピークに達する。そして、出力バッファ回路の入力信号がNMOS FETの閾値電圧 V thn より低くなった時点でNMOS FETがオフ状態になり、貫通電流が流れなくなる。

#### [0009]

上記したように従来の半導体集積回路の出力バッファ回路は、CMOS FETのプッシュプル駆動に際して貫通電流が流れるが、この貫通電流はFET のサイズが大きくなると多くなり、消費電流の増大をまねく。

## [0010]

【発明が解決しようとする課題】

上記したように従来の半導体集積回路のCMOS構成の出力バッファ回路は、CMOS FETのサイズが大きくなると貫通電流が大きくなり、消費電流の増大をまねくという問題があった。

#### [0011]

本発明は上記の問題点を解決すべくなされたもので、CMOS FETのサイズが大きい場合でも 貫通電流を抑制でき、消費電流の増大を抑制し得るCMOS構成の出力バッファ回路を備えた 半導体集積回路を提供することを目的とする。

### [0012]

## 【課題を解決するための手段】

本発明の半導体集積回路は、内部回路から供給される信号が入力する第1制御回路と、前記第1制御回路の出力信号が入力し、互いの立ち上がりのタイミングおよび立ち下がりのタイミングが異なるとともに同一論理レベルの期間が異なる2つの出力信号を生成する第2制御回路と、前記第2制御回路の2つの出力信号が対応してゲートに供給される電流吐き出し用のPMOS FETおよび電流吸い込み用のNMOS FETの各ドレインが出力端子に接続された出力バッファ回路とを具備し、前記第2制御回路は前記電流吐き出し用のPMOS FETおよび電流吸い込み用のNMOS FETのうちの一方のオン状態のFET がオフ状態に反転した後に他方のオフ状態のFET がオン状態になるように制御することを特徴とする。

## [0013]

### 【発明の実施の形態】

以下、図面を参照して本発明の実施の形態を詳細に説明する。

20

30

40

10

20

40

50

#### [0014]

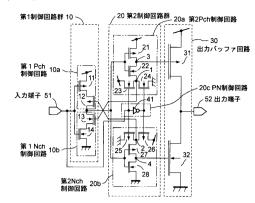

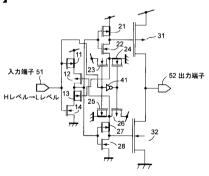

図1は、本発明の第1の実施の形態に係る半導体集積回路のCMOS構成の出力回路の一例を示している。

### [0015]

LSI 内部回路から入力端子51に供給される入力信号は、第 1 制御回路10に入力し、この第 1 制御回路10の出力信号および前記内部回路から供給される信号が第 2 制御回路20に入力する。この第 2 制御回路20は、 2 つの制御出力ノード1,2 の電位を前記第 1 制御回路10に帰還させ、互いの立ち上がりのタイミングおよび立ち下がりのタイミングが異なるとともに同一論理レベルの期間が異なる 2 つの出力信号を 2 つの出力ノード3.4 から出力する。

#### [0016]

出力バッファ回路30は、前記第2制御回路20の2つの出力信号が対応してゲートに供給される電流吐き出し用のPMOS FET31および電流吸い込み用のNMOS FET32の各ドレインが共通に出力端子52に接続されている。

## [0017]

即ち、この出力バッファ回路30は、ソース・ドレイン間がVCC (電源電位)ノードと出力端子52との間に接続された電流吐き出し用のPMOS FET31と、ドレイン・ソース間が出力端子52とGND (接地電位)ノードとの間に接続された電流吸い込み用のNMOS FET32とからなる。

## [0018]

前記第2制御回路20は、上記したCMOS FET31、32をプッシュプル駆動する際、CMOS FETのうちの一方のオン状態のFET がオフ状態に反転した後に他方のオフ状態のFET がオン状態になるように制御するように構成されている。

### [0019]

以下、前記第1制御回路10および第2制御回路20の構成を詳細に説明する。

#### [0020]

前記第1制御回路10は、内部回路から供給される信号の論理レベルと前記第2制御回路20の2つの制御出力ノード1,2から帰還する電位の論理レベルが所定の条件を満たした時に出力信号の論理レベルが確定するように構成されている。

## [0021]

具体例として、第 1 制御回路10は、第 1 のPMOS制御回路10a および第 1 のNMOS制御回路10b からなる。上記第 1 のPMOS制御回路10a は、ソースがVCC ノードに接続された第 1 のPMOS FET11と、この第 1 のPMOS FETのドレインにソースが接続された第 2 のPMOS FET12とからなる。また、前記第 1 のNMOS制御回路10b は、ソースがGND ノードに接続された第 1 のNMOS FET14と、この第 1 のNMOS FET14のドレインにソースが接続された第 2 のNMOS FET13とからなる。

## [0022]

上記第 1 の PMOS FET11と前記第 1 の NMOS FET14は、各ゲートが共通に接続されており、前記第 2 の PMOS FET12と第 2 の NMOS FET13は、各ドレインが共通に接続され、第 1 制御回路10の出力ノードになっている。

### [0023]

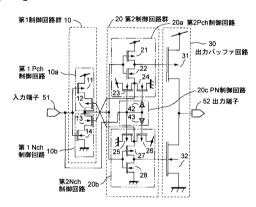

前記第2制御回路20は、第2のPMOS制御回路20a、第2のNMOS制御回路20b および接続ノード切換制御回路20c からなる。

### [0024]

上記第2のPMOS制御回路20a は、ソースがVCC ノードに接続された第3のPMOS FET21と、この第3のPMOS FETとゲート同士、ドレイン同士が接続され、ソースが第1の制御出力ノード1 となる第3のNMOS FET22と、ドレイン・ソース間がVCC ノードと上記第1の制御出力ノード1 との間に接続された第4のNMOS FET23と、ドレイン・ソース間が上記第1の制御出力ノード1 とGND ノードとの間に接続された第5のNMOS FET24とからなる。

### [0025]

そして、上記第3のPMOS FET21と第3のNMOS FET22の各ゲートに第1制御回路10の出力ノ

ードの信号が共通に入力し、上記第 1 の制御出力ノード1 に接続された第 4 のNMOS FET23 および第 5 のNMOS FET24の各ゲートには前記接続ノード切換制御回路20c から別々に供給される信号が別々に入力する。

### [0026]

前記第2のNMOS制御回路20b は、ソースがGND ノードに接続された第6のNMOS FET28と、この第6のNMOS FETとゲート同士、ドレイン同士が接続され、ソースが第2の制御出力ノード2 となる第6のPMOS FET27と、ソース・ドレイン間がVCC ノードと上記第2の制御出力ノード2 との間に接続された第4のPMOS FET26と、ソース・ドレイン間が上記第2の制御出力ノード2 とGND ノードとの間に接続された第5のPMOS FET25とからなる。

#### [0027]

そして、上記第6のPMOS FET27と第6のNMOS FET28の各ゲートに第1制御回路10の出力ノードの信号が共通に入力し、上記第2の制御出力ノード2に接続された第4のPMOS FET26および第5のPMOS FET25の各ゲートには前記接続ノード切換制御回路20cから別々に供給される信号が別々に入力する。

#### [0028]

前記接続ノード切換制御回路20c は、前記LSI 内部回路から供給される入力信号が入力し、この入力信号を前記第2のPMOS制御回路20a の第4のNMOS FET23のゲートおよび第2のNMOS制御回路20b の第5のPMOS FET25のゲートに直接に供給する。また、上記入力信号をインバータ回路41で反転させた後に前記第2のPMOS制御回路20a の第5のNMOS FET24のゲートおよび第2のNMOS制御回路20b の第4のPMOS FET26のゲートに供給する。

#### [0029]

そして、前記第2のPMOS制御回路20aの第1の制御出力ノード1の電位は前記第1のNMOS制御回路10bの第2のNMOS FET13のゲートの帰還入力となり、前記第2のNMOS制御回路20bの第2の制御出力ノード2の電位は前記第1のPMOS制御回路10aの第2のPMOS FET12のゲートの帰還入力となる。

### [0030]

そして、前記第2のPMOS制御回路20aの第3のPMOS FET21と第3のNMOS FET22の各ドレインが接続された出力ノード3の出力信号は、出力バッファ回路30の電流吐き出し用のPMOS FET31のゲートに入力し、前記第2のNMOS制御回路20bの第6のPMOS FET27と第6のNMOS FET28の各ドレインが接続された出力ノード4の出力信号は、出力バッファ回路30の電流吸い込み用のNMOS FET32のゲートに入力する。

## [0031]

図2万至図5は、図1の出力回路の入力信号の論理レベルが一定状態の時、あるいは遷移(変化)する時にオン状態になっているFETのソース・ドレイン間を太線で短絡して示した回路図である。

### [0032]

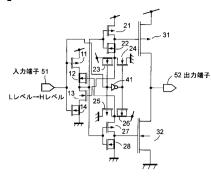

図 2 は、図 1 の出力回路の入力信号が"L" の時にオン状態になっているFET のソース・ドレイン間を太線で短絡して示した回路図である。

#### [0033]

図 3 は、図 1 の出力回路の入力信号が"L" から"H" に変化する時にオン状態になるFET の 40 ソース・ドレイン間を太線で短絡して示した回路図である。

#### [0034]

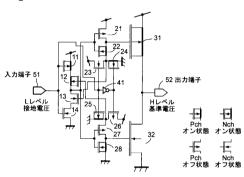

図4は、図1の出力回路の入力信号が"H"の時にオン状態になっているFETのソース・ドレイン間を太線で短絡して示した回路図である。

### [0035]

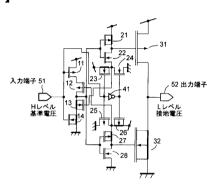

図 5 は、図 1 の出力回路の入力信号が "H" から "L" に変化する時にオン状態になる FET のソース・ドレイン間を太線で短絡して示した回路図である。

#### [0036]

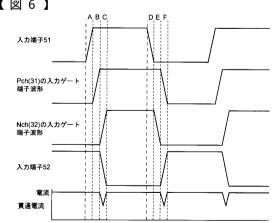

図6は、図1の出力回路の動作の一例を示す波形図である。

## [0037]

50

10

20

以下、図6を参照しながら、図1の出力回路の動作例を詳細に説明する。

### [0038]

まず、入力信号が"L" の時には、図 2 に示すように、第 1 のPMOS制御回路 10aの 2 個のPMO S FET11、12はそれぞれオン状態であり、第 1 制御回路 10の出力ノードの信号は"H" である。そして、第 2 のPMOS制御回路 20a のNMOS FET22とNMOS FET24がそれぞれオン状態であり、第 2 のPMOS制御回路 20a の出力信号が"L" であり、出力バッファ回路 30の電流吐き出し用のPMOS FET31がオン状態に駆動されている。

#### [0039]

この時、第2のNMOS制御回路20bのPMOS FET25とNMOS FET28がそれぞれオン状態であり、第2のNMOS制御回路20bの出力信号は"L"であり、出力バッファ回路30の電流吸い込み用のNMOS FET32はオフ状態である。したがって、出力端子52は"H"である。

## [0040]

次に、期間 A に示すように、入力信号が"L" から"H" に変化すると、図 3 に示すように、第 1 の PMOS制御回路 10a の PMOS FET11がオンからオフに変化し、第 1 の NMOS制御回路 10b の NMOS FET14がオフからオンに変化する。そして、第 2 の PMOS制御回路 20a の NMOS FET23がオフからオンに変化し、第 2 の PMOS制御回路 20aの NMOS FET24がオンからオフに変化し、第 2 の NMOS制御回路 20b の PMOS FET25がオンからオフに変化し、第 2 の NMOS制御回路 20 b の PMOS FET26がオフからオンに変化する。

#### [0041]

これにより、第2のPMOS制御回路20aの出力信号は"L"から"H"に変化するが、第2のNM OS制御回路20bの出力信号は"L"のままである。これにより、期間Bに示すように、出力バッファ回路30の電流吐き出し用のPMOS FET31がオン状態からオフ状態に変化するように駆動されるが、出力バッファ回路30の電流吸い込み用のNMOS FET32はオフ状態のままであり、したがって、出力端子52は"H"のままである。この時、貫通電流は流れない。

#### [0042]

次に、期間 C に示すように、入力信号が "H" の時には、図 4 に示すように、第 2 の PMOS制御回路 20a の NMOS FET 22のソースノードの電位 "H" が第 1 の NMOS制御回路 10b の PMOS FET 13のゲートに帰還し、この NMOS FET 13がオフからオンに変化する。また、第 2 の NMOS制御回路 20b の PMOS FET 27のソースノードの電位 "H" が第 1 の PMOS制御回路 10a の PMOS FET 1 2 のゲートに帰還し、この PMOS FET 12がオンからオフに変化する。

#### [0043]

これにより、第 1 制御回路 10の出力ノードの信号が "H" から "L" に変化し、第 2 の PMOS制御回路 20a の NMOS FET22がオンからオフに変化し、第 2 の PMOS制御回路 20a の PMOS FET21がオフからオンに変化するが、第 2 の PMOS制御回路 20a の出力信号は "H" のままであり、出力バッファ回路 30の電流吐き出し用の PMOS FET31はオフ状態のままである。

## [0044]

また、前記したように第 1 制御回路 10の出力ノードの信号が "H" から "L" に変化すると、第 2 の NMOS制御回路 20b の NMOS FET 28がオンからオフに変化し、第 2 の NMOS制御回路 20b の PMOS FET 27がオフからオンに変化し、第 2 の NMOS制御回路 20b の出力信号は "L" から "H" に変化する。

## [0045]

これにより、出力バッファ回路30の電流吸い込み用のNMOS FET32がオフ状態からオン状態に変化するように駆動され、出力端子52は"H" から"L" に変化する。この時、貫通電流は殆んど流れない。

#### [0046]

次に、期間 D に示すように、入力信号が "H" から "L" に変化すると、図 5 に示すように、第 1 の PMOS制御回路 10a の PMOS FET11がオフからオンに変化し、第 1 の NMOS制御回路 10b の NMOS FET14がオンからオフに変化する。そして、第 2 の PMOS制御回路 20a の NMOS FET23 がオンからオフに変化し、第 2 の PMOS制御回路 20b の PMOS FET26がオンからオフに変化し、第 2 の NMOS制御回路 20b の PMOS FET26がオンからオフに変化し、第 2 の NMOS制御回路 20

20

30

40

b のPMOS FET25がオフからオンに変化する。

### [0047]

これにより、第2のPMOS制御回路20aの出力信号は"H"のままであるが、第2のNMOS制御回路20bの出力信号は"H"から"L"に変化する。これにより、期間 Eに示すように、出力バッファ回路30の電流吐き出し用のPMOS FET31はオフ状態のままであるが、出力バッファ回路30の電流吸い込み用のNMOS FET32はオン状態からオフ状態に変化するように駆動され、したがって、出力端子52は"H"のままである。この時、貫通電流は流れない。

### [0048]

次に、期間 F に示すように、入力信号が"L" の時には、図 2 に示したように、第 2 の PMOS 制御回路 20a の NMOS FET 22のソースノードの電位 "L" が第 1 の NMOS制御回路 10b の PMOS FET 13のゲートに帰還し、この PMOS FET 13がオフからオンに変化する。また、第 2 の NMOS制御回路 20b の PMOS FET 27のソースノードの電位 "H"が第 1 の PMOS制御回路 10a の PMOS FET 1 2のゲートに帰還し、この PMOS FET 12がオンからオフに変化する。

## [0049]

これにより、第 1 制御回路 10の出力ノードの信号が "L" から "H" に変化し、第 2 の NMOS制御回路 20a の PMOS FET 21がオンからオフに変化し、第 2 の NMOS制御回路 20a の NMOS FET 22がオフからオンに変化するが、第 2 の NMOS制御回路 20a の出力信号は "L" のままであり、出力バッファ回路 30の電流吸い込み用の NMOS FET 32はオフ状態のままである。

#### [0050]

また、前記したように第 1 制御回路 10の出力ノードの信号が "L" から "H" に変化すると、第 2 の PMOS制御回路 20a の NMOS FET 22 がオンからオフに変化し、第 2 の PMOS制御回路 20a の PMOS FET 21 がオフからオンに変化し、第 2 の PMOS制御回路 20a の出力信号は "H" から "L" に変化する。

#### [0051]

これにより、出力バッファ回路30の電流吐き出し用のPMOS FET31がオフ状態からオン状態に変化するように駆動され、出力端子52は"L" から"H" に変化する。この時、貫通電流は 殆んど流れない。

#### [0052]

上記したように、第1の制御回路10および第2制御回路20は、出力バッファ回路30のCMOS FETをプッシュプル駆動する際、CMOS FETの一方のオン状態のFET がオフ状態に反転した後に他方のオフ状態のFET がオン状態になるように制御する。この際、入力信号の論理レベルが遷移した後に一定状態になった時に、第2制御回路20により第1の制御回路10を帰還制御する。これにより、出力バッファ回路30のCMOS FETが同時にオン状態の期間が存在しなくなり、VCC ノードとGND ノードとの間でCMOS FETを貫通する電流が流れなくなる。

## [0053]

### < 変形例 >

図 1 に示した出力回路において、接続ノード切換制御回路20c は、入力信号を 1 個のインバータ回路41で反転した後に第 2 のPMOS制御回路20a のNMOS FET24および第 2 のNMOS制御回路20b のPMOS FET26の各ゲートに共通に供給したが、図 7 に示すように変形実施することも可能である。

## [0054]

即ち、図 7 に示す接続ノード切換制御回路は、入力信号を第 1 のインバータ回路 42で反転した後に第 2 のPMOS制御回路 20a のNMOS FET24のゲートに供給し、入力信号を第 2 のインバータ回路 43で反転した後に第 2 のNMOS制御回路 20b のPMOS

FET26のゲートに供給している。

## [0055]

なお、図7において、図1中と同一部分には同一符号を付してその説明を省略する。

#### [0056]

### 【発明の効果】

上述したように本発明によれば、CMOS FETのサイズが大きい場合でも貫通電流を抑制でき

20

30

-

、消費電流の増大を抑制し得るCMOS構成の出力回路を備えた半導体集積回路を提供することができる。

【図面の簡単な説明】

- 【図1】本発明の第1の実施の形態に係る半導体集積回路のCMOS構成の出力回路の一例を示す回路図。

- 【図2】図1の出力回路の入力信号が"L"の時にオン状態になっているFETのソース・ドレイン間を太線で短絡して示した回路図。

- 【図3】図1の出力回路の入力信号が"L"から"H"に変化する時にオン状態になるFETのソース・ドレイン間を太線で短絡して示した回路図。

- 【図4】図1の出力回路の入力信号が"H"の時にオン状態になっているFETのソース・ド 10レイン間を太線で短絡して示した回路図。

- 【図 5 】図 1 の出力回路の入力信号が"H" から"L" に変化する時にオン状態になるFETのソース・ドレイン間を太線で短絡して示した回路図。

- 【図6】図1の出力回路の動作例を示す波形図。

- 【図7】図1中の接続ノード切換制御回路の変形例を示す回路図。

- 【図8】従来のLSIのCMOS構成の出力回路の一例を示す回路図。

- 【図9】図8の出力回路の動作例を示す波形図。

- 【図10】図9に示す動作例において出力バッファ回路の入力信号のレベルが遷移する過程において貫通電流が流れる様子を示す波形図。

### 【符号の説明】

- 1 ... 第 1 の制御出力ノード、

- 2 … 第 2 の制御出力ノード、

- 3,4 … 出力 ノード、

- 10...第1制御回路、

- 10a ... 第 1 の PMOS制御回路、

- 10b … 第 1 の NMOS制御回路、

- 11... 第 1 の PMOS FET、

- 12... 第 2 の PMOS FET、

- 14…第1のNMOS FET、

- 13... 第 2 の NMOS FET、

- 20...第2制御回路、

- 20a … 第 2 の PMOS制御回路、

- 20b ... 第 2 の NMOS制御回路、

- 20c …接続ノード切換制御回路、

- 21... 第 3 の PMOS FET、

- 22... 第 3 の NMOS FET、

- 23... 第 4 の NMOS FET、

- 24...第5のNMOS FET、

- 25…第5のPMOS FET、

- 26…第4のPMOS FET、

- 27... 第 6 の PMOS FET、

- 28... 第 6 の NMOS FET、

- 30... 出力バッファ回路、

- 31... 電流吐き出し用のPMOS FET、

- 32... 電流吸い込み用のNMOS FET、

- 41...インバータ回路、

- 51...入力端子、

- 52... 出力端子。

20

20

30

# 【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

## フロントページの続き

(74)代理人 100091351

弁理士 河野 哲

(74)代理人 100088683

弁理士 中村 誠

(74)代理人 100070437

弁理士 河井 将次

(72)発明者 横山 正成

神奈川県川崎市川崎区駅前本町25番地1 東芝マイクロエレクトロニクス株式会社内

## 審査官 石井 研一

(56)参考文献 特開2000-101415(JP,A)

特開平06-237158(JP,A)

特開平06-164346(JP,A)

特開平05-160706(JP,A)

特開平04-111529(JP,A)

## (58)調査した分野(Int.CI.<sup>7</sup>, DB名)

H03K 19/0175

H03K 17/16

H03K 17/687