### (19) **日本国特許庁(JP)**

# (12)特 許 公 報(B2)

(11)特許番号

特許第6688698号 (P6688698)

(45) 発行日 令和2年4月28日 (2020.4.28)

(24) 登録日 令和2年4月8日(2020.4.8)

| (51) Int.Cl. |          |           | F I  |          |     |

|--------------|----------|-----------|------|----------|-----|

| HO1L         | 21/336   | (2006.01) | HO1L | 29/78    | 371 |

| HO1L         | 29/788   | (2006.01) | HO1L | 27/11568 |     |

| HO1L         | 29/792   | (2006.01) | HO1L | 27/11573 |     |

| HO1L         | 27/11568 | (2017.01) | HO1L | 27/10    | 481 |

| HO1L         | 27/11573 | (2017.01) |      |          |     |

請求項の数 12 (全 38 頁) 最終頁に続く

(21) 出願番号 特願2016-135766 (P2016-135766) (22) 出願日 平成28年7月8日 (2016.7.8) (65) 公開番号 特開2018-6694 (P2018-6694A) (43) 公開日 平成30年1月11日 (2018.1.11) 審査請求日 平成31年1月16日 (2019.1.16) ||(73)特許権者 302062931

ルネサスエレクトロニクス株式会社 東京都江東区豊洲三丁目2番24号

||(74)代理人 110002066

特許業務法人筒井国際特許事務所

||(72)発明者 津田 是文

東京都江東区豊洲三丁目2番24号 ルネサスエレクトロニクス株式会社内

審査官 上田 智志

最終頁に続く

# (54) 【発明の名称】半導体装置およびその製造方法

#### (57)【特許請求の範囲】

# 【請求項1】

主面を有する半導体基板と、

前記半導体基板の第1領域において、前記半導体基板の一部分であって、前記半導体基板の前記主面に沿う第1方向に延在し、前記半導体基板の前記主面に沿って前記第1方向と直交する第2方向に互いに離間して設けられた複数の第1突出部と、

互いに隣り合う前記第1突出部の間に設けられた第1素子分離領域と、

前記第1素子分離領域の上面から露出する前記第1突出部の上部に、前記第1方向に互いに隣接して設けられた第1トランジスタおよび第2トランジスタと、を有し、

前記第1トランジスタおよび前記第2トランジスタは、不揮発性メモリセルを構成し、 前記第1トランジスタは、前記第1素子分離領域の上面から露出する前記第1突出部の 上部の上面および側壁に形成された第1絶縁膜と、前記第1絶縁膜を介して前記第2方向 に延在する第1ゲート電極と、を有し、

前記第2トランジスタは、前記第1素子分離領域の上面から露出する前記第1突出部の上部の上面および側壁に形成された第2絶縁膜と、前記第2絶縁膜を介して前記第2方向に延在する第2ゲート電極と、を有し、

前記第2絶縁膜はトラップ性絶縁膜を含み、前記第2絶縁膜を介して前記第1ゲート電極と前記第2ゲート電極とが配置されており、

前記第2方向に互いに隣り合う前記第1突出部の間において、前記第1素子分離領域の

上面の一部が、一方の前記第1突出部の側壁に接する前記第1素子分離領域の上面の位置と他方の前記第1突出部の側壁に接する前記第1素子分離領域の上面の位置とを結んだ第1面よりも高い位置にある、半導体装置。

### 【請求項2】

請求項1記載の半導体装置において、

前記第1領域とは異なる、前記半導体基板の第2領域において、前記半導体基板の一部分であって、前記半導体基板の前記主面に沿う第3方向に延在し、前記半導体基板の前記主面に沿って前記第3方向と直交する第4方向に互いに離間して設けられた複数の第2突出部と、

互いに隣り合う前記第2突出部の間に設けられた第2素子分離領域と、

前記第2素子分離領域の上面から露出する前記第2突出部の上部に設けられた第3トランジスタと、

#### をさらに有し、

前記第4方向に互いに隣り合う前記第2突出部の間において、前記第2素子分離領域の上面の平面度が、前記第1素子分離領域の上面の平面度よりも小さい、半導体装置。

#### 【請求項3】

請求項1記載の半導体装置において、

前記第1領域とは異なる、前記半導体基板の第2領域において、前記半導体基板の一部分であって、前記半導体基板の前記主面に沿う第5方向に延在し、前記半導体基板の前記主面に沿って前記第5方向と直交する第6方向に互いに離間して設けられた複数の第3突出部と、

互いに隣り合う前記第3突出部の間に設けられた第3素子分離領域と、

前記第3素子分離領域の上面から露出する前記第3突出部の上部に設けられた第4トランジスタと、

#### をさらに有し、

前記第6方向に互いに隣り合う前記第3突出部の間において、前記第3素子分離領域の上面の一部が、一方の前記第3突出部の側壁に接する前記第3素子分離領域の上面の位置と他方の前記第3突出部の側壁に接する前記第3素子分離領域の上面の位置とを結んだ第2面よりも高い位置にある、半導体装置。

# 【請求項4】

請求項1記載の半導体装置において、

前記第1突出部の側壁と前記第2絶縁膜を挟んだ位置にある、前記第2ゲート電極の下部の端部は、前記第1素子分離領域の上面よりも上に位置する、半導体装置。

### 【請求項5】

請求項1記載の半導体装置において、

前記第2方向に互いに隣り合う前記第1突出部の間において、前記第1素子分離領域の上面が、前記第2方向に沿った断面において凸形状となっている、半導体装置。

#### 【請求項6】

請求項1記載の半導体装置において、

前記第1面の前記第2方向の幅をWとし、前記第1面から前記第1素子分離領域の上面の最も高い位置までの距離をHとすると、H/Wは0.2~0.5である、半導体装置。

# 【請求項7】

請求項1記載の半導体装置において、

前記第1面から前記第1素子分離領域の上面の最も高い位置までの距離は、20nm~30nmである、半導体装置。

# 【請求項8】

(a)半導体基板の主面上に、第1厚さの第1絶縁膜を形成した後、前記第1絶縁膜上に、前記第1厚さよりも厚い第2厚さの第2絶縁膜を形成する工程、

(b)前記第2絶縁膜、前記第1絶縁膜および前記半導体基板を順次加工して、複数の 溝を形成することにより、前記半導体基板の前記主面に沿う第1方向に延在し、前記半導 10

20

30

50

40

体基板の前記主面に沿って前記第1方向と直交する第2方向に互いに離間する、前記半導体基板の一部分からなる複数の突出部を形成する工程、

- (c)前記半導体基板の主面上に第3絶縁膜を堆積して、前記複数の溝の内部を前記第3絶縁膜で埋め込む工程、

- (d)前記第3絶縁膜の上面および前記第2絶縁膜の上面を平坦化する工程、

- (e)前記第2絶縁膜を除去する工程、

- (f)等方性のドライエッチングを行い、前記第1絶縁膜を除去して複数の前記突出部の上面を露出させ、前記第3絶縁膜の上面および側面を後退させて複数の前記突出部の側壁を前記第3絶縁膜の上面から露出させる工程、

- (g)前記第3絶縁膜の上面から露出した前記突出部の上面および側壁と第4絶縁膜を介し、前記第2方向に延在する第1ゲート電極を形成する工程、

- (h)前記第3絶縁膜の上面から露出した前記突出部の上面および側壁並びに前記第1 ゲート電極の一方の側壁とトラップ性絶縁膜を含む第5絶縁膜を介し、前記第2方向に延 在する第2ゲート電極を形成する工程、

#### を有し、

前記第2方向に互いに隣り合う前記突出部の間において、前記第3絶縁膜の上面の一部が、一方の前記突出部の側壁に接する前記第3絶縁膜の上面の位置と他方の前記突出部の側壁に接する前記第3絶縁膜の上面の位置とを結んだ第1面よりも高い、半導体装置の製造方法。

# 【請求項9】

請求項8記載の半導体装置の製造方法において、

前記(a)工程において、第1室化シリコン膜、酸化シリコン膜および第2室化シリコン膜からなる積層構造の前記第2絶縁膜を形成し、

前記(e)工程において、

- (e1)前記第2室化シリコン膜を除去する工程、

- (e2)等方性のドライエッチングを行い、前記酸化シリコン膜を除去し、前記第3絶縁膜の上面および側面を後退させる工程、

- (e3)前記第1室化シリコン膜を除去する工程、

を有する、半導体装置の製造方法。

### 【請求項10】

請求項8記載の半導体装置の製造方法において、

前記(e)工程と前記(f)工程との間に、

(i) エッチングを行い、前記第3絶縁膜の上面を後退させる工程、

を有する、半導体装置の製造方法。

### 【請求項11】

請求項8記載の半導体装置の製造方法において、

前記第1面の前記第2方向の幅をWとし、前記第1面から前記第3絶縁膜の上面の最も高い位置までの距離をHとすると、H/Wは0.2~0.5である、半導体装置の製造方法。

#### 【請求項12】

請求項8記載の半導体装置の製造方法において、

前記第1面から前記第3絶縁膜の上面の最も高い位置までの距離は、20nm~30nmである、半導体装置の製造方法。

# 【発明の詳細な説明】

#### 【技術分野】

# [0001]

本発明は半導体装置およびその製造方法に関し、例えばフィン(Fin)状の半導体部により構成されるフィン型トランジスタ(FINFET: Fin Field Effect Transistor)を有する半導体装置およびその製造に好適に利用できるものである。

### 【背景技術】

50

40

10

20

#### [0002]

例えば米国特許出願公開第2015/0270401号明細書(特許文献1)には、少なくとも2種類の異なった半導体材料にチャネル領域が形成されたFINFETが記載されている。

# [0003]

また、米国特許出願公開第2014/0346612号明細書(特許文献2)には、複数のフィン同士を分離する素子分離領域が、熱酸化、プラズマ酸化または酸素のイオン注入により形成する技術が記載されており、素子分離領域の上面は凸形状となっている。

### 【先行技術文献】

【特許文献】

[0004]

【 特 許 文 献 1 】 米 国 特 許 出 願 公 開 第 2 0 1 5 / 0 2 7 0 4 0 1 号 明 細 書

【 特 許 文 献 2 】 米 国 特 許 出 願 公 開 第 2 0 1 4 / 0 3 4 6 6 1 2 号 明 細 書

【発明の概要】

【発明が解決しようとする課題】

[0005]

16nmノード以降のフィン型チャネルを有するスプリットゲート型メモリセルでは、 互いに隣り合うメモリセルの間の距離が近くなり、メモリセル間で繋がっているトラップ 性絶縁膜(電荷蓄積膜、電荷保持膜)を通じた電荷の拡散が、メモリセルの信頼性に影響 を及ぼすことが懸念された。

[0006]

その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

[0007]

一実施の形態による半導体装置は、半導体基板の一部分であって、半導体基板の主面に沿う第1方向に延在し、半導体基板の主面に沿って第1方向と直交する第2方向に互いに離間する複数のフィンが設けられている。そして、第2方向に互いに隣り合うフィンの間において、素子分離領域の上面の一部が、一方のフィンの側壁に接する素子分離領域の上面の位置と他方のフィンの側壁に接する素子分離領域の上面の位置とを結んだ面よりも高い位置にあり、第2方向に沿った断面において、素子分離領域の上面は凸形状となっている。

[00008]

一実施の形態による半導体装置の製造方法は、半導体基板の主面上に、窒化膜を形成する工程と、窒化膜および半導体基板を順次加工して、複数の溝を形成することにより、半導体基板の主面に沿う第1方向に延在し、半導体基板の主面に沿って第1方向と直交する第2方向に互いに離間する、半導体基板の一部分からなる複数の突出部を形成する工程と、を有する。さらに、半導体基板の主面上に酸化膜を堆積して、複数の溝の内部を酸化膜で埋め込む工程と、酸化膜の上面および窒化膜の上面を平坦化する工程と、窒化膜を除去する工程と、等方性のドライエッチングを行い、酸化膜の上面および側面をそれぞれ後退させて、複数の突出部の上面および側壁を酸化膜の上面から露出させる工程と、を有する。そして、第2方向に互いに隣り合う突出部の間において、酸化膜の上面の一部が、一方の突出部の側壁に接する酸化膜の上面の位置と他方の突出部の側壁に接する酸化膜の上面の位置とを結んだ面よりも高い位置にあり、第2方向に沿った断面において、酸化膜の上面を凸形状とする。

# 【発明の効果】

[0009]

一実施の形態によれば、半導体装置の信頼性を向上させることができる。

【図面の簡単な説明】

[0010]

10

20

30

10

20

30

40

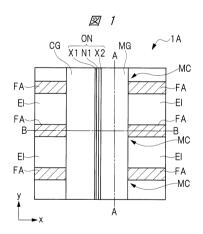

- 【図1】実施の形態1による半導体装置のメモリセル領域を示す平面図である。

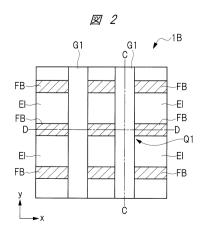

- 【図2】実施の形態1による半導体装置のロジック領域を示す平面図である。

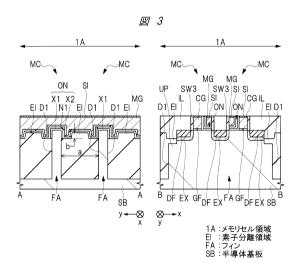

- 【図3】実施の形態1による半導体装置のメモリセル領域を示す、図1のA-A線およびB-B線に沿った断面図である。

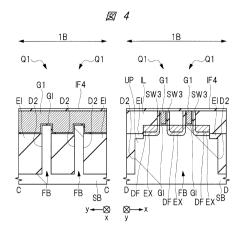

- 【図4】実施の形態1による半導体装置のロジック領域を示す、図2のC-C線およびD-D線に沿った断面図である。

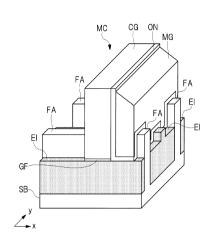

- 【図 5 】実施の形態 1 による半導体装置のメモリセル領域に形成されたメモリセルの鳥瞰図である。

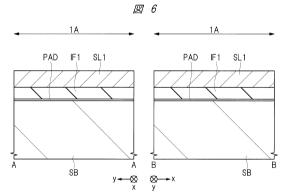

- 【図 6 】実施の形態 1 による半導体装置(メモリセル領域)の製造工程を説明する、図 1 の A A 線および B B 線に沿った断面図である。

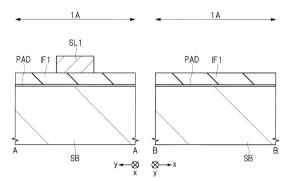

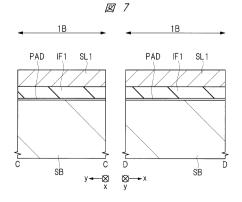

- 【図7】実施の形態1による半導体装置(ロジック領域)の製造工程を説明する、図2の C-C線およびD-D線に沿った断面図である。

- 【図8】図6に続く半導体装置の製造工程を説明する断面図である。

- 【図9】図7に続く半導体装置の製造工程を説明する断面図である。

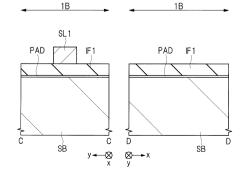

- 【図10】図8に続く半導体装置の製造工程を説明する断面図である。

- 【図11】図9に続く半導体装置の製造工程を説明する断面図である。

- 【図12】図10に続く半導体装置の製造工程を説明する断面図である。

- 【図13】図11に続く半導体装置の製造工程を説明する断面図である。

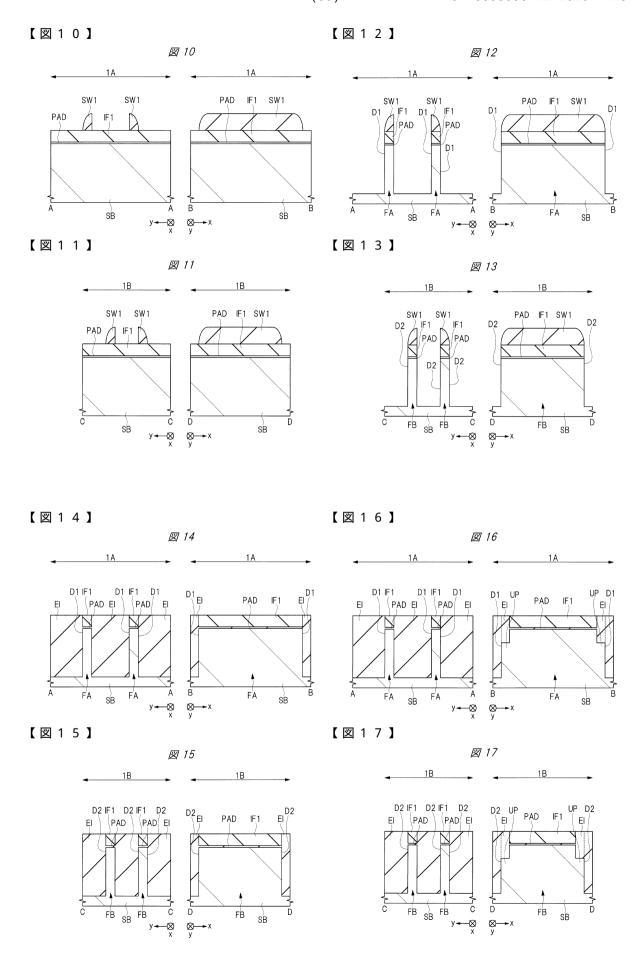

- 【図14】図12に続く半導体装置の製造工程を説明する断面図である。

- 【図15】図13に続く半導体装置の製造工程を説明する断面図である。

- 【図16】図14に続く半導体装置の製造工程を説明する断面図である。

- 【図17】図15に続く半導体装置の製造工程を説明する断面図である。

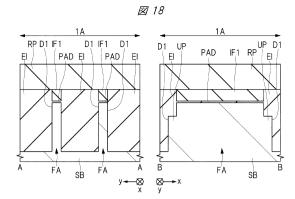

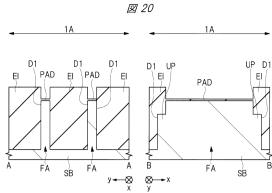

- 【図18】図16に続く半導体装置の製造工程を説明する断面図である。

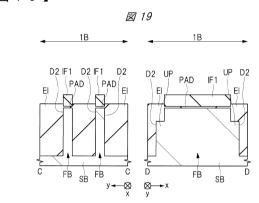

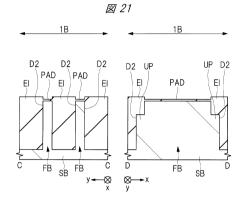

- 【図19】図17に続く半導体装置の製造工程を説明する断面図である。

- 【図20】図18に続く半導体装置の製造工程を説明する断面図である。

- 【図21】図19に続く半導体装置の製造工程を説明する断面図である。

- 【図22】図20に続く半導体装置の製造工程を説明する断面図である。

- 【図23】図21に続く半導体装置の製造工程を説明する断面図である。

- 【図24】実施の形態1による半導体装置のメモリセル領域を示す、図1のA-A線に沿った断面図である。

- 【図 2 5 】実施の形態 1 による半導体装置のメモリセル領域を示す、図 1 の A A 線に沿った断面図である。

- 【図 2 6 】実施の形態 1 による半導体装置のメモリセル領域を示す、図 1 の A A 線に沿った断面図である。

- 【図27】実施の形態1による半導体装置のメモリセル領域を示す、図1のA-A線に沿った断面図である。

- 【図28】図22に続く半導体装置の製造工程を説明する断面図である。

- 【図29】図23に続く半導体装置の製造工程を説明する断面図である。

- 【図30】図28に続く半導体装置の製造工程を説明する断面図である。

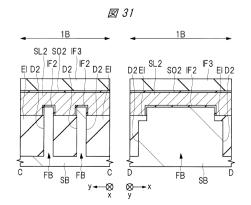

- 【図31】図29に続く半導体装置の製造工程を説明する断面図である。

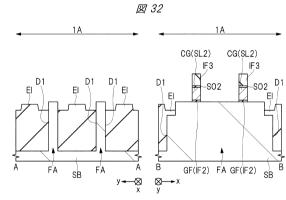

- 【図32】図30に続く半導体装置の製造工程を説明する断面図である。

- 【図33】図31に続く半導体装置の製造工程を説明する断面図である。

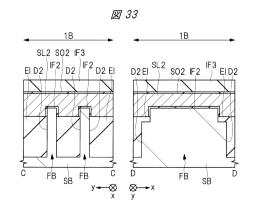

- 【図34】図32に続く半導体装置の製造工程を説明する断面図である。

- 【図35】図33に続く半導体装置の製造工程を説明する断面図である。

- 【図36】図34に続く半導体装置の製造工程を説明する断面図である。

- 【図37】図35に続く半導体装置の製造工程を説明する断面図である。

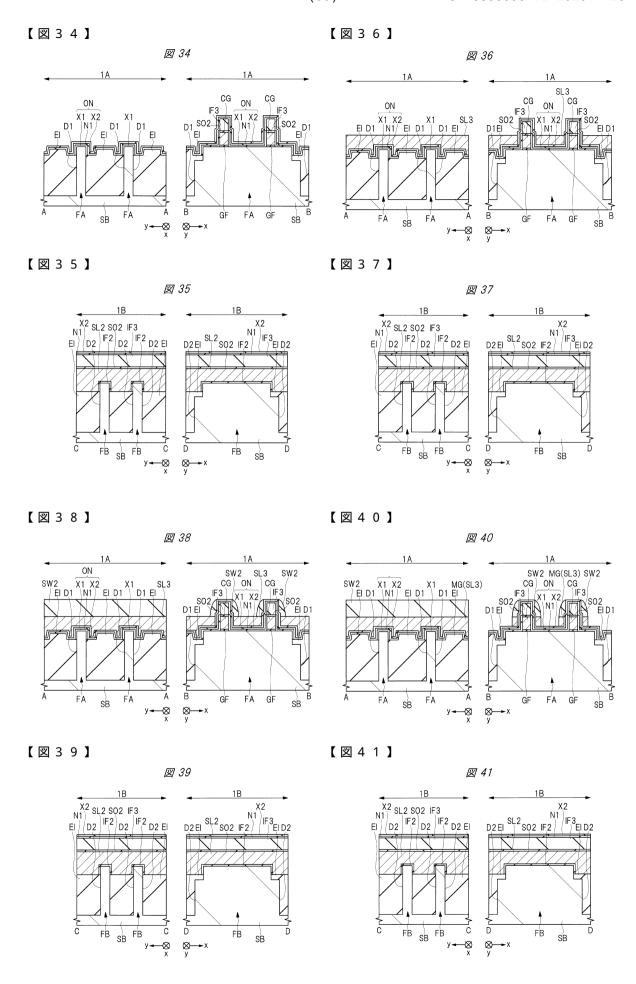

- 【図38】図36に続く半導体装置の製造工程を説明する断面図である。 【図39】図37に続く半導体装置の製造工程を説明する断面図である。

- 【図40】図38に続く半導体装置の製造工程を説明する断面図である。

- 【図41】図39に続く半導体装置の製造工程を説明する断面図である。

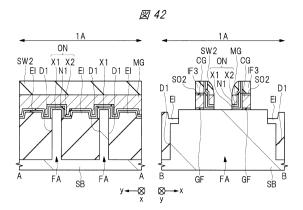

- 【図42】図40に続く半導体装置の製造工程を説明する断面図である。

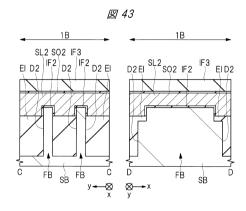

- 【図43】図41に続く半導体装置の製造工程を説明する断面図である。

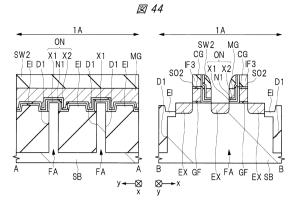

- 【図44】図42に続く半導体装置の製造工程を説明する断面図である。

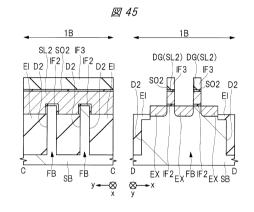

- 【図45】図43に続く半導体装置の製造工程を説明する断面図である。

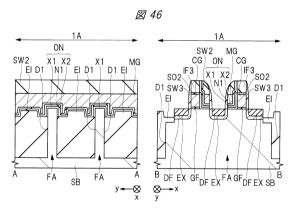

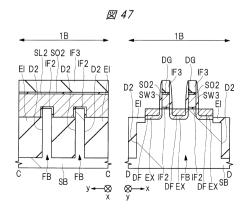

- 【図46】図44に続く半導体装置の製造工程を説明する断面図である。

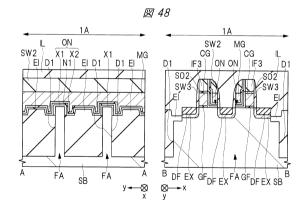

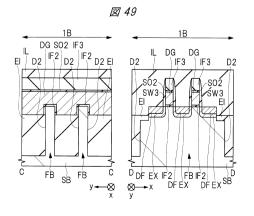

- 【図47】図45に続く半導体装置の製造工程を説明する断面図である。

- 【図48】図46に続く半導体装置の製造工程を説明する断面図である。

- 【図49】図47に続く半導体装置の製造工程を説明する断面図である。

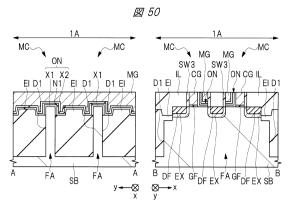

- 【図50】図48に続く半導体装置の製造工程を説明する断面図である。

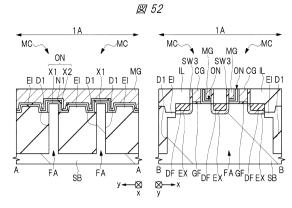

- 【図51】図49に続く半導体装置の製造工程を説明する断面図である。

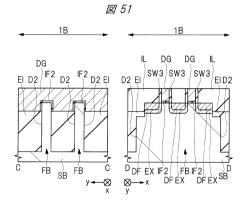

- 【図52】図50に続く半導体装置の製造工程を説明する断面図である。

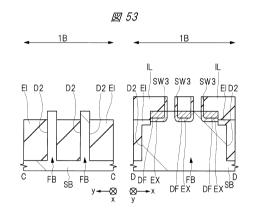

- 【図53】図51に続く半導体装置の製造工程を説明する断面図である。

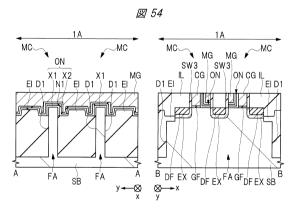

- 【図54】図52に続く半導体装置の製造工程を説明する断面図である。

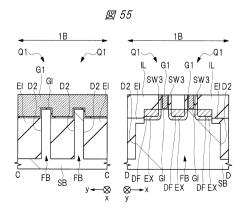

- 【図55】図53に続く半導体装置の製造工程を説明する断面図である。

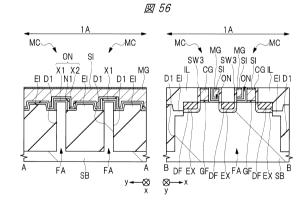

- 【図56】図54に続く半導体装置の製造工程を説明する断面図である。

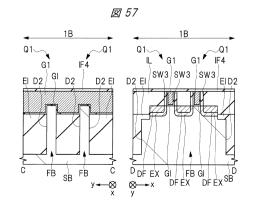

- 【図57】図55に続く半導体装置の製造工程を説明する断面図である。

- 【図 5 8 】実施の形態 1 による半導体装置のメモリセル領域を示す、図 1 の A A 線に沿った拡大断面図である。

- 【図59】実施の形態1の変形例による半導体装置のメモリセル領域を示す、図1のA-A線に沿った拡大断面図である。

- 【図60】実施の形態2による半導体装置のメモリセル領域を示す平面図である。

- 【図 6 1 】実施の形態 2 による半導体装置のメモリセル領域を示す、図 6 0 の E E 線および F F 線に沿った断面図である。

- 【図62】実施の形態2による半導体装置(メモリセル領域)の製造工程を説明する、図60のE-E線に沿った断面図である。

- 【図63】図62に続く半導体装置の製造工程を説明する断面図である。

- 【図64】図63に続く半導体装置の製造工程を説明する断面図である。

- 【図65】図64に続く半導体装置の製造工程を説明する断面図である。

- 【図66】図65に続く半導体装置の製造工程を説明する断面図である。

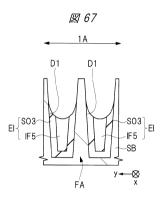

- 【図67】図66に続く半導体装置の製造工程を説明する断面図である。

- 【発明を実施するための形態】

# [0011]

以下の実施の形態において、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

# [0012]

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。

#### [0013]

また、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。

# [0014]

また、「Aからなる」、「Aよりなる」、「Aを有する」、「Aを含む」と言うときは、特にその要素のみである旨明示した場合等を除き、それ以外の要素を排除するものでないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

10

20

30

40

#### [0015]

また、以下の実施の形態を説明するための全図において、同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。また、断面図および平面図において、各部位の大きさは実デバイスと対応するものではなく、図面を分かりやすくするため、特定の部位を相対的に大きく表示する場合がある。また、断面図と平面図とが対応する場合においても、図面を分かりやすくするため、特定の部位を相対的に大きく表示する場合がある。また、断面図であっても図面を見易くするためにハッチングを省略する場合もあり、平面図であっても図面を見易くするためにハッチングを付す場合もある。

### [0016]

以下、本実施の形態を図面に基づいて詳細に説明する。

10

#### [0017]

# (実施の形態1)

#### 《半導体装置の構造》

本実施の形態1による半導体装置の構造について図1~図5を用いて説明する。図1は、本実施の形態1による半導体装置のメモリセル領域を示す平面図である。図2は、本実施の形態1による半導体装置のロジック領域を示す平面図である。図3は、本実施の形態1による半導体装置のメモリセル領域を示す、図1のA・A線およびB・B線に沿った断面図である。図4は、本実施の形態1による半導体装置のロジック領域を示す、図2のC・C線およびD・D線に沿った断面図である。図5は、本実施の形態1による半導体装置のメモリセル領域に形成されたメモリセルの鳥瞰図である。

20

### [0018]

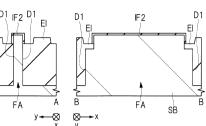

図3に示すA・A線に沿った断面は、メモリセル領域のフィン上のゲート電極の延在方向に沿う断面であり、B・B線に沿った断面は、メモリセル領域のフィンの延在方向に沿う断面である。図4に示すC・C線に沿った断面は、ロジック領域のフィン上のゲート電極の延在方向に沿う断面であり、D・D線に沿った断面は、ロジック領域のフィンの延在方向に沿う断面である。なお、図1および図2では、ソース・ドレイン領域、層間絶縁膜、各ゲート電極上のシリサイド層などの図示を省略している。さらに、図5では、サイドウォールの図示を省略している。

# [0019]

本実施の形態1による半導体装置は、同一半導体チップ上に、2つのFINFETからなるスプリットゲート型メモリセルと、例えば低耐圧のn型のFINFETとを搭載したものである。メモリセルはメモリセル領域に配置され、低耐圧のFINFETはロジック領域に配置されている。メモリセル領域およびロジック領域は、半導体基板の主面に沿う方向に並ぶ領域である。

30

# [0020]

図1、図3および図5のメモリセル領域1Aに示すように、メモリセル(不揮発性記憶素子)MCは、半導体基板SBの一部であって、半導体基板SBの上部に形成された板状のフィンFAの上部に形成されている。また、図2および図4のロジック領域1Bに示すように、低耐圧のFINFETであるトランジスタQ1は、半導体基板SBの一部であって、半導体基板SBの上部に形成された板状のフィンFBの上部に形成されている。

40

# [0021]

フィンFA,FBのそれぞれは、半導体基板SBの主面に沿う×方向(第1方向)に沿って延在する半導体層のパターンであって、×方向に対して直交し、半導体基板SBの主面に沿うy方向(第2方向)におけるフィンFA,FBのそれぞれの幅は、×方向のFA,FBのそれぞれの幅に比べて著しく小さい。半導体基板SBは、例えば単結晶シリコンからなる。

#### [0022]

フィンFA,FBのそれぞれは、y方向に互いに離間して複数並んで配置されている。 図1および図2では、y方向に並ぶフィンFA,FBのそれぞれを3つのみ示しているが、フィンFA,FBのそれぞれは、y方向においてさらに多く並んで配置されていてもよ

11.

### [0023]

また、メモリセル領域1Aでは、×方向においても複数のフィンFAが並んで配置されていてもよいし、長さ、幅および高さを有する突出部であれば、その形状は問わない。例えば平面視において蛇行するパターンも含まれる。また、フィンFAの並び方も問わない。同様に、ロジック領域1Bでは、×方向においても複数のフィンFBが並んで配置されていてもよいし、長さ、幅および高さを有する突出部であれば、その形状は問わない。例えば平面視において蛇行するパターンも含まれる。また、フィンFBの並び方も問わない

#### [0024]

複数のフィンFA同士の間には、半導体基板SBの上面に形成された溝D1が形成されている。複数のフィンFB同士の間には、半導体基板SBの上面に形成された溝D2が形成されている。

# [0025]

図3に示すように、 y 方向に互いに隣り合う 2 つのフィンFAの互いの端部は、半導体基板SBの一部であって、素子分離領域EIに覆われた下部パターンUPにより接続されている。なお、下部パターンUPは、当該 2 つのフィンFAの互いの端部から y 方向に延在しており、フィンFAを接続していれば、その形状は問わない。同様に、図4に示すように、 y 方向に互いに隣り合う 2 つのフィンFBの互いの端部は、半導体基板SBの一部であって、素子分離領域EIに覆われた下部パターンUPにより接続されている。なお、下部パターンUPは、当該 2 つのフィンFBの互いの端部から y 方向に延在しており、フィンFBを接続していれば、その形状は問わない。

#### [0026]

フィンFA、およびフィンFAに接続された下部パターンUPのそれぞれの側壁は、溝D1の側壁を構成している。また、フィンFB、およびフィンFBに接続された下部パターンUPのそれぞれの側壁は、溝D2の側壁を構成している。フィンFA,FBのそれぞれに接続された下部パターンUPは、形成されていなくてもよい。つまり、下部パターンUPが形成された領域は、溝D1,D2のそれぞれに埋め込まれた素子分離領域EIの一部となっていてもよい。

### [0027]

図3および図4に示すように、素子分離領域EIは、溝D1,D2のそれぞれを埋め込む絶縁膜である。但し、素子分離領域EIは溝D1,D2のそれぞれを完全に埋め込んではおらず、素子分離領域EIの上面上には、フィンFA,FBのそれぞれの一部が突出している。素子分離領域EIの上面から露出するフィンFA,FBのそれぞれの高さは、例えば40nm~60nm程度である。素子分離領域EIは、下部パターンUPの全体を覆っている。素子分離領域EIは、例えば酸化シリコンからなる。

# [0028]

本実施の形態1では、メモリセル領域1Aの半導体基板SBの一部を構成するパターンであって、素子分離領域EIから露出し、×方向に延在する上層パターンと、当該上層パターンの直下において、当該上層パターン側から溝D1の底部まで達する下層パターンとを含む板状の半導体層をフィンFAと呼ぶ。同様に、ロジック領域1Bの半導体基板SBの一部を構成するパターンであって、素子分離領域EIから露出し、×方向に延在する上層パターンと、当該上層パターンの直下において、当該上層パターン側から溝D2の底部まで達する下層パターンとを含む板状の半導体層をフィンFBと呼ぶ。

#### [0029]

すなわち、フィンとは、半導体基板SBの上面において半導体基板SBの上方へ突出する半導体パターンであり、例えば図1および図2の×方向に延在する突出部である。ここでは、下部パターンUPはフィンFA,FBのそれぞれの一部ではないものとして説明を行う。図示はしていないが、フィンFA,FBのそれぞれの上面には、p型不純物(例えばホウ素(B))を含むp型ウェルが、後述するソース・ドレイン領域に比べて深く形成

10

20

30

40

されている。

### [0030]

図3および図5に示すように、メモリセル領域1Aにおいて、素子分離領域EIの上面はy方向に沿った断面において凸形状となっている。言い換えると、y方向に互いに隣り合うフィンFAの間において、素子分離領域EIの上面の一部が、一方のフィンFAの側壁に接する素子分離領域EIの上面の位置と他方のフィンFAの側壁に接する素子分離領域EIの上面の位置とを結んだ面よりも高い位置にある。

### [0031]

但し、素子分離領域EIの上面の凸部の高さが大きくなり過ぎると、素子分離領域EIの上面の段差が大きくなり、素子分離領域EIを形成した後の加工プロセスが難しくなる。このため、素子分離領域EIの上面の凸部の高さは、例えば20nm~30nm程度が望ましく、例えばy方向に互いに隣り合うフィンFAの間隔をa、凸部の高さをbとすると、b/aは0.2~0.5程度が望ましい。ここで、凸部の高さとは、y方向に互いに隣り合うフィンFAの間において、一方のフィンFAの側壁に接する素子分離領域EIの上面の位置と他方のフィンFAの側壁に接する素子分離領域EIの上面の位置とを結んだ面から、素子分離領域EIの上面の最も高い位置までの距離である。

#### [0032]

このように、メモリセル領域1Aの素子分離領域EIの上面を凸形状とすることにより、素子分離領域EIの上面が平坦形状の場合と比べて、y方向に互いに隣り合うメモリセルMCの間において、後述するONO膜(Oxide-Nitride-Oxide)膜ONを構成するトラップ性絶縁膜の経路が長くなるので、電荷拡散の影響を抑えることができる。

#### [0033]

一方、図4に示すように、ロジック領域1Bにおいて、y方向に互いに隣り合うフィンFBの間隔が、例えば50nm以下の小さい場合は、素子分離領域EIの上面はy方向に沿った断面において凸形状とならず、ほぼ平坦となる。すなわち、ロジック領域1Bの素子分離領域EIの上面の平面度は、メモリセル領域1Aの素子分離領域EIの上面の平面度よりも小さくなる。

#### [0034]

これに対して、 y 方向に互いに隣り合うフィン F B の間隔が、例えば 6 0 n m以上の大きい場合は、素子分離領域 E I の上面は y 方向に沿った断面において凸形状となる。但し、ロジック領域 1 B では、メモリセル領域 1 A において生じるような電荷拡散の問題は無く、また、素子分離領域 E I の上面に凸部があると、ロジック領域 1 B における素子分離領域 E I を形成した後の加工プロセスが難しくなることから、素子分離領域 E I の上面は平坦であることが望ましい。

# [0035]

図 1 、図 3 および図 5 に示すように、メモリセル領域 1 A において、 y 方向に並ぶ複数のフィン F A の直上には、それらのフィン F A を跨ぐように、 y 方向に延在する制御ゲート電極 C G および y 方向に延在するメモリゲート電極 M G が形成されている。

# [0036]

制御ゲート電極CGは、素子分離領域EIの上面から露出するフィンFAの上面および側壁にゲート絶縁膜GFを介して形成されている。ゲート絶縁膜GFは、例えば酸化シリコンからなり、制御ゲート電極CGは、例えばポリシリコンからなる。

### [0037]

×方向における制御ゲート電極CGの一方の側壁はサイドウォールSW3により覆われ、他方の側壁には、ONO膜ONを介してメモリゲート電極MGが形成されている。サイドウォールSW3は、例えば窒化シリコン、酸化シリコンまたはそれらの積層膜からなる。ONO膜ONは、半導体基板SB側および制御ゲート電極CG側から順に酸化シリコン膜X1、窒化シリコン膜N1および酸化シリコン膜X2を積層した積層膜であり、メモリゲート電極MGは、例えばポリシリコンからなる。窒化シリコン膜N1はトラップ性絶縁膜(電荷蓄積膜、電荷保持膜)であり、メモリセルMCの動作により窒化シリコン膜N1

10

20

30

40

10

20

30

40

50

の電荷蓄積状態を変化させることで、メモリセルMCのしきい値電圧を変化させることができる。

# [0038]

メモリゲート電極MGは、素子分離領域EIの上面から露出するフィンFAの上面および側壁にONO膜ONを介して形成されている。すなわち、ONO膜ONは、フィンFAの上面と、制御ゲート電極CGの側壁とに沿って連続的に形成されたL字型の断面を有する。メモリゲート電極MGは、ONO膜ONにより制御ゲート電極CGおよびフィンFAから絶縁されている。

# [0039]

×方向におけるメモリゲート電極MGの側壁であって、ONO膜ONと接していない方の側壁は、サイドウォールSW3により覆われている。制御ゲート電極CGおよびメモリゲート電極MGのそれぞれの上面には、シリサイド層SIが形成されている。シリサイド層SIは、例えばニッケルシリサイド(NiSi)またはコバルトシリサイド(CoSi)からなる。シリサイド層SIは、制御ゲート電極CGの上面およびメモリゲート電極MGの上面のそれぞれに対し接続されるコンタクトプラグ(図示しない)と、制御ゲート電極CGまたはメモリゲート電極MGとの接続抵抗を低減するために設けられている。

#### [0040]

メモリセル領域1AのフィンFAの直上には、ONO膜ONを介して互いに隣接する制御ゲート電極CGおよびメモリゲート電極MGを含むパターンが×方向に並んで一対形成されている。当該一対のパターンは互いに離間しており、当該一対のパターンを構成する2つの制御ゲート電極CG同士の対向する面には、メモリゲート電極MGが隣接している

#### [0041]

×方向における当該パターンの横の両側のフィンFAの上面には、一対のソース・ドレイン領域が形成されている。ソース・ドレイン領域のそれぞれは、n型不純物(例えばリン(P)またはヒ素(As))が導入された2つのn型半導体領域、つまりエクステンション領域EXおよび拡散層DFにより構成されている。エクステンション領域EXは、拡散層DFよりもn型不純物の濃度が低い領域である。ここでは、エクステンション領域EXは拡散層DFよりも深く形成されている。また、エクステンション領域EXは、隣接する拡散層DFよりも、制御ゲート電極CGおよびメモリゲート電極MGのそれぞれの直下に近い位置に配置されている。このように、当該ソース・ドレイン領域は、不純物濃度が低いエクステンション領域EXと、不純物濃度が高い拡散層DFとを含むLDD(Lightly Doped Drain)構造を有している。

### [0042]

制御ゲート電極 C G と、当該制御ゲート電極 C G の両側のフィンF A の上面に形成された一対のソース・ドレイン領域とは、M I S F E T (Metal Insulator Semiconductor Field Effect Transistor)構造の第 1 トランジスタ (制御用トランジスタ)を構成している。また、メモリゲート電極 M G と、当該メモリゲート電極 M G の両側のフィンF A の上面に形成された一対のソース・ドレイン領域とは、M I S F E T 構造の第 2 トランジスタ (メモリ用トランジスタ)を構成している。本実施の形態 1 による 1 つのメモリセル M C は、互いにソース・ドレイン領域を共有する第 1 トランジスタと第 2 トランジスタとにより構成されている。すなわち、メモリセル M C は、制御ゲート電極 C G、メモリゲート電極 M G の N O 膜 O N 、制御ゲート電極 C G の近傍のドレイン領域、およびメモリゲート電極 M G の近傍のソース領域を有している。

#### [0043]

1つのフィンFA上には、2つのメモリセルMCが形成されている。当該2つのメモリセルMCは、互いのソース領域を共有している。制御ゲート電極CGおよびメモリゲート電極MGのそれぞれの直下のフィンFAの上面は、メモリセルMCの動作時にチャネルが形成されるチャネル領域を含んでいる。当該チャネルは、フィン型チャネルである。メモリセルMCは、書き込み動作および消去動作とも電気的に書き換え可能な不揮発性メモリ

である。

### [0044]

また、図2および図4に示すように、ロジック領域1Bにおいて、y方向に並ぶ複数のフィンFBの直上には、それらのフィンFBを跨ぐように、y方向に延在するゲート電極G1が形成されている。

#### [0045]

ゲート電極G1は、素子分離領域EIの上面から露出するフィンFBの上面および側壁にゲート絶縁膜GIを介して形成されている。

#### [0046]

また、ゲート絶縁膜GIは、ゲート電極G1の底面および両側の側壁を連続的に覆っている。つまり、ゲート電極G1は、その上面以外の面をゲート絶縁膜GIにより囲まれている。なお、図示はしていないが、ゲート絶縁膜GIとフィンFBとの間に、ゲート絶縁膜GIの一部として、例えば酸化シリコン膜が形成されていてもよい。ゲート絶縁膜GIには、例えば酸化ハフニウム(HfO₂)膜、酸化ジルコニウム(ZrO₂)膜、酸化アルミニウム(A1₂О₃)膜、酸化タンタル(Ta₂О₅)膜または酸化ランタン(La₂О₃)膜などの金属酸化物膜を用いることができる。ゲート絶縁膜GIは、酸化シリコン膜よりも誘電率が高い、いわゆるhigh-k膜である。

#### [0047]

ゲート電極 G 1 は、例えばアルミニウム(A 1)からなる。また、ゲート電極 G 1 は、例えば半導体基板 S B 上に順に積層されたチタンアルミニウム(T i A 1)およびアルミニウム(A 1)からなる積層構造を有していてもよい。

#### [0048]

×方向におけるゲート電極 G 1 の両側の側壁はサイドウォール S W 3 により覆われている。ゲート電極 G 1 の上面には、シリサイド層 S I は形成されていない。ゲート電極 G 1 と、その上のコンタクトプラグ(図示しない)とを接続する場合、金属膜からなるゲート電極 G 1 はシリコン膜に比べて低抵抗であるため、シリサイド層 S I を介さずともゲート電極 G 1 とコンタクトプラグとをオーミックに接続することができる。

#### [0049]

ロジック領域1BのフィンFBの直上には、ゲート電極G1が×方向に並んで一対形成されている。当該一対のゲート電極G1は互いに離間している。

#### [0050]

×方向におけるゲート電極 G 1 の横の両側のフィン F B の上面には、一対のソース・ドレイン領域が形成されている。ソース・ドレイン領域のそれぞれは、メモリセル領域 1 A のソース・ドレイン領域と同様に、 n 型不純物 ( 例えばリン ( P ) またはヒ素 ( A s ) )が導入された 2 つの n 型半導体領域、つまりエクステンション領域 E X および拡散層 D F により構成されている。なお、ロジック領域 1 B のソース・ドレイン領域の不純物濃度は、メモリセル領域 1 A のソース・ドレイン領域の不純物濃度よりも小さい。

#### [0051]

ゲート電極G1と、当該ゲート電極G1の両側のフィンFBの上面に形成された一対の ソース・ドレイン領域とは、MISFET構造を有する低耐圧なトランジスタQ1を構成 している。

#### [0052]

1 つのフィンFB上には、2 つのトランジスタQ 1 が形成されている。ゲート電極 G 1 の直下のフィンFBの上面は、トランジスタQ 1 の動作時にチャネルが形成されるチャネル領域を含んでいる。当該チャネルは、フィン型チャネルである。また、2 つのトランジスタQ 1 は、互いが有する一対のソース・ドレイン領域のうちの一方を共有している。

#### [0053]

本実施の形態1では、フィンFAの一部をチャネル領域として有し、フィンFAの上部に形成された上記の第1トランジスタ、第2トランジスタおよびトランジスタQ1を、FINFETと呼ぶ。メモリセルMCを構成する第1トランジスタおよび第2トランジスタ

10

20

30

40

は、ロジック回路を構成する低耐圧のトランジスタQ1に比べ、高い電圧で駆動するトランジスタであるため、トランジスタQ1に比べて高い耐圧性能が求められる。

#### [0054]

また、図3および図4に示すように、メモリセル領域1Aおよびロジック領域1Bにおいて、素子分離領域EIの上面、フィンFA,FBのそれぞれの上面および側壁、並びにサイドウォールSW3の側壁などは、層間絶縁膜ILにより覆われている。層間絶縁膜ILは、例えば酸化シリコンからなる。なお、図示はしていないが、層間絶縁膜ILと、素子分離領域EIの上面、フィンFA,FBのそれぞれの上面および側壁、並びにサイドウォールSW3の側壁との間には、薄い絶縁膜が形成されており、当該絶縁膜は、例えば窒化シリコンからなる。層間絶縁膜IL、サイドウォールSW3、ゲート電極G1、ONO膜ON、制御ゲート電極CGおよびメモリゲート電極MGのそれぞれの上面は、略同一の平面において平坦化されている。

#### [0055]

図示はしていないが、層間絶縁膜IL、メモリセルMCおよびトランジスタQ1のそれぞれの上部は、層間絶縁膜により覆われている。また、図示はしていないが、層間絶縁膜ILと、層間絶縁膜IL上の当該層間絶縁膜とを貫通する複数のコンタクトプラグが形成されており、コンタクトプラグは、ゲート電極G1、制御ゲート電極CG、メモリゲート電極MGおよび各ソース・ドレイン領域に電気的に接続されている。また、図示はしていないが、コンタクトプラグ上には配線が形成されている。

### [0056]

《半導体装置の特徴および効果》

本実施の形態 1 による半導体装置の主な特徴は、メモリセル領域 1 A の素子分離領域 E I の上面を凸形状としている点にある。

#### [0057]

16nmノード以降のスプリットゲート型メモリセルMCでは、y方向に互いに隣り合うメモリセルMCの間の距離が小さくなり、y方向に互いに隣り合うメモリセルMCがそれぞれ有するONO膜ONの距離が近くなる。このため、ONO膜ONを構成する、トラップ性絶縁膜である窒化シリコン膜N1を通じて電荷が拡散して、メモリセルMCの信頼性に影響を及ぼすことが考えられる。

# [0058]

しかし、本実施の形態 1 による半導体装置では、メモリセル領域 1 A の素子分離領域 E I の上面を凸形状とすることにより、 y 方向に互いに隣り合うメモリセルMCの間の窒化シリコン膜 N 1 (トラップ性絶縁膜)の経路を長くしている。すなわち、凸部を形成した場合、凸部を形成しない場合と比べて、窒化シリコン膜 N 1 の経路が長くなり、電荷の拡散距離が長くなるので、 y 方向に互いに隣り合うメモリセルMCの間の窒化シリコン膜 N 1 の経路を介したデータ変動を抑制することができる。これにより、半導体装置の信頼性を向上することができる。

#### [0059]

《半導体装置の動作》

本実施の形態 1 による半導体装置のうち、主に不揮発性メモリの動作について説明する

#### [0060]

本実施の形態1によるメモリセルは、MISFET構造を有し、MISFETのゲート電極内のトラップ性絶縁膜での電荷蓄積状態を記憶情報とし、それをMISFETのしきい値として読み出すものである。トラップ性絶縁膜とは、電荷の蓄積可能な絶縁膜をいい、一例として、窒化シリコン膜などが挙げられる。このような電荷蓄積領域への電荷の注入・放出によってMISFETのしきい値をシフトさせ、記憶素子として動作させる。トラップ性絶縁膜を用いた不揮発性半導体記憶装置としては、本実施の形態1によるメモリセルのように、スプリットゲート型のMONOS(Metal-Oxide-Nitride-Oxide-Semiconductor)メモリがある。

10

20

30

50

#### [0061]

メモリセルの「書込み」および「消去」を行う動作法として、例えばSSI(Source Side Injection)方式、BTBT(Band To Band Tunneling)方式およびFN(Fowler Nordheim)方式などがある。

#### [0062]

SSI方式は、トラップ性絶縁膜にホットエレクトロンを注入することによってメモリセルの書込みを行う動作法とみなすことができ、BTBT方式は、トラップ性絶縁膜にホットホールを注入することによってメモリセルの消去を行う動作法とみなすことができ、FN方式は、エレクトロンまたはホールのトンネリングによって書込みまたは消去を行う動作法とみなすことができる。FN方式について、別の表現でいうと、FN方式の書込みは、トラップ性絶縁膜にFNトンネル効果によりエレクトロンを注入することによってメモリセルの書込みを行う動作方式とみなすことができ、FN方式の消去は、トラップ性絶縁膜にFNトンネル効果によりホールを注入することによってメモリセルの消去を行う動作方式とみなすことができる。

#### [0063]

以下、SSI方式による書込みを行い、FN方式による消去を行う場合について説明する。すなわち、トラップ性絶縁膜(例えば図3に示す絶縁膜ONO膜ON中の電荷蓄積部である窒化シリコン膜N1)へのエレクトロンの注入を「書込み」、ホールの注入を「消去」と定義する。

### [0064]

SSI方式の書込みでは、書込みを行う選択メモリセルの各部位にそれぞれ書込み動作電圧を印加し、選択メモリセルのトラップ性絶縁膜中にホットエレクトロンを注入することで書込みを行う。

#### [0065]

この際、ホットエレクトロンは、2つのゲート電極(メモリゲート電極MGおよび制御ゲート電極CG)間の下のチャネル領域(ソース、ドレイン間)で発生し、メモリゲート電極MGの下のトラップ性絶縁膜にホットエレクトロンが注入される。注入されたホットエレクトロンは、トラップ性絶縁膜中のトラップ準位に捕獲され、その結果、選択トランジスタのしきい値電圧が上昇する。すなわち、選択トランジスタは書込み状態となる。

# [0066]

FN方式の消去では、消去を行う選択メモリセルの各部位にそれぞれ消去動作電圧を印加し、選択メモリセルにおいて、メモリゲート電極MGからホールをトンネリングさせ、トラップ性絶縁膜にホールを注入することで消去を行う。この際、ホールはメモリゲート電極MGからFNトンネリング(FNトンネル効果)によりトラップ性絶縁膜中に注入され、トラップ性絶縁膜中のトラップ準位に捕獲され、その結果、選択トランジスタのしきい値電圧が低下する。すなわち、選択トランジスタは消去状態となる。

# [0067]

読出し時には、読出しを行う選択メモリセルの各部位にそれぞれ読出し動作電圧を印加する。読出し時のメモリゲート電極MGに印加する電圧を、書込み状態におけるしきい値電圧と消去状態におけるしきい値電圧との間の値にすることで、書込み状態と消去状態とを判別することができる。

#### [0068]

《半導体装置の製造方法》

本実施の形態1による半導体装置の製造方法について図6~図57を用いて説明する。図6~図57は、本実施の形態1による半導体装置の製造工程を説明する断面図である。

# [0069]

図6~図22および図28~図56のうち偶数図番は、図1に示すメモリセル領域のA-A線に沿った断面図およびB-B線に沿った断面図である。また、図7~図23および図29~図57のうち奇数図番は、図2に示すロジック領域のC-C線に沿った断面図およびD-D線に沿った断面図である。図24~図27は、図1に示すメモリセル領域のA

10

20

30

40

- A線に沿った断面図である。

### [0070]

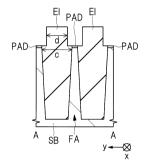

まず、図 6 および図 7 に示すように、半導体基板 S B を用意し、半導体基板 S B 上に、例えば熱酸化法を用いて酸化膜 P A D を形成する。酸化膜 P A D は、例えば酸化シリコンからなり、その厚さは、例えば 1 0 n m程度である。続いて、酸化膜 P A D 上に、例えば C V D (Chemical Vapor Deposition) 法を用いて絶縁膜 I F 1 を形成する。絶縁膜 I F 1 は、例えば窒化シリコンからなり、その厚さは、例えば 9 0 n m ~ 1 2 0 n m程度である。続いて、絶縁膜 I F 1 上に、例えば C V D 法を用いてアモルファスシリコン膜 S L 1 を形成する。アモルファスシリコン膜 S L 1 の厚さは、例えば 1 6 0 n m 程度である。

### [0071]

次に、図8および図9に示すように、レジストパターンをマスクとしたドライエッチングにより、アモルファスシリコン膜SL1を加工する。これにより、アモルファスシリコン膜SL1は、平面視において×方向に延在する長方形の形状を有する。図8および図9では、メモリセル領域1Aおよびロジック領域1Bのそれぞれに1つずつアモルファスシリコン膜SL1のパターンを示しているが、図示していない領域を含め、メモリセル領域1Aおよびロジック領域1Bのそれぞれには複数のアモルファスシリコン膜SL1が平面視において行列状に配置されている。メモリセル領域1Aのアモルファスシリコン膜SL1のy方向における幅は、ロジック領域1Bのアモルファスシリコン膜SL1のy方向における幅より大きい。

# [0072]

次に、図10および図11に示すように、アモルファスシリコン膜SL1および絶縁膜IF1の上に、例えばCVD法を用いて酸化シリコン膜を堆積した後、当該酸化シリコン膜をエッチバックすることで、酸化シリコンからなるサイドウォールSW1を形成する。サイドウォールSW1のy方向の幅は、例えば20nm~50nm程度である。すなわち、当該エッチバックでは、アモルファスシリコン膜SL1の上面および絶縁膜IF1の上面を露出させる。

### [0073]

続いて、例えばウェットエッチングにより、アモルファスシリコン膜SL1を除去する。これにより、メモリセル領域1Aおよびロジック領域1Bのそれぞれの絶縁膜IF1上には、アモルファスシリコン膜SL1の側壁を覆う、平面視において矩形の枠状のサイドウォールSW1が残る。

# [0074]

次に、図12および図13に示すように、サイドウォールSW1をマスクとしたドライエッチングにより、絶縁膜IF1と、酸化膜PADと、半導体基板SBの上面の一部とを加工する。これにより、メモリセル領域1Aにおいて半導体基板SBの上面を含む一部からなるフィンFAと、フィンFAの周囲の溝D1とを形成し、ロジック領域1Bにおいて半導体基板SBの上面を含む一部からなるフィンFBと、フィンFBの周囲の溝D2とを形成する。溝D1,D2のそれぞれの深さは、例えば120nm~250nm程度である

# [0075]

すなわち、メモリセル領域1AのサイドウォールSW1から露出する絶縁膜IF1および半導体基板SBの上面の一部を加工することで、半導体基板SBの上面において上方に突出する板状のフィンFAを形成する。半導体基板SBの上面の一部である板状パターンは、×方向に延在する2つのフィンFAを含み、平面視において矩形の環状構造を有している。

# [0076]

また、ロジック領域1BのサイドウォールSW1から露出する絶縁膜IF1および半導体基板SBの上面の一部を加工することで、半導体基板SBの上面において上方に突出する板状のフィンFBを形成する。半導体基板SBの上面の一部である板状パターンは、×方向に延在する2つのフィンFBを含み、平面視において矩形の環状構造を有している。

10

20

30

40

#### [0077]

次に、図14および図15に示すように、例えばCVD法を用いて溝D1,D2のそれぞれの内側を絶縁膜により埋め込む。当該絶縁膜は、例えば酸化シリコンからなる。その後、例えばCMP(Chemical Mechanical Polishing)法を用いて当該絶縁膜およびサイドウォールSW1を研磨する。これにより、メモリセル領域1Aおよびロジック領域1Bの絶縁膜IF1の上面を露出させ、絶縁膜IF1の上面と、溝D1,D2のそれぞれに埋め込まれた上記絶縁膜との上面を平坦化する。当該研磨により、サイドウォールSW1は除去される。溝D1,D2のそれぞれに埋め込まれた上記絶縁膜は、素子分離領域EIを構成する。

### [0078]

次に、図16および図17に示すように、レジストパターンをマスクとしたドライエッチングにより、素子分離領域EIの上面から露出する絶縁膜IF1の一部と、半導体基板SBの上面を含む板状パターンの一部を除去する。

# [0079]

すなわち、メモリセル領域1Aにおいて、矩形の環状構造を有する板状パターンのうち、例えばy方向に延在する部分、つまり、y方向に並ぶ2つのフィンFA同士の端部を接続する部分を加工する。これにより、板状パターンを構成し、y方向に延在するパターンのうち、上部の一部分が除去される。この工程では同様に、ロジック領域1Bにおいて、矩形の環状構造を有する板状パターンのうち、例えばy方向に延在する部分、つまり、y方向に並ぶ2つのフィンFB同士の端部を接続する部分を加工する。これにより、板状パターンを構成し、y方向に延在するパターンのうち、上部の一部分が除去される。

#### [0800]

これにより、 y 方向に互いに隣り合うフィン F A の互いの端部を接続する下部パターン U P を形成する。同様に、 y 方向に互いに隣り合うフィン F B の互いの端部を接続する下 部パターン U P を形成する。除去されるパターンは任意であり、この除去工程により、最 終的に回路を構成するための任意のフィン F A , F B がそれぞれ形成される。

#### [0081]

続いて、上記工程において絶縁膜IF1の一部および板状パターンの一部を除去した領域に、CVD法などを用いて、例えば酸化シリコンからなる絶縁膜を埋め込む。その後、例えばCMP法を用いて研磨を行い、これにより、当該絶縁膜の上面を平坦化させて、絶縁膜IF1の上面を露出させる。

# [0082]

なお、図16および図17では、当該絶縁膜と、図14および図15を用いて説明した 工程において溝D1、D2のそれぞれの内側に埋め込んだ絶縁膜との境界を点線で示して いる。それらの絶縁膜は、素子分離領域EIを構成している。

### [0083]

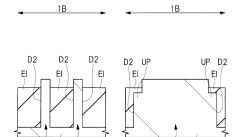

次に、図18および図19に示すように、ロジック領域1Bを露出し、メモリセル領域1Aを覆うレジストパターンRPを形成した後、ロジック領域1Bの素子分離領域EIの上面をエッチバックにより後退させることで、絶縁膜IF1の側壁を素子分離領域EIから露出させる。当該エッチバックは、ウェットエッチングまたはドライエッチングのいずれを用いてもよい。

#### [0084]

次に、図20および図21に示すように、ウェットエッチングにより、絶縁膜IF1を除去してフィンFA,FBのそれぞれの上面上の酸化膜PADを露出させる。ここで、メモリセル領域1AにおけるフィンFAのy方向の幅は、例えば20nm~50nm程度であり、素子分離領域EIのよ面から突出する素子分離領域EIの高さは、例えば50nm~70nm程度である。一方、ロジック領域1BにおけるフィンFBの上面から突出する素子分離領域EIの高さは、例えば10nm~20nm程度である。

# [0085]

20

10

30

次に、図22および図23に示すように、等方性のドライエッチングを用いて素子分離領域EIの上面を後退させることで、酸化膜PADを除去し、フィンFA,FBのそれぞれの側壁を素子分離領域EIから露出させる。このとき、板状パターンの一部であって、 y 方向に延在する下部パターンUPは、素子分離領域EIから露出させない。つまり、素子分離領域EIの上面から露出する半導体基板SBは、×方向に延在するフィンFAおよびフィンFBのみである。

#### [0086]

また、メモリセル領域1Aでは、等方性のドライエッチングを用いて素子分離領域EIの上面を後退させたことで、素子分離領域EIの上面はy方向に沿った断面において凸形状となっている。これは、メモリセル領域1Aでは、露出している素子分離領域EIの上面方向および側面方向からエッチングが進むからである。但し、素子分離領域EIの上面の凸部の高さが大きくなり過ぎると、素子分離領域EIの上面の段差が大きくなり、素子分離領域EIを形成した後の加工プロセスが難しくなるため、素子分離領域EIの上面の凸部の高さは、例えば20nm~30nm程度が好ましい。また、素子分離領域EIの上面から露出するフィンFAの高さは、例えば40nm~60nm程度である。

#### [0087]

一方、ロジック領域1Bでは、素子分離領域EIの上面は凸形状となっておらず、ほぼ平坦である。すなわち、ロジック領域1Bの素子分離領域EIの上面の平面度は、メモリセル領域1Aの素子分離領域EIの上面の平面度よりも小さくなる。

# [0088]

これは、等方性のドライエッチングを行う前では、フィンFBの上面から突出する素子分離領域EIの高さがフィンFAの上面から突出する素子分離領域EIの高さよりも低く、かつ、y方向に互いに隣り合うフィンFAの間隔よりも小さいことから、ロジック領域1Bでは、主に素子分離領域EIの上面方向からエッチングが進むからである。

#### [0089]

但し、y方向に互いに隣り合うフィンFBの間隔が大きくなると、ロジック領域1Bにおいても、素子分離領域EIの上面はy方向に沿った断面において凸形状となる。

### [0090]

なお、素子分離領域 E I の上面に対する等方性のドライエッチングは、メモリセル領域 1 A およびロジック領域 1 B のそれぞれに対して別々に行ってもよい。この場合は、エッチングを行わない方の領域をレジストパターンで覆った状態でエッチングを行う。このようにして、メモリセル領域 1 A では素子分離領域 E I の上面を凸形状とし、ロジック領域 1 B では素子分離領域 E I の上面を平坦形状にしてもよい。

# [0091]

本実施の形態1の主な特徴の1つは、メモリセル領域1Aの素子分離領域EIの上面を 凸形状とすることで、メモリセル領域1Aにおいてy方向に互いに隣り合うメモリセルの 間のトラップ性絶縁膜の経路が長くなり、電荷拡散の影響が抑えられることである。

### [0092]

凸部の高さおよび幅を調節する方法としては、例えば以下の方法がある。

# [0093]

(1)絶縁膜IF1の厚さを変えることにより、凸部の高さを変えることができる。

# [0094]

(2)等方性のドライエッチングを用いて素子分離領域 E I の上面を後退させる前に、メモリセル領域 1 A の素子分離領域 E I の上面を均一に後退させることにより、凸部の高さを変えることができる。例えば図 1 4 を用いて説明した工程の後に、ウェットエッチングを用いて素子分離領域 E I の上面を後退させる。

#### [0095]

(3)酸化膜 P A D の厚さを変えることにより、凸部の幅を変えることができる。例えば酸化膜 P A D が厚い場合は、等方性のドライエッチングの起点が、半導体基板 S B の上

10

20

30

40

10

20

30

40

50

面から遠くなり、所望のフィンFAの高さが得られるまでのエッチング時間が長くなる。 その結果、凸部の幅が狭くなる。

#### [0096]

(4)絶縁膜IFの構成を変えることにより、凸部の幅を変えることができる。

#### [0097]

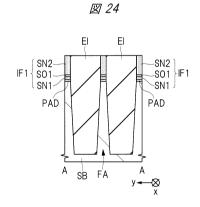

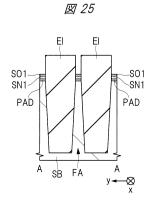

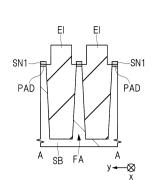

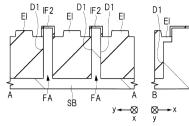

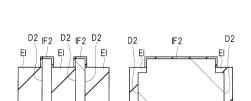

一例として、絶縁膜IF1を、下層の窒化シリコン膜SN1、酸化シリコン膜SO1および上層の窒化シリコン膜SN2からなる積層構造とした場合について、図24~図27を用いて以下に説明する。

# [0098]

素子分離領域EIの上面を平坦に加工した後(図24)、上層の窒化シリコン膜SN2を除去し(図25)、さらに、等方性のドライエッチングを用いて素子分離領域EIの上面および側面を後退させる(図26)。この際、酸化シリコン膜SO1は除去される。続いて、下層の窒化シリコン膜SN1を除去する(図27)。これにより、フィンFAの上面よりも上に、y方向に互いに隣り合うフィンFAの間の距離cよりも小さい幅dを有する素子分離領域EIを形成することができる。ここから、等方性のドライエッチングを用いて素子分離領域EIの上面を後退させて、フィンFAを露出させることにより、凸部の幅を小さくすることができる。

#### [0099]

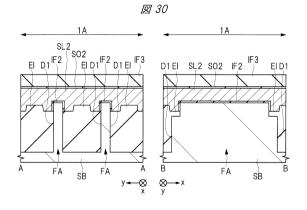

次に、図28および図29に示すように、素子分離領域EIの上面から露出するフィンFA,FBのそれぞれの表面を覆う絶縁膜IF2を形成する。絶縁膜IF2は、例えば熱酸化法を用いて形成することができ、例えば酸化シリコンからなる。絶縁膜IF2はフィンFA,FBのそれぞれの上面および側壁を覆っており、素子分離領域EIの上面は絶縁膜IF2から露出している。絶縁膜IF2の厚さは、例えば1nm~2nm程度である。

#### [0100]

次に、図30および図31に示すように、素子分離領域EIおよび絶縁膜IF2の上に、例えばCVD法を用いてポリシリコン膜SL2を形成した後、ポリシリコン膜SL2の上面をCMP法などにより研磨する。フィンFA,FBのそれぞれの上面からポリシリコン膜SL2の上面までのポリシリコン膜SL2の厚さは、例えば60nm~150nm程度である。

### [0101]

続いて、ポリシリコン膜SL2の上面を熱酸化することで、当該上面を覆う酸化シリコン膜SO2を形成する。酸化シリコン膜SO2の厚さは、例えば6nm~10nm程度である。続いて、酸化シリコン膜SO2上に、例えばCVD法を用いて絶縁膜IF3を形成する。絶縁膜IF3は、例えば窒化シリコンからなり、その厚さは、例えば90nm程度である。

### [0102]

次に、図32および図33に示すように、レジストパターンをマスクとしたドライエッチングにより、メモリセル領域1Aの絶縁膜IF3、酸化膜SO2、ポリシリコン膜SL2および絶縁膜IF2を加工する。すなわち、レジストパターン(図示しない)によりロジック領域1Bを覆った状態でパターニングを行う。レジストパターンは、当該パターニングの後に除去する。これにより、フィンFAの直上において、絶縁膜IF3、酸化膜SO2、ポリシリコン膜SL2および絶縁膜IF2からなる積層パターンを×方向に並べて形成する。このパターニングにより、ポリシリコン膜SL2からなる制御ゲート電極CGを形成し、絶縁膜IF2からなるゲート絶縁膜GFを形成する。

#### [0103]

絶縁膜IF3および制御ゲート電極CGからなる積層パターンはy方向に延在し、複数のフィンFA上およびゲート絶縁膜GF上を跨ぐように配置されている。メモリセル領域1Aにおいて、当該積層パターンが形成された箇所以外の領域では、上記エッチングによりメモリセル領域1Aの絶縁膜IF3、酸化膜SO2、ポリシリコン膜SL2および絶縁膜IF2が除去されたことにより、フィンFAの表面および素子分離領域EIの上面が露

出している。

### [0104]

次に、図34および図35に示すように、熱酸化法を用いてゲート絶縁膜GFから露出するフィンFAの上面および側壁並びに制御ゲート電極CGの側壁を酸化する。これにより、フィンFAの上面および側壁並びに制御ゲート電極CGの側壁を覆う酸化シリコン膜(ボトム酸化膜)X1を形成する。図34では、フィンFAの上面から制御ゲート電極CGの側壁に亘って連続的に形成された酸化シリコン膜X1を示しているが、ゲート絶縁膜GFの側壁に酸化シリコン膜X1が形成されていなくてもよい。

### [0105]

続いて、例えばCVD法を用いて酸化シリコン膜 X 1、絶縁膜 I F 3 および素子分離領域 E I の上に窒化シリコン膜 N 1 を形成する。当該窒化シリコン膜 N 1 は、後に形成するメモリセルにおいて電荷を蓄積するためのトラップ性絶縁膜として機能する。なお、ここでは、トラップ性絶縁膜として窒化シリコン膜 N 1 を形成することについて説明したが、トラップ性絶縁膜としては窒化シリコン膜 N 1 に限らず、例えば C V D 法を用いて窒化シリコン膜 N 1 上に酸化シリコン膜 (トップ酸化膜) X 2 を形成する。

#### [0106]

半導体基板SB側から順に積層された酸化シリコン膜X1、窒化シリコン膜N1および酸化シリコン膜X2からなる積層膜は、ONO膜ONを構成する。制御ゲート電極CGの側壁に接するONO膜ONは、制御ゲート電極CG側から順にx方向に形成された酸化シリコン膜X1、窒化シリコン膜N1および酸化シリコン膜X2からなる。ここでは、ONO膜ONの最上層のトップ酸化膜の材料は、酸化シリコンに限らず、例えばアルミナ(A1203)であってもよい。

#### [0107]

なお、ONO膜ONは、原則、酸化シリコン膜X1、室化シリコン膜N1および酸化シリコン膜X2からなる積層膜を言うが、説明の便宜上、窒化シリコン膜N1および酸化シリコン膜X2からなる積層膜をONO膜ONと言うこともある。

#### [0108]

次に、図36および図37に示すように、ONO膜ON上に、例えばCVD法を用いてポリシリコン膜SL3を形成する。ポリシリコン膜SL3の厚さは、少なくとも制御ゲート電極CGの厚さ以上の大きさを有する。ここでは、ポリシリコン膜SL3を、制御ゲート電極CG、酸化シリコン膜SO2および絶縁膜IF3からなる積層膜の膜厚よりも大きい膜厚で形成することで、制御ゲート電極CG、酸化シリコン膜SO2、絶縁膜IF3およびONO膜ONを含む積層膜を覆う。その後、CMP法などを用いてポリシリコン膜SL3の上面を平坦化する。

### [0109]

続いて、エッチバックを行うことで、ポリシリコン膜SL3の上面を後退させて、例えばポリシリコン膜SL3の上面の高さと、制御ゲート電極CGの上面の高さとを揃える。これにより、絶縁膜IF3および絶縁膜IF3を覆うONO膜ONは、ポリシリコン膜SL3の上面上に突出する。上記ポリシリコン膜SL3に対する平坦化工程およびエッチバック工程により、ロジック領域1Bのポリシリコン膜SL3は除去される。

#### [0110]

次に、図38および図39に示すように、ONO膜ONおよびポリシリコン膜SL3の上に、例えばCVD法を用いて絶縁膜を形成する。当該絶縁膜は、例えば窒化シリコンからなり、その厚さは、例えば10~50nmである。続いて、ドライエッチングにより、ポリシリコン膜SL3の上面と、絶縁膜IF3の直上のONO膜ONの上面とを当該絶縁膜から露出させる。これにより、絶縁膜IF3の側壁には、ONO膜ONを介して、当該絶縁膜からなるサイドウォールSW2が形成される。当該ドライエッチング工程により、ロジック領域1Bの当該絶縁膜は除去される。

# [0111]

50

20

10

30

10

20

30

40

50

次に、図40および図41に示すように、サイドウォールSW2をハードマスクとしたドライエッチングにより、ポリシリコン膜SL3を加工する。これにより、フィンFAの上面および側壁に接するONO膜ONの上面がポリシリコン膜SL3から露出する。制御ゲート電極CGの横の両側には、ONO膜ONを介してポリシリコン膜SL3のパターンからなるメモリゲート電極MGが形成される。但し、制御ゲート電極CGの一方の側壁に隣接するメモリゲート電極MGは、後の工程で除去されるパターンであり、完成後の半導体装置には残らない。

### [0112]

次に、図42および図43に示すように、レジストパターンをマスクとしたドライエッチングにより、制御ゲート電極CGおよび絶縁膜IF3からなる積層膜の一方の側壁に隣接するメモリゲート電極MGおよび当該メモリゲート電極MGの直上のサイドウォールSW2を除去する。これにより、制御ゲート電極CGの他方の側壁に隣接するメモリゲート電極MGが残る。続いて、制御ゲート電極CG、メモリゲート電極MGから露出するONO膜ONを除去する。

#### [0113]

すなわち、ONO膜ONは、メモリゲート電極MGとフィンFAとの間、メモリゲート電極MGと制御ゲート電極CGとの間、およびサイドウォールSW2と絶縁膜IF3との間にのみ残る。従って、メモリセル領域1Aでは、制御ゲート電極CGおよびメモリゲート電極MGから露出する領域において、フィンFAの上面および側壁並びに素子分離領域EIの上面が露出する。また、メモリセル領域1Aにおいて絶縁膜IF3の上面および一方の側壁が露出し、ロジック領域1Bにおいて絶縁膜IF3の上面が露出する。

#### [0114]

フィンFAの上面、つまり半導体基板SBに沿って延在するONO膜ONと、制御ゲート電極CGの側壁に沿って延在するONO膜ONとは連続的に形成されており、L字型の断面を有している。フィンFA上には、制御ゲート電極CGおよび当該制御ゲート電極CGにONO膜ONを介して隣接するメモリゲート電極MGを有するパターンが一対形成されており、一対の制御ゲート電極CG同士の間において、一対のメモリゲート電極MG同士が対向している。続いて、後にフィンFAに対して行う不純物注入工程において、フィンFAがダメージを受けることを防ぐことなどを目的として、フィンFAの上面および側壁に対して酸化処理を行ってもよい。

#### [0115]

次に、図44および図45に示すように、メモリセル領域1Aを覆い、ロジック領域1Bの一部を露出するレジストパターン(図示しない)を形成した後、当該レジストパターンをマスクとしたドライエッチングにより、ロジック領域1Bの絶縁膜IF3、酸化膜SO2、ポリシリコン膜SL2および絶縁膜IF2を加工する。これにより、フィンFBの直上に、絶縁膜IF2、ポリシリコン膜SL2からなるダミーゲート電極DG、酸化膜SO2および絶縁膜IF3からなる積層膜が、×方向に並んで一対形成される。それらの積層膜の横の領域では、フィンFBおよび素子分離領域EIの上面が露出する。すなわち、フィンFB上には、絶縁膜IF2を介してダミーゲート電極DG、酸化膜SO2および絶縁膜IF3が形成されている。ダミーゲート電極DGは、後の工程において除去される擬似的なゲート電極であり、完成した半導体装置には残らない。

#### [0116]

続いて、上記レジストパターンを除去した後、絶縁膜IF3およびサイドウォールSW2をマスクとしたイオン注入工程を行うことで、フィンFA,FBのそれぞれの上面にn型不純物(例えばリン(P)またはヒ素(As))を打ち込む。これにより、比較的不純物濃度が低いn型半導体領域であるエクステンション領域EXを複数形成する。メモリセル領域1Aのエクステンション領域EXは、制御ゲート電極CGと、当該制御ゲート電極CGにONO膜ONを介して隣接するメモリゲート電極MGとを有するパターンの横のフィンFAの上面に形成される。ロジック領域1Bのエクステンション領域EXは、ダミーゲート電極DGの横のフィンFBの上面に形成される。ここでは、必要に応じて、フィン

10

20

30

40

50

FA, FBのそれぞれに対してハロー注入としてp型不純物(例えばホウ素(B))の打ち込みを行ってもよい。

### [0117]

次に、図46および図47に示すように、半導体基板SB上に、例えばCVD法を用いて絶縁膜を形成する。当該絶縁膜は、例えば酸化シリコン、窒化シリコンまたはそれらの積層膜からなる。続いて、ドライエッチングにより、フィンFA,FBのそれぞれおよび絶縁膜IF3の上面を当該絶縁膜から露出させる。これにより、メモリセル領域1Aでは、制御ゲート電極CG、メモリゲート電極MG、ONO膜ON、酸化膜SO2、絶縁膜IF3およびサイドウォールSW2を含むパターンの両側の側壁に、上記絶縁膜からなるサイドウォールSW3が形成される。また、ロジック領域1Bでは、ダミーゲート電極DG、酸化シリコン膜SO2および絶縁膜IF3からなる積層膜の両側の側壁に、上記絶縁膜からなるサイドウォールSW3が形成される。

### [0118]

続いて、絶縁膜IF3およびサイドウォールSW2,SW3のそれぞれをマスクとしたイオン注入工程を行うことで、フィンFA,FBのそれぞれの上面にn型不純物(例えばリン(P)またはヒ素(As))を打ち込む。これにより、比較的不純物濃度が高いn型半導体領域である拡散層DFを複数形成する。メモリセル領域1Aの拡散層DFは、制御ゲート電極CGと、当該制御ゲート電極CGにONO膜ONを介して隣接するメモリゲート電極MGとを有するパターンの横のフィンFAの上面に形成される。ロジック領域1Bの拡散層DFは、ダミーゲート電極DGの横のフィンFBの上面に形成される。

#### [0119]

拡散層DFは、当該拡散層DFに接するエクステンション領域EXに比べ、×方向において制御ゲート電極CG、メモリゲート電極MGまたはダミーゲート電極DGよりも離れた位置に形成される。拡散層DFは、エクステンション領域EXよりも形成深さが浅く、n型不純物濃度が高い。互いに接するエクステンション領域EXおよび拡散層DFは、トランジスタのソース・ドレイン領域を構成する。この後、エクステンション領域EX内および拡散層DF内の不純物を活性化させるため、必要に応じて熱処理を行う。

#### [0120]

なお、ここでは、メモリセル領域1Aおよびロジック領域1Bのそれぞれのソース・ドレイン領域を同一工程で形成することについて説明したが、ロジック領域1Bに形成するトランジスタに比べて高耐圧なメモリセルを形成するメモリセル領域1Aでは、ソース・ドレイン領域の不純物濃度をロジック領域1Bのソース・ドレイン領域の不純物濃度よりも大きくすることが考えられる。よって、メモリセル領域1Aのエクステンション領域EXおよび拡散層DFの形成工程と、ロジック領域1Bのエクステンション領域EXおよび拡散層DFの形成工程と、ロジック領域1Bのエクステンション領域EXおよび拡散層DFの形成工程とを別々に行ってもよい。また、ここでは、イオン注入によりソース・ドレイン領域を形成することについて説明したが、イオン注入を行う代わりに、不純物が導入されたエピタキシャル層を、各ゲート電極の横のフィンFA,FBのそれぞれの上面および側壁にエピタキシャル成長法を用いて形成してもよい。

### [0121]

次に、図48および図49に示すように、半導体基板SB上に、例えばCVD法を用いて、例えば5nm~20nmの膜厚を有する窒化シリコンからなる絶縁膜(図示しない)と、例えば酸化シリコンからなる層間絶縁膜ILとを順に形成する。層間絶縁膜ILは、少なくとも制御ゲート電極CGよりも大きい膜厚を有しており、ここでは、ゲート絶縁膜GF、制御ゲート電極CG、酸化シリコン膜SO2および絶縁膜IF3からなる積層膜よりも大きい膜厚を有している。

# [0122]

次に、図50および図51に示すように、層間絶縁膜ILの上面を、例えばCMP法を用いて研磨することで平坦化する。当該研磨工程では、絶縁膜IF3およびサイドウォールSW2を全て除去し、サイドウォールSW3およびONO膜ONのそれぞれの上部の一部を除去し、制御ゲート電極CG、メモリゲート電極MGおよびダミーゲート電極DGの

それぞれの上面を露出させる。つまり、制御ゲート電極 C G、メモリゲート電極 M G およびダミーゲート電極 D G、並びに O N O 膜 O N、サイドウォール S W 3 および層間絶縁膜 I L のそれぞれの上面は、略同一平面において平坦化され、同じ高さに揃えられる。

#### [0123]

これにより、上面が露出した制御ゲート電極 C G およびメモリゲート電極 M G と、当該制御ゲート電極 C G およびメモリゲート電極 M G を含むパターンの両側に形成されたエクステンション領域 E X および拡散層 D F からなるソース・ドレイン領域とは、スプリットゲート型のメモリセル M C を構成する。すなわち、メモリセル M C は、制御ゲート電極 C G を含む第 1 トランジスタと、メモリゲート電極 M G を含む第 2 トランスタとを含む M O N O S 型の不揮発性メモリを構成する。

# [0124]

図50に示すように、メモリセル領域1Aの制御ゲート電極CGは、フィンFAおよび素子分離領域EIのそれぞれの直上において、複数のフィンFAの上部を跨ぐようにy方向に延在している。また、制御ゲート電極CGは、素子分離領域EIから突出する複数のフィンFA同士の間を埋め込むように形成されている。また、図51に示すように、ロジック領域1Bのダミーゲート電極DGは、フィンFBおよび素子分離領域EIのそれぞれの直上において、複数のフィンFBの上部を跨ぐようにy方向に延在している。また、ダミーゲート電極DGは、素子分離領域EIから突出する複数のフィンFB同士の間を埋め込むように形成されている。

# [0125]

次に、図52および図53に示すように、レジストパターン(図示しない)によりメモリセル領域1Aの制御ゲート電極CGおよびメモリゲート電極MGを保護した状態で、ウェットエッチングにより、ダミーゲート電極DGを除去する。続いて、絶縁膜IF2を除去する。なお、絶縁膜IF2は除去せず、後の工程でロジック領域1Bに形成するゲート絶縁膜GIの一部として用いてもよい。上記除去工程により、ロジック領域1Bでは、ダミーゲート電極DGおよび絶縁膜IF2を除去した領域に溝が形成される。その後、メモリセル領域1Aの上記レジストパターンを除去する。

#### [0126]

次に、図54および図55に示すように、半導体基板SB上に、例えばALD(Atomic layer Deposition:原子層堆積)法を用いて絶縁膜を形成した後、当該絶縁膜上に、例えばスパッタリング法を用いて金属膜を形成することで、当該絶縁膜および当該金属膜からなる積層膜により上記溝内を埋め込む。その後、例えばCMP法を用いて研磨を行うことで、層間絶縁膜IL上の余分な上記の絶縁膜および金属膜を除去し、層間絶縁膜IL、制御ゲート電極CGおよびメモリゲート電極MGのそれぞれの上面を露出させる。これにより、上記溝内に埋め込まれた絶縁膜からなるゲート絶縁膜GIと、上記溝内にゲート絶縁膜GIを介して埋め込まれた金属膜からなるゲート電極G1とを形成する。

# [0127]

# [0128]

ゲート電極 G 1 を構成する上記金属膜は、例えば 2 層の積層膜により構成される。当該積層膜は、半導体基板 S B 側から順に積層された第 1 金属膜および第 2 金属膜を有する。第 1 金属膜は、例えばチタンアルミニウム(TiAl)膜からなり、第 2 金属膜は、例えばアルミニウム(Al)からなる。また、第 1 金属膜および第 2 金属膜の間に、チタン(

10

20

30

40

10

20

40

50

Ti)膜、窒化チタン(TiN)膜またはそれらの積層膜を介在させて、トランジスタQ1のしきい値電圧を調整しても良い。なお、図55では上記の第1金属膜および第2金属膜を1つの金属膜として示している。

#### [0129]

ゲート絶縁膜GIは、上記溝内において、ゲート電極G1の底面および側壁、並びに当該溝の底面および側壁を覆っている。なお、図52および図53を用いて説明した工程において絶縁膜IF2を除去した場合、ゲート絶縁膜GIを形成する前に酸化処理を行うことで、当該溝の底面に新たな絶縁膜を形成し、当該絶縁膜をゲート絶縁膜GIの一部として用いてもよい。また、ここでは、ダミーゲート電極DGの除去後にhigh‐k膜を形成することについて説明したが、ダミーゲート電極DGを構成するポリシリコン膜SL2(図31参照)の形成前であって、図23を用いて説明した工程の後にhigh‐k膜を形成し、当該high‐k膜をロジック領域1Bのゲート絶縁膜GIとして残してもよい

# [0130]

次に、図56および図57に示すように、ロジック領域1Bのゲート電極G1の上面を 絶縁膜IF4により覆った後、制御ゲート電極CGおよびメモリゲート電極MGのそれぞ れの上面を覆うシリサイド層SIを形成する。

#### [0131]

絶縁膜IF4は、例えばCVD法により形成された酸化シリコンからなる。ここでは、メモリセル領域1Aおよびロジック領域1Bを覆うように絶縁膜IF4を形成した後、パターニングを行うことでメモリセル領域1Aの絶縁膜IF4を除去する。これにより、ロジック領域1Bの層間絶縁膜IL、サイドウォールSW3およびゲート電極G1のそれぞれの上面を覆う絶縁膜IF4が残る。

#### [ 0 1 3 2 ]

続いて、露出している制御ゲート電極 C G およびメモリゲート電極 M G の上に、例えばスパッタリング法を用いてニッケル ( N i ) またはコバルト ( C o ) からなる金属膜を形成した後、熱処理を行って当該金属膜と制御ゲート電極 C G およびメモリゲート電極 M G のそれぞれの上面とを反応させる。

### [0133]

これにより、制御ゲート電極 C G およびメモリゲート電極 M G のそれぞれの上面を覆う、ニッケルシリサイド ( N i S i ) またはコバルトシリサイド ( C o S i ) からなるシリサイド層 S I を形成する。

#### [0134]

続いて、未反応の金属膜をウェットエッチングなどにより除去する。これにより、層間絶縁膜ILおよび絶縁膜IF4が露出する。ここでは、ゲート電極G1を絶縁膜IF4により覆っているため、メタルゲート電極であるゲート電極G1が当該ウェットエッチングにより除去されることを防ぐことができる。また、ゲート電極G1上にはシリサイド層SIは形成されない。

### [0135]

この後、図示はしていないが、層間絶縁膜IL上にさらに層間絶縁膜を形成し、それらの層間絶縁膜を貫通し、制御ゲート電極CG、メモリゲート電極MG、ソース・ドレイン領域またはゲート電極G1に接続された複数のコンタクトプラグ(接続部)を形成することで、本実施の形態1による半導体装置が完成する。

# [0136]

具体的には、例えばCVD法を用いて酸化シリコンなどからなる層間絶縁膜を層間絶縁膜IL上に形成した後、レジストパターンをマスクとしたドライエッチングにより、層間絶縁膜ILおよびその上の当該層間絶縁膜からなる積層層間絶縁膜を貫通する複数のコンタクトホールを形成する。コンタクトホールは、メモリセルMCのソース・ドレイン領域を構成する拡散層DF、トランジスタQ1のソース・ドレイン領域を構成する拡散層DF、制御ゲート電極CG、メモリゲート電極MGまたはゲート電極G1のそれぞれの上面を

積層層間絶縁膜から露出する開口部である。なお、制御ゲート電極CGおよびメモリゲート電極MGのそれぞれの直上のコンタクトホールの底面には、シリサイド層SIの上面が露出する。

### [0137]

続いて、例えばスパッタリング法などを用いて積層層間絶縁膜上に、接続用の導電膜として、例えば主としてタングステン(W)からなる金属膜を形成し、これにより各コンタクトホール内を完全に埋め込む。ここでは、例えばチタン(Ti)、窒化チタン(TiN)またはそれらの積層膜からなるバリア導体膜を形成した後、バリア導体膜上にタングステン(W)膜からなる主導体膜を形成することで、バリア導体膜および主導体膜からなる当該金属膜を形成する。

[0138]

その後、積層層間絶縁膜上の不要な当該金属膜をCMP法などにより除去することにより、各コンタクトホール内に埋め込まれたコンタクトプラグを形成する。コンタクトプラグは、制御ゲート電極CG、メモリゲート電極MG、ソース・ドレイン領域またはゲート電極G1に電気的に接続される。

[0139]

このように、本実施の形態1によれば、メモリセル領域1Aの素子分離領域EIの上面を凸形状とすることにより、互いに隣り合うメモリセルMCの間において、トラップ性絶縁膜の経路が長くなるので、電荷拡散の影響を抑えることができて、半導体装置の信頼性が向上する。

[0140]

《变形例》

本実施の形態1の変形例による半導体装置について、図58および図59を用いて説明する。図58は、本実施の形態1による半導体装置のメモリセル領域を示す、図1のA-A線に沿った拡大断面図である。図59は、本実施の形態1の変形例による半導体装置のメモリセル領域を示す、図1のA-A線に沿った拡大断面図である。

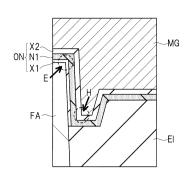

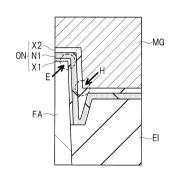

[0141]

前述の実施の形態1では、図3に示したように、互いに隣り合うフィンFAの間の素子分離領域EIの上面に形成された凸部は、例えば2つのフィンFAの間のほぼ中央部であって、2つのフィンFAのそれぞれの側壁から離れた位置に形成されている。従って、図58に示すように、互いに隣り合うフィンFAの間で、ONO膜ONの上面は、素子分離領域EIの上面に倣った形状となる。また、フィンFAの側壁とONO膜ONを介した位置にあるメモリゲート電極MGの下部の端部(図58に矢印Hで示す領域)は、素子分離領域EIの凸部の最も高い位置よりも下に位置している。

[0142]

しかし、本実施の形態1の変形例では、図59に示すように、互いに隣り合うフィンFAの間の素子分離領域EIの上面は凸形状であるが、フィンFAと素子分離領域EIの凸部との間にONO膜ONが埋め込まれている。これにより、互いに隣り合うフィンFAの間で、ONO膜ONの上面はほぼ平坦となる。また、フィンFAの側壁とONO膜ONを介した位置にあるメモリゲート電極MGの下部の端部(図59に矢印Hで示す領域)は、素子分離領域EIの凸部の最も高い位置よりも上にある。

[0143]

前述したように、メモリセルの「書込み」および「消去」を行う動作法として、それぞれSSI方式の書込みおよびFN方式の消去を適用することができる。SSI方式の書込みでは、電界およびホットエレクトロンの注入位置はフィンFAの上部に集中する(図58および図59に矢印Eで示す領域)。また、FN方式の消去では、電界およびホールの注入位置はメモリゲート電極MGの下部の端部に集中する(図58および図59に矢印Hで示す領域)。

[0144]

しかし、変形例のように、フィンFAと素子分離領域EIの凸部との距離が近づいて、

20

10

30

40

両者間がONO膜ONで埋まることにより、メモリゲート電極MGの下部の端部がフィンFAの上部に近づく。これにより、書き換えのミスマッチが改善されるので、素子分離領域EIの上面に凸部を形成したことによるデータ変動の抑制に加えて、書き換え効率の向上を図ることができる。

### [0145]

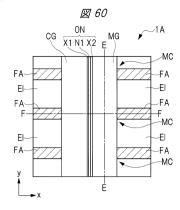

### (実施の形態2)

#### 《半導体装置の構造》

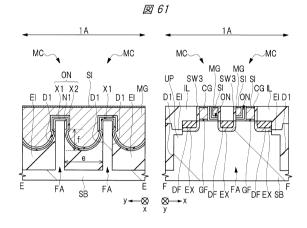

本実施の形態 2 による半導体装置の構造について図 6 0 および図 6 1 を用いて説明する。図 6 0 は、本実施の形態 2 による半導体装置のメモリセル領域を示す平面図である。図 6 1 は、本実施の形態 2 による半導体装置のメモリセル領域を示す、図 6 0 の E - E 線および F - F 線に沿った断面図である。

#### [0146]

図61のE-E線に沿った断面は、メモリセル領域のフィン上のゲート電極の延在方向に沿う断面を示し、F-F線に沿った断面は、メモリセル領域のフィンの延在方向に沿う断面を示す。なお、図60では、ソース・ドレイン領域、層間絶縁膜、各ゲート電極上のシリサイド層などの図示を省略している。

#### [0147]

本実施の形態 2 による半導体装置が、前述の実施の形態 1 による半導体装置と相違する点は、メモリセル領域 1 A の素子分離領域 E I の上面の形状である。すなわち、前述の実施の形態 1 による半導体装置では、メモリセル領域 1 A の素子分離領域 E I の上面は凸形状であるが、本実施の形態 2 による半導体装置では、メモリセル領域 1 A の素子分離領域 E I の上面は凹形状である。メモリセル領域 1 A の素子分離領域 E I の上面の形状以外の構成は、前述した実施の形態 1 による半導体装置とほぼ同一であるので、以下、前述の実施の形態 1 と相違する点を中心に説明する。

#### [0148]

図60および図61に示すように、メモリセル領域1Aにおいて、メモリセルMCは、 半導体基板SBの一部であって、半導体基板SBの上部に形成された板状のフィンFAの 上部に形成されている。複数のフィンFA同士の間には、半導体基板SBの上面に形成された満D1が形成されている。

### [0149]

素子分離領域EIは、溝D1を埋め込む絶縁膜である。但し、素子分離領域EIは溝D1を完全に埋め込んではおらず、素子分離領域EIの上面上には、フィンFAのそれぞれの一部が突出している。素子分離領域EIの上面から露出するフィンFAの高さは、例えば40nm~60nm程度である。素子分離領域EIは、例えば酸化シリコンからなる。

### [0150]

図61に示すように、素子分離領域EIの上面はy方向に沿った断面において凹形状となっている。言い換えると、y方向に互いに隣り合うフィンFAの間において、素子分離領域EIの上面の一部または全部が、一方のフィンFAの側壁に接する素子分離領域EIの上面の位置と他方のフィンFAの側壁に接する素子分離領域EIの上面の位置とを結んだ面よりも低い位置にある。

# [0151]

但し、素子分離領域EIの上面の凹部の深さが大きくなり過ぎると、素子分離領域EIの上面の段差が大きくなり、素子分離領域EIを形成した後の加工プロセスが難しくなる。このため、素子分離領域EIの上面の凹部の深さは、例えば40nm~80nm程度が望ましく、例えばy方向に互いに隣り合うフィンFAの間隔をe、凹部の深さをfとすると、f/eは0.4~0.8程度が望ましい。ここで、凹部の深さとは、y方向に隣り合うフィンFAの間において、一方のフィンFAの側壁に接する素子分離領域EIの上面の位置とを結んだ面から、素子分離領域EIの上面の最も低い位置までの距離である。

### [0152]

50

40

10

20

このように、メモリセル領域 1 A の素子分離領域 E I の上面を凹形状とすることにより、素子分離領域 E I の上面が平坦形状の場合と比べて、 y 方向に互いに隣り合うメモリセル M C の間において、トラップ性絶縁膜の経路が長くなるので、電荷拡散の影響を抑えることができる。

# [0153]

なお、本実施の形態 2 では、その説明は省略するが、ロジック領域における素子分離領域 E I の上面は凹形状とならず、ほぼ平坦となる。すなわち、ロジック領域の素子分離領域 E I の上面の平面度は、メモリセル領域 1 A の素子分離領域 E I の上面の平面度よりも小さくなる。

### [0154]

さらに、メモリセル領域1Aにおいて、y方向に並ぶ複数のフィンFAの直上には、それらのフィンFAを跨ぐように、y方向に延在する制御ゲート電極CGおよびy方向に延在するメモリゲート電極MGが形成されている。

# [0155]

制御ゲート電極CGは、素子分離領域EIの上面から露出するフィンFAの上面および 側壁にゲート絶縁膜GFを介して形成されている。ゲート絶縁膜GFは、例えば酸化シリ コンからなり、制御ゲート電極CGは、例えばポリシリコンからなる。

#### [0156]

×方向における制御ゲート電極CGの一方の側壁はサイドウォールSW3により覆われ、他方の側壁には、ONO膜ONを介してメモリゲート電極MGが形成されている。また、メモリゲート電極MGは、素子分離領域EIの上面から露出するフィンFAの上面および側壁にONO膜ONを介して形成されている。すなわち、ONO膜ONは、フィンFAの上面と、制御ゲート電極CGの側壁とに沿って連続的に形成されたL字型の断面を有する。メモリゲート電極MGは、ONO膜ONにより制御ゲート電極CGおよびフィンFAから絶縁されている。

# [0157]

《半導体装置の特徴および効果》

本実施の形態 2 による半導体装置の主な特徴は、メモリセル領域 1 A の素子分離領域 E I の上面を凹形状としている点にある。

# [0158]

本実施の形態 2 による半導体装置では、メモリセル領域 1 A の素子分離領域 E I の上面を凹形状とすることにより、 y 方向に互いに隣り合うメモリセルMCの間の窒化シリコン膜 N 1 (トラップ性絶縁膜)の経路を長くしている。すなわち、凹部を形成した場合、凹部を形成しない場合と比べて、窒化シリコン膜 N 1 の経路が長くなり、電荷の拡散距離が長くなるので、 y 方向に互いに隣り合うメモリセルMCの間の窒化シリコン膜 N 1 の経路を介したデータ変動を抑制することができる。これにより、半導体装置の信頼性を向上することができる。

#### [0159]

# 《半導体装置の製造方法》

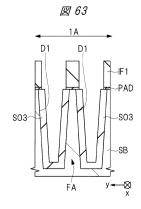

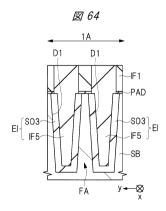

本実施の形態 2 による半導体装置(メモリセル領域)の製造方法について図 6 2 ~ 図 6 7 を用いて説明する。図 6 2 ~ 図 6 7 は、本実施の形態 2 による半導体装置(メモリセル領域)の製造工程を説明する断面図であり、図 6 0 の E - E 線に沿った断面図である。

### [0160]

まず、図62に示すように、メモリセル領域1Aにおいて半導体基板SBの上面を含む 一部からなるフィンFAと、フィンFAの周囲の溝D1とを形成する。溝D1の深さは、 例えば120nm~250nm程度である。

#### [0161]

なお、溝 D 1 を形成するまでの製造過程は、前述の実施の形態 1 とほぼ同様であるため (図 6 ~ 図 1 2 参照)、その説明を省略する。

# [0162]

50

10

20

30

次に、図63に示すように、溝D1の底面および側壁に、例えば熱酸化法を用いて酸化膜SO3を形成する。酸化膜SO3は、例えば酸化シリコンからなり、その厚さは、例えば10nm~20nm程度である。

### [0163]

次に、図64に示すように、例えばCVD法を用いて溝D1の内側を絶縁膜IF5により埋め込む。絶縁膜IF5は、例えば酸化シリコンからなる。その後、例えばCMP法を用いて絶縁膜IF5を研磨する。これにより、絶縁膜IF1の上面を露出させ、絶縁膜IF1の上面と、溝D1に埋め込まれた絶縁膜IF5の上面とを平坦化する。酸化膜SO3と、溝D1に埋め込まれた絶縁膜IF5とは素子分離領域EIを構成する。

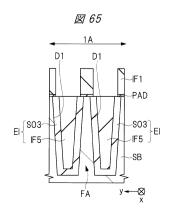

### [0164]

次に、図65に示すように、絶縁膜IF5の上面をエッチバックにより後退させることで、絶縁膜IF1の側壁を素子分離領域EIから露出させる。当該エッチバックは、ウェットエッチングまたはドライエッチングのいずれを用いてもよい。

# [0165]

次に、図66に示すように、ウェットエッチングにより絶縁膜IF1を除去してフィンFAの上面の酸化膜PADを露出させる。ここで、メモリセル領域1AにおけるフィンFAのy方向の幅は、例えば20nm~50nm程度であり、素子分離領域EIのy方向の幅は、例えば90nmである。

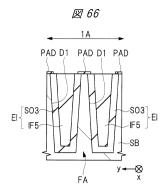

#### [0166]

次に、図67に示すように、ウェットエッチングを用いて酸化膜PADを除去し、素子分離領域EIの上面を後退させることで、フィンFAの側壁を素子分離領域EIから露出させる。

#### [0167]

熱酸化法を用いて形成された酸化膜 S O 3 のエッチングレートは、 C V D 法を用いて形成された絶縁膜 I F 5 のエッチングレートが遅いため、絶縁膜 I F 5 は酸化膜 S O 3 よりも早くウェットエッチングが進む。これにより、素子分離領域 E I の上面は y 方向に沿った断面において凹形状となる。但し、素子分離領域 E I の上面の凹部の深さが大きくなり過ぎると、素子分離領域 E I の上面の段差が大きくなり、素子分離領域 E I を形成した後の加工プロセスが難しくなるため、素子分離領域 E I の上面の凹部の深さは、例えば 4 0 n m ~ 8 0 n m 程度が好ましい。また、素子分離領域 E I の上面から露出するフィン F A の高さは、例えば 4 0 n m ~ 6 0 n m 程度である。

# [0168]

本実施の形態2の主な特徴の1つは、メモリセル領域1Aの素子分離領域EIの上面を 凹形状とすることで、メモリセル領域1Aにおいてy方向に互いに隣り合うメモリセルの 間のトラップ性絶縁膜の経路が長くなり、電荷拡散の影響が抑えられることである。

#### [0169]

その後は、前述の実施の形態1と同様にして、制御ゲート電極CG、ゲート絶縁膜GF、メモリゲート電極MG、ONO膜ON、ソース・ドレイン領域、シリサイド層SIなどを形成することにより、半導体装置が略完成する。

#### [0170]

このように、本実施の形態 2 によれば、メモリセル領域 1 A の素子分離領域 E I の上面を凹形状とすることにより、互いに隣り合うメモリセルMCの間において、トラップ性絶縁膜の経路が長くなるので、電荷拡散の影響を抑えることができて、半導体装置の信頼性が向上する。

#### [0171]

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

### [0172]

本発明は少なくとも以下の実施の形態を含む。

10

20

30

#### [0173]

〔付記1〕

- (a) 半導体基板の主面上に、第1 絶縁膜を形成する工程、

- (b)前記第1絶縁膜および前記半導体基板を順次加工して、複数の溝を形成することにより、前記半導体基板の前記主面に沿う第1方向に延在し、前記半導体基板の前記主面に沿って前記第1方向と直交する第2方向に互いに離間する、前記半導体基板の一部分からなる複数の突出部を形成する工程、

- (c)熱酸化法を用いて、前記複数の溝の内部の露出した前記半導体基板の表面に第1酸化膜を形成する工程、

- (d)CVD法を用いて、前記複数の溝の内部を第2酸化膜で埋め込む工程、

- (e)前記第1絶縁膜の上面および前記第2酸化膜の上面を平坦化する工程、

- (f)前記第2酸化膜を後退させて、前記第1絶縁膜の側壁を露出させる工程、

- (g)前記第1絶縁膜を除去する工程、

- (h)ウェットエッチングを用いて、前記第1および第2酸化膜の上面を後退させて、 複数の前記突出部の側壁を露出させる工程、

- (i)前記第1および第2酸化膜の上面から露出した前記突出部の上部の上面および側壁と第2絶縁膜を介し、前記第2方向に延在する第1ゲート電極を形成する工程、

- (j)前記第1および第2酸化膜の上面から露出した前記突出部の上部の上面および側壁並びに前記第1ゲート電極の一方の側壁とトラップ性絶縁膜を含む第3絶縁膜を介し、前記第2方向に延在する第2ゲート電極を形成する工程、 を有し、

前記第2方向に互いに隣り合う前記突出部の間において、前記第2酸化膜の上面が、一方の前記突出部の側壁に接する前記第1酸化膜の上面の位置と他方の前記突出部の側壁に接する前記第1酸化膜の上面の位置とを結んだ第1面よりも低い、半導体装置の製造方法

[0174]

〔付記2〕

付記1記載の半導体装置の製造方法において、

前記第1面の前記第2方向の幅をWとし、前記第1面から前記第2酸化膜の上面の最も低い位置までの距離をDとすると、D/Wは0.4~0.8である、半導体装置の製造方法。

[0175]

〔付記3〕

付記1記載の半導体装置の製造方法において、

前記第1面から前記第2酸化膜の上面の最も低い位置までの距離は、40nm~60nmである、半導体装置の製造方法。

# 【符号の説明】

[0176]

- 1 A メモリセル領域

- 1 B ロジック領域

- CG 制御ゲート電極

- D1,D2 溝

- DF 拡散層

- DG ダミーゲート電極

- EI 素子分離領域

- EX エクステンション領域

- FA, FB フィン

- G1 ゲート電極

- GF、GI ゲート絶縁膜

- IF1,IF2,IF3,IF4,IF5 絶縁膜

40

30

10

20

IL 層間絶縁膜

MC メモリセル

MG メモリゲート電極

N1 窒化シリコン膜

ON ONO膜

PAD 酸化膜

Q1 トランジスタ

R P レジストパターン

SI シリサイド層

SB 半導体基板

SL1 アモルファスシリコン膜

SL2, SL3 ポリシリコン膜

S N 1 , S N 2 室化シリコン膜

SО1,SО2 酸化シリコン膜

SO3 酸化膜

SW1,SW2,SW3 サイドウォール

UP 下部パターン

X 1 , X 2 酸化シリコン膜

# 【図1】

# 【図2】

# 【図3】

【図4】

【図5】

**⊠** 5

【図8】

⊠ 8

【図7】

【図9】

【図18】

【図20】

【図19】

【図21】

【図22】

D1 UP

EI

**⊗**−

図 23

【図24】

UP D,1

FΑ

【図23】

SB

-⊗ × **⊗→** X

【図25】

# 【図26】

**26**

【図28】

**28**

【図27】

図 27

【図29】

図 29

【図30】

【図32】

【図31】

【図33】

【図44】

【図43】

【図45】

【図46】

【図48】

【図47】

【図49】

【図52】

【図51】

【図53】

【図54】

【図56】

【図55】

【図57】

【図58】

図 58

【図59】

図 59

【図62】

【図63】

【図60】

【図61】

【図64】

【図65】

# 【図66】

# 【図67】

# フロントページの続き

(51) Int.CI. F I

H 0 1 L 27/10 (2006.01)

(56)参考文献 米国特許出願公開第2006/0292781(US,A1)

特開2014-017343(JP,A)

特開2013-143437(JP,A)

特開2011-097057(JP,A)

特開2004-327812(JP,A)

特開2011-077321(JP,A)

米国特許出願公開第2011/0097889(US,A1)

米国特許出願公開第2014/0008716(US,A1)

米国特許出願公開第2008/0057644(US,A1)

(58)調査した分野(Int.CI., DB名)

H01L 21/336,21/70,

27/088,27/10,

27/11568,27/11573,

29/78,29/788,29/792