## (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**HO3M 13/11** (2006.01) **HO3M 13/00** (2017.01) **HO3M 13/35** (2006.01)

(52) CPC특허분류

**HO3M 13/1162** (2013.01) **HO3M 13/35** (2013.01)

(21) 출원번호 10-2019-7021800(분할)

(22) 출원일자(국제) **2018년02월05일** 심사청구일자 **2021년02월01일**

(85) 번역문제출일자 2019년07월24일

(65) 공개번호 **10-2019-0107039**

(43) 공개일자 2019년09월18일

(62) 원출원 **특허 10-2018-7032458** 원출원일자(국제) **2018년02월05일** 심사청구일자 **2018년11월13일**

(86) 국제출원번호 PCT/KR2018/001505

(87) 국제공개번호 **WO 2018/143743** 국제공개일자 **2018년08월09일**

(30) 우선권주장

62/455,478 2017년02월06일 미국(US) 62/518,609 2017년06월13일 미국(US)

(56) 선행기술조사문헌 US20110083052 A1 KR1020060061145 A (45) 공고일자 2022년10월04일

(11) 등록번호 10-2450243

(24) 등록일자 2022년09월28일

(73) 특허권자

#### 엘지전자 주식회사

서울특별시 영등포구 여의대로 128 (여의도동)

(72) 발명자

#### 신종웅

서울특별시 서초구 양재대로11길 19 LG전자 특허 센터

### 김봉회

서울특별시 서초구 양재대로11길 19 LG전자 특허 센터

(뒷면에 계속)

(74) 대리인

특허법인(유한)케이비케이

전체 청구항 수 : 총 8 항

심사관 : 조춘근

#### (54) 발명의 명칭 행-직교 구조(row-orthogonal)를 이용한 LDPC 코드 전송 방법 및 이를 위한 장치

#### (57) 요 약

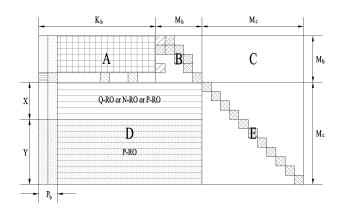

$H = \begin{bmatrix} A & B & C \\ D & E \end{bmatrix}$ 를 기반으로 한 인코딩/디코딩 방법 및 장치가 제공된다. 상기 패리티 체크 행렬 (뒷면에 계속)

#### 대 표 도 - 도16

은 각각이 Z\*Z 차원의 영 행렬 또는 Z\*Z 차원의 순환 퍼뮤테이션 행렬인 복수의 서브블록들록 구성되고, 상기 패리티 체크행렬에서, [A B]는 M<sub>b</sub>\*(K<sub>b</sub> + M<sub>b</sub>) 차원의 행렬이고, B는 M<sub>b</sub>\*M<sub>b</sub> 차원의 이중 대각 구조 행렬이며, C는 M<sub>b</sub>\*M<sub>c</sub> 차원의 영 행렬이고, E는 M<sub>c</sub>\*M<sub>c</sub> 차원의 단일 대각 구조 행렬이고, D는 의사-행 직교 구조의 행렬이다.

(52) CPC특허분류

**HO3M 13/6502** (2013.01) **HO3M 13/6508** (2013.01) 변일무

서울특별시 서초구 양재대로11길 19 LG전자 특허센

(72) 발명자

김진우

서울특별시 서초구 양재대로11길 19 LG전자 특허센터

#### 명세서

## 청구범위

#### 청구항 1

무선 통신 시스템에서 전송 장치가 저밀도 패리티 체크(low density parity check, LDPC) 코드를 이용하여 정보 블록을 전송함에 있어서,

$$H = \begin{bmatrix} A & B & C \\ D & E \end{bmatrix}$$

를 기반으로 상기 정보 블록을 인코딩; 및

상기 인코딩된 정보 블록을 전송하는 것을 포함하며,

상기 LDPC 코드 행렬의 각 원소(element)는 Z\*Z 차원(dimension)의 영(zero) 행렬, 또는 Z\*Z 차원의 단위 (identity) 행렬을 오른쪽으로 음이 아닌 정수 번만큼 순환적으로 천이하여 얻어진 Z\*Z 차원의 순환 퍼뮤테이션 행렬을 나타내고, 여기서 Z는 양의 정수이며,

"[A B]"는 M,\*(K, + M,) 차원의 행렬이며, 여기서 M,와 K,는 각각(respectively) 양의 정수들이고,

"B"는, "B"의 제1 대각선의 M<sub>6</sub>개 원소들, "B"의 상기 제1 대각선의 원소들 바로 위 제2 대각선의 (M<sub>6</sub> - 1)개 원소들, 및 "B"의 가장 왼쪽 열(column)의 원소들 중 "B"의 상기 제1 대각선의 가장 왼쪽 원소 아래 2개 원소들을 제외한, "B"의 모든 원소가 상기 Z\*Z 차원의 영 행렬을 나타내는, M<sub>6</sub>\*M<sub>6</sub> 차원의 이중 대각 구조 행렬(dual diagonal structure matrix)이며,

"C"는 M<sub>b</sub>\*M<sub>c</sub> 차원의 행렬이고, "C"의 모든 원소는 상기 Z\*Z 차원의 영 행렬을 나타내며, 여기서 M<sub>c</sub>는 양의 정수이고,

"E"는, "E"의 대각선의 Mc개 원소들을 제외한 "E"의 모든 원소가 상기 Z\*Z 차원의 영 행렬을 나타내는, Mc\*Mc 차원의 단일 대각 구조 행렬(single diagonal structure matrix)이며,

"D"는 (M<sub>c</sub> - Y)개 상위 행(row)들과 Y개 하위 행들로 구성된 M<sub>c</sub>\*(K<sub>b</sub> + M<sub>b</sub>) 차원의 행렬이며, 여기서 (M<sub>c</sub> - Y)는 양의 정수이고,

상기 Y개 하위 행들은 상기 Y개 하위 행들의 매 2개 연속(consecutive) 행들이 각 열 내에 상기 Z\*Z 차원의 행렬을 나타내지 않는 원소를 많아야 1개 가지며,

상기 (M<sub>c</sub> - Y)개 상위 행들은:

i) 상기 LDPC 코드 행렬의 평처링 영역에 속하는, "D"의 가장 왼쪽 2개 열들을 제외한 각 열 내에 상기 Z\*Z 차원의 행렬을 나타내지 않는 원소를 많아야 1개 가지고, ii) 상기  $(M_c-Y)$ 개 상위 행들의 각 행 i에 대해, 여기 서  $i=1,\cdots$ ,  $(M_c-Y)$ , 상기 행 i 및 상기 행 i 바로 위 행 또는 상기 i 및 상기 행 i 바로 아래 행이 상기 가장 왼쪽 2개 열들 중 적어도 하나에서 상기 Z\*Z 영 행렬을 나타내지 않는 원소를 1개보다 많이 가지는, 의사행 직교 구조(quasi-row orthogonal structure)인,

정보 블록 전송 방법.

#### 청구항 2

제1항에 있어서,

"A"는 행 직교 구조가 아닌,

정보 블록 전송 방법.

#### 청구항 3

무선 통신 시스템에서 전송 장치가 저밀도 패리티 체크(low density parity check, LDPC) 코드를 이용하여 정보 블록을 전송함에 있어서,

$$H = \begin{bmatrix} A & B & C \\ D & E \end{bmatrix}$$

를 기반으로 상기 정보 블록을 인코딩하도록 구성된 인코더; 및

상기 인코딩된 정보 블록을 전송하도록 구성된 전송 모듈을 포함하며,

상기 LDPC 코드 행렬의 각 원소(element)는 Z\*Z 차원(dimension)의 영(zero) 행렬, 또는 Z\*Z 차원의 단위 (identity) 행렬을 오른쪽으로 음이 아닌 정수 번만큼 순환적으로 천이하여 얻어진 Z\*Z 차원의 순환 퍼뮤테이션 행렬을 나타내고, 여기서 Z는 양의 정수이며,

"[A B]"는 M<sub>b</sub>\*(K<sub>b</sub> + M<sub>b</sub>) 차원의 행렬이며, 여기서 M<sub>b</sub>와 K<sub>b</sub>는 각각(respectively) 양의 정수들이고,

"B"는, "B"의 제1 대각선의 M<sub>b</sub>개 원소들, "B"의 상기 제1 대각선의 원소들 바로 위 제2 대각선의 (M<sub>b</sub> - 1)개 원소들, 및 "B"의 가장 왼쪽 열(column)의 원소들 중 "B"의 상기 제1 대각선의 가장 왼쪽 원소 아래 2개 원소들을 제외한, "B"의 모든 원소가 상기 Z\*Z 차원의 영 행렬을 나타내는, M<sub>b</sub>\*M<sub>b</sub> 차원의 이중 대각 구조 행렬(dual diagonal structure matrix)이며,

"C"는  $M_b*M_c$  차원의 행렬이고, "C"의 모든 원소는 상기 Z\*Z 차원의 영 행렬을 나타내며, 여기서  $M_c$ 는 양의 정수이고.

"E"는, "E"의 대각선의  $M_c$ 개 원소들을 제외한 "E"의 모든 원소가 상기 Z\*Z 차원의 영 행렬을 나타내는,  $M_c*M_c$  차원의 단일 대각 구조 행렬(single diagonal structure matrix)이며,

"D"는 (M<sub>c</sub> - Y)개 상위 행(row)들과 Y개 하위 행들로 구성된 M<sub>c</sub>\*(K<sub>b</sub> + M<sub>b</sub>) 차원의 행렬이며, 여기서 (M<sub>c</sub> - Y)는 양의 정수이고,

상기 Y개 하위 행들은 상기 Y개 하위 행들의 매 2개 연속(consecutive) 행들이 각 열 내에 상기 Z\*Z 차원의 행렬을 나타내지 않는 원소를 많아야 1개 가지며,

상기 (M<sub>c</sub> - Y)개 상위 행들은:

i) 상기 LDPC 코드 행렬의 평처링 영역에 속하는, "D"의 가장 왼쪽 2개 열들을 제외한 각 열 내에 상기 Z\*Z 차원의 행렬을 나타내지 않는 원소를 많아야 1개 가지고, ii) 상기 (M<sub>c</sub> - Y)개 상위 행들의 각 행 i에 대해, 여기서 i = 1,…, (M<sub>c</sub> - Y), 상기 행 i 및 상기 행 i 바로 위 행 또는 상기 i 및 상기 행 i 바로 아래 행이 상기가장 왼쪽 2개 열들 중 적어도 하나에서 상기 Z\*Z 영 행렬을 나타내지 않는 원소를 1개보다 많이 가지는, 의사행 직교 구조(quasi-row orthogonal structure)인,

전송 장치.

### 청구항 4

제3항에 있어서,

"A"는 행 직교 구조가 아닌,

전송 장치.

#### 청구항 5

무선 통신 시스템에서 수신 장치가 저밀도 패리티 체크(low density parity check, LDPC) 코드를 이용하여 정보 블록을 수신함에 있어서,

인코딩된 정보 블록을 수신; 및

$H = \begin{bmatrix} A & B & C \\ D & E \end{bmatrix}$ 상기 인코딩된 정보 블록을 LDPC 코드 행렬 = 기반으로 디코딩하여 상기 정보 블록을 획득하는 것을 포함하며,

상기 LDPC 코드 행렬의 각 원소(element)는 Z\*Z 차원(dimension)의 영(zero) 행렬, 또는 Z\*Z 차원의 단위 (identity) 행렬을 오른쪽으로 음이 아닌 정수 번만큼 순환적으로 천이하여 얻어진 Z\*Z 차원의 순환 퍼뮤테이션 행렬을 나타내고, 여기서 Z는 양의 정수이며,

"[A B]"는 M,\*(K, + M,) 차원의 행렬이며, 여기서 M,와 K,는 각각(respectively) 양의 정수들이고,

"B"는, "B"의 제1 대각선의 M₀개 원소들, "B"의 상기 제1 대각선의 원소들 바로 위 제2 대각선의 (M₀ - 1)개 원소들, 및 "B"의 가장 왼쪽 열(column)의 원소들 중 "B"의 상기 제1 대각선의 가장 왼쪽 원소 아래 2개 원소들을 제외한, "B"의 모든 원소가 상기 Z\*Z 차원의 영 행렬을 나타내는, M₀\*M₀ 차원의 이중 대각 구조 행렬(dual diagonal structure matrix)이며,

"C"는 M<sub>b</sub>\*M<sub>c</sub> 차원의 행렬이고, "C"의 모든 원소는 상기 Z\*Z 차원의 영 행렬을 나타내며, 여기서 M<sub>c</sub>는 양의 정수이고,

"E"는, "E"의 대각선의  $M_c$ 개 원소들을 제외한 "E"의 모든 원소가 상기 Z\*Z 차원의 영 행렬을 나타내는,  $M_c*M_c$  차원의 단일 대각 구조 행렬(single diagonal structure matrix)이며,

"D"는 (M<sub>c</sub> - Y)개 상위 행(row)들과 Y개 하위 행들로 구성된 M<sub>c</sub>\*(K<sub>b</sub> + M<sub>b</sub>) 차원의 행렬이며, 여기서 (M<sub>c</sub> - Y)는 양의 정수이고,

상기 Y개 하위 행들은 상기 Y개 하위 행들의 매 2개 연속(consecutive) 행들이 각 열 내에 상기 Z\*Z 차원의 행렬을 나타내지 않는 원소를 많아야 1개 가지며,

상기 (M<sub>c</sub> - Y)개 상위 행들은:

i) 상기 LDPC 코드 행렬의 평처링 영역에 속하는, "D"의 가장 왼쪽 2개 열들을 제외한 각 열 내에 상기 Z\*Z 차원의 행렬을 나타내지 않는 원소를 많아야 1개 가지고, ii) 상기 (M<sub>c</sub> - Y)개 상위 행들의 각 행 i에 대해, 여기서 i = 1,…, (M<sub>c</sub> - Y), 상기 행 i 및 상기 행 i 바로 위 행 또는 상기 i 및 상기 행 i 바로 아래 행이 상기가장 왼쪽 2개 열들 중 적어도 하나에서 상기 Z\*Z 영 행렬을 나타내지 않는 원소를 1개보다 많이 가지는, 의사행 직교 구조(quasi-row orthogonal structure)인, 정보 블록 수신 방법.

#### 청구항 6

제5항에 있어서,

"A"는 행 직교 구조가 아닌,

정보 블록 수신 방법.

## 청구항 7

무선 통신 시스템에서 수신 장치가 저밀도 패리티 체크(low density parity check, LDPC) 코드를 이용하여 정보 블록을 수신함에 있어서,

인코딩된 정보 블록을 수신하도록 구성된 수신 모듈; 및

상기 LDPC 코드 행렬의 각 원소(element)는 Z\*Z 차원(dimension)의 영(zero) 행렬, 또는 Z\*Z 차원의 단위 (identity) 행렬을 오른쪽으로 음이 아닌 정수 번만큼 순환적으로 천이하여 얻어진 Z\*Z 차원의 순환 퍼뮤테이션 행렬을 나타내고, 여기서 Z는 양의 정수이며,

"[A B]"는 M,\*(K, + M,) 차원의 행렬이며, 여기서 M,와 K,는 각각(respectively) 양의 정수들이고,

"B"는, "B"의 제1 대각선의 M<sub>b</sub>개 원소들, "B"의 상기 제1 대각선의 원소들 바로 위 제2 대각선의 (M<sub>b</sub> - 1)개 원소들, 및 "B"의 가장 왼쪽 열(column)의 원소들 중 "B"의 상기 제1 대각선의 가장 왼쪽 원소 아래 2개 원소들을 제외한, "B"의 모든 원소가 상기 Z\*Z 차원의 영 행렬을 나타내는, M<sub>b</sub>\*M<sub>b</sub> 차원의 이중 대각 구조 행렬(dual diagonal structure matrix)이며,

"C"는  $M_b*M_c$  차원의 행렬이고, "C"의 모든 원소는 상기 Z\*Z 차원의 영 행렬을 나타내며, 여기서  $M_c$ 는 양의 정수이고,

"E"는, "E"의 대각선의 Mc개 원소들을 제외한 "E"의 모든 원소가 상기 Z\*Z 차원의 영 행렬을 나타내는, Mc\*Mc 차원의 단일 대각 구조 행렬(single diagonal structure matrix)이며,

"D"는 (M<sub>c</sub> - Y)개 상위 행(row)들과 Y개 하위 행들로 구성된 M<sub>c</sub>\*(K<sub>b</sub> + M<sub>b</sub>) 차원의 행렬이며, 여기서 (M<sub>c</sub> - Y)는 양의 정수이고,

상기 Y개 하위 행들은 상기 Y개 하위 행들의 매 2개 연속(consecutive) 행들이 각 열 내에 상기 Z\*Z 차원의 행렬을 나타내지 않는 원소를 많아야 1개 가지며,

상기 (M<sub>c</sub> - Y)개 상위 행들은:

i) 상기 LDPC 코드 행렬의 평처링 영역에 속하는, "D"의 가장 왼쪽 2개 열들을 제외한 각 열 내에 상기 Z\*Z 차원의 행렬을 나타내지 않는 원소를 많아야 1개 가지고, ii) 상기 (M<sub>c</sub> - Y)개 상위 행들의 각 행 i에 대해, 여기서 i = 1,…, (M<sub>c</sub> - Y), 상기 행 i 및 상기 행 i 바로 위 행 또는 상기 i 및 상기 행 i 바로 아래 행이 상기가장 왼쪽 2개 열들 중 적어도 하나에서 상기 Z\*Z 영 행렬을 나타내지 않는 원소를 1개보다 많이 가지는, 의사-행 직교 구조(quasi-row orthogonal structure)인,

수신 장치.

#### 청구항 8

제7항에 있어서,

"A"는 행 직교 구조가 아닌,

수신 장치.

## 발명의 설명

#### 기술분야

[0001] 본 발명은 무선 랜 시스템에 관한 것으로서, 보다 상세하게는 LDPC (Low-Density Parity-Check) 코드를 지원하는 시스템에서 row-orthogonal 구조를 이용하여 LDPC 코드를 전송하는 방법 및 이를 지원하는 장치에 관한 것이다.

### 배경기술

- [0002] 무선 접속 시스템이 음성이나 데이터 등과 같은 다양한 종류의 통신 서비스를 제공하기 위해 광범위하게 전개되고 있다. 일반적으로 무선 접속 시스템은 가용한 시스템 자원(대역폭, 전송 파워 등)을 공유하여 다중 사용자와의 통신을 지원할 수 있는 다중 접속(multiple access) 시스템이다. 다중 접속 시스템의 예들로는 CDMA(code division multiple access) 시스템, FDMA(frequency division multiple access) 시스템, TDMA(time division multiple access) 시스템, OFDMA(orthogonal frequency division multiple access) 시스템, SC-FDMA(single carrier frequency division multiple access) 시스템 등이 있다.

- [0003] 상술한 통신 시스템들에서뿐만 아니라, 방송 시스템에 있어서도 채널 코드(channel code)가 필수적으로 이용되고 있다. 채널 코드의 일반적인 구성 방법의 예시로서, 송신단이 부호화기를 이용하여 입력 심볼에 대하여 부호화를 수행하고 부호화된 심볼을 송신할 수 있다. 또한, 예를 들어, 수신단은 부호화된 심볼을 수신하고 수신된 심볼에 대하여 복호를 수행하여 입력 심볼을 복원할 수 있다. 이 경우, 입력 심볼의 크기와 부호화된 심볼의 크기는 통신 시스템에 따라서 달리 정의될 수 있다. 예를 들어, 3GPP (3rd Generation Partnership Project)의

LTE (Long Term Evolution) 통신 시스템에서 사용되는 데이터 정보용 터보(turbo) 코드에서, 입력 심볼의 크기는 최대 6144 비트이고, 부호화된 심볼의 크기는 18432 (6144\*3) 비트이다. LTE 통신 시스템에서의 터보 코딩은 3GPP 기술 규격 36.212에 의하여 참조될 수 있다.

- [0004] 그러나, LTE 터보 코드는 코드의 구조상 SNR (Signal to Noise Ratio)이 증가되더라도 일정 영역을 벗어나면 성능 개선이 미미한 특징이 있다. 이와 관련하여, 보다 오류 발생률이 낮은 코드를 이용하는 것이 고려될 수 있으나, 이 경우, 복잡도가 증가하는 문제점이 있다.

- [0005] 통신 시스템에 있어서 높은 오류율은 불필요한 데이터의 재송신과 채널 수신 실패를 초래할 수 있다. 또한, 지나치게 높은 복잡도의 코드는 기지국과 단말의 부하를 증가시킬 뿐만 아니라, 송수신 지연을 초래할 수 있다. 특히, 더 빠른 데이터의 송수신이 요구되는 차세대 통신 시스템에 있어서는, 상술한 문제점들이 해결이 요구된다. 따라서, 오류율을 낮추면서도 낮은 복잡도를 갖는 코딩 방법이 요구된다.

- [0006] 특히, 5 세대 이동통신 기술과 관련하여, URLLC (Ultra Reliable and Low-Latency Communication)가 논의되고 있다. URLLC 시나리오에서, 10-5 이하의 BLER(Block Error Rate)에서 오류 플로어가 발생할 것이 요구된다. 여기서 오류 플로어는 정보 크기의 증가에도 불구하고 오류율의 감소가 미미한 지점을 의미한다. LTE 터보 코드에 있어서는 정보 크기의 증가에 따라, 10-4 이하의 BLER에서 오류 플로어가 발생한다. 따라서, 터보 코드의 대안으로써 LDPC 코드가 이용될 수 있다. LDPC는 상대적으로 낮은 복잡도를 가지면서도 낮은 오류율을 달성할 수 있다. LDPC 코드의 효율적인 이용을 위하여, 다중 LDPC 코드에서의 베이스 코드 선택 방법 등이 결정될 필요가 있다.

### 발명의 내용

#### 해결하려는 과제

- [0007] 본 발명이 이루고자 하는 기술적 과제는, LDPC 코드를 사용하는 무선랜 시스템에서 주어진 통신환경에 부합하는 LDPC 코드를 전송하는 방법을 제공하는데 있다.

- [0008] 본 발명이 이루고자 하는 또 다른 기술적 과제는 다중 LDPC 코드를 사용하는 무선랜 시스템에서 활용될 수 있는 row-orthogonal 구조의 LDPC 코드 구조 생성 방법을 제공하는 데 있다.

- [0009] 본 발명은 상술된 기술적 과제에 한정되지 않으며 다른 기술적 과제들이 본 발명의 실시예들로부터 유추될 수 있다.

## 과제의 해결 수단

- [0010] 상술한 기술적 과제를 이루기 위한 본 발명의 일 측면에 따른 LDPC (Quasi-Cyclic Low-Density Parity-Check) 코드의 인코딩 방법은 고 율 코드(high rate code) 행렬과 단일 패리티 체크 코드 행렬로 구성되는 다 엣지 (multi edge) LDPC 코드 행렬을 생성하는 단계; 및 상기 다 엣지 LDPC 코드 행렬을 이용하여 신호를 인코딩 하는 단계를 포함하되, 상기 단일 패리티 체크 코드 행렬은 비 행-직교(non row-orthogonal) 구조 행렬로 구성되는 제 1 행렬과 순 행-직교(pure row-orthogonal) 구조로 구성되는 제 2 행렬이 연접하여 구성될 수 있다.

- [0011] 또한, 본 발명의 다른 일 측면에 따른, LDPC (Quasi-Cyclic Low-Density Parity-Check) 코드를 인코딩하는 장치는 송수신기, 및 프로세서를 포함하고, 상기 프로세서는, 고 율 코드(high rate code) 행렬과 단일 패리티 체크 코드 행렬로 구성되는 다 엣지(multi edge) LDPC 코드 행렬을 생성하고, 상기 다 엣지 LDPC 코드 행렬을 이용하여 신호를 인코딩 하도록 구성되되, 상기 단일 패리티 체크 코드 행렬은 비 행-직교(non row-orthogonal) 구조 행렬로 구성되는 제 1행렬과 순 행-직교(pure row-orthogonal) 구조로 구성되는 제 2 행렬이 연접하여 구성될 수 있다.

- [0012] 또한, LDPC (Quasi-Cyclic Low-Density Parity-Check) 코드를 인코딩하는 방법 및 장치에 대해서 다음 사항들이 공통으로 적용될 수 있다.

- [0013] 상기 제 1 행렬은 연속하는 행(row)에 대해 동일한 열(column) 값을 가지는 엣지를 포함하고, 상기 제 2 행렬은 연속하는 행에 대해 동일한 열 값을 가지는 엣지를 포함하지 않을 수 있다.

- [0014] 상기 제 1 행렬은 제 1 값의 행 개수를 가지고, 상기 제 2 행렬은 제 2 값의 행 개수 가지되, 상기 제 1값 및 상기 제 2값은, 상기 단일 패리티 체크 코드 행렬의 전체 행 개수와 상기 다 엣지 LDPC 코드의 최소 부호 율 (code rate)에 따라 결정 될 수 있다.

- [0015] 상기 제 1 값은 상기 단일 패리티 체크 코드 행렬의 전체 행 개수와 상기 최소 부호율의 곱으로 결정되고, 상기 제 2값은 상기 단일 패리티 체크 코드 행렬의 전체 행 개수에서 상기 제 1값을 뺀 값으로 결정 될 수 있다.

- [0016] 상기 제 1 행렬은 제 1 값의 행 개수를 가지고, 상기 제 2 행렬은 제 2 값의 행 개수 가지되, 상기 제 1값 및 상기 제 2값은, 기 설정된 부호율을 가지는 상기 단일 패리티 체크 코드 행렬의 행부터 상기 제 2행렬이 할당되도록 결정될 수 있다.

- [0017] 상기 제 1 행렬은 22의 행 값으로 설정되고, 상기 제 2 행렬은 20의 행 값으로 설정될 수 있다.

- [0018] 상기 고율 코드 행렬은 7 x 17의 행렬 구조로 설정될 수 있고, 상기 고율 코드 행렬은 4 x 4 구조의 이중 대각 선(dual diagonal) 패리티 행렬을 포함할 수 있다.

#### 발명의 효과

- [0019] 본 발명의 일 실시예에 따르면, 다양한 통신 환경에 부합하는 LDPC 코드를 이용하여 LDPC 코드를 생성할 수 있는 효과가 있다.

- [0020] 본 발명의 또 다른 일 실시예에 따르면, 부분(partial) row-orthogonal 구조의 LDPC 코드 구조를 이용하여, 시 스템의 성능 열화 없이 LDPC 코드를 전송할 수 있는 효과가 있다.

- [0021] 상술된 기술적 효과 외에 다른 기술적 효과들이 본 발명의 실시예들로부터 유추될 수 있다.

#### 도면의 간단한 설명

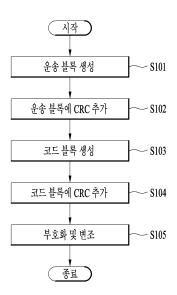

- [0022] 도 1은 일 예시에 따른 부호화 과정을 도시한 순서도이다.

- 도 2는 일 예시에 따른 운송 블록의 부호화 과정을 도시한 도면이다.

- 도 3은 일 예시에 따른 RSC (Recursive Systematic Convolutional) 부호화기를 도시한 도면이다.

- 도 4는 LTE 터보 부호화기(encoder)를 도시한 도면이다.

- 도 5는 RSC 부호화기에 따른 트렐리스(Trellis)의 일 예시를 도시한 도면이다.

- 도 6은 트렐리스 구조의 일 예시를 도시한 도면이다.

- 도 7은 일 예시에 따른 구조화된 패리티 체크 행렬을 도시한 도면이다.

- 도 8은 일 예시에 따른 모델 행렬(model matrix)을 도시한 도면이다.

- 도 9는 쉬프트 수에 따른 행렬의 변환을 설명하기 위한 도면이다.

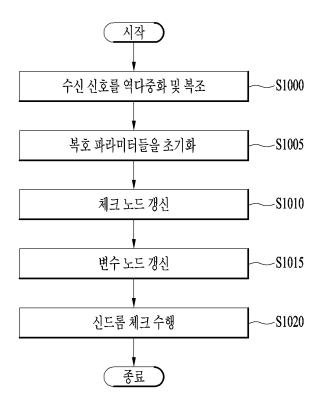

- 도 10은 일 예시에 따른 LDPC 코드 복호화 방법을 도시한 순서도이다.

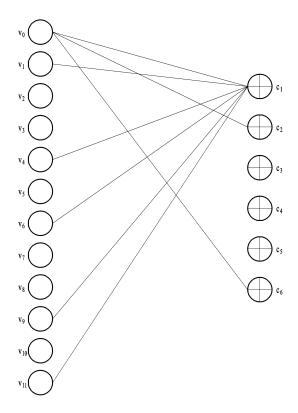

- 도 11은 일 예시에 따른 이분 그래프(bipartite graph)를 도시한 도면이다.

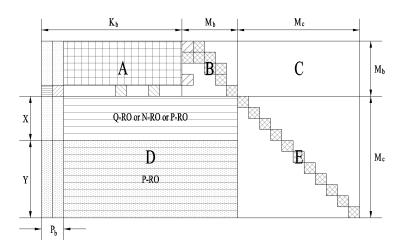

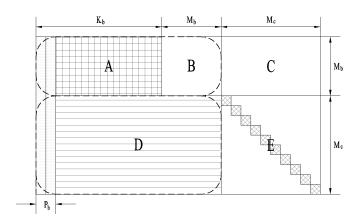

- 도 12는 본 발명의 일 실시예에 따른 LDPC 코드의 구조를 도시한 도면이다.

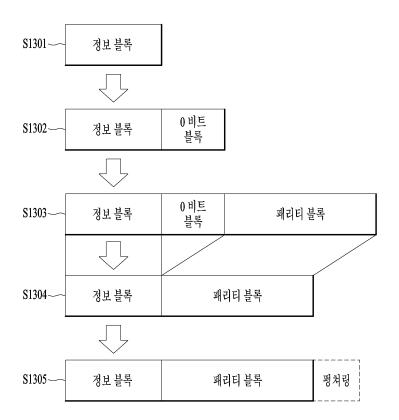

- 도 13은 일 예시에 따른 레이트 매칭 과정을 도시한 도면이다.

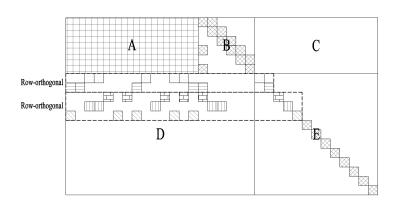

- 도 14는 행-직교(row-orthogonal) 구조를 이용한 LDPC 코드 구조를 설명하기 위한 도면이다.

- 도 15는 본 발명의 몇몇 실시예에 사용 될 수 있는, 부분 행-직교(partial row-orthogonal) LDPC 코드 구조를 설명하기 위한 도면이다.

- 도 16은 본 발명의 일 실시예에 따른 partial row-orthogonal LDPC 코드 구조를 도시한 도면이다.

- 도 17은 본 발명의 일 실시예에 따른 partial row-orthogonal LDPC 코드 구조를 도시한 다른 도면이다.

- 도 18은 본 발명의 다른 일 실시예에 따른 partial row-orthogonal LDPC 코드 구조를 도시한 다른 도면이다.

- 도 19는 본 발명의 일 실시예에 따른 장치를 설명하기 위한 도면이다.

#### 발명을 실시하기 위한 구체적인 내용

[0023] 이하, 본 발명에 따른 바람직한 실시 형태를 첨부된 도면을 참조하여 상세하게 설명한다. 첨부된 도면과 함께

이하에 개시될 상세한 설명은 본 발명의 예시적인 실시형태를 설명하고자 하는 것이며, 본 발명이 실시될 수 있는 유일한 실시형태를 나타내고자 하는 것이 아니다.

- [0024] 이하의 상세한 설명은 본 발명의 완전한 이해를 제공하기 위해서 구체적 세부사항을 포함한다. 그러나, 당업자는 본 발명이 이러한 구체적 세부사항 없이도 실시될 수 있음을 안다. 몇몇 경우, 본 발명의 개념이 모호해지는 것을 피하기 위하여 공지의 구조 및 장치는 생략되거나, 각 구조 및 장치의 핵심기능을 중심으로 한 블록도 형식으로 도시된다.

- [0025] 이하의 기술은 CDMA(code division multiple access), FDMA(frequency division multiple access), TDMA(time division multiple access), OFDMA(orthogonal frequency division multiple access), SC-FDMA(single carrier frequency division multiple access) 등과 같은 다양한 무선 접속 시스템에 사용될 수 있다. CDMA는 UTRA(Universal Terrestrial Radio Access)나 CDMA2000과 같은 무선 기술(radio technology)로 구현될 수 GSM(Global System for Mobile communications)/GPRS(General Service)/EDGE(Enhanced Data Rates for GSM Evolution)와 같은 무선 기술로 구현될 수 있다. OFDMA는 IEEE 802.11(Wi-Fi), IEEE 802.16(WiMAX), IEEE 802-20, E-UTRA(Evolved UTRA) 등과 같은 무선 기술로 구현될 수 있 다. UTRA는 UMTS(Universal Mobile Telecommunications System)의 일부이다. 3GPP(3rd Generation Partnership Project) LTE(long term evolution)는 E-UTRA를 사용하는 E-UMTS(Evolved UMTS)의 일부로서 하향 링크에서 OFDMA를 채용하고 상향링크에서 SC-FDMA를 채용한다. LTE-A(Advanced)는 3GPP LTE의 진화된 버전이다.

- [0026] 설명을 명확하게 하기 위해, 3GPP LTE/LTE-A를 위주로 기술하지만 본 발명의 기술적 사상이 이에 제한되는 것은 아니다. 또한, 이하의 설명에서 사용되는 특정(特定) 용어들은 본 발명의 이해를 돕기 위해서 제공된 것이며, 이러한 특정 용어의 사용은 본 발명의 기술적 사상을 벗어나지 않는 범위에서 다른 형태로 변경될 수 있다.

- [0027] 도 1은 일 예시에 따른 부호화 과정을 도시한 순서도이다.

- [0028] LTE 통신 시스템에서 이용하는 터보 코드를 포함하는 많은 채널 코드들에 도 1과 같은 부호화 과정이 적용될 수 있다. 이하에서는, 설명의 편의를 위하여 LTE 통신 시스템의 표준 문서에 따른 용어에 기초하여 부호화 과정을 설명한다.

- [0029] 도 1의 예시에서, 송신단은 운송 블록(Transport Block, TB)을 생성(S101)할 수 있다. 또한, 송신단은 운송 블록에 운송 블록에 대한 CRC 비트를 추가(S102)된다. 또한, 송신단은 CRC 비트가 추가된 운송 블록으로부터 코드블록을 생성(S103)할 수 있다. 예를 들어, 송신단은 인코더의 입력 크기에 기초하여 운송 블록을 코드 블록으로 분할(segmentation)할 수 있다. 또한, 송신단은 분할된 각각의 코드 블록에 대하여 CRC 비트를 추가(S104)할 수 있다. 이 경우, 예를 들어, 코드 블록 및 코드 블록 CRC 비트의 크기는 6144 비트로 구성될 수도 있다. 송신단은 코드 블록과 CRC 비트로 구성된 블록 각각에 대하여 부호화 및 변조(S105)를 수행할 수 있다. 예를 들어, 상술한 바와 같이, 터보 코딩이 적용될 수도 있다.

- [0030] 복호화 과정은 도 1의 부호화 과정의 역순으로 수행될 수 있다. 예를 들어, 수신단은 각 부호화기에 대응하는 복호화기(decoder)를 이용하여 각 코드 블록 단위로 복호화를 수행하고, 최종적으로 하나의 운송 블록을 구성하여, 운송 블록의 CRC 통과여부를 확인할 수 있다.

- [0031] 예를 들어, 입력 심볼의 크기는 MAC(Media Access Control) 계층으로부터의 운송 블록(transport block, TB)의 크기와는 상이할 수 있다. 운송 블록의 크기가 터보 코드의 최대 입력 심볼 크기보다 큰 경우에는, 운송 블록은 복수의 코드 블록(code block, CB)들로 분할 될 수 있다. LTE 통신 시스템의 표준에 따를 경우, 코드 블록의 크기는 6144 비트에서 CRC (Cyclic Redundancy Check) 비트를 감산한 것과 동일할 수도 있다. 터보 코드의 입력 심볼은 코드 블록과 CRC를 포함하는 데이터 또는 운송 블록 (예를 들어, 운송 블록은 6144 비트 미만) 과 CRC를 포함하는 데이터로 정의될 수도 있다. CRC 비트는 6144 비트에 비하여 매우 작은 값(예를 들어, 최대 24 비트)이다. 따라서, 이하의 설명에 있어서는, 다르게 정의되지 않는 한, 코드 블록은 코드 블록 자체 또는 코드 블록과 대응하는 CRC 비트를 지칭할 수 있으며, 운송 블록은 운송 블록 자체 또는 운송 블록과 대응하는 CRC 비트를 지칭할 수 있다.

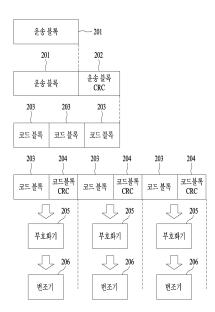

- [0032] 도 2는 일 예시에 따른 운송 블록의 부호화 과정을 도시한 도면이다.

- [0033] 도 2는 도 1과 관련하여 상술한 부호화 과정에 대응하는 운송 블록(201)의 부호화 과정을 도시한다. 먼저, 운송 블록(201)에 운송 블록 CRC(202)가 추가된다. 운송 블록 CRC(202)는 복호 과정에서 운송 블록(201)의 확인을 위하여 이용될 수 있다. 그 후에 운송 블록(201) 및 운송 블록 CRC(202)는 3개의 코드 블록(203)들로 분할 된다.

본 실시예에서는 3 개의 코드 블록(203)들로 분할되었으나, 운송 블록(201)은 부호화기(205)의 입력 크기에 기초하여 복수의 코드블록들로 분할될 수 있다.

- [0034] 코드 블록(203) 각각에는 코드 블록 CRC(204)가 추가된다. 코드 블록 CRC(204)는 수신단에서 코드 블록(203)의 확인을 위하여 이용될 수 있다. 코드 블록(203)과 코드 블록 CRC(204)은 부호화기(205) 및 변조기(206)를 거쳐 부호화될 수 있다.

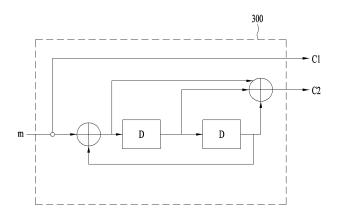

- [0035] 도 3은 일 예시에 따른 RSC (Recursive Systematic Convolutional) 부호화기를 도시한 도면이다.

- [0036] 도 3의 RSC 부호화기(300)는 터보 코딩에 이용될 수 있다. 도 3에서, m은 입력 데이터를 나타내며, C1은 시스테 매틱(systematic) 비트열, C2는 부호화된(coded) 비트열을 나타낸다. 여기서, RSC 부호화기(300)는 1/2 코드율 (code rate)을 갖는다.

- [0037] RSC 부호화기(300)는 비재귀적(nonrecursive)-비-시스테매틱(non-systematic) 콘볼루셔널(convoluational) 부호화기의 입력에 부호화된 출력을 피드백함으로써 구성될 수 있다. 도 3의 실시예에서 부호화기(300)는 2개의 지연기(301, 302)들을 포함한다. 지연기(301, 302)의 값 D는 코딩 방식(coding scheme)에 따라서 결정될 수 있다. 지연기(301, 302)는 메모리 또는 쉬프트 레지스터(shift register)로 구성될 수 있다.

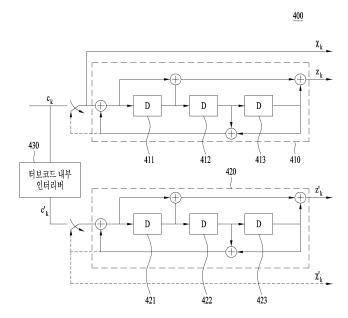

- [0038] 도 4는 LTE 터보 부호화기(encoder)를 도시한 도면이다.

- [0039] LTE 터보 부호화기(400)의 코딩 방식(scheme)은 2개의 8-상태 요소 부호화기(410, 420)들(constituent encoders)과 하나의 터보 코드 내부 인버리버(internal interleaver)(430)를 갖는 병렬 연접 컨벌루션 코드 (Parallel Concatenated Convolutional Code, PCCC)이다.

- [0040] 도 4에서, 터보 부호화기(400)은 제1 요소 부호화기(constituent encoder)(410), 제2 요소 부호화기(420), 및 터보 코드 내부 인터리버(internal interleaver)(430)로 구성된다. 제1 요소 부호화기(410) 및 제2 요소 부호화기(420)는 8-상태(state) 요소 부호화기들이다. 제1 요소 부호화기(410) 및 제2 요소 부호화기(420)는 각각 도 3의 RSC 부호화기와 유사한 구조로 구성된다. 제1 요소 부호화기(410) 및 제2 요소 부호화기(420)는 각각 3 개의 지연기(411, 412, 413, 421, 422, 423)를 포함한다.

- 도 4에서, D는 코딩 방식(coding scheme)에 따라서 결정되는 값이다. ck는 터보 부호화기(400)로의 입력이다. [0041] 제1 요소 부호화기(410) 및 제2 요소 부호화기(420)로부터의 출력은 각각 z<sub>k</sub>와 z'<sub>k</sub>으로 표시된다(denoted). 터 코드 내부 인터리버(430)로부터 출력되는 c'<sub>k</sub>로 표시된다. 일반적으로, 값은 수 있다. 그러나, (411,412,413,421,42,423)는 입력된 값을 1 클록씩 지연시킬 지연기 (411,412,413,421,42,423)는 내부 설정에 따라 1 클록 이상 동안 입력된 값을 지연시키도록 구성될 수 있다. 지 연기(411,412,413,421,42,423)는 쉬프트 레지스터(shift register)로 구성될 수 있으며, 기설정된 클록만큼 입 력된 비트를 지연시킨 뒤 입력된 비트를 다음 지연기(411.412.413.421.42.423)로 출력하도록 구성될 수 있다.

- [0042] 터보 코드 내부 인터리버(430)는 무선 채널로의 신호 송신시 발생할 수 있는 버스트 오류(burst error)의 영향을 감소시킬 수 있다. 예를 들어, 터보 코드 내부 인터리버(430)는 QPP(Quadratic Polynomial Permutation) 인터리버일 수도 있다.

- [0043] 터보 코드는 고성능 순방향 오류 정정 (forward error correction, FEC) 코드로서, LTE 통신 시스템에서 이용되고 있다. 예를 들어, 터보 코드에 의하여 코딩된 데이터 블록은 3개의 서브블록들로 구성될 수도 있다. 하나의 서브블록은 m 비트의 페이로드(payload) 데이터에 대응할 수 있다. 다른 서브블록은, RSC(recursive systematic convolution) 코드를 이용하여 계산된, 페이로드에 대한 n/2 비트의 패리티(parity) 비트들로 구성될 수 있다. 또한, 나머지 서브 블록은 RSC 코드를 이용하여 계산된, 페이로드 데이터의 퍼뮤테이션 (permutation)에 대한 n/2 비트의 패리티 비트들로 구성될 수 있다. 예를 들어, 상술한 퍼뮤테이션은 인터리버 (interleaver)에 의하여 수행될 수 있다. 따라서, 페이로드와 함께 서로 상이한 패리티 비트의 2개의 서브블록들이 하나의 블록으로서 구성될 수 있다. 예를 들어, m이 n/2와 동일한 경우, 하나의 블록은 1/3의 부호율(code rate)을 갖는다.

- [0044] 제1 요소 부호화기(410)에서, 입력  $c_k$ 가 부호화된 비트  $z_k$ 에 도달하는 과정은 두 개의 경로로 구분될 수 있다. 두 개의 경로는 입력단으로부터 출력단으로 출력 피드백 없이 연결된 제1 경로와 입력단으로부터 다시 입력단으로 피드백되는 제2 경로이다.

[0045] 제1 경로에서, 입력  $c_k$ , 지연기(411)을 거친 입력  $c_k$ , 및 지연기들(411, 412, 및 413)을 거친 입력  $c_k$ 가 출력단에 인가된다. 제1 경로에 대한 입력단 출력단 사이의 관계는 다항식으로 표현될 수 있다. 제1 경로에 대한 다항식은 순방향 생성기 다항식(forward generator polynomial)으로 호칭되고, 하기의 수학식의 gl과 같이 표현될수 있다.

### 수학식 1

[0046]

$$g1(D) = 1 + D + D^3$$

[0047] 한편, 제2 경로에서, 입력  $c_k$ , 지연기들(411 및 412)을 거친 입력  $c_k$ , 및 지연기들(411, 412, 및 413)을 거친 입력  $c_k$ 가 입력단에 피드백된다. 제2 경로에 대한 다항식은 재귀적 생성기 다항식(recursive generator polynomial)으로 호칭되고, 하기의 수학식의 g0와 같이 표현될 수 있다.

### 수학식 2

[0048]

$$g0(D) = 1 + D^2 + D^3$$

- [0049] 상기 수학식 1 및 2에서, "+"는 배타적 논리합(exclusive OR, XOR)을 의미하며, 1은 입력이 0번의 지연을 거침을 의미한다. 또한, D<sup>n</sup>은 입력이 n번의 지연을 거침을 의미한다.

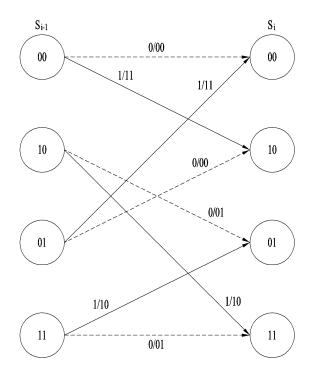

- [0050] 도 5는 RSC 부호화기에 따른 트렐리스(Trellis)의 일 예시를 도시한 도면이다.

- [0051] 도 5는 도 3에 도시된 RSC 부호화기의 트렐리스의 구성을 도시한다. 도 5에서  $S_i$ 는 i번째 입력 데이터의 상태 (state)를 나타낸다. 도 5에서, 각 원은 각 노드를 나타낸다. 아울러, 각 노드들 사이에 이어진 선은 브랜치 (branch)를 의미한다. 실선의 브랜치는 입력값 1에 대한 브랜치를, 점선의 브랜치는 입력값 0에 대한 브랜치를 의미한다. 브랜치 상의 값은 m/C1C2 (입력값/시스테매틱 비트, 부호화된 비트)로 표시된다. 또한, 인코더의 메모리의 개수에 지수적으로 비례하는 상태를 가질 수 있다. 예를 들어, 인코더가 a개의 메모리를 포함하는 경우,  $2^a$ 개의 상태가 트렐리스에 포함될 수 있다.

- [0052] 트렐리스는 2개의 상태 사이에서 가능한 부호기의 상태 전이를 도시하는 상태 기계(state machine)이다. RSC 부호화기와 같은 컨볼루션 부호화기는 트렐리스 다이어그램(diagram)에 따라서 부호화를 수행할 수 있다. RSC 부호화기에 의하여 부호화된 코드워드는 트렐리스 구조에 기반한 알고리즘에 따라서 복호화될 수 있다. 예를 들어, 비터비(Viterbi) 또는 BCJR(Bahl, Cocke, Jelinek and Raviv) 알고리즘이 이용될 수 있다.

- [0053] 도 6은 트렐리스 구조의 일 예시를 도시한 도면이다.

- [0054] 도 6에서, n은 코드워드(codeword)의 길이를 나타낸다. 통상적으로, 추가적인 비트들을 입력 시퀀스 뒤에 추가함으로써, 트렐리스가 종료(terminated)될 수 있다. 일반적으로 0의 시퀀스로 구성된 시퀀스는 테일 비트(tail bit)로 호칭된다. 테일 비트는 트렐리스의 한 상태의 노드들이 0 값을 가지도록 하여 트렐리스를 종료시킨다.

- [0055] 도 6에서, 코드워드의 길이는 입력 데이터의 길이 k 및 테일 비트의 길이 t를 고려하여 결정될 수 있다. 예를 들어, 코드율이 R인 경우, 코드워드의 길이 n은 (k+t)/R의 값을 가질 수 있다. 일반적으로, 테일 비트의 길이 t는 부호화기의 모든 지연기(예를 들어, 메모리)를 리셋할 수 있는 길이로 결정될 수 있다. 예를 들어, 도 3의 RSC 부호화기는 총 2 비트의 테일 비트를 사용할 수 있다. 또한, 도 4와 같은 LTE 통신의 터보 부호화기는 3 비트의 테일 비트를 사용할 수 있다.

- [0056] 테일 비트는 입력 데이터의 길이에 비하여 상대적으로 짧은 길이를 갖는다. 상술한 바와 같이 코드워드의 길이는 테일 비트의 길이와 연관되기 때문에, 코드워드의 길이가 한정된 경우에 테일 비트로 인한 코드율 손실이 발생할 수 있다. 그러나, 테일 비트로 인한 코드율 손실에도 불구하고, 테일 비트를 이용한 트렐리스 종료가 널리이용되고 있다. 계산의 복잡도가 낮고 오류 정정 성능이 우수하기 때문이다.

- [0057] 평처링(puncturing) 코드는 코드워드 중 일부를 평처링하는 방식이다. 평처링 코드에서, 코드워드 중 일부가 평

처링됨으로써 일부 코드워드가 송신되지 않는다. 예를 들어, 테일 비트의 추가로 인한 코드율 손실을 감소시키기 위하여 평처링 코드가 이용될 수 있다. 이 경우, 수신단은 입력 데이터의 길이 k와 테일 비트의 길이 t의 합에 대응하는 트렐리스를 이용하여 복호를 수행할 수 있다. 즉, 수신단은 평처링되지 않은 코드워드를 수신한 것으로 가정하고 복호를 수행할 수 있다. 이 경우, 수신단은 평처링된 비트(즉, 송신단에서 송신되지 않은 비트)에 대응하는 노드로부터의 브랜치에 대하여는 입력값이 없는 것으로 간주할 수 있다. 즉, 해당 노드의 브랜치들에 대하여 입력 데이터는 동일한 확률로 0 또는 1로 가정된다.

- [0058] 도 1과 관련하여 상술한 바와 같이, 코드블록에 대한 CRC가 코드블록에 추가된다. CRC는 송신하려는 데이터를 기설정된 체크값을 제수로 사용하여 나눈 후, 도출되는 나머지로서 결정될 수 있다. CRC는 일반적으로 송신 데이터의 끝에 추가될 수 있다. 수신단은 수신 데이터를 기설정된 체크 값으로 나눈 나머지를 CRC와 비교하거나, CRC를 포함한 전체 수신 데이터에 대하여 체크 값으로 나눈 나머지가 0인지를 판단할 수 있다.

- [0059] 운송 블록의 크기가 6144 비트인 경우, CRC의 크기는 최대 24 비트로 구성될 수 있다. 따라서, CRC 비트를 제외한 나머지 비트가 코드 블록의 크기로 결정된다.

- [0060] 수신단은 복호화를 각 코드블록 단위로 수행할 수 있다. 그 후, 수신단은 코드블록으로부터 운송블록을 구성하고, 운송블록에 대한 CRC를 확인함으로써 복호 성공 여부를 판단할 수 있다. 현재의 LTE 시스템에서, 코드블록 CRC는 빠른 복호화 종료(early decoding termination)를 위하여 이용된다. 예를 들어, 하나의 코드블록에 대한 CRC 체크가 실패하는 경우, 수신단은 나머지 코드블록들을 복호화하지 않고 NACK (Negative ACKnowledgement)을 송신단에 송신할 수 있다.

- [0061] NACK이 수신되는 경우, 송신단은 송신 데이터의 적어도 일부를 재송신할 수 있다. 예를 들어, 송신단은 운송블록 또는 하나 이상의 코드 블록을 재송신할 수도 있다. 예를 들어, 운송블록 전체를 재송신하는 경우, 재송신을 위하여 무선 자원이 과다하게 소모될 수 있다. 또한, 예를 들어, 수신단에서 코드블록 CRC 실패로 인한 NACK이 발생하는 경우, 수신단은 CRC 실패가 발생한 코드블록의 정보(예를 들어, 코드블록의 인덱스)를 송신단에 송신할 수 있다. 또한, 송신단은 코드블록의 정보를 이용하여 CRC 실패가 발생한 코드블록만을 전송하여 무선 자원효율을 증가시킬 수도 있다. 그러나, 코드블록의 개수가 증가되는 경우, 코드블록의 정보(예를 들어, 코드블록의 의 인덱스)를 피드백하기 위한 데이터 양이 증가하게 된다.

- [0062] LTE 통신 시스템에서, 수신단은 ACK/NACK 신호를 이용하여 데이터 수신 성공 여부를 송신단에 알려줄 수 있다. FDD(Frequency Division Duplex)의 경우, i번째 서브프레임에서 수신된 데이터에 대한 ACK/NACK이 i+4번째 서브프레임에서 송신된다. i+4번째 서브프레임에서 NACK이 수신되는 경우, 재전송은 i+8번째 서브프레임에서 수행될 수 있다. 이는, 운송블록을 처리하기 위한 시간과 ACK/NACK 생성을 위한 시간을 고려한 것이다. 운송블록의 처리를 위한 채널 코드 처리가 많은 시간을 소요하기 때문이다. TDD(Time Division Duplex)의 경우, 운송블록의 처리와 ACK/NACK 생성을 위한 시간과 상향링크 서브프레임 할당(예를 들어, TDD 상향링크/하향링크 설정)에 기초하여 ACK/NACK 및 재전송 서브프레임이 결정될 수 있다. 또한, ACK/NACK 번들링(bundling) 및 멀티플랙싱이이용될 수 있다.

- [0063] 상술한 바와 같이, 터보 코드는 일정 SNR을 넘어서면 더 이상의 오류율 개선이 미미하다. 터보 코드의 대안으로 서, LDPC (Low-Density Parity-Check) 코드가 제안되고 있다. LDPC 코드는 선형 블록 코드(linear block cod e)로서, IEEE 802.11n, 802.11ac 및 디지털 비디오 브로드캐스팅(Digital Video Broadcasting, DVB)에서 이용된다. LDPC 코드는 생성 행렬(generation matrix)과 패리티 검사 행렬(parity check matrix)로 구성될 수있다. LDPC 코드에서, 데이터는 메시지 비트들(message bits)과 생성 행렬에 대한 곱 연산을 통하여 부호화될수있다. 일반적으로 LDPC 코드를 이용하는 통신 표준에서는, 생성 행렬 대신에 패리티 검사 행렬이 이용될 수있다. 예를 들어, 패리티 검사 행렬을 이용하여 데이터의 부호화가 수행될 수 있다.

- [0064] 선형 블록 코드는 생성행렬 G 또는 패리티 체크 행렬 H에 기초하여 생성될 수 있다. 선형 블록 코드는 모든 코드워드 c에 대하여, Hc<sup>t</sup>가 0의 값을 갖도록 코드가 구성된다. LDPC 코드 또한, 다른 선형 블록 코드와 동일하게, 패리티 검사 행렬 H와 코드워드 c의 곱이 '0'이 되는지를 확인함으로써 수행될 수 있다. 예를 들어, 코드워드 c의 전치행렬과 패리티 검사 행렬에 대한 곱(즉, Hc<sup>t</sup>)이 0인지를 판단함으로써 LDPC 코드의 복호화가 수행될 수 있다.

- [0065] LDPC 코드에 있어서, 패리티 체크 행렬의 원소는 대부분 0으로 이루어지고, 0이 아닌 원소의 수는 코드의 길이에 비하여 적은 수를 가진다. 따라서, LDPC 부호는 확률에 기초한 반복적 복호가 가능하다. 초기에 제안된 LDPC 부호에서, 패리티 체크 행렬을 비체계적(non-systematic) 형태로 정의되고, 패리티 체크 행렬의 행(row)과 열

(column)에 균일하게 적은 웨이트(weight)가 적용되었다. 웨이트는 행 또는 열에 포함된 1의 개수를 의미할 수 있다.

- [0066] 상술한 바와 같이, LDPC 코드의 패리티 체크 행렬 H 상에 0이 아닌 원소의 밀도가 낮다. 따라서, LDPC 코드는 낮은 복호 복잡도를 가지면서도 섀넌(Shannon)의 이론적 한계에 근접하는 성능을 갖는다. 이러한 LDPC 코드의 높은 오류 정정 성능과 낮은 복호 복잡도로 인하여, LDPC 코드는 고속 무선 통신에 적합한 특성을 갖는다.

- [0067] <u>구조화된(structured) LDPC 코드</u>

- [0068] 상술한 바와 같이, LDPC 코드의 생성을 위하여 패리티 체크 행렬 H가 이용될 수 있다. H 행렬은 많은 0과 적은 수의 1을 포함한다. H 행렬의 크기는  $10^5$  비트 이상의 크기를 가질 수 있으며, H 행렬을 표현하기 위하여 많은 메모리가 소모될 수 있다.

- [0069] 도 7은 일 예시에 따른 구조화된 패리티 체크 행렬을 도시한 도면이다.

- [0070] 구조화된 LDPC 코드에서, H 행렬의 원소들은, 도 7에 도시된 바와 같이, 일정한 크기의 서브 블록(sub-block)들로 표현될 수 있다. 도 7에서, 행렬 H의 각각의 요소들은 하나의 서브블록을 나타낸다.

- [0071] IEEE 802.16e 표준 문서에서는, 서브 블록을 하나의 정수 인덱스(index)로 표시함으로써, H 행렬을 표현하기 위한 메모리의 크기를 감소시킬 수 있다. 각각의 서브 블록은, 예를 들어, 일정한 크기의 퍼뮤테이션 행렬 (permutation matrix)일 수도 있다.

- [0072] 도 8은 일 예시에 따른 모델 행렬(model matrix)을 도시한 도면이다.

- [0073] 예를 들어, IEEE 802.16e 표준 문서를 참조하면, 코드워드의 크기가 2304이고 부호율(code rate)이 2/3인 경우, LDPC 코드 부호화/복호화를 위하여 사용되는 모델 행렬은 도 8과 같다. 모델 행렬은 이하에서 설명되는 적어도 하나의 서브 블록으로 구성된 패리티 검사 행렬을 의미할 수 있다. 또한, 서브 블록은, 이하의 설명에 있어서, 쉬프트 수(shift number)로 지칭될 수 있다. 모델 행렬은 후술하는 방법에 기초하여 패리티 검사 행렬로 확장될 수 있다. 따라서, 특정한 모델 행렬에 기초한 부호화 및 복호화는 해당 모델 행렬의 확장으로부터 생성된 패리티 검사 행렬에 기초한 부호화 및 복호화를 의미한다.

- [0074] 도 8에서, 인덱스 '-1'은 기설정된 크기의 영 행렬(zero matrix)을 나타낸다. 또한, 인덱스 '0'은 기설정된 크기의 단위 행렬(identity matrix)을 나타낸다. '-1' 및 '0'을 제외한 양의 정수의 인덱스는 쉬프트 수를 나타낸다. 예를 들어, '1'의 인덱스로 표현되는 서브 블록은 단위 행렬으로부터 특정한 방향으로 1회 쉬프트된 행렬을 의미할 수 있다.

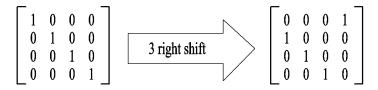

- [0075] 도 9는 쉬프트 수에 따른 행렬의 변환을 설명하기 위한 도면이다.

- [0076] 예를 들어, 도 9는 서브 블록의 크기가 4행 및 4열을 갖는 경우를 도시한다. 도 9에서, 서브 블록은 단위 행렬으로부터 우측으로 3회 쉬프트 된다. 이 경우, 구조화된 LDPC의 코드의 패리티 체크 행렬은 '3'의 정수 인덱스를 이용하여 서브 블록을 표시할 수 있다.

- [0077] 일반적으로, LDPC 코드의 부호화는 패리티 체크 행렬 H로부터 생성 행렬(Generation Matrix) G를 생성하고, 생성 행렬을 이용하여 정보 비트를 부호화함으로써 수행될 수 있다. 생성 행렬 G의 생성을 위하여, 패리티 체크 행렬 H에 대하여 가우스 소거(Gaussian Reduction)를 수행하여 [P<sup>T</sup>: I] 형태의 행렬을 구성한다. 정보 비트의 수가 k이고 부호화된 코드워드의 크기가 n인 경우, 행렬 P는 행의 개수가 k이고 열의 개수가 n-k인 행렬이고, I는 크기가 k인 단위 행렬이다.

- [0078] 패리티 체크 행렬 H가 [P<sup>T</sup> : I] 의 형태를 갖는 경우, 생성 행렬 G는 [I : P<sup>T</sup>]의 형태를 갖는다. 크기 k비트의 정보 비트가 부호화되는 경우, 부호화된 정보 비트는 1행 k열의 행렬 x로 표현될 수 있다. 이 경우, 코드워드 c는 xG이고, xG는 [x : xP]의 형태를 갖는다. 여기서, x는 정보 부분(또는 시스테매틱 부분(systematic part))을 나타내고, xP는 패리티 부분(parity part)을 나타낸다.

- [0079] 또한, 가우스 소거를 이용하지 않고, H 행렬을 특수한 구조로 설계함으로써, 행렬 G를 유도하지 않고 H 행렬로 부터 직접 정보 비트를 부호화할 수도 있다. 상술한 H 행렬과 G 행렬의 구조로부터, 행렬 G와 행렬 H의 전치 행렬의 곱은 0의 값을 갖는다. 이러한 특징과 상술한 정보 비트와 코드워드 사이의 관계를 이용하면, 정보 비트의 뒤에 패리티 비트를 추가함으로써 코드워드가 획득될 수 있다.

- [0080] 도 10은 일 예시에 따른 LDPC 코드 복호화 방법을 도시한 순서도이다.

- [0081] 통신 시스템에서, 부호화된 데이터는 무선 채널을 통과하는 과정에서 잡음을 포함하게 된다. 따라서, 코드워드 c는 수신단에서 잡음을 포함하는 코드워드 c'으로 표현된다. 수신단은 수신신호에 대하여 역다중화 및 복조 (demultiplexing and demodulation)를 수행(S1000)하고, 복호 파라미터들을 초기화(S1005)한다. 수신단은 체크 노드(check node)와 변수 노드(variable)를 갱신(S1010, S1015)하고, 신드롬 체크를 수행(S1020)한다. 즉, c'H<sup>T</sup>가 0인지를 확인함으로써, 복호화 절차가 종료될 수 있다. c'H<sup>T</sup>가 0인 경우, c'에서 처음 k개의 비트가 정보 비트x로 결정될 수 있다. 만약 c'H<sup>T</sup>가 0이 아닌 경우, 합곱(sum-product) 알고리즘 등의 복호화 기법에 기초하여 c'H<sup>T</sup>가 0을 만족하는 c'을 찾음으로써 정보 비트x가 복구될 수 있다.

- [0082] 도 11은 일 예시에 따른 이분 그래프(bipartite graph)를 도시한 도면이다.

- [0083] 도 11에서, 좌측의 노드들(v<sub>0</sub>, v<sub>1</sub>, …, v<sub>11</sub>)은 변수 노드(variable node)들을 나타내며, 우측의 노드들(c<sub>1</sub>, c<sub>2</sub>, …, c<sub>6</sub>)은 체크 노드들을 나타낸다. 도 11의 예시에서, 설명을 위하여 변수 노드 v<sub>0</sub>와 체크 노드 c<sub>1</sub>을 중심으로 이진 그래프가 도시되었다. 도 11의 이진 그래프의 연결선은 에지(edge)로 호칭될 수 있다. 도 11의 이진 그래프는 Hc<sup>t</sup>로부터 생성될 수 있다. 따라서, 도 11에서, 변수 노드 v<sub>0</sub>로부터의 에지는 패리티 체크 행렬 H의 1열에 대응하고, 체크 노드 c<sub>1</sub>으로부터의 에지는 행렬 H의 1행에 대응한다.

- [0084] 상술한 바와 같이, 복호가 성공되기 위하여는, 패리티 체크 행렬H와 코드워드 행렬c의 전치행렬의 곱이 '0'값을 가져야 한다. 따라서, 하나의 체크 노드에 연결된 변수 노드들의 값이 0이어야 한다. 따라서, 도 11의 경우, 체크 노드 c<sub>1</sub>에 연결된 변수 노드들(v<sub>0</sub>, v<sub>1</sub>, v<sub>4</sub>, v<sub>6</sub>, v<sub>9</sub>, v<sub>11</sub>)의 값의 배타적 논리합(exclusive OR, XOR)의 값이 '0'이어야 한다. 신드롬 체크(syndrome check)는, 각 체크 노드에 연결된 변수 노드들의 값이 배타적 논리합의 값이 0인지를 확인하는 것을 의미한다.

### [0085] QC (Quasi-Cyclic) LDPC 코드

- [0086] 이하에서, QC (Quasi-Cyclic) LDPC 코드에 대하여 설명한다.

- [0087] LDPC 코드의 우수한 성능을 획득하기 위하여, 패리티 체크 행렬(또는 생성 행렬)이 임의적으로 구성될 수 있다. 또한, LDPC 코드의 성능은 블록의 길이가 증가함에 따라서 향상될 수 있다. 또한, 복호에 있어서, 최적 (optimal) 복호 방법을 통하여 LDPC 코드의 성능이 향상될 수 있다. 그러나, 최적 복호의 복호 복잡성으로 인하여, LDPC 코드의 복호를 위하여 신뢰 전파(belief propagation) 알고리즘이 이용된다. 또한, 임의적으로 생성된 LDPC 코드의 패리티 체크 행렬은 우수한 성능을 가지나, 그 구현과 표현이 매우 복잡하다. 따라서, 상술한 바와 같은 구조화된 LDPC 코드가 널리 사용된다. 이러한 구조화된 LDPC 코드로서, QC LDPC 코드가 널리 사용된다.

- [0088] QC-LDPC 코드는 Q×Q 크기를 갖는 0행렬과 Q×Q 크기를 갖는 순환순열 행렬(Circulant Permutation Matrix, CPM)으로 구성된다. 순환순열행렬은P³는 Q×Q 크기의 단위 행렬(identity matrix)을 순환이동 값 a만큼 순환 이동시킨 형태(도 9 참조)를 갖는다. 예를 들어, 도 7에 도시된 바와 같이, 패리티 체크 행렬(H)은 (mb+1)× (nb+1) 개의 순환순열행렬들로 구성될 수 있다. 상술한 바와 같이, 순환이동 값 0은 단위 행렬을, -1은 0행렬을 나타낸다. 또한, 패리티 체크 행렬은, 도 8에 도시된 바와 같이, 순환이동 값들의 행렬로 표현될 수도 있다. 여기서 각각의 순환 이동의 값은 -1 이상 Q-1 이하의 값을 갖도록 설정될 수 있다. 도 8과 같이 순환이동의 값으로 구성된 행렬은 순환이동 행렬 또는 특성 행렬(characteristic matrix)으로 호칭될 수 있다.

- [0089] 도 12는 본 발명의 일 실시예에 따른 LDPC 코드의 구조를 도시한 도면이다.

- [0090] 이하의 실시예에 있어서, 다-에지(multi-edge) QC LDPC 코드가 이용될 수 있다. 예를 들어, 도 12에 도시된 바와 같이, 다-에지 QC LDPC 코드는 QC-IRS(Irregular Repeat Accumulation)와 유사한 고율 코드(high rate code)와 단일 패리티 체크 코드가 연접된 구조를 가질 수 있다. 예를 들어, 다-에지 QC-LDPC 코드의 패리티 체크 행렬(H)은 하기와 같은 형태로 정의될 수 있다.

### 수학식 3

$[0091] \qquad H = \begin{bmatrix} A & B & C \\ D & E \end{bmatrix}$

- [0092] 위 수식에서, A 와 B(Mb \* (Kb+Mb))는 QC-IRA와 유사한 구조를 갖는 고율 코드를 나타내며. C (Mb \* Mc)는 0 행렬을 나타낸다. 또한, D(Mc \*(Kb+Mb) 와 E (Mc \* Mc)는 단일(single) 패리티 체크 코드의 정보와 패리티를 각각 나타낸다. 이 때 E는 단일 대각선(single-diagonal) 구조로 결정 될 수 있다.

- [0093] 도 12에서 Kb 는 인코딩 되는 정보(information)의 크기를 나타낸다. 또한, Mb은 고율 코드 부분의 패리티를, Mc는 단일 패러티 체크 코드 부분의 패리티 크기를 각각 나타낸다. Pb는 LDPC 코드에 적용되는 평쳐링의 크기를 나타낸다.

- [0094] 이때 Pb의 크기는 LDPC 디코더가 수행 가능한 최대 반복 회수(iteration)을 고려해서 결정 될 수 있다. 본 발명의 몇몇 실시예에서 디코더의 최대 반복 회수는 50일 수 있으며, 이에 따른 P의 크기는 2Z 일 수 있다. 하지만 본 발명이 이러한 구성에 한정되는 것은 아니다. 또한, 도 12 상에서 고율 코드 부분(A)의 패리티 구조는 인코딩 방식을 고려하여 이중 대각선(dual-diagonal) 구조로 결정 될 수 있다.

- [0095] 원하는 크기의 QC LDPC 코드의 구성을 위하여, 리프팅(lifting) 동작이 수행될 수 있다. 리프팅은 기설정된 패리티 체크 행렬으로부터 원하는 크기의 패리티 체크 행렬을 획득하기 위하여 이용된다. 리프팅 크기를 변경함으로써 다양한 코드 길이가 지원될 수 있다. 예를 들어, 플로어(floor) 리프팅 또는 모듈로(modulo) 리프팅이 이용될 수 있다. 예를 들어, 모듈로 리프팅에 따른 패리티 체크 행렬은 하기의 수식과 같이 획득될 수 있다.

## 수학식 4

[0096]

$$H_{Q} = \begin{cases} a_{ij}MOD\ Q & if\ a_{ij} \neq -1\\ -1 & if\ a_{ij} = -1 \end{cases}$$

- [0097] 위 수학식에서, Q는 리프팅 크기를 나타낸다. 또한, a<sub>ij</sub>는 기설정된 패리티 체크 행렬의 i행 j열의 쉬프트 값을 나타낸다 (도 8 참조). 또한, MOD Q는 Q값에 기초한 모듈로 연산을 나타낸다. 즉, 기설정된 패리티 체크 행렬의 순환 이동 행렬에서, 0행렬에 대응하는 값들은 유지되고, 나머지 순환 이동 값들에 대하여는 리프팅 크기 Q에 기초한 모듈로 연산이 수행된다. 따라서, 순환 이동 행렬의 쉬프트 값이 -1 이상 Q-1이하의 값들로 변환된다.

- [0098] 도 13은 일 예시에 따른 레이트 매칭 과정을 도시한 도면이다.

- [0099] 실질적으로 송신될 수 있는 데이터 비트의 길이는 이용가능한 물리 자원의 크기에 기초하여 결정될 수 있다. 따라서, 레이트 매칭을 통하여 이용가능한 물리 자원의 크기에 대응하는 부호율(code rate)을 갖는 코드워드가 생성될 수 있다. 예를 들어, 레이트 매칭을 위하여 쇼트닝(shortening) 기법 또는 평처링(puncturing) 기법이 이용될 수 있다. 쇼트닝 기법은, 예를 들어, 코드워드의 정보 부분의 일부를 제거함으로써 수행될 수 있다. 정보비트의 일부가 줄어들기 때문에, 쇼트닝 기법에 의하여 부호율이 감소될 수 있다. 평처링 기법은, 예를 들어, 코드워드의 패리티의 적어도 일부를 평처링함으로써 수행될 수 있다. 평처링의 경우, 정보 비트의 비율이 증가하기 때문에 부호율이 증가될 수 있다. 따라서, 이론적으로, 쇼트닝과 평처링의 조합을 통하여 임의의 부호율에 대응하는 코드워드가 생성될 수 있다.

- [0100] 쇼트닝 및 평처링의 성능은 쇼트닝 또는 평처링되는 비트의 순서에 따라 결정될 수도 있다. 그러나, QC LDPC 코드의 경우, Q×Q 단위 블록 내에서의 비트 평처링의 순서는 성능에 영향을 주지 않는다. 따라서, 패리티 블록에 대한 리프팅 사이즈(Q) 단위의 인터리빙이 수행된 후, 평처링은 패리티 비트의 마지막 부분으로부터 수행될 수 있다. 또한, 쇼트닝은 정보 비트의 마지막 부분으로부터 수행될 수 있다.

- [0101] 한편, 부호화된 LDPC 코드의 길이보다 물리 자원의 크기가 큰 경우, 반복기법을 통하여 레이트 매칭이 수행될 수 있다.

- [0102] 도 13을 참조하여, 먼저, 송신하고자 하는 정보 비트를 포함하는 정보 블록이 생성(S1301)된다. 코드 블록의 크기가 LDPC 정보부분의 길이보다 작은 경우, 부호화 전에 0 비트 정보가 정보 블록의 뒤에 추가될 수 있다. 도

13의 예시에서, 추후의 쇼트닝을 위하여, 정보 블록의 뒤에 0 비트 블록이 삽입(S1302)된다. 그 후, 정보 블록 과 0 비트 블록에 대하여 LDPC 코드에 기초한 부호화를 수행함으로써 패리티 블록을 포함하는 코드워드가 생성(S1303)될 수 있다. 단계 S1303에서, 정보 블록과 0 비트 블록은 LDPC 코드의 정보 부분에 대응하고, 패리티 블록은 LDPC 코드의 패리티 부분에 대응할 수 있다.

- [0103] 상술한 바와 같이, 레이트 매칭을 위하여 쇼트닝 기법이 적용될 수 있다. 이 경우, 기삽입된 0 비트 블록이 제 거(S1304)될 수 있다. 또한, 후술하는 평쳐링을 위하여, 패리티 블록에 대하여 리프팅 사이즈 단위의 인터리빙 (또는 퍼뮤테이션(permutation))이 수행될 수 있다. 또한, 레이트 매칭을 위하여, 패리티 블록의 마지막 부분이 평처링될 수 있다 (S1305).

- [0104] 5G 무선랜 시스템은 최대 20Gbps부터 최소 수 십 bps까지의 전송율을 제공한다(LTE의 경우 40 bps까지 지원한다). 이처럼 5G 무선랜 시스템이 지원하는 전송 환경은 다양하다고 할 수 있다. 이처럼 다양한 환경에 대해 정보를 효율적으로 인코딩하기 위해서는 인코딩에 사용되는 LDPC 코드가 다양한 부호율을 지원해야 하나, 종대와 같이 하나의 LDPC 코드를 이용하여 정보를 인코딩하는 하는 경우, 다양한 통신 환경에 대한 대응이라는 측면에서 비효율적이라는 문제가 존재 한다.

- [0105] 본 발명에서는 이러한 다양한 통신 환경에 대한 효과적인 인코딩을 제공하기 위해, LDPC 코드가 여러 개 (multiple)의 베이스 코드(Base code)를 사용하는 것을 제안한다.

- [0106] 본 발명에서 제안되는 몇몇 베이스 코드는 큰 전송 블록(large block)과 많은 양의 스루풋(throughput)에 유리한 베이스 코드이거나, 작은 전송 블록(small block), 짧은 지연 시간(latency)에 유리한 베이스 코드일 수 있다

- [0107] LDPC 코드는 터보 코드와 달리 부호율이 낮아질수록 처리 해야 하는 H 매트릭스의 행(row)이 증가한다는 문제가 있다. 예를 들어 LDPC 코드의 부호율이 8/9인 경우, 인코더가 처리 해야 하는 행의 개수가 6개라 한다면, 동일한 조건하에 부호율이 2/3으로 감소하는 경우에는, 인코더가 처리해야 하는 행이 18개로 증가하게 된다. 처리해야 하는 행의 개수가 3배 증가함에 따라, 지연 시간 역시 3배 증가하게 된다.

- [0108] 본원 발명에서는 이러한 문제점을 극복하기 위해, 작은 전송 블록의 인코딩을 위한 별도의 짧은 코드(short code)를 도입하는 것을 제안한다. 이러한 다중 베이스 코드를 도입함에 따라, 디코딩 지연 시간과 전력 소모 측면에서 이점을 얻을 수 있다.

- [0109] 기지국과 단말 간에 전송되는 데이터 패킷은, 상기 데이터 패킷이 상향링크 또는 하향링크 중 어느 것을 통해 전송되는지에 따라 다른 특징을 가진다. 하향링크 전송의 경우, 상향링크 전송에 비해 상대적으로 높은 부호율을 가지기 때문에 큰 크기의 전송 블록이 대부분의 트래픽을 차지한다. 반면, 상향링크 전송의 경우, 상대적으로 작은 크기의 전송 블록이 대부분의 트래픽을 차지한다.

- [0110] 이러한 특징을 고려하여, 송신단의 인코더가 각각의 통신환경에 부합하는 LDPC 코드를 사용하여 정보를 인코딩 하는 경우 지연 시간을 효과적으로 줄일 수 있다.

- [0111] 본원발명에서는 송신단의 인코더가 부분 행-직교(partial row-orthogonal) 구조를 이용하여, LDPC 코드를 생성하는 방법에 대해서 제안한다. 여기서 부분 partial row-orthogonal LDPC 구조라 함은, LDPC 코드를 구성하는 서로 다른 레이어 중 일부 레이어의 구성 만이 row-orthogonal 구조를 가지는 LDPC 구조를 의미할 수 있다. 이하에서, 본원 발명이 제안하는 row orthogonal 구조 및 partial row-orthogonal 구조에 대해서 자세히 설명한다.

- [0112] 행-직교(Row-orthogonal) 구조를 이용한 LDPC 코드 구조

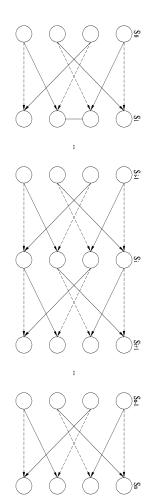

- [0113] 도 14은 행-직교(row-orthogonal) 구조를 이용한 LDPC 코드 구조를 설명하기 위한 도면이다.

- [0114] Row-orthogonal 구조는 도 14에 도시되어 있는 것과 같이 LDPC의 패리티 체크 행렬(D)을 구성하는 레이어 (layer) 내의 엣지(edge)들이 연속하는 행에 대해, 위 아래로 서로 겹치지 않도록 설계되는 구조 일 수 있다. 여기서 레이어란 하나 또는 여려 개의 행(row)들의 집합을 의미 할 수 있다.

- [0115] 도 14에 개시되어 있는 예시를 통해 row-orthogonal 구조에 대해서 보다 자세히 설명한다. 도 14에 도시되어 있는 점선 영역 중 상단에 위치한 제 1 레이어의 경우, 2개의 행이 하나의 레이어를 구성하도록 설정되어 있으며, 하단에 위치한 제 2 레이어는 3개의 행이 하나의 레이어를 구성하도록 설정되어 있다.

- [0116] 이때 제 1 레이어 및 제 2 레이어를 구성하는 각각의 엣지들은 연속하는 행 사이에서 위 아래로 엣지가 겹치지

않게 설정되어 있으므로, 상기 제 1 레이어와 상기 제 2 레이어는 모두 row-orthogonal 구조를 가진다고 정의할 수 있다.

- [0117] 하지만 이와 같은 구조는 상기 제 1 레이어와 상기 제 2 리에어 간의 메모리 충돌이 발생할 수 있으므로, 지연시간을 줄이는데 효과적이지 않은 문제가 있다. 또한 row-orthogonal 구조는 앞서 설명한 것과 같이, 연속하는 행에 대해 엣지가 겹쳐지지 않도록(동일한 열 값을 가지지 않도록), 행렬 내에서 엣지의 위치가 제한되므로, 전체 시스템의 성능 열화가 발생한다는 문제점이 발생 한다.

- [0118] 이하, 상기와 같은 문제점을 해결하기 위해 제안 되는, 본 발명의 일 실시예에 따른 LDPC 코드 구조를 설명한다. 구체적으로, 단일 패리티 채크 행렬 중 일부의 레이어 만을 row-orthogonal 구조로 설정하는 partial row-orthogonal 구조를 이용하여 LDPC 코드를 생성하는 방법에 대해서 설명한다.

- [0119] <u>부분 행-직교(partial Row-orthogonal) 구조를 이용한 LDPC 코드 구조</u>

- [0120] 도 15는 본 발명의 몇몇 실시예에 사용 될 수 있는, 부분 행-직교(partial row-orthogonal) LDPC 코드 구조를 설명하기 위한 도면이다. Partial row-orthogonal 구조는 다음과 같은 LDPC 코드의 특징을 이용하여 설계 될 수 있다.

- [0121] LDPC 코드의 디코딩 지연 시간은 부호율이 낮아 질수록, 처리 해야 하는 행의 수가 증가하기 때문에, 낮은 부호율에서 적용되는 경우 큰 지연 시간 이득(gain)을 얻을 수 있다.

- [0122] 또한, 도 15에 개시되어 있는 패리티 채크 행렬 D는 부호율이 낮아질수록 엣지의 위치를 위한 여유 공간(spare space)가 증가하므로, 앞서 설명한 성능 열화 없이 row-orthogonal한 엣지 배치 구조를 설계 할 수 있다.

- [0123] 앞서 설명한 레이어 간의 메모리 충돌을 최소화 하기 위해, 서로 다른 레이어의 경계에서 엣지가 겹쳐지지 않도록 설계된다.

- [0124] 이러한 점을 고려하여, partial row-orthogonal 구조는 D 행렬의 모든 레이어가 row-orthogonal하게 설계되는 것이 아니라, D 행렬 중 높은 부호율을 가지는 부분은 서로 다른 행 간에 존재하는 엣지가 겹쳐지도록, 즉 row-orthogonal 구조가 이루어지지 않도록 설계될 수 있다. 또한 D 행렬 중 낮은 부호율을 가지는 부분은 서로 다른 행 간에 존재하는 엣지가 겹쳐지지 않도록, 즉 row-orthogonal 구조가 이루어지도록 설계될 수 있다.

- [0125] 위와 같이 패리티 채크 행렬 내의 구성을 분할하여, LDPC 코드의 부호율이 낮은 일부 부분에 대해서만 row-orthogonal 구조를 사용하는 경우, 엣지 선택 및 메모리 충돌에 따라 발생하는 row-orthogonal의 성능 열화를 줄임 수 있다. 즉, 높은 부호율을 가지는 일부 부분에 대해서는 엣지 선택의 폭을 높여 지연 시간 열화를 상쇄할 수 수 있는 효과가 있다.

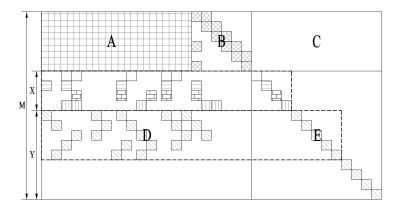

- [0126] 도 15에 도시되는 X는, 패리티 채크 행렬 D 내 상위 X 개의 행 만큼의 공간에서는 연속되는 행간 엣지가 겹치는 구간 (동일한 열 값을 가지는)이 존재함을 의미한다. 즉, 패리티 채크 행령 D 내의 상위 X 개의 행 만큼의 공간에서는 row-orthogonal 구조가 이루어지지 않음을 의미한다.

- [0127] D 행렬 내에 X개의 행으로 이루어지는 공간에서는, 행간 위치하는 엣지가 서로 겹쳐, 신호의 fully pipe-line이 이루어질 수 없으므로, 디코딩시 지연 시간이 증가 될 수 있으나, Y개의 행으로 구성되는 하위 공간에서는 행간 위치하는 엣지가 서로 겹치지 않으므로 fully pipe-line이 가능하며, 이로 인해 디코딩 지연 시간이 줄어들게된다. 즉, 지연 시간 이득(gain)을 얻을 수 있다.

- [0128] 이러한 성능과 지연 시간을 조율하는 row-orthogonal 구조로서 quasi row-orthogonal 구조가 활용 될 수 있다. 이는 평쳐링 부분에서만 엣지가 겹쳐지고 나머지 영역에서는 엣지가 겹쳐지지 않는 row-orthogonal 구조를 의미한다. Quasi row-orthogonal 구조의 디코딩을 위해서는 시스템은 기존의 레이어 디코딩 방법 외에 추가적인 로직을 필요로 할 수 있다.

- [0129] 이하 상술한 X 및 Y 값을 결정하는 방법에 대해서 설명한다.

- [0130] 아래의 표 1은 본 발명의 일 실시예로서 사용될 수 있는 베이스 그래프(base graph)의 파리미터들을 도시하며, 상기 베이스 그래프를 구성하는 제 1 베이스 코드와 제 2 베이스 코드의 몇몇 파라미터를 제안한다. 다만 본 발 명의 특징이 상기 표가 제안하는 파라미터에 의해 제한되는 것은 아니다.

#### [0131] [ 표 1]

| Base<br>code | Size<br>M <sub>b</sub> xN <sub>b</sub> | Code<br>Rate | Pb | Max<br>information | Kb,max/<br>Kb,min | Lifting Values<br>(Z)               |  |  |

|--------------|----------------------------------------|--------------|----|--------------------|-------------------|-------------------------------------|--|--|

| BC1          | 6x38                                   | 0.89         | 2  | 8192               | 32 / 24           | 256, 192, 144,<br>108, 82           |  |  |

| BC2          | 6x16                                   | 0.71         | 2  | 2040               | 10 / 6            | 204, 128, 88, 56, 36, 24, 16, 10, 6 |  |  |

[0132]

- [0133] 상기 표에서 Mb는 각각의 베이스 코드의 패리티(parity) 크기를, Nb는 각각의 베이스 코드의 코드워드의 크기를 나타낸다. 또한, Pb는 각각의 베이스 코드의 평처링 크기를 나타낸다. Kb,max는 각각의 베이스 코드의 열 (column)의 수 중 최대값, Kb,min은 각각의 베이스 코드의 열(column)의 수 중 최소 값을 각각 나타 낸다.

- [0134] 첫 번째로, 전체 베이스 코드의 양(전체 행의 개수)을 고려한 비율을 통해 상기 X 및 Y를 결정 할 수 있다.

- [0135] 예를 들어, 표 1과 같은 베이스 그래프를 가지며, 제 1 베이스 코드의 최저 부호율이 1/3이라 가정하면, Row의 개수는 66개로 설정될 수 있다. 이때 전체 행의 1/3부터 row-orthogonal 구조를 통해 패리티 비트 행렬이 생성된다고 가정하면, X=66/(1/3)=22로 결정될 수 있고, Y = 66-22 = 44로 결정 될 수 있다.

- [0136] 두 번째로, row-orthogonal 구조가 요구되는 부호율을 사전에 결정하고, 해당 부호율에 대응하는 패리티 채크 행렬의 행부터 row-orthogonal 구조가 적용 되도록 설정 할 수 있다.

- [0137] 예를 들어, 위와 같은 예시에서, 부호율 2/3의 행렬부터 row-orthogonal 구조를 적용하고자 한다면, X = 32/(2/3) (32-2) =18로 결정될 수 있고, Y=66-18 =48로 결정 될 수 있다. 이때 2Z의 평쳐링이 고려되었다.

- [0138] 셋째로, 베이스 코드의 크기가 작은 경우, row-orthogonal 구조를 가지는 패리티 체크 행렬의 X 및 Y를 구하는 방법에 대해서 설명한다.

- [0139] 예를 들어, 상기 표 1과 같은 베이스 그래프를 가지며, 제 2 베이스 코드가 사용되는 상황을 고려 할 수 있다. 베이스 코드의 크기가 작더라도, LDPC 코드가 매우 낮은 부호율을 지원한다면, 패리티 체크 행렬을 구성하는 행의 수가 크기 때문에, 이 경우 디코딩 지연 시간을 줄이기 위해, 패리티 채크 행렬은 일부 부분에 대한 row-orthogonal 구조를 가질 수 있다. 이 경우 row-orthogonal이 시작되는 부호율이 큰 베이스 코드(위의 제 1 베이스 코드의 예시) 보다 낮다.

- [0140] 위와 같은 예시에서 제 2 베이스 코드의 최소 부호율을 1/5라 가정하는 경우, 총 row의 개수는 10/(1/5) = 50으로 결정 될 수 있다. 여기서 약 1/2 부호율부터 row-orthogonal 구조를 적용한다고 하는 경우, X는 X=10/(1/2) -(10 2) = 18로 결정 될 수 있고, Y = 50-18 = 32로 결정 될 수 있다.

- [0141] 최근 3GPP 표준에서는 Partial row-orthogonal 구조의 LDPC 코드 구조에 대한 제안들이 제시되고 있다. 이하에 서는 상기 제안들에 따른 본 발명의 몇몇 실시예에 대해서 설명한다.

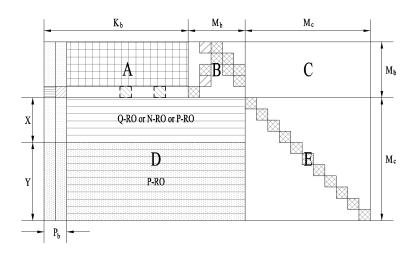

- [0142] 도 16는 본 발명의 일 실시예에 따른 partial row-orthogonal LDPC 코드 구조를 도시한 도면이며, 도 17는 본 발명의 일 실시예에 따른 partial row-orthogonal LDPC 코드 구조를 도시한 다른 도면이다.

- [0143] 이하에서는 도 16 및 도 17에 개시되어 있는 본 발명의 일 실시예가 제시하는 LDPC 코드 구조에 대해서 설명한다.

- [0144] 성능적인 측면에서 본 발명의 일 실시예가 제시하는 LDPC 코드 구조는 다음과 같이 제안될 수 있다. 제시되는 LDPC 코드 구조는 0.89~0.93의 부호율 성능을 확보하기 위한 구조로 제안 될 수 있다. 이 때 부호율 0.89를 만족하기 위해 행렬 A와 행렬 B는 5\*27(2열의 평쳐링 포함)로 구성되는 것이 바람직하며, 상기 5\*27의 행렬에서 이중 대각선 구조를 가지는 패리티 행렬은 4\*4로 결정되는 것이 바람직하다. 또한 상기 5\*27 행렬에는 Degree -1 variable node가 패리티에 포함될 수 있다. 또한 상기 Degree-1 variable node의 채크 노드에는(행렬 A 및 행렬 B의 마지막 행) 2열의 평쳐링이 인접하여 구성될 수 있다.

- [0145] 또한, 상기 일 실시예가 제시하는 LDPC 코드 구조의 행렬 D와 관련하여, 임의의 X 행 까지는 Quasi row-orthogonal, 비(non) row-orthogonal 및 순(pure) row-orthogonal 구조가 설정 될 수 있다. 여기서 non row-orthogonal 구조는 특정 영역의 전체 영역이 row-othogonal이 아닌 영역으로 설정됨을 의미하며, pure row-orthogonal은 특정 영역의 전체 영역이 모두 row-orthogonal 구조로 설정 됨을 의미한다. 이때 나머지 Y 행 영역은 pure row-orthogonal 구조로 설정될 수 있다.

- [0146] 복잡도(complexity) 측면에서 상기 본 발명의 일 실시예가 제시하는 구조는 다음과 같이 제안 될 수 있다. LDPC 코드 구조가 포함하는 총 엣지의 수는 300에서 310개 정도로 제한 될 수 있다. 보다 구체적으로, LDPC 코드 구조가 1/3의 부호율을 지원하기 위해, 상기 LDPC 코드 구조가 포함하는 초 엣지의 수는 300~310개 정도로 제한 될 수 있다. 이 경우, 낮은 부호율에서의 트루풋(throughput)을 확보하기 위해, Y행 영역에 대해서는 pure roworthogonal 구조가 활용되는 것이 바람직하다. 경우에 따라 X 또는 Y 중 어느 하나는 0의 값을 가질 수도 있다.

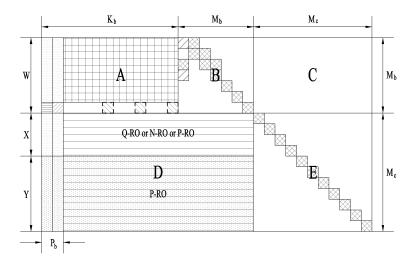

- [0147] 도 18는 본 발명의 다른 일 실시예에 따른 partial row-orthogonal LDPC 코드 구조를 도시한 다른 도면이다.

- [0148] 이하에서는 도 18에 개시되어 있는 본 발명의 다른 일 실시예가 제시하는 LDPC 코드 구조에 대해서 설명한다.

- [0149] 성능적인 측면에서 본 발명의 다른 실시예가 제시하는 LDPC 코드 구조는 다음과 같이 제안될 수 있다. 제시되는 LDPC 코드 구조는 0.67(=2/3)의 부호율 성능을 확보하기 위한 구조로 제안 될 수 있다. 이 때 부호율 0.89를 만족하기 위해 행렬 A와 행렬 B는 7\*17(2열의 평쳐링 포함)로 구성되는 것이 바람직하며, 상기 5\*27의 행렬에서 이중 대각선 구조를 가지는 패리티 행렬은 4\*4로 결정되는 것이 바람직하다. 또한 상기 7\*17 행렬에는 Degree -1 variable node가 패리티에 포함될 수 있다. 이때 상기 Degree-1 node의 개수가 많으면 낙수(water fall) 영역 성능에 우수하나, 오류 마루(error floor) 성능은 감소 할 수 있다. 본 발명의 다른 실시예에 따르면 Degree-1 node의 개수는 3개로 제안 될 수 있으며, 행렬 B를 구성하는 오른쪽 하단의 3개의 노드가 degree 1 node로 설정 될 수 있다. 또한 상기 Degree-1 variable node의 채크 노드에는(행렬 A 및 행렬 B의 마지막 행) 2열의 평처링이 인접하여 구성될 수 있다.

- [0150] 또한, 상기 다른 실시예가 제시하는 LDPC 코드 구조의 행렬 D와 관련하여, 임의의 X 행 까지는 Quasi row-orthogonal, non-row-orthogonal 및 pure row-orthogonal 구조가 설정 될 수 있다. 여기서 non-row-orthogonal 구조는 특정 영역의 전체 영역이 row-othogonal이 아닌 영역으로 설정됨을 의미하며, pure row-orthogonal은 특정 영역의 전체 영역이 모두 row-orthogonal 구조로 설정 됨을 의미한다. 이때 나머지 Y 행 영역은 pure row-orthogonal 구조로 설정될 수 있다. 경우에 따라 X 또는 Y 중 어느 하나는 0의 값을 가질 수도 있다.

- [0151] 복잡도(complexity) 측면에서 상기 본 발명의 다른 실시예가 제시하는 구조는 다음과 같이 제안 될 수 있다. LDPC 코드 구조가 포함하는 총 엣지의 수는 190에서 195개 정도로 제한 될 수 있다. 보다 구체적으로, LDPC 코드 구조가 1/5의 부호율을 지원하기 위해, 상기 LDPC 코드 구조가 포함하는 초 엣지의 수는 190~195개 정도로 제한 될 수 있다. 이 경우, 낮은 부호율에서의 트루풋(throughput)을 확보하기 위해, Y행 영역에 대해서는 pure row-orthogonal 구조가 활용되는 것이 바람직하다. 경우에 따라 X 또는 Y 중 어느 하나는 0의 값을 가질 수도 있다.

- [0152] 앞서 설명한 실시예에 따라, 부호율 별로 상기 X 및 Y를 설정하는 경우, 도 18에 개시되는 파라미터 및 부호율 기준은 다음의 표 2와 같이 설정 될 수 있다.

High rate: ~2/3, W=7

Middle rate : ~1/3, X=22

Low rate : ~ 1/5, Y=20

[0154]

[0155] 또한, 도 18에 의해 개시되는 본 발명의 다른 실시예에 따른 LDPC 코드 구조는 아래의 표 3에 따른 파리미터에 따라 제안 될 수 있다.

|        | Kb | Mb | Mc | Pb | ₩ | Х    | Y    | Х+У |

|--------|----|----|----|----|---|------|------|-----|

| [0157] | 10 | 7  | 42 | 2  | 7 | [22] | [20] | 42  |

- [0158] 이상, 본 발명의 일 실시예인 LDPC 코드 구조의 일 예에 대해서 설명하였으나, 상술한 수치 또는 도면에 의해 본 발명의 권리범위가 제한 되는 것은 아니다. 상술한 발명의 특징을 포함하는 다양한 형태의 실시예가 본 발명의 권리범위에 포함 될 수 있다.

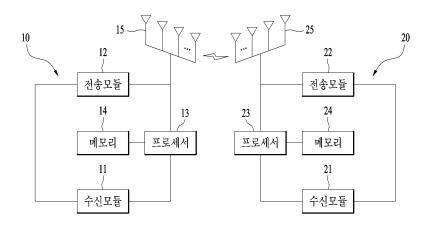

- [0159] 도 19는 본 발명의 일 실시예에 따른 장치를 설명하기 위한 도면이다.

- [0160] 도 19을 참조하여, 본 발명에 따른 기지국 장치(10)는, 수신 모듈(11), 송신모듈(12), 프로세서(13), 메모리

- (14) 및 복수개의 안테나(15)를 포함할 수 있다. 송신 모듈(12)은 외부 장치(예를 들어, 단말)로의 각종 신호, 데이터 및 정보를 전송할 수 있다. 수신 모듈(11)은 외부 장치(예를 들어, 단말)로부터의 각종 신호, 데이터 및 정보를 수신할 수 있다. 수신 모듈(11)과 송신 모듈(12)은 트랜시버(transceiver)로서 호칭될 수 있다. 프로세서(13)는 기지국 장치(10) 전반의 동작을 제어할 수 있다. 복수개의 안테나(15)는 예를 들어 2-차원 안테나 배치에 따라서 구성될 수 있다.

- [0161] 본 발명의 일례에 따른 기지국 장치(10)의 프로세서(13)는, 본 발명에서 제안하는 예시들에 따라서 채널상태정보를 수신하도록 구성될 수 있다. 기지국 장치(10)의 프로세서(13)는 그 외에도 기지국 장치(10)가 수신한정보, 외부로 전송할 정보 등을 연산 처리하는 기능을 수행하며, 메모리(14)는 연산 처리된 정보 등을 소정시간동안 저장할 수 있으며, 버퍼(미도시)등의 구성요소로 대체될 수 있다.

- [0162] 도 19을 참조하여, 본 발명에 따른 단말 장치(20)는, 수신 모듈(21), 송신 모듈(22), 프로세서(23), 메모리(24) 및 복수개의 안테나(25)를 포함할 수 있다. 복수개의 안테나(25)는 MIMO 송수신을 지원하는 단말 장치를 의미한다. 송신 모듈(22)은 외부 장치(예를 들어, 기지국)로의 각종 신호, 데이터 및 정보를 전송할 수 있다. 수신 모듈(21)은 외부 장치(예를 들어, 기지국)로부터의 각종 신호, 데이터 및 정보를 수신할 수 있다. 수신 모듈(21) 과 송신 모듈(22)은 트랜시버(transceiver)로서 호칭될 수 있다. 프로세서(23)는 단말 장치(20) 전반의 동작을 제어할 수 있다.

- [0163] 본 발명의 일례에 따른 단말 장치(20)의 프로세서(23)는, 본 발명에서 제안하는 예시들에 따라서 채널상태정보를 송신하도록 구성될 수 있다. 단말 장치(20)의 프로세서(23)는 그 외에도 단말 장치(20)가 수신한 정보, 외부로 전송할 정보 등을 연산 처리하는 기능을 수행하며, 메모리(24)는 연산 처리된 정보 등을 소정시간 동안 저장할 수 있으며, 버퍼(미도시) 등의 구성요소로 대체될 수 있다.

- [0164] 위와 같은 단말 장치(10)의 구체적인 구성은, 전술한 본 발명의 다양한 실시예에서 설명한 사항들이 독립적으로 적용되거나 또는 2 이상의 실시예가 동시에 적용되도록 구현될 수 있으며, 중복되는 내용은 명확성을 위하여 설명을 생략한다.

- [0165] 또한, 본 발명의 다양한 실시예들을 설명함에 있어서, 하향링크 전송 주체(entity) 또는 상향링크 수신 주체는 주로 기지국을 예로 들어 설명하였고, 하향링크 수신 주체 또는 상향링크 전송 주체는 주로 단말을 예로 들어 설명하지만, 본 발명의 범위가 이에 제한되는 것은 아니다. 예를 들어, 상기 기지국에 대한 설명은 셀, 안테나 포트, 안테나 포트 그룹, RRH, 전송 포인트, 수신 포인트, 액세스 포인트, 중계기 등이 단말로의 하향링크 전송 주체가 되거나 단말로부터의 상향링크 수신 주체가 되는 경우에 동일하게 적용될 수 있다. 또한, 중계기가 단말로의 하향링크 전송 주체가 되거나 단말로부터의 상향링크 수신 주체가 되는 경우, 또는 중계기가 기지국으로의 상향링크 전송 주체가 되거나 기지국으로부터의 하향링크 수신 주체가 되는 경우에도 본 발명의 다양한 실시예를 통하여 설명한 본 발명의 원리가 동일하게 적용될 수도 있다.

- [0166] 상술한 본 발명의 실시예들은 다양한 수단을 통해 구현될 수 있다. 예를 들어, 본 발명의 실시예들은 하드웨어, 펌웨어(firmware), 소프트웨어 또는 그것들의 결합 등에 의해 구현될 수 있다.

- [0167] 하드웨어에 의한 구현의 경우, 본 발명의 실시예들에 따른 방법은 하나 또는 그 이상의 ASICs(Application Specific Integrated Circuits), DSPs(Digital Signal Processors), DSPDs(Digital Signal Processing Devices), PLDs(Programmable Logic Devices), FPGAs(Field Programmable Gate Arrays), 프로세서, 컨트롤러, 마이크로 컨트롤러, 마이크로 프로세서 등에 의해 구현될 수 있다.

- [0168] 펌웨어나 소프트웨어에 의한 구현의 경우, 본 발명의 실시예들에 따른 방법은 이상에서 설명된 기능 또는 동작들을 수행하는 모듈, 절차 또는 함수 등의 형태로 구현될 수 있다. 소프트웨어 코드는 메모리 유닛에 저장되어 프로세서에 의해 구동될 수 있다. 상기 메모리 유닛은 상기 프로세서 내부 또는 외부에 위치하여, 이미 공지된 다양한 수단에 의해 상기 프로세서와 데이터를 주고 받을 수 있다.

- [0169] 이상에서 설명된 실시예들은 본 발명의 구성요소들과 특징들이 소정 형태로 결합된 것들이다. 각 구성요소 또는 특징은 별도의 명시적 언급이 없는 한 선택적인 것으로 고려되어야 한다. 각 구성요소 또는 특징은 다른 구성요소나 특징과 결합되지 않은 형태로 실시될 수 있다. 또한, 일부 구성요소들 및/또는 특징들을 결합하여 본 발명의 실시예를 구성하는 것도 가능하다. 본 발명의 실시예들에서 설명되는 동작들의 순서는 변경될 수 있다. 어느실시예의 일부 구성이나 특징은 다른 실시예에 포함될 수 있고, 또는 다른 실시예의 대응하는 구성 또는 특징과교체될 수 있다. 특허청구범위에서 명시적인 인용 관계가 있지 않은 청구항들을 결합하여 실시예를 구성하거나출원 후의 보정에 의해 새로운 청구항으로 포함시킬 수 있음은 자명하다.

- [0170] 본 발명은 본 발명의 정신 및 필수적 특징을 벗어나지 않는 범위에서 다른 특정한 형태로 구체화될 수 있음은 통상의 기술자에게 자명하다. 따라서, 상기의 상세한 설명은 모든 면에서 제한적으로 해석되어서는 아니되고 예시적인 것으로 고려되어야 한다. 본 발명의 범위는 첨부된 청구항의 합리적 해석에 의해 결정되어야 하고, 본 발명의 등가적 범위 내에서의 모든 변경은 본 발명의 범위에 포함된다.

- [0171] 본 발명의 실시예들은 다양한 무선접속 시스템 및 방송 통신 시스템에 적용될 수 있다. 다양한 무선접속 시스템 들의 일례로서, 3GPP(3rd Generation Partnership Project), 3GPP2 및/또는 IEEE 802.xx (Institute of Electrical and Electronic Engineers 802) 시스템 등이 있다. 본 발명의 실시예들은 상기 다양한 무선접속 시스템뿐 아니라, 상기 다양한 무선접속 시스템을 응용한 모든 기술 분야에 적용될 수 있다.

### 도면1

$$H = \begin{bmatrix} P^{\ h}{}^{b}_{00} & P^{\ h}{}^{b}_{01} & P^{\ h}{}^{b}_{02} & \cdots & P^{\ h}{}^{b}_{0\ nb} \\ P^{\ h}{}^{b}_{10} & P^{\ h}{}^{b}_{11} & P^{\ h}{}^{b}_{12} & \cdots & P^{\ h}{}^{b}_{1\ nb} \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ P^{\ h}{}^{b}_{mb\ 0} & P^{\ h}{}^{b}_{mb\ 1} & P^{\ h}{}^{b}_{mb\ 2} & \cdots & P^{\ h}{}^{b}_{mb\ nb} \end{bmatrix} = P^{\ H}b$$

#### 도면8

2 -1 19 -1 47 -1 48 -1 36 -1 82 -1 47 -1 15 -1 95 0 -1 -1 -1 -1 -1 -1 -1 -1 69 -1 88 -1 33 -1 3 -1 16 -1 37 -1 40 -1 48 -1 0 0 -1 -1 -1 -1 -1 -1 10 -1 86 -1 62 -1 28 -1 85 -1 16 -1 34 -1 73 -1 -1 -1 0 0 -1 -1 -1 -1 -1 -1 28 -1 32 -1 81 -1 27 -1 88 -1 5 -1 56 -1 37 -1 -1 -1 0 0 -1 -1 -1 -1 23 -1 29 -1 15 -1 30 -1 66 -1 24 -1 50 -1 62 -1 -1 -1 -1 -1 0 0 -1 -1 -1 30 -1 65 -1 54 -1 14 -1 0 -1 30 -1 74 -1 0 -1 -1 -1 -1 -1 0 0 -1 32 -1 0 -1 15 -1 56 -1 85 -1 5 -1 6 -1 52 -1 0 -1 -1 -1 -1 -1 0 0 -1 0 -1 47 -1 13 -1 61 -1 84 -1 55 -1 78 -1 41 98 -1 -1 -1 -1 -1 -1 0

## 도면13

## 도면16