## (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第3648466号 (P3648466)

(45) 発行日 平成17年5月18日(2005.5.18)

(24) 登録日 平成17年2月18日 (2005.2.18)

| (51) Int.C1. <sup>7</sup>                               | FI<br>HO1L                                                                                                                                | 29/78 6                                      | 18B                                                                                                                                      |          |                                                                                             |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------|

| HO1L 21/76                                              | HO1L                                                                                                                                      |                                              | В                                                                                                                                        |          |                                                                                             |

| HO1L 21/762                                             | HO1L                                                                                                                                      | 29/78 6                                      | 18E                                                                                                                                      |          |                                                                                             |

| HO1L 27/12                                              | HO1L                                                                                                                                      | 29/78 6                                      | 26C                                                                                                                                      |          |                                                                                             |

|                                                         | HO1L                                                                                                                                      | 21/76                                        | D                                                                                                                                        |          |                                                                                             |

|                                                         |                                                                                                                                           |                                              | 清求項の数 11                                                                                                                                 | (全 16 頁) | 最終頁に続く                                                                                      |

| (21) 出願番号<br>(22) 出願日<br>(65) 公開番号<br>(43) 公開日<br>審査請求日 | 特願2001-199820 (P2001-199820)<br>平成13年6月29日 (2001.6.29)<br>特開2003-17705 (P2003-17705A)<br>平成15年1月17日 (2003.1.17)<br>平成15年2月27日 (2003.2.27) | (74) 代理人<br>(74) 代理人<br>(72) 発明者<br>(72) 発明者 | 株式京75683<br>弁100075683<br>弁100084515<br>弁手塚奈会山川社 勉県東直県東<br>では、川本 では、<br>がは、<br>がは、<br>がは、<br>がは、<br>がは、<br>がは、<br>がは、<br>がは、<br>がは、<br>が | 喜久男      | で<br>で<br>で<br>で<br>で<br>で<br>で<br>で<br>で<br>で<br>で<br>で<br>で<br>で<br>で<br>で<br>で<br>で<br>で |

|                                                         |                                                                                                                                           | 審査官<br>                                      | 綿引隆                                                                                                                                      | 最        | <b>と終頁に続く</b>                                                                               |

(54) 【発明の名称】電界効果トランジスタ、半導体基板、電界効果トランジスタの製造方法及び半導体基板の製造方法

## (57)【特許請求の範囲】

### 【請求項1】

Si層と、このSi層表面上に形成されたSi酸化物層と、このSi酸化物層表面上に形成された、Si酸化物にGe酸化物を含有したGe酸化物含有層と、このGe酸化物含有層表面上に形成された格子緩和SiGe層と、この格子緩和SiGe層表面上に形成された歪Si層あるいは歪SiGe層と、この歪Si層あるいは歪SiGe層表面上に形成されたゲート絶縁層と、このゲート絶縁層表面上に形成されたゲート電極と、前記歪Si層あるいは歪SiGe層中に形成されたソース領域及びドレイン領域とを具備することを特徴とする電界効果トランジスタ。

### 【請求項2】

10

Si層と、このSi層表面上に形成された第1のSi酸化物層と、この第1のSi酸化物層表面上に形成された、Si酸化物にGe酸化物を含有したGe酸化物含有層と、このGe酸化物層表面上に形成された第2のSi酸化物層と、この第2のSi酸化物層表面上に形成された第2のSi酸化物層と、この第2のSi酸化物層表面上に形成された在Si層あるいは歪SiGe層と、この歪Si層あるいは歪SiGe層表面上に形成されたゲート絶縁層と、このゲート絶縁層表面上に形成されたゲート電極と、前記歪Si層あるいは歪SiGe層中に形成されたソース領域及びドレイン領域とを具備することを特徴とする電界効果トランジスタ。

### 【請求項3】

前記Ge酸化物含有層のGe酸化物は1重量%以上50重量%以下であることを特徴と

する請求項1または2記載の電界効果トランジスタ。

### 【請求項4】

Si層と、このSi層表面上に形成された第1のSi酸化物層と、この第1のSi酸化物層表面上に形成された、Si酸化物にGe酸化物を含有したGe酸化物含有層と、このGe酸化物含有層表面上に形成された格子緩和SiGe層とを具備することを特徴とする半導体基板。

## 【請求項5】

Si層と、このSi層表面上に形成された第1のSi酸化物層と、この第1のSi酸化物層表面上に形成された、Si酸化物にGe酸化物を含有したGe酸化物含有層と、このGe酸化物含有層表面上に形成された第2のSi酸化物層と、この第2のSi酸化物層表面上に形成された格子緩和SiGe層とを具備することを特徴とする半導体基板。

#### 【請求項6】

第1のSi層表面上にSiGe層を形成する工程と、前記SiGe層表面上に第2のSi層を形成する工程と、前記第2のSi層の全てと前記SiGe層の一部を酸化することにより前記第2のSi層を第1のSi酸化物層とし、前記SiGe層の一部をSi酸化物とGe酸化物の混合酸化物であるGe酸化物含有層とする工程と、前記第1のSi層中にマイクロクラック領域を形成する工程と、前記第1のSi酸化物層と第2のSi層を接合する工程と、前記第1のSi層の一部を前記マイクロクラック領域で前記第1のSi層の残部から剥離する工程と、前記第1のSi層表面から酸化することにより前記第1のSi層を第2のSi酸化物層とし、前記SiGe層の前記Ge酸化物含有層に隣接する領域を格子緩和SiGe層にする工程と、前記第2のSi酸化物層を除去する工程と、前記格子緩和SiGe層表面に歪Si層あるいは歪SiGe層表面上にゲート酸化膜、ゲート電極を形成する上程と、前記歪Si層あるいは歪SiGe層表面上にゲート酸化膜、ゲート電極を形成するとともに、前記歪Si層あるいは歪SiGe層中にソース領域並びにドレイン領域を形成する工程とを具備することを特徴とする電界トランジスタの製造方法。

### 【請求項7】

### 【請求項8】

第1のSi層表面上にSiGe層を形成する工程と、前記SiGe層表面上に第2のSi層を形成する工程と、前記第2のSi層の全てと前記SiGe層の一部を酸化することにより前記第2のSi層を第1のSi酸化物層とし前記SiGe層の一部をSi酸化物とGe酸化物の混合酸化物であるGe酸化物含有層とする工程と、前記第1のSi層中にマイクロクラック領域を形成する工程と、前記第1のSi酸化物層と第2のSi層を接合する工程と、前記第1のSi層の一部を前記マイクロクラック領域で前記第1のSi層の残部から剥離する工程と、前記第1のSi層表面から酸化することにより前記第1のSi層を第2のSi酸化物層とし、前記SiGe層の前記Ge酸化物含有層に隣接する領域を格子緩和SiGe層にする工程とを具備することを特徴とする半導体基板の製造方法。

## 【請求項9】

50

40

30

20

10

SU

第1のSi層表面上にSi酸化物層を形成する工程と、前記Si酸化物層表面からGeイオン並びに酸素イオンを注入することにより前記Si酸化物層表面にGe・酸素含有層を形成する工程と、第2のSi層表面上にSiGe層を形成する工程と、前記SiGe層表面上に第3のSi層を形成する工程と、前記第2のSi層中にマイクロクラック領域を形成する工程と、前記Ge・酸素含有層と前記第3のSi層を接合する工程と、前記第2のSi層の一部を前記マイクロクラック領域で前記第1のSi層の残部から剥離する工程と、前記第2のSi層表面から酸化することにより、格子緩和SiGe層を形成し、同時に、前記Ge・酸素含有層をSi酸化物とGe酸化物の混合酸化物であるGe酸化物含有層とする工程とを具備することを特徴とする半導体基板の製造方法。

#### 【請求項10】

【請求項11】

第1のSi層表面上に第1のSi酸化物層を形成する工程と、前記第1のSi酸化物層表面上に第2のSi層を形成する工程と、この第2のSi層中にGeイオン及び酸素イオンを注入し前記第2のSi層中にGe・酸素含有層を形成する工程と、前記第2のSi層表面上にSiGe層を形成する工程と、前記SiGe層表面上に第3のSi層を形成する工程と、前記第3のSi層表面から酸化を行うことにより、前記第1の酸化物層表面上にGe酸化物及びSi酸化物の混合酸化物からなるGe酸化物含有層を形成し、このGe酸化物含有層表面上に格子緩和SiGe層を形成し、この格子緩和SiGe層表面上に第2のSi酸化物層を形成する工程とを具備することを特徴とする半導体基板の製造方法。

第1のSi層表面上に第1のSiGe層を形成する工程と、この第1のSiGe層表面上に第2のSi層を形成する工程と、この第2のSi層を形成する工程と、前記第3のSi層を形成する工程と、前記第3のSi層の全て、前記第2のSiGe層表面上に第3のSi層を形成する工程と、前記第3のSi層の全て、前記第2のSi層表面上に第1のSi酸化物層、Ge酸化物及びSi酸化物の混合酸化物からなるGe酸化物含有層並びに第2の酸化物層を形成する工程と、前記第1のSi層中にマイクロクラック領域を形成する工程と、第4のSi層表面上に前記第2の酸化物層を接合する工程と、前記第1のSi層の一部を前記マイクロクラック領域で前記第1のSi層の残部から剥離する工程と、前記第1のSi層表面から酸化することにより、前記第1のSi酸化物層表面上に格子緩和SiGe層及びこの格子緩和SiGe層表面上に第3のSi酸化物層を形成する工程とを具備することを特徴とする半導体基板の製造方法。

【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は、電界効果トランジスタ<u>、半導体基板、電界効果トランジスタの製造方法及び</u> 半導体基板の製造方法に関する。

[00002]

【従来の技術】

マイクロプロセサ等の大規模集積回路(LSI)の高速化、高機能化、低消費電力化を図るためには、回路を構成する個々のトランジスタの駆動力を維持或いは向上させつつ微細化する必要がある。例えば従来、MOSFETにおいては、ゲート長を短縮することで対応してきた。

[0003]

しかしながら、近年、ゲート長を短縮するには技術的或いは経済的な障壁が急激に高くなってきている。そこで、ゲート長を短縮する方法以外に、LSIを高速化させる方法として、高移動度のチャネル材料を用いる方法がある。

[0004]

高移動度のチャネル材料として、歪Siや歪SiGeが注目されている。このうち歪Siは、Siより格子定数の大きな格子緩和SiGe上にエピタキシャル成長させることにより形成される。また歪SiGeは、これよりGe組成比が大きな格子緩和SiGe上にエ

10

20

30

40

ピタキシャル成長することにより形成される。歪Siは、面内の引張り歪により、また、歪SiGeは面内の圧縮歪により、電子、正孔の移動度がいずれも増大する。また、下地の格子緩和SiGeとチャネル材料とのGe組成差が大きいほど、すなわち格子定数の差が大きいほどチャネル層に導入される歪量が大きくなり、移動度は大きくなる。

[0005]

本発明者らは、歪Si及び歪SiGeとSOI(Si‐on‐insulator)構造とを組み合わせたMOSFET(歪SOI‐MOSFET)を提案し、さらに動作実証してきた。(T. Mizuno, S. Takagi, N. Sugiyama, J. Koga, T. Tezuka, K. Usuda, T. Hatakeyama, A. Kurobe, and A. Toriumi, IEDM Technical Digests p.934 (1999) )。

[0006]

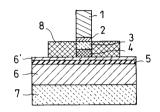

図9に、歪Siを用いた歪SOI-MOSFETの断面図を示す。

[0007]

図9に示すように、歪SOI-MOSFETは、Si基板7と、このSi基板7上に形成された絶縁層6と、この絶縁層6上に形成された格子緩和 $Si_{0...9}$  Ge $_{0...1}$  バッファ層4と、この格子緩和 $Si_{0...9}$  Ge $_{0...1}$  バッファ層4上に形成された歪Si 層3と、この歪Si 層3上に形成されたゲート酸化層2と、このゲート酸化層2上に形成されたゲート電極1とを具備している。ゲート酸化層2下の歪Si 層3はチャネル領域となり、このチャネル領域を挟むようにソース領域及びドレイン領域8が形成されている。

[0008]

このような歪SOI・MOSFETは、歪Si層3をチャネルとして用いているのでキャリア移動度が高いという利点がある。また、この利点のほか、SOI構造により接合容量を小さくできる利点、また、不純物濃度を低く抑えたまま微細化ができる利点がある。さらに、インパクトイオン化で発生した正孔が緩和SiGe層を通してソース領域に容易に吸収されるため、通常SOI構造で問題となるボディ浮遊効果も抑制することができる。

[0009]

本発明者らの研究の結果、このような利点を有する歪SOI-MOSFETを実用させるためには、格子緩和 $Si_{1-x}Ge_x$ バッファ層4をより低転位密度で、かつほぼ完全に格子緩和0、厚さ30nm以下に抑える必要があることが分かった。このような条件を満足する格子緩和 $Si_{1-x}Ge_x$ バッファ層4上に歪Si層3をエピタキシャル成長させることで歪Si層3の移動度をより向上させることができることが分かった。

[0010]

このような格子緩和Si<sub>1 - ×</sub> Ge  $_{\times}$  バッファ層  $_{4}$  を形成するための方法として、本発明者らは絶縁層  $_{6}$  上にGe組成比が低いSi $_{1}$  -  $_{\times}$  Ge  $_{\times}$  層( $_{\times}$  = 0 . 1)を成長させ、このSi $_{1}$  -  $_{\times}$  Ge  $_{\times}$  層( $_{\times}$  = 0 . 1)層を高温で熱酸化する方法を見出している。これは熱酸化が進むにつれてSi $_{1}$  -  $_{\times}$  Ge  $_{\times}$  層( $_{\times}$  = 0 . 1)のGeが濃縮されGe組成比の高いSi $_{1}$  -  $_{\times}$  Ge  $_{\times}$  層( $_{\times}$  > 0 . 5)が形成されると同時に、このSi $_{1}$  -  $_{\times}$  Ge  $_{\times}$  層( $_{\times}$  > 0 . 5)が格子緩和し、薄層化することを利用したものである。(T. Tezuka,N. Sugiyama,T. Mizuno,M. Suzuki,and S. Takagi,Extended Abstracts of the 2000 In ternational Conference on Solid State Devices and Materials (Sendai, 2000),p. 472.)。

[0011]

【発明が解決しようとする課題】

絶縁層6上に形成されたGe組成比が小さいSi $_{1-x}$  Ge $_{x}$  層( $_{x}$  = 0 . 1)を、高温で乾燥熱酸化することにより、表面に形成されるSiGe酸化層中からGe原子が吐き出され、残りのSiGe層中に蓄積される。一方、下地層の絶縁層6はGe原子がSi基板7中に拡散するのを防ぐ。したがって、酸化が進行するとともに残りのSiGe層中のGe組成比は増大する。

[0012]

G e 組成比が高いほど S i G e の格子定数は大きくなるので、絶縁層 6 と S i G e 層 4 との界面にはせん断応力が生じる。界面での滑り或いは絶縁層 6 の塑性変形が充分であれば

10

20

30

40

、このせん断応力によりSiGe層4は自由に伸縮できるので、格子緩和が転位の発生を伴うことなく進行する。

### [0013]

[0014]

このようにSiGe層が溶解しないようにして貫通転位密度を実用上の目安となる値10 <sup>4</sup> cm<sup>・2</sup> まで低減するのが困難であるという問題があった。

[0015]

本発明は、格子緩和SiGe層の貫通転位密度を低減でき、この格子緩和SiGe層上に 歪Si層或いは歪SiGe層を形成した電界効果トランジスタを提供することを目的とす る。

[0016]

【課題を解決するための手段】

上記目的を達成するために、本発明は、Si層と、このSi層表面上に形成されたSi酸化物層と、このSi酸化物層表面上に形成された、Si酸化物にGe酸化物を含有したGe酸化物含有層と、このGe酸化物含有層表面上に形成された格子緩和SiGe層と、この格子緩和SiGe層表面上に形成された歪Si層あるいは歪SiGe層と、この歪Si層あるいは歪SiGe層と、この歪Si層あるいは歪SiGe層表面上に形成されたゲート絶縁層と、このゲート絶縁層表面上に形成されたゲート電極と、前記歪Si層あるいは歪SiGe層中に形成されたソース領域及びドレイン領域とを具備することを特徴とする電界効果トランジスタを提供する。

[0017]

また、本発明は、Si層と、このSi層表面上に形成された第1のSi酸化物層と、この第1のSi酸化物層表面上に形成された、Si酸化物にGe酸化物を含有したGe酸化物含有層と、このGe酸化物層表面上に形成された第2のSi酸化物層と、この第2のSi酸化物層表面上に形成された格子緩和SiGe層と、この格子緩和SiGe層表面上に形成された歪Si層あるいは歪SiGe層と、この歪Si層あるいは歪SiGe層表面上に形成されたゲート絶縁層と、このゲート絶縁層表面上に形成されたゲート電極と、前記歪Si層あるいは歪SiGe層中に形成されたソース領域及びドレイン領域とを具備することを特徴とする電界効果トランジスタを提供する。

[0018]

また、<u>本発明は前記Ge酸化物含有層のGe酸化物は1重量%以上50重量%以下であることを特徴とする電界効果トランジスタを提供する。</u>

[0019]

また、本発明は、Si層と、このSi層表面上に形成された第1のSi酸化物層と、この第1のSi酸化物層表面上に形成された、Si酸化物にGe酸化物を含有したGe酸化物含有層と、このGe酸化物含有層表面上に形成された格子緩和SiGe層とを具備することを特徴とする半導体基板を提供する。

[0020]

また、本発明は、Si層と、このSi層表面上に形成された第1のSi酸化物層と、この第1のSi酸化物層表面上に形成された、Si酸化物にGe酸化物を含有したGe酸化物含有層と、このGe酸化物含有層表面上に形成された第2のSi酸化物層と、この第2のSi酸化物層表面上に形成された格子緩和SiGe層とを具備することを特徴とする半導体基板を提供する。

[0021]

10

20

30

40

また、本発明は、第1のSi層表面上にSiGe層を形成する工程と、前記SiGe層表面上に第2のSi層を形成する工程と、前記第2のSi層の全てと前記SiGe層の一部を酸化することにより前記第2のSi層を第1のSi酸化物層とし、前記SiGe層の一部をSi酸化物とGe酸化物の混合酸化物であるGe酸化物含有層とする工程と、前記第1のSi層中にマイクロクラック領域を形成する工程と、前記第1のSi酸化物層と第2のSi層を接合する工程と、前記第1のSi層の一部を前記マイクロクラック領域で前記第1のSi層の残部から剥離する工程と、前記第1のSi層表面から酸化することにより前記第1のSi層を第2のSi酸化物層とし、前記SiGe層の前記Ge酸化物含有層に隣接する領域を格子緩和SiGe層にする工程と、前記第2のSi酸化物層を除去する工程と、前記格子緩和SiGe層表面に歪Si層あるいは歪SiGe層を形成する工程と、前記歪Si層あるいは歪SiGe層表面上にゲート酸化膜、ゲート電極を形成するとともに、前記歪Si層あるいは歪SiGe層表面上にゲート酸化膜、ゲート電極を形成するとともに、前記歪Si層あるいは歪SiGe層中にソース領域並びにドレイン領域を形成する工程と、負債することを特徴とする電界トランジスタの製造方法を提供する。

### [0022]

また、本発明は、第1のSi層表面上にSi酸化物層を形成する工程と、前記Si酸化物層表面からGeイオン並びに酸素イオンを注入することにより前記Si酸化物層表面にGe・酸素含有層を形成する工程と、第2のSi層表面上にSiGe層を形成する工程と、前記SiGe層表面上に第3のSi層を形成する工程と、前記第2のSi層中にマイクロクラック領域を形成する工程と、前記Ge・酸素含有層と前記第3のSi層を接合する工程と、前記第2のSi層の一部を前記マイクロクラック領域で前記第1のSi層の残部から剥離する工程と、前記第2のSi層表面から酸化することにより、格子緩和SiGe層を形成し、同時に、前記Ge・酸素含有層をSi酸化物とGe酸化物の混合酸化物であるGe酸化物含有層とする工程と、前記第2のSi酸化物層を除去する工程と、前記在Si層を移れてまららのSiGe層表面に在Si層あるいは在SiGe層上にゲート酸化膜、ゲート電極を形成するとともに、前記在Si層あるいは在SiGe層中にソース領域並びにドレイン領域を形成する工程とを具備することを特徴とする電界効果トランジスタの製造方法を提供する。

### [0023]

また、本発明は、第1のSi層表面上にSiGe層を形成する工程と、前記SiGe層表面上に第2のSi層を形成する工程と、前記第2のSi層の全てと前記SiGe層の一部を酸化することにより前記第2のSi層を第1のSi酸化物層とし前記SiGe層の一部をSi酸化物とGe酸化物の混合酸化物であるGe酸化物含有層とする工程と、前記第1のSi層中にマイクロクラック領域を形成する工程と、前記第1のSi酸化物層と第2のSi層を接合する工程と、前記第1のSi層の一部を前記マイクロクラック領域で前記第1のSi層の残部から剥離する工程と、前記第1のSi層表面から酸化することにより前記第1のSi層を第2のSi酸化物層とし、前記SiGe層の前記Ge酸化物含有層に隣接する領域を格子緩和SiGe層にする工程とを具備することを特徴とする半導体基板の製造方法を提供する。

## [0024]

また、本発明は、第1のSi層表面上にSi酸化物層を形成する工程と、前記Si酸化物層表面からGeイオン並びに酸素イオンを注入することにより前記Si酸化物層表面にGe・酸素含有層を形成する工程と、第2のSi層表面上にSiGe層を形成する工程と、前記SiGe層表面上に第3のSi層を形成する工程と、前記第2のSi層中にマイクロクラック領域を形成する工程と、前記Ge・酸素含有層と前記第3のSi層を接合する工程と、前記第2のSi層の一部を前記マイクロクラック領域で前記第1のSi層の残部から剥離する工程と、前記第2のSi層表面から酸化することにより、格子緩和SiGe層を形成し、同時に、前記Ge・酸素含有層をSi酸化物とGe酸化物の混合酸化物であるGe酸化物含有層とする工程とを具備することを特徴とする半導体基板の製造方法を提供する。

[0025]

10

20

30

また、本発明は、第1のSi層表面上に第1のSi酸化物層を形成する工程と、前記第1のSi酸化物層表面上に第2のSi層を形成する工程と、この第2のSi層中にGeイオン及び酸素イオンを注入し前記第2のSi層中にGe・酸素含有層を形成する工程と、前記第2のSi層表面上にSiGe層を形成する工程と、前記SiGe層表面上に第3のSi層を形成する工程と、前記第3のSi層表面から酸化を行うことにより、前記第1の酸化物層表面上にGe酸化物及びSi酸化物の混合酸化物からなるGe酸化物含有層を形成し、このGe酸化物含有層表面上に格子緩和SiGe層を形成し、この格子緩和SiGe層表面上に第2のSi酸化物層を形成する工程とを具備することを特徴とする半導体基板の製造方法を提供する。

#### [0026]

また、本発明は、第1のSi層表面上に第1のSiGe層を形成する工程と、この第1のSiGe層表面上に第2のSi層を形成する工程と、この第2のSi層表面上に第2のSiGe層を形成する工程と、この第2のSiGe層表面上に第3のSi層を形成する工程と、前記第3のSi層の全て、前記第2のSiGe層の全て並びに前記第2のSi層の一部を酸化することにより、前記第2のSi層表面上に第1のSi酸化物層、Ge酸化物及びSi酸化物の混合酸化物からなるGe酸化物含有層並びに第2の酸化物層を形成する工程と、前記第1のSi層中にマイクロクラック領域を形成する工程と、第4のSi層表面上に前記第2の酸化物層を接合する工程と、前記第1のSi層の一部を前記マイクロクラック領域で前記第1のSi層の残部から剥離する工程と、前記第1のSi層表面から酸化することにより、前記第1のSi酸化物層表面上に格子緩和SiGe層及びこの格子緩和SiGe層表面上に第3のSi酸化物層を形成する工程とを具備することを特徴とする半導体基板の製造方法を提供する。

### [0027]

### 【発明の実施の形態】

以下、図面を参照して、本発明の実施形態について説明する。

### [0028]

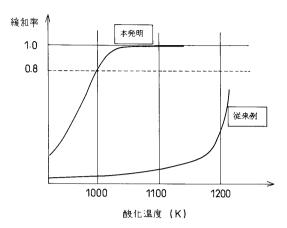

先ず、図 7 に絶縁層上に厚さ 9 0 n m の S i  $_0$  .  $_9$  G e  $_0$  .  $_1$  層を形成し、これを酸化によって厚さ 3 0 n m の S i  $_0$  .  $_7$  G e  $_0$  .  $_3$  層にした場合の絶縁層と S i G e 層との界面での滑りによって生じる緩和率の酸化温度との関係を示す。

## [0029]

本発明として、絶縁層は $GeO_2$ が9重量%含有した $SiO_2$ 層を用いた。従来例として、絶縁層は純粋な $SiO_2$ 層を用いた。

### [0030]

図7に示すように、従来例では酸化温度が1200 においても5割程度の緩和率しか得られないのに対し、本発明では1000 で8割に達する緩和率が得られる。

### [0031]

以上のように、絶縁層としてGe酸化物を1重量%以上含有するGe酸化物含有層を導入すると、熱処理温度が1000 でSiGe層との界面で充分な滑りが生じて転位を発生させること無くSiGe層を緩和させることが可能になる。これはGe酸化物を1重量%以上含有するGe酸化物含有層は、純粋なSiO₂に比べ軟化温度が低いためである。軟化温度はGeの含有量が増加するにつれて低下する。例えば、SiO₂にGeO₂を1重量%添加することで、軟化温度が約20 低下する。また、GeO₂を9重量%添加することで、軟化温度が約20 低下する(枝広ほか、電子通信学会論文誌 C、63(1980)751参照)。

## [0032]

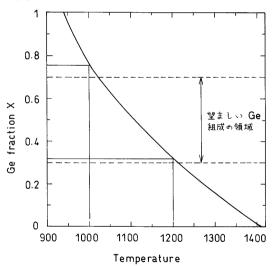

次に、図 8 に S i  $_{1-x}$  G e  $_{x}$  の G e 組成 x と融点との関係を示す。

### [0033]

10

20

30

40

20

30

40

50

は、緩和SiGe層のGe組成として望ましい値よりも低い値である。すなわち、上層に 形成する歪Siの歪量をより大きくするためには十分ではない。

[0034]

一方SiGe層を1000 で熱処理するのであれば、SiGeはGe組成が約0.8まで融解しないので、必要な格子定数の大きさを全て実現することができる。

[0035]

すなわち絶縁層として G e 酸化物が 1 重量%以上含む G e 酸化物含有層を導入することで、 1 0 0 0 で十分な格子緩和処理ができることになる。したがって、 S i G e の G e 組成を 0 . 8 まで実現できるので設計自由度を向上できるという効果がある。

[0036]

実質的な  $GeO_2$  添加の効果を得るには、 Ge組成が 1 重量%以上の含有量であれば良い。これは、軟化点温度に換算すると <math>20 以上の低下に相当する。図 8 から見て取れるように、わずか 20 のプロセス温度の低下であってもプロセス温度マージン増大の効果が得られる。

[0037]

次に、本発明における電界効果トランジスタを説明する。

[0038]

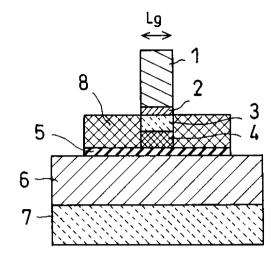

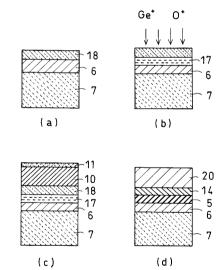

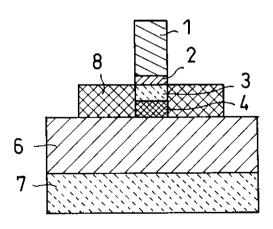

図1は、本発明の第1の実施形態にかかる電界効果トランジスタの断面図である。

[0039]

この電界効果トランジスタは、Si基板 7 と、このSi基板 7 上に形成された厚さ 3 0 0 n m のSi酸化物からなる絶縁層 6 と、この絶縁層 6 上に形成された厚さ 2 0 n m のSi酸化物とGe酸化物との混合酸化物からなるGe酸化物含有層 5 と、このGe酸化物含有層 5 上に形成された厚さ 2 0 n m の格子緩和Si $_0$ . $_7$  Ge $_0$ . $_3$  層 4 と、この格子緩和Si $_0$ . $_7$  Ge $_0$ . $_3$  層 4 と、この格子緩和Si $_0$ . $_7$  Ge $_0$ . $_3$  層 4 上に形成された厚さ 1 0 n m の歪Si層 3 と、この歪Si層 3 上に形成された厚さ 1 . 5 n m のゲート酸化層 2 と、このゲート酸化層 2 上に形成された 厚さ 2 0 0 n m のポリシリコンゲート電極 1 と、歪Si層 3 中に形成されたソース領域及びドレイン領域 8 とを具備する。ゲート長は 1 0 0 n m である。ゲート幅 W は 1  $\mu$  m である。この電界効果トランジスタは、格子緩和Si $_0$ . $_7$  Ge $_0$ . $_3$  層 4 が直接 G e 酸化物含有層 5 に接している。このGe酸化物含有層 5 のGe酸化物の重量組成は 1 6 重量%である。

[0040]

このようにGe酸化物含有層5上に直接SiGe層4を形成することで熱処理温度が1000程度で転位が生じない格子緩和を十分することができ素子の特性向上に寄与する。

[0041]

また、Ge酸化物含有層5のGe酸化物は50重量%以下であることが好ましい。これは50重量%を越えると水に対して溶けるという問題があるためであり、信頼性を考慮するとGe酸化物は20重量%以下であることがより好ましい。

[0042]

また、Ge酸化物含有層 5 は C、H、N、As、P、B等の不純物が 1 0 <sup>2 0</sup> cm<sup>-3</sup>程度なら混入していても問題ない。

[0043]

また、歪Si層は、SiGe、SiC、GeC、SiGeC等Ge、Cを含有するものでも良い。

[0044]

また、格子緩和SiGe層は、SiC、GeC、SiGeC等Ge、Cを含有するものでも良い。

[0045]

また、格子緩和S $i_1$   $I_1$   $I_2$   $I_3$   $I_4$   $I_4$   $I_5$   $I_5$

30

40

50

プとをそれぞれ独立に制御することが出来るので、素子作製の自由度が向上される。

### [0046]

図2は、本発明の第2の実施形態にかかる電界効果トランジスタの断面図である。

#### [0047]

図 2 に示すように、この電界効果トランジスタは、Si基板 7 と、このSi基板 7 上に形成された厚さ 3 0 0 n m のSi〇  $_2$  絶縁層 6 と、この絶縁層 6 上に形成された厚さ 2 0 n m のSi酸化物とGe酸化物の混合酸化物からなるGe酸化物含有層 5 と、このGe酸化物含有層 5 上に形成された厚さ 1 0 n m のSi〇  $_2$  絶縁層 6 'と、このSi〇  $_2$  絶縁層 6 'と、このSi〇  $_2$  絶縁層 6 'と、このSi〇  $_2$  絶縁層 6 '上に形成された厚さ 2 0 n m の格子緩和Si $_0$  、  $_7$  Ge $_0$  、  $_3$  層 4 と、この格子緩和Si $_0$  、  $_7$  Ge $_0$  、  $_3$  層 4 上に形成された厚さ 1 0 n m の歪Si層 3 と、この歪Si層 3 上に形成された厚さ 1 、5 n m のゲート酸化層 2 と、このゲート酸化層 2 上に形成された厚さ 1 、5 n m のゲート酸化層 2 と、このゲート酸化層 2 上に形成された厚さ 2 0 0 n m のポリシリコンゲート電極 1 と、歪Si層 3 中に形成されたソース領域及びドレイン領域 8 とを具備する。ゲート長は 1 0 0 n m である。ゲート幅 W は 1  $\mu$  m である。この電界効果トランジスタは、格子緩和Si。、 $_7$  Ge。、 $_3$  層 4 が直接 G e 酸化物含有層 5 に接していない点が第 1 の実施形態とことなる。このGe酸化物含有層 5 のGe酸化物の重量組成は 1 6 重量% である。

### [0048]

この実施形態では、格子緩和 S i G e 層 4 と G e 酸化物含有層 5 の間に厚さ 1 0 n m の S i O  $_2$  絶縁層 6 が挿入されている。本実施形態では、格子緩和 S i G e 層 4 と S i O  $_2$  絶縁層 6 との界面の電気的特性が良好である点を利用し第1の実施形態よりも素子特性が優れている。

### [0049]

第 1 の実施形態及び第 2 の実施形態では、 G e 酸化物含有層 5 と S i O  $_2$  絶縁層 6 及び 6 'として、独立に層を形成しているが、例えば G e 酸化物が S i O  $_2$  絶縁層 6 及び 6 '全体に含まれても良い。また、このとき G e 酸化物の含有量が S i 基板 7 側から格子緩和 S i G e 層 4 に向けて徐々に大きくなっても良いし小さくなっても良い。

### [0050]

また、ゲート電極 1 やゲート絶縁層 2 、ソース領域及びドレイン領域 8 については、既に公知となっている種々の構造、材料を適用することが可能である。例えば、ゲート電極 1 として、ポリSiGe、タングステンシリサイド或いはコバルトシリサイドゲート等を用いることができる。また、ゲート絶縁層 2 としては、 $Z r O_2$ 、 $A l_2 O_3$ 、 $H f O_2$ 、 $S i_3 N_4$ 、 $T i O_2$ 等の高誘電率誘電体を用いることができる。またソース領域及びドレイン領域 8 として、せり上げソース・ドレイン構造等を用いることができる。

## [0051]

また、歪Si層3の代わりに歪Ge層或いは歪Si $_{1-x}$  Ge $_{x}$  ( $_{x}$  × 0 . 5)を用いることができる。また、格子緩和Si $_{0-7}$  Ge $_{0-3}$  層4の代わりに緩和Si $_{0-3}$  Ge $_{0-7}$  層を用いることができる。このようにGe組成が大きくなっても格子緩和させるための処理温度が1000 程度と低いために溶融が生じず転位の発生もない。この場合Ge組成比が大きなため、歪Si層3の移動度が大きくなるという効果もある。特にpチャネルトランジスタにおいてより大きな移動度増大の効果が得られる。

## [0052]

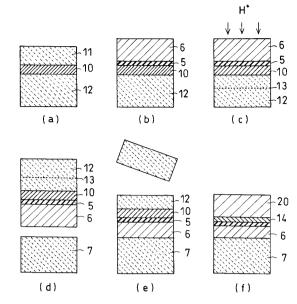

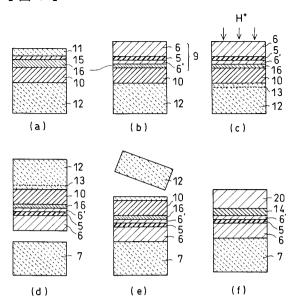

次に、図3を用いて第1の実施形態にかかる電界効果トランジスタの製造方法を説明する

## [0053]

先ず、図 3 ( a )に示すように、Si基板 1 2 上に厚さ 7 0 n m の S i  $_{0...9}$  G e  $_{0...1}$  層 1 0 を成長する。次に、このSi $_{0...9}$  G e  $_{0...1}$  層 1 0 上に、厚さ 1 5 0 n m の S i 層 1 1 を成長する。これらの成長はU H V - C V D 或いは L P - C V D 法により基板温度 5 0 0 から 6 5 0 にてエピタキシャル成長する。

### [0054]

次に、図3(b)に示すように、700 でのウェット酸化によりSi層の全てとSiG

30

40

50

e層の一部を酸化する。この酸化工程により厚さ 3 0 0 n m の S i O  $_2$  層 6 と厚さ 2 0 n m の S i 酸化物と G e 酸化物の混合酸化物である G e 酸化物含有層 5 を形成する。このときの G e 酸化物含有層 5 の G e O  $_2$  重量  $_8$  は、 1 6 重量  $_8$  である。

[0055]

次に、図 3 ( c )に示すように、 S i O  $_2$  層 6 上から、 1 0 0 K e V の注入エネルギー 5 × 1 0  $^1$  6 c m  $^2$  のドーズ量で水素イオンを注入する。この水素イオン注入により、 S i O  $_2$  層の表面から深さ約 6 5 0 n m の位置の S i 基板 1 2 中に格子欠陥が高密度に形成されたマイクロクラック領域 1 3 を形成する。

[0056]

次に、図 3 ( d )に示すように、基板をひっくり返し、 S i O  $_2$  層 6 の表面を別の S i 基板 7 に常温にて張り合わせる。

[0057]

次に、図3(e)に示すように、600 で3時間熱処理することにより、マイクロクラック領域13でウェハーを剥離する。剥離面はCMPにより平坦化する。Si基板12は、選択ウェットエッチングを用いた剥離方法を用いても良い。

[0058]

次に、図3(f)に示すように、基板温度1050 でドライ酸化する。このドライ酸化により基板表面から酸化が行われ、格子緩和SiGe層14が形成される。符号20はドライ酸化により酸化されたSiO $_2$  酸化層である。このドライ酸化では格子緩和SiGe層14は、厚さが20nmになり、Geが濃縮されてGe組成が増大し、それに伴い格子緩和する。この工程によりGe組成は0.3になる。

[0059]

次に、 $SiO_2$ 層20をフッ化アンモニウム溶液で除去する。次に、UHV-CVD或いは LP-CVD法により基板温度650 にて、格子緩和 $Si_{0...7}$  Ge $_{0...3}$ 層14上に歪Si層をエピタキシャル成長する。こうして十分に歪のかかった転位等のダメージのない良好なチャネル層を形成できる。

[0060]

この後の工程は、通常のSOI-MOSFET製造プロセスに従って、ゲート絶縁層、ゲート電極、ソース領域及びドレイン領域を形成して、図1に示す電界効果トランジスタを 形成する。

[0061]

次に、図4を用いて第1の実施形態にかかる電界効果トランジスタの別の製造方法を説明する。

[0062]

先ず、図 4 (a)に示すように、Si基板 7 を熱酸化して厚さ 1 0 0 n m の SiO  $_2$  層 6 を形成する。この酸化方法は、ウェットでもドライでもかまわない。

[0063]

次に、図 4 ( b ) に示すように、G e イオンを、3 0 K e V の注入エネルギー、1 . 5 ×  $10^{16}$  c m  $^{-2}$  のドーズ量でイオン注入する。引き続き、酸素イオンを、2 5 k e V の注入エネルギー、1 . 0 ×  $10^{17}$  c m  $^{-2}$  のドーズ量でイオン注入する。また、これらのイオン注入の順番は逆でも良い。これらのイオン注入後、酸素雰囲気中で 700 、 3 時間熱処理する。こうして S i O  $_2$  層 6 の表面領域にG e 及び酸素を含有する層 1 7 を形成する。

[0064]

次に、図4(c)に示すように、別のSi基板12上に、厚さ60nmのSi $_0$  ...  $_9$  Ge $_0$  ...  $_1$  層10、厚さ20nmのSiキャップ層11をUHV-CVD或いはLP-CVD法により基板温度500 から650 にてエピタキシャル成長する。引き続き100keVの注入エネルギー、5×10  $^1$   $^6$  cm  $^2$  のドーズ量で水素イオンをイオン注入する。このイオン注入により、Siキャップ層11の表面から深さ約650nmの領域に格子欠陥が高密度に形成されたマイクロクラック領域13を形成する。

### [0065]

次に、図4(d)に示すように、Siキャップ層11の表面を、図4(b)に示すGe及び酸素を含有する層17上に常温にて張り合わせる。次に600 で3時間熱処理することにより、マイクロクラック領域13でウェハーを剥離する。この剥離面はCMPにて平坦化する。

## [0066]

次に、図4(f)に示すように、基板温度1050 でドライ酸化する。このドライ酸化により基板表面から酸化が行われ、格子緩和SiGe層14が形成される。符号20はドライ酸化により酸化されたSi酸化層である。このドライ酸化では格子緩和SiGe層14は、厚さが20nmになり、Geが濃縮されてGe組成が増大し、それに伴い格子緩和する。この工程によりGe組成は0.3になる。また、このドライ酸化によりGe及び酸素を含有する層17は、より酸化が強固になりGe酸化物及びSi酸化物の混合酸化物であるGe酸化物含有層5となる。

## [0067]

次に、 $SiO_2$  層 20 をフッ化アンモニウム溶液で除去する。次に、UHV-CVD或いは LP-CVD法により基板温度 650 にて、格子緩和  $Si_{0...7}$  Ge  $_{0...3}$  層 14 上に歪 Si 層をエピタキシャル成長する。こうして十分に歪のかかった転位等のダメージのない良好なチャネル層を形成できる。

#### [0068]

この後の工程は、通常のSOI - MOSFET製造プロセスに従って、ゲート絶縁層、ゲート電極、ソース領域及びドレイン領域を形成して、図1に示す電界効果トランジスタを 形成する。

### [0069]

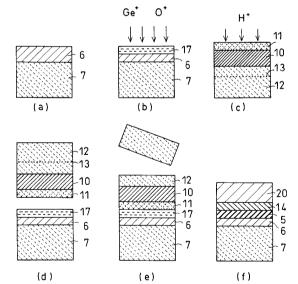

次に、図5を用いて第1の実施形態にかかる電界効果トランジスタの別の製造方法を説明する。

## [0070]

先ず、図 5 (a)に示すように、Si基板 7 上にSiO $_2$  絶縁層 6、SOI層 1 8 を具備するSOI基板を準備する。このSOI基板を熱酸化してSOI層 1 8 の厚さを 5 0 nmにする。この酸化方法は、ウェットでもドライでもかまわない。

### [0071]

次に、図 5 ( b )に示すように、 G e イオンを 5 0 k e V の注入エネルギー、 1 . 5 x 1 0  $^{1-6}$  c m  $^{-2}$  のドーズ量でイオン注入する。引き続き、酸素イオンを 3 5 k e V の注入エネルギー、 1 . 0 x 1 0  $^{1-7}$  c m  $^{-2}$  のドーズ量でイオン注入する。こうして S i 層中に G e 及び酸素を含有する領域 1 7 を形成する。これらのイオン注入後、酸素雰囲気中で 7 0 0 、 3 時間熱処理し、さらに 1 0 0 0 にて1分間 R T A 処理を行い S O I 層 1 8 に生じたダメージを除去する。次に、表面の酸化層をフッ化アンモニウム溶液で剥離する

### [0072]

### [0073]

次に、図5(d)に示すように、基板温度1050 でドライ酸化する。このドライ酸化により基板表面から酸化が行われ、格子緩和SiGe層14が形成される。符号20はドライ酸化により酸化されたSi酸化層である。このドライ酸化では格子緩和SiGe層14は、厚さが20nmになり、Geが濃縮されてGe組成が増大し、それに伴い格子緩和する。この工程によりGe組成は0.3になる。また、このドライ酸化によりGe及び酸素を含有する層17は、より酸化が強固になりGe酸化物及びSi酸化物の混合酸化物であるGe酸化物含有層5となる。

## [0074]

50

20

30

50

次に、 $SiO_2$ 層20をフッ化アンモニウム溶液で除去する。次に、UHV-CVD或いは LP-CVD法により基板温度650 にて、格子緩和 $Si_0$  7  $Ge_0$  8 層14上に歪Si 層をエピタキシャル成長する。こうして十分に歪のかかった転位等のダメージのない良好なチャネル層を形成できる。

### [0075]

この後の工程は、通常のSOI-MOSFET製造プロセスに従って、ゲート絶縁層、ゲート電極、ソース領域及びドレイン領域を形成して、図1に示す電界効果トランジスタを 形成する。

### [0076]

次に、図6を用いて第2の実施形態にかかる電界効果トランジスタの製造方法を説明する

#### [0077]

### [0078]

次に、図6(b)に示すように、700 でのウェット酸化することによりSiキャップ層 11 と第 2 の $Si_{0...9}$  G  $e_{0...1}$  層 15 の全て及びSi 中間層 16 の一部を酸化する。このウェット酸化により、厚さ 250 nmの絶縁層 9 中に厚さ約 40 nmの 6 e 酸化物とSi 酸化物の混合酸化物である6 e 酸化物含有層 5 を形成する。符号 6 及び 6 'は純粋な5i 0 0 である。

## [0079]

次に、水素イオンを 1 0 0 k e V の注入エネルギー、  $5 \times 1$  0  $^{1}$  6 c m  $^{-2}$  のドーズ量でイオン注入する。このイオン注入で、 5 i O  $_2$  層 6 の表面から深さ約 6 5 0 n m の領域に格子欠陥が高密度に形成されたマイクロクラック領域 1 3 を形成する。

### [0080]

次に、図 6 (d)に示すように、基板をひっくり返して SiO $_2$ 層 6 の表面を別の Si基板 7 に常温にて張り合わせる。

### [0081]

次に、図6(e)に示すように、600 で3時間熱処理すると、マイクロクラック領域13でウェハーが剥離する。次に、剥離面をCMPにて平坦化する。

### [0082]

次に、図6(f)に示すように、基板温度1050 でドライ酸化する。このドライ酸化により基板表面から酸化が行われ、格子緩和SiGe層14が形成される。符号20はドライ酸化により酸化されたSi酸化層である。このドライ酸化では格子緩和SiGe層14は、厚さが20nmになり、Geが濃縮されてGe組成が増大し、それに伴い格子緩和する。この工程によりGe組成は0.3になる。

### [0083]

次に、 $SiO_2$ 層20をフッ化アンモニウム溶液で除去する。次に、UHV-CVD或い 4 は LP-CVD法により基板温度650 にて、格子緩和 $Si_0$ .7  $Ge_0$ .3 層14上 に歪Si 層をエピタキシャル成長する。こうして十分に歪のかかった転位等のダメージの ない良好なチャネル層を形成できる。

## [0084]

この後の工程は、通常のSOI-MOSFET製造プロセスに従って、ゲート絶縁層、ゲート電極、ソース領域及びドレイン領域を形成して、図 2 に示す電界効果トランジスタを形成する。

## [0085]

## 【発明の効果】

低転位密度で格子緩和SiGe層が形成できるので、この上に歪量の大きな歪Si層を形

成できる。その結果、信頼性が高く、高速でかつ低消費電力の歪SOI-MOSFETを 実現できる。

### 【図面の簡単な説明】

- 【図1】 本発明の第1の実施形態にかかる電界効果トランジスタの断面図。

- 【図2】 本発明の第2の実施形態にかかる電界効果トランジスタの断面図。

- 【図3】 本発明の第1の実施形態にかかる電界効果トランジスタの製造工程を説明する主要工程における断面図。

- 【図4】 本発明の第1の実施形態にかかる電界効果トランジスタの製造工程を説明する主要工程における断面図。

- 【図5】 本発明の第1の実施形態にかかる電界効果トランジスタの製造工程を説明する 1 主要工程における断面図。

- 【図6】 本発明の第2の実施形態にかかる電界効果トランジスタの製造工程を説明する主要工程における断面図。

- 【図7】 絶縁層上に厚さ90nmの $Si_{0...9}Ge_{0...1}$ 層を形成し、これを酸化によって厚さ30nmの $Si_{0...7}Ge_{0...3}$ 層にした場合の絶縁層とSiGe層との界面での滑りによって生じる緩和率の酸化温度との関係を示すグラフ。

- 【図8】 SiGeのGe組成と軟化温度との関係を示すグラフ。

- 【図9】 従来の電界効果トランジスタの断面図。

### 【符号の説明】

- 1・・・ゲート電極

- 2・・・ゲート絶縁層

- 3 · · · 歪 S i

- 4・・・格子緩和SiGe層

- 5・・・Ge酸化物を含有するSiOっ層

- 6、6'・・・Si酸化層

- 7・・・Si基板

- 8・・・ソース領域及びドレイン領域

- 9・・・絶縁層

- 10···SiGe層

- 11・・・Siキャップ層

- 1 2 ・・・支持基板

- 13・・・マイクロクラック

- 14・・・格子緩和SiGe層

- 15···SiGe層

- 16・・・Si中間層

- 17・・・イオン注入領域

- 18・・・SOI層

20

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

## フロントページの続き

(51) Int.CI.7

FΙ

H 0 1 L 21/76 R

(56)参考文献 特開2001-094082(JP,A)

特開昭62-051240(JP,A)

特開平07-153685(JP,A)

特開平08-064675(JP,A)

特開2000-012860(JP,A)

特開2002-076347(JP,A)

特開2001-148473(JP,A)

特開平09-321307(JP,A)

特開平10-209453(JP,A)

(58)調査した分野(Int.CI.<sup>7</sup>, DB名)

H01L 21/20

H01L 21/336

H01L 21/76

H01L 27/12

H01L 29/786