# (19) 国家知识产权局

# (12) 发明专利

(51) Int.CI.

**H04L** 12/40 (2006.01)

审查员 赵静

(10)授权公告号 CN 111526077 B (45)授权公告日 2023.06.30

(21)申请号 202010073120.X

(22)申请日 2020.01.21

(65) 同一申请的已公布的文献号 申请公布号 CN 111526077 A

(43) 申请公布日 2020.08.11

(30)优先权数据

19155260.3 2019.02.04 EP

(73) 专利权人 恩智浦有限公司 地址 荷兰埃因霍温高科技园区60邮编: 5656 AG

(72) 发明人 克莱门斯 • G • J • 德哈斯 马西亚斯 • 伯特德 • 穆斯

(74) 专利代理机构 中科专利商标代理有限责任 公司 11021

专利代理师 倪斌

权利要求书2页 说明书17页 附图8页

## (54) 发明名称

控制器局域网(CAN)、CAN装置和其方法

## (57)摘要

描述了一种控制器局域网CAN装置,包括:CAN发射器,连接到CAN装置的两个CAN总线端;接收器电路,可操作地耦合到CAN装置的两个CAN总线端;以及控制器,控制器连接到CAN发射器。控制器被配置成:确定CAN装置是作为发射器节点操作还是作为接收器节点操作;检测CAN装置从显性状态到隐性状态的转变;并且响应于检测到所述CAN装置从所述显性状态到所述隐性状态的转变以及确定CAN装置是作为发射器节点操作还是作为接收器节点操作两者,在连接到CAN装置的CAN总线上的差分驱动器电压减小为预定义电压的同时将CAN发射器的输出阻抗控制为处于阻抗值范围内。

CN 111526077 B

1.一种控制器局域网CAN装置(400),其特征在于,所述CAN装置(400)包括:

CAN发射器,所述CAN发射器连接到所述CAN装置(400)的两个CAN总线端;

接收器电路(450),所述接收器电路(450)耦合到所述CAN装置(400)的所述两个CAN总线端;以及

控制器,所述控制器连接到所述CAN发射器,其中所述控制器被配置成:

确定所述CAN装置(400)是作为发射器节点操作还是作为接收器节点操作;

检测所述CAN装置(400)从显性状态到隐性状态的转变:并且

响应于检测到所述CAN装置(400)从所述显性状态到所述隐性状态的转变以及所述确定所述CAN装置(400)是作为发射器节点操作还是作为接收器节点操作两者,在连接到所述CAN装置(400)的CAN总线(104,304,404)上的差分驱动器电压减小为预定义电压的同时将所述CAN发射器的输出阻抗控制到处于所述显性状态下的阻抗值范围内。

- 2.根据权利要求1所述的CAN装置(400),其特征在于,所述控制器是阻抗控制器(432), 并且所述发射器是阻抗桥(430)。

- 3.根据权利要求2所述的CAN装置(400),其特征在于,连接到所述CAN发射器的所述阻抗控制器(432)被配置成当所述CAN装置作为发射器节点操作时提供以前馈方式将所述阻抗桥(430)的所述输出阻抗控制为处于第一预定义阻抗值范围内的控制,并且被配置成当所述CAN装置作为接收器节点操作时提供将所述阻抗桥(430)的所述输出阻抗控制为处于第二预定义阻抗值范围内的控制。

- 4.根据权利要求2或权利要求3所述的CAN装置(400),其特征在于,所述阻抗桥(430)包括两个臂,并且其中所述两个臂中的每个臂包括串联连接在公共电压电源轨(411)与公共接地轨(413)之间并且连接到所述两个CAN总线端中的每个CAN总线端的可调拉电路(415)和可调推电路(410)。

- 5.根据权利要求1-3中任一项所述的CAN装置(400),其特征在于,所述控制器被另外配置成:

在所述CAN总线(104,304,404)上的所述差分驱动器电压保持处于预定义电压电平的同时,将所述CAN发射器的所述输出阻抗增加为处于所述CAN总线(104,304,404)的特性阻抗的范围的阈值内;并且

随后,在所述CAN总线(104,304,404)上的所述差分驱动器电压保持处于所述预定义电压电平的同时,将所述CAN发射器的所述输出阻抗从所述CAN总线(104,304,404)的所述特性阻抗增加为高欧姆值。

- 6.根据权利要求1-3中任一项所述的CAN装置(400),其特征在于,所述控制器被另外配置成在数据采样点之前,在所述CAN总线(104,304,404)上的差分驱动器电压保持处于预定义电压电平的同时,将所述CAN发射器的所述输出阻抗增加为处于所述CAN总线(104,304,404)的特性阻抗的阻抗值范围内。

- 7.根据权利要求1-3中任一项所述的CAN装置(400),其特征在于,另外包括时间窗口滤波器电路(460),所述时间窗口滤波器电路(460)耦合到所述接收器电路(450)和所述控制器并且被配置成确定所述CAN总线电压是否在一段时间内高于阈值,并且响应于此而向所述控制器提供所述CAN装置作为接收器节点操作的指示。

- 8.根据权利要求7所述的CAN装置,其特征在于,所述时间窗口滤波器电路(460)被另外

配置成过滤来自所述接收器电路(450)的接收数据信号(455)的噪声。

9.一种用于在控制器局域网CAN装置(400)中进行振铃抑制的方法,其特征在于,所述方法包括:

确定所述CAN装置(400)是作为发射器节点操作还是作为接收器节点操作;

检测(1005)所述CAN装置从显性状态到隐性状态的转变;以及

响应于检测到所述CAN装置(400)从所述显性状态到所述隐性状态的转变以及所述确定所述CAN装置(400)是作为发射器节点操作还是作为接收器节点操作两者,在连接到所述CAN装置(400)的CAN总线(104,304,404)上的差分驱动器电压减小为预定义电压的同时将CAN发射器的输出阻抗控制(804)为处于所述显性状态下的阻抗值范围内。

10.一种控制器局域网CAN,其特征在于,包括根据前述权利要求1到8中任一项所述的 CAN装置(400)。

# 控制器局域网(CAN)、CAN装置和其方法

#### 技术领域

[0001] 本发明的领域涉及一种控制器局域网(CAN)、一种CAN装置和一种用于振铃抑制例如以提高较慢的CAN FD波特率的方法。具体地说,本发明的领域涉及一种具有可以用于抑制振铃的前馈和反馈阻抗控制的CAN装置的收发器。

## 背景技术

[0002] 控制器局域网 (CAN) 总线是一种连接网络中的一个或多个节点并且通常用于汽车和工业自动化应用中的多主机串行总线。CAN总线的使用受各种ISO标准约束,所述标准例如针对CAN协议的ISO11898-1、针对高速CAN物理层的ISO 11898-2和针对低速或容错CAN物理层的ISO 11898-3。当网络拓扑以理想方式端接时,CAN总线在传统CAN的情况下能够支持高达1Mb/s的比特率,并且在CAN灵活数据速率 (CAN FD) 的情况下能够支持高达8Mb/s的比特率。

[0003] 只有在网络的端节点处存在合适的终端电阻(120欧姆),并且通过短截线(stub)连接到总线的中间节点的长度足够短时,才能满足理论速度。终端存在的目的是防止总线上产生可能使总线上的信号失真或损害其完整性的反射。离终端电阻器最远的节点在所述节点之一进行传输时可能引起信号反射,所述信号反射可能在总线上引起振铃。这种"振铃"可能降低总线可以正确操作的最大数据速率。传统上,如总线电缆的长度等其它因素还可能将数据速率限制于比振铃会成为问题的速度低的速度。然而,CAN总线协议的进步(例如,CAN总线灵活数据速率(CAN FD))已经将可能的数据速率提高到振铃变得有影响且有问题的点。

[0004] 一些已知的技术已经提出了前馈振铃抑制概念。然而,前馈振铃抑制概念的缺点是在仅用一个装置支持所有CAN FD波特率与在较低的CAN FD波特率(≤2Mbps)下实现最佳振铃抑制性能之间达到平衡。前馈概念对CAN总线上的信号的显性到隐性转变具有最快的响应时间,并且用于支持最高的CAN FD波特率和错误帧检测。前馈概念仅具有一个振铃抑制装置,所述振铃抑制装置在数据阶段传输期间活跃。由于这种行为,设计不良的网络拓扑(例如,引起冲突反射的缆线长度相等的区段)存在潜在的性能代价。单个发射器无法将总线驱动到足以有效抵消整个拓扑上的这些冲突信号反射的低欧姆状态。

[0005] 一些已知的技术(例如,US 8,593,202)已经提出了反馈振铃抑制概念。然而,振铃抑制电路可能由于CAN总线上的干扰而被无意触发,从而导致CAN数据通信破坏。由于反馈概念的电抗性质,对显性到隐性转变的响应时间较慢,由此限制最大波特率(≤2Mbps),并且显性到隐性转变需要振铃抑制电路具有固定定时特性。

#### 发明内容

[0006] 根据本发明的一个方面,提供了一种控制器局域网(CAN)、一种CAN装置和一种用于抑制振铃的方法,所述CAN装置(400)包括:

[0007] CAN发射器,所述CAN发射器连接到所述CAN装置(400)的两个CAN总线端:

[0008] 接收器电路(450),所述接收器电路(450)可操作地耦合到所述CAN装置(400)的所述两个CAN总线端;以及

[0009] 控制器,所述控制器连接到所述CAN发射器,其中所述控制器被配置成:

[0010] 确定所述CAN装置(400)是作为发射器节点操作还是作为接

[0011] 收器节点操作;

[0012] 检测所述CAN装置(400)从显性状态到隐性状态的转变;并

[0013] 目

[0014] 响应于检测到所述CAN装置(400)从所述显性状态到所述隐性状态的转变以及所述确定所述CAN装置(400)是作为发射器节点操作还是作为接收器节点操作两者,在连接到所述CAN装置(400)的CAN总线(104,304,404)上的差分驱动器电压减小为预定义电压的同时将所述CAN发射器的输出阻抗控制到处于所述显性状态下的阻抗值范围内。

[0015] 根据一个或多个实施例,所述控制器是阻抗控制器(432),并且所述发射器是阻抗桥(430)。

[0016] 根据一个或多个实施例,连接到所述CAN发射器的所述阻抗控制器(432)被配置成当所述CAN装置作为发射器节点操作时提供以前馈方式将所述阻抗桥(430)的所述输出阻抗控制为处于第一预定义阻抗值范围内的控制,并且被配置成当所述CAN装置作为接收器节点操作时提供将所述阻抗桥(430)的所述输出阻抗控制为处于第二预定义阻抗值范围内的控制。

[0017] 根据一个或多个实施例,所述阻抗桥(430)包括两个臂,并且其中所述两个臂中的每个臂包括串联连接在公共电压电源轨(411)与公共接地轨(413)之间并且连接到所述两个CAN总线端中的每个CAN总线端的可调拉电路和可调推电路。

[0018] 根据一个或多个实施例,所述控制器被另外配置成:

[0019] 在所述CAN总线(104,304,404)上的所述差分驱动器电压保持处于预定义电压电平的同时,将所述CAN发射器的所述输出阻抗增加为处于所述CAN总线(104,304,404)的特性阻抗的范围的阈值内;并且

[0020] 随后,在所述CAN总线(104,304,404)上的所述差分驱动器电压保持处于所述预定义电压电平的同时,将所述CAN发射器的所述输出阻抗从所述CAN总线(104,304,404)的所述特性阻抗增加为高欧姆值。

[0021] 根据一个或多个实施例,所述控制器被另外配置成在数据采样点之前,在所述CAN总线(104,304,404)上的差分驱动器电压保持处于所述预定义电压电平的同时,将所述CAN发射器的所述输出阻抗增加为处于所述CAN总线(104,304,404)的特性阻抗的阻抗值范围内。

[0022] 根据一个或多个实施例,另外包括时间窗口滤波器电路(460),所述时间窗口滤波器电路(460)可操作地耦合到所述接收器电路(450)和所述控制器并且被配置成确定所述CAN总线电压是否在一段时间内高于阈值,并且响应于此而向所述控制器提供所述CAN装置作为接收器节点操作的指示。

[0023] 根据一个或多个实施例,所述时间窗口滤波器电路(460)被另外配置成过滤来自所述接收器电路(450)的接收数据信号(455)的噪声。

[0024] 根据一个或多个实施例,所述时间窗口滤波器电路(460)是耦合到位定时逻辑电

路(765)的被配置成拒绝所述接收器电路的除了针对显性到隐性转变的输出之外的输出的窗口滤波器(760)。

[0025] 根据一个或多个实施例,CAN装置另外包括以下中的至少一个:

[0026] 波特率检测器电路 (910),所述波特率检测器电路 (910)被配置成测量所述CAN装置 (400)采用的比特率并且向所述控制器提供所测量的比特率;

[0027] 串行-并行接口SPI,所述SPI被配置成向所述控制器提供预定的所采用比特率。

[0028] 根据本发明的另一个方面,提供一种用于在控制器局域网CAN装置(400)中进行振铃抑制的方法,所述方法包括:

[0029] 确定所述CAN装置(400)是作为发射器节点操作还是作为接收器节点操作;

[0030] 检测(1005)所述CAN装置从显性状态到隐性状态的转变;以及

[0031] 响应于检测到所述CAN装置(400)从所述显性状态到所述隐性状态的转变以及所述确定所述CAN装置(400)是作为发射器节点操作还是作为接收器节点操作两者,在连接到所述CAN装置(400)的CAN总线(104,304,404)上的差分驱动器电压减小为预定义电压的同时将所述CAN发射器的输出阻抗控制(804)为处于阻抗值范围内。

[0032] 根据本发明的另一个方面,提供一种控制器局域网CAN,包括CAN装置(400)。

[0033] 本发明的这些和其它方面将根据下文描述的实施例而变得显而易见,并且将参考所述实施例对所述方面进行阐述。

## 附图说明

[0034] 将参考附图仅通过举例描述本发明的另外的细节、方面和实施例。在附图中,相似的附图标记用于标识相似或功能上类似的要素。附图中的要素是为了简单和清楚起见而示出的并且不一定按比例绘制。

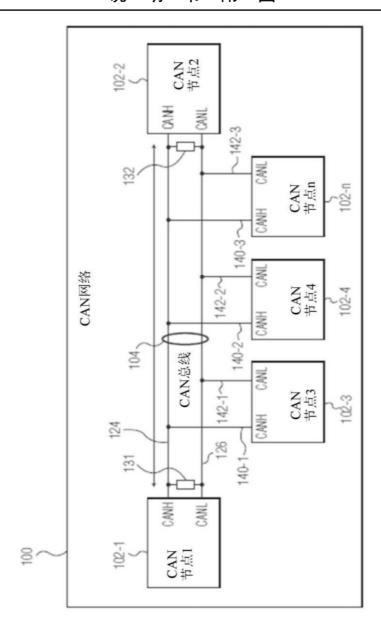

[0035] 图1示意性地示出了根据本发明的例子的具有多个节点的CAN总线网络的例子的框图。

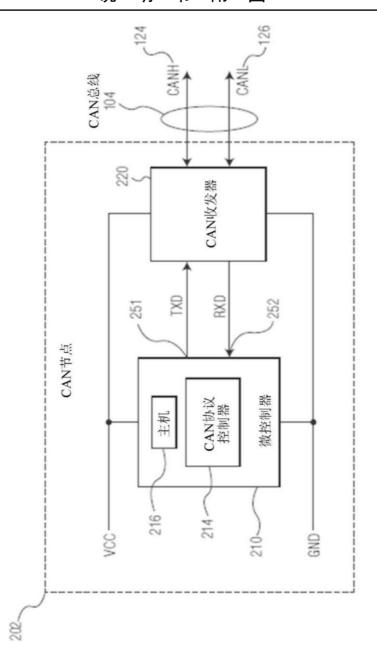

[0036] 图2示意性地示出了根据本发明的一些例子的CAN装置的简化概览框图。

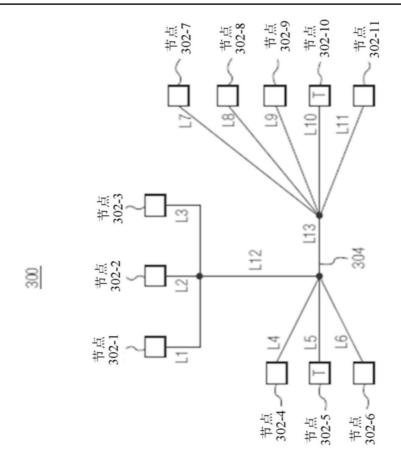

[0037] 图3示意性地示出了根据本发明的一些例子的具有多个节点的CAN总线网络的例子的框图。

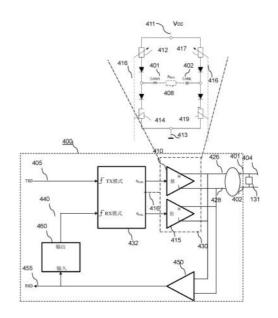

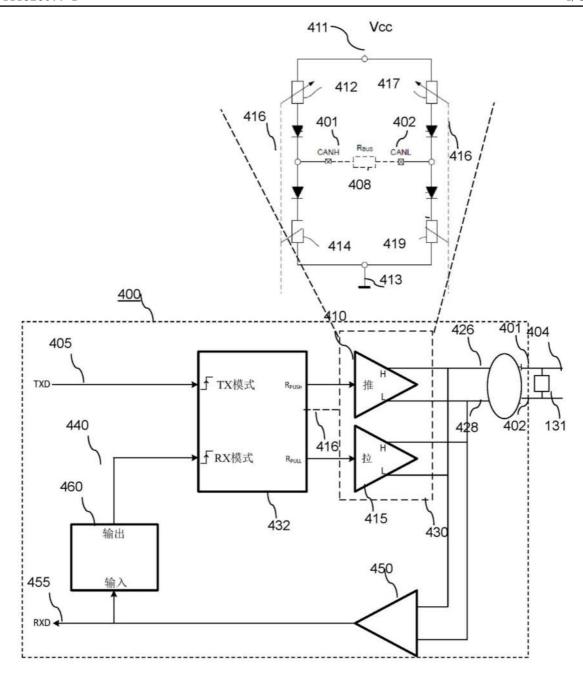

[0038] 图4示出了根据本发明的一些例子的具有前馈反馈组合架构的CAN装置的第一例子的简化框图。

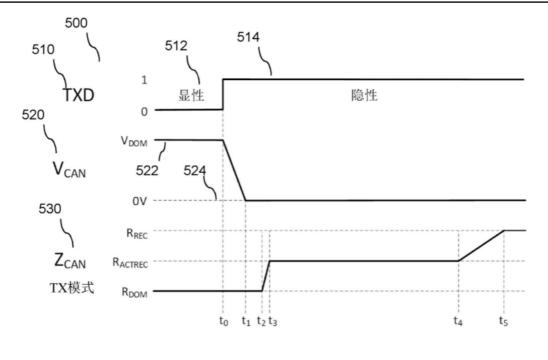

[0039] 图5示出了理想化的发射节点显性到隐性操作的例子。

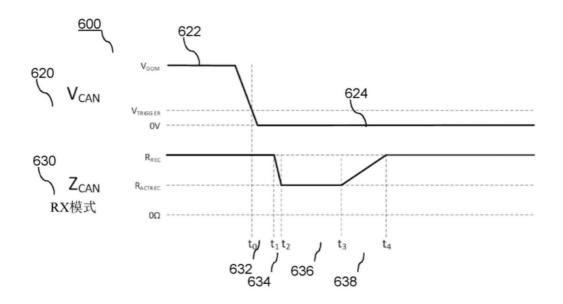

[0040] 图6示出了根据本发明的一些例子的检测CAN装置在显性到隐性操作中作为接收节点操作的例子。

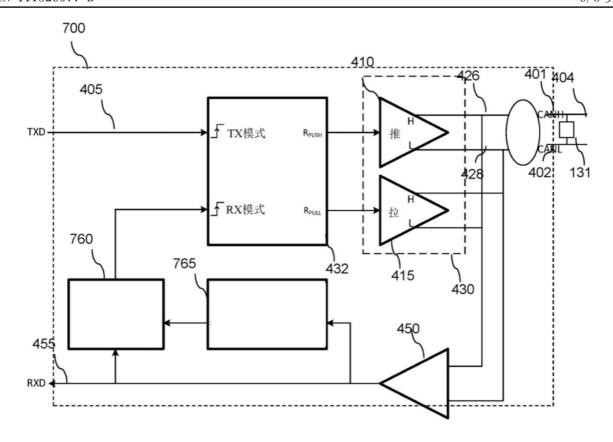

[0041] 图7示出了根据本发明的一些例子的具有窗口滤波的反馈概念。

[0042] 图8示出了根据本发明的一些例子的图7的具有窗口滤波的示例反馈概念的定时图。

[0043] 图9示出了根据本发明一些例子的波特率检测器框图。

[0044] 图10示出了根据本发明的一些例子的用于抑制CAN系统中的振铃的示例方法的流程图。

# 具体实施方式

[0045] 最近提出的CAN系统采用反馈架构来抑制振铃。这种反馈架构的一个问题在于,从系统的角度来看,这种反馈架构的可预测性较低,并且所述架构必须依赖于滤波以防止误触发。根据本发明的一些示例实施例,描述了一种组合前馈概念和反馈概念两者的方法,所述方法减轻或防止误触发。以此方式,CAN系统可以例如在较低的CAN和CAN FD波特率下表现出两种概念的最佳振铃抑制性能。

根据本发明的一些示例实施例,提供了一种控制器局域网CAN装置,所述CAN装置 包括:发射器(例如,阻抗桥),所述发射器连接到所述CAN装置的两个CAN总线端:接收器电 路,所述接收器电路可操作地耦合到所述CAN装置的所述两个CAN总线端;以及控制器(例 如,阻抗控制器),所述控制器连接到所述发射器。所述控制器被配置成:确定所述CAN装置 是作为发射器节点操作还是作为接收器节点操作;检测所述CAN装置从显性状态到隐性状 态的转变;以及响应于检测到所述CAN装置从所述显性状态到所述隐性状态的转变和所述 确定所述CAN装置是作为发射器节点操作还是作为接收器节点操作两者,在连接到所述CAN 装置的CAN总线上的差分驱动器电压下降为第二预定义电压的同时,将所述发射器的输出 阻抗控制为处于所述显性状态下的阻抗值的第一预定义范围内。由于在到第二预定义电压 的转变期间,驱动器输出阻抗相对于显性状态下的阻抗值的第一预定义范围保持恒定,因 此进入网络的能量梯级被最小化,并且这使反射较小。以此方式,通过控制器根据CAN装置 作为发射器或接收器操作对发射器进行配置,发明人已经认识到,CAN装置能够得益于通过 接收器进行的前馈振铃抑制方法和反馈振铃抑制方法两者的优点。具有还以反馈振铃抑制 方式操作的CAN装置的益处在于,在大型网络(例如,其中节点之间的距离较大且存在大量 节点)中,这些CAN装置全都并行工作以抑制振铃。所述CAN装置与仅具有前馈振铃抑制的已 知CAN装置(其中仅一个发射CAN装置能够在CAN数据阶段期间活跃执行振铃抑制)形成对 比,并且节点之间的最长距离引起比活跃抑制时间更长的传播延迟(通常为5纳秒/米)。此 处,振铃抑制变得不太有效。因此,本发明的例子结合了这样一种方法,所述方法得益于前 馈振铃抑制的优点中的一些优点,但是因为网络中的每个节点都能够参与振铃抑制而另外 引入了反馈振铃抑制。

[0047] 根据本发明的一些例子,所述控制器可以是阻抗控制器,并且所述发射器可以是阻抗桥。根据本发明的一些例子,所述阻抗控制器可以连接到所述CAN发射器并且被配置成当所述CAN装置作为发射器节点操作时提供以前馈方式将所述阻抗桥的所述输出阻抗控制为处于所述第一预定义范围内的控制,并且被配置成当所述CAN装置作为接收器节点操作时提供将所述阻抗桥(430)的所述输出阻抗控制为处于第二预定义范围内的控制。根据本发明的一些例子,所述阻抗桥可以包括两个臂,并且其中所述两个臂中的每个臂可以包括串联连接在公共电压电源轨与公共接地轨之间并且连接到所述两个CAN总线端中的每个CAN总线端的可调拉电路和可调推电路。根据本发明的一些例子,所述控制器可以被另外配置成:在所述CAN总线上的所述差分驱动器电压保持处于预定义电压电平的同时,将所述CAN发射器的所述输出阻抗增加为处于所述CAN总线的特性阻抗的范围的阈值内,例如,所述CAN总线的特性阻抗的±10%,并且优选地基本上等于所述CAN总线的特性阻抗;并且随后,在所述CAN总线上的所述差分驱动器电压保持处于所述预定义电压电平的同时,将所述CAN发射器的所述输出阻抗从所述CAN总线的所述特性阻抗增加为高欧姆值。根据本发明的

一些例子,所述控制器可以被另外配置成在数据采样点之前,在所述CAN总线上的差分驱动器电压保持处于所述预定义电压电平的同时,将所述CAN发射器的所述输出阻抗增加为处于所述CAN总线的特性阻抗的所述第一预定义阻抗值范围内。根据本发明的一些例子,所述CAN装置可以包括时间窗口滤波器电路,所述时间窗口滤波器电路可操作地耦合到所述接收器电路和所述控制器并且被配置成确定所述CAN总线电压是否在一段时间内高于阈值,并且响应于此而向所述控制器提供所述CAN装置作为接收器节点操作的指示。根据本发明的一些例子,所述时间窗口滤波器电路可以被另外配置成从来自所述接收器电路的接收数据信号过滤噪声。根据本发明的一些例子,所述时间窗口滤波器电路可以是耦合到位定时逻辑电路并且被配置成拒绝所述接收器电路的除了针对显性到隐性转变的输出之外的输出的窗口逻辑电路。根据本发明的一些例子,所述CAN装置可以另外包括以下中的至少一个:波特率检测器电路,所述波特率检测器电路被配置成测量所述CAN装置采用的比特率并且向所述控制器提供所测量的比特率;以及串行-并行接口SPI,所述SPI被配置成向所述控制器提供预定的所采用比特率。

[0048] 现在参考图1,示出了根据本申请的例子的包括通过CAN总线耦合到一起的多个节点的网络100的说明性例子。网络100包括通过第一节点102-1、第二节点102-2、第三节点102-3、例如第(n-1)节点102-4和第n节点102-n例示的多个节点。节点102-1到102-n耦合到一起以实现通过总线110进行的通信。在本文中,所述总线被例示为CAN总线104,所述CAN总线104以包括CANH导线124和CANL导线126的双导线总线的形式实施。在这种情况下,导线124和126形成具有标称电缆阻抗的单条双绞线电缆。节点102-1到102-5中的每个节点通过抽头线耦合到CANH导线124和CANL导线126。在此例子中,标称电缆阻抗为120 $\Omega$ ,所述阻抗在CAN总线的一些汽车应用中具有代表性。然而,应当理解的是,实施例适用于其它线路阻抗,并且本申请不应被理解为限于特定的标称电缆阻抗。还应当理解的是,线路的确切阻抗可能受如所使用的电缆和/或隔离材料等物理因素的影响。虽然线路阻抗被假设为120 $\Omega$ ,但实际的线路阻抗可以围绕这个值变化并且可以被视为约120 $\Omega$ 。类似地,终端电阻器的确切值可以例如由于实际实施方案而发生变化。

[0049] 第一节点102-1是CAN总线104的第一端节点,并且具有对应于标称电缆阻抗(如 $120\,\Omega$ )的终端电阻 $R_{Term}$  131。第二节点102-2是第二端节点,并且具有对应于标称电缆阻抗(如 $120\,\Omega$ )的终端电阻 $R_{Term}$ 132。第三节点、第(n-1) 节点和第n节点是中间节点并且通过短截线140-1、142-1、140-2、142-2和140-3、142-3耦合到CAN总线104。在一些系统中,可以使这种中间节点不被端接或者任选地应用有处于千欧姆范围内的高欧姆终端。在一些例子中,虽然高欧姆终端可以在电缆的这些准开放端处提供有限的振铃抑制,但是由于与标称电缆阻抗的偏差,有效性非常有限。

[0050] 所述节点中的每个节点可以耦合到如传感器或微控制器等另外的电路系统,所述另外的电路系统可以被配置成使用CAN总线104与其它节点中的一个或多个节点通信。

[0051] 技术人员应当了解,在一些情况下,电路或组件的集成水平可以取决于实施方案。 [0052] 图2更详细地示出了节点202(例如,图1的节点102-1到102-n之一)的框图。节点 202通过图1的短截线140-1和图1的短截线142-1耦合到CAN总线104,所述短截线140-1耦合 到CANH导线124,所述短截线142-1耦合到CANL导线126。图1的短截线140-1、142-1耦合到节 点202的CAN总线收发器220。应当理解的是,在不需要短截线的情况下,例如对于端节点, CAN总线收发器将直接耦合到导线124和126。CAN总线收发器220通过发射数据连接(TXD)(或TXD引脚)251和接收数据连接(RXD)(或RXD引脚)252耦合到CAN控制器214。

[0053] CAN控制器214可以形成节点202的微控制器210的一部分。

[0054] 微控制器210可以确定要在总线上传输的消息,并且将这些消息提供给CAN控制器214。微处理器可以从CAN控制器214接收来自总线的消息并且解译所述消息。微控制器210可以另外连接到如传感器或致动器等其它实体,并在所述其它实体与CAN总线104之间提供接口。

[0055] CAN控制器214可以(通过CAN总线收发器220)从CAN总线104接收位,并且将所述位 重构为要由微控制器210解译的消息。CAN控制器214可以从微控制器210接收消息,并且通过CAN总线收发器220将所述消息以串列位的方式提供给总线。

[0056] CAN总线收发器220可以将TXD引脚251上来自CAN控制器214的数字数据位转换成模拟总线信号。CAN总线收发器220可以另外将模拟总线信号转换成要通过RXD引脚252提供给CAN控制器214的数字位。

[0057] 网络100、200的实施方案可能受某些参数约束,以减少振铃并且保护在较高的数据速率下传送的数据的完整性。例如,CAN总线104可以具有可以实现最大数据速率的最大长度。在另一个例子中,可以使将中间节点102-1到102-5连接到CAN总线104的短截线140和142保持尽可能短以减少反射。在一种情况下,可以将CAN总线的最大长度限制为40m,并且将短截线的最大长度限制为小于0.3m,但是应当理解的是,这仅仅是举例。

[0058] 尽管存在这个要求,但是总线和短截线的长度可能受其它因素影响。例如,在例如汽车应用中,CAN总线网络的实施方案可能受车辆的形状和大小以及节点的位置的约束。短截线不可能总是如期望的那么短。此外,即使在短截线尽可能短的情况下,在较高的数据速率下仍可能发生振铃。

[0059] 未端接的短截线中的振铃可能破坏总线上的通信。对于数据速率更高的新协议 (例如,CAN FD)而言,这会成为更大的问题。解决振铃的一种方法是重新设计网络拓扑以改善终端,然而,这种方法耗时且成本高。

[0060] 因此,本申请的一些示例实施例提供了一种可以在现有网络拓扑上容易地实施的抑制振铃的方法。此外,实施例可以考虑实施这种抑制的速度,并且减轻振铃抑制电路中发生毛刺的可能性。

[0061] 基本上,最大总线长度由所选信号传递速率决定,或准确地说,与所选信号传递速率存在权衡关系。信号传递速率随传输距离增加而减小。虽然在最长的传输距离下,稳态损耗可能成为一个因素——限制信号传递速率的主要因素,但随着距离增加,使信号转变时间降级并引入符号间干扰(ISI)的电缆带宽限制也是在传输距离增加时降低可实现的信号传递速率的主要因素。对于CAN总线而言,信号传递速率还由以下决定:(i)系统的两个最远节点之间的总系统延迟(有时称为"向下和向后");以及(ii)进入和离开具有双绞线电缆的典型传播延迟(例如,5纳秒/米)的总线上的节点的延迟的总和。而且,由于电缆的阻抗和收发器的输入阻抗的存在,所以必须考虑信号幅度损耗。在严格的分析下,集肤效应、与其它电路系统的接近度、介电损耗和辐射损耗效应各自起到影响主要线路参数并使信号降级的作用。

[0062] 由于短截线未被端接,因此可能在短截线中产生信号反射,所述信号反射跨接收

器的输入阈值来回驱动信号电平,从而产生误差。位采样在位的端部附近发生。因此,为了提供充分的安全裕度,必须使CAN短截线中的所有信号反射在传播延迟部分之前或期间得到衰减。为了使反射最小化,短截线长度不应超过线路的临界长度的三分之一(1/3)。超出此短截线长度,许多变量开始起作用,因为短截线不再被视为集总元件/参数。所述短截线长度是短截线对传输线保持不可见的最大长度。总线线路的临界长度在信号通过线路的所谓"向下和向后"传播延迟等于信号的转变时间(上升或下降时间中的较大者)的时刻发生。例如,典型的CAN驱动器的转变时间可以为50纳秒,并且当考虑典型的双绞线传输线传播延迟为5纳秒/米时,一米距离的"向下和向后"延迟变为10纳秒/米。临界长度变为5m(50纳秒/10纳秒/米=5m),并且网络的最大未端接短截线长度为临界长度的1/3,或1²/3m(≈1.67m)。[0063] 本领域的技术人员应当立即理解,在传输速率增加的情况下,可能无法维持例如针对网络上的(较低)目标数据传输速率而开发的现有网络拓扑,除非采取另外的措施来抑制信号干扰并提高信号质量。

[0064] 图3示出了根据本申请的例子的包括通过CAN总线耦合到一起的多个节点的网络的示例性真实情况场景的框图300。网络包括节点"1"到节点"11"302-1到302-11,所述网络总体上示出了耦合到一起以实现通过CAN总线进行的通信的多个节点。在本文中,CAN总线和其短截线被示出为指示上述单条双绞线电缆的实线。如所示出的,节点"5"和节点"10"应被视为形成CAN总线的相应端节点。节点"5"和节点"10"中的每个节点具有根据标称电缆阻抗(如120  $\Omega$ )的终端电阻 $R_{Term}$ "T"。

[0065] 当例如离节点"5"和"10"处的终端电阻器更远(图3中指示了示例性短截线长度)的节点1、2、3、4、7、8或11之一开始发送数据时,网络中的反射将引起信号干扰。CAN FD控制器例如通常在位时间的70%内对总线进行采样。如果信号干扰的持续时间长于典型的采样时间,则可能捕获到错误的位信息,这会引起数据消息破坏。通过使用更长的位时间,可以避免这种信号干扰问题。然而,这有效地限制了网络的最大数据传输速率。当在例如500kb/s的传输速率下使用针对传统的CAN协议开发的网络拓扑时,由于短截线太长而引起的反射是主要的传输速率限制因素。所述反射也是最近的CAN FD协议的限制因素,所述最新的CAN FD协议指定的传输速率为1兆位/秒到5兆位/秒或甚至更高。

[0066] 另外,应当考虑的是,即使是在良好端接的网络中,由于高电容总线负载,也可能存在另外的主要传输速率限制因素。在大量节点连接到CAN总线网络的情况下,显性到隐性转变变得非常慢。在隐性状态下,发射器处于高欧姆状态。当每个连接节点向CAN总线添加例如最大100pF的电容并且CAN总线阻抗固定为 $60\Omega$ 时,在连接了十个节点的网络的情况下,显性到隐性转变将永不会快于约100纳秒。如果期望网络的传输速率为5兆位/秒或更高,则位时间为200纳秒或更短。

[0067] 当未端接的节点中的任何节点开始发送数据时,网络中的反射将引起信号干扰,所述信号干扰取决于相对于终端和电缆分支的物理位置。CAN FD控制器通常在接近位时间结束时对总线进行采样,并且如果信号干扰的持续时间较长,则可能捕获到错误的位信息。因此,由于节点具有变化的终端,所以可能产生引起信号降级的信号干扰,这可能导致数据消息破坏。通过使用较长的位时间,可以避免这种信号干扰问题,但是代价是有效限制网络的最大速度。

[0068] 使用更新的CAN FD协议,可以消除速度限制因素之一(即,最大电缆长度),并且可

以实现高于1兆位/秒的数据速率。然而,下一个限制因素是网络中由于短截线太长而导致的反射。反射是所使用且可用的电缆拓扑的纯粹性质,而不是较高速度的结果。因此,具有临界反射的拓扑相关时间段更接近于单个位的时间段,尤其是在较高的数据速率下。因此,这些较短的位的数据采样点现在处于危险中。汽车消费者需要其车辆的现有CAN网络拓扑(其允许的最大比特率为传统CAN的情况下的500kb/s)能够通过使用CAN FD技术达到2Mb/s或更高。

[0069] 本发明的例子通过提供组合前馈技术和反馈技术的架构来解决上述问题,如图4 所示。图4示出了CAN装置400(有时被称为CAN收发器)(例如,图2中描绘的CAN节点202)的第一例子的简化框图。根据示例实施例,CAN装置400包括根据本发明的例子的前馈反馈组合架构440。在图4中示出的示例CAN装置400中,例如采取阻抗桥430的形式的CAN发射器和例如采取阻抗控制器432的形式的控制器被配置成控制发射器的输出阻抗。在其它例子中,设想的是,CAN装置的前馈反馈组合架构440可以采用可替换的发射器和控制器设计。因此,下文解释有关阻抗桥430和阻抗控制器432的操作的描述是一个这种示例实施方案。

[0070] 通过(例如,基于从TXD路径接收到的发射数据连接(TXD)信号,简称TXD信号405)控制CAN装置400的阻抗桥430,可以独立于CAN总线404处的所驱动的差分输出电压调节CAN装置400的输出阻抗,即,阻抗桥430可以驱动CAN总线404,使得输出驱动器阻抗不受输出电压的影响。当然,这种情况仅在CAN总线404上存在单个活跃发射器时才有效。因此,可以通过受控的阻抗桥430减少或抑制CAN总线404处的信号反射/振铃。

[0071] 在图4描绘的实施例中,阻抗桥430连接到CANH端401和CANL端402,所述CANH端401和CANL端402进而分别耦合到抽头/短截线,如图1中示出的示例实施例中的短截线140或142,并且另外耦合到(图1中示出的示例实施例中的)CANH总线导线124和CANL总线导线126。阻抗桥430包括第一臂(leg)426(也称为CANH(侧)臂)和第二臂428(也称为CANL(侧)臂)。每个臂包括两个可控阻抗412、414,例如,可调电阻器,所述两个可控阻抗412、414具有可以例如由阻抗控制器432通过控制路径416动态调节的阻抗性质。在其它例子中,每个臂的可控阻抗可以是例如可调电容器和/或可调电感器等。在其它例子中,每个臂的阻抗性质可以由例如边缘检测器动态调节。在非理想的实施方案中,设想的是,阻抗控制器432可以定位在微控制器内部和/或CAN-FD控制器中。在一些例子中,还设想的是,阻抗桥430和接收器可以定位在单独的装置(例如,收发器)中。图4还示出了示例阻抗桥430的扩展电路,所述扩展电路突出了用于构造可调阻抗桥的一种方法。

[0072] 阻抗桥430的CANH臂包括在一些例子中可以连接在公共电压电源轨411,即 $V_{\rm CC}$ 与 CANH端401之间的"推"阻抗电路410 (例如,实施为至少一个推电阻器 $R_{\rm PUSH1}$  412) 和连接在 CANH端401与公共接地轨413之间的"拉"阻抗电路415 (例如,实施为至少一个拉电阻器  $R_{\rm PULL1}$ 414)。阻抗桥430的CANL臂包括连接在公共电压电源轨411与CANL端402之间的拉阻抗电路 (例如,实施为拉电阻器 $R_{\rm PULL2}$  417) 和连接在CANL端402与公共接地轨413之间的推阻抗电路 (例如,实施为推电阻器 $R_{\rm PULL2}$  617)。

[0073] 尽管在一些例子中,阻抗电路410、415可以被实施为电阻器,但是设想的是,在其它示例实施例中,阻抗电路410、415中的至少一个阻抗电路可以被实施为一个或多个晶体管(MOSFET晶体管或双极型晶体管)、一个或多个可调电容器、一个或多个可调电感器、或一个或多个可调电阻器、一个或多个电容器和/或一个或多个可调电感器的组合。在一些示例

实施例中,推电阻器 $R_{PUSH1}$  412和 $R_{PUSH2}$  419以及拉电阻器 $R_{PULL1}$ 414和 $R_{PULL2}$  417中的至少一个电阻器被实施为电阻器梯或其它可调电阻器网络,并且阻抗控制器432可以调节推电阻器  $R_{PUSH1}$  412和 $R_{PUSH2}$ 419以及拉电阻器 $R_{PULL1}$  414和 $R_{PULL2}$  417中的至少一个电阻器的电阻值(例如,通过控制电阻器梯或其它可调电阻器网络内的开关(例如,MOSFET晶体管或其它有源半导体装置)连接或绕过电阻器组件)。

[0074] 在一些例子中,臂可以相对于CANH端401和CANL端402具有对称电阻器配置。在一些例子中,CAN总线404可以具有由等效总线阻抗 $R_{BUS}$ 表示的负载阻抗。通常,根据上述典型的120 $\Omega$ 标称电缆阻抗,总线阻抗 $R_{BUS}$ 408的阻抗为约60 $\Omega$ ,条件是CAN总线在每个端部处端接有终端电阻 $R_{Term}$ =120 $\Omega$ 。在一些实施例中,可以将二极管与阻抗电路410、415中的每个阻抗电路串联连接,以防止在公共电压电源轨411上存在高于供电电压电位的总线电压或者在公共接地轨413上存在低于接地电位的总线电压的情况下,反向电流从CAN总线流到公共电压电源轨411和公共接地轨413中。在一些示例实施例中,可以使用其它方案防止反向电流从CAN总线流到公共电压电源轨411和公共接地轨413中,例如,与公共电压电源轨411串联的二极管和与公共接地轨413串联的二极管。

[0075] 在一些示例实施例中,可调推电阻器 $R_{PUSH1}$  412和 $R_{PUSH2}$  419以及可调拉电阻器  $R_{PULL1}$  414和 $R_{PULL2}$  417的阻抗值可基于两个参数"x"和"y"动态调节。在一些示例实施例中,参数x的域可以包括值范围x=(0,1),其中x=(0,1)= {x  $\in \mathcal{R}$ ,0 < x < 1},并且参数y的域可以包括值范围y=(0,2],其中y=(0,2]= {y  $\in \mathcal{R}$ ,0 < y  $\leq$  2}。在一些示例实施例中,参数x和y可以彼此独立。在一些示例实施例中,推电阻器 $R_{PUSH1}$  412和 $R_{PUSH2}$  419的推阻抗值 $Z_{PUSH}$ 可以表示为:

$$[0076] Z_{PUSH} = \frac{R_f}{x \cdot y} (1)$$

[0077] 其中Rf表示参考电阻值。可调拉电阻器 $R_{PULL1}$  414和 $R_{PULL2}$  417的拉阻抗值 $Z_{PULL}$ 可以表示为:

[0078]

$$Z_{PULL} = \frac{R_f}{(1-x) \cdot y}$$

(2)

[0079] 阻抗桥430的总差分阻抗(其还是CAN装置400的驱动器阻抗 $Z_{CAN}$ )可以表示为:

[0080]

$$Z_{CAN} = 2 \cdot \frac{1}{\frac{1}{Z_{PUSH}} + \frac{1}{Z_{PULL}}}$$

(3)

$$[0081] Z_{CAN} = 2 \cdot \frac{R_f}{y} (4)$$

[0082] 阻抗桥430的总差分阻抗(其是CAN装置400的驱动器阻抗 $Z_{CAN}$ )可以被动态地调节为本文中由最低驱动器阻抗值 $Z_{CAN}=R_f$ 决定的低欧姆状态与本文中由 $Z_{CAN}=\infty$ 表示的高欧姆状态之间的任何阻抗值。 $R_f$ 是CAN装置400的最小驱动阻抗值。例如,最小驱动阻抗值可以是 $R_f=15\Omega$ 。应当注意的是,本文中通过 $Z_{CAN}=\infty$ 引用的高欧姆状态可以包括处于千欧姆或兆欧姆范围内的最大驱动阻抗值。与等效总线阻抗 $R_{RIS}$ 408相比,驱动器阻抗 $Z_{CAN}$ 需要处于高

欧姆状态,以允许差分总线阻抗在缓慢的位时间结束时再次达到例如60欧姆的标称值。因此,最大驱动阻抗与最小驱动阻抗的比率可以处于例如一千或更大的范围内。

[0083] 在一些示例实施例中,阻抗控制器432可以被实施为如微控制器等处理器。在一些示例实施例中,阻抗控制器包括信号边缘检测器。在一些示例实施例中,阻抗控制器432可以被配置成检测CAN装置400从显性状态到隐性状态的转变。响应于检测到CAN装置400从显性状态到隐性状态的转变,阻抗控制器432可以将阻抗桥430的输出阻抗(例如,在CANH端401与CANL端402之间测量的阻抗)控制为处于比显性状态下的阻抗值高或低的某一百分比内(例如,通过同时调节在此示例电路中的推电阻器R<sub>PUSH1</sub> 412和R<sub>PUSH2</sub> 419以及拉电阻器R<sub>PULL1</sub> 414和R<sub>PULL2</sub> 417的阻抗配置,使得在差分输出电压减小为预定义电压的同时,阻抗桥的输出阻抗处于比显性状态下的阻抗值高或低的某一百分比内)。基本与此同时,可以将CAN总线404上的差分驱动器电压(例如,在CANH端401与CANL端402之间测量的不同的电压)连接到CAN装置400,并且所述差分驱动器电压减小为预定义电压(例如,0V或其它适合的电压电平)。例如,可以在CAN总线上的差分驱动器电压减小到预定义电压的同时将CAN装置400的输出阻抗控制为显性状态下的阻抗值的±5%、±10%或处于显性状态下的阻抗值的其它适合的值范围内。在一些实施例中,在差分输出电压减小到预定义电压的同时,CAN装置400的输出阻抗被控制为处于固定阻抗。

[0084] 通过在差分驱动器电压的斜降期间将CAN装置400的输出阻抗控制为处于比显性状态下的阻抗值高或低的某一百分比内,在各种CAN总线拓扑和数据速度下,可以减少耗散到CAN网络中的能量,由此使CAN总线404上的反射较低。

[0085] 在一些例子中,阻抗控制器432可以通过监测在CAN装置400处从TXD路径(例如,从图2的微控制器210)接收到的TXD信号405来检测CAN装置400从显性状态到隐性状态的转变。例如,阻抗控制器可以通过标识TXD信号405的信号边缘来检测CAN装置400从显性状态到隐性状态的转变。活动的CAN装置400(即,处于显性状态的CAN装置400)将CAN总线波形驱动为"显性"状态,表示为TXD信号405的逻辑低电平(逻辑0)。不活动的CAN装置400(即,处于隐性状态的CAN装置400)从CAN总线移除其差分输出电压,表示为TXD信号405的逻辑高电平(逻辑1)。尽管描述了TXD信号的具体逻辑电平,但是在其它网络中,设想的是,可以使用其它信号逻辑电平。在一些实施例中,阻抗控制器432可以被配置成在连接到CAN装置400的CAN总线上的差分驱动器电压减小为预定义电压的同时控制阻抗桥430的可调推电阻器RPIERE 412和RPIERE 419以及可调拉电阻器RPIERE 414和RPIERE 417的电阻值。

[0086] 在示例实施例中,在TXD信号405的正/上升或负/下降信号边缘期间,阻抗控制器 432可以调节可调推电阻器 $R_{PUSH1}$  412和 $R_{PUSH2}$  419以及可调拉电阻器 $R_{PULL1}$  414和 $R_{PULL2}$  417中的一个或多个电阻器的电阻值。例如,在TXD信号405的显性(下降)边缘期间,阻抗控制器 432可以在使可调拉电阻器 $R_{PULL1}$  414和 $R_{PULL2}$  417的电阻值处于静态高欧姆状态的同时将可调推电阻器 $R_{PUSH1}$  412和 $R_{PUSH2}$  419的电阻值调节为处于比显性状态下的阻抗值高或低的某个百分比内。在另一个例子中,在TXD信号405的隐性(上升)边缘期间,阻抗控制器432可以分别以不同的斜率调节可调推电阻器 $R_{PUSH1}$  412和 $R_{PUSH2}$  419以及可调拉电阻器 $R_{PULL1}$  414和 $R_{PULL2}$  417中的每个电阻器的电阻值以便使阻抗桥430的整体阻抗保持处于比显性状态下的阻抗值高或低的阻抗值高或低的某个百分比内。

[0087] 在一些实施例中,阻抗控制器432被配置成在CAN总线404上的差分驱动器电压(例

如,在CANH端401与CANL端402之间测量的差分电压)保持处于预定义电压的同时增加CAN装 置400的输出阻抗(例如,在CANH端401与CANL端402之间测量的阻抗)。因为在CAN装置400的 输出阻抗增加的同时,CAN总线电压保持处于预定义电压(例如,OV),所以阻抗变化将不会 导致大量能量耗散到CAN网络中并且因此减少或防止CAN总线上的新反射。例如,推电阻器  $R_{\text{PIISHI}}$  412和 $R_{\text{PIISH2}}$  419以及拉电阻器 $R_{\text{PIIIII}}$  414和 $R_{\text{PIIIII2}}$  417中的至少一个电阻器可以被实施 为电阻器梯或其它可调电阻器网络,并且阻抗控制器可以增加推电阻器R<sub>PUSH</sub> 412和R<sub>PUSH</sub>2 419以及拉电阻器R<sub>PIILL</sub> 414和R<sub>PIIL</sub> 417中的至少一个电阻器的电阻值(例如,通过控制电 阻器梯或其它可调电阻器网络内的开关以连接电阻器组件)。在数据采样点之前,阻抗控制 器432可以在CAN总线上的差分驱动器电压保持处于预定义电压的同时将CAN装置400的输 出阻抗增加为处于CAN总线的特性阻抗(例如,CAN总线的±10%特性阻抗)的范围的阈值内 并且优选地基本上等于CAN总线的特性阻抗,或增加为低于或高于CAN总线的特性阻抗的预 定义阻抗值(例如,CAN总线的特性阻抗的±5%、±10%或处于CAN总线的特性阻抗的其它 合适的值范围内),以避免数据样本错误。在一些实施例中,阻抗控制器432在CAN总线上的 差分驱动器电压保持处于预定义电压的同时将CAN装置400的输出阻抗增加为基本上等于 CAN总线的特性阻抗(例如,±5%、±10%或处于其它适合的值范围内),并且随后在CAN总 线上的差分驱动器电压保持处于预定电压的同时将CAN装置400的输出阻抗从CAN总线的特 性阻抗增加为高欧姆值。

[0088] 本发明的发明人已经认识并理解,采用阻抗控制器432连同阻抗桥430的前馈架构对CAN总线的显性到隐性转变表现出最快的响应时间并且能够支持最高的CAN FD波特率和错误帧检测。使用"推"阻抗电路410和"拉"阻抗电路415,在数据阶段传输期间仅一个振铃抑制装置活跃。由于这种行为,例如电缆导线长度区段可能不相等并导致冲突反射的设计不良的网络拓扑存在潜在的性能代价。因此,单个发射器无法将CAN总线404驱动到足以有效抵消整个拓扑上的这些冲突信号反射的低欧姆状态。

[0089] 因此,根据本发明的例子,CAN装置400被修改为包括另外的反馈(接收器)路径。在一些例子中,设想的是,另外的反馈(接收器)路径可以是现有CAN总线接收器电路450或专用接收器。

[0090] 在此例子中,接收器电路450连接到滤波器电路460,使得接收器电路接收CAN总线404上的差分信号并输出接收器数据(RXD)信号455。接收器检测CAN总线上的电压下降,即下降到低于触发电压电平(例如,下降到介于0.9V与0.5V之间的电平),条件是CAN总线电压在某个先前时间内足够高,例如,2Mbps下400纳秒,由此避免检测CAN总线毛刺。在此例子中,使用滤波器电路460确定CAN总线电压在某个先前时间内足够高。

[0091] 优选的实施方案是使用现有接收器电路,如图4所示,因为为了防止误触发,接收器电路450已经设计有所想到的最佳信噪比和电压阈值。

[0092] 对于支持高波特率的CAN装置400,接收器电路450已经尽可能快。因此,这种电路是用于反馈振铃抑制的最佳电路类型。当前的IS011898-2:2016CAN标准仅要求接收器电压阈值介于0.9V与0.5V之间。最先进的CAN装置400中已经使用的改进是滞后,其中降压阈值介于0.7V与0.5V之间,并且升压阈值介于0.9V与0.7V之间。因为在接收器不具有滞后的情况下,将仅在总线电压上升到超过0.7V而不是超过最坏情况电压0.5V时才检测到CAN总线上的反射,所以这种滞后会提高信噪比,从而提供200mV噪声容限改进。

[0093] 在一些例子中,为了减少或防止前馈振铃抑制电路的误触发,应将触发电压设置为尽可能低,但仍高到足以能够可靠地检测显性到隐性边缘。

[0094] 在本发明的例子中,阻抗控制器432连同阻抗桥430可以被配置成以某个电压和阻抗波形(如图5的第三波形所示)驱动CAN总线404。取决于CAN装置400是作为发射节点还是作为接收节点活跃指示如何驱动CAN总线电压和阻抗。例如,当CAN装置400作为发射节点活跃时,检测到TXD输入引脚上的显性到隐性边缘(例如,在前馈实施方案中),并且TXD线路如图5所示那样切换。如果在TXD线上检测到"0",则不允许CAN装置作用于接收器模式节点。如果在TXD线上检测到"0"到"1"转变,则不允许CAN装置400在某个时间段内作用于接收器模式节点。这种消隐时间等于图5中描绘的发射节点模式的长度乘以时间t<sub>5</sub>减去时间t<sub>0</sub>。如果在TXD线路上检测到"1",则CAN装置400的阻抗控制器432能够在阻抗桥430中执行接收器节点阻抗。相反,当CAN装置400作为接收节点活跃时,可以检测到CAN总线引脚上的显性到隐性边缘(例如,在反馈实施方案中),如图6所示。

[0095] 尽管图4的例子示出了定位在CAN发射器上的推-拉级,但是设想的是,在其它例子中,可以使用表现出120欧姆阻抗的浮动开关。

[0096] 以此方式,可以由阻抗控制器432根据CAN装置被检测为以发射器节点还是接收器节点操作以不同的方式控制阻抗桥430。有利地,可以在不对CAN控制器进行任何改变的情况下在已知的CAN系统或CAN FD系统中采用这种方法,注意,作为实施本文描述的示例概念中的一些示例概念的替代方法,还可以通过在TXD/RXD引脚旁边在控制器与CAN装置400之间采用另外的引脚来使已知的CAN控制器非标准化。

[0097] 现在参考图5,定时图例子500示出了根据本发明的例子的理想化的发射节点显性到隐性操作。第一波形表示例如由在 $V_{\rm CC}$  (例如,等于5伏)的公共电压电源轨411与接地之间操作的CAN发射器产生的理想化的CAN总线信号的发射数据 (TXD)信号510。如图4的CAN装置400等活跃CAN装置将波形驱动到表示逻辑低电平 (逻辑0)的"显性"状态,简称显性512。总线收发器被偏置为约 $V_{\rm CC}/2$ ,使得差分波形峰值CANH 111和CANL 112通过不接近供电电压轨而避免失真。当收发器驱动器被停用并且从CAN总线上移除其相应的差分输出电压,即从CAN显性电压522转变为例如零电压524时,产生CAN总线逻辑高"隐性"电平,简称隐性514。

[0098] 在时间点 $t_0$ 处,TXD上的TXD信号510从低转变为高,这引起如图4中的CAN总线404等CAN总线上的差分驱动器电压 $V_{CAN}$ (例如,在CANH端401与CANL端402之间测量的差分电压)的显性512到隐性514转变。应当理解的是,TXD路径上的TXD信号510的低到高转变可能不会立即引起CAN总线电压 $V_{CAN}$ 520的变化,例如因为当TXD路径上的TXD信号510被CAN装置400接收并转换为CAN总线的电压电平时可能存在延迟。在显性512下,图4的阻抗控制器432将推电阻器 $R_{PUSH1}$ 412和 $R_{PUSH2}$ 419控制为保持处于显性阻抗电平(例如,15  $\Omega$ ),并且将拉电阻器 $R_{PULL1}$ 414和 $R_{PULL2}$ 417控制为保持处于高欧姆,这产生处于显性阻抗电平 $R_{DOM}$ (例如,30  $\Omega$ )的低欧姆驱动器阻抗 $Z_{CAN}$ 530。

[0099] 响应于在时间点 $t_0$ 处检测到显性到隐性转变,阻抗控制器432控制推电阻器 $R_{PUSH1}$ 412和 $R_{PUSH2}$ 419以及拉电阻器 $R_{PULL1}$ 414和 $R_{PULL2}$ 417,以控制驱动器阻抗 $Z_{CAN}$ ,使得所述驱动器阻抗保持不变。例如,在时间点 $t_0$ 与时间点 $t_1$ 之间,推电阻器 $R_{PUSH1}$ 412和 $R_{PUSH2}$ 419以及拉电阻器 $R_{PULL1}$ 414和 $R_{PULL2}$ 417中的每个电阻器的电阻值被改变为使得在驱动器阻抗 $Z_{CAN}$ 530保持恒定的同时,CAN总线电压 $V_{CAN}$ 从 $V_{DOM}$ 斜降为零。阻抗控制器可以将推电阻器 $R_{PUSH1}$

412和 $_{\text{RPUSH2}}$  419的电阻值从一个值 (例如,15欧姆) 逐渐增加为更高的值 (例如,30欧姆),同时将拉电阻器 $_{\text{PULL1}}$  414和 $_{\text{PULL2}}$  417的电阻值从"无穷大"减小为某个值 (例如,30欧姆)。在时间点 $_{\text{L}_{1}}$ 处,推电阻器 $_{\text{PUSH2}}$  412和 $_{\text{PUSH2}}$  419以及拉电阻器 $_{\text{PULL1}}$  414和 $_{\text{PULL2}}$  417的电阻值可以彼此相同,而驱动器阻抗 $_{\text{CAN}}$ 保持恒定。在时间点 $_{\text{L}_{1}}$ 处,CAN总线电压 $_{\text{CAN}}$  520达到隐性状态 (0V),并且阻抗控制器将驱动器阻抗 $_{\text{CAN}}$  530控制为相对于驱动器阻抗 $_{\text{CAN}}$  530在时间点 $_{\text{L}_{0}}$ 处的阻抗值保持不变。在CAN总线电压 $_{\text{CAN}}$ 520达到隐性状态 (0V)之后,阻抗控制器将驱动器阻抗 $_{\text{CAN}}$ 530控制为在另一个持续时间内保持不变。通过将驱动器阻抗 $_{\text{CAN}}$ 530控制为在CAN总线电压 $_{\text{CAN}}$ 520的斜降期间保持不变,可以减少耗散到CAN网络中的能量,从而使CAN总线电压 $_{\text{CAN}}$ 520的反射较低。

在时间点 $t_2$ 处,图4的阻抗控制器432开始将驱动器阻抗 $Z_{CAN}$ 530从低欧姆阻抗 $R_{DOM}$ 增加为更高值,直到时间点 $t_3$ 。例如,推电阻器 $R_{PUSH1}412$ 和 $R_{PUSH2}419$ 以及拉电阻器 $R_{PULL1}414$ 和R<sub>PILL2</sub> 417中的至少一个电阻器可以被实施为电阻器梯或其它可调电阻器网络,并且阻抗 控制器可以增加推电阻器 $R_{PUSH1}$  412和 $R_{PUSH2}$  419以及拉电阻器 $R_{PULL1}$  414和 $R_{PULL2}$  417中的至 少一个电阻器的电阻值(例如,通过控制电阻器梯或其它可调电阻器网络中的开关以连接 电阻器组件)。在时间点 $t_3$ 处,驱动器阻抗 $Z_{CAN}$  530达到活跃隐性阻抗水平 $R_{ACTREC}$ ,所述活跃 隐性阻抗水平R<sub>ACTREC</sub>可以调整为CAN网络电缆的特性阻抗(例如,120欧姆)或任何其它合适 的值。因为在驱动器阻抗 $Z_{CAN}$ 530增加的同时,CAN总线电压 $V_{CAN}$ 520保持处于OV,所以阻抗 变化不会导致大量能量耗散到CAN网络中,并且因此减少或防止CAN总线404上的新反射。驱 动器阻抗Z<sub>CAN</sub> 530的调节可以随着时间的推移连续执行并且可以以恒定变化速率增加。在 一些示例实施例中,驱动器阻抗Z<sub>CAN</sub> 530的恒定变化速率被设定为低于预定义值,以逐渐增 加驱动器阻抗Z<sub>CAN</sub> 530。阻抗控制器可以通过以下调节驱动器阻抗Z<sub>CAN</sub> 530:控制推电阻器  $R_{PUSH1}$  412和 $R_{PUSH2}$  419以及拉电阻器 $R_{Pull1}$ 和 $R_{Pull2}$  417以将其阻抗从起始推阻抗(例如, $Z_{CAN}$  $=30\,\Omega$ )增加为目标推阻抗(例如, $Z_{CAN}=120\,\Omega$ )。在一些实施例中,阻抗控制器随着时间的 推移以恒定变化速率连续地增加推电阻器 $R_{PUSH1}$  412和 $R_{PUSH2}$  419以及拉电阻器 $R_{Pull1}$ 和 $R_{Pull2}$ 417的阻抗。在一些实施例中,时间点t,与时间点t,之间的持续时间为零。

[0101] CAN总线404上的反射得到抑制,直到时间点 $t_4$ 。时间点 $t_0$ 与时间点 $t_4$ 之间的持续时间越长,振铃抑制性能就越好。在时间点 $t_4$ 处,阻抗控制器432开始将驱动器阻抗 $Z_{CAN}$ 530从活跃隐性阻抗水平 $R_{ACTREC}$ 增加为更高值,直到时间点 $t_5$ 。在时间点 $t_5$ 处,驱动器阻抗 $Z_{CAN}$ 达到隐性阻抗水平 $R_{REC}$ 。在一些实施例中,在总线电压在时间点 $t_4$ 处不为零的情况下,时间点 $t_4$ 与时间点 $t_5$ 之间的持续时间高于某一持续时间,以减少或防止另外的能量耗散到CAN网络中。例如,如果例如在仲裁期间或在发射错误帧时,另一个发射器也将总线驱动为显性,则总线电压在时间点 $t_4$ 处可以不为零。 $t_4$ 与 $t_5$ 之间的阈值持续时间取决于网络拓扑复杂性。

[0102] 现在参考图6,定时图例子600示出了根据本发明的一些例子的检测(在接收器/反馈电路中)CAN装置在CAN总线引脚上的显性到隐性操作中作为接收节点操作的例子。

[0103] 第一波形620示出了CAN装置驱动器何时停用并且其相应的差分输出电压何时从CAN总线移除,即,从CAN显性电压622转变为例如零电压624。此处,接收器检测CAN总线上的电压下降,即下降到低于触发电压电平(例如,下降到介于0.9V与0.5V之间的电平),条件是CAN总线电压在某个先前时间内足够高。可以使用例如滤波器电路(如图4的滤波器电路460)执行总线滤波(例如,2Mbps下400纳秒)来确定CAN总线电压在某一之前时间内足够高。

还确定TXD输入在长于消隐时间的至少某个时间内是隐性的(由此指示CAN装置作为接收节点操作)。然后,阻抗控制器(如图4中的阻抗控制器432)产生阻抗曲线,如图6中描绘的第二波形630。

[0104] 如果例如以同等方式驱动推输出级和拉输出级(例如,图4的阻抗桥430的推输出 级,即推阻抗电路410和拉输出级,即拉阻抗电路415),则这会导致CAN总线被某一阻抗驱动 为0V。时间t<sub>0</sub>与t<sub>1</sub>之间的第一时间延迟632指示滤波器处理时间和接收器延迟的组合,其中 典型的实际值可以介于10纳秒与50纳秒之间。时间t,与t,之间的第二时间延迟634指示从高 阻抗到低阻抗(所谓的活跃隐性阻抗)的转变时间,其中典型的实际值可以是10纳秒。时间 t。与t。之间的第三时间延迟636指示所谓的活跃隐性时间,其是输出阻抗与防止反射的电缆 阻抗基本上相等的时间段。时间长,与长,之间的第四时间延迟638指示所谓的缓慢释放,并且 防止当总线电压不为零伏特时由于其它显性发射器而造成的新反射。第四时间延迟638的 典型的实际时间段为75纳秒。本质上,to与ta之间的总时间(即,632+634+636+638)取决于 CAN总线波特率,因为如果此时间与CAN-FD控制器的采样点相比变得更长,则通信将受到破 坏,因为所有节点均将总线驱动为处于低欧姆状态,使得发射显性(即,在错误帧状况下)的 节点将被隐性信号盖写。在这种情况下,2Mbps下的最坏情况采样点为约220纳秒,而在 5Mbps下,最坏情况采样点为65纳秒。在2Mbps下,t,与t,之间的实际时间为85纳秒(=220纳 秒-50纳秒-10纳秒-75纳秒)。由于典型的可靠接收器的延迟,反馈振铃抑制的反应时间可 能如此慢,以至于在5Mbps下未留下抑制时间。

[0105] 因此,仍然存在接收器电路(如图4的接收器电路450)不会在显性到隐性边缘上,而在存在于CAN总线上的毛刺上触发的风险。此类毛刺可能是由电磁耦合(EMC)干扰或CAN总线导线耦合到其它高开关电流承载导线引起的。在正常的CAN系统中,因为隐性状态只在采样点处进行评估,所以CAN装置的RXD引脚上的这些毛刺不会导致通信问题。CAN总线上的此类毛刺的时间可能由于反馈振铃抑制概念而延长,由此增加毛刺延长到采样点窗口中的机会。

[0106] 在一些示例实施例中,为了避免CAN总线上的毛刺(所述毛刺由于反馈振铃抑制概念而在时间上延长,由此增加毛刺延长到采样点窗口中的机会),可以采用窗口化概念。图7中示出了根据本发明的例子的可以用于采用窗口化概念的电路架构的一个例子。图7中的窗口化概念代替图4中的滤波器电路460,以试图在发射器节点在CAN总线上驱动显性时,并且在另一个节点为隐性时(即,在显性信号可能由于引入另外的120欧姆阻抗而受到干扰时)移除毛刺。

[0107] 图4的发射器操作与图7相同,因此仅出于简单的目的,此处未重复对所述操作的描述。在图7中,接收器电路450的输出RXD信号连接到位时间逻辑(BTL)电路765,所述BTL电路765被配置成以与已知的CAN-FD控制器的操作类似的方式使RXD信号455与CAN总线数据流同步。以此方式,BTL电路765能够预测CAN总线404上的潜在显性到隐性转变。

[0108] 来自BTL电路765的经过同步的输出输入到窗口滤波器760中,所述窗口滤波器760被配置成拒绝接收器的处于潜在显性到隐性转变之外的输出。BTL电路765被配置成以与CAN协议控制器类似的方式使RXD信号永久同步。只要CAN总线线路上存在量值仍允许CAN协议控制器的适当操作的干扰,CAN装置700内部的BTL电路765就能够识别出总线上具有相同性能的潜在边缘。使用CAN装置700内部的这种嵌入式BTL电路765,CAN装置700现在能够可

靠地及时预测潜在CAN协议相关位转变可能在何处发生。在一些例子中,BTL电路765可以能够将所述预测限制于显性到隐性位转变。以此方式,在一些例子中,BTL电路765可以被配置成解决特定于振铃抑制的问题,而不是如其它已知的CAN系统中所描述的纯粹对CAN位流进行解码。

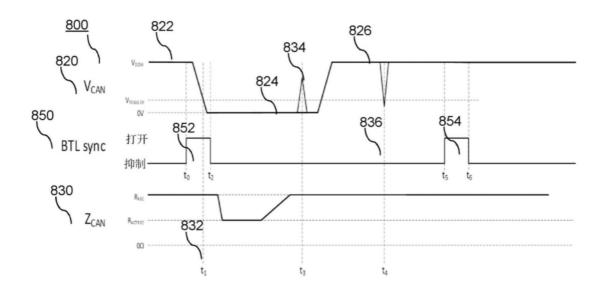

[0109] 现在参考图8,示出了根据本发明的例子的具有图7的窗口滤波的示例反馈概念的定时图。第一波形820示出了CAN装置驱动器何时停用并且其相应的差分输出电压何时从CAN总线移除,即,从CAN显性电压822转变为例如零电压824。此处,接收器检测CAN总线上的电压下降,即下降到低于触发电压电平(例如,下降到介于0.7V与0.5V之间的电平),条件是CAN总线电压在某个先前时间内足够高。

[0110] 第二波形示出了BTL同步输入信号850 (如来自图7的BTL电路765的输出信号) 的定时。时间 $t_0$ 与 $t_2$ 之间的时间段852指示BTL与CAN总线上的数据流同步,并且打开窗口,以便在显性到隐性边缘上触发。第三波形830指示阻抗控制器 (如图4的阻抗控制器432) 产生的阻抗波形。在时间 $t_1$ 832处,在第一波形820中检测到显性到隐性边缘,并且阻抗控制器432产生 $Z_{CAN}$ 中所描述的阻抗曲线。在时间 $t_3$ 834处,CAN总线上存在隐性状态,即零电压824期间的显性毛刺,并且在不进行窗口滤波的情况下,可以触发阻抗控制器432以产生潜在地干扰随后的隐性到显性边缘的阻抗曲线。在此例子中,在窗口滤波活跃的情况下,如图7所描述的,时间 $t_3$ 834处的毛刺被抑制。在时间 $t_4$ 836处,CAN总线上存在显性状态826期间的隐性毛刺,并且在不进行窗口滤波的情况下,可以触发阻抗控制器432以产生干扰显性状态的阻抗曲线。然而,在窗口滤波活跃的情况下,如图7所描述的,时间 $t_4$ 836处的毛刺被抑制。在时间 $t_5$ 与 $t_6$ 之间854的第二波形中,触发窗口打开,持续潜在的隐性边缘,但是未检测到显性到隐性边缘。

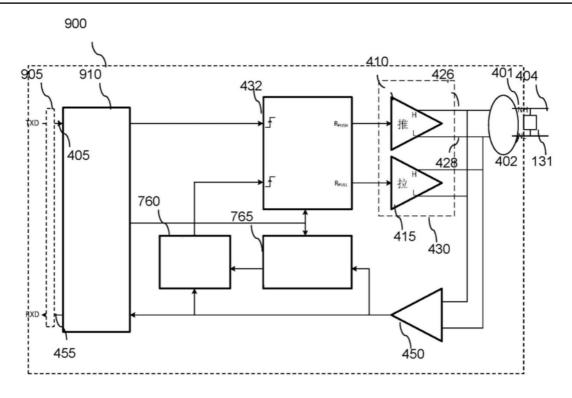

[0111] 在此窗口滤波反馈概念中,图7的BTL电路765最初需要知道CAN-FD波特率是什么。因此,在一些例子中,CAN-FD波特率在CAN装置中可以是固定的,或者由某个接口(未示出)(如串行-并行接口SPI)配置。在其它例子中,可以在微控制器与CAN装置之间采用其它接口,如I2C接口。在一些例子中,通过添加如图9所示的波特率检测器电路可以解决最初知道CAN-FD波特率是什么的这一需求。

[0112] 现在参考图9,示出了根据本发明的一些例子的具有波特率检测器电路910的CAN 装置900。再次,在一些示例实施例中,为了避免CAN总线上的毛刺(所述毛刺由于反馈振铃抑制概念而在时间上延长,由此增加毛刺延长到采样点窗口中的机会),可以采用窗口化概念。图9中示出了根据本发明的例子的可以用于采用窗口化概念的电路架构的一个例子。图 9中的窗口化概念代替图4中的滤波器电路460,以试图在发射器节点在CAN总线上驱动显性时,并且在另一个节点为隐性时(即,在显性信号可能由于引入另外的120欧姆阻抗而受到干扰时)移除毛刺。

[0113] 图4的发射器操作与图9相同,因此仅出于简单的目的,此处未重复所述操作。在图 9中,接收器电路450的输出RXD信号再次连接到位时间逻辑(BTL)电路765,所述BTL电路765被配置成以与已知的CAN-FD控制器的操作类似的方式使RXD信号455与CAN总线数据流同步。以此方式,BTL电路765能够预测CAN总线404上的潜在显性到隐性转变。

[0114] 来自BTL电路765的经过同步的输出输入到窗口滤波器760中,所述窗口滤波器760被配置成拒绝接收器的处于潜在显性到隐性转变之外的输出。BTL电路765被配置成以与

CAN协议控制器类似的方式使RXD信号永久同步。只要CAN总线线路上存在量值仍允许CAN协议控制器的适当操作的干扰,CAN装置700内部的BTL电路765就能够识别出总线上具有相同性能的潜在边缘。使用CAN装置900内部的这种嵌入式BTL电路765,CAN装置900现在能够可靠地及时预测潜在CAN协议相关位转变可能在何处发生。在一些例子中,BTL电路765可以能够将所述预测限制于显性到隐性位转变。以此方式,在一些例子中,BTL电路765可以被配置成解决特定于振铃抑制的问题,而不是如其它已知的CAN系统中所描述的纯粹对CAN位流进行解码。

[0115] 当CAN装置900第一次上电时,波特率检测器电路910被配置成阻挡到阻抗控制器432的TXD信号405并且阻挡到CAN-FD控制器的RXD信号455。微控制器将需要在上电后在数据阶段中传输包含例如10101010模式的CAN-FD帧,使得波特率检测器电路910能够根据所述CAN FD帧得出波特率。

[0116] 在一些例子中,设想的是,CAN装置900的架构可以能够支持不同的帧长度和类型,只要其采用"已知"数据模式即可。在此学习阶段期间,RXD信号455(输出)紧随TXD信号405(输入),使得CAN-FD控制器检测不到错误。任选地,波特率检测器电路910可以在正确检测到波特率时提供CAN确认位。

[0117] 在一些例子中,只需在微控制器中进行软件更改,就可以在上电后传输虚设/学习消息。在学习阶段之后,波特率检测器电路910将BTL电路765和发射器/阻抗控制器配置成以正确的定时操作,并使TXD信号405和RXD信号455通过。根据所学的波特率,发射器/阻抗控制器可以被配置成使得在不破坏数据样本的情况下,RX阻抗模式的活跃隐性时间 $t_2$ 到 $t_3$ 的长度(图8中)针对关于振铃抑制电路的最佳定时特性的每个波特率具有最大长度。

[0118] 尽管图9被示出为具有波特率检测器电路910,但设想的是,在其它例子中,波特率检测器电路910可以用被配置成向阻抗控制器432提供预定波特率值的串行-并行接口(SPI)905代替。

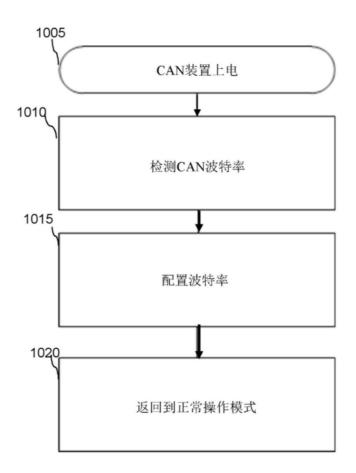

[0119] 图10示出了根据本发明的示例实施例的用于CAN装置的振铃抑制方法的例子的简化流程图1000。简化流程图1000在1005处开始于例如微控制器中的CAN控制器(或CAN FD控制器)的上电操作以及CAN装置的上电。在1010处,流程图包括检测CAN波特率。例如,当阻抗控制器432处于隐性阶段并且RXD信号输出紧随TXD输入信号时,CAN FD控制器在TXD信号上传输数据模式。在1015处,流程图1000包括配置波特率。在一些例子中,这包括例如对图7中的BTL电路765中的位时间逻辑引入定时调节。在此阶段中,阻抗控制器432处于隐性阶段并且RXD信号输出处于高逻辑状态(即,隐性)。在1020处,CAN装置返回到正常操作模式,由此TXD信号输入到阻抗控制器432,并且接收器输出是RXD输出信号。

[0120] 在前面的说明书中,已经参考本发明的实施例的具体例子描述了本发明。然而,将显而易见的是,在不脱离如所附权利要求中阐述的本发明的范围的情况下,可以对其进行各种修改和改变,并且权利要求不限于上文描述的具体例子。具体地说,本发明的例子可以用于传统的CAN系统的标准CAN装置,或在提供改进的或优化的振铃抑制时用作CAN FD系统的新CAN装置。

[0121] 此外,因为本发明的所示实施例在很大程度上可以由本领域的技术人员已知的电子组件和电路实施,所以如上文所说明的,对细节的解释将不会超过认为必要的程度,以便于理解和认识本发明的基本概念并且以免混淆本发明的教导或将注意力转移到本发明的

教导之外。

[0122] 本文讨论的连接可以是适合于例如通过中间装置来往于相应节点、电路或装置传送信号的任何类型的连接。因此,除非另有暗示或说明,否则连接可以是例如直接连接或间接连接。可以关于单个连接、多个连接、单向连接或双向连接对所述连接进行说明或描述。然而,不同实施例可以改变连接的实施方式。例如,可以使用单独的单向连接而不使用双向连接,并且反之亦然。而且,多个连接可以用连续地或以时分复用的方式传送多个信号的单个连接代替。同样,承载多个信号的单一连接可以被分成承载这些信号的子集的各种不同连接。因此,存在许多用于传送信号的选项。

[0123] 本领域的技术人员将认识到,逻辑块之间的界限仅仅是说明性的,并且替代性实施例可能合并逻辑块或电路元件或向各个逻辑块或电路元件添加功能的替代分解。因此,应理解的是,本文描绘的架构仅仅是示例性的,并且实际上可以实施实现相同功能的许多其它架构。

[0124] 用于实现相同功能的组件的任何布置被有效"关联",使得期望功能得以实现。因此,本文中被组合以实现特定功能的任何两个组件可以被视为彼此"相关联",使得期望功能被实现,而不论架构或中间组件如何。同样,如此关联的任何两个组件也可以被视为彼此"可操作地连接"或"可操作地耦合"以实现期望功能。

[0125] 另外,本领域的技术人员将认识到,上文所描述的操作之间的界限仅仅是说明性的。可以在时间上至少部分重叠地执行所述多个操作。此外,替代性示例实施例可以包括特定操作的多个实例,并且在各个其它实施例中可以改变操作的顺序。

[0126] 而且,例如,在一个实施例中,所示出的例子可以被实施为定位在单个集成电路上或同一装置内的电路系统。可替换的是,所述例子可以被实施为以合适的方式彼此互连的任何数量的单独集成电路或单独装置。

[0127] 而且,本发明的例子不限于以非可编程硬件实施的电路,但是也可以应用于能够通过根据适合的程序代码进行操作来执行期望的装置功能的无线可编程装置或电路。然而,其它修改、变更和替代方案也是可能的。因此,说明书和附图将被视为是说明性的,而不是限制性的。

[0128] 在权利要求中,括号内的任何附图标记不应解释为限制权利要求。"包括"一词不排除存在除了权利要求中列出的元件或步骤之外的元件或步骤。此外,如本文所用的术语"一个或一种(a或an)"被定义为一个或多于一个。而且,在权利要求中使用如"至少一个"和"一个或多个"等引入性短语不应被解释为暗示通过不定冠词"一个或一种(a或an)"引入另一权利要求要素将包含这种所引入权利要求要素的任何特定权利要求限于仅包含一个这种要素的发明,甚至是在同一权利要求包括引入性短语"一个或多个"或"至少一个"以及如"一个或一种(a或an)"等不定冠词时也是如此。对于定冠词的使用也是如此。除非另有说明,否则如"第一"和"第二"等术语用于任意区分这种术语描述的要素。因此,这些术语不一定旨在指示这种要素的时间优先次序或其它优先次序。在彼此不同的权利要求中叙述了某些措施的简单事实并不表明这些措施的组合不能被有利地使用。

图1

图2

图3

图4

图5

图6

图7

图8

图9

1000

图10