(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6951423号 (P6951423)

(45) 発行日 令和3年10月20日(2021.10.20)

(24) 登録日 令和3年9月28日 (2021.9.28)

(51) Int. CL.

FΙ

HO4N 5/378 (2011.01)

HO4N 5/378

請求項の数 18 (全 51 頁)

(21) 出願番号 特願2019-509966 (P2019-509966)

(86) (22) 出願日 平成30年3月28日 (2018.3.28)

(86) 国際出願番号 PCT/JP2018/012723

(87) 国際公開番号 W02018/181463

(87) 国際公開日 平成30年10月4日 (2018.10.4)

審査請求日 令和1年12月3日(2019.12.3)

(31) 優先権主張番号 特願2017-71682 (P2017-71682) (32) 優先日 平成29年3月31日 (2017.3.31)

(33) 優先権主張国・地域又は機関

日本国(JP)

||(73)特許権者 521182560

ブリルニクス シンガポール プライベー

ト リミテッド

シンガポール 079906 アンソン・

p-F 79 #07-03

(74)代理人 110001863

特許業務法人アテンダ国際特許事務所

(72) 発明者 大倉 俊介

東京都品川区南大井6丁目21番12号 大森プライムビル7階 ブリルニクスジャ

パン株式会社内

審査官 鈴木 明

最終頁に続く

(54) 【発明の名称】 固体撮像装置、固体撮像装置の駆動方法、および電子機器

## (57)【特許請求の範囲】

## 【請求項1】

光電変換を行う画素が配置された画素部と、

前記画素から信号線に読み出される画素信号をアナログ信号からデジタル信号に変換するアナログデジタル(AD)変換機能を有する読み出し回路と、を有し、

前記画素から読み出される前記画素信号は、

第1の動作により前記画素から順に読み出される読み出しリセット信号および読み出 し輝度信号を含む第1の画素信号と、

第2の動作により前記画素から順に読み出される読み出し輝度信号および読み出しリセット信号を含む第2の画素信号と、のうちの少なくともいずれかであり、

前記読み出し回路は、

前記画素信号を増幅する増幅部と、

前記増幅部で増幅された画素信号を、探索信号に関連付けてアナログ信号からデジタル信号に変換するAD変換部と、を含み、

前記第1の画素信号のときの第1の探索信号と前記第2の画素信号のときの第2の探索信号とは、探索レベルが反転した関係に設定可能である

固体撮像装置。

## 【請求項2】

前記増幅部は、

第1の演算増幅器と、

10

前記第1の画素信号または前記第2の画素信号の入力ラインと前記第1の演算増幅器の第1の入力端子との間に接続された第1のサンプリングキャパシタと、

前記第1の演算増幅器の出力端子と前記第1の入力端子との間に接続される第1の帰還キャパシタと、

オフセット電位と、

前記<u>第1の</u>帰還キャパシタの一端側を前記第1の演算増幅器の出力端子または前記オフセット電位に選択的に接続する第1のスイッチ部と、を含み、

前記第1の演算増幅器の第2の入力端子は少なくとも参照電位に接続可能である 請求項1記載の固体撮像装置。

#### 【請求項3】

前記増幅部は、

前記第1の画素信号または前記第2の画素信号の入力ラインと前記第1の演算増幅器の第2の入力端子との間に接続された第2のサンプリングキャパシタと、

前記第1の演算増幅器の前記第2の入力端子と基準電位との間に接続された第2の帰還キャパシタと、

前記参照電位を前記第1の演算増幅器の前記第2の入力端子に選択的に接続する第2のスイッチ部と、を含む

請求項2記載の固体撮像装置。

### 【請求項4】

前記AD変換部は、

第2の演算増幅器と、

前記増幅部の信号出力ラインに接続されたサンプルホールドスイッチと、

前記第2の演算増幅器の第1の入力端子と前記サンプルホールドスイッチとの間に接続された入力キャパシタと、

前記入力キャパシタの前記サンプルホールドスイッチとの接続端子側と前記探索信号の供給ラインとの間に接続され、前記探索信号を前記入力キャパシタの前記サンプルホールドスイッチとの接続端子側に入力する探索信号入力部と、を含み、

前記第2の演算増幅器の第2の入力端子は参照電位に接続されている 請求項2または3記載の固体撮像装置。

## 【請求項5】

前記AD変換部の前記探索信号入力部は、

一端子側が前記入力キャパシタの前記サンプルホールドスイッチとの接続端子側に接続され、他端子側が前記探索信号の供給ライン側に接続された探索信号入力用キャパシタを含む

請求項4記載の固体撮像装置。

#### 【請求項6】

前記AD変換部の前記探索信号入力部は、

ー端子側が前記入力キャパシタの前記サンプルホールドスイッチとの接続端子側に接続された複数のキャパシタと、

前記複数のキャパシタに対応して配置され、二分探索法に従った制御信号に応じて当該対応するキャパシタの他端側を、参照電位または基準電位に選択的に接続する複数のスイッチと、を含む

請求項4記載の固体撮像装置。

# 【請求項7】

前記増幅部は、

前記<u>第1の</u>演算増幅器の前記第1の入力端子と出力端子との間に接続された第1のオートゼロスイッチを含み、

前記AD変換部は、

前記第2の演算増幅器の前記第1の入力端子と出力端子との間に接続された第2のオートゼロスイッチを含む

10

20

30

50

請求項4から6のいずれか一に記載の固体撮像装置。

## 【請求項8】

前記第1の画素信号がシングルエンドの信号として前記増幅部の第1のサンプリングキャパシタに入力される場合、

前記増幅部の第1の帰還キャパシタは前記第1のスイッチ部により前記第1の演算増幅器の出力端子に接続され、前記第1の演算増幅器の第2の入力端子が前記参照電位に接続され、

前記AD変換部には前記第1の探索信号が供給され、

前記第2の画素信号がシングルエンドの信号として前記増幅部の第1のサンプリングキャパシタに入力される場合、

前記増幅部の第1の帰還キャパシタは前記第1のスイッチ部により前記オフセット電位に選択的に接続され、前記第1の演算増幅器の第2の入力端子が前記参照電位に接続され、

前記AD変換部には前記第1の探索信号とは探索レベルが反転した関係にある前記第2の探索信号が供給される

請求項2から7のいずれか一に記載の固体撮像装置。

#### 【請求項9】

前記第1の画素信号が差動の信号として前記増幅部の第1のサンプリングキャパシタおよび第2のサンプリングキャパシタに入力される場合、

前記増幅部の第1の帰還キャパシタは前記第1のスイッチ部により前記第1の演算増幅器の出力端子に接続され、

前記AD変換部には前記第1の探索信号が供給される

請求項2から8のいずれか一に記載の固体撮像装置。

#### 【請求項10】

前記第2の画素信号が差動の信号として前記増幅部の第1のサンプリングキャパシタおよび第2のサンプリングキャパシタに入力される場合、

前記増幅部の第1の帰還キャパシタは前記第1のスイッチ部により前記第1の演算増幅器の出力端子に接続され、

前記AD変換部には前記第1の探索信号が供給される

請求項2から9のいずれか一に記載の固体撮像装置。

### 【請求項11】

光電変換読み出し部および信号保持部を含む第1の画素と前記光電変換読み出し部を含む第2の画素のうち、少なくとも前記第1の画素が配置された前記画素部と、

前記画素部から画素信号の読み出しを行う読み出し部と、

前記光電変換読み出し部の読み出し信号が出力される第1の信号線と、

前記信号保持部の保持信号が出力される第2の信号線と、を有し、

少なくとも前記第1の画素の前記光電変換読み出し部は、

出力ノードと、

蓄積期間に光電変換により生成した電荷を蓄積する光電変換素子と、

前記光電変換素子に蓄積された電荷を転送期間に転送可能な転送素子と、

前記転送素子を通じて前記光電変換素子で蓄積された電荷が転送されるフローティングディフュージョンと、

前記フローティングディフュージョンの電荷を電荷量に応じた電圧信号に変換し、変換した信号を前記出力ノードに出力するソースフォロワ素子と、

リセット期間に前記フローティングディフュージョンを所定の電位にリセットするリセット素子と、

第1の期間に前記出力ノードを前記第1の信号線と電気的に接続する選択素子と、を 含み、

前記信号保持部は、

前記第1の画素の前記光電変換読み出し部の出力ノードから出力される信号を保持可

10

30

20

50

能な信号保持キャパシタと、

第2の期間に前記信号保持キャパシタを前記光電変換読み出し部の出力ノードと選択的に接続するスイッチ素子と、

前記第2の期間に前記信号保持キャパシタに保持された信号を保持電圧に応じて出力するソースフォロワ素子を含み、変換した信号を選択的に前記第2の信号線に出力する出力部と、を含む

請求項1から10のいずれか一に記載の固体撮像装置。

## 【請求項12】

前記画素部は、少なくとも、

複数の前記第1の画素の前記光電変換読み出し部が行列状に配置された第1の画素アレイと、

前記複数の前記第1の画素の前記信号保持部が行列状に配置された保持部アレイと、 を含む

請求項11記載の固体撮像装置。

## 【請求項13】

前記画素部は、

複数の前記第2の画素の前記光電変換読み出し部が行列状に配置された第2の画素アレイを有し、

前記第2の画素の前記光電変換読み出し部は、

蓄積期間に光電変換により生成した電荷を蓄積する光電変換素子と、

前記光電変換素子に蓄積された電荷を転送期間に転送可能な転送素子と、

前記転送素子を通じて前記光電変換素子で蓄積された電荷が転送されるフローティングディフュージョンと、

前記フローティングディフュージョンの電荷を電荷量に応じた電圧信号に変換する ソースフォロワ素子と、

リセット期間に前記フローティングディフュージョンを所定の電位にリセットする リセット素子と、

第1の期間に前記ソースフォロワ素子による電圧信号の出力ラインを前記第1の信号線と電気的に接続する選択素子と、を含む

請求項12記載の固体撮像装置。

## 【請求項14】

前記読み出し部は、

第1の動作時には、前記第1の画素の前記第1の画素アレイおよび前記第2の画素の 前記第2の画素アレイをアクティブにして画素信号の読み出しを行う

請求項13記載の固体撮像装置。

## 【請求項15】

前記読み出し部は、

第2の動作時には、前記第1の画素および前記第2の画素の前記光電変換読み出し部における前記選択素子を非選択状態とした状態で、前記第1の画素の前記第1の画素アレイおよび前記保持部アレイをアクティブにして画素信号の読み出しを行う

請求項12から14のいずれか一に記載の固体撮像装置。

#### 【請求項16】

第1の基板と、

第2の基板と、を含み、

前記第1の基板と前記第2の基板は接続部を通して接続された積層構造を有し、

前記第1の基板には、

少なくとも、前記第1の画素の前記光電変換読み出し部、および前記第1の信号線が 形成され、

前記第2の基板には、

少なくとも、前記第1の画素の前記信号保持部、前記第2の信号線、および前記読み

20

10

30

40

出し部の少なくとも一部が形成されている

請求項11から15のいずれか一に記載の固体撮像装置。

#### 【請求項17】

光電変換を行う画素が配置された画素部と、

前記画素から信号線に読み出される画素信号をアナログ信号からデジタル信号に変換するアナログデジタル(AD)変換機能を有する読み出し回路と、を有し、

前記読み出し回路は、

前記画素信号を増幅する増幅部と、

前記増幅部で増幅された画素信号を、探索信号に関連付けてアナログ信号からデジタル信号に変換するAD変換部と、を含む、

10

固体撮像装置の駆動方法であって、

前記画素から読み出される前記画素信号は、

第1の動作により前記画素から順に読み出される読み出しリセット信号および読み出 し輝度信号を含む第1の画素信号と、

第2の動作により前記画素から順に読み出される読み出し輝度信号および読み出しり セット信号を含む第2の画素信号と、のうちの少なくともいずれかであり、

前記読み出し回路に供給する前記探索信号について、

前記第1の画素信号のときの第1の探索信号と前記第2の画素信号のときの第2の探索信号とで、探索レベルが反転した関係に設定する

固体撮像装置の駆動方法。

20

### 【請求項18】

固体撮像装置と、

前記固体撮像装置に被写体像を結像する光学系と、を有し、

前記固体撮像装置は、

光電変換を行う画素が配置された画素部と、

前記画素から信号線に読み出される画素信号をアナログ信号からデジタル信号に変換するアナログデジタル(AD)変換機能を有する読み出し回路と、を含み、

前記画素から読み出される前記画素信号は、

第1の動作により前記画素から順に読み出される読み出しリセット信号および読み出し輝度信号を含む第1の画素信号と、

30

第 2 の動作により前記画素から順に読み出される読み出し輝度信号および読み出し リセット信号を含む第 2 の画素信号と、のうちの少なくともいずれかであり、

前記読み出し回路は、

前記画素信号を増幅する増幅部と、

前記増幅部で増幅された画素信号を、探索信号に関連付けてアナログ信号からデジタル信号に変換するAD変換部と、を含み、

前記第1の画素信号のときの第1の探索信号と前記第2の画素信号のときの第2の 探索信号とは、探索レベルが反転した関係に設定可能である

電子機器。

40

50

# 【発明の詳細な説明】

#### 【技術分野】

[0001]

本発明は、固体撮像装置、固体撮像装置の駆動方法、および電子機器に関するものであ る。

## 【背景技術】

#### [0002]

光を検出して電荷を発生させる光電変換素子を用いた固体撮像装置(イメージセンサ)

として、CMOS (Complementary Metal Oxide Semiconductor) イメージセンサが実用に供されている。

CMOSイメージセンサは、デジタルカメラ、ビデオカメラ、監視カメラ、医療用内視鏡、パーソナルコンピュータ(PC)、携帯電話等の携帯端末装置(モバイル機器)等の各種電子機器の一部として広く適用されている。

### [0003]

CMOSイメージセンサは、画素毎にフォトダイオード(光電変換素子)および浮遊拡散層(FD:Floating Diffusion、フローティングディフュージョン)を有するFDアンプを持ち合わせており、その読み出しは、画素アレイの中のある一行を選択し、それらを同時に列(カラム)出力方向へと読み出すような列並列出力型が主流である。

## [0004]

ところで、CMOSイメージセンサでは、フォトダイオードで生成しかつ蓄積した光電荷を、画素毎あるいは行毎に順次走査して読み出す動作が行われる。

この順次走査、すなわち、電子シャッタとしてローリングシャッタを採用した場合は、 光電荷を蓄積する露光の開始時間、および終了時間を全ての画素で一致させることができ ない。そのため、順次走査の場合、動被写体の撮像時に撮像画像に歪みが生じるという問 題がある。

## [0005]

そこで、画像歪みが許容できない、高速に動く被写体の撮像や、撮像画像の同時性を必要とするセンシング用途では、電子シャッタとして、画素アレイ部中の全画素に対して同一のタイミングで露光開始と露光終了とを実行するグローバルシャッタが採用される。

#### [0006]

電子シャッタとしてグローバルシャッタを採用したCMOSイメージセンサは、画素内に、たとえば、光電変換読み出し部から読み出された信号を信号保持キャパシタに保持する信号保持部が設けられている。

グローバルシャッタを採用したCMOSイメージセンサでは、フォトダイオードから電荷を電圧信号として一斉に信号保持部の信号保持キャパシタに蓄積し、そののち順次読み出すことにより、画像全体の同時性を確保している(たとえば、非特許文献1参照)。

また、このCMOSイメージセンサは、光電変換読み出し部の出力を、信号保持部をバイパスして信号線に転送するバイパススイッチを有しており、グローバルシャッタ機能に加えてローリングシャッタ機能を併せ持つように構成されている。

# [0007]

非特許文献1に記載された積層型CMOSイメージセンサにおいては、第1の基板(Pixel die)と第2の基板(ASIC die)とがマイクロバンプ(接続部)を通して接続された積層構造を有する。そして、第1の基板には各画素の光電変換読み出し部が形成され、第2の基板には各画素の信号保持部、信号線、垂直走査回路、水平走査回路、カラム読み出し回路等が形成されている。

## [0008]

非特許文献 2 には、 C M O S イメージセンサのカラム読み出し回路の構成例が記載されている ( F i g . 5 )。

このカラム読み出し回路は、ローリングシャッタ機能に対応した構成を有しており、カラムアンプ、相関二重サンプリング(CDS:Correlated Double Sampling)回路、およびアナログデジタル変換器(ADC)を含んで構成されている。

# 【先行技術文献】

## 【非特許文献】

# [0009]

【非特許文献1】J. Aoki, et al., "A Rolling-Shutter Distortion-Free 3D Stacked Image Sensor with -160dB Parasitic Light Sensitivity In-Pixel Storage Node" ISSCC 2013 /

10

20

30

40

SESSION 27 / IMAGE SENSORS / 27.3.

【非特許文献 2】S. Okura, et al., "A 3.7 M-Pixel 1300-fps CMOS Image Sensor With 5.0 G-Pixel/s High-Speed Readout Circuit," in IEEE Journal of Solid-State Circuits, vol. 50, no. 4. pp. 1016-1024, April 2015.

#### 【発明の概要】

【発明が解決しようとする課題】

# [0010]

ところが、従来のローリングシャッタ機能とグローバルシャッタ機能を備えるCMOS イメージセンサでは、カラム読み出し回路において、画素出力のリセットレベルと信号レベルのそれぞれを保持するキャパシタ容量を備え、機能毎に異なる画素出力信号を整列し、AD変換器で処理する必要があり、キャパシタ容量が占める面積とそれを駆動するための消費電力が問題となっている。

#### [0011]

また、ローリングシャッタモード時は、画素から読み出しリセット信号および読み出し 輝度信号が順に読み出されてカラム読み出し回路で処理される。

一方、グローバルシャッタモード時は、画素から読み出し輝度信号および読み出しリセット信号の順に読み出されてカラム読み出し回路で処理される。

そのため、ローリングシャッタ機能とグローバルシャッタ機能でカラム読み出し回路が 別構成とせざるを得ないのが現状である。

#### [0012]

したがって、ローリングシャッタ機能のCMOSイメージセンサとグローバルシャッタ機能を備えるCMOSイメージセンサでは、カラム読み出し回路を共用することが困難である。

同様に、ローリングシャッタ機能とグローバルシャッタ機能を備えるCMOSイメージセンサにおいても、カラム読み出し回路を共用することが困難であり、モードに応じたカラム読み出し回路を個別に設ける必要があり、回路規模の増大や制御の複雑化を招く等の不利益がある。

# [0013]

また、画素から読み出す読み出し信号として、シングルエンド信号の場合や、差動信号の場合等が考えられるが、この場合も信号形態に応じたカラム読み出し回路を個別に設ける必要があり、回路規模の増大や制御の複雑化を招く等の不利益がある。

### [0014]

本発明は、動作モードや読み出し信号の信号形態にかかわらず読み出し回路を共用することが可能となり、ひいては、回路規模の低減、制御の容易化、低消費電力化を実現することが可能な固体撮像装置、固体撮像装置の駆動方法、および電子機器を提供することにある。

## 【課題を解決するための手段】

#### [0015]

本発明の第1の観点の固体撮像装置は、光電変換を行う画素が配置された画素部と、前記画素から信号線に読み出される画素信号をアナログ信号からデジタル信号に変換するアナログデジタル(AD)変換機能を有する読み出し回路と、を有し、前記画素から読み出される前記画素信号は、第1の動作により前記画素から順に読み出される読み出しりせっト信号を含む第2の画素信号と、第2の動作により前記画素から順に読み出される読み出し輝度信号および読み出しリセット信号を含む第2の画素信号と、のうちの少なくともいずれかであり、前記読み出し回路は、前記画素信号を増幅する増幅部と、前記増幅部で増幅された画素信号を、探索信号に関連付けてアナログ信号からデジタル信号に変換するAD変換部と、を含み、前記第1の画素信号のときの第1の探索信号とは、探索レベルが反転した関係に設定

40

30

10

20

可能である。

## [0016]

本発明の第2の観点は、光電変換を行う画素が配置された画素部と、前記画素から信号線に読み出される画素信号をアナログ信号からデジタル信号に変換するアナログデジタル信号に変換するアナログデジタル信号に変換するアナログデジタル信号に変換する内し、前記読み出し回路は、前記画素信号を増幅する増幅部と、前記増幅部で増幅された画素信号を、探索信号に関連付けてアナログ信号からデジタル信号に変換するAD変換部と、を含む、固体撮像装置の駆動方法であって、前記画素から読み出される前記画素信号は、第1の動作により前記画素から順に読み出し輝度信号を含む第1の画素信号と、第2の動作により前記画素から順に読み出し輝度信号および読み出しリセット信号を含む第2の画素信号と、のうちの少なくともいずれかであり、前記読み出し回路に供給する前記探索信号について、前記第1の画素信号のときの第1の探索信号とで、探索レベルが反転した関係に設定する。

## [0017]

本発明の第3の観点の電子機器は、固体撮像装置と、前記固体撮像装置に被写体像を結像する光学系と、を有し、前記固体撮像装置は、光電変換を行う画素が配置された画素部と、前記画素から信号線に読み出される画素信号をアナログ信号からデジタル信号に変換するアナログデジタル(AD)変換機能を有する読み出し回路と、を含み、前記画素から読み出される前記画素信号は、第1の動作により前記画素から順に読み出される読み出し輝度信号を含む第1の画素信号と、第2の動作により前記画素から順に読み出される読み出し輝度信号および読み出しリセット信号を含む第2の画素信号と、のうちの少なくともいずれかであり、前記読み出し回路は、前記画素信号を増幅部と、前記増幅部で増幅された画素信号を、探索信号に関連付けてアナログ信号からデジタル信号に変換するAD変換部と、を含み、前記第1の画素信号のときの第1の探索信号と前記第2の画素信号のときの第2の探索信号とは、探索レベルが反転した関係に設定可能である。

## 【発明の効果】

#### [0018]

本発明によれば、動作モードや読み出し信号の信号形態にかかわらず読み出し回路を共用することが可能となり、ひいては、回路規模の低減、制御の容易化、低消費電力化を実現することができる。

【図面の簡単な説明】

[0019]

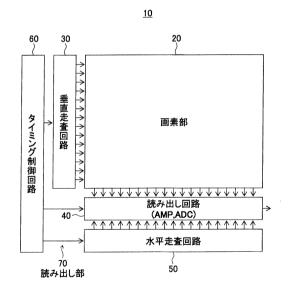

- 【図1】図1は、本発明の第1の実施形態に係る固体撮像装置の構成例を示すブロック図である。

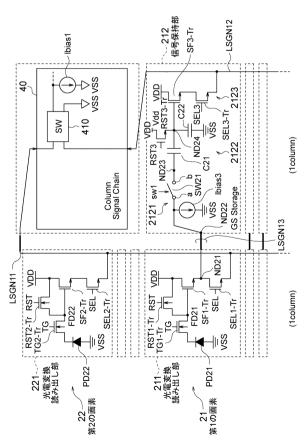

- 【図2】図2は、本発明の第1の実施形態に係る固体撮像装置の第1の画素および第2の画素の一例を示す回路図である。

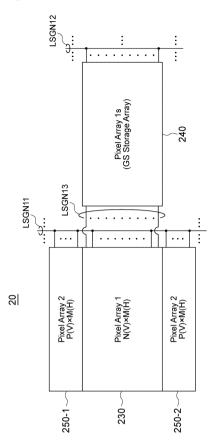

- 【図3】図3は、本発明の第1の実施形態に係る固体撮像装置の画素部における画素アレイについて説明するための図である。

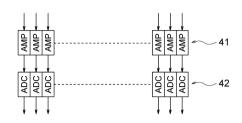

- 【図4】図4は、本発明の実施形態に係る固体撮像装置の画素部の列出力の読み出し系の 構成例を説明するための図である。

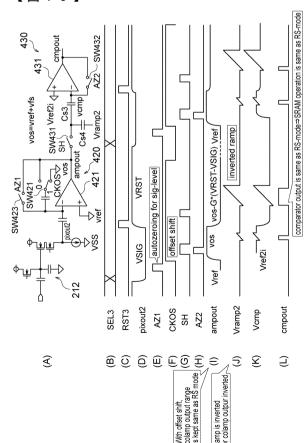

- 【図5】図5は、本発明の第1の実施形態に係る固体撮像装置のカラム読み出し回路の構成例を示す回路図である。

- 【図6】図6は、本第1の実施形態に係る固体撮像装置の積層構造について説明するための図である。

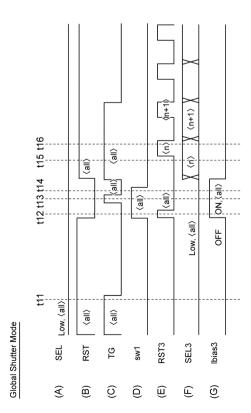

- 【図7】図7(A)~(D)は、本第1の実施形態に係る固体撮像装置のローリングシャッタモード時の主として画素部における読み出し動作を説明するためのタイミングチャートである。

- 【図8】図8(A)~(L)は、本第1の実施形態に係る固体撮像装置のローリングシャッタモード時の主としてカラム読み出し回路おける読み出し動作を説明するためのタイミ

10

20

30

40

10

20

30

40

50

ングチャートである。

【図9】図9(A)~(G)は、本第1の実施形態に係る固体撮像装置のグローバルシャッタモード時の主として画素部における読み出し動作を説明するためのタイミングチャートである。

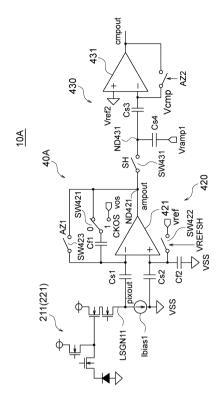

【図10】(A)~(L)は、本第1の実施形態に係る固体撮像装置のグローバルシャッタモード時の主としてカラム読み出し回路における読み出し動作を説明するためのタイミングチャートである。

【図11】図11は、本発明の第2の実施形態に係る固体撮像装置の画素およびカラム読み出し回路の構成例を示す図である。

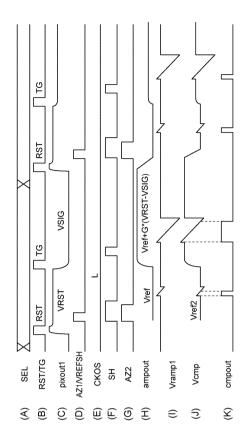

【図12】図12(A)~(K)は、本第2の実施形態に係る固体撮像装置の差動のローリングシャッタモード時の主としてカラム読み出し回路における読み出し動作を説明するためのタイミングチャートである。

【図13】図13は、本発明の第3の実施形態に係る固体撮像装置の第1の画素の構成例を示す図である。

【図14】図14(A)~(F)は、本第3の実施形態に係る固体撮像装置のグローバルシャッタモード時の主として画素部における読み出し動作を説明するためのタイミングチャートである。

【図15】図15(A)~(L)は、本第3の実施形態に係る固体撮像装置のグローバルシャッタモード時の主としてカラム読み出し回路における読み出し動作を説明するためのタイミングチャートである。

【図16】図16は、本第3の実施形態に係るカラム読み出し回路の第1のオペアンプの 構成例を示す回路図である。

【図17】図17は、差動のグローバルシャッタモード時の第1のオペアンプの入力レンジの制御の一例を説明するためのである。

【図18】図18は、本発明の第4の実施形態に係るカラム読み出し回路の構成例を示す 回路図である。

【図19】図19(A)および(B)は、本第4の実施形態に係るAD変換部に採用される反転二分探索法に対応した探索信号入力部の構成例を説明するための図である。

【図 2 0 】本発明の実施形態に係る固体撮像装置が適用される電子機器の構成の一例を示す図である。

【符号の説明】

[0020]

10,10A~10C·・・固体撮像装置、20,20A,20B·・・画素部、PD21,PD22·・・フォトダイオード、TG1-Tr、TG2-Tr・・・転送トランジスタ、RST1-Tr,RST2-Tr・・・リセットトランジスタ、SF1-Tr,SEL2-Tr,SF3-Tr・・・選択トランジスタ、SFL1-Tr,SEL2-Tr,SEL3-Tr・・・選択トランジスタ、FD21,FD22·・・フローティングディフュージョン、21·・・第1の画素、211·・・光電変換読み出し部、212·・・信号保持部、22·・・第2の画素、221·・・光電変換読み出し部、30·・・垂直走査回路、40,40C・・・読み出し回路(カラム読み出し回路)、420・・・増幅部、430・・・AD変換部、440・・・入力部、50・・・水平走査回路、60・・・タイミング制御回路、70・・・読み出し部、300・・・電子機器、310・・・CMOSイメージセンサ、320・・・光学系、330・・・信号処理回路(PRC)。

【発明を実施するための形態】

[0021]

以下、本発明の実施形態を図面に関連付けて説明する。

[0022]

(第1の実施形態)

図1は、本発明の第1の実施形態に係る固体撮像装置の構成例を示すブロック図である

本実施形態において、固体撮像装置10は、たとえばCMOSイメージセンサにより構成される。

# [0023]

この固体撮像装置10は、図1に示すように、撮像部としての画素部20、垂直走査回路(行走査回路)30、読み出し回路(カラム読み出し回路)40、水平走査回路(列走査回路)50、およびタイミング制御回路60を主構成要素として有している。

これらの構成要素のうち、たとえば垂直走査回路30、読み出し回路40、水平走査回路50、およびタイミング制御回路60により画素信号の読み出し部70が構成される。

## [0024]

本第1の実施形態において、固体撮像装置10は、後で詳述するように、画素部20において、画素として光電変換読み出し部および信号保持部を含む第1の画素と、光電変換読み出し部を含む第2の画素が混在されて、第1の動作であるローリングシャッタと第2の動作であるグローバルシャッタの両動作機能を併せ持つ、たとえば積層型のCMOSイメージセンサとして構成されている。

本第1の実施形態に係る固体撮像装置10において、画素部20は、複数の第1の画素の光電変換読み出し部が行列状に配置された第1の画素アレイと、複数の第1の画素の信号保持部が行列状に配置された保持部アレイと、複数の第2の画素の光電変換読み出し部が行列状に配置された第2の画素アレイと、を含んで構成されている。

そして、第1の動作であるローリングシャッタモード時に、第1の画素および第2の画素の光電変換読み出し部の読み出し信号が第1の垂直信号線にバイパス経路をたどることなく直ちに出力される。

また、第2の動作であるグローバルシャッタモード時に、第1の画素の信号保持部の保持信号が第2の垂直信号線に出力される。

#### [0025]

そして、第1の垂直信号線または第2の垂直信号線を伝送される画素読み出し信号に対してカラム読み出し回路40において、増幅処理およびAD変換処理が行われる。

本第1の実施形態に係る固体撮像装置10において、カラム読み出し回路40は、後で 詳述するように、動作モードや読み出し信号の信号形態(シングルエンドや差動等の信号) にかかわらず一つの回路構成で共用することが可能に形成されている。

### [0026]

以下、固体撮像装置10の各部の構成および機能の概要、特に、画素部20およびカラム読み出し回路40の構成および機能、それらに関連した読み出し処理、並びに、画素部20と読み出し部70の積層構造等について詳述する。

## [0027]

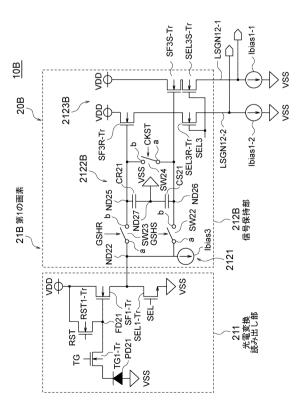

(第1の画素および第2の画素並びに画素部20の構成)

図 2 は、本発明の第 1 の実施形態に係る固体撮像装置 1 0 の第 1 の画素および第 2 の画素の一例を示す回路図である。

## [0028]

画素部20に配置される第1の画素21は、光電変換読み出し部211および信号保持部212を含んで構成されている。

画素部20に配置される第2の画素22は、光電変換読み出し部221を含んで構成されている。

# [0029]

第1の画素21の光電変換読み出し部211は、フォトダイオード(光電変換素子)と画素内アンプとを含んで構成される。

具体的には、この光電変換読み出し部211は、たとえば光電変換素子であるフォトダイオードPD21を有する。

このフォトダイオードPD21に対して、転送素子としての転送トランジスタTG1-Tr、リセット素子としてのリセットトランジスタRST1-Tr、ソースフォロワ素子 10

20

30

40

としてのソースフォロワトランジスタSF1-Tr、出力ノードND21、および選択素子(選択スイッチ)としての選択トランジスタSEL1-Trをそれぞれ一つずつ有する。

このように、第1の実施形態に係る第1の画素21の光電変換読み出し部211は、転送トランジスタTG1-Tr、リセットトランジスタRST1-Tr、ソースフォロワトランジスタSF1-Tr、および選択トランジスタSEL1-Trの4トランジスタ(4Tr)を含んで構成されている。

#### [0030]

本第1の実施形態に係る光電変換読み出し部211は、出力ノードND21が第1の画素21の信号保持部212の入力部に接続され、選択トランジスタSEL1-Tァを介して第1の垂直信号線LSGN11に接続されている。

光電変換読み出し部 2 1 1 は、ローリングシャッタモード時に第 1 の画素信号 p i x o u t 1 である読み出しリセット信号(信号電圧)(VRST1)および読み出し輝度信号(信号電圧)(VSIG1)を第 1 の垂直信号線 L S G N 1 1 に出力する。

光電変換読み出し部 2 1 1 は、グローバルシャッタモード時に第 2 の画素信号 p x o u t 2 である読み出し輝度信号(信号電圧)(VSIG1)および読み出しリセット信号(信号電圧)(VRST1)を信号保持部 2 1 2 に出力する。

## [0031]

本第1の実施形態において、第1の垂直信号線LSGN11はローリングシャッタモード時に定電流源Ibias1により駆動され、第2の垂直信号線LSGN12はグローバルシャッタモード時に定電流源Ibias1により駆動される。

定電流源Ibias1は、ローリングシャッタモード時とグローバルシャッタモード時 とで共用される。

定電流源 I b i a s 1 は、図 2 に示すように、スイッチ部 4 1 0 により動作モードに応じて接続先が切り替えられる。ローリングシャッタモード時には、第 1 の垂直信号線 L S G N 1 1 が定電流源 I b i a s 1 に接続され、第 2 の垂直信号線 L S G N 1 2 が基準電位 V S S (たとえばグランド)に接続される。一方、グローバルシャッタモード時には、第 2 の垂直信号線 L S G N 1 2 が定電流源 I b i a s 1 に接続され、第 1 の垂直信号線 L S G N 1 1 が基準電位 V S S (たとえばグランド)に接続される。

## [0032]

フォトダイオード P D 2 1 は、入射光量に応じた量の信号電荷(ここでは電子)を発生 し、蓄積する。

以下、信号電荷は電子であり、各トランジスタが n 型トランジスタである場合について 説明するが、信号電荷が正孔(ホール)であったり、各トランジスタが p 型トランジスタ であっても構わない。

また、本実施形態は、複数のフォトダイオードおよび転送トランジスタ間で、各トランジスタを共有している場合にも有効である。

# [0033]

光電変換読み出し部 2 1 1 の転送トランジスタTG1-Trは、フォトダイオードPD2 1 とフローティングディフュージョンFD 2 1 の間に接続され、制御線を通じてゲートに印加される制御信号TGにより制御される。

転送トランジスタTG1-Trは、制御信号TGがハイ(H)レベルの転送期間に選択されて導通状態となり、フォトダイオードPD21で光電変換され蓄積された電荷(電子)をフローティングディフュージョンFD21に転送する。

# [0034]

リセットトランジスタRST1-Trは、電源電位VDDとフローティングディフュージョンFD21の間に接続され、制御線を通じてゲートに印加される制御信号RSTにより制御される。

リセットトランジスタRST1・Trは、制御信号RSTがHレベルのリセット期間に選択されて導通状態となり、フローティングディフュージョンFD21を電源電圧VDDの電位にリセットする。

10

20

30

40

10

20

30

40

50

#### [0035]

ソースフォロワトランジスタSF1-Tァと選択トランジスタSEL1-Tァは、電源電位VDDと定電流源Ibias1により駆動される第1の垂直信号線LSGN11の間に直列に接続されている。

ソースフォロワトランジスタSF1-Trのソースと選択トランジスタSEL1-Tr のドレインとの接続点により出力ノードND21が形成されている。

この出力ノードND21と信号保持部212の入力部間の信号線LSGN13は、たとえば信号保持部212の入力部に配置された定電流源Ibias3により駆動される。

ソースフォロワトランジスタSF1・TrはフローティングディフュージョンFD21の電荷を電荷量に応じた電圧信号に変換した列出力の読み出しリセット信号(VRST1)および読み出し輝度信号(VSIG1)および読み出しリセット信号(VRST1)を出力ノードND21に出力する。

#### [0036]

ソースフォロワトランジスタSF1-TrのゲートにはフローティングディフュージョンFD21が接続され、選択トランジスタSEL1-Trは制御線を通じてゲートに印加される制御信号SELにより制御される。

選択トランジスタSEL1-Trは、制御信号SELがHレベルの選択期間に選択されて導通状態となる。これにより、ソースフォロワトランジスタSF1-TrはフローティングディフュージョンFD21の電荷を電荷量に応じた電圧信号に変換した読み出しリセット信号(VRST1)および読み出し輝度信号(VSIG1)を第1の垂直信号線LSGN11に出力する。

#### [0037]

第1の画素21の信号保持部212は、基本的に、定電流源Ibias3が接続されている入力部2121、サンプルホールド部2122、出力部2123、ノードND22~ND24を含んで構成されている。

## [0038]

定電流源Ibias3は、ノードND22と基準電位VSSとの間に接続され、たとえばグローバルシャッタ期間中の所定の期間にオン状態に制御される。

## [0039]

なお、定電流源Ibias3の代わりに、ノードND22と基準電位VSSとの間に接続され、たとえばグローバルシャッタ期間中の所定の期間にオン状態に制御されるスイッチ素子を設けてもよい。

#### [0040]

サンプルホールド部 2 1 2 2 は、第 2 の期間であるグローバルシャッタ期間に、サンプルホールド部 2 1 2 2 の信号保持キャパシタを光電変換読み出し部 2 1 1 の出力ノード N D 2 1 と選択的に接続するスイッチ素子 S W 2 1、第 1 の画素 2 1 の光電変換読み出し部 2 1 1 の出力ノード N D 2 1 から出力される信号を保持可能な信号保持キャパシタ C 2 1 、C 2 2 と、ノー N D 2 4 をリセットするためのリセットトランジスタ R S T 3 - T r を有する。

スイッチ素子SW21の端子aが第3の信号線LSGN13に接続された入力ノードND22と接続され、端子bがサンプルホールド部2122側と接続されたノードND23に接続されている

スイッチ素子SW21は、たとえば信号sw1がハイレベルの期間に端子aとbが接続されて導通状態となる。

信号保持キャパシタC21は、ノードND23とノードND24との間に接続されている。

信号保持キャパシタC22は、ノードND24と基準電位VSSとの間に接続されている。

## [0041]

リセットトランジスタRST3-Trは、電源電位VDDとノードND24との間に接

続され、制御線を通じてゲートに印加される制御信号RST3により制御される。

リセットトランジスタRST3・Trは、制御信号RST3がHレベルのリセット期間に選択されて導通状態となり、ノードND24(およびキャパシタC21、C22)を電源電圧VDDの電位にリセットする。

## [0042]

出力部2123は、第2の期間であるグローバルシャッタ期間に信号保持キャパシタC21、C22に保持された信号を保持電圧に応じて出力するソースフォロワトランジスタSF3-Trを含み、保持した信号を選択的に選択トランジスタSEL3-Trを介して定電流源Ibias1により駆動される第2の垂直信号線LSGN12に出力する。

#### [0043]

ソースフォロワトランジスタSF3・Trと選択トランジスタSEL3・Trは、電源電位VDDと定電流源Ibias1により駆動される第2の垂直信号線LSGN12の間に直列に接続されている。

## [0044]

ソースフォロワトランジスタSF3-TrのゲートにはノードND24が接続され、選択トランジスタSEL3-Trは制御線を通じてゲートに印加される制御信号SEL3により制御される。

選択トランジスタSEL3・Trは、制御信号SEL3がHレベルの選択期間に選択されて導通状態となる。これにより、ソースフォロワトランジスタSF3・Trは信号保持キャパシタC21、C22の保持電圧に応じた列出力の読み出し電圧(VRST,VSIG)を第2の垂直信号線LSGN12に出力する。

#### [0045]

なお、上述した信号保持部 2 1 2 の構成は、一例であり、第 2 の期間であるグローバルシャッタ期間に、上述した光電変換読み出し部 2 1 1 の出力する読み出し輝度信号(VSIG1)および読み出しリセット信号(VRST1)を保持する機能を備える回路であればその構成を問わない。

### [0046]

画素部20に配置される第2の画素22は、光電変換読み出し部221を含んで構成されている。

第2の画素22の光電変換読み出し部221は、上述した第1の画素21の光電変換読み出し部211と同様の構成を有する。

# [0047]

すなわち、第2の画素22の光電変換読み出し部221は、フォトダイオード(光電変換素子)と画素内アンプとを含んで構成される。

具体的には、この光電変換読み出し部221は、たとえば光電変換素子であるフォトダイオードPD22を有する。

このフォトダイオード P D 2 2 に対して、転送素子としての転送トランジスタ T G 2 - T r 、リセット素子としてのリセットトランジスタ R S T 2 - T r 、ソースフォロワ素子としてのソースフォロワトランジスタ S F 2 - T r 、および選択素子(選択スイッチ)としての選択トランジスタ S E L 2 - T r をそれぞれ一つずつ有する。

このように、第1の実施形態に係る第2の画素22の光電変換読み出し部221は、転送トランジスタTG2-Tr、リセットトランジスタRST2-Tr、ソースフォロワトランジスタSF2-Tr、および選択トランジスタSEL2-Trの4トランジスタ(4Tr)を含んで構成されている。

#### [0048]

本第1の実施形態に係る光電変換読み出し部221は、ローリングシャッタモード時に読み出しリセット信号(信号電圧)(VRST2)および読み出し輝度信号(信号電圧)(VSIG2)を第1の垂直信号線LSGN11に出力する。

## [0049]

フォトダイオードPD22は、入射光量に応じた量の信号電荷(ここでは電子)を発生

10

20

30

40

#### し、蓄積する。

信号電荷は電子であり、各トランジスタが n 型トランジスタである場合について説明するが、信号電荷が正孔(ホール)であったり、各トランジスタが p 型トランジスタであっても構わない。

また、本実施形態は、複数のフォトダイオードと転送トランジスタ間で、各トランジスタを共有している場合にも有効である。

#### [0050]

光電変換読み出し部 2 2 1 の転送トランジスタTG 2 - Trは、フォトダイオードPD 2 2 とフローティングディフュージョンFD 2 2 の間に接続され、制御線を通じてゲート に印加される制御信号TGにより制御される。

転送トランジスタTG2-Trは、制御信号TGがHレベルの転送期間に選択されて導通状態となり、フォトダイオードPD22で光電変換され蓄積された電荷(電子)をフローティングディフュージョンFD22に転送する。

## [0051]

リセットトランジスタRST2-Trは、電源電位VDDとフローティングディフュージョンFD22の間に接続され、制御線を通じてゲートに印加される制御信号RSTにより制御される。

リセットトランジスタRST2・Trは、制御信号RSTがHレベルのリセット期間に選択されて導通状態となり、フローティングディフュージョンFD22を電源電圧VDDの電位にリセットする。

### [0052]

ソースフォロワトランジスタSF2・Trと選択トランジスタSEL2・Trは、電源電位VDDと定電流源Ibias1により駆動される第1の垂直信号線LSGN11の間に直列に接続されている。

#### [0053]

ソースフォロワトランジスタSF2-TrのゲートにはフローティングディフュージョンFD22が接続され、選択トランジスタSEL2-Trは制御線を通じてゲートに印加される制御信号SELにより制御される。

選択トランジスタSEL2-Trは、制御信号SELがHレベルの選択期間に選択されて導通状態となる。これにより、ソースフォロワトランジスタSF2-TrはフローティングディフュージョンFD22の電荷を電荷量に応じた電圧信号に変換した列出力の読み出しりセット信号(VRST2)および読み出し輝度信号(VSIG2)を第1の垂直信号線LSGN11に出力する。

### [0054]

本第1の実施形態に係る画素部20は、以上のような構成を有する第1の画素21および第2の画素22が、たとえば図3に示すように、画素アレイとして配列され、複数の画素アレイが組み合わされて構成されている。

## [0055]

図3は、本発明の第1の実施形態に係る固体撮像装置10の画素部20における画素アレイについて説明するための図である。

# [0056]

第1の実施形態に係る固体撮像装置10の画素部20は、第1の画素アレイ230、保持部アレイ240、上側の第2の画素アレイ250-1、および下側の第2の画素アレイ250-2を含んで構成されている。

#### [0057]

第1の画素アレイ230は、複数の第1の画素21の光電変換読み出し部211がN行×M列の2次元の行列状(マトリクス状)に配列されている。

第1の画素アレイ230は、たとえば16:9のアスペクト比の画像が出力可能なように、複数の第1の画素21の光電変換読み出し部211がN行×M列の2次元の行列状(マトリクス状)に配列されている。

10

20

30

40

#### [0058]

保持部アレイ240は、複数の第1の画素21の信号保持部212が、第1の画素アレイ230に対応してN行×M列の2次元の行列状(マトリクス状)に配列されている。

保持部アレイ240は、第1の画素アレイ230と同様に、たとえば16:9のアスペクト比の画像が出力可能なように、複数の第1の画素21の信号保持部212がN行×M列の2次元の行列状(マトリクス状)に配列されている。

#### [0059]

上側の第2の画素アレイ250-1は、複数の第2の画素22の光電変換読み出し部2 21がP(P<N)行×M列の2次元の行列状(マトリクス状)に配列されている。

#### [0060]

同様に、下側の第2の画素アレイ250-2は、複数の第2の画素22の光電変換読み出し部221がP(P<N)行×M列の2次元の行列状(マトリクス状)に配列されている。

## [0061]

図3の例において、第2の画素アレイ250-1,250-2は、第1の画素アレイ230の第1の垂直信号線LSGN11の配線方向の両側(上側および下側)に配置されている。なお、第2の画素アレイ250は、第1の画素アレイ230の第1の垂直信号線LSGN11の配線方向の両側のうち少なくとも一方側に配置されていてもよい。

## [0062]

第2の画素アレイ250-1,250-2は、ローリングシャッタモード時に、第1の画素アレイ230とともに、アクティブとされ、全体としてたとえば1:1のアスペクト比の画像を出力可能なように、複数の第2の画素22の光電変換読み出し部221がP(P<N)行×M列の2次元の行列状(マトリクス状)に配列されている。上記アスペクト比は4:3など任意の比率でも良い。

#### [0063]

なお、ローリングシャッタモード時には、第1の画素アレイ230を電子式手ぶれ補正用の領域として利用し、16:9のアスペクト比の画像を出力するようにしてもよい。

#### [0064]

また、第1の画素アレイ230と第2の画素アレイ250-1,250-2の同一列の 光電変換読み出し部211は、共通の第1の垂直信号線LSGN11に接続されている。

### [0065]

固体撮像装置10が、後述するように、第1の基板(上基板)と第2の基板(下基板)の積層構造を有する場合、第1の基板に第1の画素アレイ230と第2の画素アレイ250-1,250-2が形成され、第2の基板に保持部アレイ240が第1の画素アレイ230と対向するように形成される。

## [0066]

画素部20は、読み出し部70の制御の下、第1の動作であるローリングシャッタモード時には、第1の画素アレイ230および第2の画素アレイ250-1,250-2をアクティブにして順次画素がアクセスされて画素信号の読み出しが行単位で行われる。

## [0067]

また、画素部20は、読み出し部70の制御の下、第2の動作であるグローバルシャッタモード時には、第1の画素アレイ230および第2の画素アレイ250-1,250-2の光電変換読み出し部221における選択トランジスタSEL1-Tr,SEL2-Trを非選択状態とした状態(信号SELがローレベル)で、第1の画素アレイ230および保持部アレイ240をアクティブにして画素信号の読み出しが行われる。

# [0068]

画素部 2 0 において、たとえば転送トランジスタTG-Tr、リセットトランジスタRST-Tr、および選択トランジスタSEL-Trの各ゲートが行単位で接続されていることから、 1 行分の各画素について同時並列的に行われる。

## [0069]

50

10

20

30

10

20

30

40

50

画素部20には、画素が(N+2P)行×M列配置されているので、各制御線LSEL、LRST、LTGはそれぞれ(N+2P)本、第1の垂直信号線LSGN11および第 2の垂直信号線LSGN12はそれぞれM本ある。

## [0070]

垂直走査回路30は、タイミング制御回路60の制御に応じてシャッタ行および読み出し行において行走査制御線を通して第1の画素21の光電変換読み出し部211および信号保持部212、並びに第2の画素22の光電変換読み出し部221の駆動を行う。

また、垂直走査回路30は、アドレス信号に従い、信号の読み出しを行うリード行と、フォトダイオードPDに蓄積された電荷をリセットするシャッタ行の行アドレスの行選択信号を出力する。

## [0071]

カラム読み出し回路 4 0 は、画素部 2 0 の各列出力に対応して配置された複数の列(カラム)信号処理回路(図示せず)を含み、複数の列信号処理回路で列並列処理が可能に構成されてもよい。

カラム読み出し回路 4 0 は、第 1 の動作であるローリングシャッタモード時に、第 1 の垂直信号線 L S G N 1 1 に、第 1 の画素 2 1 の光電変換読み出し部 2 1 1 および第 2 の画素 2 2 の光電変換読み出し部 2 2 1 から読み出された第 1 の画素信号 p i x o u t 1 ( V S L 1 )、並びに、第 2 の動作であるグローバルシャッタモード時に、第 2 の垂直信号線 L S G N 1 2 に、第 1 の画素 2 1 の信号保持部 2 1 2 から読み出された第 2 の画素信号 p i x o u t 2 ( V S L 2 ) に対して、増幅処理および A D 変換処理を行う。

### [0072]

ここで、第1の画素信号pixout1(VSL1)は、第1の動作であるローリングシャッタモード時に画素(本例では第1の画素21の光電変換読み出し部211および第2の画素22の光電変換読み出し部221)から順に読み出される読み出しリセット信号VRSTおよび読み出し輝度信号VSIGを含む画素読み出し信号をいう。

第2の画素信号pixout2(VSL2)は、第2の動作であるグローバルシャッタモード時に画素(本例では第1の画素21の光電変換読み出し部211、さらに信号保持部212)から順に読み出される読み出し輝度信号VSIGおよび読み出しリセット信号VRSTを含む画素読み出し信号をいう。

## [0073]

本第1の実施形態に係る固体撮像装置10において、カラム読み出し回路40は、動作モードや読み出し信号の信号形態(シングルエンドや差動等の信号)にかかわらず一つの回路構成で共用することが可能に形成されている。

### [0074]

カラム読み出し回路 4 0 は、たとえば図 4 に示すように、アンプ(AMP,増幅器) 4 1 および A D C (アナログデジタルコンバータ; A D 変換器) 4 2 を含んで構成される。カラム読み出し回路 4 0 は、図 5 に関連付けて説明するように、第 1 の画素信号 p i x o u t 1 (V S L 1) および第 2 の画素信号 p i x o u t 2 (V S L 2) を増幅する増幅部 4 2 0、並びに、増幅部 4 2 0で増幅された画素部 2 0 の各列出力のアナログ読み出し

部420、並びに、増幅部420で増幅された画素部20の各列出力のアナログ読み出し信号VSL1、VSL2をデジタル信号に変換するAD変換器を含むAD変換部430により構成されている。

#### [0075]

本第1の実施形態において、カラム読み出し回路40は、たとえば各列の列信号処理回路に、第1の垂直信号線LSGN11を伝送された信号と第2の垂直信号線LSGN12を伝送された信号を動作モードに応じて選択的に入力させる回路が配置されている。

## [0076]

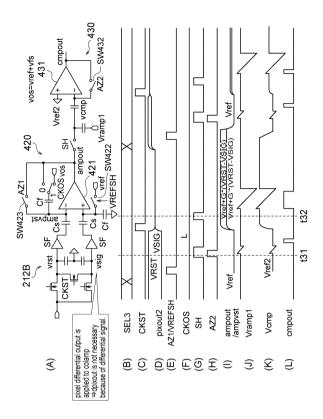

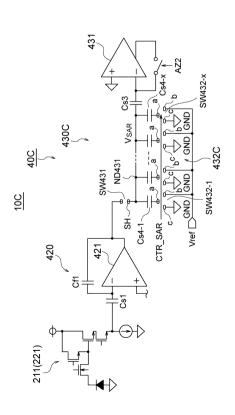

図 5 は、本発明の第 1 の実施形態に係る固体撮像装置のカラム読み出し回路の構成例を示す回路図である。

## [0077]

カラム読み出し回路40は、図5に示すように、第1の画素信号pixout1(VS

10

20

30

40

50

L 1 )、第2の画素信号pixout2(VSL2)を増幅する増幅部420、および増幅部420で増幅された画素信号を、探索信号(たとえばVramp)に関連付けてアナログ信号からデジタル信号に変換するAD変換部430が縦続接続されて構成されている

また、カラム読み出し回路40は、入力段にモード信号MODx(x=1,2,3,4,・・)に応じて画素の読み出し信号pixoutを、増幅部420に配置される演算増幅器の2つの入力端子に選択的に入力させる入力部440が配置されている。

## [0078]

増幅部420は、第1の演算増幅器(以下、オペアンプという)421、第1のサンプリングキャパシタ(入力キャパシタ)Cs1、第1の帰還キャパシタ(フィードバックキャパシタ)Cf1、第2のサンプリングキャパシタCs2、第2の帰還キャパシタCf2、第1のスイッチ部SW421、第2のスイッチ部SW422、第1のオートゼロスイッチ部SW423、出力ノードND421、オフセット電位VOS、および参照電位Vrefを含んで構成されている。

## [0079]

第1のオペアンプ421は、第1の入力端子、本実施形態では反転入力端子(-)、および第2の入力端子、本実施形態では非反転入力端子(+)の2つの入力端子を有し、第1の入力端子(-)への入力電圧Vin1と第2の入力端子(+)への入力電圧Vin2の差分をゲインA0倍して(増幅して)アンプ出力ampoutを得る。ここで、ゲイン(A0)が十分に高ければ、第1のスイッチ部SW421または第1のオートゼロスイッチ部SW423を介して負帰還回路が構成される時に、第1の入力端子(-)と第2の入力端子(+)は仮想接地される。

第1のオペアンプ421の出力端子は、出力ノードND421に接続されている。

#### [0800]

第1のサンプリングキャパシタCs1は、第1の画素信号または第2の画素信号の入力ライン端としての入力部440の第1の出力端子TO1と第1のオペアンプ421の第1の入力端子(-)との間に接続されている。

#### [0081]

第2のサンプリングキャパシタCs2は、第1の画素信号または第2の画素信号の入力ライン端としての入力部440の第2の出力端子TO2と第1のオペアンプ421の第2の入力端子(+)との間に接続されている。

# [0082]

入力部440の第1の出力端子TO1からは、4つのモード信号MOD1~MOD4に応じて以下の画素信号(信号電圧)が供給される。

第1のモード信号MOD1のときは、ローリングシャッタモード時のシングルエンドの第1の画素信号pixout1が、入力部440の第1の出力端子TO1から供給される

第 2 のモード信号 M O D 2 のときは、グローバルシャッタモード時のシングルエンドの第 2 の画素信号 p i x o u t 2 が、入力部 4 4 0 の第 1 の出力端子 T O 1 から供給される

第3のモード信号MOD3のときは、差動ローリングシャッタモード時の差動信号のうちの一方の第1の画素信号pixout1d1が、入力部440の第1の出力端子TO1から供給される。

第4のモード信号MOD4のときは、差動グローバルシャッタモード時の差動信号のうちの一方の第2の画素信号pixout2d1が、入力部440の第1の出力端子TO1から供給される。

#### [0083]

入力部440の第2の出力端子TO2からは、4つのモード信号MOD1~MOD4に応じて以下の画素信号(信号電圧)が供給される。

第1のモード信号MOD1のときは、画素信号は入力部440の第2の出力端子TO2

から供給されない。

第2のモード信号MOD2のときは、画素信号は入力部440の第2の出力端子TO2から供給されない。

第3のモード信号MOD3のときは、差動ローリングシャッタモード時の差動信号のうちの他方の第1の画素信号pixout1d2が、入力部440の第2の出力端子TO2から供給される。

第4のモード信号MOD4のときは、差動グローバルシャッタモード時の差動信号のうちの他方の第2の画素信号pixout2d2が、入力部440の第2の出力端子TO2から供給される。

[0084]

第1の帰還キャパシタCf1は、一方の電極端が第1のオペアンプ421の第1の入力端子(-)に接続され、他方の電極端が第1のスイッチ部SW421に接続されている。

[0085]

第2の帰還キャパシタCf2は、一方の電極端が第1のオペアンプ421の第2の入力端子(+)に接続され、他方の電極端が基準電位VSS(たとえばグランドGND)に接続されている。

[0086]

第1のスイッチ部SW421は、端子aが第1のサンプリングキャパシタCf1の他方の電極端に接続され、端子bが出力ノードND421(第1のオペアンプ421の出力端子)に接続され、端子cがオフセット電位VOSに接続されている。

第1のスイッチ部SW421は、たとえば制御信号CKOSがローレベル(L)のときは端子aを端子bと接続し、制御信号CKOSがハイレベル(H)のときは端子aを端子cと接続する。

[0087]

本実施形態において、制御信号 C K O S は、入力部 4 4 0 に供給されるモード信号が、第 1 のモード信号 M O D 1 (シングルエンドのローリングシャッタモード)、第 3 のモード信号 M O D 3 (差動のローリングシャッタモード)、および第 4 のモード信号 M O D 4 (差動のグローバルシャッタモード)のとき L レベルで供給され、第 2 のモード信号 M O D 2 (シングルエンドのグローバルシャッタモード)のときクロックで供給される。

すなわち、第1の帰還キャパシタCf1は、入力部440に供給されるモード信号が、第1のモード信号MOD1(シングルエンドのローリングシャッタモード)、第3のモード信号MOD3(差動のローリングシャッタモード)、および第4のモード信号MOD4(差動のグローバルシャッタモード)のとき、第1のオペアンプ421の第1の入力端子(・)と出力ノードND421との間に接続される。

第1の帰還キャパシタCf1は、入力部440に供給されるモード信号が、第2のモード信号MOD2(シングルエンドのグローバルシャッタモード)のとき、第1のオペアンプ421の第1の入力端子(-)は、出力ノードND421と接続される状態と、オフセット電位VOSとの間に接続される状態を遷移する。

[0088]

本第1の実施形態において、オフセット電位VOSは、参照電位Vrefより電圧Vfs分高い値(VOS=Vref+Vfs)に設定される。

[0089]

第2のスイッチ部SW422は、端子aが第1のオペアンプ421の第2の入力端子(+)に接続され、端子bが参照電位Vrefに接続されている。

第2のスイッチ部SW422は、制御信号VREFSHがクロックとして供給され、クロックがHレベルのとき端子aと端子bが導通状態(オン状態)に保持され、Lレベルのとき端子aと端子bは非導通状態(オフ状態)に保持される。

第2のスイッチ部SW422は、入力部440に供給されるモード信号が、第1のモード信号MOD1(シングルエンドのローリングシャッタモード)、第2のモード信号MOD2(シングルエンドのグローバルシャッタモード)のとき、端子aと端子bが導通状態

10

20

30

40

(オン状態)に保持され、第3のモード信号MOD3(差動のローリングシャッタモード)、第4のモード信号MOD4(差動のグローバルシャッタモード)のとき、導通状態(オン状態)と非導通状態(オフ状態)を遷移される。

## [0090]

オートゼロスイッチ部SW423は、端子aが第1のオペアンプ421の第1の入力端子(-)に接続され、端子bが出力ノードND421(第1のオペアンプ421の出力端子)に接続されている。

オートゼロスイッチ部SW423は、制御信号AZ1がHレベルのとき端子aと端子bが導通状態(オン状態)に保持され、Lレベルのとき端子aと端子bは非導通状態(オフ状態)に保持される。

第 1 のオペアンプ 4 2 1 は、オートゼロスイッチ部 S W 4 2 3 が導通状態のとき、リセット状態となる。

#### [0091]

A D 変換部 4 3 0 は、第 2 のオペアンプ 4 3 1、探索信号入力部 4 3 2、サンプルホールドスイッチ部 S W 4 3 1、第 3 のサンプリングキャパシタ C s 3、第 2 のオートゼロスイッチ部 S W 4 3 2、入力ノード N D 4 3 1、および出力ノード N D 4 3 2 を含んで構成されている。

## [0092]

第2のオペアンプ431は、第1の入力端子、本実施形態では反転入力端子(-)、および第2の入力端子、本実施形態では非反転入力端子(+)の2つの入力端子を有する。第2のオペアンプ431の第1の入力端子(-)に供給される入力信号電圧Vcmpは、AD変換中には、第3のサンプリングキャパシタCs3に保持された電圧、第4のサンプリングキャパシタCs4に保持された電圧、および探索信号入力部432による探索信号Vrampを合成した信号電圧である。

## [0093]

ここでは、探索信号Vrampは、ある傾きを持った線形に変化するスロープ波形の信号である。

本例では、探索信号Vrampとしては、たとえば図5中の第1の探索信号Vramp 1のように左側がレベルが高く右側がレベルが低い右下がりのスロープ波形として供給される。

また、本例では、探索信号Vrampとしては、たとえば図5中の第2の探索信号Vramp2のように左側がレベルが低く右側がレベルが高い右上がりのスロープ波形として供給される。

第1の探索信号Vramp1と第2の探索信号Vramp2は、探索レベル、ここではスロープ波形のレベルが反転した関係にある。

#### [0094]

本実施形態において、探索信号 V r a m p として、入力部 4 4 0 に供給されるモード信号が、第 1 のモード信号 M O D 1 (シングルエンドのローリングシャッタモード)、第 3 のモード信号 M O D 3 (差動のローリングシャッタモード)、第 4 のモード信号 M O D 4 (差動のグローバルシャッタモード)のとき第 1 の探索信号 V r a m p 1 が探索信号入力部 4 3 2 に供給される。

一方、本実施形態において、探索信号 V r a m p として、入力部 4 4 0 に供給されるモード信号が、第 2 のモード信号 M O D 2 (シングルエンドのグローバルシャッタモード) のとき第 2 の探索信号 V r a m p 2 が探索信号入力部 4 3 2 に供給される。

## [0095]

図 5 の探索信号入力部 4 3 2 は、第 4 のサンプリングキャパシタ(入力キャパシタ) C s 4 を含んで構成されている。

第4のサンプリングキャパシタC s 4 は、入力ノードN D 4 3 1 と探索信号 V r a m p の供給ラインとの間に接続されている。

## [0096]

50

10

20

30

10

20

30

40

50

第2のオペアンプ431は、第1の入力端子(-)に第3のサンプリングキャパシタCs3を介して入力される入力信号電圧Vcmpと第2の入力端子(+)に供給される参照電位Vref2とを比較し、入力信号電圧Vcmpが参照電位Vref2と交差すると、比較出力信号cmpoutをLレベルからHレベルに、あるいはHレベルからLレベルに切り替える。この交差するまでの時間を図示しないカウンタで測定することにより、AD変換が行われる。

このように、第2のオペアンプ431は、比較器として機能する。

## [0097]

第3のサンプリングキャパシタ(入力キャパシタ) Cs3は、入力ノード ND431と 第2のオペアンプ431の第1の入力端子(-)との間に接続されている。

[0098]

サンプルホールドスイッチ部 S W 4 3 1 は、端子 a が増幅部 4 2 0 の出力ノード N D 4 2 1 に接続され、端子 b が入力ノード N D 4 3 1 に接続されている。

サンプルホールドスイッチ部SW431は、たとえば制御信号SHがHレベルのとき端子aと端子bが導通状態(オン状態)に保持され、Lレベルのとき端子aと端子bは非導通状態(オフ状態)に保持される。

A D 変換部 4 3 0 は、サンプルホールドスイッチ部 S W 4 3 1 が導通状態のときに、増幅部 4 2 0 のアンプ出力 a m p o u t を入力ノード N D 4 3 1 に入力させる。

[0099]

オートゼロスイッチ部SW432は、たとえば端子aが第2のオペアンプ431の第1の入力端子(-)に接続され、端子bが出力ノードND432(第2のオペアンプ431の出力端子)に接続されている。

オートゼロスイッチ部SW432は、制御信号AZ2がHレベルのとき端子aと端子bが導通状態(オン状態)に保持され、Lレベルのとき端子aと端子bは非導通状態(オフ状態)に保持される。

第2のオペアンプ431は、オートゼロスイッチ部SW432が導通状態のとき、リセット状態となる。

[0100]

以上の構成を有するカラム読み出し回路40においては、第1のモード信号MOD1に応じたシングルエンド信号の第1の画素信号pixout1(VSL1)が増幅部420の第1のサンプリングキャパシタCs1に入力される場合、増幅部420の第1の帰還キャパシタCf1は第1のスイッチ部SW421により出力ノードND421(第1のオペアンプ421の出力端子)に接続され、第1のオペアンプ421の第2の入力端子(+)が参照電位Vrefに接続される。

このとき、AD変換部430には、探索信号入力部432を通して右下がりのスロープ 波形の第1の探索信号Vramp1が供給される。

[0101]

また、カラム読み出し回路40においては、第2のモード信号MOD2に応じたシングルエンド信号の第2の画素信号pixout2(VSL2)が増幅部420第1のサンプリングキャパシタCs1に入力される場合、増幅部420の帰還キャパシタCf1は第1のスイッチ部SW421によりオフセット電位VOSまたは出力ノードND421(第1のオペアンプ421の出力端子)に接続され、第1のオペアンプ421の第2の入力端子(+)が参照電位Vrefに接続される。

このとき、AD変換部430には、探索信号入力部432を通して第1の探索信号Vramp1とはレベルが反転した関係にある右上がりのスロープ波形の第2の探索信号Vramp2が供給される。

[0102]

また、カラム読み出し回路40においては、第3のモード信号MOD3に応じた差動信号の第1の画素信号pixout1d1(VSL1D1)、pixout1d2(VSL1D2)が増幅部420の第1のサンプリングキャパシタCs1および第2のサンプリン

10

20

30

40

50

グキャパシタC S 2 に入力される場合、増幅部 4 2 0 の帰還キャパシタC f 1 は第 1 のスイッチ部 S W 4 2 1 により出力ノード N D 4 2 1 (第 1 のオペアンプ 4 2 1 の出力端子)に接続される。

このとき、AD変換部430には、探索信号入力部432を通して右下がりのスロープ 波形の第1の探索信号Vramp1が供給される。

#### [0103]

また、カラム読み出し回路40においては、第4のモード信号MOD4に応じた差動信号の第2の画素信号pixout2d1(VSL2D1)、pixout2d2(VSL2D2)が増幅部420の第1のサンプリングキャパシタCs1および第2のサンプリングキャパシタCs2に入力される場合、増幅部420の帰還キャパシタCf1は第1のスイッチ部SW421により出力ノードND421(第1のオペアンプ421の出力端子)に接続される。

このとき、 A D 変換部 4 3 0 には、探索信号入力部 4 3 2 を通して右下がりのスロープ 波形の第 1 の探索信号 V r a m p 1 が供給される。

### [0104]

このように、本第1の実施形態のカラム読み出し回路40は、第1のモード信号MOD 1、第2のモード信号MOD2、第3のモード信号MOD3、および第4のモード信号MOD4に応じた画素信号を処理可能に構成されている。

ただし、本第1の実施形態において、画素部20は第1のモード信号MOD1および第 2のモード信号MOD2に応じた画素信号を生成するように構成されている。

したがって、本第1の実施形態のカラム読み出し回路40は、第1のモード信号MOD 1に応じたローリングシャッタモード時のシングルエンドの第1の画素信号pixout 1(VSL1)、および第2のモード信号MOD2に応じたグローバルシャッタモード時のシングルエンドの第2の画素信号pixout2(VSL2)を処理することになる。

#### [0105]

水平走査回路50は、カラム読み出し回路40のADC等の複数の列信号処理回路で処理された信号を走査して水平方向に転送し、図示しない信号処理回路に出力する。

#### [0106]

タイミング制御回路60は、画素部20、垂直走査回路30、カラム読み出し回路40、水平走査回路50等の信号処理に必要なタイミング信号を生成する。

### [0107]

本第1の実施形態において、読み出し部70は、第1の動作であるローリングシャッタモード時に、第1の画素アレイ230および第2の画素アレイ250-1,250-2をアクティブにして順次画素をアクセスさせて、シングルエンドの第1の画素信号pixout1の読み出しを行単位で行う。

## [0108]

本第1の実施形態において、読み出し部70は、第2の動作であるグローバルシャッタモード時に、第1の画素アレイ230および第2の画素アレイ250-1,250-2の光電変換読み出し部221における選択トランジスタSEL1-Tr.SEL2-Trを非選択状態とした状態(信号SELがローレベル)で、第1の画素アレイ230および保持部アレイ240をアクティブにして、シングルエンドの第2の画素信号pixout2の読み出しを行う。

## [0109]

# (固体撮像装置10の積層構造)

次に、本第1の実施形態に係る固体撮像装置10の積層構造について説明する。

## [0110]

図 6 は、本第 1 の実施形態に係る固体撮像装置 1 0 の積層構造について説明するための図である。

## [0111]

本第1の実施形態に係る固体撮像装置10は、第1の基板(上基板)110と第2の基

板(下基板)120の積層構造を有する。

固体撮像装置10は、たとえばウェハレベルで貼り合わせた後、ダイシングで切り出した積層構造の撮像装置として形成される。

本例では、第2の基板120上に第1の基板110が積層された構造を有する。

## [0112]

第1の基板110には、その中央部を中心として画素部20の各第1の画素21の光電 変換読み出し部211が配列された第1の画素アレイ230が形成され、第1の画素アレ イ230の第1の垂直信号線LSGN11の配線方向の両側(上側および下側)に第2の 画素アレイ250-1,250-2が形成されている。

また、第1の基板110には、第1の垂直信号線LSGN11が形成されている。

## [0113]

このように、本第1の実施形態においては、第1の基板110には、第1の画素21の 光電変換読み出し部211および第2の画素22の光電変換読み出し部221が行列状に 形成されている。

#### [0114]

第2の基板120には、その中央部を中心として第1の画素アレイ230の各光電変換読み出し部211の出力ノードND21と接続される各第1の画素21の信号保持部212がマトリクス状に配列された保持部アレイ240(領域121)および第2の垂直信号線LSGN12が形成されている。

そして、保持部アレイ240の周囲、図6の例では、図中の上側および下側にカラム読み出し回路40用の領域122,123が形成されている。なお、カラム読み出し回路40は、保持部アレイ240の領域121の上側および下側のいずれかに配置されるように構成してもよい。

また、保持部アレイ240の側部側に垂直走査回路30用の領域124や、デジタル系や出力系の領域125が形成されている。

また、第2の基板120には、垂直走査回路30、水平走査回路50、およびタイミング制御回路60も形成されてもよい。

# [0115]

このような積層構造において、第1の基板110の第1の画素アレイ230の各光電変換読み出し部211の出力ノードND21と第2の基板120の各第1の画素21の信号保持部212の入力ノードND22とが、たとえば図2に示すように、それぞれビア(Die-to-Die Via)やマイクロバンプ等を用いて電気的な接続が行われている

また、第1の基板110の第1の垂直信号線LSGN11と第2の基板120のカラム 読み出し回路40の入力部とが、たとえば図2に示すように、それぞれビア(Die・t o・Die Via)やマイクロバンプ等を用いて電気的な接続が行われている。

# [0116]

(固体撮像装置10の読み出し動作)

以上、固体撮像装置10の各部の特徴的な構成および機能について説明した。

次に、本第1の実施形態に係る固体撮像装置10のローリングシャッタモード時のシングルエンドの第1の画素信号およびグローバルシャッタモード時のシングルエンドの第2の画素信号の読み出し動作等について詳述する。

#### [0117]

(ローリングシャッタモード時の読み出し動作)

次に、ローリングシャッタモード時の読み出し動作について説明する。

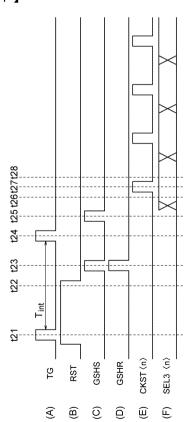

図7(A)~(D)は、本第1の実施形態に係る固体撮像装置のローリングシャッタモード時の主として画素部における読み出し動作を説明するためのタイミングチャートである。

図8(A)~(L)は、本第1の実施形態に係る固体撮像装置のローリングシャッタモード時の主としてカラム読み出し回路における読み出し動作を説明するためのタイミング

10

20

30

40

チャートである。

## [0118]

図7(A)は第1の画素21の光電変換読み出し部211および第2の画素22の光電変換読み出し部221の選択トランジスタSEL1-Tr、SEL2-Trの制御信号SELを示している。図7(B)は第1の画素21の光電変換読み出し部211および第2の画素22の光電変換読み出し部221のリセットトランジスタRST1-Tr、RST2-Trの制御信号RSTを示している。図7(C)は第1の画素21の光電変換読み出し部211および第2の画素22の光電変換読み出し部221の転送トランジスタTG1-Tr、TG2-Trの制御信号TGを示している。

図 7 ( D ) は第 1 の画素 2 1 の信号保持部 2 1 2 のスイッチ素子 S W 2 1 の制御信号 S w 1、選択トランジスタ S E L 3 - T r の制御信号 S E L 3 を示している。

## [0119]

図8(A)は画素およびカラム読み出し回路の等価回路を、図8(B)は第1の画素21の光電変換読み出し部211および第2の画素22の光電変換読み出し部221の選択トランジスタSEL1-Tr、SEL2-Trの制御信号SELを示している。図8(C)は第1の画素21の光電変換読み出し部211および第2の画素22の光電変換読み出し部221のリセットトランジスタRST1-Tr、RST2-Trの制御信号RST、並びに、転送トランジスタTG1-Tr、TG2-Trの制御信号TGを示している。

図8(D)はローリングシャッタモード時のシングルエンドの第1の画素信号pixout1を示し、図8(E)はオートゼロスイッチ部SW423の制御信号AZ1を示し、図8(F)は第1のスイッチ部SW421の制御信号CKOSを示し、図8(G)はサンプルホールドスイッチ部SW431の制御信号SHを示し、図8(H)はオートゼロスイッチ部SW432の制御信号AZ2を示している。

図8(I)は第1のオペアンプ421の出力信号(アンプ出力)ampoutを示し、図8(J)は第1の探索信号 Vramp1を示し、図8(K)は第2のオペアンプ431の入力信号(信号電圧) Vcmpを示し、図8(L)は第2のオペアンプ431の出力信号(比較出力)cmpoutを示している。

# [0120]

なお、このローリングシャッタモード期間においては、保持部アレイ240のすべての信号保持部212の駆動を制御する、スイッチ素子SW21の制御信号Sw1、選択トランジスタSEL3・Tァを制御する制御信号SEL3はLレベルに設定され、スイッチ素子SW21、選択トランジスタSEL3・Tァが非導通状態に制御されている。また、定電流源Ibias3はオフ状態に制御されている。

## [0121]

すなわち、ローリングシャッタモード期間においては、第2の基板120に形成された 保持部アレイ240の全ての信号保持部212はアクセスされない。

ローリングシャッタモード期間においては、第1の基板110に形成されただ第1の画素アレイ230および第2の画素アレイ250-1,250-2が行単位で順次にアクセスされる。

## [0122]

ローリングシャッタモード期間においては、図7(A)に示すように、第1の画素アレイ230または第2の画素アレイ250-1,250-2の中のある一行を選択するために、その選択された行の第1の画素アレイ230の各光電変換読み出し部211または第2の画素アレイ250-1,250-2の光電変換読み出し部221を制御(駆動)する制御信号SELがHレベルに設定されて画素の選択トランジスタSEL2-Tr(またはSEL1-Tr)が導通状態となる。

## [0123]

この選択状態において、リセット期間PRにリセットトランジスタRST2-Tr(またはRST1-Tr)が、制御線RSTがHレベルの期間に選択されて導通状態となり、フローティングディフュージョンFDが電源電圧VDDの電位にリセットされる。

10

20

30

40

このリセット期間 P R が経過した後(リセットトランジスタ R S T 2 - T r または R S T 1 - T r が非導通状態)、転送期間 P T が開始されるまでの時刻 t 1 を含む期間が、リセット状態時の画素信号を読み出す第 1 読み出し期間となる。

### [0124]

時刻 t 1 において、選択された行のソースフォロワトランジスタSF2-Tr(またはSF1-Tr)により、フローティングディフュージョンFD22(またはFD21)の電荷が電荷量に応じた電圧信号に変換され、列出力の読み出しリセット信号VRSTとして第1の垂直信号線LSGN11に直ちに出力され、カラム読み出し回路40に供給される。

## [0125]

ここで、第1読み出し期間が終了し、転送期間 PTとなる。

転送期間 P T に転送トランジスタ T G 2 - T r (または T G 1 - T r )が、制御信号 T G がハイレベル ( H )の期間に選択されて導通状態となり、フォトダイオード P D 2 2 (または P D 2 1)で光電変換され蓄積された電荷 (電子)がフローティングディフュージョン F D 2 2 (または F D 2 1)に転送される。

この転送期間PTが経過した後(転送トランジスタTG2-TrまたはTG1-Trが 非導通状態)、フォトダイオードPD22(またはPD21)が光電変換して蓄積した電 荷に応じた画素信号を読み出す時刻t2を含む第2読み出し期間となる。

## [0126]

第2読み出し期間が開始された時刻 t 2 において、選択された行のソースフォロワトランジスタSF2・Tr(またはSF1・Tr)により、フローティングディフュージョンFD22(またはFD21)の電荷が電荷量に応じた電圧信号に変換され、列出力の読み出し輝度信号VSIGとして第1の垂直信号線LSGN11に直ちに出力され、カラム読み出し回路40に供給される。

#### [0127]

そして、たとえば読み出し部70の一部を構成するカラム読み出し回路40において、順次に供給される第1の画素信号pixout1の読み出しリセット信号VRSTと読み出し輝度信号VSIGに対する増幅処理、AD変換処理が行われ、また、両信号の差分{VRST-VSIG}がとられてCDS処理が行われる。

## [0128]

より具体的には、ローリングシャッタモード期間においては、カラム読み出し回路 4 0 の入力部 4 4 0 に対して第 1 のモード信号 M O D 1 が供給されている。

また、ローリングシャッタモード期間において、カラム読み出し回路40の増幅部42 0の第1のスイッチ部SW421に対して制御信号CKOSがLレベルで供給される。これにより、第1のスイッチ部SW421は、端子aを端子bとが接続されて、第1の帰還キャパシタCf1は、第1のオペアンプ421の第1の入力端子(-)と出力ノードND421との間に接続される。

また、ローリングシャッタモード期間において、カラム読み出し回路40の増幅部42 0の第2のスイッチ部SW422は、導通状態に保持され、第1のオペアンプ421の第 2の入力端子(+)が参照電位Vrefに接続されている。

# [0129]

このような状態において、入力部440に第1の画素信号が入力され、ローリングシャッタモード時のシングルエンドの第1の画素信号pixout1が、入力部440の第1の出力端子TO1から、第1のサンプリングキャパシタCs1が接続された第1のオペアンプ421の第1の入力端子(-)側に供給される。

第1のオペアンプ421の第1の入力端子(-)側には、図8(D)に示すように、第1の画素21の光電変換読み出し部211および第2の画素22の光電変換読み出し部221から順に読み出されるシングルエンドの読み出しリセット信号VRST、読み出し輝度信号VSIGが順に供給される。

## [0130]

10

20

30

そして、読み出しリセット信号 V R S T が入力されてから所定期間(リセット状態時の画素信号を読み出す第 1 読み出し期間が開始されてから所定の期間)、図 8 ( E ) , ( G ) , ( H ) に示すように、制御信号 A Z 1、S H、および A Z 2 が H レベルに設定される。これにより、増幅部 4 2 0 のオートゼロスイッチ部 S W 4 2 3、 A D 変換部 4 3 0 のサンプルホールドスイッチ部 S W 4 3 1、およびオートゼロスイッチ部 S W 4 3 2 が導通状態となる。

制御信号AZ1、SH、およびAZ2がHレベルに設定される期間としては、制御信号SH、AZ2,AZ1の順で長く設定される。

これにより、増幅部420の第1のオペアンプ421、およびAD変換部430の第2のオペアンプ431がリセット状態となる。

その結果、増幅部420の第1のオペアンプ421の出力信号(アンプ出力) ampoutは、参照電位 Vrefとなり、サンプルホールドスイッチ部 SW431を通してAD変換部430に転送され、第3のサンプリングキャパシタCs3と第4のサンプリングキャパシタCs4に保持される。

## [0131]

次に、AD変換部430には、図8(J)に示すように、探索信号入力部432を通して右下がリのスロープ波形の第1の探索信号Vramp1が供給される。

そして、図8(K)に示すように、第4のサンプリングキャパシタCs4に保持された電圧と探索信号入力部432による探索信号Vramp1を合成した信号電圧Vcmpが第2のオペアンプ431の第1の入力端子(-)側に供給される。

第2のオペアンプ431においては、第1の入力端子(-)に第3のサンプリングキャパシタCs3を介して入力される入力信号電圧Vcmpと第2の入力端子(+)に供給される参照電位Vref2と交差するまでの間、図8(L)に示すように、比較出力信号cmpoutがHレベルで出力される。このHレベル期間を図示しないカウンタに保持することで、AD変換を行う。

## [0132]

第 1 読み出し期間が終了すると、増幅部 4 2 0 には読み出しリセット信号 V R S T より低電位の読み出し輝度信号 V S I G が供給される。

そして、第1のオペアンプ421の出力信号ampoutは、参照電位Vrefを基準に、読み出しリセット信号VRSTと低電位の読み出し輝度信号VSIGの差分に容量比倍Gを掛け合わせたレベル増幅された信号(Vref+G\*(VRST-VSIG))となる。

そして、転送期間後の所定期間、図8(G)に示すように、制御信号SHがHレベルに設定され、AD変換部430のサンプルホールドスイッチ部SW431が導通状態となる

その結果、増幅部 4~2~0~0第 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0

## [0133]

次に、AD変換部430には、図8(J)に示すように、探索信号入力部432を通して右下がリのスロープ波形の第1の探索信号Vramp1が供給される。

そして、図8(K)に示すように、第4のサンプリングキャパシタCs4に保持された電圧と探索信号入力部432による探索信号Vramp1を合成した信号電圧Vcmpが第2のオペアンプ431の第1の入力端子(-)側に供給される。

第2のオペアンプ431においては、第1の入力端子(・)に第3のサンプリングキャパシタCs3を介して入力される入力信号電圧Vcmpと第2の入力端子(+)に供給される参照電位Vref2と交差するまでの間、図8(L)に示すように、比較出力信号cmpoutがHレベルで出力される。このHレベル期間を図示しないカウンタに保持することで、AD変換を行う。

10

20

30

### [0134]

そして、たとえば読み出し部70の一部を構成するカラム読み出し回路40において、 読み出しリセット信号VRSTと読み出し輝度信号VSIGとの差分{VRST-VSIG}がとられてCDS処理が行われる。

## [0135]

上述したように、ローリングシャッタモード期間においては、第1の基板110に形成された第1の画素アレイ230および第2の画素アレイ250-1,250-2が行単位で順次にアクセスされ、上記した読み出し動作が順次に行われる。

## [0136]

(グローバルシャッタモード時の読み出し動作)

次に、グローバルシャッタモード時の読み出し動作について説明する。

図9(A)~(G)は、本第1の実施形態に係る固体撮像装置のグローバルシャッタモード時の主として画素部における読み出し動作を説明するためのタイミングチャートである。

図10(A)~(L)は、本第1の実施形態に係る固体撮像装置のグローバルシャッタモード時の主としてカラム読み出し回路における読み出し動作を説明するためのタイミングチャートである。

## [0137]

図9(A)は第1の画素21の光電変換読み出し部211および第2の画素22の光電変換読み出し部221の選択トランジスタSEL1-Tr、SEL2-Trの制御信号SELを示している。図9(B)は第1の画素21の光電変換読み出し部211および第2の画素22の光電変換読み出し部221のリセットトランジスタRST1-Tr、RST2-Trの制御信号RSTを示している。図9(C)は第1の画素21の光電変換読み出し部211および第2の画素22の光電変換読み出し部221の転送トランジスタTG1-Tr、TG2-Trの制御信号TGを示している。

図9(D)は第1の画素21の信号保持部212のスイッチ素子SW21の制御信号SW1を示している。図9(E)は第1の画素21の信号保持部212のリッセットトランジスタRST3-Trの制御信号RST3を示している。図9(F)は第1の画素21の信号保持部212の選択トランジスタSEL3-Trの制御信号SEL3を示している。図9(G)は第1の画素21の信号保持部212に配置された定電流源Ibias3の駆動状態(オン、オフ状態)を示している。

## [0138]

図10(A)は画素およびカラム読み出し回路の等価回路を、図10(B)は第1の画素21の信号保持部212の選択トランジスタSEL3-Trの制御信号SEL3を示している。図10(C)は第1の画素21の信号保持部212のリッセットトランジスタRST3-Trの制御信号RST3を示している。

図 1 0 ( D ) はグローバルシャッタモード時のシングルエンドの第 2 の画素信号 p i x o u t 2 を示し、図 1 0 ( E ) はオートゼロスイッチ部 S W 4 2 3 の制御信号 A Z 1 を示し、図 1 0 ( F ) は第 1 のスイッチ部 S W 4 2 1 の制御信号 C K O S を示し、図 1 0 ( G ) はサンプルホールドスイッチ部 S W 4 3 1 の制御信号 S H を示し、図 1 0 ( H ) はオートゼロスイッチ部 S W 4 3 2 の制御信号 A Z 2 を示している。

図 1 0 ( I ) は第 1 のオペアンプ 4 2 1 の出力信号(アンプ出力) a m p o u t を示し、図 1 0 ( J ) は第 2 の探索信号 V r a m p 2 を示し、図 1 0 ( K ) は第 2 のオペアンプ 4 2 1 の入力信号電圧 V c m p を示し、図 1 0 ( L ) は第 2 のオペアンプ 4 3 1 の出力信号(比較出力) c m p o u t を示している。

# [0139]

グローバルシャッタモード時には、図9(A)に示すように、第1の画素21の光電変換読み出し部211および第2の画素22の光電変換読み出し部221の選択トランジスタSEL1-Tr、SEL2-Trの制御信号SELがグローバルシャッタモードの全期間中ローレベル(L)に設定される。

10

20

30

40

これにより、グローバルシャッタモードの全期間中第1の画素アレイ230と第2の画素アレイ250-1,250-2から第1の垂直信号線LSGN11への電圧信号の出力が抑止(停止)される。

したがって、第2の画素アレイ250-1,250-2は非アクティブ状態に制御される。

また、第1の画素アレイ230は、アクティブ状態であり、出力ノードND21からの電圧信号の信号保持部212への出力可能状態となっている。

## [0140]

図9(A)~(G)において、時刻 t 1 1 ~ t 1 2 は、第 1 の画素アレイ 2 3 0 のすべての光電変換読み出し部 2 1 1 におけるフォトダイオード P D 2 1 およびフローティングディフュージョン F D 2 1 のリセット期間および電荷の蓄積期間である。

### [0141]

なお、このリセット期間および電荷の蓄積期間においては、図9(D)~(G)に示すように、保持部アレイ240のすべての信号保持部212の駆動を制御する、スイッチ素子SW21の制御信号sw1、リセットトランジスタRST3・Trを制御する制御信号RST3、選択トランジスタSEL3・Trを制御する制御信号SEL3はLレベルに設定され、スイッチ素子SW21、リセットトランジスタRST3・Tr、選択トランジスタSEL3・Trが非導通状態に制御され、定電流源Ibias3はオフ状態に制御されている。

# [0142]

このような状態で、リセット期間において、リセットトランジスタRST1-Trが、 制御信号RSTがHレベルの期間に選択されて導通状態となる。

そして、制御信号RSTがHレベル期間中に、転送トランジスタTG1-Trが、制御信号TGがHレベルの期間に選択されて導通状態となり、フォトダイオードPD21で光電変換され蓄積された電荷(電子)の蓄積ノードがフローティングディフュージョンFD21と導通状態となり、フォトダイオードPD21およびフローティングディフュージョンFD21が電源電圧VDDの電位にリセットされる。

# [0143]

フォトダイオードPD21のリセット後、転送トランジスタTG1-Trの制御信号TGがLレベルに切り替えられ、転送トランジスタTG1-Trが非導通状態となり、フォトダイオードPD21では光電変換された電荷の蓄積が開始される。

このとき、リセットトランジスタRST1-Trの制御信号RSTはHレベルに保持されており、フローティングディフュージョンFD21が電源電圧VDDの電位にリセットされたままの状態に保持される。

そして、リセット期間の終了のため、時刻 t 1 2 の前に、リセットトランジスタ R S T 1 - T r の制御信号 R S T は L レベルに切り替えられ、リセットトランジスタ R S T 1 - T r は非導通状態となる。

このリセット期間 P R が経過した後(リセットトランジスタ R S T 1 - T r が非導通状態)、転送期間 P T が開始されるまでの時刻 t 1 2 を含む期間が、リセット状態時の画素信号を読み出す第 1 読み出し期間となる。

# [0144]

同様に、信号保持部 2 1 2 において、時刻 t 1 2 を含む所定期間に、リセットトランジスタ R S T 3 - T r を制御する制御信号 R S T 3 が H レベルに切り替えられ、リセットトランジスタ R S T 3 - T r が導通状態に保持され、ノード N D 2 4 が電源電圧 V D D の電位にリセットされる。

また、時刻 t 1 2 , t 1 3 、 t 1 4 を含む所定期間、スイッチ素子 S W 2 1 の制御信号 s w 1 が H レベルに保持され、スイッチ素子 S W 2 1 がオン状態(導通状態)に保持される。

同様に、時刻t12,t13、t14を含む所定期間、定電流源Ibias3がオン状態に制御される。

20

10

30

40

なお、定電流源Ibias3は、時刻t14を経過し、スイッチ素子SW21の制御信号sw1がLレベルに切り替えられスイッチ素子SW21がオフ状態(非導通状態)となった後に、オフ状態に制御される。

## [0145]

時刻 t 1 2 を含む所定期間において、全画素のソースフォロワトランジスタSF1-T r により、フローティングディフュージョンFD21 の電荷が電荷量に応じた電圧信号に 変換され、画素の読み出しリセット信号VRST0 として第3 の信号線LSGN13 を介して信号保持部212 に転送され、さらにスイッチ素子SW21を通して信号保持キャパシタC21に保持される。

## [0146]

ここで、第1読み出し期間が終了し、時刻t13を含む所定期間が転送期間PTとなる

転送期間 P T に転送トランジスタ T G 1 - T r が、制御信号 T G がハイレベル(H)の期間に選択されて導通状態となり、フォトダイオード P D 2 1 で光電変換され蓄積された電荷(電子)がフローティングディフュージョン F D 2 1 に転送される。

この転送期間PTが経過した後(転送トランジスタTG1-Trが非導通状態)、フォトダイオードPD2)が光電変換して蓄積した電荷に応じた画素信号を読み出す時刻t1 4を含む第2読み出し期間となる。

#### [0147]

第2読み出し期間が開始された時刻 t 1 4 において、全画素のソースフォロワトランジスタSF1 - Trにより、フローティングディフュージョンFD21の電荷が電荷量に応じた電圧信号に変換され、画素の読み出し輝度信号VSIG0として第3の信号線LSGN13を介して信号保持部212に転送され、さらにスイッチ素子SW21を通して保持信号VSIG(=VSIG0・VRST0)が信号保持キャパシタC21およびC22に保持される。このCDS動作により、ソースフォロワトランジスタSF1・Trのオフセット電圧をキャンセルすることができる。

#### [0148]

この状態で保持した保持信号 V S I G を読み出すため、保持部アレイ 2 4 0 の中のある一行を選択するために、その選択された行の各選択トランジスタ S E L 3 - T r の制御信号 S E L 3 が H レベルに設定されて、その選択トランジスタ S E L 3 - T r が導通状態となる。

そして、時刻 t 1 5 において、信号保持キャパシタ C 2 1 および C 2 2 に保持された保持信号 V S I G ( V S I G ・ V R S T )の読み出しが行われる。

このとき、各信号保持部212においては、ゲートがノードND24に接続されたソースフォロワトランジスタSF3-Trにより、ノードND24に接続された信号保持キャパシタC21およびC22の保持電圧に応じて、列出力の読み出し輝度信号(VSIG-VRST)として第2の垂直信号線LSGN12に出力され、カラム読み出し回路40に供給される。

## [0149]

次いで、時刻 t 1 6 を含む所定期間に、制御信号 R S T 3 が H レベルに切り替えられ、 リセットトランジスタ R S T 3 - T r が導通状態となり、ノード N D 2 4 がリセットされる

そして、時刻 t 1 6 を含む所定期間において、ノードND24 に接続された信号保持キャパシタC21 およびC22に保持されたリセット保持信号(VRST)の読み出しが行われる。

このとき、各信号保持部212においては、ゲートがノードND24に接続されたソースフォロワトランジスタSF3-Trにより、ノードND24に接続された信号保持キャパシタC21およびC22の保持電圧に応じて、列出力の読み出しリセット信号(VRST)として第2の垂直信号線LSGN12に出力され、カラム読み出し回路40に供給される。

10

20

30

#### [0150]

そして、たとえば読み出し部70の一部を構成するカラム読み出し回路40において、 時刻t15を含む所定期間に読み出された読み出し輝度信号(VSIG-VRST)と時 刻t16を含む所定期間に読み出された読み出しリセット信号VRSTとが、第2の画素 信号pixout2として順に増幅部420に供給される。

### [0151]

たとえば読み出し部70の一部を構成するカラム読み出し回路40において、入力部440を通して順次に供給される第2の画素信号pixout2の読み出し輝度信号VSIG(CMS)と読み出しリセット信号VRSTに対する増幅処理、AD変換処理が行われる。また、両信号の差分{VSIG-VRST}がとられてさらにCDS処理が行われ、ソースフォロワトランジスタSF3.Trのオフセット電圧をキャンセルする。

### [0152]

より具体的には、シングルエンドのグローバルシャッタモード期間においては、カラム 読み出し回路40の入力部440に対して第2のモード信号MOD2が供給されている。

また、シングルエンドのグローバルシャッタモード期間において、カラム読み出し回路40の増幅部420の第2のスイッチ部SW422は、導通状態に保持され、第1のオペアンプ421の第2の入力端子(+)が参照電位Vrefに接続されている。

## [0153]

このような状態において、入力部440に第2の画素信号が入力され、グローバルシャッタモード時のシングルエンドの第2の画素信号pixout2が、入力部440の第1の出力端子TO1から、第1のサンプリングキャパシタCs1が接続された第1のオペアンプ421の第1の入力端子(-)側に供給される。

第1のオペアンプ421の第1の入力端子(-)側には、図10(D)に示すように、第1の画素21の光電変換読み出し部211から読み出され、さらに信号保持部212から順に読み出されるシングルエンドの読み出し輝度信号VSIG、読み出しリセット信号VRSTが順に供給される。

### [0154]

そして、読み出し輝度信号VSIGが入力されてから所定期間、図10(E)に示すように、制御信号AZ1がHレベルに設定される。これにより、増幅部420のオートゼロスイッチ部SW423が導通状態となる。

これにより、増幅部420の第1のオペアンプ421がリセット状態となる。

その結果、増幅部 4 2 0 の第 1 のオペアンプ 4 2 1 の出力信号(アンプ出力) a m p o u t は、参照電位 V r e f となる。

### [0155]

次いで、シングルエンドのグローバルシャッタモード期間において、カラム読み出し回路40の増幅部420の第1のスイッチ部SW421に対して制御信号CKOSがLレベルからHレベルに遷移される。これにより、第1のスイッチ部SW421は、端子aが端子bから端子cに接続されて、第1の帰還キャパシタCf1は、オフセット電位VOSから第1のオペアンプ421の出力に接続変更される。

これにより、増幅部 4~2~0 の第 1 のオペアンプ 4~2~1 の出力信号(アンプ出力) a m p o u t は、参照電位 V r e f にオフセット v f s 分シフトされ、オフセット電位 V O S にオフセットシフトされる。

このオフセットシフトにより、第1のオペアンプ421の出力レンジは、上述したローリングシャッタモード時と同じレベルに維持される。

#### [0156]

そして、制御信号 CKOSがHレベルに切り替えられてから所定期間、図10(G)、(H)に示すように、制御信号 SHおよびAZ2がHレベルに設定される。これにより、AD変換部430のサンプルホールドスイッチ部SW431、およびオートゼロスイッチ部SW432が導通状態となる。

制御信号SHおよびAZ2がHレベルに設定される期間としては、制御信号SH、AZ

10

20

30

40

2の順で長く設定される。

これにより、AD変換部430の第2のオペアンプ431がリセット状態となる。

そして、増幅部420の第1のオペアンプ421の出力信号(アンプ出力)ampoutは、読み出し輝度信号VSIGに対応する部分はオフセット電位VOSとなり、サンプルホールドスイッチ部SW431を通してAD変換部430に転送され、第3のサンプリングキャパシタCs3および第4のサンプリングキャパシタCs4に保持される。

#### [0157]

次に、AD変換部430には、図10(J)に示すように、探索信号入力部432を通して右下がリのスロープ波形の第1の探索信号Vramp1とレベルが反転した関係にある右上がリのスロープ波形の第2の探索信号Vramp2が供給される。

そして、図8(K)に示すように、第4のサンプリングキャパシタCs4に保持された電圧と探索信号入力部432による探索信号Vramp2を合成した信号電圧Vcmpが第2のオペアンプ431の第1の入力端子(-)側に供給される。

第2のオペアンプ431においては、第1の入力端子(・)に第3のサンプリングキャパシタCs3を介して入力される入力信号電圧Vcmpと第2の入力端子(+)に供給される参照電位Vref2iと交差するまでの間、図10(L)に示すように、比較出力信号cmpoutがHレベルで出力される。この交差するまでの時間を図示しないカウンタで測定することにより、AD変換が行われる。

## [0158]

増幅部420には読み出し輝度信号VSIGより高電位の読み出しリセット信号VRSTが供給される。

読み出しリセット信号 V R S T に対応する部分は、オフセットシフトによりオフセット電位 V O S より G \* ( V R S T - V S I G ) だけ低い電位 ( V O S - G \* ( V R S T - V S I G ) ) となる。

そして、転送期間後の所定期間、図10(G)に示すように、制御信号SHがHレベルに設定され、AD変換部430のサンプルホールドスイッチ部SW431が導通状態となる。

その結果、増幅部420の第1のオペアンプ421の出力信号(アンプ出力) ampoutは、信号(VOS-G\*(VRST-VSIG))となり、サンプルホールドスイッチ部SW431を通してAD変換部430に転送され、第4のサンプリングキャパシタCs4に保持される。

# [0159]

このとき、AD変換部430には、図10(J)に示すように、探索信号入力部432 を通して右上がりのスロープ波形の第2の探索信号Vramp2が供給される。

そして、図10(K)に示すように、サンプリングキャパシタCs4に保持された電圧と探索信号入力部432による探索信号Vramp2を合成した信号電圧Vcmpが第2のオペアンプ431の第1の入力端子(-)側に供給される。

第2のオペアンプ431においては、第1の入力端子(-)に第3のサンプリングキャパシタCs3を介して入力される入力信号電圧Vcmpと第2の入力端子(+)に供給される参照電位Vrefと交差するまでの間、図10(L)に示すように、比較出力信号cmpoutがHレベルで出力される。この交差するまでの時間を図示しないカウンタで測定することにより、AD変換が行われる。

#### [0160]

この比較出力信号 cmpoutは、上述したローリングシャッタモード時の場合と同じ結果が得られる。

# [0161]

そして、たとえば読み出し部70の一部を構成するカラム読み出し回路40において、 読み出しリセット信号VRSTと読み出し輝度信号VSIGとの差分{VSIG-VRST}がとられてCDS処理が行われる。

## [0162]

10

20

40

30

以上説明したように、本第1の実施形態によれば、固体撮像装置10は、光電変換を行う画素が配置された画素部20と、画素から垂直信号線に読み出される画素信号をアナログ信号からデジタル信号に変換するAD(アナログデジタル)変換機能を有するカラム読み出し回路40と、を有する。

固体撮像装置10において、画素から読み出される画素信号は、第1の動作であるローリングシャッタにより画素から順に読み出される読み出しリセット信号VRSTおよび読み出し輝度信号を含む第1の画素信号pixout1と、第2の動作であるグローバルシャッタにより画素から順に読み出される読み出し輝度信号VSIGおよび読み出しリセット信号VRSTを含む第2の画素信号pixout2と、のうちの少なくともいずれかである。そして、カラム読み出し回路40は、画素信号を増幅する増幅部420と、増幅部420で増幅された画素信号を、探索信号に関連付けてアナログ信号からデジタル信号に変換するAD変換430と、を含み、第1の画素信号pixout1のときの第1の探索信号Vramp1と第2の画素信号pixout2のときの第2の探索信号Vramp2とは、探索レベルが反転した関係に設定可能である。

## [0163]

したがって、本第1の実施形態において、カラム読み出し回路40は、動作モードや読み出し信号の信号形態にかかわらず読み出し回路を共用することが可能となり、ひいては、回路規模の低減、制御の容易化、低消費電力化を実現することができる。

本第1の実施形態によれば、特に、リセットレベルが先行して出力される低ノイズなローリングシャッタモードと、動体歪みのないグローバルシャッタモードの画素信号の両方を取得可能な画素に対して、サンプルホールド回路を追加することなく小面積で、かつ、低電圧で処理することが可能となる。

具体的には、カラムアンプである第1のオペアンプ421において、第1の帰還キャパシタCf1の接続先を、第1のオペアンプ421の出力端子およびオフセット電位VOSのいずれかに、シングルエンドのローリングシャッタモードとシングルエンドのグローバルシャッタモードに応じて切り替え可能な第1のスイッチ部SW421とバイアス信号線を追加するだけで、動作モードや読み出し信号の信号形態にかかわらず読み出し回路を共用することが可能となる。

## [0164]

また、本第1の実施形態によれば、固体撮像装置10は、画素部20において、画素として光電変換読み出し部および信号保持部を含む第1の画素21と、光電変換読み出し部を含む第2の画素22が混在されて、第1の動作であるローリングシャッタと第2の動作であるグローバルシャッタの両動作機能を併せ持つ、たとえば積層型のCMOSイメージセンサとして構成されている。

本第1の実施形態に係る固体撮像装置10において、画素部20は、複数の第1の画素21の光電変換読み出し部211が行列状に配置された第1の画素アレイ230と、複数の第1の画素21の信号保持部212が行列状に配置された保持部アレイ240と、複数の第2の画素の光電変換読み出し部が行列状に配置された第2の画素アレイ250-1,250-2と、を含んで構成されている。

そして、第1の動作であるローリングシャッタモード時に、第1の画素 2 1 および第 2 の画素 2 2 の光電変換読み出し部 2 1 1 , 2 2 1 の読み出し信号が第 1 の垂直信号線 L S G N 1 1 にバイパス経路をたどることなく直ちに出力される。また、第 2 の動作であるグローバルシャッタモード時に、第 1 の画素の信号保持部 2 1 2 の保持信号が第 2 の垂直信号線 L S G N 1 2 に出力される。

#### [ 0 1 6 5 ]

したがって、本第1の実施形態の固体撮像装置10によれば、構成の複雑化を防止しつつ、レイアウト上の面積効率の低下を防止することができる。

#### [0166]

また、本第1の実施形態の固体撮像装置10によれば、動作モード時に応じて所望のアスペクト比の画像信号を得ることができる。

10

20

30

40

#### [0167]

また、本第1の実施形態に係る固体撮像装置10は、第1の基板(上基板)110と第 2の基板(下基板)120の積層構造を有する。

第1の基板110には、その中央部を中心として画素部20の各第1の画素21の光電変換読み出し部211が配列された第1の画素アレイ230が形成され、第1の画素アレイ230の第1の垂直信号線LSGN11の配線方向の両側(上側および下側)に第2の画素アレイ250-1,250-2が形成されている。

また、第1の基板110には、第1の垂直信号線LSGN11が形成されている。

第2の基板120には、その中央部を中心として第1の画素アレイ230の各光電変換読み出し部211の出力ノードND21と接続される各第1の画素21の信号保持部212がマトリクス状に配列された保持部アレイ240(領域121)および第2の垂直信号線LSGN12が形成されている。

そして、保持部アレイ240の周囲にカラム読み出し回路40用の領域122,123 等が形成されている。

## [0168]

したがって、本第1の実施形態において、第1の基板110側を、基本的に、NMOS系の素子だけで形成すること、および、第1の画素アレイと第2の画素アレイ画素により有効画素領域を最大限に拡大することにより、コストあたりの価値を最大限に高めることができる。

## [0169]

(第2の実施形態)

図11は、本発明の第2の実施形態に係る固体撮像装置の画素およびカラム読み出し回路の構成例を示す図である。

#### [ 0 1 7 0 ]

本第2の実施形態に係る固体撮像装置10Aが、上述した第1の実施形態に係る固体撮像装置10と異なる点は、次のとおりである。

本第2の実施形態に係る固体撮像装置10Aでは、ローリングシャッタモード時にカラム読み出し回路40Aへの第1の画素信号が、シングルエンドではなく差動の画素信号として供給される。

## [0171]

具体的には、第1の垂直信号線LSGN11を転送された第1の画素信号pixout1は、カラム読み出し回路40Aの入力部440を介して増幅部420の第1のオペアンプ421の第1の入力端子(-)側に、第1のサンプリングキャパシタCs1を介して供給される。

そして、電流源 I b i a s 1 と基準電位 V S S との接続ライン側に流れる信号が、入力部 4 4 0 を介して増幅部 4 2 0 の第 1 のオペアンプ 4 2 1 の第 2 の入力端子(+)側に、第 2 のサンプリングキャパシタ C s 2 を介して供給される。

## [0172]

第2の実施形態に係る固体撮像装置10Aのその他の構成は第1の実施形態に係る固体撮像装置10と同様である。

# [0173]

より具体的には、差動のローリングシャッタモード期間においては、カラム読み出し回路40Aの入力部440に対して第3のモード信号MOD3が供給されている。

また、ローリングシャッタモード期間において、カラム読み出し回路40Aの増幅部420の第1のスイッチ部SW421に対して制御信号CKOSがLレベルで供給される。これにより、第1のスイッチ部SW421は、端子aを端子bとが接続されて、第1の帰還キャパシタCf1は、第1のオペアンプ421の第1の入力端子(-)と出力ノードND421との間に接続される。

また、ローリングシャッタモード期間において、カラム読み出し回路40Aの増幅部4 20の第2のスイッチ部SW422に対して制御信号VREFSHがクロックで供給され 10

20

30

40

る。

## [0174]

図12(A)~(K)は、本第2の実施形態に係る固体撮像装置の差動のローリングシャッタモード時の主としてカラム読み出し回路における読み出し動作を説明するためのタイミングチャートである。

## [0175]

図12(A)は第1の画素21の光電変換読み出し部211および第2の画素22の光電変換読み出し部221の選択トランジスタSEL1-Tr、SEL2-Trの制御信号SELを示している。図12(B)は第1の画素21の光電変換読み出し部211および第2の画素22の光電変換読み出し部221のリセットトランジスタRST1-Tr、RST2-Trの制御信号RST、並びに、転送トランジスタTG1-Tr、TG2-Trの制御信号TGを示している。

図12(C)はグローバルシャッタモード時のシングルエンドの第1の画素信号 pixout1を示し、図12(D)はオートゼロスイッチ部SW423の制御信号 AZ1および第2のスイッチ部SW422の制御信号 VREFSHを示し、図12(E)は第1のスイッチ部SW421の制御信号 CKOSを示し、図12(F)はサンプルホールドスイッチ部SW431の制御信号 SHを示し、図12(G)はオートゼロスイッチ部SW432の制御信号 AZ2を示している。

図12(H)は第1のオペアンプ421の出力信号(アンプ出力)ampoutを示し、図12(I)は第1の探索信号Vramp1を示し、図12(J)は第2のオペアンプ431の入力信号電圧Vcmpを示し、図12(K)は第2のオペアンプ431の出力信号(比較出力)cmpoutを示している。

#### [0176]

差動のローリングシャッタモード時の画素およびカラム読み出し回路40Aにおける読み出し動作は、図8(A)~(L)に関連付けて説明したシングルエンドのローリングシャッタモード時の画素およびカラム読み出し回路40における読み出し動作、制御信号VREFSHが制御信号AZ1と同じように遷移する点を除くと同様である。

したがって、その詳細な動作説明はここでは割愛する。

## [0177]

本第2の実施形態によれば、上述した第1の実施形態の効果を得られることはもとより、電流源Ibias1と基準電位VSSとの接続ライン側に流れる信号が、入力部440を介して増幅部420の第1のオペアンプ421の第2の入力端子(+)側に、第2のサンプリングキャパシタCs2を介して供給されることから、ローリングシャッタ画素に対して、カラム(列)ごとのグランド(GND)浮をキャンセルすることができ、ひいては、シェーディングなどのノイズを低減することができる。

また、画素はグローバルシャッタモードで動作しても良い。具体的には、第2の垂直信号線LSGN12から出力された第2の画素信号pixout2は、カラム読み出し回路40Aの入力部440を介して増幅部420の第1のオペアンプ421の第1の入力端子(-)側に、第1のサンプリングキャパシタCs1を介して供給される。

そして、電流源 I b i a s 1 と基準電位 V S S との接続ライン側に流れる信号が、入力部 4 4 0 を介して増幅部 4 2 0 の第 1 のオペアンプ 4 2 1 の第 2 の入力端子(+)側に、第 2 のサンプリングキャパシタ C s 2 を介して供給される。この時も同様に、グローバルシャッタ画素に対して、シェーディングなどのノイズを低減することができる。

# [0178]

## (第3の実施形態)

図13は、本発明の第3の実施形態に係る固体撮像装置の第1の画素の構成例を示す図である。

### [0179]

本第3の実施形態に係る固体撮像装置10Bが上述した第1の実施形態および第2の実施形態に係る固体撮像装置10,10Aと異なる点は、第1の画素21Bにおける信号保

10

20

30

40

持部212Bの構成にある。

## [0180]

第1の画素21の信号保持部212Bは、基本的に、定電流源Ibias3が接続されている入力部2121、サンプルホールド部2122B、出力部2123B、ノードND22、ND25~ND27を含んで構成されている。

#### [0181]

定電流源Ibias3は、ノードND22と基準電位VSSとの間に接続され、たとえばグローバルシャッタ期間中の所定の期間にオン状態に制御される。

## [0182]

なお、定電流源Ibias3の代わりに、ノードND22と基準電位VSSとの間に接続され、たとえばグローバルシャッタ期間中の所定の期間にオン状態に制御されるスイッチ素子を設けてもよい。

#### [0183]

サンプルホールド部 2 1 2 2 B は、スイッチ素子SSW22~SW24、リセット信号用保持キャパシタCR21、信号用保持キャパシタCS21、およびノードND25~ND27を含んで構成されている。

## [0184]

スイッチ素子SW22は、第2の期間であるグローバルシャッタ期間に、サンプルホールド部2122Bの信号用保持キャパシタCS21をノードND26を介して光電変換読み出し部211の出力ノードND21と選択的に接続する。

スイッチ素子SW22は、端子aが第3の信号線LSGN13に接続された入力ノードND22と接続され、端子bがノードND26に接続されている。

スイッチ素子SW22は、たとえば制御信号GSHSがハイレベルに期間に端子aとbが接続されて導通状態となる。

信号用保持キャパシタCS21は、ノードND26と基準電位VSSに接続されたノードND27との間に接続されている。

### [0185]

スイッチ素子SW23は、第2の期間であるグローバルシャッタ期間に、サンプルホールド部2122Bのリセット信号用保持キャパシタCR21をノードND25を介して光電変換読み出し部211の出力ノードND21と選択的に接続する。

スイッチ素子SW23は、端子aが第3の信号線LSGN13に接続された入力ノードND22と接続され、端子bがノードND25に接続されている。

スイッチ素子SW23は、たとえば制御信号GSHRがハイレベルに期間に端子aとbが接続されて導通状態となる。

リセット信号用保持キャパシタCR21は、ノードND25と基準電位VSSに接続されたノードND27との間に接続されている。

# [0186]

スイッチ素子SW24は、第2の期間であるグローバルシャッタ期間に、リセット信号用保持キャパシタCR21に接続されたノードND25と信号用保持キャパシタCS21が接続されたノードND26を接続する。

スイッチ素子SW24は、端子aがノードND26に接続され、端子bがノードND2 5に接続されている。

スイッチ素子SW24は、たとえば制御信号CKSTがハイレベルに期間に端子aとbが接続されて導通状態となる。これにより、選択行のリセットレベルと信号レベルの平均化が行われる。

# [0187]

なお、スイッチ素子SW22~SW24は、MOSトランジスタ、たとえばn チャネル MOS(NMOS)トランジスタにより形成される。

## [0188]

出力部2123Bは、第2の期間であるグローバルシャッタ期間に、基本的に信号用保

20

10

30

40

持キャパシタCS21に保持された信号を保持電圧に応じて出力するソースフォロワトランジスタSF3S・Trを含み、保持した信号を選択的に選択トランジスタSEL3S・Trを介して定電流源Ibias1・1により駆動される第2の垂直信号線LSGN12・1に出力する。

## [0189]

ソースフォロワトランジスタSF3S-Tァと選択トランジスタSEL3S-Tァは、電源電位VDDと定電流源Ibias1-1により駆動される第2の垂直信号線LSGN12-1の間に直列に接続されている。

## [0190]

ソースフォロワトランジスタSF3S-TrのゲートにはノードND26が接続され、 選択トランジスタSEL3S-Trは制御線を通じてゲートに印加される制御信号SEL 3により制御される。

選択トランジスタSEL3S-Trは、制御信号SEL3がHレベルの選択期間に選択されて導通状態となる。これにより、ソースフォロワトランジスタSF3S-Trは信号用保持キャパシタCS21の保持電圧または平均化電圧に応じた列出力の読み出し電圧(VRST,VSIG)を第2の垂直信号線LSGN12-1に出力する。

## [0191]

さらに、出力部2123Bは、第2の期間であるグローバルシャッタ期間に、基本的にリセット信号用保持キャパシタCR21に保持された信号を保持電圧に応じて出力するソースフォロワトランジスタSF3R・Trを含み、保持した信号を選択的に選択トランジスタSEL3R・Trを介して定電流源Ibias1-2により駆動される第2の垂直信号線LSGN12-2に出力する。

#### [0192]

ソースフォロワトランジスタSF3R- Trと選択トランジスタSEL3R- Trは、電源電位VDDと定電流源Ibias1-2により駆動される第2の垂直信号線LSGN12-2の間に直列に接続されている。

#### [0193]

ソースフォロワトランジスタSF3R-TrのゲートにはノードND25が接続され、 選択トランジスタSEL3R-Trは制御線を通じてゲートに印加される制御信号SEL 3により制御される。

選択トランジスタSEL3R-Trは、制御信号SEL3がHレベルの選択期間に選択されて導通状態となる。これにより、ソースフォロワトランジスタSF3R-Trはリセット信号用保持キャパシタCR21の保持電圧または平均化電圧に応じた列出力の読み出し電圧(VRST,VSIG)を第2の垂直信号線LSGN12-2に出力する。

## [0194]

(差動のグローバルシャッタモード時の読み出し動作)

次に、差動のグローバルシャッタモード時の読み出し動作について説明する。

図14(A)~(F)は、本第3の実施形態に係る固体撮像装置のグローバルシャッタ モード時の主として画素部における読み出し動作を説明するためのタイミングチャートで ある。

図 1 5 ( A ) ~ ( L ) は、本第 3 の実施形態に係る固体撮像装置のグローバルシャッタ モード時の主としてカラム読み出し回路における読み出し動作を説明するためのタイミン グチャートである。

# [0195]

図14(A)は第1の画素21の光電変換読み出し部211の転送トランジスタTG1-Trの制御信号TGを示している。図14(B)は第1の画素21の光電変換読み出し部211のリセットトランジスタRST1-Trの制御信号RSTを示している。

図14(C)は第1の画素21の信号保持部212Bのスイッチ素子SW22の制御信号GSHSを示している。図14(D)は第1の画素21の信号保持部212Bのスイッチ素子SW23の制御信号GSHRを示している。図14(E)は第1の画素21の信号

10

20

30

40

保持部 2 1 2 B のスイッチ素子 S W 2 4 の制御信号 C K S T を示している。図 1 4 (F)は第 1 の画素 2 1 の信号保持部 2 1 2 の選択トランジスタ S E L 3 - T r の制御信号 S E L 3 を示している。

## [0196]

図15(A)は画素およびカラム読み出し回路の等価回路を、図15(B)は第1の画素21の信号保持部212Bの選択トランジスタSEL3R-Tr、SEL3S-Trの制御信号SEL3を示している。図15(C)は第1の画素21の信号保持部212Bのスイッチ素子SW24の制御信号CKSTを示している。

図 1 5 ( D ) はグローバルシャッタモード時の差動の第 2 の画素信号 p i x o u t 2 を示し、図 1 5 ( E ) はオートゼロスイッチ部 S W 4 2 3 の制御信号 A Z 1 および第 2 のスイッチ部 S W 4 2 2 の制御信号 C K O S を示し、図 1 5 ( G ) はサンプルホールドスイッチ部 S W 4 2 1 の制御信号 C K O S を示し、図 1 5 ( G ) はサンプルホールドスイッチ部 S W 4 3 1 の制御信号 S H を示し、図 1 5 ( H ) はオートゼロスイッチ部 S W 4 3 2 の制御信号 A Z 2 を示している。

図 1 5 ( I ) は第 1 のオペアンプ 4 2 1 の出力信号(アンプ出力) a m p o u t および帰還信号 a m p v s t を示し、図 1 5 ( J ) は第 1 の探索信号 V r a m p 1 を示し、図 1 5 ( K ) は第 2 のオペアンプ 4 3 1 の入力信号電圧 V c m p を示し、図 1 5 ( L ) は第 2 のオペアンプ 4 3 1 の出力信号(比較出力) c m p o u t を示している。

## [0197]

グローバルシャッタモード時には、第1の画素21の光電変換読み出し部211および第2の画素22の光電変換読み出し部221の選択トランジスタSEL1-Tr、SEL2-Trの制御信号SELがグローバルシャッタモードの全期間中ローレベル(L)に設定される。

これにより、グローバルシャッタモードの全期間中第1の画素アレイ230と第2の画素アレイ250-1,250-2から第1の垂直信号線LSGN11への電圧信号の出力が抑止(停止)される。

したがって、第2の画素アレイ250-1,250-2は非アクティブ状態に制御される。

また、第1の画素アレイ230は、アクティブ状態であり、出力ノードND21からの電圧信号の信号保持部212Bへの出力可能状態となっている。

### [0198]

図14(A)~(F)において、時刻t21~t22は、第1の画素アレイ230のすべての光電変換読み出し部211におけるフォトダイオードPD21およびフローティングディフュージョンFD21のリセット期間および電荷の蓄積期間Tintである。

## [0199]

なお、このリセット期間および電荷の蓄積期間においては、保持部アレイ240のすべての信号保持部212Bの駆動を制御する、スイッチ素子SW22~SW24の制御信号GSHS、GSHR、CKST、選択トランジスタSEL3・Trを制御する制御信号SEL3はLレベルに設定され、スイッチ素子SW22~SW24、選択トランジスタSEL3・Trが非導通状態に制御され、定電流源Ibias3はオフ状態に制御されている

## [0200]

このような状態で、リセット期間において、リセットトランジスタRST1-Trが、制御信号RSTがHレベルの期間に選択されて導通状態となる。

そして、制御信号RSTがHレベル期間中に、転送トランジスタTG1-Trが、制御信号TGがHレベルの期間に選択されて導通状態となり、フォトダイオードPD21で光電変換され蓄積された電荷(電子)の蓄積ノードがフローティングディフュージョンFD21と導通状態となり、フォトダイオードPD21およびフローティングディフュージョンFD21が電源電圧VDDの電位にリセットされる。

## [0201]

50

20

10

30

10

20

30

40

50

フォトダイオード P D 2 1 のリセット後、転送トランジスタ T G 1 - T r の制御信号 T G が L レベルに切り替えられ、転送トランジスタ T G 1 - T r が非導通状態となり、フォトダイオード P D 2 1 では光電変換された電荷の蓄積が開始される。

このとき、リセットトランジスタRST1-Trの制御信号RSTはHレベルに保持されており、フローティングディフュージョンFD21が電源電圧VDDの電位にリセットされたままの状態に保持される。

この状態で時刻 t 2 2 に、各光電変換読み出し部 2 1 1 では、ソースフォロワトランジスタ S F 1 - T r により、フローティングディフュージョン F D 2 1 の電荷が電荷量に応じた電圧信号に変換され、列出力の読み出しリセット信号 V R S T として出力ノード N D 2 1 から出力される。

そして、リセット期間の終了のため、時刻 t 2 2 を経過後、リセットトランジスタ R S T 1 - T r の制御信号 R S T は L レベルに切り替えられ、リセットトランジスタ R S T 1 - T r は非導通状態となる。

次に、時刻 t 2 3 を含む所定期間に、第 1 の画素 2 1 の信号保持部 2 1 2 B のスイッチ素子 S W 2 2 の制御信号 G S H S およびスイッチ素子 S W 2 3 の制御信号 G S H R が H レベルに切り替えられて、信号用保持キャパシタ C S 2 1 およびリセット信号用保持キャパシタ C R 2 1 が初期化される。また、定電流源 I b i a s 3 がオン状態となるように制御される。

かつ、時刻 t 2 3 を含む所定期間において、各光電変換読み出し部 2 1 1 の出力ノード N D 2 1 から出力される読み出しリセット信号 V R S T は、第 3 の信号線 L S G N 1 3 を通して対応する信号保持部 2 1 2 B に伝送され、スイッチ素子 S W 2 3 を通してリセット信号用保持キャパシタ C R 2 1 に保持される。

そして、第1の画素21Bの信号保持部212Bのスイッチ素子SW22の制御信号GSHSおよびスイッチ素子SW23の制御信号GSHRがLレベルに切り替えられ、スイッチ素子SW22およびSW23が非導通状態となる。

### [0202]

ここで、時刻t24を含む所定期間が転送期間となる。

転送期間には、各光電変換読み出し部 2 1 1 において、転送トランジスタTG 1 - Trが、制御信号TGがHレベルの期間に選択されて導通状態となり、フォトダイオードPD 2 1 で光電変換され蓄積された電荷(電子)がフローティングディフュージョンFD 2 1 に転送される。

転送期間が終了すると、転送トランジスタTG1-Trの制御信号TGがLレベルに切り替えられ、転送トランジスタTG1-Trが非導通状態となる。

#### [0203]

また、光電変換読み出し部211において、転送トランジスタTG1-Trの制御信号TGがLレベルに切り替えられ、転送期間が終了されるタイミングに並行して、保持部アレイ240のすべての信号保持部212Bでは、次の制御が行われる。

信号保持部212Bにおいて、時刻t25を含む所定期間に制御信号GSHSがHレベルに切り替えられてスイッチ素子SW22が導通状態となり、定電流源Ibias3がオン状態となるように制御される。

# [0204]

これにより、時刻 t 2 5 を含む所定期間において、各光電変換読み出し部 2 1 1 の出力 ノードND 2 1 から出力される読み出し輝度信号 V S I G は、第 3 の信号線 L S G N 1 3 を通して対応する信号保持部 2 1 2 に伝送され、スイッチ素子 S W 2 2 を通して信号用保持キャパシタ C S 2 1 に保持される。

## [0205]

信号用保持キャパシタCS21に読み出し輝度信号VSIGを保持した後、制御信号GSHSがLレベルに切り替えられて、スイッチ素子SW22が非導通状態となる。

### [0206]

この状態で保持した信号を読み出すため、保持部アレイ240の中のある一行を選択す

10

20

30

40

50

るために、その選択された行の各選択トランジスタSEL3-Trの制御信号SEL3が Hレベルに設定されて、その選択トランジスタSEL3S-TrおよびSEL3R-Tr が導通状態となる。

そして、時刻 t 2 6 において、信号用保持キャパシタ C S 2 1 に保持された読み出し輝度信号 V S I G の読み出し、並びに、リセット信号用保持キャパシタ C R 2 1 に保持された読み出しリセット信号 V R S T の読み出しが並行して行われる。

#### [0207]

このとき、各信号保持部 2 1 2 B においては、ゲートがノード N D 2 6 に接続されたソースフォロワトランジスタ S F 3 S - T r により、ノード N D 2 6 に接続された信号用保持キャパシタ C S 2 1 の保持電圧に応じて、列出力の読み出し輝度信号 V S I G として第2の垂直信号線 L S G N 1 2 - 1 に出力され、カラム読み出し回路 4 0 に供給される。

同様に、各信号保持部 2 1 2 B においては、ゲートがノードND 2 5 に接続されたソースフォロワトランジスタSF 3 R - T r により、ノードND 2 5 に接続されたリセット信号用保持キャパシタCR 2 1 の保持電圧に応じて、列出力の読み出しリセット信号VRSTとして第 2 の垂直信号線LSGN 1 2 - 2 に出力され、カラム読み出し回路 4 0 に供給される。

### [0208]

次に、信号保持部 2 1 2 B において、時刻 t 2 7 を含む所定期間に制御信号 C K S T が H レベルに切り替えられてスイッチ素子 S W 2 4 が導通状態となる。

これにより、選択行のリセットレベルと信号レベルの平均化が行われる。

そして、時刻 t 2 8 において、信号用保持キャパシタ C S 2 1 に保持された読み出し輝度信号 V S I G、並びに、リセット信号用保持キャパシタ C R 2 1 に保持された読み出しリセット信号 V R S T を平均化して信号の読み出しが並行して行われる。

#### [0209]

このとき、各信号保持部212Bにおいては、ゲートがノードND26に接続されたソースフォロワトランジスタSF3S-Trにより、ノードND26における平均化電圧に応じて、列出力の平均化信号として第2の垂直信号線LSGN12-1に出力され、カラム読み出し回路40に供給される。

同様に、各信号保持部212Bにおいては、ゲートがノードND25に接続されたソースフォロワトランジスタSF3R-Trにより、ノードND25における平均化電圧に応じて、列出力の平均化信号AVSRとして第2の垂直信号線LSGN12-2に出力され、カラム読み出し回路40に供給される。

#### [0210]

# [0211]

### 「数1]

$V_{OUTR}(t26) - V_{OUTS}(t26) = V_{R} + V_{OS2} - (V_{S} + V_{OS1})$

$V_{OUTR}(t28) - V_{OUTS}(t28) = (V_R + V_S) / 2 + V_{OS2} - ((V_R + V_S) / 2 + V_{OS1})$

$V_{OUTR}(t26) - V_{OUTS}(t26)$  {  $V_{OUTR}(t28) - V_{OUTS}(t28)$  }

$$= V_R - V_S$$

#### [0212]

ここで、 $V_{OUTR}$ (t 2 6) は時刻t 2 6に読み出されるリセット信号電圧を、 $V_{OUTR}$ (t 2 6) は時刻t 2 6に読み出される信号電圧を、 $V_{OUTR}$ (t 2 8)は時刻t 2 8に読み出されるリセット信号電圧を、 $V_{OUTS}$ (t 2 8)は時刻t 2 8に読み出

される信号電圧を、それぞれ示している。

### [0213]

以上より、後段回路で差動信号をCDS処理することで、ソースフォロワトランジスタ SF3S-Tr、SF3R-Trのオフセットを除去することができる。

### [0214]

そして、たとえば読み出し部70の一部を構成するカラム読み出し回路40において、 時刻t26に同時並列的に読み出された読み出し輝度信号VSIGおよび読み出しリセット信号VRST、並びに時刻t28に読み出される平均化信号AVSRと、第2の画素信号pixout2として並列に増幅部420に供給される。

#### [0215]

たとえば読み出し部70の一部を構成するカラム読み出し回路40において、入力部440を通して同時並列的に供給される第2の画素信号pixout2の読み出し輝度信号VSIGと読み出しリセット信号VRST、および平均化信号AVSRに対する増幅処理、AD変換処理が行われ、また、両信号の差分{VRST・VSIG-AVSR)}がとられてCDS処理が行われる。

#### [0216]

より具体的には、差動のグローバルシャッタモード期間においては、カラム読み出し回路40の入力部440に対して第4のモード信号MOD4が供給されている。

また、差動のグローバルシャッタモード期間において、カラム読み出し回路40の増幅部420の第1のスイッチ部SW421に対して制御信号CKOSがLレベルで供給される。これにより、第1のスイッチ部SW421は、端子aを端子bとが接続されて、第1の帰還キャパシタCf1は、第1のオペアンプ421の第1の入力端子(-)と出力ノードND421との間に接続される。

また、差動のグローバルシャッタモード期間において、カラム読み出し回路40の増幅部420の第2のスイッチ部SW422に対して制御信号VREFSHがクロックで供給される。

#### [0217]

このような状態において、入力部440に第2の画素信号pixout2が入力され、グローバルシャッタモード時の差動の一方の第2の画素信号pixout2d1が、入力部440の第1の出力端子TO1から、第1のサンプリングキャパシタCs1が接続された第1のオペアンプ421の第1の入力端子(-)側に供給される。

これと並行して、グローバルシャッタモード時の差動の他方の第2の画素信号pixout2d2が、入力部440の第2の出力端子TO2から、第2のサンプリングキャパシタCs2が接続された第1のオペアンプ421の第2の入力端子(+)側に供給される。

### [0218]

そして、読み出し輝度信号 V S I G および読み出しリセット信号 V R S T が入力されてから所定期間、図 1 5 (E)に示すように、制御信号 A Z 1 および制御信号 V R E F S H が H レベルに設定される。これにより、増幅部 4 2 0 のオートゼロスイッチ部 S W 4 2 3 およびスイッチ部 S W 4 2 2 が導通状態となる。

これにより、増幅部420の第1のオペアンプ421がリセット状態となる。

その結果、増幅部420の第1のオペアンプ421の出力信号(アンプ出力) ampoutは、所定のDC電位、たとえば参照電位Vrefとなる。

### [0219]

そして、制御信号AZ1および制御信号VREFSHがLレベルに切り替えられてから 所定期間、図15(G)、(H)に示すように、制御信号SHおよびAZ2がHレベルに 設定される。これにより、AD変換部430のサンプルホールドスイッチ部SW431、 およびオートゼロスイッチ部SW432が導通状態となる。

制御信号SHおよびAZ2がHレベルに設定される期間としては、制御信号SH、AZ 2の順で長く設定される。

これにより、AD変換部430の第2のオペアンプ431がリセット状態となる。

10

20

30

40

#### [0220]

その結果、増幅部 4 2 0 の第 1 のオペアンプ 4 2 1 の出力信号(アンプ出力) a m p o u t は、参照電位 V r e f となり、サンプルホールドスイッチ部 S W 4 3 1 を通して A D 変換部 4 3 0 に転送され、第 3 のサンプリングキャパシタ C s 3 および第 4 のサンプリングキャパシタ C s 4 に保持される。

#### [0221]

このとき、AD変換部430には、図15(J)に示すように、探索信号入力部432 を通して右下がりのスロープ波形の第1の探索信号Vramp1が供給される。

そして、図15(K)に示すように、第4のサンプリングキャパシタCs4に保持された電圧と探索信号入力部432による探索信号Vramp1を合成した信号電圧Vcmpが第2のオペアンプ431の第1の入力端子(-)に供給される。

第2のオペアンプ431においては、第1の入力端子(・)に第3のサンプリングキャパシタCs3を介して入力される入力信号電圧Vcmpと第2の入力端子(+)に供給される参照電位Vref2と交差するまでの間、図15(L)に示すように、比較出力信号cmpoutがHレベルで出力される。この交差するまでの時間を図示しないカウンタで測定することにより、AD変換が行われる。

### [0222]

続いて、増幅部420には読み出し輝度信号VSIGおよび読み出しリセット信号VRSTの平均化信号AVSRが供給される。

そして、第1のオペアンプ4211の出力信号ampoutは、参照電位Vrefを基準に、読み出しリセット信号電圧VRSTと低電位の読み出し輝度信号VSIGの差分に容量比倍Gを掛け合わせたレベル増幅された信号(Vref+G^\*(VRST-VSIG))となる。また、帰還信号ampvstは(Vref+G^\*(VRST-VSIG))となる。

そして、転送期間後の所定期間、図15(G)に示すように、制御信号SHがHレベルに設定され、AD変換部430のサンプルホールドスイッチ部SW431が導通状態となる。

その結果、増幅部 4~2~0~0第 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0 1~0

## [0223]

このとき、AD変換部430には、図15(J)に示すように、探索信号入力部432 を通して右下がりのスロープ波形の第1の探索信号Vramp1が供給される。

そして、図15(K)に示すように、第4のサンプリングキャパシタCs4に保持された電圧と探索信号入力部432による探索信号Vramp1を合成した信号電圧Vcmpが第2のオペアンプ431の第1の入力端子(-)側に供給される。

第2のオペアンプ431においては、第1の入力端子(-)に第3のサンプリングキャパシタCs3を介して入力される入力信号電圧Vcmpと第2の入力端子(+)に供給される参照電位Vref2と交差するまでの間、図15(L)に示すように、比較出力信号cmpoutがHレベルで出力される。この交差するまでの時間を図示しないカウンタで測定することにより、AD変換が行われる。

### [0224]

そして、たとえば読み出し部70の一部を構成するカラム読み出し回路40において、 読み出しリセット信号VRSTと読み出し輝度信号VSIGとの差分{VRST-VSI G-AVSR)}がとられてデジタルCDS処理が行われる。

### [0225]

ここで、本第3の実施形態に係るカラム読み出し回路を通してのCDS処理について図15(A)~(L)に関連付けて考察する。

図 1 5 ( A ) ~ ( L ) においては、時刻 t 3 1 に第 1 の画素 2 1 の信号保持部 2 1 2 B

10

20

30

40

により読み出し輝度信号 V S I G および読み出しリセット信号 V R S T が同時並列的に読み出されてカラム読み出し回路 4 0 の第 1 のオペアンプ 4 2 1 に入力される場合を例としている。

同様に、図15(A)~(L)において、時刻t32に第1の画素21の信号保持部212Bにより読み出し輝度信号VSIGおよび読み出しリセット信号VRSTの平均化信号AVSRが同時並列的に読み出されてカラム読み出し回路40に入力される場合を例としている。

[0226]

時刻 t 3 1 における第 1 のオペアンプ 4 2 1 の第 2 の入力端子(+)の入力信号 V i n p (t 3 1)は次式で与えられる。

10

[0227]

「数21

Vinp(t31) = Vref + (Qinj/(Cs + Cf)) = V´ref

[0228]

時刻 t 3 1 における第 1 のオペアンプ 4 2 1 の第 1 の入力端子(-)の入力信号 V i n n (t 3 1)に関連して次式が与えられる。

[0229]

「数31

Csx(V´ref-Vrst)+Cfx0+Qinj =Csx(V´ref-Vrst)+Cfx(V´ref-Vout)

20

[0230]

したがって、時刻t31の出力Vout(t31)は次式で与えられる。

[0231]

「数4]

Vout(t31) = V'ref-Qinj/Cf

[0232]

時刻 t 3 2 における第 1 のオペアンプ 4 2 1 の第 2 の入力端子(+)の入力信号 V i n p (t 3 2)については次式が与えられる。

[0233]

[数5]

30

C s x ( V ' r e f - V r s t ) + C f x V ' r e f = C s x ( V i n p - ( V r s t + V s i g ) / 2 ) + C f x V i n p

[0234]

したがって、時刻 t 3 2 の第 1 のオペアンプ 4 2 1 の第 2 の入力端子(+)の入力信号 V i n p ( t 3 2 ) は次式で与えられる。

[0235]

[数6]

Vinp(t32)

= V 'ref+(Cs/(Cs+Cf)) x (Vrst-VsiG)/2

[0236]

40

時刻 t 3 2 における第 1 のオペアンプ 4 2 1 の第 1 の入力端子(-)の入力信号 V i n n (t 3 1)に関連して次式が与えられる。

[0237]

「数71

C s x ( V ' r e f - V r s t ) + C f x 0 + Q i n j = C s x ( V i n p - ( V r s t + V s i g ) / 2 ) + C f x ( V i n p - V o u t )

[0238]

したがって、時刻t32の出力Vout(t32)は次式で与えられる。

[0239]

[数8]

Vout (t32)

= V'ref-(Qinj/Cf)+(Cs/Cf)x(Vrst-Vsig)

### [0240]

したがって、デジタルCDS処理の差分出力は次式で与えられる。

## [0241]

「数91

Vout(t32) - Vout(t31) = (Cs/Cf) x (Vrst - Vsig)

[0242]

以上より、差動信号をCDS処理することで、読み出し輝度信号VSIGおよび読み出しりセット信号VRSTの差分を出力することができる。また、上式では明記されないが、読み出し輝度信号VSIGおよび読み出しリセット信号VRSTの平均化信号AVSRをCDS処理することで、ソースフォロワトランジスタSF3S-Tr、SF3R-Tr等のオフセットを除去することができる。

[0243]

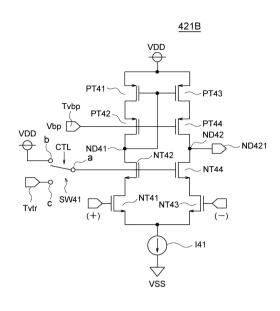

ここで、カラム読み出し回路 4 0 の第 1 のオペアンプ 4 2 1 の具体的な構成例について 説明する。

[0244]

図16は、本第3の実施形態に係るカラム読み出し回路の第1のオペアンプの構成例を示す回路図である。

図 1 7 は、差動のグローバルシャッタモード時の第 1 のオペアンプの入力レンジの制御の一例を説明するためのである。

[0245]

第1のオペアンプ421としては、たとえば図16に示すようなソースカップルペア入力の高利得オペアンプが適用可能である。

[0246]

図 1 6 のオペアンプ 4 2 1 B は、P M O S トランジスタ P T 4 1 ~ P T 4 4 、N M O S トランジスタ N T 4 1 ~ N T 4 4 、スイッチ部 S W 4 1 、電流源 I 4 1 、およびノード N D 4 1 , N D 4 2 を含んで構成されている。

[0247]

PMOSトランジスタPT41,PT42、NMOSトランジスタNT41,NT42が電源電位 V DDと基準電位 V S S との間に縦続接続され、PMOSトランジスタPT43,PT44、NMOSトランジスタNT43,NT44が電源電位 V DDと基準電位 V S S との間に縦続接続されている。

そして、 P M O S トランジスタ P T 4 1 のソースと P M O S トランジスタ P T 4 3 のソース同士が接続されて、その接続ノードが電源電位 V D D に接続されている。

NMOSトランジスタPT41のソースとNMOSトランジスタPT43のソース同士が接続されて、その接続ノードが基準電位VSSに接続されて電流源I41に接続されている。

[0248]

PMOSFランジスタPT42のドレインとNMOSFランジスタNT42のドレインとの接続点によりノードND41が形成され、<math>PMOSFランジスタPT44のドレインとNMOSFランジスタNT44のドレインとの接続点によりノードND42が形成されている。

そして、ノードND41がPMOSトランジスタPT41, PT43のゲートに接続され、ノードND42が出力ノードND421に接続されている。

また、PMOSトランジスタPT42,PT44のゲートがバイアス電位Vbpの供給 端子Tvbpに共通に接続されている。

[0249]

スイッチ部SW41は、端子aがNMOSトランジスタNT42,NT44のゲートに

20

10

30

40

共通に接続され、端子bが電源電位VDDに接続され、端子cがテレスコピック電位Vtrの供給端子Tvtrに接続されている。

スイッチ部SW41は、たとえば制御信号CTLがLレベルのときは端子aと端子bとを導通状態に保持し、制御信号CTLがHレベルのときは端子aと端子cとを導通状態に保持する。

# [0250]

第1のオペアンプ421は、ゲイン設定Gが低いときはスイッチ部SW41により、NMOSトランジスタNT42,NT44のゲートが電源電位VDDに接続されるように制御され、いわゆるテレスコピックアンプとして機能しないように制御される。これは、広い入力レンジに対応するためである。

第 1 のオペアンプ 4 2 1 は、ゲイン設定 G が高いときはスイッチ部 S W 4 1 により、N M O S トランジスタ N T 4 2 , N T 4 4 のゲートがテレスコピック電位 V t r に接続されるように制御され、いわゆるテレスコピックアンプとして機能するように制御される。これは、ゲインエラーを低減するためである。

### [0251]

図 1 7 の例では、ゲインが×1、×2の低いゲインの場合、明時のゲインエラーよりも 光子(フォトン)ショットノイズが支配的であることから、NMOSトランジスタNT4 2 ,NT44のゲートを電源電位VDDに接続し、テレスコピックアンプとして機能させ ない。

一方、ゲインが×4、×8の高いゲインの場合は、入力レンジが小さいため、NMOSトランジスタNT42,NT44のゲートをテレスコピック電位Vtrに接続し、高いゲインのテレスコピックアンプとして機能させ、明時のゲインエラーを低減する。

## [0252]

本第3の実施形態によれば、上述した第1および第2の実施形態の効果を得られることはもとより、差動出力型のグローバルシャッタ画素に対して、キャパシタ等を追加することなく、小面積で差動出力信号のCDS処理を実現することができる。

### [0253]

# (第4の実施形態)

図18は、本発明の第4の実施形態に係るカラム読み出し回路の構成例を示す回路図である。

図19(A)および(B)は、本第4の実施形態に係るAD変換部に採用される反転二分探索法に対応した探索信号入力部の構成例を説明するための図である。

#### [0254]

本第4の実施形態に係る固体撮像装置10Cが上述した第1、第2および第3の実施形態に係る固体撮像装置10,10A,10Bと異なる点は、カラム読み出し回路40におけるAD変換部430Cの探索信号入力部432Cの構成にある。

# [0255]

第1~第3の実施形態においては、探索信号 V r a m p として、第1のモード信号 M O D 1(シングルエンドのローリングシャッタモード)、第3のモード信号 M O D 3(差動のローリングシャッタモード)、第4のモード信号 M O D 4(差動のグローバルシャッタモード)のとき第1の探索信号 V r a m p 1 が探索信号入力部432に供給される。

そして、第1~第3の実施形態においては、探索信号Vrampとして、第2のモード信号MOD2(シングルエンドのグローバルシャッタモード)のとき第2の探索信号Vramp2が探索信号入力部432に供給される。

すなわち、第1~第3の実施形態においては、AD変換部430にレベル反転させた第 1の探索信号Vramp1と第2の探索信号Vramp2を採用している。

#### [0256]

これに対して、本第4の実施形態においては、AD変換部430CをSAR型(逐次比較型)ADCとして構成し、探索信号の供給に反転二分探索を採用している。

## [0257]

10

20

30

40

(44)

探索信号入力部432Cは、複数(×個)の第4のサンプリングキャパシタCs4-1~Cs4-x、および複数のスイッチ部SW432-1~SW432-xを含んで構成されている。

第4のサンプリングキャパシタCs4-1~Cs4-xは、一方の電極(端子)がAD変換部430Cの入力ノードND431に共通に接続され、他方の電極(端子)が、対応して配置されたスイッチ部SW432-1~SW432-xの端子aに接続されている。

スイッチ部 S W 4 3 2 - 1 ~ S W 4 3 2 - x の端子 b が参照電位 V r e f に接続され、 端子 c がグランド G N D に接続されている。

[0258]

カラム読み出し回路 4 0 C に読み出しリセット信号 V R S T、読み出し輝度信号 V S I G の順に読み出される第 1 の画素信号 p i x o u t 1 が入力される場合、スイッチ部 S W 4 3 2 - 1 ~ S W 4 3 2 - x は制御信号 C T R\_S A R により参照電位 V r e f とグランド G N D で、この順に交互にスイッチするように制御される。

このように、スイッチ部SW432-1~SW432-xを制御信号CTR\_SARにより参照電位VrefとグランドGNDで、この順に交互にスイッチすることにより、図19(A)に示すように、読み出しリセット信号VRST、読み出し輝度信号VSIGの順に読み出される第1の画素信号pixout1をAD変換することができる。

[0259]

カラム読み出し回路 4 0 C に読み出し輝度信号 V S I G、読み出しリセット信号 V R S T の順に読み出される第 2 の画素信号 p i x o u t 2 が入力される場合、スイッチ部 S W 4 3 2 - 1 ~ S W 4 3 2 - x は制御信号 C T R\_S A R によりグランド G N D と参照電位 V r e f で、この順に交互にスイッチするように制御される。

このように、スイッチ部SW432-1~SW432-xを制御信号CTR\_SARによりグランドGNDと参照電位Vref、この順に交互にスイッチすることにより、図19(B)に示すように、読み出し輝度信号VSIG、読み出しリセット信号VRSTの順に読み出される第2の画素信号pixout2をAD変換することができる。

[0260]

本第4の実施形態によれば、上述した第1、第2および第3の実施形態の効果と同様の効果を得ることができる。

[0261]

以上説明した固体撮像装置10,10A~10Cは、デジタルカメラやビデオカメラ、 携帯端末、あるいは監視用カメラ、医療用内視鏡用カメラなどの電子機器に、撮像デバイ スとして適用することができる。

[0262]

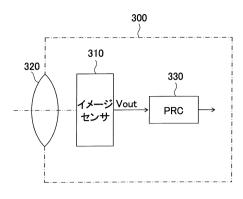

図 2 0 は、本発明の実施形態に係る固体撮像装置が適用されるカメラシステムを搭載した電子機器の構成の一例を示す図である。

[0263]

本電子機器300は、図20に示すように、本実施形態に係る固体撮像装置10,10 A~10Cが適用可能なCMOSイメージセンサ310を有する。

さらに、電子機器300は、このCMOSイメージセンサ310の画素領域に入射光を導く(被写体像を結像する)光学系(レンズ等)320を有する。

電子機器 3 2 0 は、 C M O S イメージセンサ 3 1 0 の出力信号を処理する信号処理回路 (PRC) 3 3 0 を有する。

[0264]

信号処理回路330は、CMOSイメージセンサ310の出力信号に対して所定の信号処理を施す。

信号処理回路 3 3 0 で処理された画像信号は、液晶ディスプレイ等からなるモニタに動画として映し出し、あるいはプリンタに出力することも可能であり、またメモリカード等の記録媒体に直接記録する等、種々の態様が可能である。

[0265]

10

20

30

40

上述したように、CMOSイメージセンサ310として、前述した固体撮像装置10, 10A~10Cを搭載することで、高性能、小型、低コストのカメラシステムを提供する ことが可能となる。

そして、カメラの設置の要件に実装サイズ、接続可能ケーブル本数、ケーブル長さ、設置高さなどの制約がある用途に使われる、たとえば、監視用カメラ、医療用内視鏡用カメラなどの電子機器を実現することができる。

# 【図1】

# 【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

| telesco<br>-amp    | off   | off   | on    | on    | off   |

|--------------------|-------|-------|-------|-------|-------|

| max(ampvst)<br>[V] | 0.500 | 0.333 | 0.200 | 0.111 | 0.667 |

| max(vrst-vsig) [V] | 1.000 | 0.500 | 0.250 | 0.125 | 2.000 |

| gain_vst<br>[V/V]  | 0.500 | 0.667 | 0.800 | 0.889 | 0.333 |

| gain<br>[VV]       | 1.0   | 2.0   | 4.0   | 8.0   | 9:0   |

【図19】

# フロントページの続き

(56)参考文献 特開2015-091081(JP,A)

特開2013-055447(JP,A)

特開2012-019410(JP,A)

(58)調査した分野(Int.CI., DB名)

H04N 5/30-5/378