## (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 110474641 B (45) 授权公告日 2022. 09. 20

- (21) 申请号 201910770614.0

- (22) 申请日 2019.08.20

- (65) 同一申请的已公布的文献号 申请公布号 CN 110474641 A

- (43) 申请公布日 2019.11.19

- (73) 专利权人 合肥工业大学地址 230009 安徽省合肥市包河区屯溪路193号

- (72) **发明人** 胡逸俊 邓红辉 饶晨光 尹勇生 陈红梅

- (74) 专利代理机构 安徽省合肥新安专利代理有限责任公司 34101 专利代理师 陆丽莉 何梅生

(51) Int.CI.

**HO3M** 1/12 (2006.01)

**HO3M** 1/10 (2006.01)

**HO3M** 13/11 (2006.01)

#### (56) 对比文件

WO 2017091928 A1,2017.06.08

US 2010182184 A1,2010.07.22

US 6222476 B1,2001.04.24

CN 106656189 A,2017.05.10

CN 104348486 A,2015.02.11

CN 105024697 A, 2015.11.04

CN 104124971 A, 2014.10.29

- US 2012326909 A1,2012.12.27

- CN 103152047 A, 2013.06.12

- CN 101478309 A, 2009.07.08

- US 2002041248 A1,2002.04.11

张睿等."流水线模数转换器设计".《电子测量与仪器学报》.2012,第26卷(第3期),第223-228页.

马恒飞."高速折叠插值模数转换器的研究与设计".《中国优秀硕士学位论文全文数据库·信息科技辑》.2016,第2016年卷(第8期),第 1135-248页.

Hongmei Chen等."A correlation-based background calibration technology for the pipeline A/D Converter".《2016 13th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT)》.2017,第1-3页.

Mingwen Zhang等."Design of low-jitter clock duty cycle stabilizer in high-performance pipelined ADC".《Anti-counterfeiting, Security, and Identification》.2012,第1-5页. (续)

审查员 李晓阳

权利要求书4页 说明书10页 附图3页

#### (54) 发明名称

应用于超高速流水线折叠插值结构的模数转换器的数字编码电路及其方法

### (57) 摘要

本发明公开了一种应用于超高速流水线折 叠插值结构的模数转换器的数字编码电路及其 方法,该电路包括:循环温度计码转多进制译码 电路模块、多进制转二进制逻辑译码器模块、串 行加法器组模块;其中,循环温度计码转多进制 码模块中包含递归钳位校正逻辑。本发明能减少由于电路结构以及工艺限制对ADC量化精度的影

响,从而实现高速、准确的数字编码。

CN 110474641 B 2/2 页

[接上页]

## (56) 对比文件

Koken Chin等."A 12-Bit 3.3MS/S pipeline cyclic ADC with correlated level

shifting technique".《2017 International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS)》.2018,第602-605页.

1.一种应用于超高速流水线折叠插值结构的模数转换器的数字编码电路,所述模数转换器是由一级预放大级和六级折叠插值级所构成的七级流水线,其特征是,所述数字编码电路包括:循环温度计码转多进制译码电路模块、多进制转二进制逻辑译码器模块、串行加法器组模块:

所述循环温度计码转多进制译码电路模块抽取所述模数转换器中一级预放大级输出的两路数字信号,包括:第0级第1路输出 $S_{0.1}$ 和第0级第2路输出 $S_{0.2}$ ;

所述循环温度计码转多进制译码电路模块抽取所述模数转换器中第一级折叠插值级至第五级折叠插值级中各级输出的三路数字信号,包括:第1级第1路输出 $S_{1,1}$ 、第1级第2路输出 $S_{1,2}$ 、第1级第3路输出 $S_{1,3}$ ~第5级第1路输出 $S_{5,1}$ 、第5级第2路输出 $S_{5,2}$ 、第5级第3路输出  $S_{5,3}$ ;

所述循环温度计码转多进制译码电路模块抽取所述模数转换器中第六级折叠插值级输出的六路数字信号,包括:第6级第1路输出 $S_{6,1}$ ~第6级第6路输出 $S_{6,6}$ ;其中,任意第m级的第1路输出 $S_{m_1}$ 包含第m-1级的所有路输出的过零点信息;m=1,2,…,6;

所述循环温度计码转多进制码译码电路模块将第六级折叠插值级输出的六路数字信号译码成三位多进制码值,依次记为第6级低位多进制码b<sub>6,0</sub>、第6级次高位多进制码b<sub>6,1</sub>和第6级高位多进制码b<sub>6,2</sub>,并根据所述六路数字信号利用编码递归钳位校正逻辑产生第6级校准码e<sub>out 6</sub>传递给第五级折叠插值级;

所述循环温度计码转多进制码译码电路模块,根据第i+1级校准码 $e_{out,i+1}$ 将第i级折叠插值级输出的三路数字信号 $S_{i,1}$ 、 $S_{i,2}$ 、 $S_{i,3}$ 译码成两位多进制码值,包括:第i级低位多进制码 $b_{i,0}$ 和第i级高位多进制码 $b_{i,1}$ ,并根据所述第i级折叠插值级中输出的三路数字信号 $S_{i,1}$ 、 $S_{i,2}$ 、 $S_{i,3}$ 利用编码递归钳位校正逻辑产生第i级校准码 $e_{out,i}$ 后传递给第i-1级折叠插值级; $i=1,2,\cdots,5$ ;

所述循环温度计码转多进制码译码电路模块,根据第1级校准码 $e_{\text{out},1}$ 将一级预放大级输出的两路数字信号 $S_{0,1}$ 和 $S_{0,2}$ 译码成两位多进制码值,包括:第0级低位多进制码 $b_{0,0}$ 和第0级高位多进制码 $b_{0,1}$ ;

所述多进制转二进制逻辑译码电路模块包含6个多进制转二进制译码单元,任意第j个多进制转二进制译码单元将第j级低位多进制码 $b_{j,0}$ 和第j级高位多进制码 $b_{j,1}$ 转成相应位数的二进制数字码值 $d_i$ ; j=0,1,…,5;

所述串行加法器组模块包将所述三位多进制码值 $b_{6,0}$ 、 $b_{6,1}$ 和 $b_{6,2}$ 以及6个二进制数字码值  $\{d_i | j=0,1,\cdots,5\}$  依次相加,得到所述数字编码电路的数字输出 $D_0$ ,  $D_1$ ,  $\cdots$ ,  $D_{11}$ 。

2.一种应用于超高速流水线折叠插值模数转换器中的数字编码方法,所述模数转换器 是由一级预放大级和六级折叠插值级所构成的七级流水线,其特征是,所述数字编码方法 是按如下步骤进行:

步骤1、抽取所述模数转换器中一级预放大级输出的两路数字信号,包括:第0级第1路输出S<sub>0.1</sub>和第0级第2路输出S<sub>0.2</sub>;

抽取所述模数转换器中第一级折叠插值级至第五级折叠插值级中各级输出的三路数字信号,包括:第1级第1路输出 $S_{1,1}$ 、第1级第2路输出 $S_{1,2}$ 、第1级第3路输出 $S_{1,3}$ ~第5级第1路输出 $S_{5,1}$ 、第5级第2路输出 $S_{5,2}$ 、第5级第3路输出 $S_{5,3}$ ;

抽取所述模数转换器中第六级折叠插值级输出的六路数字信号,包括:第6级第1路输

出 $S_{6,1}$ ~第6级第6路输出 $S_{6,6}$ ;其中,任意第m级的第1路输出 $S_{m,1}$ 包含第m-1级的所有路输出的过零点信息; $m=1,2,\cdots,6$ ;

步骤2、利用式(1)将第六级折叠插值级输出的六路数字信号译码成三位多进制码值,依次记为第6级低位多进制码b<sub>6.0</sub>、第6级次高位多进制码b<sub>6.1</sub>和第6级高位多进制码b<sub>6.2</sub>:

$$\begin{cases} b_{6,2} = S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5} + S'_{6,1}S'_{6,2}S'_{6,3}S'_{6,4}S'_{6,5} \\ b_{6,1} = S'_{6,1}S'_{6,2}S'_{6,3}S_{6,5}S_{6,6} + S_{6,1}S_{6,2}S_{6,3}S'_{6,5}S'_{6,6} \\ b_{6,0} = S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} + S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} \\ + S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} + S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} \\ + S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} + S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} \end{cases}$$

(1)

式 (1) 中, $S'_{6,m}$ 表示第6级折叠插值级的第m路输出 $S_{6,m}$ 的逻辑非;+号表示逻辑"或"; $S_{6,m}$  $S_{6,m}$ 2表示两路输出的逻辑"与"操作;

步骤3:根据所述六路数字信号,利用式(2)产生第6级校准码e<sub>out,6</sub>:

$$e_{\text{out},6} = S_{6,1}$$

(2)

步骤4、根据第i+1级校准码 $e_{out,i+1}$ ,利用式(3)将第i级折叠插值级输出的三路数字信号  $S_{i,1}$ 、 $S_{i,2}$ 、 $S_{i,3}$ 译码成两位多进制码值,包括:第i级低位多进制码 $b_{i,0}$ 和第i级高位多进制码 $b_{i,1}$ :

$$\begin{cases} b_{i,0} = S_{i,1} S_{i,3} e'_{out,i+1} + S'_{i,1} S_{i,3} e_{out,i+1} \\ b_{i,1} = S_{i,1} S_{i,2} e_{out,i+1} \end{cases}$$

(3)

式(3)中, $e'_{out,i+1}$ 表示第i+1级校准码 $e_{out,i+1}$ 的逻辑非;

步骤5、根据所述第i级折叠插值级中输出的三路数字信号 $S_{i,1}$ 、 $S_{i,2}$ 、 $S_{i,3}$ ,利用式 (4) 产生第i级校准码 $e_{out}$  ;

$$e_{\text{out,i}} = S'_{i,2}S_{i,3}e_{\text{out,i+1}} + S_{i,1}S'_{i,3}e'_{\text{out,i+1}} + S_{i,1}S_{i,2}e_{\text{out,i+1}}$$

(4)

步骤6、根据第1级校准码 $e_{out,1}$ ,利用式 (5) 将一级预放大级输出的两路数字信号 $S_{0,1}$ 和  $S_{0,2}$ 译码成两位多进制码值,包括:第0级低位多进制码 $b_{0,0}$ 和第0级高位多进制码 $b_{0,1}$ ;

$$\begin{cases} b_{0,0} = S_{0,1} e'_{out,1} \\ b_{0,1} = S_{0,1} S_{0,2} e_{out,1} \end{cases}$$

(5)

式(5)中, $e'_{out,1}$ 表示第1级校准码 $e_{out,1}$ 的逻辑非;

步骤7、将第j级低位多进制码 $b_{j,0}$ 和第j级高位多进制码 $b_{j,1}$ 转成相应位数的二进制数字码值 $d_i$ ,j=0,1,…,5:

步骤7.1、利用式 (6) 将第5级低位多进制码 $b_{5,0}$ 和第5级高位多进制码 $b_{5,1}$ 转成4位数的二进制数字码值 $d_5 = \{d_{5.3}, d_{5.2}, d_{5.1}, d_{5.0}\}$ :

$$\begin{cases} d_{5,3} = b_{5,1} \\ d_{5,2} = b_{5,1} + b_{5,0} \\ d_{5,1} = b_{5,0} \\ d_{5,0} = 0 \end{cases}$$

(6)

步骤7.2、利用式(7)将第4级低位多进制码b4.0和第4级高位多进制码b4.1转成6位数的

二进制数字码值 $\mathbf{d_4} = \{\mathbf{d_{4,5}}, \mathbf{d_{4,4}}, \mathbf{d_{4,3}}, \mathbf{d_{4,2}}, \mathbf{d_{4,1}}, \mathbf{d_{4,0}}\}$ :

$$\begin{cases} d_{4,5} = b_{4,1} \\ d_{4,4} = b_{4,0} \\ d_{4,3} = 0 \\ d_{4,2} = b_{4,1} \\ d_{4,1} = b_{4,0} \\ d_{4,0} = 0 \end{cases}$$

$$(7)$$

步骤7.3、利用式 (8) 将第3级低位多进制码 $b_{3,0}$ 和第3级高位多进制码 $b_{3,1}$ 转成7位数的二进制数字码值 $d_3 = \{d_{3,6}, d_{3,5}, d_{3,4}, d_{3,3}, d_{3,2}, d_{3,1}, d_{3,0}\}$ :

$$\begin{cases} d_{3,6} = b_{3,1} \\ d_{3,5} = b_{3,1} + b_{3,0} \\ d_{3,4} = b_{3,0} \\ d_{3,3} = b_{3,1} \\ d_{3,2} = b_{3,1} + b_{3,0} \\ d_{3,1} = b_{3,0} \\ d_{3,0} = 0 \end{cases}$$

$$(8)$$

步骤7.4、利用式 (9) 将第2级低位多进制码 $b_{2,0}$ 和第2级高位多进制码 $b_{2,1}$ 转成9位数的二进制数字码值 $d_2$ =  $\{d_{2,8},d_{2,7},d_{2,6},d_{2,5},d_{2,4},d_{2,3},d_{2,2},d_{2,1},d_{2,0}\}$ :

$$\begin{cases} d_{2,8} = b_{2,1} \\ d_{2,7} = b_{2,0} \\ d_{2,6} = b_{2,1} \\ d_{2,5} = b_{2,0} \\ d_{2,4} = 0 \\ d_{2,3} = 0 \\ d_{2,8} = b_{2,1} \\ d_{2,8} = b_{2,0} \\ d_{2,8} = 0 \end{cases}$$

$$(9)$$

步骤7.5、利用式 (10) 将第1级低位多进制码 $b_{1,0}$ 和第2级高位多进制码 $b_{1,1}$ 转成9位数的二进制数字码值 $d_1 = \{d_{1.9}, d_{1.8}, d_{1.7}, d_{1.6}, d_{1.5}, d_{1.4}, d_{1.3}, d_{1.2}, d_{1.1}, d_{1.0}\}$ :

$$\begin{cases} d_{0,11} = b_{0,1} \\ d_{0,10} = b_{0,0} \\ d_{0,9} = b_{0,1} \\ d_{0,8} = b_{0,1} + b_{0,0} \\ d_{0,7} = b_{0,0} \\ d_{0,6} = b_{0,1} \\ d_{0,5} = b_{0,1} + b_{0,0} \\ d_{0,4} = b_{0,0} \\ d_{0,3} = 0 \\ d_{0,2} = b_{0,1} \\ d_{0,1} = b_{0,0} \\ d_{0,11} = 0 \end{cases}$$

$$(10)$$

步骤7.6、利用式 (11) 将预放大级低位多进制码 $b_{0,0}$ 和第2级高位多进制码 $b_{0,1}$ 转成12位数的二进制数字码值 $d_0 = \{d_{0,11}, d_{0,10}, d_{0,9}, d_{0,8}, d_{0,7}, d_{0,6}, d_{0,5}, d_{0,4}, d_{0,3}, d_{0,2}, d_{0,1}, d_{0,0}\}$ :

$$\begin{cases} d_{0,11} = b_{0,1} \\ d_{0,10} = b_{0,0} \\ d_{0,9} = b_{0,1} \\ d_{0,8} = b_{0,1} + b_{0,0} \\ d_{0,7} = b_{0,0} \\ d_{0,6} = b_{0,1} \\ d_{0,5} = b_{0,1} + b_{0,0} \\ d_{0,4} = b_{0,0} \\ d_{0,3} = 0 \\ d_{0,2} = b_{0,1} \\ d_{0,1} = b_{0,0} \\ d_{0,11} = 0 \end{cases}$$

$$(11)$$

步骤8、将所述三位多进制码值 $b_{6,0}$ 、 $b_{6,1}$ 和 $b_{6,2}$ 以及6个二进制数字码值  $\{d_j | j=0,1,\cdots,5\}$  依次相加,得到数字编码电路的数字输出 $D_0,D_1,\cdots,D_{11}$ 。

# 应用于超高速流水线折叠插值结构的模数转换器的数字编码 电路及其方法

### 技术领域

[0001] 本发明属于混合信号电路设计中模数转换器的数字编码方案技术领域,具体说就是一种适用于超高速流水线折叠插值ADC的数字编码解决方案。

### 背景技术

[0002] 当前随着5G移动通信的兴起,欧盟启动Mobile andWireless Communications Enablers for the Twenty-Twenty Information Society (METIS)项目,建立了新一代5G通信的标准,提出的指标中包含峰值数据速率需要大于10Gb/s和无线延迟小于1毫秒等,而我国工信部提出的5G通信标准中,要求ADC的速度和精度需要分别达到3.6Gs/s和12位,因此研究高速、高精度ADC具有重大意义和价值。

[0003] ADC实现的结构众多,其中主要有全并行、流水线、逐次逼近型和折叠插值等结构。全并行结构可以实现超高速量化转换,但是功耗和面积随着精度的提高而呈指数增加;流水线结构利用流水分级量化原理实现高速和高精度,由于结构内部负反馈对带宽的制约,较难实现超高速度;逐次逼近型结构具备较高设计自由度和较低功耗,同时利用时间交织技术可以达到超高速性能,然而增加过多的通道也引入了新的误差因素,需要额外的校准技术保证其精度性能,设计难度大大提高;折叠插值结构速度可以和全并行结构相媲美,而折叠电路和插值电路又有效降低了功耗和面积。另外,为了结合各个结构的优点,混合架构ADC也应运而生,如将流水结构应用于级联折叠插值ADC,可以有效解决级间带宽受限问题,进一步提高了ADC的速度与精度。

[0004] 综上可以看出,流水线折叠插值技术在实现超高速和高精度ADC上具有一定的优势。然而折叠插值ADC采用全开环结构,其折叠内插信号产生的过零点对工艺偏差极其敏感,影响实际量化精度。在工艺特征尺寸越来越小、电源电压不断降低的情况下,模拟电路的失配成为电路设计的难点之一,也制约了折叠插值ADC的发展。

### 发明内容

[0005] 本发明旨针对超高速流水线折叠插值的设计难点,提出一种应用于超高速流水线折叠插值结构的模数转换器的数字编码电路及其方法,以期能减少由于电路结构以及工艺限制对ADC量化精度的影响,从而实现高速、准确的数字编码。

[0006] 本发明为解决技术问题采用如下技术方案:

[0007] 本发明一种应用于超高速流水线折叠插值结构的模数转换器的数字编码电路,所述模数转换器是由一级预放大级和六级折叠插值级所构成的七级流水线,其特点是,所述数字编码电路包括:循环温度计码转多进制译码电路模块、多进制转二进制逻辑译码器模块、串行加法器组模块;

[0008] 所述循环温度计码转多进制译码电路模块抽取所述模数转换器中一级预放大级输出的两路数字信号,包括:第0级第1路输出S<sub>0.1</sub>和第0级第2路输出S<sub>0.2</sub>;

[0009] 所述循环温度计码转多进制译码电路模块抽取所述模数转换器中第一级折叠插值级至第五级折叠插值级中各级输出的三路数字信号,包括:第1级第1路输出 $S_{1,1}$ 、第1级第2路输出 $S_{1,2}$ 、第1级第3路输出 $S_{1,3}$ ~第5级第1路输出 $S_{5,1}$ 、第5级第2路输出 $S_{5,2}$ 、第5级第3路输出 $S_{5,3}$ ;

[0010] 所述循环温度计码转多进制译码电路模块抽取所述模数转换器中第六级折叠插值级输出的六路数字信号,包括:第6级第1路输出 $S_{6,1}$ ~第6级第6路输出 $S_{6,6}$ ;其中,任意第m级的第1路输出 $S_{m,1}$ 包含第m-1级的所有路输出的过零点信息;m=1,2,…,6;

[0011] 所述循环温度计码转多进制码译码电路模块将第六级折叠插值级输出的六路数字信号译码成三位多进制码值,依次记为第6级低位多进制码 $b_{6,0}$ 、第6级次高位多进制码 $b_{6,1}$ 和第6级高位多进制码 $b_{6,2}$ ,并根据所述六路数字信号利用编码递归钳位校正逻辑产生第6级校准码 $e_{out}$ 6传递给第五级折叠插值级;

[0012] 所述循环温度计码转多进制码译码电路模块,根据第i+1级校准码 $e_{out,i+1}$ 将第i级折叠插值级输出的三路数字信号 $S_{i,1}$ 、 $S_{i,2}$ 、 $S_{i,3}$ 译码成两位多进制码值,包括:第i级低位多进制码 $b_{i,0}$ 和第i级高位多进制码 $b_{i,1}$ ,并根据所述第i级折叠插值级中输出的三路数字信号  $S_{i,1}$ 、 $S_{i,2}$ 、 $S_{i,3}$ 利用编码递归钳位校正逻辑产生第i级校准码 $e_{out,i}$ 后传递给第i-1级折叠插值级; $i=1,2,\cdots,5$ ;

[0013] 所述循环温度计码转多进制码译码电路模块,根据第1级校准码 $e_{\text{out},1}$ 将一级预放大级输出的两路数字信号 $S_{0,1}$ 和 $S_{0,2}$ 译码成两位多进制码值,包括:第0级低位多进制码b $_{0,0}$ 和第0级高位多进制码b $_{0,1}$ ;

[0014] 所述多进制转二进制逻辑译码电路模块包含6个多进制转二进制译码单元,任意第j个多进制转二进制译码单元将第j级低位多进制码 $b_{j,0}$ 和第j级高位多进制码 $b_{j,1}$ 转成相应位数的二进制数字码值 $d_i$ ; j=0,1,…,5;

[0015] 所述串行加法器组模块包将所述三位多进制码值 $b_{6,0}$ 、 $b_{6,1}$ 和 $b_{6,2}$ 以及6个二进制数字码值  $\{d_i | j=0,1,\cdots,5\}$  依次相加,得到所述数字编码电路的数字输出 $D_0,D_1,\cdots,D_{11}$ 。

[0016] 本发明一种应用于超高速流水线折叠插值模数转换器中的数字编码方法,所述模数转换器是由一级预放大级和六级折叠插值级所构成的七级流水线,其特点是,所述数字编码方法是按如下步骤进行:

[0017] 步骤1、抽取所述模数转换器中一级预放大级输出的两路数字信号,包括:第0级第1路输出S<sub>0</sub>,和第0级第2路输出S<sub>0</sub>。;

[0018] 抽取所述模数转换器中第一级折叠插值级至第五级折叠插值级中各级输出的三路数字信号,包括:第1级第1路输出 $S_{1,1}$ 、第1级第2路输出 $S_{1,2}$ 、第1级第3路输出 $S_{1,3}$ ~第5级第1路输出 $S_{5,2}$ 、第5级第2路输出 $S_{5,2}$ 、第5级第3路输出 $S_{5,3}$ ;

[0019] 抽取所述模数转换器中第六级折叠插值级输出的六路数字信号,包括:第6级第1路输出 $S_{6,1}$ ~第6级第6路输出 $S_{6,6}$ ;其中,任意第m级的第1路输出 $S_{m,1}$ 包含第m-1级的所有路输出的过零点信息; $m=1,2,\cdots,6$ ;

[0020] 步骤2、利用式(1)将第六级折叠插值级输出的六路数字信号译码成三位多进制码值,依次记为第6级低位多进制码 $b_{6,0}$ 、第6级次高位多进制码 $b_{6,1}$ 和第6级高位多进制码 $b_{6,2}$ :

$$\begin{bmatrix} b_{6,2} = S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5} + S_{6,1}'S_{6,2}'S_{6,3}'S_{6,4}'S_{6,5}' \\ b_{6,1} = S_{6,1}'S_{6,2}'S_{6,3}'S_{6,5}S_{6,6} + S_{6,1}S_{6,2}S_{6,3}S_{6,5}'S_{6,6}' \\ b_{6,0} = S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} + S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} \\ + S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} + S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} \\ + S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} + S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} \end{bmatrix}$$

(1)

式 (1) 中, $S'_{6,m}$ 表示第6级折叠插值级的第m路输出 $S_{6,m}$ 的逻辑非;+号表示逻辑 "或";S。,S。,表示两路输出的逻辑"与"操作;

步骤3:根据所述六路数字信号,利用式(2)产生第6级校准码e<sub>out.6</sub>: [0023]

$$[0024] \quad e_{\text{out},6} = S_{6,1} \tag{2}$$

$e_{\text{out},6} = S_{6,1}$  步骤4、根据第i+1级校准码 $e_{\text{out},i+1}$ ,利用式(3)将第i级折叠插值级输出的三路数 字信号S<sub>i1</sub>、S<sub>i2</sub>、S<sub>i3</sub>译码成两位多进制码值,包括:第i级低位多进制码b<sub>i0</sub>和第i级高位多 进制码b; 1:

[0026]

$$\begin{cases} b_{i,0} = S_{i,1} S_{i,3} e'_{out,i+1} + S'_{i,1} S_{i,3} e_{out,i+1} \\ b_{i,1} = S_{i,1} S_{i,2} e_{out,i+1} \end{cases}$$

(3)

式(3)中,e'<sub>out,i+1</sub>表示第i+1级校准码e<sub>out,i+1</sub>的逻辑非; [0027]

步骤5、根据所述第i级折叠插值级中输出的三路数字信号 $S_{i,1}$ 、 $S_{i,2}$ 、 $S_{i,3}$ ,利用式 [0028] (4)产生第i级校准码e ;:

[0029]

$$e_{\text{out,i}} = S'_{i,2} S_{i,3}^{\text{out,i+1}} + S_{i,1} S'_{i,3} e'_{\text{out,i+1}} + S_{i,1} S_{i,2} e_{\text{out,i+1}}$$

(4)

步骤6、根据第1级校准码e<sub>out,1</sub>,利用式(5)将一级预放大级输出的两路数字信号 [0030] S<sub>0.1</sub>和S<sub>0.2</sub>译码成两位多进制码值,包括:第0级低位多进制码b<sub>0.0</sub>和第0级高位多进制码b<sub>0.1</sub>;

[0031]

$$\begin{cases} b_{0,0} = S_{0,1} e'_{out,1} \\ b_{0,1} = S_{0,1} S_{0,2} e_{out,1} \end{cases}$$

(5)

式(5)中,e'<sub>out.1</sub>表示第1级校准码e<sub>out.1</sub>的逻辑非; [0032]

步骤7、将第j级低位多进制码b; n和第j级高位多进制码b; 1转成相应位数的二进 [0033] 制数字码值 $d_i$ ,  $j=0,1,\dots,5$ :

步骤7.1、利用式(6)将第5级低位多进制码b<sub>50</sub>和第5级高位多进制码b<sub>51</sub>转成4位 [0034] 数的二进制数字码值 $d_5 = \{d_{5,3}, d_{5,2}, d_{5,1}, d_{5,0}\}$ :

[0035]

$$\begin{cases} d_{5,3} = b_{5,1} \\ d_{5,2} = b_{5,1} + b_{5,0} \\ d_{5,1} = b_{5,0} \\ d_{5,0} = 0 \end{cases}$$

(6)

[0036] 步骤7.2、利用式(7)将第4级低位多进制码 $b_{4,0}$ 和第4级高位多进制码 $b_{4,1}$ 转成6位 数的二进制数字码值 $d_4 = \{d_{4.5}, d_{4.4}, d_{4.3}, d_{4.2}, d_{4.1}, d_{4.0}\}$ :

$$\begin{bmatrix} d_{4,5} = b_{4,1} \\ d_{4,4} = b_{4,0} \\ d_{4,3} = 0 \\ d_{4,2} = b_{4,1} \\ d_{4,1} = b_{4,0} \\ d_{4,0} = 0 \\ \end{bmatrix} \tag{7}$$

[0038] 步骤7.3、利用式 (8) 将第3级低位多进制码 $b_{3,0}$ 和第3级高位多进制码 $b_{3,1}$ 转成7位数的二进制数字码值 $d_3$ =  $\{d_{3,6},d_{3,5},d_{3,4},d_{3,3},d_{3,2},d_{3,1},d_{3,0}\}$ :

$$\begin{cases} d_{3,6} = b_{3,1} \\ d_{3,5} = b_{3,1} + b_{3,0} \\ d_{3,4} = b_{3,0} \\ d_{3,3} = b_{3,1} \\ d_{3,2} = b_{3,1} + b_{3,0} \\ d_{3,1} = b_{3,0} \\ d_{3,0} = 0 \end{cases} \tag{8}$$

[0040] 步骤7.4、利用式 (9) 将第2级低位多进制码 $b_{2,0}$ 和第2级高位多进制码 $b_{2,1}$ 转成9位数的二进制数字码值 $d_2$ =  $\{d_{2,8},d_{2,7},d_{2,6},d_{2,5},d_{2,4},d_{2,3},d_{2,2},d_{2,1},d_{2,0}\}$ :

$$\begin{cases} d_{2,8} = b_{2,1} \\ d_{2,7} = b_{2,0} \\ d_{2,6} = b_{2,1} \\ d_{2,5} = b_{2,0} \\ d_{2,4} = 0 \\ d_{2,3} = 0 \\ d_{2,8} = b_{2,1} \\ d_{2,8} = b_{2,0} \\ d_{2,8} = 0 \end{cases} \tag{9}$$

[0042] 步骤7.5、利用式 (10) 将第1级低位多进制码 $b_{1,0}$ 和第2级高位多进制码 $b_{1,1}$ 转成9位数的二进制数字码值 $d_1 = \{d_{1,9}, d_{1,8}, d_{1,7}, d_{1,6}, d_{1,5}, d_{1,4}, d_{1,3}, d_{1,2}, d_{1,1}, d_{1,0}\}$ :

$$\begin{bmatrix} d_{0,11} = b_{0,1} \\ d_{0,10} = b_{0,0} \\ d_{0,9} = b_{0,1} \\ d_{0,8} = b_{0,1} + b_{0,0} \\ d_{0,7} = b_{0,0} \\ d_{0,6} = b_{0,1} \\ d_{0,5} = b_{0,1} + b_{0,0} \\ d_{0,4} = b_{0,0} \\ d_{0,3} = 0 \\ d_{0,2} = b_{0,1} \\ d_{0,1} = b_{0,0} \\ d_{0,11} = 0 \\ \end{bmatrix}$$

[0044] 步骤7.6、利用式 (11) 将预放大级低位多进制码 $b_{0,0}$ 和第2级高位多进制码 $b_{0,1}$ 转成12位数的二进制数字码值 $d_0 = \{d_{0,11}, d_{0,10}, d_{0,9}, d_{0,8}, d_{0,7}, d_{0,6}, d_{0,5}, d_{0,4}, d_{0,3}, d_{0,2}, d_{0,1}, d_{0,0}\}$ :

$$\begin{cases} d_{0,11} = b_{0,1} \\ d_{0,10} = b_{0,0} \\ d_{0,9} = b_{0,1} \\ d_{0,8} = b_{0,1} + b_{0,0} \\ d_{0,7} = b_{0,0} \\ d_{0,6} = b_{0,1} \\ d_{0,5} = b_{0,1} + b_{0,0} \\ d_{0,4} = b_{0,0} \\ d_{0,3} = 0 \\ d_{0,2} = b_{0,1} \\ d_{0,1} = b_{0,0} \\ d_{0,11} = 0 \end{cases}$$

(11)

[0046] 步骤8、将所述三位多进制码值 $b_{6,0}$ 、 $b_{6,1}$ 和 $b_{6,2}$ 以及6个二进制数字码值 { $d_j$  | j=0, 1,…,5} 依次相加,得到所述数字编码电路的数字输出 $D_0$ ,  $D_1$ ,…, $D_{11}$ 。

[0047] 与现有技术相比,本发明的有益效果在于:

[0048] 1、本发明基于模数转换器的结构,通过合理设计每级比较器信号抽取、比较器抽取信号冗余,以及通过后级递归校准前级的方案,仅需23个比较器信号,即可完成12位精度的量化。与传统全并行模数转换器或者折叠插值模数转换器相比,大大减少了比较器数目。 [0049] 2、本发明利用简易的逻辑电路以及冗余操作进行递归钳位校正,从而实现了低复杂度的数字校正;

[0050] 3、本发明利用简易逻辑电路以及少量串行进位加法器实现了循环温度计码到多进制码再到二进制码的转换,避免了复杂逻辑以及复杂计算,实现了简易的全定制化译码。

### 附图说明

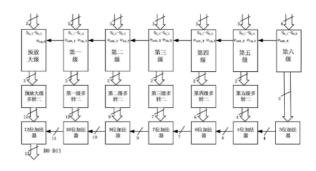

[0051] 图1为本发明的整体实现框图;

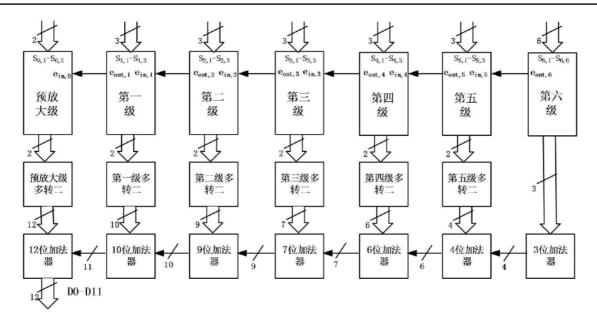

[0052] 图2为本发明的多进制转二进制译码具体实现方案图;

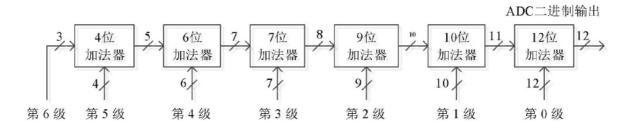

[0053] 图3为本发明的串行进位加法器组的实现与组织方案图;

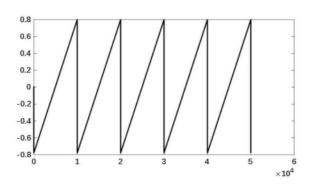

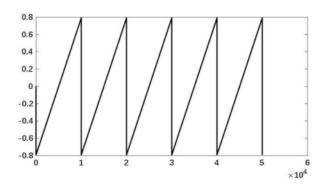

[0054] 图4a为本发明中模数转换器输入的斜坡信号图;

[0055] 图4b为本发明中输入斜坡信号时编码电路的输出图;

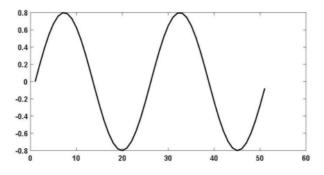

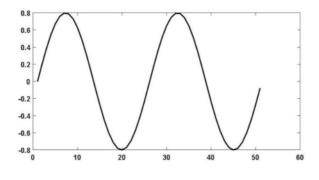

[0056] 图5a为本发明中模数转换器输入的正弦信号图:

[0057] 图5b为本发明中输入正弦信号时编码电路的输出图。

### 具体实施方式

[0058] 本实施例中,模数转换器是由一级预放大级和六级折叠插值级所构成的七级流水线,一种应用于超高速流水线折叠插值结构的模数转换器的数字编码电路,如图1所示,包括:循环温度计码转多进制译码电路模块、多进制转二进制逻辑译码器模块、串行加法器组模块;

[0059] 循环温度计码转多进制译码电路模块抽取模数转换器7级流水线中共23个比较器输出信号,因此本实施例中编码电路仅需要23个比较器,相比于传统折叠插值ADC,大大节省了比较器数目。23个比较器的输出信号具体包括:一级预放大级输出的两路数字信号,即:第0级第1路输出 $S_{0,1}$ 和第0级第2路输出 $S_{0,2}$ ;第一级折叠插值级至第五级折叠插值级中各级输出的三路数字信号,即:第1级第1路输出 $S_{1,1}$ 、第1级第2路输出 $S_{1,2}$ 、第1级第3路输出 $S_{1,3}$ ~第5级第1路输出 $S_{5,1}$ 、第5级第2路输出 $S_{5,2}$ 、第5级第3路输出 $S_{5,3}$ ;第六级折叠插值级输出的六路数字信号,即:第6级第1路输出 $S_{6,1}$ ~第6级第6路输出 $S_{6,6}$ ;其中,任意第m级的第1路输出 $S_{m}$  包含第m-1级的所有路输出的过零点信息;m=1,2,…,6;

[0060] 循环温度计码转多进制码译码电路模块将第六级折叠插值级输出的六路数字信号译码成三位多进制码值,依次记为第6级低位多进制码 $b_{6,0}$ 、第6级次高位多进制码 $b_{6,1}$ 和第6级高位多进制码 $b_{6,2}$ ,由于之前比较器信号抽取时,第6级的第一路 $S_{6,1}$ 包含第五级所有抽取比较器输出信号的过零点,同时由于流水线折叠插值模数转换器的级间增益放大作用,经过7级流水线放大的比较器输出可以近似为理想值,因此可以根据式 (2) 所示的递归钳位校正逻辑产生第6级校准码 $e_{\text{out.}6}$ 传递给第5级;

[0061] 循环温度计码转多进制码译码电路模块根据第i+1级校准码 $e_{out,i+1}$ 将第i级折叠插值级输出的三路数字信号 $S_{i,1}$ 、 $S_{i,2}$ 、 $S_{i,3}$ 译码成两位多进制码值,包括:第i级低位多进制码 $b_{i,0}$ 和第i级高位多进制码 $b_{i,1}$ ,并根据第i级折叠插值级中输出的三路数字信号 $S_{i,1}$ 、 $S_{i,2}$ 、 $S_{i,3}$ 利用编码递归钳位校正逻辑产生第i级校准码 $e_{out,i}$ 后传递给第i-1级折叠插值级;i=1, 2,  $\cdots$ , 5;

[0062] 循环温度计码转多进制码译码电路模块根据第1级校准码 $e_{out,1}$ 将一级预放大级输出的两路数字信号 $S_{0,1}$ 和 $S_{0,2}$ 译码成两位多进制码值,包括:第0级低位多进制码 $b_{0,0}$ 和第0级高位多进制码 $b_{0,1}$ ;

[0063] 如图1所示,多进制转二进制逻辑译码电路模块包含6个多进制转二进制译码单元,任意第j个多进制转二进制译码单元将第j级低位多进制码 $b_{j,0}$ 和第j级高位多进制码 $b_{j,0}$ 和第j级高位多进制码 $b_{j,0}$ 和第j级高位多进制码 $b_{j,0}$ 和第j级高位多进制码

[0064] 串行加法器组模块包将三位多进制码值 $b_{6,0}$ 、 $b_{6,1}$ 和 $b_{6,2}$ 以及6个二进制数字码值  $\{d_i | j=0,1,\cdots,5\}$  依次相加,得到数字编码电路的数字输出 $D_0,D_1,\cdots,D_{11}$ 。

[0065] 本实施例中,一种应用于超高速流水线折叠插值模数转换器中的数字编码方法是按如下步骤进行:

[0066] 步骤1、如图1所示,抽取模数转换器中一级预放大级输出的两路数字信号,包括:第0级第1路输出S<sub>0.1</sub>和第0级第2路输出S<sub>0.2</sub>;

[0067] 抽取模数转换器中第一级折叠插值级至第五级折叠插值级中各级输出的三路数字信号,包括:第1级第1路输出 $S_{1,1}$ 、第1级第2路输出 $S_{1,2}$ 、第1级第3路输出 $S_{1,3}$ ~第5级第1路输出 $S_{5,1}$ 、第5级第2路输出 $S_{5,2}$ 、第5级第3路输出 $S_{5,3}$ ;

[0068] 抽取模数转换器中第六级折叠插值级输出的六路数字信号,包括:第6级第1路输出 $S_{6,1}$ ~第6级第6路输出 $S_{6,6}$ ;其中,任意第m级的第1路输出 $S_{m,1}$ 包含第m-1级的所有路输出的过零点信息; $m=1,2,\cdots,6$ ;

[0069] 步骤2、利用式(1)将第六级折叠插值级输出的六路数字信号译码成三位多进制码值,依次记为第6级低位多进制码b<sub>6.0</sub>、第6级次高位多进制码b<sub>6.1</sub>和第6级高位多进制码b<sub>6.2</sub>:

$$\begin{bmatrix} b_{6,2} = S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5} + S'_{6,1}S'_{6,2}S'_{6,3}S'_{6,4}S'_{6,5} \\ b_{6,1} = S'_{6,1}S'_{6,2}S'_{6,3}S_{6,5}S_{6,6} + S_{6,1}S_{6,2}S_{6,3}S'_{6,5}S'_{6,6} \\ b_{6,0} = S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} + S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} \\ + S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} + S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} \\ + S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} + S_{6,1}S_{6,2}S_{6,3}S_{6,4}S_{6,5}S_{6,6} \end{bmatrix}$$

(1)

[0071] 式 (1) 中, $S'_{6,m}$ 表示第6级折叠插值级的第m路输出 $S_{6,m}$ 的逻辑非;+号表示逻辑"或"; $S_{6,1}S_{6,2}$ 表示两路输出的逻辑"与"操作;

[0072] 步骤3:根据六路数字信号利用式(2)产生第6级校准码equt 6:

[0073]

$$e_{\text{out},6} = S_{6,1}$$

(2)

[0074] 步骤4、根据第i+1级校准码 $e_{out,i+1}$ ,利用式 (3) 将第i级折叠插值级输出的三路数字信号 $S_{i,1}$ 、 $S_{i,2}$ 、 $S_{i,3}$ 译码成两位多进制码值,包括:第i级低位多进制码 $b_{i,0}$ 和第i级高位多进制码 $b_{i,1}$ :

[0075]

$$\begin{cases} b_{i,0} = S_{i,1} S_{i,3} e'_{out,i+1} + S'_{i,1} S_{i,3} e_{out,i+1} \\ b_{i,1} = S_{i,1} S_{i,2} e_{out,i+1} \end{cases}$$

(3)

[0076] 式(3)中, $e'_{out,i+1}$ 表示第i+1级校准码 $e_{out,i+1}$ 的逻辑非;

[0077] 步骤5、根据第i级折叠插值级中输出的三路数字信号 $S_{i,1}$ 、 $S_{i,2}$ 、 $S_{i,3}$ ,利用式(4)产生第i级校准码 $e_{out,i}$ :

$$[0078] \quad e_{\text{out,i}} = S'_{i,2} S_{i,3} e_{\text{out,i+1}} + S_{i,1} S'_{i,3} e'_{\text{out,i+1}} + S_{i,1} S_{i,2} e_{\text{out,i+1}}$$

(4)

[0079] 步骤6、根据第1级校准码 $e_{\text{out},1}$ ,利用式(5)将一级预放大级输出的两路数字信号  $S_{0.1}$ 和 $S_{0.2}$ 译码成两位多进制码值,包括:第0级低位多进制码 $b_{0.0}$ 和第0级高位多进制码 $b_{0.1}$ ;

[0080]

$$\begin{cases} b_{0,0} = S_{0,1} e'_{out,1} \\ b_{0,1} = S_{0,1} S_{0,2} e_{out,1} \end{cases}$$

(5)

[0081] 式(35)中,e'<sub>out.1</sub>表示第1级校准码e<sub>out.1</sub>的逻辑非;

[0082] 步骤7、如图2所示的方式,将第j级低位多进制码 $b_{j,0}$ 和第j级高位多进制码 $b_{j,1}$ 转成相应位数的二进制数字码值 $d_i$ ,j=0,1,…,5:

[0083] 步骤7.1、利用式 (6) 将第5级低位多进制码 $b_{5,0}$ 和第5级高位多进制码 $b_{5,1}$ 转成4位数的二进制数字码值 $d_5 = \{d_{5,3}, d_{5,2}, d_{5,1}, d_{5,0}\}$ :

[0084]

$$\begin{cases} d_{5,3} = b_{5,1} \\ d_{5,2} = b_{5,1} + b_{5,0} \\ d_{5,1} = b_{5,0} \\ d_{5,0} = 0 \end{cases}$$

(6)

[0085] 步骤7.2、利用式 (7) 将第4级低位多进制码 $b_{4,0}$ 和第4级高位多进制码 $b_{4,1}$ 转成6位数的二进制数字码值 $d_4$ =  $\{d_{4,5},d_{4,4},d_{4,3},d_{4,2},d_{4,1},d_{4,0}\}$ :

$$\begin{bmatrix} d_{4,5} = b_{4,1} \\ d_{4,4} = b_{4,0} \\ d_{4,3} = 0 \\ d_{4,2} = b_{4,1} \\ d_{4,1} = b_{4,0} \\ d_{4,0} = 0 \\ \end{bmatrix}$$

(7)

[0087] 步骤7.3、利用式 (8) 将第3级低位多进制码 $b_{3,0}$ 和第3级高位多进制码 $b_{3,1}$ 转成7位数的二进制数字码值 $d_3 = \{d_{3,6}, d_{3,5}, d_{3,4}, d_{3,3}, d_{3,2}, d_{3,1}, d_{3,0}\}$ :

$$\begin{bmatrix} d_{3,6} = b_{3,1} \\ d_{3,5} = b_{3,1} + b_{3,0} \\ d_{3,4} = b_{3,0} \\ d_{3,3} = b_{3,1} \\ d_{3,2} = b_{3,1} + b_{3,0} \\ d_{3,1} = b_{3,0} \\ d_{3,0} = 0 \end{bmatrix}$$

(8)

[0089] 步骤7.4、利用式 (9) 将第2级低位多进制码 $b_{2,0}$ 和第2级高位多进制码 $b_{2,1}$ 转成9位数的二进制数字码值 $d_2$ =  $\{d_{2,8},d_{2,7},d_{2,6},d_{2,5},d_{2,4},d_{2,3},d_{2,2},d_{2,1},d_{2,0}\}$ :

$$\begin{cases} d_{2,8} = b_{2,1} \\ d_{2,7} = b_{2,0} \\ d_{2,6} = b_{2,1} \\ d_{2,5} = b_{2,0} \\ d_{2,4} = 0 \\ d_{2,3} = 0 \\ d_{2,8} = b_{2,1} \\ d_{2,8} = b_{2,0} \\ d_{2,8} = 0 \end{cases} \tag{9}$$

[0091] 步骤7.5、利用式 (10) 将第1级低位多进制码 $b_{1,0}$ 和第2级高位多进制码 $b_{1,1}$ 转成9位数的二进制数字码值 $d_1 = \{d_{1,9}, d_{1,8}, d_{1,7}, d_{1,6}, d_{1,5}, d_{1,4}, d_{1,3}, d_{1,2}, d_{1,1}, d_{1,0}\}$ :

$$\begin{bmatrix} d_{0,11} = b_{0,1} \\ d_{0,10} = b_{0,0} \\ d_{0,9} = b_{0,1} \\ d_{0,8} = b_{0,1} + b_{0,0} \\ d_{0,7} = b_{0,0} \\ d_{0,6} = b_{0,1} \\ d_{0,5} = b_{0,1} + b_{0,0} \\ d_{0,4} = b_{0,0} \\ d_{0,3} = 0 \\ d_{0,2} = b_{0,1} \\ d_{0,1} = b_{0,0} \\ d_{0,1} = 0 \end{bmatrix}$$

$$(10)$$

[0093] 步骤7.6、利用式 (11) 将预放大级低位多进制码b<sub>0,0</sub>和第2级高位多进制码b<sub>0,1</sub>转成 12位数的二进制数字码值d<sub>0</sub>=  $\{d_{0,11},d_{0,10},d_{0,9},d_{0,8},d_{0,7},d_{0,6},d_{0,5},d_{0,4},d_{0,3},d_{0,2},d_{0,1},d_{0,0}\}$ :

$$\begin{cases} d_{0,11} = b_{0,1} \\ d_{0,10} = b_{0,0} \\ d_{0,9} = b_{0,1} \\ d_{0,8} = b_{0,1} + b_{0,0} \\ d_{0,7} = b_{0,0} \\ d_{0,6} = b_{0,1} \\ d_{0,5} = b_{0,1} + b_{0,0} \\ d_{0,4} = b_{0,0} \\ d_{0,3} = 0 \\ d_{0,2} = b_{0,1} \\ d_{0,1} = b_{0,0} \\ d_{0,11} = 0 \end{cases}$$

[0095] 步骤8、如图3所示的加法器组,将三位多进制码值 $b_{6,0}$ 、 $b_{6,1}$ 和 $b_{6,2}$ 以及6个二进制数字码值  $\{d,|j=0,1,\cdots,5\}$  依次相加,得到数字编码电路的数字输出 $D_0,D_1,\cdots,D_{11}$ 。

[0096] 图4a所示为输入模数转换器的斜坡信号,归一化幅值为-0.8到0.8,斜坡数量为5,图4b为经过模数转换器量化后,按照本发明抽取相应23个比较器输出,然后再编码,将编码后的12位二进制值转成归一化数值后的结果,可以看到数字编码电路编码完全正确。

[0097] 图5a所示为输入模数转换器的正弦信号波形,归一化幅值为-0.8-0.8,周期数为2,图5b为经过模数转换器量化后,按照本发明抽取相应23个比较器输出,然后再编码,将编码后的12位二进制值转成归一化数值后的结果,可以看到数字编码电路同样编码完全正确。

[0098] 综上所述,本发明通过简易逻辑以及少量加法计算,实现了编码,节省了硬件开销以及功耗。

图1

| 输入       | H 174 | 输出           |         | 编码信号对 |

|----------|-------|--------------|---------|-------|

| 三进制      | 电路    | 二进制          | 十进制     | 应的级数  |

| 00       |       | 0000         | 0       |       |

| 01<br>10 | 0     | 0110<br>1100 | 6<br>12 | 第5级   |

| 00       | •     | 000000       | 0       |       |

| 01       |       | 010010       | 18      | 第4级   |

| 10       | 0     | 100100       | 36      |       |

| 00       |       | 0000000      | 0       |       |

| 01       |       | 0110110      | 54      | 第3级   |

| 10       | 0     | 1101100      | 108     |       |

| 00       | •     | 000000000    | 0       |       |

| 01       | 0     | 010100010    | 162     | 第2级   |

| 10       |       | 101000100    | 324     |       |

| 00       |       | 0000000000   | 0       |       |

| 01       | 12110 | 0111100110   | 486     | 第1级   |

| 10       | 0-    | 1111001100   | 972     |       |

| 00       |       | 000000000000 | 0       |       |

| 01       |       | 010110110010 | 1458    | 预放大级  |

| 10       | 0     | 101101100100 | 2916    |       |

图2

图3

图4a

图4b

图5a

图5b