# (19)대한민국특허청(KR) (12) 등록특허공보(B1)

(51) 。Int. Cl.

H01L 27/115 (2006.01)

H01L 21/8247 (2006.01)

(45) 공고일자 2007년06월15일 (11) 등록번호 10-0728985

(24) 등록일자 2007년06월08일

(21) 출원번호10-2006-0044173(22) 출원일자2006년05월17일심사청구일자2006년05월17일

(65) 공개번호 (43) 공개일자

(73) 특허권자 주식회사 하이닉스반도체

경기 이천시 부발읍 아미리 산136-1

(72) 발명자 장헌용

경기 수원시 팔달구 우만동 600번지 월드 메르디앙 103동 702호

(74) 대리인 강성배

(56) 선행기술조사문헌 1020040050407 1020030087426

1020040038422 1020050033340

심사관: 김기현

전체 청구항 수 : 총 6 항

## (54) 상변환 기억 소자 및 그의 제조방법

#### (57) 요약

본 발명은 상변환 기억 소자 및 그의 제조방법을 개시한다. 개시된 본 발명에 따른 상변환 기억 소자는, 하부전극이 형성된 반도체기판; 상기 기판 상에 형성되고 하부전극의 일부를 노출시키는 콘택홀을 갖는 제1층간절연막; 상기 콘택홀을 매립 하면서 콘택홀 주위의 제1층간절연막 부분 상에 형성된 제1상변환막; 상기 제1상변환막 상에 형성된 절연막; 상기 절연막 상에 형성된 상부전극; 상기 상부전극, 절연막 및 제1상변환막의 적층 패턴 측벽에 형성된 제2상변환막; 상기 제2상변환막을 포함한 적층 패턴을 덮도록 제1층간절연막 상에 형성된 제2층간절연막; 상기 제2층간절연막 상에 상부전극과 콘택하도록 형성된 비트라인;을 포함하는 것을 특징으로 한다.

#### 대표도

도 3

## 특허청구의 범위

## 청구항 1.

하부전극이 형성된 반도체기판;

상기 기판 상에 형성되고 하부전극의 일부를 노출시키는 콘택홀을 갖는 제1층간절연막;

상기 콘택홀을 매립하면서 콘택홀 주위의 제1층간절연막 부분 상에 형성된 제1상변환막;

상기 제1상변환막 상에 형성된 절연막;

상기 절연막 상에 형성된 상부전극;

상기 상부전극, 절연막 및 제1상변환막의 적층 패턴 측벽에 형성된 제2상변환막;

상기 제2상변환막을 포함한 적층 패턴을 덮도록 제1층간절연막 상에 형성된 제2층간절연막;

상기 제2층간절연막 상에 상부전극과 콘택하도록 형성된 비트라인;

을 포함하는 것을 특징으로 하는 상변환 기억 소자.

## 청구항 2.

제 1 항에 있어서,

상기 상부전극의 비트라인과의 콘택 영역 이외의 영역과 제2상변환막의 표면 및 제1층간절연막의 표면을 따라 형성된 캡 핑막을 더 포함하는 것을 특징으로 하는 상변환 기억 소자.

## 청구항 3.

제 2 항에 있어서,

상기 캡핑막은 질화막으로 이루어진 것을 특징으로 하는 상변환 기억 소자.

## 청구항 4.

하부전극이 형성된 반도체기판을 마련하는 단계;

상기 기판 상에 하부전극을 덮도록 제1층간절연막을 형성하는 단계;

상기 제1층간절연막을 식각하여 하부전극의 일부를 노출시키는 콘택홀을 형성하는 단계;

상기 콘택홀을 매립하도록 제1층간절연막 상에 제1상변환물질막을 형성하는 단계;

상기 제1상변환물질막 상에 절연막과 도전막을 차례로 형성하는 단계;

상기 도전막, 절연막 및 제1상변환물질막을 식각하여 하부전극과 콘택하는 제1상변환막, 절연막 및 상부전극의 적층 패턴을 형성하는 단계;

상기 제1상변환막, 절연막 및 상부전극의 적층 패턴 측벽에 제2상변환막을 형성하는 단계;

상기 제2상변환막을 포함한 적층 패턴을 덮도록 제1층간절연막 상에 제2층간절연막을 형성하는 단계; 및

상기 제2층간절연막 상에 상부전극과 콘택하는 비트라인을 형성하는 단계;

를 포함하는 것을 특징으로 하는 상변환 기억 소자의 제조방법.

## 청구항 5.

제 4 항에 있어서,

상기 제2상변환막을 형성하는 단계 후, 그리고, 상기 제2층간절연막을 형성하는 단계 전, 상기 상부전극과 제2상변환막의 표면 및 제1층간절연막의 표면을 따라 캡핑막을 형성하는 단계를 더 포함하는 것을 특징으로 하는 상변환 기억 소자의 제조방법.

## 청구항 6.

제 5 항에 있어서,

상기 캡핑막은 질화막으로 형성하는 것을 특징으로 하는 상변환 기억 소자의 제조방법.

#### 명세서

### 발명의 상세한 설명

#### 발명의 목적

## 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 상변환 기억 소자에 관한 것으로, 보다 상세하게는, 낮은 프로그래밍 전류를 갖는 상변환 기억 소자에 관한 것이다.

기억 소자는 전원이 차단되면 입력된 정보를 잃어버리는 휘발성의 램(Random Access Memory : RAM) 소자와 전원이 차단되더라도 입력된 정보의 저장 상태를 계속해서 유지하는 롬(Read Only Memory : ROM) 소자로 크게 구분된다. 상기 휘발성의 램 소자로는 디램(DRAM) 및 에스램(SRAM)을 들 수 있으며, 상기 비휘발성의 롬 소자로는 EEPROM (Elecrtically Erasable and Programmable ROM)과 같은 플래쉬 기억(Flash Memory) 소자를 들 수 있다.

그런데, 상기 디램은 잘 알려진 바와 같이 매우 우수한 기억 소자임에도 불구하고 높은 전하저장 능력이 요구되고, 이를 위해, 전극 표면적을 증가시켜야만 하므로 고집적화에 어려움이 있다. 또한, 상기 플래쉬 기억 소자는 두 개의 게이트가 적층된 구조를 갖는 것과 관련해서 전원전압에 비해 높은 동작전압이 요구되고, 이에 따라, 쓰기 및 소거 동작에 필요한 전압을 형성하기 위해 별도의 승압 회로를 필요로 하므로 고집적화에 어려움이 있다.

이에, 상기 비휘발성 기억 소자의 특성을 가지면서 고집적화를 이룰 수 있고, 또한, 구조가 단순한 새로운 기억 소자를 개발하기 위한 많은 연구들이 진행되고 있으며, 그 한 예로 최근 상변환 기억 소자(Phase Change RAM)가 제안되었다.

상변환 기억 소자는 하부전극과 상부전극 사이의 전류 흐름을 통해서 상기 전극들 사이에 개재된 상변환막이 결정 상태에서 비정질 상태로 상변화가 일어나는 것으로부터 결정질과 비정질에 따른 저항 차이를 이용하여 셀에 저장된 정보를 판별하는 기억 소자이다. 다시말해, 상변환 기억 소자는 상변환막으로 칼코제나이드(Chalcogenide)막을 이용하는데, 이러한 칼코제나이드막은 게르마늄(Ge), 스티비움(Sb) 및 텔루리움(Te)으로 이루어진 화합물막으로서, 인가된 전류에 의해 발생하는 열, 즉, 주울 열(Joule Heat)에 의해 비정질(Amorphouse) 상태와 결정질(Crystalline) 상태 사이에서 상변화가 일어나며, 이때, 비정질 상태를 갖는 상변환막의 비저항이 결정질 상태를 갖는 상변환막의 비저항 보다 높다는 것으로부터, 읽기 모드에서 상변환막을 통하여 흐르는 전류를 감지하여 상변환 기억 셀에 저장된 정보가 논리 '1'인지 또는 논리 '0'인지를 판별하게 된다.

한편, 이러한 상변환 기억 소자에서 상변환막이 결정질 상태에서 비정질 상태로 되는 것을 리세트(reset)라고 하고, 반대로 비정질 상태에서 결정질 상태로 되는 것을 세트(set)라고 하는데, 소비 전력 및 동작 속도 측면에서 상기 리세트/세트 (프로그래밍)를 위한 전류의 크기는 낮을수록 좋다. 따라서, 상변환막과 전극과의 접촉 면적을 가능한 작게 만들어줌으로 써, 두 물질간의 접촉면에서의 전류 밀도를 높여 상변화에 필요한 전류를 낮추어야 한다.

이에, 종래에는 하부전극과 상변환막 간의 접촉 면적을 줄여주기 위해 하부전극 또는 상변환막을 플러그형으로 형성하고 있다.

이하에서는, 도 1a 및 도 1b를 참조하여 종래의 상변환 기억 소자를 설명하도록 한다.

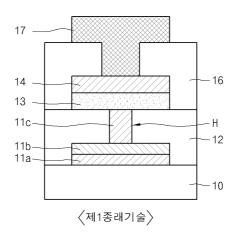

도 1a를 참조하면, 종래의 상변환 기억 소자는, 소정의 하부구조물(미도시)을 구비한 반도체기판(10) 상에 제1하부전극(11a) 및 제2하부전극(11b)의 적층 패턴이 형성되고, 상기 적층 패턴을 덮도록 기판(10) 상에 제1층간절연막(12)이 형성되며, 상기 제1층간절연막(12)에 형성된 콘택홀(H) 내에 제2하부전극(11b)과 콘택하는 플러그형 제3하부전극(11b)이 형성된 구조를 갖는다. 그리고, 상기 제1층간절연막(12) 상에 제3하부전극(11b)과 콘택하는 패턴 형태의 상변환막(13)과 상부전극(15)이 차례로 구비된다. 미설명된 도면부호 16은 상기 상변환막(13)과 상부전극(15)을 덮도록 제1층간절연막(12) 상에 형성된 제2층간절연막을 나타내고, 도면부호 17은 상기 제2층간절연막(16) 상에 상부전극(15)과 콘택하도록 형성된비트라인을 나타낸다.

여기서, 상기 제2하부전극(11b)과 제3하부전극(11c)은 동일한 재질로 형성되고, 제1하부전극(11a)으로부터 발생되는 열을 상변환막(13)에 전달하는 역할을 한다.

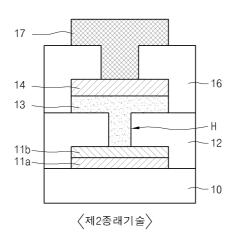

한편, 도 1b에 도시된 종래의 다른 상변환 기억 소자는, 상기 도 1a와 기본적으로 동일한 구조를 갖지만 제1층간절연막 (12)에 형성된 콘택홀(H) 내에 제3하부전극이 형성되는 대신에 상변환물질이 매립된 구조를 갖는다. 즉, 도 1b에서는 상변환막(13)이 도 1a에서와 같이 제1층간절연막(12) 상에 패턴 형태로 형성될 뿐만 아니라 플러그 형태를 갖고 제2하부전 극(11b)과 콘택하고 있다.

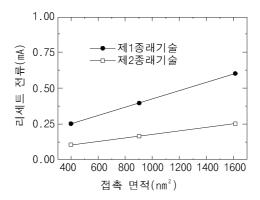

이와 같이, 상변환막 또는 하부전극을 플러그형으로 형성하면, 그들 간의 접촉 면적을 감소시킬 수 있어서 프로그래밍 전류를 낮출 수 있다. 특히, 도 1b와 같은 구조가 도 1a와 같은 구조 보다 프로그래밍 전류를 낮추는데 효과가 있는데, 이것은 도 2로부터 확인할 수 있다. 도 2는 상기 두 가지 종래의 상변환 기억 소자의 상변환막과 하부전극과의 접촉 면적에 따른 리세트 전류의 변화를 나타내는 그래프이다.

#### 발명이 이루고자 하는 기술적 과제

그러나, 전술한 종래의 상변환 기억 소자에서는 하부전극(11a, 11b, 11c), 상변환막(13), 상부전극(15) 및 비트라인(17)이 동일축 상에 형성되기 때문에, 비트라인(17)과 상부전극(15)의 콘택 마진을 고려하여 상변환막(13)과 상부전극(15)의 크기를 소정 크기 이상 확보해주어야 한다. 여기서, 상기 상변환막(13)과 상부전극(15)은 동일한 폭으로 형성되는데, 이는 상변환막(13)과 상부전극(15)을 동시에 패터닝해야 하기 때문이다. 만약, 상부전극용 도전막의 형성 없이 상변환물질막 만을 단독으로 패터닝하는 경우 상변환물질막이 손상(damage)되어 그 특성이 열화된다.

그러므로, 종래의 상변환 기억 소자에서는 상변환막(13)과 상부전극(15) 간의 접촉 면적을 줄이기 어렵고, 프로그래밍 전류를 낮추는데 한계가 있다. 즉, 상변환막(13)과 상부전극(15) 간의 접촉 면적이 상변환막(13)과 하부전극 간의 접촉 면적에 비해 상대적으로 매우 넓기 때문에 프로그래밍에 필요한 전류가 여전히 높다는 문제가 있다.

따라서, 본 발명은 상기와 같은 종래의 문제점을 해결하기 위해 안출된 것으로서, 하부전극과 상변환막 간의 접촉 면적 뿐만 아니라 상부전극과 상변환막 간의 접촉 면적 또한 감소시켜 프로그래밍 전류를 낮춰줄 수 있는 상변환 기억 소자를 제공함에 그 목적이 있다.

#### 발명의 구성

상기와 같은 목적을 달성하기 위하여, 본 발명은, 하부전극이 형성된 반도체기판; 상기 기판 상에 형성되고 하부전극의 일부를 노출시키는 콘택홀을 갖는 제1층간절연막; 상기 콘택홀을 매립하면서 콘택홀 주위의 제1층간절연막 부분 상에 형성된 제1상변환막; 상기 제1상변환막 상에 형성된 절연막; 상기 절연막 상에 형성된 상부전극; 상기 상부전극, 절연막 및 제1

상변환막의 적층 패턴 측벽에 형성된 제2상변환막; 상기 제2상변환막을 포함한 적층 패턴을 덮도록 제1층간절연막 상에 형성된 제2층간절연막; 상기 제2층간절연막 상에 상부전극과 콘택하도록 형성된 비트라인;을 포함하는 상변환 기억 소자 를 제공한다.

여기서, 상기 상부전극의 비트라인과의 콘택 영역 이외의 영역과 제2상변환막의 표면 및 제1층간절연막의 표면을 따라 형성된 캡핑막을 더 포함할 수 있다.

이때, 상기 캡핑막은 질화막으로 형성된다.

한편, 상기와 같은 목적을 달성하기 위한 본 발명의 상변환 기억 소자의 제조방법은, 하부전극이 형성된 반도체기판을 마련하는 단계; 상기 기판 상에 하부전극을 덮도록 제1충간절연막을 형성하는 단계; 상기 제1충간절연막을 식각하여 하부전 극의 일부를 노출시키는 콘택홀을 형성하는 단계; 상기 콘택홀을 매립하도록 제1충간절연막 상에 제1상변환물질막을 형성하는 단계; 상기 제1상변환물질막 상에 절연막과 도전막을 차례로 형성하는 단계; 상기 도전막, 절연막 및 제1상변환물 질막을 식각하여 하부전극과 콘택하는 제1상변환막, 절연막 및 상부전극의 적층 패턴을 형성하는 단계; 상기 제1상변환막, 절연막 및 상부전극의 적층 패턴을 형성하는 단계; 상기 제1상변환 막, 절연막 및 상부전극의 적층 패턴 측벽에 제2상변환막을 형성하는 단계; 상기 제2상변환막을 포함한 적층 패턴을 덮도록 제1충간절연막 상에 제2층간절연막을 형성하는 단계; 및 상기 제2층간절연막 상에 상부전극과 콘택하는 비트라인을 형성하는 단계;를 포함한다.

상기 본 발명의 상변환 기억 소자의 제조방법은, 상기 제2상변환막을 형성하는 단계 후, 그리고, 상기 제2층간절연막을 형성하는 단계 전, 상기 상부전극과 제2상변환막의 표면 및 제1층간절연막의 표면을 따라 캡핑막을 형성하는 단계를 더 포함할 수 있다.

이때, 상기 캡핑막은 질화막으로 형성한다.

(실시예)

이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시예를 상세하게 설명하도록 한다.

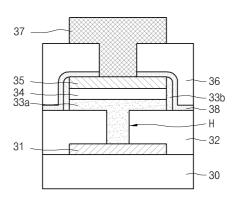

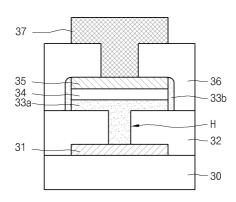

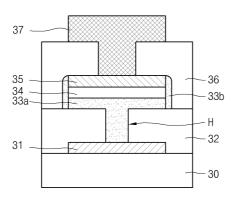

도 3는 본 발명의 일 실시예에 따른 상변환 기억 소자를 도시한 단면도로서 이를 참조하면, 본 발명의 상변환 기억 소자는 패턴 형태의 하부전극(31)이 형성된 반도체기판(30)과, 상기 기판(30) 상에 형성되고 하부전극(31)의 일부를 노출시키는 콘택홀(H)을 갖는 제1층간절연막(32)과, 상기 콘택홀(H)을 매립하면서 콘택홀(H) 주위의 제1층간절연막(32) 부분 상에 형성된 제1상변환막(33a)과, 상기 제1상변환막(33a) 상에 형성된 절연막(34)과, 상기 절연막(34) 상에 형성된 상부전극(35)과, 상기 상부전극(35), 절연막(34) 및 제1상변환막(33a)의 적층 패턴 측벽에 형성된 제2상변환막(33b)과, 상기 제2 상변환막(33b)을 포함한 적층 패턴을 덮도록 제1층간절연막(32) 상에 형성된 제2층간절연막(36)과, 상기 제2층간절연막(36) 상에 상부전극(35)과 콘택하도록 형성된 비트라인(37)을 포함한다.

도 4a 내지 도 4d는 상기 도 3과 같은 구조를 갖는 본 발명의 일 실시예에 따른 상변환 기억 소자의 제조방법을 설명하기 위한 공정별 단면도이다.

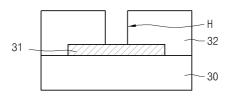

도 4a를 참조하면, 소정의 하부구조물(미도시) 및 패턴 형태의 하부전극(31)이 형성된 반도체기판(30)을 마련한 후, 상기기판(30) 상에 하부전극(31)을 덮도록 제1층간절연막(32)을 형성하고, 상기 제1층간절연막(32)을 식각하여 하부전극(31)의 일부를 노출시키는 콘택홀(H)을 형성한다.

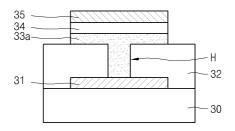

도 4b를 참조하면, 상기 콘택홀(H)을 매립하도록 제1층간절연막(32) 상에 제1상변환물질막을 형성하고, 이어서, 상기 제 1상변환물질막 상에 절연막과 도전막을 차례로 형성한 다음, 상기 도전막, 절연막 및 제1상변환물질막을 식각하여 하부전 극(31)과 콘택하는 제1상변환막(33a), 절연막(34) 및 상부전극(35)의 적층 패턴을 형성한다.

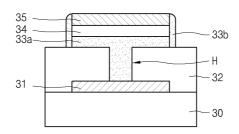

도 4c를 참조하면, 상기 제1상변환막(33a), 절연막(34) 및 상부전극(35)의 적층 패턴 및 제1층간절연막(32) 상에 일정한 두께의 제2상변환물질막을 형성한 후, 상기 제2상변환물질막을 이방성 식각하여 제1상변환막(33a), 절연막(34) 및 상부전극(35)의 적층 패턴 측벽에 제2상변환막(33b)을 형성한다.

도 4d를 참조하면, 상기 제2상변환막(33b)을 포함한 적층 패턴을 덮도록 제1층간절연막(32) 상에 제2층간절연막(36)을 형성한 후, 상기 제2층간절연막(36) 상에 상부전극(35)과 콘택하는 비트라인(37)을 형성한다.

이와 같이, 본 발명은 제1상변환막(33a)이 플러그 모양을 갖고 하부전극(31)과 콘택되도록 하고, 아울러, 절연막(34)에 의해 전기적으로 분리된 제1상변환막(33a)과 상부전극(35)의 측벽들이 제2상변환막(33b)에 의해 콘택되도록 한다. 이 경우, 하부전극과 상변환막 간의 접촉 면적을 감소시킬 수 뿐만 아니라, 상부전극과 상변환막 간의 접촉 면적 또한 감소시킬수 있어서 상변환에 필요한 프로그래밍 전류를 용이하게 낮춰줄수 있다. 이때, 상부전극(35)의 크기는 종래와 동일한수준으로 유지되기 때문에 상부전극(35)과 비트라인(37) 간의 콘택 마진은 전혀 감소하지 않는다.

한편, 본 발명의 다른 실시예에서는, 상기 제2상변환막(33b)을 형성하는 단계 후, 그리고, 상기 제2층간절연막(36)을 형성하는 단계 전, 상기 상부전극(35)과 제2상변환막(33b)의 표면 및 제1층간절연막(32)의 표면을 따라 질화막 재질의 캡핑막 형성하는 단계를 더 포함할 수도 있다.

이러한 본 발명의 다른 실시예에 따른 상변환 기억 소자는, 도 5에 도시된 바와 같이, 상기 상부전극(35)의 비트라인(37)과의 콘택 영역 이외의 영역과 제2상변환막(33b)의 표면 및 제1층간절연막(32)의 표면을 따라 형성된 질화막 재질의 캡핑막(38)을 포함한다. 상기 캡핑막(38)은 제2상변환막(33b)으로 산소 등이 침투하는 것을 방지하는 역할을 한다.

이상, 여기에서는 본 발명을 몇 가지 예를 들어 설명하였으나, 본 발명은 이에 한정되는 것은 아니며, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자라면 본 발명이 그의 본질적인 사상에서 벗어나지 않는 범위에서 변형된 형태로 구현될수 있음을 이해할 수 있을 것이다.

#### 발명의 효과

이상에서와 같이, 본 발명은 상변환 기억 소자를 제조함에 있어서, 제1상변환막이 플러그 형태를 갖고 하부전극과 콘택되도록 하고, 제2상변환막이 상부전극의 측벽과 콘택되도록 함으로써, 상변환막과 상하부전극들 간의 접촉 면적을 동시에 감소시킬 수 있어서, 프로그래밍 전류를 낮출 수 있다.

## 도면의 간단한 설명

도 1a 및 도 1b는 종래의 상변환 기억 소자들을 도시한 단면도.

도 2는 종래 상변환 기억 소자들의 상변환막과 하부전극의 접촉 면적 변화에 따른 리세트 전류 변화를 나타내는 그래프.

도 3은 본 발명의 일 실시예에 따른 상변환 기억 소자의 단면도.

도 4a 내지 도 4d는 본 발명의 일 실시예에 따른 상변환 기억 소자의 제조방법을 설명하기 위한 공정별 단면도.

도 5는 본 발명의 다른 실시예에 따른 상변환 기억 소자의 단면도.

\* 도면의 주요 부분에 대한 부호의 설명 \*

30 : 반도체기판 31 : 하부전극

32: 제1층간절연막 H: 콘택홀

33a: 제1상변환막 33b: 제2상변환막

34 : 절연막 35 : 상부전극

36: 제2층간절연막 37: 비트라인

도면

도면1a

도면1b

도면2

## 도면3

도면4a

도면4b

도면4c

## 도면4d

도면5