### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2010-56457 (P2010-56457A)

(43) 公開日 平成22年3月11日(2010.3.11)

(51) Int.Cl.

$\mathbf{F}$  L

テーマコード (参考)

HO1L 33/32

(2010, 01)

HO1L 33/00

С

5F041

審査請求 未請求 請求項の数 3 OL (全8頁)

(21) 出願番号

特願2008-222507 (P2008-222507)

(22) 出願日

平成20年8月29日 (2008.8.29)

(71) 出願人 000006633

京セラ株式会社

京都府京都市伏見区竹田鳥羽殿町6番地

(72) 発明者 正木 克明

京都府相楽郡精華町光台3丁目5番地3号

京セラ株式会社中央研究所内

(72)発明者 西薗 和博

京都府相楽郡精華町光台3丁目5番地3号

京セラ株式会社中央研究所内

(72)発明者 安田 隆則

京都府相楽郡精華町光台3丁目5番地3号

京セラ株式会社中央研究所内

F ターム (参考) 5F041 AA42 CA05 CA40 CA46 CB25

FF11

### (54) 【発明の名称】発光素子アレイの製造方法

### (57)【要約】

【課題】 作製工程を短縮化した発光素子アレイの製造方法を提供する。

【解決手段】 本発明の発光素子アレイの製造方法は、(1)成長用基板上部に第1導電型の半導体層、発光層及び第2導電型の半導体層で構成される光半導体層を含むIII族窒化物半導体層を形成する工程と、(2)前記III族窒化物半導体層の一方主面の一部を除去し一方主面と型の異なるIII族窒化物半導体層を露出させ、前記第1導電型および前記第2導電型の半導体層にそれぞれ電極を形成する工程と、(3)前記半導体層の一方主面に形成した前記電極を、支持基板の主面のうち該電極に対向する位置に形成した電極に接合した後に、成長用基板を除去する工程と、を具備する

【選択図】 図1

### 【特許請求の範囲】

### 【請求項1】

- (1)成長用基板上に、第1導電型の半導体層と、発光層と、第2導電型の半導体層と、から構成される光半導体層を複数形成する工程と、

- (2)前記複数の光半導体層の各々において、一部を除去し、前記第1導電型の半導体層および前記第2導電型の半導体層を露出させ、それぞれ第1および第2の電極を形成する 工程と、

- (3)複数の前記光半導体層に形成した前記第1および第2の電極を、これらの電極に対して対向する位置に設けられた支持基板上の電極にそれぞれ接合して、前記成長用基板を 前記支持基板に実装する工程と、

- (4)前記成長用基板を除去する工程と、

を具備する発光素子アレイの製造方法。

### 【請求項2】

前記工程(1)は、

- (1-1)前記成長用基板上に、前記光半導体層のエピタキシャル成長に対して不活性な材料から成る物質により成長抑制マスクパターンを形成して、相互に分離された前記成長用基板上に露出部を複数形成する工程と、

- (1-2)前記成長用基板上の複数の露出部に、エピタキシャル成長によって前記光半導体層を形成する工程と、

- (1-3)前記成長抑制マスクパターンを除去する工程と、

を含む請求項1記載の発光素子アレイの製造方法。

#### 【請求項3】

前記成長用基板と前記光半導体層が異種材料である場合、前記工程(4)において、レーザーリフトオフにより前記成長用基板を除去する請求項1または2記載の発光素子アレイの製造方法。

【発明の詳細な説明】

### 【技術分野】

# [0001]

本発明は、複数の発光素子から構成される発光素子アレイの製造方法に関する。

#### 【背景技術】

### [ 0 0 0 2 ]

近年、光半導体から構成される発光素子が開発されており、照明装置などの用途に用いられている。このような発光素子としては、例えば、青色発光素子、紫外光発光素子などのIII族 V族系化合物半導体が挙げられる。

### [0003]

発光素子の開発とともに、発光素子の製造方法についても種々の方法が開発されており、例えば、成長用基板に発光素子を成長させたのち、発光素子を成長用基板から剥がして発光素子を作製する製造方法が開示されている(特許文献1参照)。

【特許文献1】特開2007-19511号公報

### 【発明の開示】

【発明が解決しようとする課題】

### [0004]

発光素子は、照明装置等に用いられる場合、高輝度を得る為にアレイ化が必要であり、 近年、発光素子のアレイ化工程の簡易化が要求されている。

### [0005]

なお、特許文献 1 に記載された技術は、あくまで発光素子をアレイ化したものではなかった。そのため、アレイ化するためには、作製した発光素子を一つ一つ回路基板上に並べる工程が別途必要であったため、十分に作製工程が短縮化されたものではなかった。

### [0006]

本発明の目的は、簡易な工程により発光素子のアレイ化をおこなう発光素子アレイの製

10

20

30

40

造方法を提供することである。

【課題を解決するための手段】

### [0007]

本発明は、(1)成長用基板上に、第1導電型の半導体層と、発光層と、第2導電型の半導体層と、から構成される光半導体層を複数形成する工程と、(2)前記複数の光半導体層の各々において、一部を除去し、前記第1導電型の半導体層および前記第2導電型の半導体層を露出させ、それぞれ第1および第2の電極を形成する工程と、(3)複数の前記光半導体層に形成した前記第1および第2の電極を、これらの電極に対して対向する位置に設けられた支持基板上の電極にそれぞれ接合して、前記成長用基板を前記支持基板に実装する工程と、(4)前記成長用基板を除去する工程と、を具備する発光素子アレイの製造方法に関する。

[00008]

前記工程(1)は、(1-1)前記成長用基板上に、前記光半導体層のエピタキシャル成長に対して不活性な材料から成る物質により成長抑制マスクパターンを形成して、相互に分離された前記成長用基板上に露出部を複数形成する工程と、(1-2)前記成長用基板上の複数の露出部に、エピタキシャル成長によって前記光半導体層を形成する工程と、(1-3)前記成長抑制マスクパターンを除去する工程と、を含むことが好ましい。

[0009]

前記成長用基板と前記光半導体層が異種材料である場合、前記工程(4)において、レーザーリフトオフにより前記成長用基板を除去することが好ましい。

【発明の効果】

[0010]

本発明の発光素子アレイの製造方法は、(1)成長用基板上に、光半導体層を複数形成する工程と、(2)複数の光半導体層の各々において、それぞれ第1および第2の電極を形成する工程と、(3)複数の光半導体層に形成した前記第1および第2の電極を、これらの電極に対して対向する位置に設けられた支持基板上の電極にそれぞれ接合して、前記成長用基板を前記支持基板に実装する工程と、(4)前記成長用基板を除去する工程と、を具備する。これにより、一つずつ発光素子を支持基板上に配列することなく、複数の光素子を支持基板上に配列することなく、複数の光素子を一度にアレイ化することができる。また、本製造方法において、1枚の成長用基板および1枚の支持基板に対して、複数の光半導体層が用いられるため、成長用基板との時の熱膨張係数差が大きい場合でも、光半導体層と成長用基板および支持基板との間の熱膨張係数が異なる成長用基板および支持基板を使用することができる。そのため、熱膨張係数が異なる成長用基板および支持基板を使用することができる

[0011]

本発明の発光素子アレイの製造方法において、工程(1)が、(1-1)前記成長用基板上に、前記光半導体層のエピタキシャル成長に対して不活性な材料から成る物質により成長抑制マスクパターンを形成して、相互に分離された前記成長用基板上に露出部を複数形成する工程と、(1-2)前記成長用基板上の複数の露出部に、エピタキシャル成長によって前記光半導体層を形成する工程と、(1-3)前記成長抑制マスクパターンを除去する工程と、を含むことが好ましい。これにより、複数の光半導体層をまとめて形成することができる。さらに、成長抑制マスクパターンをフォトリソグラフィプロセスにより微細加工でき、成長抑制マスクパターンによりパターン化された複数の光半導体層を支持基板上に同じ配置で転写できる為、素子間隔が精密に制御された複数の光半導体層をまとめて形成することができる。

[0012]

本発明の発光素子アレイの製造方法において好ましくは、前記成長用基板と前記光半導体層が異種材料である場合、前記工程(4)において、レーザーリフトオフにより前記成長用基板を除去することが好ましい。これにより、支持基板上に接合された光半導体層のみを選択的に成長用基板から容易に除去することが可能となる。

10

20

30

40

#### 【発明を実施するための最良の形態】

[0013]

以下、図面を参照しながら本発明の発光素子アレイの製造方法を詳細に説明する。

[0014]

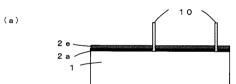

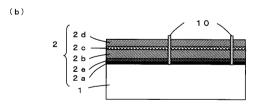

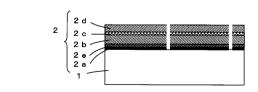

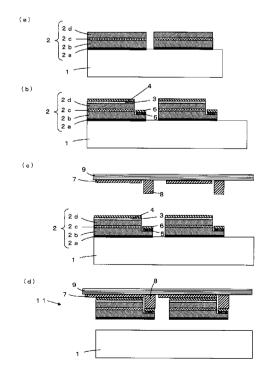

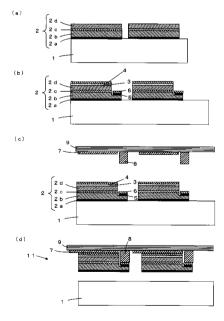

図1は、本発明の発光素子アレイの第1の実施の形態の示す断面図である。図1において、1は成長用基板、2は半導体層、2aはバッファ層、2bは第1導電型(n型)の半導体層、2cは発光層、2dは第2導電型(p型)の半導体層、3は第2導電側の導電層、4は第2導電側(p側)のパッド電極(第2の電極)、5は第1導電側(n側)の導電層、6は第1導電側(n側)のパッド電極(第1の電極)、7は第2導電側(p側)のパターン電極、8は第1導電側(n側)のパターン電極、9は支持基板をそれぞれ示す。

[0015]

本発明の発光素子アレイの製造方法は、(1)成長用基板1上に光半導体層2を複数形成する工程と、(2)複数の光半導体層2に電極を形成する工程と、(3)光半導体層2の一方主面に形成した電極を、支持基板の主面の電極に接合した後に、成長用基板を除去する工程と、を具備する。

[0016]

以下にそれぞれの工程について説明する。

[0017]

(工程1)

工程 1 では、図 1 (a)に示すように、成長用基板 1 上に複数の光半導体層 2 を形成する。

[0018]

成長用基板1は、光半導体層2を成長させることが可能な基板であればよい。具体的に、基板1としては、サファイア(Al<sub>2</sub>О<sub>3</sub>)、窒化ガリウム(GaN)、窒化アルミニウム(AlN)、酸化亜鉛(ZnO),シリコンカーバイド(SiC)等が挙げられる。成長用基板1の厚みとしては、100μm~1000μm程度である。

[0019]

光半導体層 2 としては、例えば、窒化ガリウム(GaN)、窒化アルミニウム(A1N)、窒化アルミニウムガリウム(A1GaN)、窒化インジウム(InN)などのIII-V族化合物半導体、ZnOなどのII-VI族化合物半導体などが挙げられる。ここで、III族とは、元素周期律表におけるIII族(13族)を意味する。

[0020]

図1(a)の場合、光半導体層2は、バッファ層2a、第1導電型の半導体層2b、発光層及2cおよび第2導電型の半導体層2dで構成される。

[0021]

バッファ層2aは、成長用基板1と光半導体層2との間の応力を緩和させるために好適に形成される。窒化物バッファ層2aは、例えば、窒化ガリウム、窒化アルミニウムなどの材料から構成される。窒化物バッファ層2aの厚みは0.01~0.2μm程度である

[0022]

第1導電型の半導体層2bとしては、n型の半導体層が挙げられる。例えば、III族窒化物半導体層をn型とするには、元素周期律表においてIV族の元素であるSi等をドーパントとして窒化物半導体層に混入させればよい。第1導電型の半導体層2bの厚みは2~3μm程度である。

[ 0 0 2 3 ]

第2導電型の半導体層2dとしては、p型の窒化物半導体が挙げられる。例えば、III 族窒化物半導体層をp型とするには、元素周期律表においてII族の元素であるMg等をドーパントとして窒化物半導体層に混入させればよい。第2導電型の半導体層2dの厚みは200~500nm程度である。

[0024]

10

20

30

40

### [0025]

成長用基板 1 上における光半導体層 2 の成長方法としては、分子線エピタキシー(MBE; Molecular Beam Epitaxy)法、有機金属エピタキシー(MOVPE; Metal Organic Vapor Phase Epitaxy)法、ハイドライド気相成長(HVPE; Hydride Vapor Phase Epitaxy)、パルスレーザデポジション(PLD; Pulsed Laser deposition)法等が用いられる。

#### [0026]

工程1において、光半導体2を複数形成する方法としては、成長用基板の一面に成長させた光半導体層2を分割する方法、III族窒化物半導体のエピタキシャル成長に対して不活性の材料から成る物質によりマスクを形成し、成長用基板1の領域を先に分割させ、その後に光半導体層2を成長させる方法などが挙げられる。成長させた光半導体層2を分割する方法としては、例えば、ダイシング法、分割する領域以外にエッチングマスクを形成した後にドライエッチングを行う方法などが挙げられる。

#### [0027]

また、光半導体層 2 を成長させる成長用基板 1 の領域を先に分割させ、その後に光半導体層 2 を成長させる方法の具体例は、以下の図 2 に示す。

#### [0028]

まず、成長用基板1上に成長抑制マスクパターンを形成する(図2(a))。その際、バッファ層2a上にテンプレート層2eを成長させたのち、マスクを形成する領域だけエッチング等によりバッファ層2aおよびテンプレート層2eを除去しておく。ここで、テンプレート層2eとは、成長抑制マスク10上には成長させないように、半導体層2bを選択的に成長させるために用いられるものである。テンプレート層2eは第1導電型の半導体層2bと同じ材料であり、厚みは1~5μm程度である。

# [0029]

成長抑制マスク10は、III族窒化物半導体のエピタキシャル成長に対して不活性の材料から成る物質により形成される。ここで、成長抑制マスク10に使用される材料としては、具体的にはSiO₂,多結晶シリコンなどが挙げられる。これらはIII族窒化物半導体のエピタキシャル成長に対して不活性である。

### [0030]

成長抑制マスク10は、具体的に、蒸着、CVD等によりマスク材料を一面に成膜した後、フォトリソグラフィおよびエッチングをすることにより形成される。

#### [0031]

成長抑制マスク10を形成した後に、テンプレート層2e上に成長抑制マスク10によって分離された、第1導電型の半導体層2bと、発光層2cと、第2導電型の半導体層2dと、を、エピタキシャル成長によって形成する(図2(b)参照)。

# [0032]

そして、それらを形成したのちに、成長抑制マスク10を除去させる(図2(c))。 具体的に、マスク材料がSiO₂の場合はフッ酸、多結晶シリコンの場合は硝酸及びフッ酸による混酸によるウェットエッチングをすることにより成長抑制マスク10を除去する

### [0033]

(工程2)

10

20

30

工程2では、図1(b)に示すように、III族窒化物半導体層2の一方主面の一部を除去し一方主面と型の異なるIII族窒化物半導体層2を露出させ、第1導電型および第2導電型の半導体層2にそれぞれ電極を形成する。

[0034]

工程 2 は、複数の光半導体層 2 の各々において、一部を除去し、第 1 導電型の半導体層 2 b および第 2 導電型の半導体層 2 d を露出させ、それぞれ第 1 導電側(n 側)のパッド電極(第 1 の電極) 6 および第 2 導電側(p 側)のパッド電極(第 2 の電極) 4 を形成する工程である。

[0035]

光半導体層2の一方主面の一部を除去して光半導体層2の第1導電型の半導体層2bを露出させるために、具体的に、RIE装置等を用いて1<sub>2</sub>ガスとBC1<sub>3</sub>の混合ガスを用い、所定の時間、ドライエッチングを行う。これにより、第2導電型の半導体層2dとは型の異なる第1導電型の半導体層2bを露出させることができる。

[0036]

図2(c)の場合、第1導電型の半導体層2b上に第1導電側の導電層5を形成し、第1導電側の導電層5上に第1の電極として第1導電側のパッド電極6を形成した。また、同様に、第2導電型の半導体層2d上に第2導電側の導電層3を形成し、第2導電側の導電層3上に第2の電極として第2導電側のパッド電極4を形成した。

[0037]

第 1 導電側の導電層 5 と第 2 導電側の導電層 3 は真空蒸着法、スパッタリング法などの方法により形成される。

[0038]

第1導電側の導電層5と第2導電側の導電層3の材質は、発光層2cから発生した光を損失なく反射し、かつ第1導電型の半導体層2bおよび第2導電型の半導体層2dと良好なオーミック接続をとるために好適に設けられる。例えば、アルミニウム(A1),チタン(Ti),ニッケル(Ni),クロム(Cr),インジウム(In),錫(Sn),モリブデン(Mo),銀(Ag),金(Au),ニオブ(Nb),タンタル(Ta),バナジウム(V),白金(Pt),鉛(Pb),ベリリウム(Be),酸化錫(SnO₂),酸化インジウム(In₂О₃),酸化インジウム錫(ITO),金・シリコン(Au・Si)合金,金・ゲルマニウム(Au・Ge)合金,金・亜鉛(Au・Zn)合金,金・ベリリウム(Au・Be)合金等の薄膜を好適に用いることができる。

[0039]

第1 導電側のパッド電極 6 および第 2 導電側のパッド電極 4 は、それぞれ後工程で支持基板 9 の第 1 の電極 6 および第 2 の電極 4 と接合し、それらと電気的接続をとるために設けられている。第1 導電側のパッド電極 6 および第 2 導電側のパッド電極 4 は、第1 導電側のパターン電極 8 および第 2 導電側のパターン電極 7 と接合できるように、例えば、チタン、またはチタンを下地層として金層を積層したものを用いる。

[0040]

第1導電側のパッド電極6および第2導電側のパッド電極4は真空蒸着法、スパッタリング法などの方法により形成される

(工程3)

工程3では、複数の光半導体層2に形成した第1導電側のパッド電極6および第2導電側のパッド電極4を、これらの電極に対して対向する位置に設けられた支持基板9上の電極7および8(p側パターン電極7およびn側パターン電極8)にそれぞれ接合して、成長用基板1を支持基板9に実装する工程である(図1(c)参照)。

[0041]

工程3の後に、成長用基板1を除去する工程のみで、発光素子アレイとして機能できるように、支持基板9上には、第1導電側のパターン電極8および第2導電側のパターン電極7と配線パターンとが予め設けられている。

[0042]

50

10

20

30

第1導電側のパターン電極8および第2導電側のパターン電極7は、第1導電側のパッド電極6および第2導電側のパッド電極4と接合することができ、かつ、電気的接続をとるものが用いられる。具体的には、An-Sn合金、Pb-Sn合金などの材料が用いられる。

[0043]

第1導電側のパターン電極8および第2導電側のパターン電極7は、メッキ法、スパッタリング法、真空蒸着法などの方法により作製される。また、それらの層の厚みは約1~ 100μmである。

[0044]

また、回路パターンは、一面に形成された銅箔などの金属膜上にフォトリソグラフィプロセスによりレジストパターンを形成し、エッチングを行い、レジストパターン除去を行うなどの方法により作製される。

[0045]

支持基板 9 は、アルミナ(A  $1_2$  O  $_3$ )、窒化アルミニウム(A 1 N)等から形成される。支持基板 9 の厚みは 0 . 5 ~ 3 m m 程度であり、この範囲内にあれば発光素子からの発熱による熱およびハンドリング時の応力に対して十分な強度を持ち、かつ高い放熱特性を有する。

[0046]

工程3において、第1導電側のパッド電極6および第2導電側のパッド電極4と、第1 導電側のパターン電極8および第2導電側のパターン電極7とをそれぞれ接合する。接合は、具体的に、支持基板9、成長用基板1等を150~400 に加熱することで行われる。

[0047]

工程3により、支持基板9に対して、複数の光発光素子2の実装を一度におこなうことができ、さらに、位置合わせも必要なくなるため、工程を非常に簡略化出来る。

[0048]

また、工程3において1枚の成長用基板および1枚の支持基板に対して、複数の光半導体層が用いられる。そのため、成長用基板と支持基板との間の熱膨張係数差が大きい場合でも、光半導体層と成長用基板および支持基板との接触面積は小さくなり、熱膨張率係数の差により発生する歪みを分散させて減少させることができる。そのため、熱膨張係数が異なる成長用基板および支持基板を使用することができる。

[0049]

(工程4)

工程4において、成長用基板1を除去する。除去方法としては、レーザーリフトオフ(成長用基板1と光半導体層2とが異種材料の場合)、基板の研磨などが挙げられる。なかでもレーザー照射により簡易に成長用基板1を除去できるため、レーザーリフトオフが除去方法として好ましい。また、工程3において、加熱された際に、そのサイクルの中でレーザーリフトオフを行うようにしてもよい。この場合、成長用基板1が先に除去された状態で支持基板9が冷却されるので、熱応力の蓄積を防止することができる。

[0050]

以上の工程1~4を行うことにより、発光素子アレイ11を製造することができる。

[0051]

なお、本発明は上記の実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲内で種々の変更を施すことは何等差し支えない。

【図面の簡単な説明】

- [0052]

- 【図1】本発明の発光素子アレイの製造方法の一つの実施の形態を示す断面図である。

- 【図2】本発明の発光素子アレイの製造方法の工程1の一つを示す断面図である。

- 【符号の説明】

- [ 0 0 5 3 ]

30

10

20

40

1:成長用基板 2:光半導体層

2 a : バッファ層

2 b: 第1導電型(n型)の半導体層

2 c : 発光層

2 d : 第 2 導電型 ( p型 ) の半導体層

2 e: テンプレート層 3: 第2導電側の導電層

4:第2導電側のパッド電極

5:第1導電側の導電層

6:第1導電側のパッド電極7:第1導電側パターン電極8:第2導電側パターン電極

9:支持基板

1 0 : 成長抑制マスク 1 1 : 発光素子アレイ

# 【図1】

# 【図2】

(c)