# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-16832 (P2008-16832A)

最終頁に続く

(43) 公開日 平成20年1月24日 (2008.1.24)

| (51) Int.C1. |           | F 1         |             | テーマコート    | : (参考) |

|--------------|-----------|-------------|-------------|-----------|--------|

| HO1L 29/786  | (2006.01) | HO1L 29/78  | 618C        | 4M1O4     |        |

| HO1L 21/28   | (2006.01) | HO1L 29/78  | 616T        | 5 F 1 1 O |        |

| HO1L 29/417  | (2006.01) | HO1L 29/78  | 626C        |           |        |

|              |           | HO1L 29/78  | 618B        |           |        |

|              |           | HO1L 29/78  | 612B        |           |        |

|              |           | 審査請求 未請求 請求 | ▼項の数 10 O L | (全 24 頁)  | 最終頁に続く |

| (21) 出願番号<br>(22) 出願日<br>(31) 優先権主張番号 | 特願2007-149712 (P2007-149712)<br>平成19年6月5日 (2007.6.5)<br>特願2006-159463 (P2006-159463) | (71) 出願人 | 000005821<br>松下電器産業株式会社<br>大阪府門真市大字門真1006番地 |  |  |

|---------------------------------------|--------------------------------------------------------------------------------------|----------|---------------------------------------------|--|--|

| (32) 優先日                              | 平成18年6月8日 (2006.6.8)                                                                 | (74) 代理人 | 100077931                                   |  |  |

| (33) 優先権主張国                           | 日本国 (JP)                                                                             |          | 弁理士 前田 弘                                    |  |  |

|                                       |                                                                                      | (74) 代理人 | 100110939                                   |  |  |

|                                       |                                                                                      |          | 弁理士 竹内 宏                                    |  |  |

|                                       |                                                                                      | (74)代理人  | 100110940                                   |  |  |

|                                       |                                                                                      |          | 弁理士 嶋田 高久                                   |  |  |

|                                       |                                                                                      | (74)代理人  | 100113262                                   |  |  |

|                                       |                                                                                      |          | 弁理士 竹内 祐二                                   |  |  |

|                                       |                                                                                      | (74)代理人  | 100115059                                   |  |  |

|                                       |                                                                                      |          | 弁理士 今江 克実                                   |  |  |

|                                       |                                                                                      | (74)代理人  | 100115691                                   |  |  |

|                                       |                                                                                      |          | 弁理士 藤田 篤史                                   |  |  |

(54) 【発明の名称】電界効果トランジスタ、TFT駆動回路、パネルおよびディスプレイ

# (57)【要約】

【課題】半導体ナノワイヤを用い良好なトランジスタ特性を有する新規な電界効果トランジスタの構造を提供する。

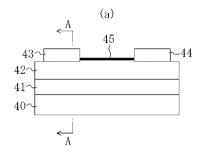

【解決手段】本発明の一例である電界効果トランジスタは、基板40、ゲート電極41、ゲート絶縁膜42がこの順に配置され、ゲート絶縁膜42の上に半導体ナノワイヤ45とソース電極43・ドレイン電極44が設けられている。半導体ナノワイヤ45とソース電極43・ドレイン電極44とのコンタクト領域において、半導体ナノワイヤ45の表面をソース電極43・ドレイン電極44の構成材料が覆っている。

【選択図】図4

#### 【特許請求の範囲】

# 【請求項1】

基板と、

前記基板上に設けられたゲート電極と、

前記ゲート電極上に設けられたゲート絶縁膜と、

前記ゲート絶縁膜上に設けられたソース電極およびドレイン電極と、

前記ソース電極およびドレイン電極の双方に電気的に接続しているとともに前記ゲート 絶縁膜の上に配置され、チャネルとして機能する半導体ナノワイヤと

を備え、

前 記 半 導 体 ナ ノ ワ イ ヤ の 表 面 の う ち 前 記 ゲ ー ト 電 極 の 最 も 近 く に 位 置 す る 半 導 体 ナ ノ ワ イヤ底部から上方へ少なくとも5mmまでの部分が前記ソース電極およびドレイン電極に 覆われている、電界効果トランジスタ。

【請求項2】

前記ソース電極およびドレイン電極に覆われている前記半導体ナノワイヤの表面は、該 ソ – ス 電 極 お よ び ド レ イ ン 電 極 と 化 学 的 に 結 合 し て い る 、 請 求 項 1 に 記 載 の 電 界 効 果 ト ラ ンジスタ。

#### 【請求項3】

前記半導体ナノワイヤの表面のうち前記ソース電極およびドレイン電極に覆われている 部 分 以 外 は 、 絶 縁 膜 に よ り 覆 わ れ て い る 、 請 求 項 1 ま た は 2 に 記 載 の 電 界 効 果 ト ラ ン ジ ス タ。

【請求項4】

前 記 半 導 体 ナ ノ ワ イ ヤ の う ち 前 記 ソ ー ス 電 極 お よ び ド レ イ ン 電 極 に 覆 わ れ て い る 部 分 以 外は、該半導体ナノワイヤの表層と芯部とが異なる材質である、請求項3に記載の電界効 果トランジスタ。

【請求項5】

前 記 半 導 体 ナ ノ ワ イ ヤ の う ち 前 記 ソ - ス 電 極 お よ び ド レ イ ン 電 極 に 覆 わ れ て い る 部 分 以 外の前記芯部がSiにより構成されている、請求項4に記載の電界効果トランジスタ。

【請求項6】

前記半導体ナノワイヤのうち前記ソース電極およびドレイン電極に覆われている部分以 外の前記表層がSiOっにより構成されている、請求項4または5に記載の電界効果トラ ンジスタ。

【請求項7】

前記基板は高分子材料または高分子材料と無機材料の複合体により構成されている、請 求 項 1 から 6 の い ず れ か 一 つ に 記 載 の 電 界 効 果 ト ラ ン ジ ス タ 。

【請求項8】

請 求 項 1 か ら 7 の ۱ ず れ か 一 つ に 記 載 の 電 界 効 果 ト ラ ン ジ ス タ に よ り 構 成 さ れ て ۱ 1 る こ とを特徴とするTFT素子。

【請求項9】

請求項8に記載のTFT素子を備えることを特徴とするパネル。

【請求項10】

請求項9に記載のパネルを備えることを特徴とするディスプレイ。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は電界効果トランジスタ、TFT駆動回路、パネルおよびディスプレイに関し、 特に、半導体ナノワイヤをチャネルに用いた電界効果トランジスタ及びそれを用いたTF T駆動回路、パネルおよびディスプレイに関するものである。

# 【背景技術】

[00002]

従 来 の ア ク テ ィ ブ 型 液 晶 表 示 装 置 や 有 機 エ レ ク ト ロ ル ミ ネ ッ セ ン ス ( E L )表 示 素 子 は ガ

20

10

30

40

30

40

50

ラス基板に形成されており、基板上にマトリックス状に配置された画素はその近傍に配置されたトランジスタ素子によって制御されている。現在の技術ではガラス基板上には結晶半導体のトランジスタを形成することができないため、アモルファスシリコンやポリシリコン薄膜からなる電界効果トランジスタ(TFT)が画素の制御に用いられている。

#### [0003]

また近年、フレキシブル基板上に有機材料や半導体ナノワイヤをチャネル材料に用いて薄膜トランジスタを形成する技術が開発されてきている(特許文献 1、非特許文献 1参照)。

#### [0004]

特許文献 1 および非特許文献 1 では、デバイスを形成する基板と異なる基板上に形成したシリコンナノワイヤを基板から剥離し、溶液に分散させて、この溶液に分散したナノワイヤを(フレキシブル)基板上に配置することで高移動度チャネルを形成する方法が提案されている。この方法では、トランジスタのチャネル領域が単結晶シリコンで形成されているため、移動度が 1 0 0 c m² V -1 s -1 を越えるトランジスタの形成に成功している。

【特許文献 1 】特表 2 0 0 4 - 5 0 7 1 0 4 号公報

【非特許文献 1 】 "High Performance thin film transistors using semiconductor na nowires and nanoribbons", Nature, vol.425, 2003, pp.274.

【非特許文献 2 】"Large-Scale Hierarchical Organization of Nanowire Arrays for Integrated Nanosystems", NANO LETTERS, vol.3,No.9 2003, pp.1255-1259.

【非特許文献 3 】"Directed Assemly of One-Dimensional Nonostructures into Functional Networks", SCIENCE, vol.291, 2001, pp.630.

#### 【発明の開示】

【発明が解決しようとする課題】

#### [0005]

しかしながら、特許文献 1 、非特許文献 1 に開示されている方法では、半導体ナノワイヤの製造方法や基板上に半導体ナノワイヤを並べることに意識が集中しており、実用上求められる半導体の基本性能が十分発揮できるようにするための検討は行われていない。特に半導体ナノワイヤとソース電極およびドレイン電極との接続、およびチャネルとしての機能に関しての検討は行われていない。

#### [0006]

このような状況において、本発明は、半導体ナノワイヤを用い良好なトランジスタ特性を有する新規な電界効果トランジスタの構造を提供することを目的の一つとする。また、本発明は、その電界効果トランジスタを用いた電子装置を提供することを目的の一つとする。

【課題を解決するための手段】

#### [0007]

上記課題を解決するために、半導体ナノワイヤをチャネル層に用いた電界効果トランジスタにおいて、電極からチャネル層への電荷注入障壁を小さくした。

#### [0008]

具体的には、本発明の第1の電界効果トランジスタは、基板と、前記基板上に設けられたゲート電極と、前記ゲート電極上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたソース電極およびドレイン電極と、前記ソース電極およびドレイン電極の上に配置され、チャネルとして機能する半導体ナノワイヤとを備え、前記半導体ナノワイヤの表面のうち前記ゲート電極の最も近くに位置する半導体ナノワイヤ底部から上方へ少なくとも5nmまでの部分が配置ソース電極およびドレイン電極に覆われている構成とした。半導体ナノワイヤが配置されている場合とゲート絶縁膜の上とは、半導体ナノワイヤがゲート絶縁膜に接している場合とゲート絶縁膜に接していなくてその上方に存する場合の両方を含む。また、上記の構成では下から上へ、基板、ゲート電極、ゲート絶縁膜、ソースおよびドレイン電極、という順番で積み重ねられている。半導体ナノワイヤの表面のうち底部から上方へ少なくとも5nmまで

30

40

50

の部分がソース電極およびドレイン電極に覆われていることによって半導体ナノワイヤと ソース電極及びドレイン電極との電気的な接続が行われている。

[0009]

ある好適な実施形態において、前記ソース電極およびドレイン電極に覆われている前記 半導体ナノワイヤの表面は、該ソース電極およびドレイン電極と化学的に結合している。 ここで、半導体ナノワイヤとソース電極およびドレイン電極とが化学的に結合していると は、例えば、半導体ナノワイヤを構成している物質と電極を構成している物質が合金化し ていることを言う。

[0010]

ある好適な実施形態において、前記半導体ナノワイヤの表面のうち前記ソース電極およびドレイン電極に覆われている部分以外は、絶縁膜により覆われている。前記半導体ナノワイヤのうち前記ソース電極およびドレイン電極に覆われている部分以外は、該半導体ナノワイヤの表層と芯部とが異なる材質であることが好ましい。前記半導体ナノワイヤのうち前記ソース電極およびドレイン電極に覆われている部分以外の前記芯部がSiにより構成されていることが好ましい。前記半導体ナノワイヤのうち前記ソース電極およびドレイン電極に覆われている部分以外の前記表層がSiO₂により構成されていることが好ましい。

[0011]

前記基板は高分子材料または高分子材料と無機材料の複合体により構成されていることが好ましい。

[0012]

本発明のTFT素子は、上記の電界効果トランジスタにより構成されている。

[0013]

本発明のパネルは、上記のTFT素子を備えている。

[0014]

本発明のディスプレイは、上記のパネルを備えている。

- 【発明の効果】

- [ 0 0 1 5 ]

本発明の電界効果トランジスタでは、半導体ナノワイヤのチャネル層に隣接して電極が 形成されているため、チャネル層への電荷注入障壁が小さい。このため、フレキシブル基 板上に、トランジスタ特性の良好な電界効果トランジスタを実現できる。

[0016]

また、高分子材料や高分子材料と無機材料の複合体からなる基板を用いることができる ため、フレキシブルな電界効果トランジスタの実現も可能となる。

【発明を実施するための最良の形態】

[0017]

本発明の実施形態を説明する前に、図1及び図2を参照しながら本願に至った過程を説明する。

[0018]

まず、電界効果トランジスタの動作原理について簡単に説明する。ゲート電極に電圧をかけると、静電誘導によってゲート絶縁膜と半導体の界面付近にチャネル層が形成される。この時にソース電極とドレイン電極との間に電圧をかけると、電荷はソース電極からチャネルへ注入され、チャネル層を伝い、ドレイン電極へ抜けるという電荷の流れが生じる。これが電界効果トランジスタにおいて電流が流れるしくみである。

[0019]

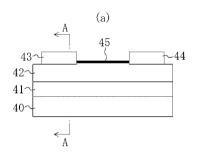

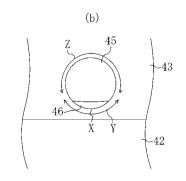

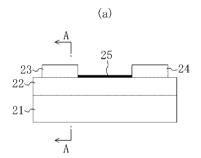

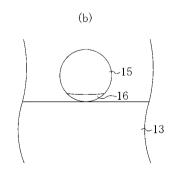

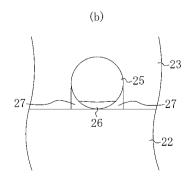

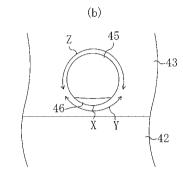

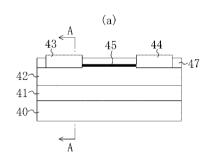

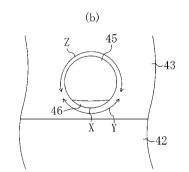

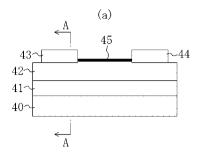

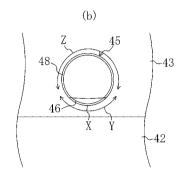

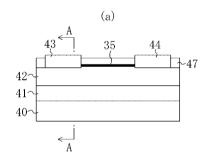

図1(a)および図2(a)は、特許文献1や非特許文献1等に記載されている従来開示されている方法を電界効果トランジスタの製造に適用して、半導体ナノワイヤ15,25をチャネルに用いて作製した電界効果トランジスタ構造の模式的な断面図であり、図1(b)は図1(a)のA-A線断面の一部拡大図、図2(b)は図2(a)のA-A線断面の一部拡大図である。

#### [0020]

半導体ナノワイヤ15を用いた電界効果トランジスタとしては、図1(a)に示すようにゲート電極11、ゲート絶縁膜12、ソース電極13・ドレイン電極14の順に形成され、ソース・ドレイン電極13,14上に半導体ナノワイヤ15が形成されるボトムコンタクト型(半導体ナノワイヤ15の底部がソース・ドレイン電極13,14に接触している)と、図2(a)に示すようにゲート電極21、ゲート絶縁膜22、半導体ナノワイヤ25の順に形成され、ナノワイヤ25上にソース電極23・ドレイン電極24が形成されるトップコンタクト型(半導体ナノワイヤ25の上部がソース・ドレイン電極23,24に接触している)が考えられる。ここで、ソース電極13,23とドレイン電極14,24との間に流れる電流は、ソース電極およびドレイン電極13,23,14,24と半導体ナノワイヤ15,25との間での電荷の移動し易さに依存している。この電荷の移動し易さは、半導体ナノワイヤ15,25とソース電極13,23・ドレイン電極14,24との接触抵抗やエネルギー準位に影響される。

# [0021]

図1(a)に示したボトムコンタクト型電界効果トランジスタにおいて、ソース電極13と半導体ナノワイヤ15とが接触している領域における断面図を図1(b)に示す。ゲート絶縁膜12上にソース電極13が形成され、その上に半導体ナノワイヤ15が配置されている。チャネル層16は半導体ナノワイヤ15の下部に形成される。前述のように、ソース電極13から半導体ナノワイヤ15の電荷の移動し易さは両者の接触抵抗に影響を受けるが、ソース電極13と半導体ナノワイヤ15の接触面積が大きいほど電荷の移動は良好に行われる。しかし、図1(b)に示すボトムコンタクト型電界効果トランジスタにおいては、ソース電極13と半導体ナノワイヤ15との接触は線接触(断面においては点接触)であるため接触面積は非常に小さく、従って電荷は移動しにくく、トランジスタ特性も低いものとなる。

#### [0022]

図2(a)に示したトップコンタクト型電界効果トランジスタにおいて、ソース電極23と半導体ナノワイヤ25が接触している領域における断面図を図2(b)に示す。だート絶縁膜22上に半導体ナノワイヤ25が配置され、その上にソース電極23が形成すると、半導体ナノワイヤ25を配置した後に蒸着系装置により電極を形成すると、半導体ナノワイヤ25を配置した後に蒸着系装置により電極を形成すると、半導体ナノワイヤ25も自身がマスクに電極がある。しかし、半導体ナノワイヤ25も自身がマスクでは半導体ナノワイヤ25の間ソース電極23と半導体ナノワイヤ25との接触面積はボトムコンタクト型に比べたきるのでは空での移動は行われ易くなる。しかし、半導体ナノワイヤ25中の電荷の通り道である電を半導体ナノワイヤ25とは接触していない。そのため、電荷は半導体ナノワイヤ25とは接触していない。そのため、電荷は半導体ナノワイヤ25と電極との接触部分から半導体ナノワイヤ25に注入され、半導体部分を経由してチャネル層26へ移動する。

#### [0023]

チャネル層 2 6 以外の半導体部分はキャリア密度も低く、高抵抗である。したがって、トップコンタクト型電界効果トランジスタではソース電極 2 3 と半導体ナノワイヤ 2 5 の接触面積は大きくなるものの、電荷がチャネル層 2 6 へ高抵抗半導体領域を経由して移動するため、トランジスタ特性は低いものとなる。このような課題を解決するために本願発明者らは種々の検討を重ねて本願発明に至った。

# [0024]

以下、本発明の実施形態を図面に基づいて詳細に説明する。以下の図面においては、説明の簡潔化のため、実質的に同一の機能を有する構成要素を同一の参照符号で示す。

#### [0025]

(実施形態1)

20

30

30

40

50

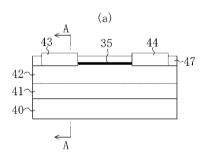

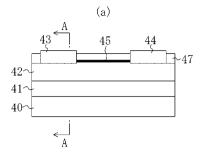

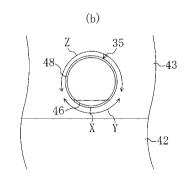

図4を参照しながら、半導体ナノワイヤ45とソース電極43およびドレイン電極44 とのコンタクト領域において半導体ナノワイヤ45の表面が電極43,44で被覆されている構造を有する実施形態1に係る電界効果トランジスタについて説明する。

## [0026]

本実施形態の電界効果トランジスタは、基板40の上にゲート電極41が形成され、さらにその上にゲート絶縁膜42が形成されている。ゲート絶縁膜42の上にはチャネルとして機能する半導体ナノワイヤ45が配置されており、さらにゲート絶縁膜42の上に半導体ナノワイヤの両端を覆ってソース電極43とドレイン電極44とが形成されている。

# [0027]

基板40としては、シリコンやガラスなどの無機材料、また、ポリイミドや芳香族ポリエステルのような有機材料によって構成される材料を用いることができるが、ここでは有機材料であるプラスティック基板を用いた。また、ゲート電極41、ソース電極43及びドレイン電極44の材料としては、Ti、Au、A1、Ni、Ag、Cu、Pt、Pdなど、あるいはこれらの合金のような無機材料や、スルホン酸やカルボン酸等をカウンターイオンとするポリアニリンやポリチオフェンなどの有機材料を使用することができるが、ここでは、A1やNiなどの金属を用いた。

#### [0028]

ソース電極 4 3 及びドレイン電極 4 4 は、それぞれ半導体ナノワイヤ 4 5 と電気的コンタクトを形成しているが、半導体ナノワイヤ 4 5 の表面をソース電極 4 3 およびドレイン電極 4 4 の構成素材である金属が覆っているだけであって、本実施形態では両者の化学的結合は存していない。ゲート電極 4 1 にバイアスを印加すると半導体ナノワイヤ 4 5 のゲート絶縁膜 4 2 との界面付近にゲート絶縁膜 4 2 を介してチャネル層 4 6 の導電性が制御される。

#### [0029]

半導体ナノワイヤ45は、例えば、Si、Ge、SiGeなどのIV族半導体、GaAs、InP、InAsなどのIII V族半導体、またはZnS、ZnSe、CdSなどのII VI族半導体からなる半導体を用いることができるが、本実施形態ではSiを用いた。また、半導体ナノワイヤ45にドーピングを施すことによりP型半導体ナノワイヤやN型半導体ナノワイヤにしてもよい。また、PNP型半導体ナノワイヤのように一本の半導体ナノワイヤにN型、P型の両方を作りこんでも良い。

#### [0030]

半導体ナノワイヤ 4 5 の長さは、例えば、 1  $\mu$  m ~ 1 0 0  $\mu$  m 程度である。また直径は、例えば、 5 n m ~ 1  $\mu$  m 程度である。これら半導体ナノワイヤ 4 5 の形状は、デバイス仕様に応じて変化する。なお、半導体ナノワイヤ 4 5 の断面形状は、円に限らず、四角形、六角形のような多角形や楕円のような形状であってもよい。

#### [0031]

本実施形態の電界効果トランジスタでは、ソース電極43及びドレイン電極44と半導体ナノワイヤ45内に形成されるチャネル層46との電荷障壁を小さくするために、半導体ナノワイヤ45の表面のうち最もゲート電極41側に位置する半導体ナノワイヤ底部との半導体ナノワイヤ45表面をソース電極43から少なくとも上方に5nmに位置するまでの半導体ナノワイヤ45表面をソース電極43およびドレイン電極44が覆うように形成されている。ここで、最もゲート電極41側に位置する半導体ナノワイヤ底部×とは、図4(b)における×点、または×面のことであり、での半導体ナノワイヤ底部×から上方に5nmに位置するまでの半導体ナノワイヤ底部×から上方に5nmに位置するまでの半導体ナノワイヤ底部×から上方に5nmというのは、高さ方向(ゲート絶縁膜42表面に対して略垂直な方向であってゲート絶縁膜42表面から遠ざかる方向)からで5nmということであり、

#### [0032]

一般にチャネル層46の厚みは、ゲート電圧に依存するのだが、ゲート電極41に最も

20

30

40

50

近い部分から上方へ2~8nm程度である。従って、このチャネル層46の表面ができるだけ広くソース電極43およびドレイン電極44の構成材料で覆われて電気的に接続していれば、電荷注入障壁が低下してソース電極43からチャネル層46への電荷注入が容易に行われ、チャネル層46からドレイン電極44へ電荷が容易に流れていくことになる。そして、チャネル層46を流れる電流が多くなり、高いトランジスタ特性が得られる。ここで、半導体ナノワイヤ底部×から、その上方に5nmに位置するまでの半導体ナノワイヤ45の表面がソース電極43およびドレイン電極44の構成材料によって覆われていればチャネル層46の表面の全てあるいは大部分がソース電極43およびドレイン電極44の構成材料で覆われることになり、従ってチャネル層46に流れる電流が十分に多くなり、優れたトランジスタ特性を有する電界効果トランジスタとなる。

[0033]

即ち本実施形態の電界効果トランジスタは、図1,2に示された電界効果トランジスタ構造とは違い、ソース電極43・ドレイン電極44と半導体ナノワイヤ45との接触面積が小さくなく、また、ソース電極43・ドレイン電極44から半導体ナノワイヤ45中のチャネル層46までの経路が長くない、ソース電極43,ドレイン電極44からチャネル層46への電荷障壁が小さいボトムゲート型電界効果トランジスタ構造を有することを特徴としている。これは、本実施形態の電界効果トランジスタでは、半導体ナノワイヤ45の中でチャネル層46となる部分とソース電極43・ドレイン電極44との接触面積が大きいことに由来している。

[0034]

半導体ナノワイヤ45の製法としては、まず、任意の基板上に触媒となる金属微粒子を配置することからスタートする。触媒金属としては、例えば、コバルト、ニッケル、金または白金などを用いるとよい。この触媒金属の微粒子を基板へ配置する方法としては、例えば、スパッタ法や蒸着法などで1~10nm程度の触媒金属の薄膜を堆積させ、任意の雰囲気中で熱処理することで金属微粒子化する方法や、金属微粒子コロイドを基板上に塗布する方法を用いるとよい。

[0035]

それからCVD法を用いてこの基板上に半導体ナノワイヤ45を成長させる。シリコンからなる半導体ナノワイヤを成長させる方法としては、例えば、ソースガスにシランやジシランを用い、基板温度を400~600 程度で成長させる方法を挙げることができる。触媒金属の微粒子からシリコンのワイヤが成長していく。

[0036]

このようにして作製した半導体ナノワイヤ45は、溶媒によって基板から剥がして溶媒中に分散させる。半導体ナノワイヤ45を剥離させる方法としては、例えば、基板に超音波処理を施し機械的に剥離する方法や、半導体ナノワイヤ45が成長した基板表面をライトエッチして剥離する方法を用いるとよい。ここで分散液に用いる溶媒としては、水溶液、有機溶媒、または、水と有機溶媒を混合したものを挙げることができる。有機溶媒としては、例えば、エタノール、プロパノール、ペンタノール、ヘキサノール、エチレングリコールなどのアルコール、エチレングリコールモノメチルエーテルなどのエステル、メチルエチルケトンなどのケトン類、ヘキサン、オクタンなどのアルカン、テトラヒドロフランの混合液などを使用することができる。アルコールの混合液、水とテトラヒドロフランの混合液などを使用することができる。

[0037]

以下に上記のようにして作製した半導体ナノワイヤ 4 5 を用いた本実施形態のボトムゲート型電界効果トランジスタを製造する方法を説明する。

[0038]

まず、リソグラフィー法を用いてプラスティック基板 4 0 上に、ゲート電極 4 1 を形成する領域以外の領域にレジストをパターニングにより形成する。

[0039]

次に、上述したレジストをマスクとしてプラスティック基板をエッチングしてゲート電

20

30

40

50

極 4 1 を形成する領域を凹ませる。エッチングは、例えば、 C F  $_4$  や酸素ガスを用いた反応性イオンエッチングによって行い、 1 0 0 ~ 3 0 0 n m 程度の深さにエッチングする。

[0040]

次に、ゲート電極 4 1 となるゲート金属をエッチングした部分に堆積させる。ゲート電極 4 1 は、例えば、 A 1 をスパッタ法によって 1 0 0 ~ 3 0 0 n m 程度堆積させて形成する。

[0041]

次に、レジストおよびレジスト上に堆積しているゲート金属を除去し、ゲート電極 4 1 部分にのみゲート金属を残す。これらの除去には、有機系のレジスト除去液を用いてレジストを溶解し、レジスト上に堆積したゲート金属を除去する。こうして、ゲート電極 4 1 を形成する。

[0042]

次に、絶縁層を堆積させてゲート絶縁膜 4~2 を形成する。ゲート絶縁膜 4~2 の形成法としては、例えば、S~i~O~2 を C~V~D 法によって 5~0~~3~0~0~n~m 程度堆積させる方法を挙げることができる。

[0043]

次に上述のように作成した半導体ナノワイヤ 4 5 を、ゲート絶縁膜 4 2 上であってゲート電極 4 1 の上方に配置する。配置する方法としては、例えば、半導体ナノワイヤ 4 5 を配置する所望の領域上にインクジェット法により半導体ナノワイヤ 4 5 を溶媒に分散させたインクを滴下、乾燥させて、半導体ナノワイヤ 4 5 を配置させる。また、スピンコート法や転写法、ディップコート法、ドクターブレード法などを用いて半導体ナノワイヤ 4 5 を配置させても良い。

[0044]

半導体ナノワイヤ45は、この後に形成するソース電極43とドレイン電極44とを結ぶものであるので、両電極43,44を結ぶ方向がワイヤ軸方向となっていることが好ましい。このように半導体ナノワイヤ45の向きを所定の方向に揃えること、即ち配向させることは、半導体ナノワイヤ45を溶媒に分散させたインクを塗布するときあるいは塗布後にそのインクに流れを作ることによって行うことができる。例えば、半導体ナノワイヤインクに基板を浸した後基板を引き上げることによりインクに流れを作って半導体ナノワイヤ45を配向させたり、基板上に半導体ナノワイヤインクを載せた後ドクターブレードでそのインクを基板上に押し広げることによってインクに流れを作って半導体ナノワイヤ45を配向させる方法などを挙げることができる。なお、非特許文献2,3に記載されている方法を用いて半導体ナノワイヤ45を配置してもよい。

[0045]

この後に、ソース電極43・ドレイン電極44を形成する。この形成方法としては、以下のような方法を用いるとよい。

[0046]

リソグラフィーによりソース電極 4 3 ・ドレイン電極 4 4 の形成される領域以外の領域にレジストをパターニングにより形成する。この後、ゲート絶縁膜 4 2 をエッチングにより 1 0 ~ 1 0 0 n m程度の深さにエッチングしてソース電極 4 3 およびドレイン電極 4 4 を形成する領域を凹ませる。

[0047]

その後、ソース電極・ドレイン電極材料であるニッケルをスパッタ法により堆積させ、それからレジストおよびレジスト上に堆積したニッケルをリフトオフして除去する。ソース電極・ドレイン電極材料をスパッタ法により堆積させる際に、基板を傾け、回転させることにより、電極材料の基板への入射角が変化するようにして、半導体ナノワイヤ底部Xまで電極材料が回り込んで堆積するようにする。また、スパッタ法の代わりにインクジェット法などによって液状電極材料を塗布し、半導体ナノワイヤ底部Xまで電極材料が回り込むようにしてもよい。また、ソース電極43・ドレイン電極44の一部を半導体ナノワイヤ45を堆積する前にゲート絶縁膜42上に形成し、半導体ナノワイヤ45を配置した

後に、上記のような手段を用いてソース・ドレイン電極材料を堆積・塗布してもよい。こうして、図4に示す電界効果トランジスタが出来上がる。

#### [0048]

本実施形態のボトムゲート型電界効果トランジスタの製法によれば、ソース電極 4 3 およびドレイン電極 4 4 と、半導体ナノワイヤ 4 5 のチャネル層 4 6 との間に広い面積の良質な電気的接続が形成される。従って基板をプラスチック基板とした場合には、プラスティック基板上にトランジスタ特性が良好な電界効果トランジスタを形成することが可能となる効果を奏する。このため、プラスティック基板上に信頼性の高い高性能なトランジスタを製造することができる。

#### [0049]

なお、図4(a)に記載の電界効果トランジスタでは、半導体ナノワイヤ45がソース電極43からドレイン電極44にゲート絶縁膜42に平行に一本で配向されているが、半導体ナノワイヤ45が複数本であったり、ソース電極43・ドレイン電極44間において両電極間を結ぶ方向と平行ではなくて斜めに配置されていてもよい。

#### [0050]

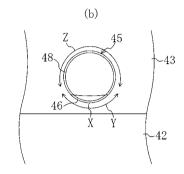

## (実施形態2)

実施形態 2 のボトムゲート型電界効果トランジスタは、図 5 に示すように半導体ナノワイヤ 4 5 の上に絶縁膜である封止膜 4 7 を有している。それ以外の電界効果トランジスタの構成部分および製造方法は実施形態 1 と同じなので、封止膜 4 7 についてのみ以下に説明をする。

## [0051]

封止膜47としては、SiNやSiO₂などの無機材料、また、ポリイミドや芳香族ポリエステルのような有機材料によって構成される絶縁性を有する材料を用いる。

#### [ 0 0 5 2 ]

封止膜 47材料として例えばSiNやSiO₂などの無機材料を用いる場合は、基板 40上にゲート電極 41、ゲート絶縁膜 42、半導体ナノワイヤ 45、ソース電極 43・ドレイン電極 44を形成した後、SiNやSiO₂をCVD法によって50~300nm程度堆積させて封止膜 47を形成すればよい。ポリイミドなど、用いる封止膜材料によっては、スピンコート法やインクジェット法などを用いても良い。また、例えば、ゲート絶縁膜 42上に半導体ナノワイヤ 45 を形成した後、封止膜 47 を形成し、その後ソース電極 43・ドレイン電極 44 を形成しても良い。また、ポリイミドなどの有機材料を封止膜 47 として用いる場合、ポリイミドの溶液、前駆体液などに半導体ナノワイヤ 45 を混合させてゲート絶縁膜 42 上に塗布して半導体ナノワイヤ 45 の配置と封止膜 47 形成とを同時に行っても良い。

# [0053]

本実施形態のボトムゲート型電界効果トランジスタによれば、ソース電極 4 3 およびドレイン電極 4 4 とチャネル層 4 6 との間の良好な電気的接続が得られ高いトランジスタ特性が得られる実施形態 1 の効果に加えて、半導体ナノワイヤ 4 5 が封止膜 4 7 に覆われていて大気中の水分や酸素の影響を受けにくいため、プラスティック基板上に良質な電気的接続を有するとともに環境変化があってもトランジスタ特性はほとんど変化しないトランジスタを形成することが可能となる。このため、プラスティック基板上に信頼性の高い高性能なトランジスタを製造することができる。

#### [0054]

# (実施形態3)

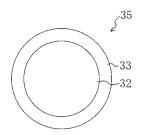

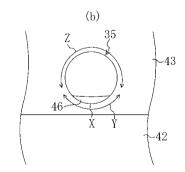

実施形態 3 のボトムゲート型電界効果トランジスタは、図 3 に示すように、横断面においてコアである芯部 3 2 の周りをシェルである表層 3 3 が覆っている、いわゆるコア・シェル型の半導体ナノワイヤ 3 5 を有している。ここで、表層 3 3 と芯部 3 2 とは互いに異なる材質からなっている。なお、この半導体ナノワイヤ 3 5 はソース電極 4 3 およびドレイン電極 4 4 と接続している領域においてはコア・シェル構造とはなっておらず、この領域では芯部 3 2 のみが存している。

20

10

30

30

40

50

[0055]

本実施形態3の電界効果トランジスタは図6(a)に示す断面形状を有しており、図6(a)のA-A線断面は図6(b)である。半導体ナノワイヤ35がコア・シェル構造であること以外は、封止膜47を備えている実施形態2のトランジスタの構造および製造方法とほぼ同じなので、コア・シェル型の半導体ナノワイヤ35のことを中心に以下に説明をする。

[0056]

コア・シェル型の半導体ナノワイヤ35の製法をまず説明する。

[0057]

最初に、実施形態1で説明したようにして、シリコンからなるナノワイヤを形成する。

[0058]

次にこのシリコンナノワイヤが成長した基板ごとシリコンナノワイヤを熱酸化することで、表層33がSiO₂、芯部32がSiである図3に示すコア・シェル型の半導体ナノワイヤ35を形成することができる。ここで、この表層33のシリコン酸化膜の膜厚や膜質は、熱酸化の酸化時間、酸化温度および酸化雰囲気に依存するため、デバイスの仕様に合わせたシリコン酸化膜設計が可能となる。本実施形態の酸化条件としては、例えば、1100 、酸素雰囲気を好ましく挙げることができ、ラピットサーマルプロセッシングにより表層33となるシリコン酸化膜を形成することが好ましい。

[0059]

本実施形態3のボトムゲート型電界効果トランジスタを製造する方法は、コア・シェル型半導体ナノワイヤ35を用いる以外の基本的な部分は実施形態2と同様である。ただし、コア・シェル型半導体ナノワイヤ35上にソース電極43・ドレイン電極44を形成する際に、ソース電極43・ドレイン電極44と電気的に接続する領域における半導体ナノワイヤ35の表層33を取り除く作業が必要であり、表層33を取り除けばソース電極43・ドレイン電極44を形成をする前にゲート絶縁膜42をエッチングする必要がないので、製造方法においてこれらに関する部分について説明する。

[0060]

まず、ゲート絶縁膜42上にコア・シェル型の半導体ナノワイヤ35を配置する。

[0061]

次にフォトリソグラフィーを用いてソース電極43・ドレイン電極44を形成する領域以外の領域にレジストをパターニングにより形成する。

[0062]

それから、ソース電極 4 3 ・ドレイン電極 4 4 とコア・シェル型の半導体ナノワイヤ 3 5 とが電気的に接続するように、上述したレジストをマスクとしコア・シェル型の半導体ナノワイヤ 3 5 の表層 3 3 を除去する。この表層 3 3 を除去する方法としては、例えば、ドライエッチングやウエットエッチングを用いる。これによりソース電極 4 3 ・ドレイン電極 4 4 を形成する領域においてはコア・シェル型の半導体ナノワイヤ 3 5 は表層 3 3 が取り除かれて芯部 3 2 のみとなり、ソース電極 4 3 ・ドレイン電極 4 4 を形成する領域におけるゲート絶縁膜 4 2 とコア・シェル型の半導体ナノワイヤ 3 5 の間には取り除いた表層 3 3 分だけ空隙ができる。したがって本実施形態では、実施形態 1 や 2 のように半導体ナノワイヤ 4 5 とゲート絶縁膜 4 2 との間の空隙を設けるためのゲート絶縁膜 4 2 のエッチングが必要なくなり、ゲート絶縁膜 4 2 をエッチングすることにより生じる虞のあるゲート絶縁膜不良を本実施形態では抑制することができる。

[0063]

次に、ソース電極 4 3 およびドレイン電極 4 4 の構成素材をゲート絶縁膜 4 2 上に堆積させる。ソース電極 4 3 およびドレイン電極 4 4 の構成素材を堆積させる方法は実施形態 2 と同じである。インクジェット法などの塗布プロセスを使用する場合は、ゲート絶縁膜 4 2 とコア・シェル型の半導体ナノワイヤ 3 5 の間に設けられた空隙にソース電極 4 3 およびドレイン電極 4 4 の構成素材が入り込めるように、空隙よりも小さな粒径の電極材料を用いることが好ましい。

#### [0064]

本実施形態では、コア・シェル構造の半導体ナノワイヤ35を用いることにより、半導体である芯部32が表層33により保護されるため、チャネル領域が大気中の水分や酸素の影響を受けにくくなり、トランジスタの動作が使用環境に左右されず安定する。ここで半導体ナノワイヤ35の芯部32がSiからなっており表層33がSiO2からなっているので、チャネル層の設計および製造に従来の半導体分野で用いられてきた装置や理論を応用でき、製造コストや開発コストを抑えることができるとともに、表層33の存在によってより酸素や水分に影響を受けにくいトランジスタ特性を得ることができる。また、ソース電極43・ドレイン電極44との接続する領域における半導体ナノワイヤ35の表層33を除くだけで、簡単に半導体ナノワイヤ35とゲート絶縁膜42との間に隙間を作ることができ、半導体ナノワイヤ35をチャネルとして用いた電界効果トランジスタを容易に作製することができる。

#### [0065]

以上より、本実施形態では、ゲート絶縁膜42をエッチングすることなく良質なソース電極43・ドレイン電極44と半導体ナノワイヤ35との電気的接続を形成することができ、かつ、大気中の水分や酸素の影響を受けにくいため、プラスティック基板上に良質なソース電極43・ドレイン電極44と半導体ナノワイヤ35との電気的接続を有するトランジスタを形成することが可能となる。

#### [0066]

#### (実施形態4)

本実施形態は、ソース電極およびドレイン電極に覆われている半導体ナノワイヤの表面がソース電極・ドレイン電極と化学的に結合している点が実施形態1と異なっており、その他の点は実施形態1と同じであるので、異なっている点について以下に説明する。

#### [0067]

図7(a)は本実施形態に係る電界効果トランジスタの断面図、図7(b)は図7(a)のA‐A線断面図である。半導体ナノワイヤ45の材料、形状は本発明第一の電界効果トランジスタと同じである。ソース電極43およびドレイン電極44は、例えば、Ni、Au、Agなどの金属で、半導体ナノワイヤ45の材料であるSiと合金化(化学的結合)する金属を適宜選択して用いる。また、製造コストを考慮した場合に、合金化する温度が低いほど好ましい。

#### [0068]

本実施形態において、半導体ナノワイヤ45とソース電極43・ドレイン電極44とが 化学的に結合している部分というのは、ソース電極43・ドレイン電極44と半導体ナノ ワイヤ45との合金部48である。

# [0069]

本実施形態では、ソース電極 4 3 及びドレイン電極 4 4 が半導体ナノワイヤ 4 5 表面を覆うように形成され、かつ、ソース電極 4 3 及びドレイン電極 4 4 と半導体ナノワイヤ 4 5 とが化学的に結合しているので、ソース電極 4 3 ・ドレイン電極 4 4 と半導体ナノワイヤ 4 5 のエネルギー準位の間に中間準位が形成される。このため、ソース電極 4 3 ・ドレイン電極 4 4 とチャネル層 4 6 との電荷障壁が実施形態 1 に係るトランジスタよりも小さくなり、トランジスタ特性が実施形態 1 に係るトランジスタよりも向上する。これ以外の効果は実施形態 1 と同じである。

#### [0070]

以下、本実施形態の電界効果トランジスタの製造方法のうち、実施形態 1 とは異なる部分である半導体ナノワイヤ 4 5 とソース電極 4 3 ・ドレイン電極 4 4 とが化学的に結合する工程を説明する。

#### [0071]

実施形態 1 において説明した製造方法によってソース電極 4 3 ・ドレイン電極 4 4 を形成した後、ソース電極 4 3 ・ドレイン電極 4 4 と半導体ナノワイヤ 4 5 とを化学的に結合させる。この結合方法としては、基板ごと電気炉に入れて不活性雰囲気の中で熱処理を行

20

30

30

40

50

う方法が好ましい。用いるソース・ドレイン電極材料に合わせて、熱処理温度、雰囲気を適宜選択すればよい。また、レーザーアニール法により、結合させてもよい。また、塗布法によりソース電極43・ドレイン電極44を形成する場合には、熱処理温度を下げるために、ソース・ドレイン電極材料として粒径の小さいもの(1~10nm)を用いることが好ましい。

#### [0072]

本実施形態のボトムゲート型電界効果トランジスタの製法によれば、ソース電極 4 3 およびドレイン電極 4 4 と、半導体ナノワイヤ 4 5 のチャネル層 4 6 との間に広い面積の良質な電気的接続が形成される。従って基板をプラスチック基板とした場合には、プラスティック基板上にトランジスタ特性が良好な電界効果トランジスタを形成することが可能となる効果を奏する。このため、プラスティック基板上に信頼性の高い高性能なトランジスタを製造することができる。

#### [0073]

(実施形態5)

本実施形態のボトムゲート型電界効果トランジスタは、図8に示すようにソース電極43 およびドレイン電極44に覆われている半導体ナノワイヤ45の表面がソース電極43 ドレイン電極44と化学的に結合しているとともに、ソース電極43 およびドレイン電極44に覆われている部分以外の半導体ナノワイヤ45の上に絶縁膜である封止膜47を有している。封止膜47以外の電界効果トランジスタの構成部分および製造方法は実施形態4と同じである。なお、封止膜47については実施形態2と同じである。従って本実施形態の電界効果トランジスタの構造および製造方法については実施形態2および4を参照することとし説明を省略する。

#### [0074]

なお製造方法において、封止膜47の形成および化学的結合の形成はどちらを先に行っても構わない。例えば、ゲート絶縁膜42上に半導体ナノワイヤ45を配置した後、封止膜47を形成し、その後ソース電極43・ドレイン電極44を形成してソース電極43・ドレイン電極44と半導体ナノワイヤ45との化学的結合を行っても良い。また、封止膜47の形成前に、半導体ナノワイヤ45とソース電極43・ドレイン電極44とを化学的に結合させてもよい。また、ポリイミドなどの有機材料を保護膜47として用いる場合、ポリイミドの溶液、前駆体液などに半導体ナノワイヤ45を混合させてゲート絶縁膜42上に塗布して半導体ナノワイヤ45の配置と封止膜47形成とを同時に行っても良い。

# [0075]

本実施形態では、実施形態 4 の効果に加えて、封止膜 4 7 に関しては実施形態 2 において説明した効果を奏する。

# [0076]

(実施形態6)

本実施形態のボトムゲート型電界効果トランジスタは、図9に示すようにソース電極43 およびドレイン電極44に覆われているコア・シェル型の半導体ナノワイヤ35の表面がソース電極43・ドレイン電極44と化学的に結合しているとともに、半導体ナノワイヤ35の上に絶縁膜である封止膜47を有している。コア・シェル型の半導体ナノワイヤ35以外の電界効果トランジスタの構成部分および製造方法は実施形態5と同じである。従って本実施形態の電界効果トランジスタの構造および製造方法については実施形態3および5を参照することとし説明を省略する。

#### [0077]

本実施形態では、実施形態5の効果に加えて、コア・シェル型の半導体ナノワイヤ35に関しては実施形態3において説明した効果を奏する。

# [0078]

(実施形態7)

実施形態7では、ディスプレイの一例として、有機エレクトロルミネッセンス素子(有

機EL素子)を用いたディスプレイについて説明する。

#### [0079]

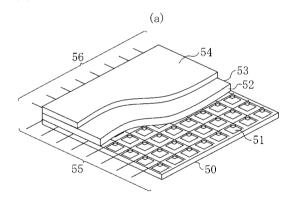

図10(a)は、本実施形態のディスプレイの構成を模式的に示す一部分解斜視図である。図10(a)に示すディスプレイは、プラスティック基板50上にアレイ状に配置された駆動回路51を備えている。駆動回路51は上記の実施形態1から6のいずれかの電界効果トランジスタを含み、画素電極に接続されている。駆動回路51の上には、有機EL層52、透明電極53および保護フィルム54が配置されている。有機EL層52は、電子輸送層、発光層および正孔輸送層といった複数の層が積層された構造を有している。各トランジスタの電極に接続されたX走査電極56とY走査電極55とは、それぞれ、Xドライバ及びYドライバを含む制御回路に接続される。

[0800]

図10(b)は、画素59近傍の回路図である。画素59はスイッチ用トランジスタ57とドライバ用トランジスタ58によって制御される。YドライバからY走査電極55を介してスイッチ用トランジスタ57のソース電極に電圧が印加される。スイッチ用トランジスタ57のドレイン電極とドライバ用トランジスタ58のゲート電極とは電気的に接続されている。ドライバ用トランジスタ58のドレイン電極は、画素59の下部に配置された画素電極(図示せず)に電気的に接続されている。また、ドライバ用トランジスタ58のソース電極には、画素59を発光させるための電圧が印加される。

[0081]

一方、スイッチ用トランジスタ57のゲート電極には、XドライバからX走査電極56を介して画像信号電圧が印加される。画像信号の電圧が印加されたスイッチ用トランジスタ57から、ドライバ用トランジスタ58のゲート電極に電圧が加えられる。これによって、ドライバ用トランジスタ58から画素電極に電圧が加えられる。画素電極と透明電極との間に電圧が加わることによって、画素59部分が発光する。

[0082]

本実施形態のディスプレイは、実施形態 1 から 6 のいずれかの電界効果トランジスタを 駆動回路に用いているので、プラスティック基板の上に信頼性の高い高性能なトランジス タを形成することができ、信頼性の高い駆動を行うことができる。

[0083]

(その他の実施形態)

上記の実施形態は本発明の例示であり、本発明はこれらの例に限定されない。例えば、 半導体ナノワイヤとソース電極 4 3 ・ドレイン電極 4 4 を構成する材料との化学的結合は 合金のみに限られず、共有結合やイオン結合などでも構わない。電界効果トランジスタを 用いたディスプレイは、液晶などでもよい。

【実施例】

[0084]

< 実施例1 >

実施例1は実施形態1の例示である。なお、この実施例は実施形態1の一例であり、本発明はこの実施例に限定されるものではない。

[0085]

図4を参照しながら、本実施例の電界効果トランジスタについて説明する。基板40としては、厚み0.5mmのPETフィルムを用いた。また、ゲート電極41、ソース電極43及びドレイン電極44の材料としては、Agを用いた。また、半導体ナノワイヤ45としてはシリコンで構成されたワイヤを用いた。

[0086]

以下に本実施例のボトムゲート型電界効果トランジスタの製法を説明する。

[0087]

まず半導体ナノワイヤ45の製造方法を説明する。

[0088]

最初に、Si基板上に触媒となる金微粒子コロイドを塗布した。次に前記基板をCVD

10

20

30

40

30

40

50

装置に入れ、ソースガスにシランやジシランを用い、基板温度を400 として C V D 法により半導体ナノワイヤ45を形成した。このとき形成された半導体ナノワイヤ45は、 Siからなり、直径50nm、長さ10~15μmであった。

[0089]

次にこの半導体ナノワイヤ45を溶媒に分散させた。この方法としては、半導体ナノワイヤ45の成長した基板をエタノールに漬け、超音波処理により、基板から半導体ナノワイヤ45を剥離させる方法を用い、それにより半導体ナノワイヤ45が分散したインクを作成した。

[0090]

つぎに、PET基板40上にリソグラフィー法を用いて、ゲート電極41を形成する領域以外にレジストが載るようにパターニングし、レジストをマスクとしてプラスティック基板をエッチングして300nmの深さの窪みを形成した。

[0091]

それから、基板 4 0 のエッチングをした面に、ゲート金属材料である A g を E B 蒸着装置により 3 0 0 n m 堆積させ、その後レジストを除去することによりゲート電極 4 1 を形成した。

[0092]

次に、基板 4 0 のゲート電極 4 1 を形成した面に、ゲート絶縁膜 4 2 として S i N を C V D 装置により 2 0 0 n m 堆積させた。

[0093]

さらに、ゲート絶縁膜42上に前述した半導体ナノワイヤ45が分散したインクをスピ ンコート法により塗布し、半導体ナノワイヤ45をゲート絶縁膜42上に配置した。

[0094]

次に、ゲート絶縁膜42上にリソグラフィー法を用いて、ソース電極43およびドレイン電極44を形成する領域以外にレジストが載るようにパターニングした。この時のソース電極43およびドレイン電極44を形成する領域の大きさは100μm×100μm、ソース電極43とドレイン電極44との距離は30μmとした。そして、レジストをマスクとしてゲート絶縁膜42をドライエッチングにより50nmエッチングした。このエッチングにより、ソース電極43・ドレイン電極44が形成される領域において、半導体ナノワイヤ45とゲート絶縁膜42間に50nmの空隙ができた。

[0095]

この後、ソース電極 4 3 およびドレイン電極 4 4 が形成される領域にAg粒子をインクジェット法により塗布してAgを 3 0 0 n m 堆積させ、ソース電極 4 3 およびドレイン電極 4 4 を形成した。このときインクに用いたAg粒子の平均粒径は 3 n m であった。また、インクの溶媒はトルエンとし、インクの粘度は 5 m P a ・ s であった。また塗布したインクは、180、2時間の焼成を行った。これにより、半導体ナノワイヤ 4 5 は底部 X から上方へ 5 0 n m のところまでソース電極 4 3 およびドレイン電極 4 4 によって覆われた。即ち、ソース電極 4 3 およびドレイン電極 4 4 により覆われた。

[0096]

最後にレジストを除去することにより本実施例のボトムゲート型電界効果トランジスタ を作製した。

[0097]

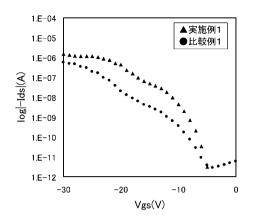

本実施例のボトムゲート型電界効果トランジスタの窒素中におけるトランジスタ特性の一つである電流・電圧特性を図11に示す。また、比較例1として構成材料は本実施例のトランジスタと同じであって、図2に示す構造を有している電界効果トランジスタの特性も同時に図11に示す。この図から、本実施例の電界効果トランジスタは比較例1の電界効果トランジスタよりも広範な電圧領域に亘って電流が増加しており、チャネル層を流れる電流が増加しているということがわかる。つまり、本実施例では、半導体ナノワイヤ45が底部Xから上方へ5mm以上(具体的には50mmのところまで)ソース電極43お

よびドレイン電極44によって覆われているため、プラスティック基板上に窒素中のような不活性雰囲気下において信頼性の高い高性能なトランジスタを製造することができた。

[0098]

< 実施例2 >

実施例2は実施形態2の例示である。なお、この実施例は実施形態2の一例であり、本発明はこの実施例に限定されるものではない。

[0099]

図5を参照しながら、本実施例の電界効果トランジスタについて説明する。基板40としては、厚み0.5mmのPETフィルムを用いた。また、ゲート電極41、ソース電極43及びドレイン電極44材料としては、Agを用いた。また、半導体ナノワイヤ45としてはシリコンで構成されたワイヤを用いた。また、封止膜47材料としては、ポリイミドを用いた。

[0100]

本実施例におけるボトムゲート型電界効果トランジスタの基本構成および製法は、封止膜47を除いて実施例1と同じであるので、封止膜47についてのみ説明する。ゲート電極41、ゲート絶縁膜42、半導体ナノワイヤ45、ソース電極43・ドレイン電極44の順に形成された基板40上に、ポリイミド溶液をスピンコート法により塗布して乾燥させることにより、500nmの厚みに封止膜47を形成した。

[0101]

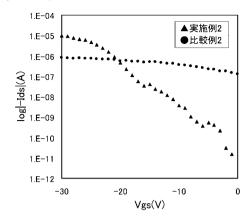

本実施例のボトムゲート型電界効果トランジスタの大気中におけるトランジスタ特性の一つである電流・電圧特性を図12に示す。また、比較例2としてゲート絶縁膜42上に半導体ナノワイヤ45、ソース・ドレイン電極の順に形成し、封止膜を設けない実施例1に示した電界効果トランジスタの特性も同時に図12に示す。図12では図11の窒素中のデータとは異なり大気中のデータを示している。この図から、比較例2ではVgsの絶対値が小さくても電流が流れてしまって、オン電流とオフ電流との比(オンオフ比)が小さいのに対し、本実施例ではVgsの絶対値が大きいときには流れる電流が大きく、Vgsの絶対値が小さくなると流れる電流も小さくなりオンオフ比を大きくできることがわかる。従って、封止膜47を半導体ナノワイヤ45上に設けることにより、大気中の水分や酸素の影響を受けにくいトランジスタ特性が得られたことがわかる。

[0102]

< 実施例3 >

実施例3は実施形態3の例示である。なお、この実施例は実施形態3の一例であり、本発明はこの実施例に限定されるものではない。

[0103]

図6を参照しながら、本実施例3の電界効果トランジスタについて説明する。基板40としては、厚み0.5mmのPETフィルムを用いた。また、ゲート電極41、ソース電極43及びドレイン電極44材料としては、Agを用いた。また、半導体ナノワイヤ35としては表層33がSiO2、芯部32がSiにより構成されたコア・シェル型の半導体ナノワイヤ35を用いた。また、封止膜47材料としては、ポリイミドを用いた。

[0104]

本実施例におけるボトムゲート型電界効果トランジスタの基本構成および製法は、半導体ナノワイヤ 3 5 の構造を除いて実施例 2 とほぼ同じであるので、実施例 2 と異なっている点について説明する。なお、実施例 2 のうち、実施例 1 と同じ部分は実施例 1 の記述を参照する。

[0105]

コア・シェル型の半導体ナノワイヤ35は以下の通りに作製した。

[0106]

まず、Si基板上に触媒となる金微粒子コロイドを塗布した。次に前記基板をCVD装置に入れ、ソースガスにシランやジシランを用い、基板温度を400 としてCVD法によりSiよりなる半導体ナノワイヤを形成した。この時点では、半導体ナノワイヤはコア

10

20

30

40

30

40

50

・シェル構造ではない。

# [0107]

次に、この半導体ナノワイヤが成長した基板を反応器に入れて、酸素雰囲気のラピットサーマルプロセッシングにより1100 にて熱酸化させてコア・シェル型の半導体ナノワイヤ45を形成した。この熱酸化により形成されたコア・シェル型半導体ナノワイヤ35は、長さ10~15μm、直径80nm、芯部32の直径50nm、表層33の厚みが15nmであった。

#### [0108]

次にこのコア・シェル型半導体ナノワイヤ35を溶媒に分散させた。この方法として、 半導体ナノワイヤ35の成長した基板をエタノールに漬け、超音波処理により、基板から コア・シェル型半導体ナノワイヤ35を剥離させる方法を用い、半導体ナノワイヤ35が 分散しているインクを作製した。

#### [0109]

それから、実施例 1 で説明した製造方法に従って作製したゲート絶縁膜 4 2 上に前述した半導体ナノワイヤインクをスピンコート法により塗布し、コア・シェル型半導体ナノワイヤ 3 5 をゲート絶縁膜 4 2 上に配置した。このとき、ゲート絶縁膜 4 2 は C V D 法によって形成されただけで、エッチングはされていない状態であった。

#### [0110]

次に、半導体ナノワイヤ35上にリソグラフィー法を用いて、ソース電極43およびドレイン電極44を形成する領域以外にレジストが載るようにパターニングした。そして、レジストをマスクとしてソース・ドレイン電極領域におけるコア・シェル型半導体ナノワイヤ35の表層33をフッ酸により取り除いた。

# [0111]

この後に、実施例1と同様に、ソース電極43およびドレイン電極44を形成した。最後にレジストを除去し、実施例2と同様にポリイミドを塗布し封止膜47を形成することにより本実施例のボトムゲート型電界効果トランジスタを作製した。

# [0112]

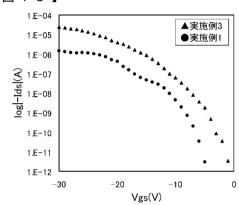

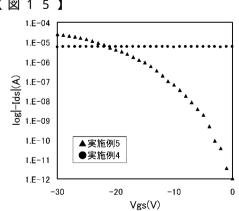

本実施例のボトムゲート型電界効果トランジスタの窒素中におけるトランジスタ特性の一つである電流・電圧特性を図13に示す。また、比較として実施例1の電界効果トランジスタの特性も同時に図13に示す。この図から、コア・シェル型半導体ナノワイヤ35をチャネルとして用いることにより、大気中の水分や酸素の影響を受けにくく、かつ、ゲート絶縁膜42をエッチングすることなく、実施例1よりも良質なトランジスタ特性が得られたことがわかる。

# [0113]

< 実施例4 >

実施例4は実施形態4の例示である。なお、この実施例は実施形態4の一例であり、本発明はこの実施例に限定されるものではない。

#### [0114]

図7を参照しながら、本実施例の電界効果トランジスタについて説明する。基板40としては、厚み0.7mmのガラスを用いた。また、ゲート電極41材料としてはA1、ソース電極43及びドレイン電極44材料としては、Niを用いた。また、半導体ナノワイヤ45としてはシリコンで構成されたワイヤを用いた。なお、本実施例は半導体ナノワイヤ45の表面の一部がソース電極43およびドレイン電極44の構成材料と化学的結合をしている点が実施例1と異なっており、その他の点は実施例1とほぼ同じであるので、実施例1と異なっている点を中心に説明をする。

# [0115]

本実施例では実施例 1 と同様に、ソース電極 4 3 及びドレイン電極 4 4 が半導体ナノワイヤ 4 5 表面を底部から上端まで覆うように形成されている。さらに、ソース電極 4 3 及びドレイン電極 4 4 と半導体ナノワイヤ 4 5 とは化学的に結合してシリサイドである合金部 4 8 が形成されており、ソース電極 4 3 ・ドレイン電極 4 4 のエネルギー準位と半導体

20

30

40

50

ナノワイヤ 4 5 とのエネルギー準位の間に中間準位が形成されている。このため、ソース電極 4 3 ・ドレイン電極 4 7 とチャネル層 4 6 との電気的に接触している接触面積が大きくなっているともに、合金部 4 8 が存在しているためソース電極 4 3 及びドレイン電極 4 4 と半導体ナノワイヤ 4 5 との間の電荷障壁が小さくなっており、実施例 1 よりもトランジスタ特性が向上している。

[0116]

以下、本実施例のボトムゲート型電界効果トランジスタの製法を説明する。

[0117]

半導体ナノワイヤ 4 5 および半導体ナノワイヤインクの製法は、実施例 1 と同じである。まず、リソグラフィー法を用いてガラス基板 4 0 上に、ゲート電極 4 1 を形成する領域以外にレジストが載るようにパターニングした。

[ 0 1 1 8 ]

それから、ガラス基板 4 0 のパターニング面にゲート金属材料である A 1 を E B 蒸着装置により 3 0 0 n m の厚みで堆積させ、その後レジストを除去することによりゲート電極 4 1 を形成した。

[0119]

次に、実施例1と同様にして、ゲート絶縁膜42の形成、エッチング、半導体ナノワイヤ45の配置を行った。

[0120]

それから、リソグラフィー法を用いて半導体ナノワイヤ45が載った基板40上に、ソース電極43およびドレイン電極44を形成する領域以外にレジストが載るようにパターニングした。この時のソース電極43およびドレイン電極44を形成する領域の大きさは100μm×100μm、ソース電極43とドレイン電極44との距離は30μmとした。その後、ソース電極43・ドレイン電極44を形成する領域にNiをEB蒸着装置により厚み300mm堆積させ、それからレジストを除去することにより、ソース電極43およびドレイン電極44を形成した。このとき、電極材料蒸発源に対し、基板40の角度を、半導体ナノワイヤ45が延びる方向に延びる基板40表面の二等分線を回転軸として変えることにより、半導体ナノワイヤ45の底部×にもNi電極が回りこみ形成されるようにした。

[0121]

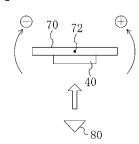

図17に蒸着時の基板40と電極材料蒸発源80との位置関係を示す。Niを堆積させるために、まず基板40を基板ステージ70に固定する。このとき半導体ナノワイヤ45が延びる方向と基板ステージ70の回転軸72とが平行になるように、即ち上記基板表面の二等分線と基板ステージ70の回転軸72とが平行になるように基板40を固定する。この固定時には基板40の蒸着面と、電極材料蒸発源80と回転軸72とを結ぶ線とが直交している。それからNiの堆積時には、回転軸72を軸として基板ステージ70を回転させてNi電極が半導体ナノワイヤ45の底部Xにも回り込むようにした。この時の基板ステージ70の回転角は、固定時の状態を0度としたときに、図の反時計回り方向(+方向)に87度まで、時計周り(-方向)に87度まで(-87度)の間を変化していった

[ 0 1 2 2 ]

最後に、電界効果トランジスタを作りこんだ基板40を窒素雰囲気のラピットサーマルプロセッシングにより500 にて熱処理を施し、半導体ナノワイヤ45とソース電極43・ドレイン電極44とを合金化させ、本実施例のボトムゲート型電界効果トランジスタを作製した。

[ 0 1 2 3 ]

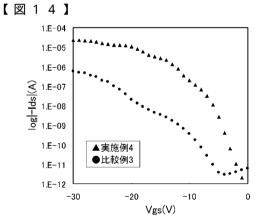

本実施例のボトムゲート型電界効果トランジスタの窒素中におけるトランジスタ特性の一つである電流・電圧特性を図14に示す。比較例3として構成材料は本実施例のトランジスタと同じであって、図2に示す構造を有している電界効果トランジスタの特性も同時に図14に示す。なお、比較例1と比較例3は同じものである。

20

30

40

50

#### [0124]

この図から、本実施例の電界効果トランジスタは比較例3の電界効果トランジスタより も広範な電圧領域に亘って電流が増加しており、チャネル層を流れる電流が増加している ことがわかり、窒素中のような不活性雰囲気下では高いトランジスタ特性を有しているこ とがわかる。

#### [0125]

< 実施例5 >

実施例5は実施形態5の例示である。なお、この実施例は実施形態5の一例であり、本発明はこの実施例に限定されるものではない。

#### [0126]

図8を参照しながら、本実施例の電界効果トランジスタについて説明する。本実施例は 封止膜47が存すること以外は実施例4と同じであるので、実施例4と異なっている点を 主に説明をする。

# [0127]

封止膜47材料としては、ポリイミドを用いた。そして、基板40上にゲート電極41、ゲート絶縁膜42、半導体ナノワイヤ45、ソース電極43・ドレイン電極44の順に形成・配置されて、窒素中において500 で熱処理を施された電界効果トランジスタ上に、ポリイミド溶液をスピンコート法を用いて塗布し、乾燥させることにより500nmの厚みの封止膜47を形成した。

#### [0128]

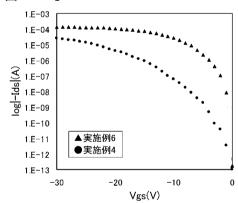

本実施例のボトムゲート型電界効果トランジスタの大気中におけるトランジスタ特性の一つである電流・電圧特性を図15に示す。また、比較として封止膜47を設けていない実施例4の電界効果トランジスタの特性も同時に図15に示す。なお、実施例4に係るトランジスタの図14に示すトランジスタ特性は、窒素中における特性であるので、大気中における図15に示す特性とは異なっている。実施例2で説明したように、図15から、封止膜47を半導体ナノワイヤ45上に設けることにより、大気中の水分や酸素の影響を受けにくいトランジスタ特性が得られたことがわかる。

#### [0129]

< 実施例6 >

実施例6は実施形態6の例示である。なお、この実施例は実施形態6の一例であり、本発明はこの実施例に限定されるものではない。

# [0130]

図9を参照しながら、本実施例の電界効果トランジスタについて説明する。なお、本実施例は、半導体ナノワイヤ35がコア・シェル型の構造を有している点以外は実施例5と同じであるので、実施例5と異なっている点を主に説明を行う。

#### [0131]

本実施例におけるボトムゲート型電界効果トランジスタの基本構成および製法は実施例5とほぼ同じである。なお、実施例5の構成及び製法は、実施例1乃至4の構成と製法を参照しているので、本実施例においても実施例1乃至4の構成と製法を参照する。また、コア・シェル型半導体ナノワイヤ35および半導体ナノワイヤインクの製法は実施例3と同じである。

#### [0132]

本実施例の電界効果トランジスタの製造は、まず実施例4と同様にして基板40上にゲート絶縁膜42を形成することからスタートした。このゲート絶縁膜42上に前述した半導体ナノワイヤインクをスピンコート法により塗布し、コア・シェル型の半導体ナノワイヤ35をゲート絶縁膜42上に配置した。

#### [0133]

次に、半導体ナノワイヤ35上にリソグラフィー法を用いて、ソース電極43およびドレイン電極44を形成する領域以外にレジストが載るようにパターニングした。この時のソース電極43およびドレイン電極44を形成する領域の大きさは100μm×100μ

m、ソース電極43とドレイン電極44との距離は30µmとした。

[0134]

それから、レジストをマスクとしてソース電極 4 3 ・ドレイン電極 4 4 が形成される領域における半導体ナノワイヤ 3 5 の表層 3 3 をフッ酸により取り除いた。

[0135]

つぎに、実施例 4 と同様にして、ソース電極 4 3 およびドレイン電極 4 4 を形成し、さらに実施例 5 と同様にして封止膜 4 7 を形成することにより本実施例のボトムゲート型電界効果トランジスタを作製した。

[0136]

本実施例のボトムゲート型電界効果トランジスタの窒素中におけるトランジスタ特性の一つである電流・電圧特性を図16に示す。また、比較として封止膜47を設けておらず、半導体ナノワイヤ45もコア・シェル型ではない実施例4の電界効果トランジスタの特性も同時に図16に示す。図16から、コア・シェル型半導体ナノワイヤ35をチャネルとして設けることにより、大気中の水分や酸素の影響を受けにくく、かつ、ゲート絶縁膜42をエッチングすることがないため良質なトランジスタ特性が得られたことがわかる。

【産業上の利用可能性】

[0137]

以上説明したように、本発明に係る電界効果トランジスタは、ソース電極及びドレイン電極とチャネル層との間の電荷注入障壁が低く、フレキシブルディスプレイやフレキシブル基板を用いた電子デバイスやマイクロデバイス等に用いるトランジスタとして有用である。

【図面の簡単な説明】

[0138]

【図1】(a)は半導体ナノワイヤを用いた電界効果トランジスタの一例の断面図、(b)は(a)のA-A線断面図である。

【図2】(a)は半導体ナノワイヤを用いた電界効果トランジスタの別の例の断面図、(b)は(a)のA-A線断面図である。

【図3】コア・シェル型の半導体ナノワイヤの横断面図である。

【図4】(a)は実施形態1に係る電界効果トランジスタの断面図、(b)は(a)のA-A線断面図である。

【図5】(a)は実施形態2に係る電界効果トランジスタの断面図、(b)は(a)のA-A線断面図である。

【図 6 】(a)は実施形態 3 に係る電界効果トランジスタの断面図、(b)は(a)の A - A 線断面図である。

【図7】(a)は実施形態4に係る電界効果トランジスタの断面図、(b)は(a)のA- A線断面図である。

【図8】(a)は実施形態 5 に係る電界効果トランジスタの断面図、(b)は(a)のA- A 線断面図である。

【図9】(a)は実施形態 6 に係る電界効果トランジスタの断面図、(b)は(a)の A-A 線断面図である。

【図10】(a)は実施形態7における有機 E L ディスプレイを模式的に示す一部分解斜視図、(b)は画素駆動用トランジスタの回路図である。

【図11】実施例1における電界効果トランジスタのトランジスタ特性図である。

【図12】実施例2における電界効果トランジスタのトランジスタ特性図である。

【 図 1 3 】 実 施 例 3 に お け る 電 界 効 果 ト ラ ン ジ ス タ の ト ラ ン ジ ス タ 特 性 図 で あ る 。

【 図 1 4 】 実 施 例 4 に お け る 電 界 効 果 ト ラ ン ジ ス タ の ト ラ ン ジ ス タ 特 性 図 で あ る 。

【 図 1 5 】 実 施 例 5 に お け る 電 界 効 果 ト ラ ン ジ ス タ の ト ラ ン ジ ス タ 特 性 図 で あ る 。

【図16】実施例6における電界効果トランジスタのトランジスタ特性図である。

【 図 1 7 】 実 施 例 6 に お け る 蒸 着 時 の 基 板 ス テ ー ジ の 回 転 を 示 す 図 で あ る 。

【符号の説明】

50

40

20

| [ 0 1 3 9 ] |               |    |

|-------------|---------------|----|

| 4 1         | ゲート電極         |    |

| 4 2         | ゲート 絶 縁 膜     |    |

| 4 3         | ソース電極         |    |

| 4 4         | ドレイン電極        |    |

| 3 5 、 4 5   | 半導体ナノワイヤ      |    |

| 4 6         | チャネル層         |    |

| 3 2         | 芯 部           |    |

| 3 3         | 表層            |    |

| 4 0 、 5 0   | 基 板           | 10 |

| 4 7         | 封 止 膜         |    |

| 4 8         | 合金部(化学的結合の部分) |    |

| 5 1         | 駆動回路          |    |

| 5 2         | 有機EL層         |    |

| 5 3         | 透明電極          |    |

| 5 4         | 保護フィルム        |    |

| 5 5         | X 走査電極        |    |

| 5 6         | Y 走査電極        |    |

| 5 7         | スイッチ用トランジスタ   |    |

| 5 8         | ドライバ用トランジスタ   | 20 |

| 5 9         | 画素            |    |

# 【図1】

# (a) A 15 13 12 A 14 12 A A

# 【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図16】

【図15】

【図17】

#### フロントページの続き

(51) Int.CI. F I テーマコード (参考)

H 0 1 L 21/28 3 0 1 B H 0 1 L 29/50 M

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 原田 健史

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 竹内 孝之

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 七井 識成

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 川島 孝啓

大阪府門真市大字門真1006番地 松下電器産業株式会社内

F ターム(参考) 4M104 AA01 AA02 AA03 AA04 AA05 AA06 AA09 AA10 BB02 BB04

BB05 BB06 BB07 BB08 BB09 BB14 EE03 EE17 FF06 GG08

HH14

5F110 AA03 BB01 CC03 CC07 DD01 DD02 DD05 EE01 EE02 EE03

EE04 EE43 EE44 FF02 FF03 FF09 FF23 FF29 GG02 GG03

GG04 GG22 GG24 GG25 GG28 GG42 GG44 HK01 HK02 HK03

HK04 HK32 HK33 HK42 HM02 HM05 HM17 NN02 NN23 NN24

NN27 NN35 NN36 QQ14