## UK Patent Application (19)GB (11)2593485

29.09.2021

2004257.8 (21) Application No:

(22) Date of Filing: 24.03.2020

(71) Applicant(s): **ARM Limited**

(Incorporated in the United Kingdom) 110 Fulbourn Road, Cambridge, Cambridgeshire, CB1 9NJ, United Kingdom

(72) Inventor(s): Jason Parker Yuval Elad

(74) Agent and/or Address for Service:

D Young & Co LLP 120 Holborn, LONDON, EC1N 2DY, United Kingdom (51) INT CL:

G06F 12/14 (2006.01) G06F 21/57 (2013.01)

(56) Documents Cited:

US 20190042324 A1 US 20140380425 A1 US 20130283017 A1 US 20050268095 A1

US 20040158727 A1

ARM, "Isolation using virtualization in the Secure world", 2018

(58) Field of Search:

INT CL G06F

Other: WPI, EPODOC, INTERNET

- (54) Title of the Invention: Apparatus and method using plurality of physical address spaces Abstract Title: Trust execution environment with root domain with own physical address space

- (57) A trust execution environment where domains are associated with Physical Address Spaces (PASs) and include a root domain for managing switching between the domains. The root domain has its own separate PAS. A root domain page table entry may include protection bits that provide memory protection allowing to select PAS of the other domains. In this way, the accessibility of the other domains may be based on accessibility permissions set by the root domain (see table, p.33). The PAS may be selected based on a domain of operation (e.g. secure, nonsecure, realm or root). Transactions remain tagged with a PAS TAG as they propagate throughout the system 24, 8 until they read a Point of Physical Aliasing (PoPA) 60 at a completer side of the system (see fig 3). At the PoPA, the PAS TAG is stripped and the address changes from a Logical Physical Address to a System Physical Address.

27 01 21

正 の 4

FIG. 7

FIG. 8

FIG. 10

FIG. 12

## APPARATUS AND METHOD USING PLURALITY OF PHYSICAL ADDRESS SPACES

The present technique relates to the field of data processing.

5

10

15

20

25

30

35

A data processing system may have address translation circuitry to translate a virtual address of memory access request to a physical address corresponding to a location to be accessed in a memory system.

At least some examples provide an apparatus comprising: processing circuitry to perform processing in one of at least three domains; and address translation circuitry to translate a virtual address of a memory access performed from a current domain to a physical address in one of a plurality of physical address spaces selected based at least on the current domain; in which: the at least three domains include a root domain for managing switching between a plurality of other domains of the at least three domains; and the plurality of physical address spaces include a root physical address space associated with the root domain, separate from physical address spaces associated with the plurality of other domains.

At least some examples provide a data processing method comprising: performing processing in one of at least three domains; and translating a virtual address of a memory access performed from a current domain to a physical address in one of a plurality of physical address spaces selected based at least on the current domain; in which: the at least three domains include a root domain for managing switching between a plurality of other domains of the at least three domains; and the plurality of physical address spaces include a root physical address space associated with the root domain, separate from physical address spaces associated with the plurality of other domains.

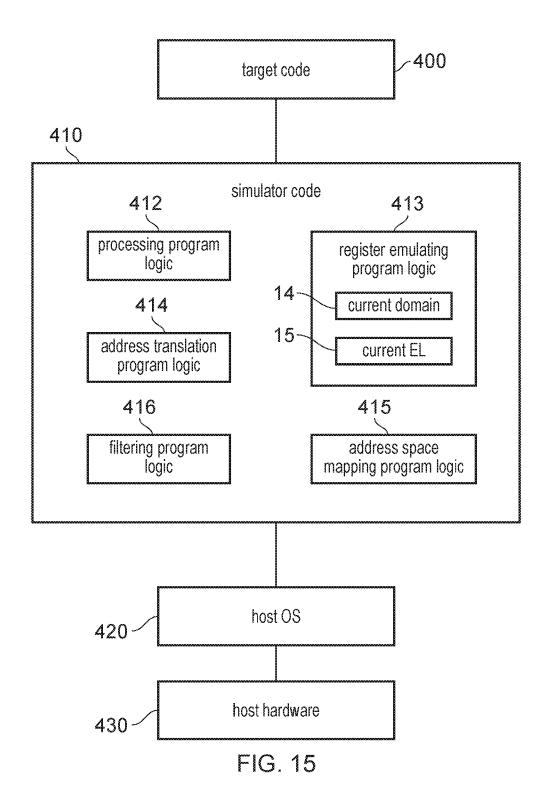

At least some examples provide a computer program for controlling a host data processing apparatus to provide an instruction execution environment for execution of target code; the computer program comprising: processing program logic to simulate processing of the target code in one of at least three domains; and address translation program logic to translate a virtual address of a memory access performed from a current domain to a physical address in one of a plurality of simulated physical address spaces selected based at least on the current domain; in which: the at least three domains include a root domain for managing switching between a plurality of other domains of the at least three domains; and the plurality of simulated physical address spaces include a root simulated physical address space associated with the root domain, separate from simulated physical address spaces associated with the plurality of other domains.

At least some examples provide a computer-readable storage medium storing the computer program described above. The computer-readable storage medium may be a non-transitory storage medium or a transitory storage medium.

Further aspects, features and advantages of the present technique will be apparent from the following description of examples, which is to be read in conjunction with the accompanying drawings, in which:

Figure 1 illustrates an example of a data processing apparatus;

5

10

15

20

25

30

35

Figure 2 illustrates a number of domains in which processing circuitry can operate;

Figure 3 illustrates an example of a processing system supporting granule protection lookups;

Figure 4 schematically illustrates aliasing of a number of physical address spaces onto a system physical address space identifying locations in the memory system;

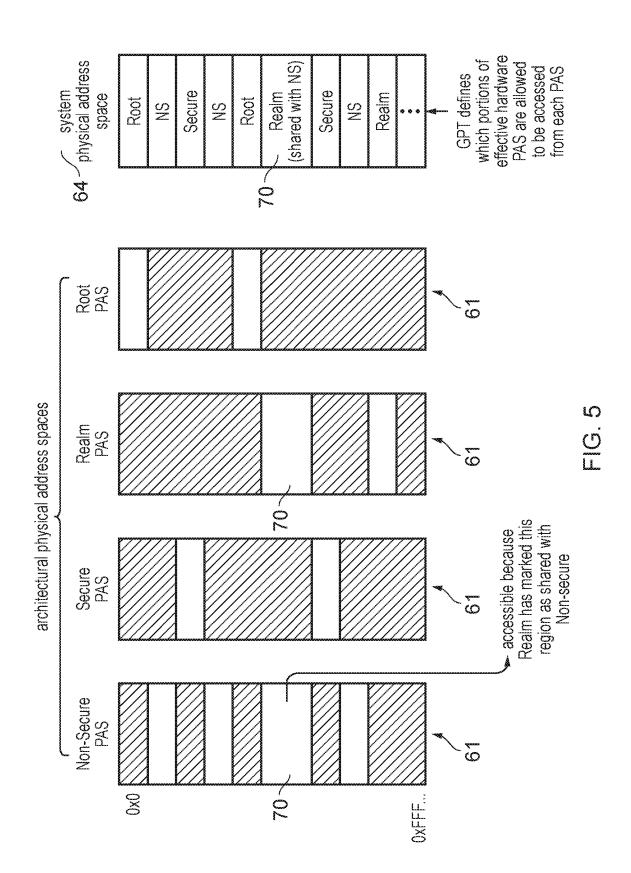

Figure 5 illustrates an example of partitioning the effective hardware physical address space so that different architectural physical address spaces have access to respective portions of the system physical address space;

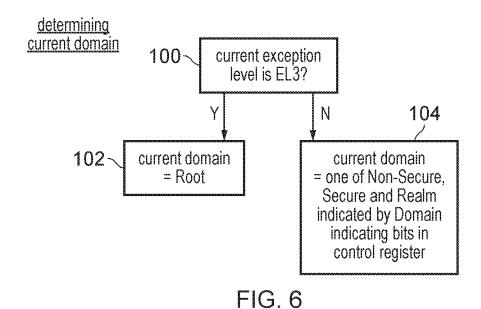

Figure 6 is a flow diagram illustrating a method of determining the current domain of operation of the processing circuitry;

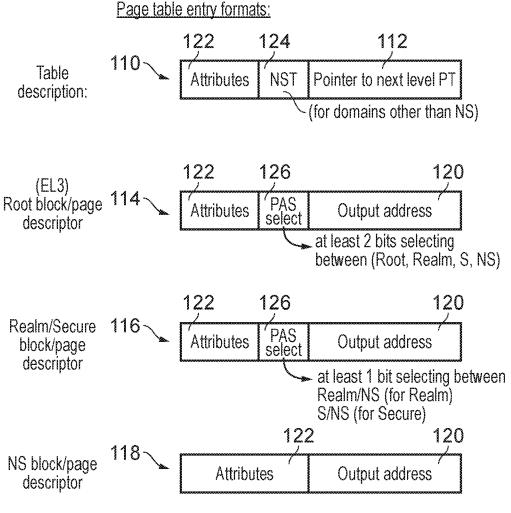

Figure 7 shows examples of page table entry formats for page table entries used for translating virtual addresses to physical addresses;

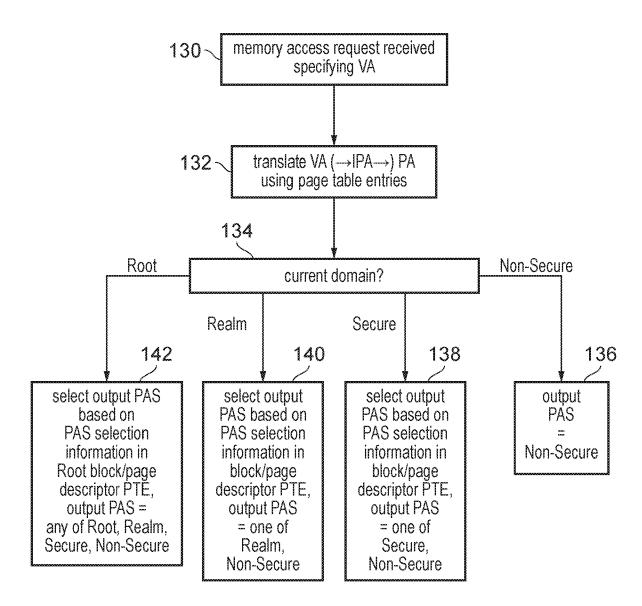

Figure 8 is a flow diagram showing a method of selecting a physical address space to be accessed by a given memory access request;

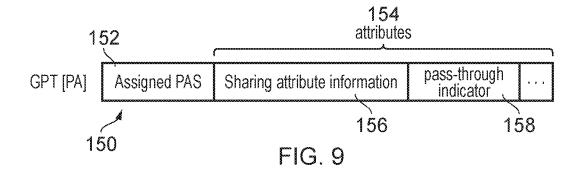

Figure 9 illustrates an example of an entry of a granule protection table for providing granule protection information indicating which physical address spaces are allowed to access a given physical address;

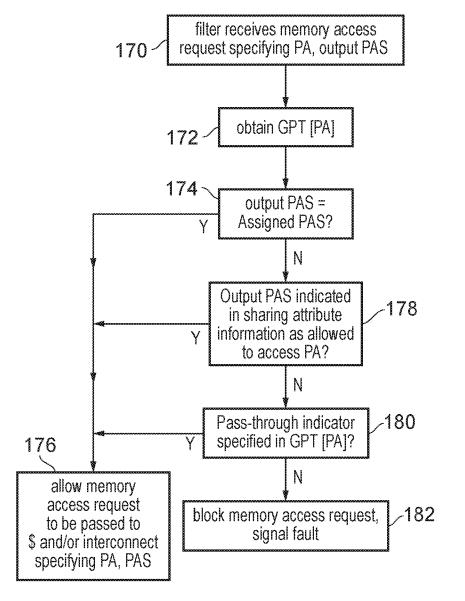

Figure 10 is a flow diagram showing a method of performing a granule protection lookup;

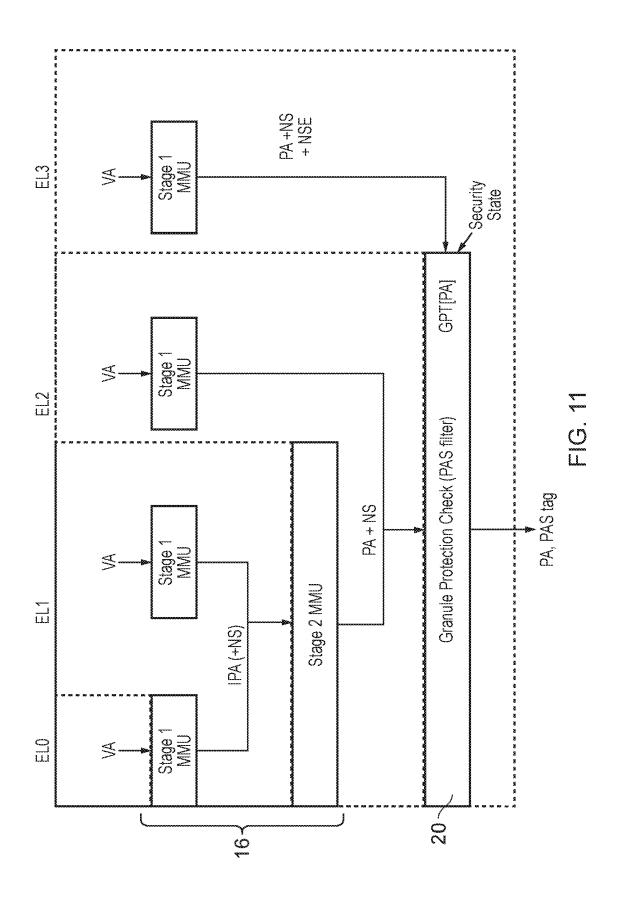

Figure 11 illustrates a number of stages of address translation and granule protection information filtering:

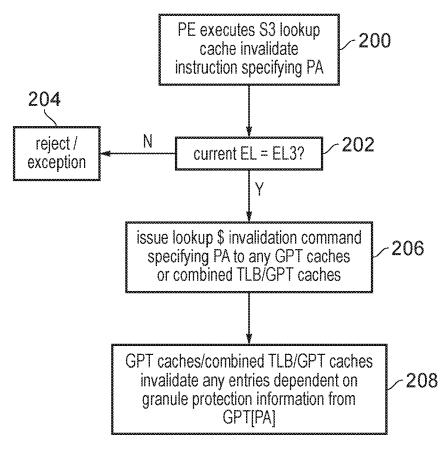

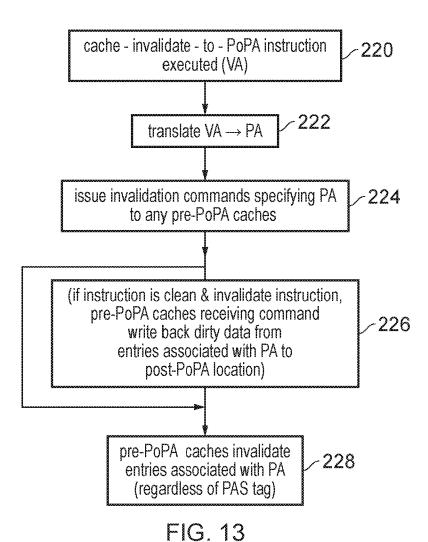

Figure 12 is a flow diagram illustrating processing of a cache invalidation instruction;

Figure 13 is a flow diagram illustrating processing of a cache-invalidate-to-PoPA (point of physical aliasing) instruction;

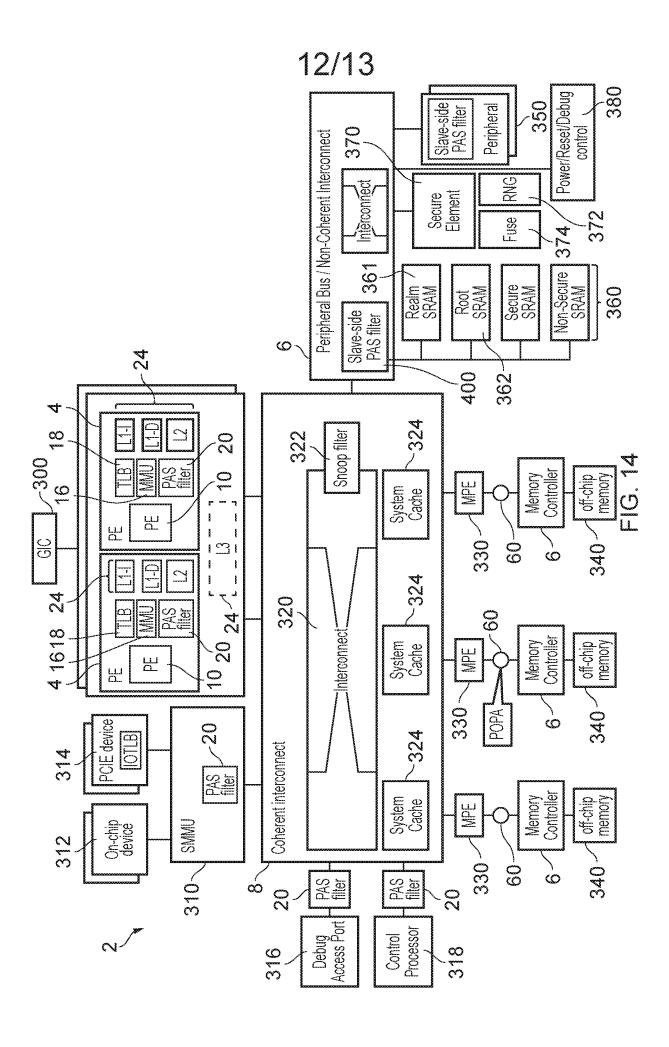

Figure 14 illustrates an example of a data processing system; and

Figure 15 shows a simulator example that may be used.

## Controlling Access to Physical Address Spaces

Data processing systems may support use of virtual memory, where address translation circuitry is provided to translate a virtual address specified by a memory access request into a physical address associated with a location in a memory system to be accessed. The mappings between virtual addresses and physical addresses may be defined in one or more page table structures. The page table entries within the page table structures could also define some access permission information which may control whether

a given software process executing on the processing circuitry is allowed to access a particular virtual address.

In some processing systems, all virtual addresses may be mapped by the address translation circuitry onto a single physical address space which is used by the memory system to identify locations in memory to be accessed. In such a system, control over whether a particular software process can access a particular address is provided solely based on the page table structures used to provide the virtual-to-physical address translation mappings. However, such page table structures may typically be defined by an operating system and/or a hypervisor. If the operating system or the hypervisor is compromised then this may cause a security leak where sensitive information may become accessible to an attacker.

5

10

15

20

25

30

35

Therefore, for some systems where there is a need for certain processes to execute securely in isolation from other processes, the system may support operation in a number of domains and a number of distinct physical address spaces may be supported, where for at least some components of the memory system, memory access requests whose virtual addresses are translated into physical addresses in different physical address spaces are treated as if they were accessing completely separate addresses in memory, even if the physical addresses in the respective physical address spaces actually correspond to the same location in memory. By isolating accesses from different domains of operation of the processing circuitry into respective distinct physical address spaces as viewed for some memory system components, this can provide a stronger security guarantee which does not rely on the page table permission information set by an operating system or hypervisor.

The processing circuitry may support processing in a root domain which is responsible for managing switching between other domains in which the processing circuitry can operate. By providing a dedicated root domain for controlling the switching, this can help to maintain security by limiting the extent to which code executing in one domain can trigger a switch to another domain. For example the root domain may perform various security checks when a switch of domain is requested.

Hence, the processing circuitry may support processing being performed in one of at least three domains: the root domain, and at least two other domains. Address translation circuitry may translate a virtual address of a memory access performed from a current domain to a physical address in one of the plurality of physical address spaces selected based at least on the current domain.

In the examples described below, the plurality of physical address spaces include a root physical address space which is associated with the root domain, separate from physical address spaces associated with the other domains. Hence, rather than using one of the physical address spaces associated with one of the other domains, the root domain

has its own physical address space allocated to it. By providing a dedicated root physical address space isolated from physical address spaces associated with the other domains, this can provide a stronger guarantee of security for the data or code associated with the root domain, which may be regarded as the most critical for security given that it will manage entry into other domains. Also, the provision of a dedicated root physical address space distinguished from the physical address spaces of other domains can simplify system development because it may simplify allocation of physical addresses within the respective physical address spaces to particular units of hardware memory storage. For example, by identifying a separate root physical address space it can be simpler for the data or program code associated with the root domain to be preferentially stored in a protected memory on-chip rather than in a less secure off-chip memory, with less overhead in determining the portions associated with the root domain than if the root domain's code or data was stored in a common address space shared with another domain.

The root physical address space may be exclusively accessible from the root domain. Hence, when the processing circuitry is operating in one of the other domains, the processing circuitry may not be able to access the root physical address space. This improves security by ensuring that code executing in one of the other domains cannot tamper with data or program code relied upon by the root domain for managing switching between domains or for controlling what rights the processing circuitry has when in one of the other domains.

On the other hand, all of the plurality of physical address spaces may be accessible from the root domain. As the code executing in the root domain has to be trusted by any party providing code operating in one of the other domains, as the root domain code will be responsible for the switching into that particular domain in which that party's code is executing, then inherently the root domain can be trusted to access any of the physical address spaces. Making all of the physical address spaces accessible from the root domain allows to perform functions such as transitioning memory regions into and out of the domain, copying code and data into a domain e.g. during boot, and providing services to that domain.

The address translation circuitry may restrict which physical address spaces are accessible depending on the current domain. When a particular physical address space is accessible to the current domain, this means that it is possible for the address translation circuitry to translate a virtual address specified for a memory access issued from the current domain into a physical address in that particular physical address space. This does not necessarily imply that the memory access would be allowed, as even if a particular memory access can have its virtual address translated into a physical address of a particular physical address space, there may be further checks performed to determine whether that physical address is actually allowed to be accessed within that particular physical address space.

This is discussed further below with reference to granule protection information which defines the partitioning of the physical addresses between respective physical address spaces. Nevertheless, by restricting which subset of physical address spaces are accessible to the current domain, this can provide stronger guarantees of security.

5

10

15

20

25

30

35

In some examples the processing circuitry may support two additional domains, in addition to the root domain. For example, the other domains may comprise a secure domain associated with a secure physical address space and a less secure domain associated with a less secure physical address space. The less secure physical address space may be accessible from each of the less secure domain, the secure domain and the root domain. The secure physical address space may be accessible from the secure domain and the root domain but may be inaccessible from the less secure domain. The root domain can be accessible to the root domain but may be inaccessible to the less secure domain and the secure domain. Hence, this allows code executing in the secure domain to have its code or data protected from access by code operating in the less secure domain with stronger security guarantees than if page tables were used as the sole security controlling mechanism. For example, portions of code which require stronger security can be executed in the secure domain managed by a trusted operating system distinct from a non-secure operating system operating in the less secure domain. An example of a system supporting such secure and less secure domains may be processing systems operating according to a processing architecture which supports the TrustZone® architecture feature provided by Arm® Limited of Cambridge, UK. In conventional TrustZone® implementations the monitor code for managing switching between secure and less secure domains uses the same secure physical address space that is used by the secure domain. In contrast, by providing a root domain for managing switching of other domains and assigning a dedicated root physical address space for use by the root domain as described above, this helps to improve security and simplify system development.

However, in other examples, the other domains could include further domains, for example at least three other domains in addition to the root domain. These domains could include the secure domain and the less secure domain discussed above, but may also include at least one further domain associated with a further physical address space. The less secure physical address space may also be accessible from the further domain, while the further physical address space may be accessible from the further domain and the root domain but may be inaccessible from the less secure domain. Hence, similar to the secure domain, the further domain may be considered more secure than the less secure domain and allow further partitioning of code into respective worlds associated with distinct physical address spaces to limit their interaction.

In some examples the respective domains may have a hierarchy so that they are associated with increasing levels of privilege as the system ascends from the less secure domain, through the secure and further domains to the root domain, with the further domain being considered more privileged than the secure domain and so having access to the secure physical address space.

5

10

15

20

25

30

35

However, increasingly there is a desire for a software provider to be provided with a secure computing environment which limits the need to trust other software providers associated with other software executing on the same hardware platform. For example, there may be a number of uses in fields such as mobile payment and banking, enforcement of anti-cheating or piracy mechanisms in computer gaming, security enhancements for operating system platforms, secure virtual machine hosting in a cloud system, confidential computing, etc., where a party providing software code may not be willing to trust the party providing an operating system or hypervisor (components which might previously have been considered trusted). In a system supporting secure and less secure domains with respective physical address spaces, such as systems based on the TrustZone® architecture described above, with the increasing take-up of secure components operating in a secure domain, the set of software typically operating in the secure domain has grown to include a number of pieces of software which may be provided from a different number of software providers, including parties such as an original equipment manufacturer (OEM) who assembles a processing device (such as a mobile phone) from components including a silicon integrated circuit chip provided by a particular silicon provider, an operating system vendor (OSV) who provides the operating system running on the device, and a cloud platform operator (or cloud host) who maintains a server farm providing server space for hosting virtual machines on the cloud. Hence, if the domains were implemented in a strict order of increasing privilege, then there may be a problem because an application provider providing application-level code which wishes to be provided with a secure computing environment may not wish to trust a party (such as the OSV, OEM or cloud host) who might traditionally have provided software executing the secure domain, but equally the parties providing the code operating in a secure domain are unlikely to wish to trust application providers to provide code operating at a higher privilege domain which is given access to data associated with less privileged domains. Therefore, it is recognised that a strict hierarchy of domains of successively increasing privilege may not be appropriate.

Hence, in the more detailed examples below, the further domain may be considered to be orthogonal to the secure domain. While the further domain and the secure domain can each access the less secure physical address space, the further physical address space associated with the further domain is inaccessible from the secure domain, while the secure physical address space associated with the secure domain is inaccessible from the further

domain. The root domain can still access the physical address spaces associated with both the secure domain and the further domain.

Hence, with this model the further domain (an example of which is the realm domain described in the examples below) and the secure domain have no dependencies upon each other and so do not need to trust each other. The secure domain and the further domain only need to trust the root domain, which is inherently trusted as it is managing the entry into the other domains.

5

10

15

20

25

30

35

While the examples below describe a single instance of the further domain (realm domain), it will be appreciated that the principle of a further domain orthogonal to the secure domain can be extended to provide multiple further domains so that each of the secure domain and at least two further domains can access the less secure physical address space, cannot access the root physical address space, and cannot access the physical address spaces associated with each other.

The less secure physical address space may be accessible from all of the domains supported by the processing circuitry. This is useful because it facilitates sharing of data or program code between software executing in different domains. If a particular item of data or code is to be accessible in different domains, then it can be allocated to the less secure physical address space so that it can be accessed from any of the domains.

When translating a virtual address to a physical address, the address translation circuitry may perform the translation based on at least one page table entry. At least when the current domain is one of a subset of the at least three domains supported by the processing circuitry, the address translation circuitry may select which of the physical address spaces is to be used as the physical address space into which the physical address is translated for a given memory access, based on the current domain and physical address space selection information specified in the at least one page table entry used for the translation of the virtual address to the physical address. Hence, information defined within the page table structure may influence which physical address space is selected for a given memory access when issued from the current domain. For some domains, this selection based on physical address space selection information specified in the page table entry may not be necessary. For example, if the current domain is the less secure domain described above, then as all the other address spaces may be inaccessible to the less secure domain, the less secure physical address space may be selected regardless of any information specified in the at least one page table entry used for the address translation.

However for other domains, it is possible for that domain to select between two or more different physical address spaces. Hence, for these domains it can be useful to define information in a page table entry for a given block of addresses indicating which physical address space should be used for that access, so that different parts of the virtual address

space seen by a given piece of software can be mapped onto different physical addresses.

For example when the current domain is the root domain, the address translation circuitry may translate the virtual address to the physical address based on a root-domain page table entry for which the physical address space selection information comprises at least two bits of physical address space selection information for selecting between at least three physical address spaces accessible from the root domain. For example, in an implementation supporting the root domain, less secure domain and secure domain, the physical address space selection information in the root-domain page table entry could select between any of these three physical address spaces. In an implementation also having at least one further domain, the physical address space selection information may select between any of the root physical address space, secure physical address space, less secure physical address space and at least one further physical address space.

5

10

15

20

25

30

35

On the other hand, when the current domain is the secure domain or the further domain, the choice of physical address spaces may be more restricted and so fewer bits of physical address space selection information may be needed compared to the root domain. For example, in the secure domain the physical address space selection information may select between the secure address space and the less secure address space (as the root physical address space and further physical address space may be inaccessible). When the current domain is the further domain, the physical address space selection information may be used to select between the further physical address space and the less secure physical address space, as the secure physical address space and the root physical address space may be inaccessible. For page table entries used to select the physical address space to be used when the current domain is the secure domain or the further domain, the physical address space selection indicator used to make this selection may be encoded at a same position within the at least one page table entry regardless of whether the current domain is the secure domain or the further domain. This makes encoding of the page table entries more efficient and allows hardware for interpreting that portion of page table entries to be reused for both secure and further domains, reducing circuit area.

The memory system may include a point of physical aliasing (PoPA), which is a point at which aliasing physical addresses from different physical address spaces which correspond to the same memory system resource are mapped to a single physical address uniquely identifying that memory system resource. The memory system may include at least one pre-PoPA memory system component which is provided upstream of the PoPA, which treats the aliasing physical addresses as if they correspond to different memory system resources.

For example, the at least one pre-PoPA memory system component could include a cache or translation lookaside buffer which may cache data, program code or address

5

10

15

20

25

30

35

translation information for the aliasing physical addresses in separate entries, so that if the same memory system resource is requested to be accessed from different physical address spaces, then the accesses will cause separate cache or TLB entries to be allocated. Also, the pre-PoPA memory system component could include coherency control circuitry, such as a coherent interconnect, snoop filter, or other mechanism for maintaining coherency between cached information at respective master devices. The coherency control circuitry could assign separate coherency states to the respective aliasing physical addresses in different physical address spaces. Hence, the aliasing physical addresses are treated as separate addresses for the purpose of maintaining coherency even if they do actually correspond to the same underlying memory system resource. Although on the face of it, tracking coherency separately for the aliasing physical addresses could appear to cause a problem of loss of coherency, in practice this is not a problem because if processes operating in different domains are really intended to share access to a particular memory system resource then they can use the less secure physical address space to access that resource (or use the restrictive sharing feature described below to access the resource using one of the other physical address spaces). Another example of a pre-PoPA memory system component may be a memory protection engine which is provided for protecting data saved to off-chip memory against loss of confidentiality and/or tampering. Such a memory protection engine could, for example, separately encrypt data associated with a particular memory system resource with different encryption keys depending on which physical address space the resource is accessed from, effectively treating the aliasing physical addresses as if they were corresponding to different memory system resources (e.g. an encryption scheme which makes the encryption dependent on the address may be used. and the physical address space identifier may be considered to be part of the address for this purpose).

Regardless of the form of the pre-PoPA memory system component, it can be useful for such a PoPA memory system component to treat the aliasing physical addresses as if they correspond to different memory system resources, as this provides hardware-enforced isolation between the accesses issued to different physical address spaces so that information associated with one domain cannot be leaked to another domain by features such as cache timing side channels or side channels involving changes of coherency triggered by the coherency control circuitry.

It may be possible, in some implementations, for the aliasing physical addresses in the different physical address spaces to be represented using different numeric physical address values for the respective different physical address spaces. This approach may require a mapping table to determine at the PoPA which of the different physical address values correspond to the same memory system resource. However, this overhead of

maintaining the mapping table may be considered unnecessary, and so in some implementations it may be simpler if the aliasing physical addresses comprise physical addresses which are represented using the same numeric physical address value in each of the different physical address spaces. If this approach is taken then, at the point of physical aliasing, it can be sufficient simply to discard the physical address space identifier which identifies which physical address space is accessed using a memory access, and then to provide the remaining physical address bits downstream as a de-aliased physical address.

5

10

15

20

25

30

35

Hence, in addition to the pre-PoPA memory system component, the memory system may also include a PoPA memory system component configured to de-alias the plurality of aliasing physical addresses to obtain a de-aliased physical address to be provided to at least one downstream memory system component. The PoPA memory system component could be a device accessing a mapping table to find the dealiased address corresponding to the aliasing address in a particular address space, as described above. However, the PoPA component could also simply be a location within the memory system where the physical address tag associated with a given memory access is discarded so that the physical address provided downstream uniquely identifies a corresponding memory system resource regardless of which physical address space this was provided from. Alternatively, in some cases the PoPA memory system component may still provide the physical address space tag to the at least one downstream memory system component (e.g. for the purpose of enabling completer-side filtering as discussed further below), but the PoPA may mark the point within the memory system beyond which downstream memory system components no longer treat the aliasing physical addresses as different memory system resources, but consider each of the aliasing physical addresses to map the same memory system resource. For example, if a memory controller or a hardware memory storage device downstream of the PoPA receives the physical address tag and a physical address for a given memory access request, then if that physical address corresponds to the same physical address as a previously seen transaction, then any hazard checking or performance improvements performed for respective transactions accessing the same physical address (such as merging accesses to the same address) may be applied even if the respective transactions specified different physical address space tags. In contrast, for a memory system component upstream of the PoPA, such hazard checking or performance improving steps taken for transactions accessing the same physical address may not be invoked if these transactions specify the same physical address in different physical address spaces.

As mentioned above, the at least one pre-PoPA memory system component may include at least one pre-PoPA cache. This could be a data cache, an instruction cache or a unified level 2, level 3 or system cache.

The processing circuitry may support a cache-invalidate-to-PoPA instruction which specifies a target address (which could be a virtual address or a physical address). In response to the cache-invalidate-to-PoPA instruction, the processing circuitry may issue at least one invalidation command to request that at least one pre-PoPA cache invalidates one or more entries associated with the target physical address value which corresponds to the target address. In contrast, when the at least one invalidation command is issued, at least one post-PoPA cache located downstream of the PoPA may be allowed to retain one or more entries associated with the target physical address value. For the at least one pre-PoPA cache, the cache may invalidate the one or more entries associated with the target physical address value specified by the at least one invalidation command, regardless of which of the physical address spaces is associated with those entries. Therefore, even if physical addresses having the same address value in different physical address spaces are treated as if they represent different physical addresses by the pre-PoPA caches, for the purpose of handling invalidations triggered by the cache-invalidate-to-PoPA instruction, the physical address space identifier may be ignored.

5

10

15

20

25

30

35

Hence, a form of cache invalidation instruction can be defined which enables the processing circuitry to request that any cached entries associated with a particular physical address corresponding to a target virtual address are invalidated in any caches up to the point of physical aliasing. This form of invalidation instruction may differ from other types of invalidation instruction which may request invalidations of cached entries which affect caches up to other points of the memory system, such as up to the point of coherency (a point at which all observers (e.g. processor cores, direct memory access engines, etc.) are guaranteed to see the same copy of data associated with a given address). Providing a dedicated form of instruction which requests invalidations up to the point of physical aliasing can be useful, especially for the root domain code which may manage changes of address allocation to the respective domains. For example, when updating granule protection information which defines which physical addresses are accessible within a given physical address space, or when reallocating a particular block of physical addresses to a different physical address space, the root domain code can use the cache-invalidate-to-PoPA instruction to ensure that any data, code or other information resident within a cache, whose accessibility depends on out of date values of the granule protection information, is invalidated to ensure that subsequent memory accesses are controlled correctly based on the new granule protection information. In some examples, in addition to invalidating a cached entry, the at least one pre-PoPA cache could also clean data from that cached entry so as to write any dirty versions of data associated with the entry to be invalidated back to a location in the memory system which is beyond the PoPA. In some cases, different versions

of the cache-invalidate-to-PoPA instruction could be supported to indicate whether cleaning is required or not.

Memory encryption circuitry may be provided which is responsive to a memory access request specifying a selected physical address space and a target physical address within the selected physical address space, when the target physical address is within a protected address region, to encrypt or decrypt data associated with the protected region based on one of a number of encryption keys selected depending on the selected physical address space. In some examples, the protected address region could be the entire physical address space, while other examples may apply the encryption/decryption only to certain sub-regions as the protected address region. By assigning a dedicated root physical address space separate from the physical address spaces associated with the other domains, this makes it simpler for the memory encryption circuitry to select a different encryption key for the root domain compared to other domains so as to improve security. Similarly, the selection of different encryption keys for all the other domains enables stronger isolation of code or data assets associated with a particular domain.

In one particular example, the apparatus may have at least one on-chip memory on a same integrated circuit as the processing circuitry, and all valid physical addresses in the root physical address space may be mapped to the at least one on-chip memory, as distinct from off-chip memory. This helps to improve security of the root domain. It will be appreciated that information from other domains could also be stored in on-chip memory. The provision of a separate root physical address space simplifies the allocation of memory because, whereas in an example where the root domain shares the secure physical address space with a secure domain, there may be too much data associated with the secure domain to hold all of that data in on-chip memory and it may be difficult to determine which particular pieces of data are associated with the root domain, it is much simpler to partition out the root domain's data (or code) when this is flagged with a separate physical address space identifier.

Nevertheless, in other examples it is possible for some addresses in the root physical address space to be mapped to off-chip memory. Memory encryption, integrity and freshness mechanisms can be used to protect root domain data stored off-chip.

The techniques discussed above can be implemented in a hardware apparatus which has hardware circuitry logic for implementing the functions as discussed above. Hence, the processing circuitry and the address translation circuitry may comprise hardware circuit logic. However, in other examples a computer program for controlling a host data processing apparatus to provide an instruction execution environment for execution of target code may be provided with processing program logic and address translation program logic which performs, in software, equivalent functions to the processing circuitry and address

translation circuitry discussed above. This can be useful, for example, for enabling target code written for a particular instruction set architecture to be executed on a host computer which may not support that instruction set architecture. Hence, functionality expected by the instruction set architecture which is not provided by the host computer could be emulated instead by simulation software providing an equivalent instruction execution environment for the target code as would be expected if the target code had been executed on the hardware device which actually supports the instruction set architecture. Hence, the computer program providing the simulation could include processing program logic which simulates processing in one of the at least three domains described earlier, and address translation program logic which translates virtual addresses to physical addresses in one of a number of simulated physical address spaces selected based at least on the current domain. As in the hardware device, the at least three domains may include a root domain for managing switching between other domains and the root domain may have a root simulated physical address space associated with it, separate from simulated physical address spaces associated with the other domains. For the approach where a simulation of the architecture is provided, the respective physical address spaces selected by the address translation program logic are simulated physical address spaces because they do not actually correspond to physical address spaces identified by hardware components of the host computer, but would be mapped to addresses within the virtual address space of the host. Providing such a simulation can be useful for a range of purposes, for example for enabling legacy code written for one instruction set architecture to be executed on a different platform which supports a different instruction set architecture, or for assisting with software development of new software to be executed for a new version of an instruction set architecture when hardware devices supporting that new version of the instruction set architecture are not available yet (this can enable the software for the new version of the architecture to start to be developed in parallel with development of the hardware devices supporting the new version of the architecture).

## **Granule Protection Lookups**

5

10

15

20

25

30

35

In a system in which a virtual address of a memory access request can be mapped to a physical address in one of two or more distinct physical address spaces, granule protection information can be used to limit which physical addresses are accessible within a particular physical address space. This can be useful for ensuring that certain physical memory locations implemented in hardware either on-chip or off-chip can be restricted for access within a particular physical address space or a particular subset of physical address spaces if desired.

In one approach for managing such restrictions, the enforcement of whether a given physical address can be accessed from a particular physical address space may be

implemented using completer-side filtering circuitry provided at or near a completer device for servicing a memory access request. For example, the completer-side filtering circuitry can be associated with a memory controller or peripheral controller. In such an approach, the issuing of memory access requests to a cache, or an interconnect for routing transactions from a requester device to the completer device, may not depend on any lookup of information for defining which physical addresses are accessible within a given physical address space.

In contrast, in the examples described below, a granule protection lookup is performed by requester-side filtering circuitry which checks whether a memory access request is allowed to be passed to a cache or an interconnect, based on a lookup of granule protection information which indicates at least one allowed physical address space associated with a target granule of physical addresses to be accessed. The granules of physical address space for which respective items of granule protection information are defined may be of a particular size, which may be the same as, or different to, the size of the pages used for a page table structure used for the address translation circuitry. In some cases the granules may be of a larger size than the pages defining address translation mappings for the address translation circuitry. Alternatively, the granule protection information may be defined at the same page-level granularity as address translation information within a page table structure. Defining granule protection information at page-level granularity can be convenient as this may then allow more fine-grained control over which regions of memory storage hardware are accessible from particular physical address spaces and hence from particular domains of operations of processing circuitry.

Hence, an apparatus may have address translation circuitry to translate a target virtual address specified by a memory access request issued by requester circuitry into a target physical address, and requester-side circuitry to perform a granule protection lookup based on the target physical address and a selected physical address space associated with the memory access request, to determine whether to allow the memory access request to be passed to a cache or passed to an interconnect for communicating with a completer device for servicing the memory access request. The selected physical address space may be one of a plurality of physical address spaces. In the granule protection lookup, the requester-side filtering circuitry may be configured to:

obtain granule protection information corresponding to a target granule of physical addresses including the target physical address, the granule protection information indicative of at least one allowed physical address space associated with the target granule; and

block the memory access request when the granule protection information indicates that the selected physical address space is not one of said at least one allowed physical address space.

An advantage of performing a granule protection lookup at the requester-side of the interconnect instead of on the completer-side is that this can enable more fine-grained control over which physical addresses are accessible from a given physical address space than would be practical at the completer-side. This is because the completer-side may typically have relatively limited ability to access the memory system as a whole. For example, a memory controller for a given memory unit may only have access to the locations within that memory unit and may not have access to other regions of the address space. Providing more fine-grained control may rely on a more complex table of granule protection information which may be stored in the memory system and it may be more practical to access such a table from the requester side where there is more flexibility to issue memory access request to a wider subset of the memory system.

5

10

15

20

25

30

35

Also, performing the granule protection lookup on the requester side can help enable the ability to dynamically update granule protection information at runtime, which may not be practical for completer-side filtering circuitry which may be restricted to accessing a relatively small amount of statically defined data defined at boot-time.

Another advantage of requester-side filtering circuitry is that this would enable the interconnect to allocate different addresses within the same granule to different completer ports communicating with different completer devices (e.g. different DRAM (dynamic random access memory) units), which may be efficient for performance but may be impractical if the granule as a whole needs to be directed to the same completer unit so that the granule protection lookup can be performed on the completer side to verify whether a memory access is allowed.

Hence there may be a number of advantages to performing the granule protection lookup for distinguishing whether a particular physical address can be accessed from a particular physical address space selected for a given memory access request at the requester side instead of the completer side.

The granule protection information can be represented in different ways. In one example the granule protection could be defined in a single linearly indexed table stored at a single contiguous block of addresses, with the particular entry to be accessed within that block selected based on the target physical address. However, in practice, granule protection information may not be defined for the entire physical address space and so it may be more efficient to use a multi-level table structure for storing the granule protection information, similar to a multi-level page table used for address translation. In such a multi-level structure, a portion of the target physical address may be used to select a level one

granule protection table entry which may provide a pointer identifying a location in memory storing a further level granule protection table. Another portion of the target physical address may then select which entry of that further granule protection table is to be obtained. After iterating through one or more levels of the table beyond the first level, eventually a granule protection table entry may be obtained which provides the granule protection information associated with the target physical address.

Regardless of the particular structure chosen for the table storing the granule protection information, the granule protection information may represent which of the physical address spaces is the at least one allowed physical address in a number of ways. One approach could be to provide a series of fields which each indicate whether a corresponding one of the physical address spaces is allowed to access the granule of physical addresses including the target physical address. For example, a bitmap may be defined within the granule protection information, with each bit of the bitmap indicating whether a corresponding physical address space is an allowed physical address space or a non-allowed physical address space for that granule.

However, in practice for most use cases it may be relatively unlikely that a significant number of the physical address spaces are expected to be allowed to access a given physical address. As discussed in the earlier section on controlling access to physical address spaces, a less secure physical address space could be available for selection in all domains so can be used when data or code is to be shared between the number of domains, so that it may not be necessary for a particular physical address to be mapped into all or a substantial fraction of the available physical address spaces.

Hence, a relatively efficient approach can be that the granule protection information may specify an assigned physical address space assigned to the target granule of physical addresses, and the at least one allowed physical address space may include at least the assigned physical address space designated by the granule protection information for that particular target granule. In some implementations the granule protection information may specify a single physical address space as the assigned physical address space. Hence in some cases the granule protection information may comprise an identifier of one particular physical address space which acts as the assigned physical address space allowed to access that target granule of physical addresses.

In some implementations the only physical address space allowed to access the target granule of physical addresses may be the assigned physical address space, and the target granule of physical addresses may not be allowed to be accessed from any other physical address space. This approach can be efficient for maintaining security. Access from different domains to a particular physical address space could instead be controlled through the address translation functionality, where the address translation circuitry may be

able to select which particular physical address space is to be used for a given memory access, so there may not be any need to allow a granule of physical addresses to be shared between multiple physical address spaces. If only the assigned physical address space is allowed to access the target granule of physical addresses, then to enable that granule of physical addresses to be accessed from other physical address spaces, this may require an update of which physical address space is the assigned physical address space. For example, this may require the root domain described earlier to perform some processing to switch the assigned physical address space for a given granule of physical addresses. This processing may have a certain performance cost, as for example it may (for security) include overwriting each location in the given granule of physical addresses with null data or other data which is independent of a previous contents of those physical addressed locations, to ensure that processes with access to the new assigned physical address space are not able to learn anything from the data previously stored at locations associated with the given granule of physical addresses.

5

10

15

20

25

30

35

Hence, another approach can be that as well as identifying an assigned physical address space, the granule protection information could also comprise sharing attribute information which indicates whether at least one other physical address space other than the assigned physical address space is one of the at least one allowed physical address space. Hence, if the sharing attribute information indicates that at least one other physical address space is allowed to access the corresponding granule of physical addresses then that granule of physical addresses can be accessed from multiple physical address spaces. This could be useful for allowing code in a domain associated with one physical address space to temporarily allow one of its assigned granules of physical addresses to be visible to a domain associated with a different physical address space. This could make temporary sharing of data or code more efficient because it is not necessary to incur a potentially costly operation for changing which physical address space is the assigned physical address space. The sharing attribute information could be set directly by code executing in the domain associated with the assigned physical address space, or could be set by the root domain on request from the code executing in the domain associated with the assigned physical address space.

Where the sharing attribute information is supported, then as well as using the sharing attribute information to validate whether an address assigned to one physical address space can be accessed by requests specifying a different address space, the requester-side filtering circuitry may also transform the physical address space selected for the memory access request issued downstream to a cache or interconnect, based on the sharing attribute information. Hence, when the granule protection lookup determines that the selected physical address space is a physical address space other than the assigned

physical address space which is one of said at least one allowed physical address space indicated by the sharing attribute information, the requester-side filtering circuitry may allow the memory access request to be passed to the cache or interconnect specifying the assigned physical address space instead of the selected physical address space. This means that, for the purpose of accessing downstream memory, the components prior to the PoPA treat the memory access as if it was issued specifying the assigned physical address space in the first place, so that cache entries or snoop filter entries tagged with that assigned physical address space can be accessed for the memory access request.

In some implementations, the requester-side filtering circuitry may obtain the granule protection information used for the granule protection lookup from memory each time a memory access request is checked against the granule protection information. This approach may require less hardware cost at the requester side. However, it may be relatively slow to obtain the granule protection information from memory.

Therefore, to improve performance the requester-side filtering circuitry may have access to at least one lookup cache which may cache the granule protection information, so that the granule protection lookup can be performed in the at least one lookup cache and if the required granule information is already stored in the at least one lookup cache then it is not necessary to fetch it from memory. The at least one lookup cache may in some cases be a separate cache from a translation lookaside buffer (TLB) used by the address translation circuitry for caching page table data providing mappings between virtual and physical addresses. However, in other examples the at least one lookup cache could combine caching of page table data with caching of granule protection information. Hence, the at least one lookup cache could in some cases store at least one combined translation-granule protection entry specifying information depending on both the granule protection information and at least one page table entry used by the address translation circuitry for mapping the target virtual address to the target physical address. Whether the TLB and granule protection cache are implemented as separate structures or as the single combined structure is an implementation choice and either can be used.

Regardless of which approach is used for the at least one lookup cache, the at least one lookup cache may be responsive to at least one lookup cache invalidation command which specifies an invalidation target physical address to invalidate lookup cache entries storing information which depends on granule protection information associated with a granule of physical addresses including the invalidation target physical address. In a conventional processing system having a TLB, while the TLB may typically support invalidation commands specifying a virtual address or (in a system supporting two stages of address translation, an intermediate address), it is not typically needed for TLBs to be able to identify which entry is to be invalidated using a physical address. However, when at least

one lookup cache is provided to cache granule protection information, then if the granule protection information for a given granule of physical addresses changes then it may be useful to be able to invalidate any entries which depend on that information. Hence, the command may identify a particular physical address for which entries containing information depending on granule protection information are to be invalidated.

If a granule protection information cache is implemented separately from a TLB, then a TLB may need not have any capability to search entries by physical address. In this case, the granule protection information cache may respond to the cache invalidation command specifying a physical address, but the command may be ignored by the TLB.

However, if the at least one lookup cache includes a combined translation/granule protection cache whose entries are searched based on a virtual address or an intermediate address and return both the page table information associated with the virtual/intermediate address and the granule protection information associated with the corresponding physical address, then it may be useful to provide a further scheme for searching entries based on the physical address, so that the at least one lookup cache invalidation command which specifies an invalidation target physical address can be processed. Such searches by physical address would not be needed by regular lookups of the combined cache, because if the entries are combined then searching by a virtual address or an intermediate address may be sufficient to access all of the combined information for performing both the address translation and the granule protection lookup. However, on cache invalidation commands the combined cache can be searched based on a physical address to identify any entries which may need to be invalidated because they depend on granule protection information for the specified physical address.

The memory system may have a PoPA memory system component, at least one pre-PoPA memory system component and at least one post-PoPA memory system component as discussed above for the earlier examples. Hence, aliasing physical addresses within different physical address spaces may correspond to the same memory system resource identified using a de-aliased physical address when memory access requests pass beyond the point of physical aliasing, in the same way as discussed earlier. Prior to the PoPA, at least one pre PoPA memory system component treats aliasing physical addresses from different physical address spaces as if they correspond to different memory system resources which can improve security. Again, although in theory it may be possible for the aliasing physical addresses in the different physical address spaces to be identified using different numeric address values, this may be relatively complex to implement and it can be simpler if the aliasing physical addresses are represented using the same physical address value in the different physical address spaces.

Where the at least one pre-PoPA memory system component comprises at least one pre-PoPA cache, the processing circuitry may be responsive to a cache-invalidate-to-PoPA instruction specifying a target virtual address to trigger invalidations by target physical address to any pre-PoPA caches which are upstream of the point of physical aliasing, while allowing any post-PoPA caches to retain data with the target physical address (as described earlier).

The selected physical address space associated with the memory access can be selected in different ways. In some examples, the selected physical address space may be selected (either by the address translation circuitry or by the requester-side filtering circuitry) based at least on a current domain of operation of the requester circuitry from which the memory access request was issued. The selection of the selected physical address space could also depend on physical address space selection information specified in at least one page table entry used for the translation of the target virtual address to the target physical address. The selection of which physical address space is the selected physical address space may be performed as discussed earlier for the preceding examples.

The domains and physical address spaces available for a selection in the given system may be as described earlier, and may include the less secure domain, secure domain, root domain and further domain as discussed above each with corresponding physical address spaces. Alternatively, the domains/physical address spaces could include a subset of these domains. Hence, any of the features relating to any of the domains described earlier can be included in a system having the requester-side filtering circuitry.

In an implementation where the root domain has a corresponding root physical address space as described earlier, then when the current domain is the root domain, the requester-side filtering circuitry could bypass the granule protection lookup. The granule protection lookup could be unnecessary when the current domain is the root domain as the root domain may be trusted to access all regions of physical addresses and so power can be saved by skipping the granule protection lookup when in the root domain.

The granule protection information may be modifiable by software executed in the root domain. Hence, the granule protection information may be dynamically updateable at run-time. This can be an advantage for some of the realm use cases discussed, where realms providing secure execution environments may be dynamically created at runtime and allocated corresponding regions of memory reserved for the realm. Such an approach would often be unpractical using completer-side filtering only. In some implementations the root domain may be the only domain allowed to modify the granule protection information, so if other domains need a change to the granule protection information to be implemented, then they may request that the root domain modifies the granule protection information, and the root domain can then check whether to allow the request made from another domain.

Although it can be beneficial to provide requester-side filtering circuitry for performing a granule protection lookup on the requester-side before a memory access request is passed to a cache or an interconnect, there may be other scenarios in which it may be preferred for protection information (defining which physical addresses can be accessed from a given physical address space) to be checked on the completer-side of the interconnect instead. For example, while for some parts of the address space it may be desirable to provide a fine-grained page-level granularity of division of the memory hardware into regions of physical addresses accessible from different physical address spaces, for other parts of the memory system it may be preferred to allocate a large block of contiguous addresses to a single physical address space, and so the overheads of accessing a (potentially multi-level) granule protection structure stored in memory may be unjustified. If an entire memory unit (e.g. a particular DRAM module) is to be allocated to a single physical address space then it may be simpler to handle the enforcement of restriction of access to that memory unit through a completer-side check.

Therefore, in some implementations, as well as providing requester-side filtering circuitry, there may also be completer-side filtering circuitry which is responsive to a memory access request received from the interconnect specifying a target physical address and a selected physical address space, to perform a completer-side protection lookup of completer-side protection information based on the target physical address and the selected physical address space, to determine whether the memory access request is allowed to be serviced by the completer device. By providing a hybrid approach enabling some parts of memory to be protected through a requester-side filter and other parts to be protected by a completer-side filter, this allows a better balance between performance and flexibility of allocating usage of memory than could be achieved either through requester-side filtering or completer-side filtering alone.

Hence, in some implementations the granule protection information may specify a pass-through indicator indicating that the at least one allowed physical address space is to be resolved by completer-side filtering circuitry. Hence, the requester-side filtering circuitry may, in cases when the granule protection information specifies the pass-through indicator, determine whether or not to pass the memory access request to the cache or the interconnect independent of any check of whether the selected physical address space is one of the at least one allowed physical address space for the target granule of physical addresses. On the other hand, if the granule protection information accessed for the target granule does not specify the pass-through indicator, then the determination of whether the memory access request can be passed to the cache or the interconnect may depend on the check of whether the selected physical address space is one of the at least one allowed physical address space, as in this case there may not be a subsequent completer-side

filtering performed after the memory access request is allowed to progress to the cache or interconnect. Hence, the pass-through indicator can enable control of a partitioning of the address space between those granules of physical addresses for which checks are to be performed requester-side and those granules for which those checks are to be performed on the completer-side, providing added flexibility for a system designer.

5

10

15

20

25

30

35

The completer-side protection information used by the completer-side filtering circuitry need not have the same format as the granule protection information used by the requester-side filtering circuitry. For example the completer-side filtering circuitry may be defined at a coarser granularity than the granule protection information used for the granule protection lookup by the requester-side filtering circuitry. The granule protection information may be defined in a multi-level table structure where each level of the table provides entries each corresponding to a block of memory of a given number of addresses corresponding to a power of two and so the entry of a given level of table needed for checking a given target physical address can be indexed simply by adding a multiple of a certain portion of bits from the target physical address to a base address associated with that level of the table, avoiding a need for comparing contents of the accessed entry with the target physical address to determine whether it is the correct entry. In contrast, for the completer-side protection information a smaller number of entries may be defined, each entry specifying start and end addresses (or a start address and size) of a region of memory which may correspond to a non-power of two number of addresses. This can be more suitable for defining relatively coarse-grained blocks in the completer-side protection information, but this approach may require the target physical address to be compared against the upper and lower bounds of the respective ranges of physical addresses defined in each completer-side protection information entry to determine whether any of those match the specified physical The indexed multi-level table approach used for the requester-side granule protection information may support a relatively large number of distinct entries so that a finegrained mapping of physical addresses to physical address spaces is supported, which would typically not be practical using the approach of defining upper and lower bounds of each region in the completer-side protection information due to the comparison overhead in looking up each of those entries to check whether a target address falls within the bounds of that entry, but the completer-side protection information may be more efficient in terms of memory storage and may be less variable in terms of performance as there is less of a penalty if there is a miss in a lookup cache. Of course this is just one example of how the looked up information could be implemented on the requester side and the completer side.

The requester-side protection information may be dynamically updateable at runtime. The completer-side protection information could be either statically defined by hardware on the system-on-chip, configured at boot time, or dynamically re-configured at run-time.

As for the earlier described examples, although the techniques described above for the granule protection lookup can be implemented in a system having dedicated hardware logic for performing the functions of the address translation circuitry and the requester-side filtering circuitry, the equivalent functions could also be implemented in software within in computer program for controlling host data apparatus to provide an instruction execution environment for execution of target code, for similar reasons to those described earlier. Hence, address translation program logic and filtering program logic may be provided to emulate the functionality of the address translation circuitry and requester-side filter described earlier. As for the earlier examples, for the computer program providing the instruction execution environment, at least one of the following may apply: the granule protection information is dynamically updatable by the target code at runtime; and the granule protection information is defined at page-level granularity.

#### Description of Examples

5

10

15

20

25

30

35

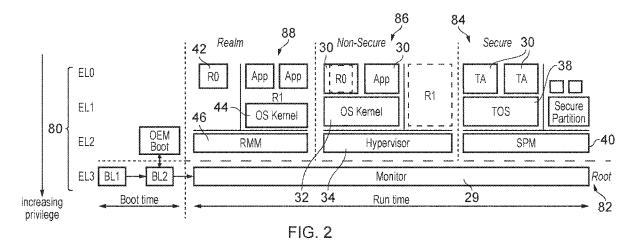

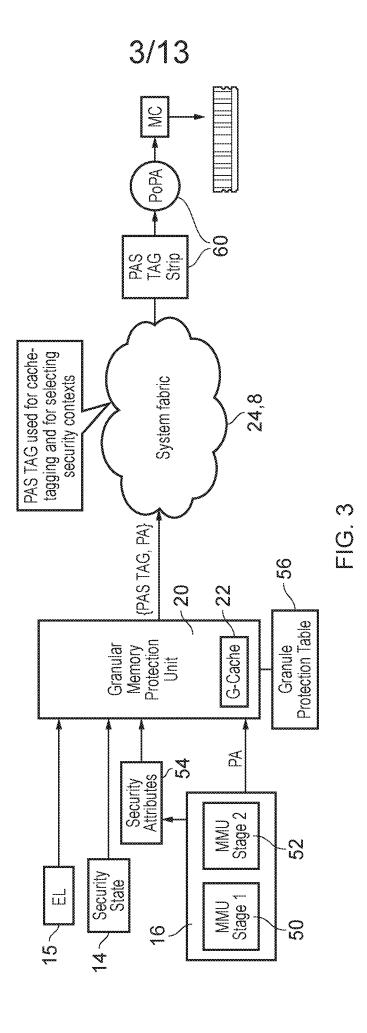

Figure 1 schematically illustrates an example of a data processing system 2 having at least one requester device 4 and at least one completer device 6. An interconnect 8 provides communication between the requester devices 4 and completer devices 6. A requester device is capable of issuing memory access requests requesting a memory access to a particular addressable memory system location. A completer device 6 is a device that has responsibility for servicing memory access requests directed to it. Although not shown in Figure 1, some devices may be capable of acting both as a requester device and as a completer device. The requester devices 4 may for example include processing elements such as a central processing unit (CPU) or graphics processing unit (GPU) or other master devices such as bus master devices, network interface controllers, display controllers, etc. The completer devices may include memory controllers responsible for controlling access to corresponding memory storage units, peripheral controllers for controlling access to a peripheral device, etc. Figure 1 shows an example configuration of one of the requester devices 4 in more detail but it will be appreciated that the other requester devices 4 could have a similar configuration. Alternatively, the other requester devices may have a different configuration to the requester device 4 shown on the left of Figure 1.

The requester device 4 has processing circuitry 10 for performing data processing in response to instructions, with reference to data stored in registers 12. The registers 12 may include general purpose registers for storing operands and results of processed instructions, as well as control registers for storing control data for configuring how processing is performed by the processing circuitry. For example the control data may include a current

domain indication 14 used to select which domain of operation is the current domain, and a current exception level indication 15 indicating which exception level is the current exception level in which the processing circuitry 10 is operating.

5

10

15

20

25

30

35

The processing circuitry 10 may be capable of issuing memory access requests specifying a virtual address (VA) identifying the addressable location to be accessed and a domain identifier (Domain ID or 'security state') identifying the current domain. Address translation circuitry 16 (e.g. a memory management unit (MMU)) translates the virtual address into a physical address (PA) through one of more stages of address translation based on page table data defined in page table structures stored in the memory system. A translation lookaside buffer (TLB) 18 acts as a lookup cache for caching some of that page table information for faster access than if the page table information had to be fetched from memory each time an address translation is required. In this example, as well as generating the physical address, the address translation circuitry 16 also selects one of a number of physical address spaces associated with the physical address and outputs a physical address space (PAS) identifier identifying the selected physical address space. Selection of the PAS will be discussed in more detail below.

A PAS filter 20 acts as requester-side filtering circuitry for checking, based on the translated physical address and the PAS identifier, whether that physical address is allowed to be accessed within the specified physical address space identified by the PAS identifier. This lookup is based on granule protection information stored in a granule protection table structure stored within the memory system. The granule protection information may be cached within a granule protection information cache 22, similar to a caching of page table data in the TLB 18. While the granule protection information cache 22 is shown as a separate structure from the TLB 18 in the example of Figure 1, in other examples these types of lookup caches could be combined into a single lookup cache structure so that a single lookup of an entry of the combined structure provides both the page table information and the granule protection information. The granule protection information defines information restricting the physical address spaces from which a given physical address can be accessed, and based on this lookup the PAS filter 20 determines whether to allow the memory access request to proceed to be issued to one or more caches 24 and/or the interconnect 8. If the specified PAS for the memory access request is not allowed to access the specified physical address then the PAS filter 20 blocks the transaction and may signal a fault.

While Figure 1 shows an example with a system having multiple requester devices 4, the features shown for the one requester device on the left hand side of Figure 1 could also be included in a system where there is only one requester device, such as a single-core processor.

While Figure 1 shows an example where selection of the PAS for a given request is performed by the address translation circuitry 16, in other examples information for determining which PAS to select can be output by the address translation circuitry 16 to the PAS filter 20 along with the PA, and the PAS filter 20 may select the PAS and check whether the PA is allowed to be accessed within the selected PAS.

The provision of the PAS filter 20 helps to support a system which can operate in a number of domains of operation each associated with its own isolated physical address space where, for at least part of the memory system (e.g. for some caches or coherency enforcing mechanisms such as a snoop filter), the separate physical address spaces are treated as if they refer to completely separate sets of addresses identifying separate memory system locations, even if addresses within those address spaces actually refer to the same physical location in the memory system. This can be useful for security purposes.

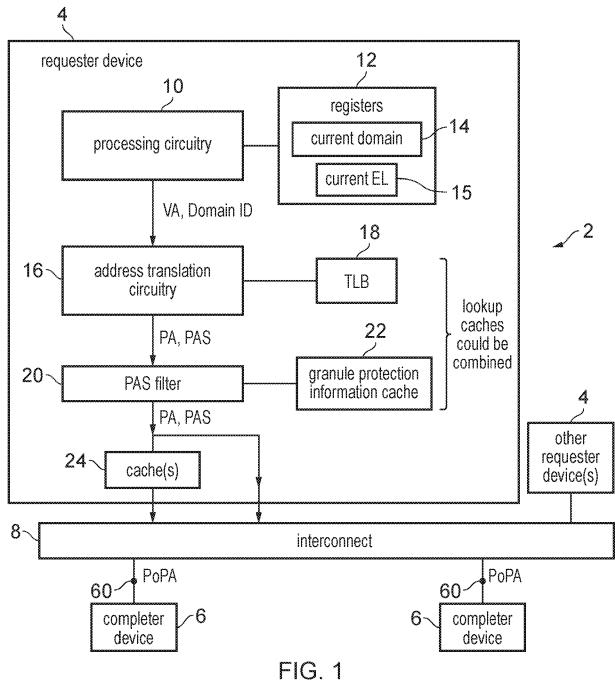

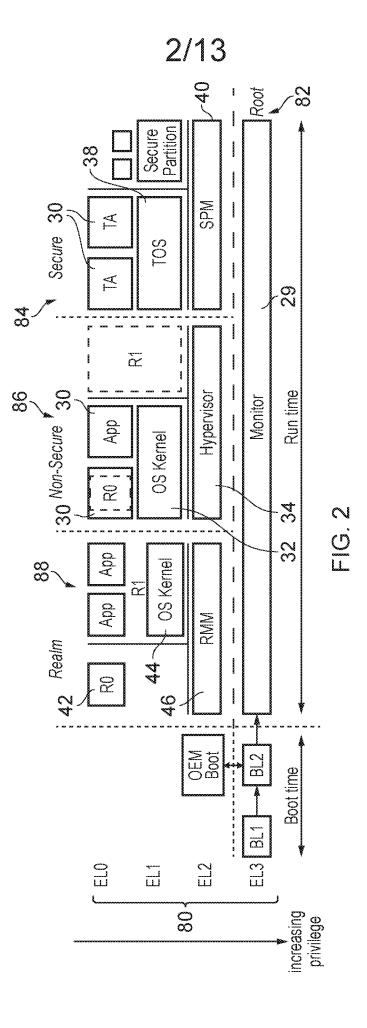

Figure 2 shows an example of different operating states and domains in which the processing circuitry 10 can operate, and an example of types of software which could be executed in the different exception levels and domains (of course, it will be appreciated that the particular software installed on a system is chosen by the parties managing that system and so is not an essential feature of the hardware architecture).

The processing circuitry 10 is operable at a number of different exception levels 80, in this example four exception levels labelled EL0, EL1, EL2 and EL3, where in this example EL3 refers to the exception level with the greatest level of privilege while EL0 refers to the exception level with the least privilege. It will be appreciated that other architectures could choose the opposite numbering so that the exception level with the highest number could be considered to have the lowest privilege. In this example the least privileged exception level EL0 is for application-level code, the next most privileged exception level EL1 is used for operating system-level code, the next most privileged exception level EL2 is used for hypervisor-level code which manages switching between a number of virtualised operating systems, while the most privileged exception level EL3 is used for monitor code which manages switches between respective domains and allocation of physical addresses to physical address spaces, as described later.