### (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第5581795号 (P5581795)

(45) 発行日 平成26年9月3日(2014.9.3)

(24) 登録日 平成26年7月25日 (2014.7.25)

| (51) Int.Cl. | F 1                           |                         |

|--------------|-------------------------------|-------------------------|

| HO1L 21/82   | <b>(2006.01)</b> HO1L         | L 21/82 B               |

| HO1L 21/822  | <b>(2006.01)</b> HO1L         | L 21/82 C               |

| HO1L 27/04   | (2006.01) HO1L                | L 27/04 A               |

| HO1L 27/092  | <b>(2006.01)</b> HO1L         | L 27/04 D               |

| HO1L 21/823  | <b>8 (2006.01)</b> HO1L       | 27/08 321F              |

|              |                               | 請求項の数 7 (全 31 頁) 最終頁に続く |

| (21) 出願番号    | 特願2010-107409 (P2010-107409)  | (73) 特許権者 302062931     |

| (22) 出願日     | 平成22年5月7日(2010.5.7)           | ルネサスエレクトロニクス株式会社        |

| (65) 公開番号    | 特開2011-238689 (P2011-238689A) | ) │ 神奈川県川崎市中原区下沼部1753番地 |

| (43) 公開日     | 平成23年11月24日 (2011.11.24)      | (74) 代理人 100064746      |

| 審査請求日        | 平成25年2月5日(2013.2.5)           | 弁理士 深見 久郎               |

|              |                               | (74) 代理人 100085132      |

|              |                               | 弁理士 森田 俊雄               |

|              |                               | (74) 代理人 100083703      |

|              |                               | 弁理士 仲村 義平               |

|              |                               | (74) 代理人 100096781      |

|              |                               | 弁理士 堀井 豊                |

|              |                               | (74) 代理人 100109162      |

|              |                               | 弁理士 酒井 將行               |

|              |                               | (74) 代理人 100111246      |

|              |                               | 弁理士 荒川 伸夫               |

|              |                               | 最終頁に続く                  |

(54) 【発明の名称】スタンダードセル、スタンダードセルを備えた半導体装置、およびスタンダードセルの配置配線 方法

### (57)【特許請求の範囲】

### 【請求項1】

半導体基板の表面に形成された第1および第2スタンダードセルを備える半導体装置で あって、

前記第1スタンダードセルは、

前記半導体基板の前記表面に形成された帯状の第1不純物拡散領域と、

前記半導体基板の前記表面に形成され、前記第1不純物拡散領域に対向する第1機能素 子領域と、

前記半導体基板の前記表面の上方に配設され、前記第1不純物拡散領域の上方において 前記第1不純物拡散領域に沿うように延在する第1幹線部および前記第1幹線部から前記 第1機能素子領域の上方に向かって延在する第1延在部を含む第1金属層と、を有し、

前記第2スタンダードセルは、

前記半導体基板の前記表面に形成され、前記第1不純物拡散領域に連続する帯状の第2 不純物拡散領域と、

前記半導体基板の前記表面に形成され、前記第2不純物拡散領域に対向する第2機能素 子領域と、

前記半導体基板の前記表面における前記第2不純物拡散領域および前記第2機能素子領 域の間に形成され、前記第2不純物拡散領域および前記第2機能素子領域を電気的に接続 する接続用不純物拡散領域と、を有し、

前記第1金属層および前記第2機能素子領域は、前記第1幹線部、前記第1不純物拡散

領域、前記第2不純物拡散領域、および前記接続用不純物拡散領域を通して電気的に接続されており、

前記第1金属層の前記第1幹線部は、前記第2不純物拡散領域の上方に到達しない長さで、前記第1不純物拡散領域の上方において前記第1不純物拡散領域に沿うように延在している、

半導体装置。

#### 【請求項2】

<u>半導体基板の表面に形成された第1および第2スタンダードセルを備える半導体装置であって、</u>

前記第1スタンダードセルは、

前記半導体基板の前記表面に形成された帯状の第1不純物拡散領域と、

前記半導体基板の前記表面に形成され、前記第 1 不純物拡散領域に対向する第 1 機能素 子領域と、

前記半導体基板の前記表面の上方に配設され、前記第1不純物拡散領域の上方において 前記第1不純物拡散領域に沿うように延在する第1幹線部および前記第1幹線部から前記 第1機能素子領域の上方に向かって延在する第1延在部を含む第1金属層と、を有し、

前記第2スタンダードセルは、

前記半導体基板の前記表面に形成され、前記第 1 不純物拡散領域に連続する帯状の第 2 不純物拡散領域と、

前記半導体基板の前記表面に形成され、前記第 2 不純物拡散領域に対向する第 2 機能素 子領域と、

前記半導体基板の前記表面における前記第2不純物拡散領域および前記第2機能素子領域の間に形成され、前記第2不純物拡散領域および前記第2機能素子領域を電気的に接続する接続用不純物拡散領域と、を有し、

前記第1金属層および前記第2機能素子領域は、前記第1幹線部、前記第1不純物拡散 領域、前記第2不純物拡散領域、および前記接続用不純物拡散領域を通して電気的に接続 されており、

前記半導体基板の前記表面に形成された第3スタンダードセルをさらに備え、

前記第3スタンダードセルは、

前記半導体基板の前記表面に形成され、前記第 2 不純物拡散領域を挟んで前記第 1 不純物拡散領域の反対側に位置し、前記第 2 不純物拡散領域に連続する帯状の第 3 不純物拡散領域と、

前記半導体基板の前記表面に形成され、前記第3不純物拡散領域に対向する第3機能素子領域と、を有し、

前記半導体基板の前記表面の上方に第2金属層が配設され、

前記第2金属層は、

前記第2不純物拡散領域の上方において前記第2不純物拡散領域に沿うように延在する第2幹線部と、

前記第2幹線部から前記第1機能素子領域の上方に向かって延在する第2延在部と、

前記第2幹線部から前記第3機能素子領域の上方に向かって延在する第3延在部と、を 有し、

前記第1機能素子領域および前記第3機能素子領域は、前記第2幹線部、前記第2延在部および前記第3延在部を通して電気的に接続され、

前記第2金属層の前記第2幹線部が延在している平面高さは、前記第1金属層が形成されている平面高さ以下である、

半導体装置。

#### 【請求項3】

半導体基板の表面に形成された第 1 および第 2 スタンダードセルを備える半導体装置であって、

前記第1スタンダードセルは、

10

20

30

前記半導体基板の前記表面に形成された帯状の第1不純物拡散領域と、

前記半導体基板の前記表面に形成され、前記第 1 不純物拡散領域に対向する第 1 機能素 子領域と、

前記半導体基板の前記表面の上方に配設され、前記第1不純物拡散領域の上方において 前記第1不純物拡散領域に沿うように延在する第1幹線部および前記第1幹線部から前記 第1機能素子領域の上方に向かって延在する第1延在部を含む第1金属層と、を有し、

前記第2スタンダードセルは、

前記半導体基板の前記表面に形成され、前記第 1 不純物拡散領域に連続する帯状の第 2 不純物拡散領域と、

前記半導体基板の前記表面に形成され、前記第 2 不純物拡散領域に対向する第 2 機能素 子領域と、

前記半導体基板の前記表面における前記第2不純物拡散領域および前記第2機能素子領域の間に形成され、前記第2不純物拡散領域および前記第2機能素子領域を電気的に接続する接続用不純物拡散領域と、を有し、

前記第1金属層および前記第2機能素子領域は、前記第1幹線部、前記第1不純物拡散 領域、前記第2不純物拡散領域、および前記接続用不純物拡散領域を通して電気的に接続 されており、

前記半導体基板の前記表面に形成された第3スタンダードセルをさらに備え、

前記第3スタンダードセルは、

前記半導体基板の前記表面に形成され、前記第2不純物拡散領域を挟んで前記第2機能素子領域の反対側に位置し、前記第2不純物拡散領域に対向する第3機能素子領域を有し

前記半導体基板の前記表面の上方において前記第2不純物拡散領域を跨ぐように、前記第2機能素子領域および前記第3機能素子領域を電気的に接続する第2金属層が延設され

前記第2金属層が前記第2不純物拡散領域を跨ぐように延在している平面高さは、前記第1金属層が形成されている平面高さ以下である、

半導体装置。

#### 【請求項4】

半導体基板の表面に形成された第1および第2スタンダードセルを含むスタンダードセルであって、

前記第1スタンダードセルは、

前記半導体基板の前記表面に形成された第1機能素子領域と、

前記半導体基板の前記表面に形成され、前記第1機能素子領域の両側を挟んで対向して 配置される帯状の第1不純物拡散領域と、

前記半導体基板の前記表面の上方に配設され、各々の前記第1不純物拡散領域の上方に おいて各々の前記第1不純物拡散領域に沿うように延在する幹線部および各々の前記幹線 部から前記第1機能素子領域の上方に向かって延在する延在部を含む金属層と、を有し、

前記第2スタンダードセルは、

前記半導体基板の前記表面に形成された第2機能素子領域と、

前記半導体基板の前記表面に形成され、前記第2機能素子領域の両側を挟んで対向して配置されるとともに、前記第1不純物拡散領域にそれぞれ連続する帯状の第2不純物拡散領域と、

前記半導体基板の前記表面に形成され、各々の前記第2不純物拡散領域と前記第2機能素子領域との間を電気的に接続する接続用不純物拡散領域と、を有し、

前記金属層および前記第2機能素子領域は、前記幹線部、前記第1不純物拡散領域、前記第2不純物拡散領域、および前記接続用不純物拡散領域を通して電気的に接続されて<u>お</u>り、

前記金属層の前記幹線部は、前記第2不純物拡散領域の上方に到達しない長さで、前記第1不純物拡散領域の上方において前記第1不純物拡散領域に沿うように延在している、

10

20

40

30

スタンダードセル。

### 【請求項5】

<u>請求項2または請求項3</u>に記載の半導体装置におけるスタンダードセ<u>ルの</u>配置配線方法であって、

前記第2スタンダードセルのパターン情報が格納されたセルライブラリを準備する工程と、

所定の回路接続情報を配置配線システムに入力する工程と、

前記配置配線システムが、前記第2スタンダードセル以外の所定のスタンダードセルの前記パターン情報を前記セルライブラリから読み出し、前記回路接続情報に対応するように複数の前記スタンダードセルの前記パターン情報を配置する工程と、

複数の前記スタンダードセル間を結ぶ配線の密度が所定値を超える配線混雑領域の発生を検出する工程と、

前記配置配線システムが、前記第2スタンダードセルの前記パターン情報を前記セルライブラリから読み出し、前記配線混雑領域に含まれる前記スタンダードセルを前記第2スタンダードセルに置換する工程と、を備える、

スタンダードセルの配置配線方法。

### 【請求項6】

<u>半導体基板の表面に形成された第1および第2スタンダードセルを備える半導体装置に</u>おけるスタンダードセルの配置配線方法であって、

前記第1スタンダードセルは、

前記半導体基板の前記表面に形成された帯状の第1不純物拡散領域と、

前記半導体基板の前記表面に形成され、前記第 1 不純物拡散領域に対向する第 1 機能素 子領域と、

前記半導体基板の前記表面の上方に配設され、前記第1不純物拡散領域の上方において 前記第1不純物拡散領域に沿うように延在する第1幹線部および前記第1幹線部から前記 第1機能素子領域の上方に向かって延在する第1延在部を含む第1金属層と、を有し、

前記第2スタンダードセルは、

前記半導体基板の前記表面に形成され、前記第 1 不純物拡散領域に連続する帯状の第 2 不純物拡散領域と、

前記半導体基板の前記表面に形成され、前記第2不純物拡散領域に対向する第2機能素 子領域と、

前記半導体基板の前記表面における前記第2不純物拡散領域および前記第2機能素子領域の間に形成され、前記第2不純物拡散領域および前記第2機能素子領域を電気的に接続する接続用不純物拡散領域と、を有し、

前記第1金属層および前記第2機能素子領域は、前記第1幹線部、前記第1不純物拡散 領域、前記第2不純物拡散領域、および前記接続用不純物拡散領域を通して電気的に接続 されており、

前記第2スタンダードセルのパターン情報が格納されたセルライブラリを準備する<u>工程</u>と、

所定の回路接続情報を配置配線システムに入力する工程と、

前記配置配線システムが、前記第2スタンダードセル以外の所定のスタンダードセルの 前記パターン情報を前記セルライブラリから読み出し、前記回路接続情報に対応するよう に複数の前記スタンダードセルの前記パターン情報を配置する工程と、

複数の前記スタンダードセル間を結ぶ配線の密度が所定値を超える配線混雑領域の発生を検出する工程と、

前記配置配線システムが、前記第2スタンダードセルの前記パターン情報を前記セルライブラリから読み出し、前記配線混雑領域に含まれる前記スタンダードセルを前記第2スタンダードセルに置換する工程と、を備える、

スタンダードセルの配置配線方法。

【請求項7】

10

20

30

40

<u>半導体基板の表面に形成された第1および第2スタンダードセルを含むスタンダードセ</u>ルの配置配線方法であって、

前記第1スタンダードセルは、

前記半導体基板の前記表面に形成された第1機能素子領域と、

前記半導体基板の前記表面に形成され、前記第1機能素子領域の両側を挟んで対向して 配置される帯状の第1不純物拡散領域と、

前記半導体基板の前記表面の上方に配設され、各々の前記第1不純物拡散領域の上方に おいて各々の前記第1不純物拡散領域に沿うように延在する幹線部および各々の前記幹線 部から前記第1機能素子領域の上方に向かって延在する延在部を含む金属層と、を有し、

前記第2スタンダードセルは、

前記半導体基板の前記表面に形成された第2機能素子領域と、

前記半導体基板の前記表面に形成され、前記第2機能素子領域の両側を挟んで対向して 配置されるとともに、前記第1不純物拡散領域にそれぞれ連続する帯状の第2不純物拡散 領域と、

前記半導体基板の前記表面に形成され、各々の前記第2不純物拡散領域と前記第2機能 素子領域との間を電気的に接続する接続用不純物拡散領域と、を有し、

前記金属層および前記第2機能素子領域は、前記幹線部、前記第1不純物拡散領域、前記第2不純物拡散領域、および前記接続用不純物拡散領域を通して電気的に接続されており、

<u>前記第2スタンダードセルのパターン情報が格納されたセルライブラリを準備する工程と、</u>

所定の回路接続情報を配置配線システムに入力する工程と、

前記配置配線システムが、前記第2スタンダードセル以外の所定のスタンダードセルの 前記パターン情報を前記セルライブラリから読み出し、前記回路接続情報に対応するよう に複数の前記スタンダードセルの前記パターン情報を配置する工程と、

複数の前記スタンダードセル間を結ぶ配線の密度が所定値を超える配線混雑領域の発生 を検出する工程と、

前記配置配線システムが、前記第2スタンダードセルの前記パターン情報を前記セルライブラリから読み出し、前記配線混雑領域に含まれる前記スタンダードセルを前記第2スタンダードセルに置換する工程と、を備える、

スタンダードセルの配置配線方法。

【発明の詳細な説明】

【技術分野】

[00001]

本発明は、スタンダードセル、スタンダードセルを備えた半導体装置、およびスタンダードセルの配置配線方法に関する。

【背景技術】

[0002]

SOC(System On Chip)等の半導体装置は、スタンダードセルを使用して設計される。下記の特許文献1~7は、スタンダードセルを使用して設計される半導体装置において、チップ面積を小さくするための技術を開示している。

[0003]

特開2001-15602号公報(特許文献1)は、p型拡散層によって構成されたVDD端子と、n型拡散層によって構成されたVSS端子と、金属層によって構成された入力端子および出力端子とを備え、上記の各拡散層と金属層とをコンタクトホールによって接続するスダンタードセルを開示している。

[0004]

特開2001-189427号公報(特許文献2)は、GND配線を第1メタル層に配置し、VDD幹線を第2メタル層に配置するスタンダードセルを開示している。

[0005]

10

20

30

40

特開2005-236107号公報(特許文献3)は、回路の上層に配置された基幹電源メタル層と、基幹電源メタル層の下側で回路基板上に形成されたトランジスタ素子層と、基幹電源メタル層からトランジスタ素子層に電源電圧を供給する内部配線層とを備えるスタンダードセルを開示している。

### [0006]

特開平8-222640号公報(特許文献4)は、n型基板の上辺に設けられ電源用導体と接続されたn型高濃度領域と、p型ウェルの下辺に設けられグランド用導体と接続されたp型高濃度領域とを備え、セル列方向に隣接するスタンダードセルとの間において、n型高濃度領域およびp型高濃度領域を連続させたスタンダードセルを開示している。

### [0007]

特開2008-4790号公報(特許文献5)は、VDD幹線およびGND幹線の間に設けられたアクティブ領域と、アクティブ領域に形成された複数のトランジスタと、アクティブ領域からVDD幹線およびGND幹線の下まで延出させた接続部とを備え、接続部とVDD幹線とを接続し、接続部とGND幹線とを接続したスタンダードセルを開示している。

#### [00008]

特開平7-249747号公報(特許文献6)は、n型チャネルトランジスタおよびp型チャネルトランジスタが、ドレイン電極領域と接地電極領域との間でチャネル幅方向に配置されたスタンダードセルを開示している。

### [0009]

特開2009-158728号公報(特許文献7)は、半導体基板と、半導体基板表面に形成されたコンタクト領域と、半導体基板上に形成された層間絶縁膜と、層間絶縁膜内にコンタクト領域まで達する線状に延設された開口溝と、開口溝内に埋設されコンタクト領域に電気的に接続された導電層とを備えるスタンダードセルを開示している。

## 【先行技術文献】

### 【特許文献】

#### [0010]

【特許文献1】特開2001-15602号公報

【特許文献2】特開2001-189427号公報

【特許文献3】特開2005-236107号公報

【特許文献4】特開平8-222640号公報

【特許文献 5 】特開 2 0 0 8 - 4 7 9 0 号公報

【特許文献 6 】特開平 7 - 2 4 9 7 4 7 号公報

【特許文献7】特開2009-158728号公報

### 【発明の概要】

【発明が解決しようとする課題】

#### [0011]

本発明は、チップ面積をさらに小さくすることができるスタンダードセル、スタンダードセルを備えた半導体装置、およびスタンダードセルの配置配線方法を提供することを目的とする。

# 【課題を解決するための手段】

#### [0012]

本発明に基づく半導体装置は、半導体基板の表面に形成された第1および第2スタンダードセルを備える半導体装置である。

#### [0013]

上記第1スタンダードセルは、上記半導体基板の上記表面に形成された帯状の第1不純物拡散領域と、上記半導体基板の上記表面に形成され、上記第1不純物拡散領域に対向する第1機能素子領域と、上記半導体基板の上記表面の上方に配設され、上記第1不純物拡散領域の上方において上記第1不純物拡散領域に沿うように延在する第1幹線部および上記第1幹線部から上記第1機能素子領域の上方に向かって延在する第1延在部を含む第1

10

20

30

30

40

金属層と、を有する。

### [0014]

上記第2スタンダードセルは、上記半導体基板の上記表面に形成され、上記第1不純物拡散領域に連続する帯状の第2不純物拡散領域と、上記半導体基板の上記表面に形成され、上記第2不純物拡散領域に対向する第2機能素子領域と、上記半導体基板の上記表面における上記第2不純物拡散領域および上記第2機能素子領域の間に形成され、上記第2不純物拡散領域および上記第2機能素子領域を電気的に接続する接続用不純物拡散領域と、を有する。

### [0015]

上記第1金属層および上記第2機能素子領域は、上記第1幹線部、上記第1不純物拡散領域、上記第2不純物拡散領域、および上記接続用不純物拡散領域を通して電気的に接続されており、上記第1金属層の上記第1幹線部は、上記第2不純物拡散領域の上方に到達しない長さで、上記第1不純物拡散領域の上方において上記第1不純物拡散領域に沿うように延在している。

本発明の他の局面に基づく半導体装置は、半導体基板の表面に形成された第1および第 2 スタンダードセルを備える半導体装置であって、上記第 1 スタンダードセルは、上記半 導体基板の上記表面に形成された帯状の第1不純物拡散領域と、上記半導体基板の上記表 面に形成され、上記第1不純物拡散領域に対向する第1機能素子領域と、上記半導体基板 の上記表面の上方に配設され、上記第1不純物拡散領域の上方において上記第1不純物拡 散領域に沿うように延在する第1幹線部および上記第1幹線部から上記第1機能素子領域 の上方に向かって延在する第1延在部を含む第1金属層と、を有し、上記第2スタンダー ドセルは、上記半導体基板の上記表面に形成され、上記第1不純物拡散領域に連続する帯 状の第2不純物拡散領域と、上記半導体基板の上記表面に形成され、上記第2不純物拡散 領域に対向する第2機能素子領域と、上記半導体基板の上記表面における上記第2不純物 拡散領域および上記第2機能素子領域の間に形成され、上記第2不純物拡散領域および上 記第2機能素子領域を電気的に接続する接続用不純物拡散領域と、を有し、上記第1金属 層および上記第2機能素子領域は、上記第1幹線部、上記第1不純物拡散領域、上記第2 不純物拡散領域、および上記接続用不純物拡散領域を通して電気的に接続されており、上 記半導体基板の上記表面に形成された第3スタンダードセルをさらに備え、上記第3スタ ンダードセルは、上記半導体基板の上記表面に形成され、上記第2不純物拡散領域を挟ん で上記第1不純物拡散領域の反対側に位置し、上記第2不純物拡散領域に連続する帯状の 第3不純物拡散領域と、上記半導体基板の上記表面に形成され、上記第3不純物拡散領域 に対向する第3機能素子領域と、を有し、上記半導体基板の上記表面の上方に第2金属層 が配設され、上記第2金属層は、上記第2不純物拡散領域の上方において上記第2不純物 拡散領域に沿うように延在する第2幹線部と、上記第2幹線部から上記第1機能素子領域 の上方に向かって延在する第2延在部と、上記第2幹線部から上記第3機能素子領域の上 方に向かって延在する第3延在部と、を有し、上記第1機能素子領域および上記第3機能 素子領域は、上記第2幹線部、上記第2延在部および上記第3延在部を通して電気的に接 続され、上記第2金属層の上記第2幹線部が延在している平面高さは、上記第1金属層が 形成されている平面高さ以下である。

本発明のさらに他の局面に基づく半導体装置は、半導体基板の表面に形成された第1および第2スタンダードセルを備える半導体装置であって、上記第1スタンダードセルは、上記半導体基板の上記表面に形成された帯状の第1不純物拡散領域と、上記半導体基板の上記表面に形成され、上記第1不純物拡散領域の上方において上記第1不純物拡散領域に沿うように延在する第1幹線部および上記第1幹線部から上記第1不純物拡散領域に沿うように延在する第1幹線部および上記第1幹線部から上記第1機能素子領域の上方に向かって延在する第1延在部を含む第1金属層と、を有し、上記第2スタンダードセルは、上記半導体基板の上記表面に形成され、上記第1不純物拡散領域に連続する帯状の第2不純物拡散領域と、上記半導体基板の上記表面に形成され、上記第2不純物拡散領域に対向する第2機能素子領域と、上記半導体基板の上記表面における上記第2

10

20

30

40

20

30

40

50

不純物拡散領域および上記第2機能素子領域の間に形成され、上記第2不純物拡散領域および上記第2機能素子領域を電気的に接続する接続用不純物拡散領域と、を有し、上記第1金属層および上記第2機能素子領域は、上記第1幹線部、上記第1不純物拡散領域、上記第2不純物拡散領域、および上記接続用不純物拡散領域を通して電気的に接続されており、上記半導体基板の上記表面に形成された第3スタンダードセルをさらに備え、上記第3スタンダードセルは、上記半導体基板の上記表面に形成され、上記第2不純物拡散領域を挟んで上記第2機能素子領域の反対側に位置し、上記第2不純物拡散領域に対向する第3機能素子領域を有し、上記半導体基板の上記表面の上方において上記第2不純物拡散領域を跨ぐように、上記第2機能素子領域および上記第3機能素子領域を電気的に接続する第2金属層が延設され、上記第2金属層が上記第2不純物拡散領域を跨ぐように延在している平面高さは、上記第1金属層が形成されている平面高さ以下である。

[0016]

本発明に基づくスタンダードセルは、半導体基板の表面に形成された第 1 および第 2 スタンダードセルを含むスダンタードセルである。

[0017]

上記第1スタンダードセルは、上記半導体基板の上記表面に形成された第1機能素子領域と、上記半導体基板の上記表面に形成され、上記第1機能素子領域の両側を挟んで対向して配置される帯状の第1不純物拡散領域と、上記半導体基板の上記表面の上方に配設され、各々の上記第1不純物拡散領域の上方において各々の上記第1不純物拡散領域に沿うように延在する幹線部および各々の上記幹線部から上記第1機能素子領域の上方に向かって延在する延在部を含む金属層と、を有する。

[0018]

上記第2スタンダードセルは、上記半導体基板の上記表面に形成された第2機能素子領域と、上記半導体基板の上記表面に形成され、上記第2機能素子領域の両側を挟んで対向して配置されるとともに、上記第1不純物拡散領域にそれぞれ連続する帯状の第2不純物拡散領域と、上記半導体基板の上記表面に形成され、各々の上記第2不純物拡散領域と上記第2機能素子領域との間を電気的に接続する接続用不純物拡散領域と、を有する。

[0019]

上記金属層および上記第 2 機能素子領域は、上記幹線部、上記第 1 不純物拡散領域、上記第 2 不純物拡散領域、および上記接続用不純物拡散領域を通して電気的に接続されて<u>おり、上記金属層の上記幹線部は、上記第 2 不純物拡散領域の上方に到達しない長さで、上</u>記第 1 不純物拡散領域の上方に延在している

[0020]

本発明に基づくスタンダードセルの配置配線方法は、半導体基板の表面に形成された第 1 および第 2 スタンダードセルを備える半導体装置におけるスタンダードセルの配置配線 方法であって、上記第1スタンダードセルは、上記半導体基板の上記表面に形成された帯 状の第1不純物拡散領域と、上記半導体基板の上記表面に形成され、上記第1不純物拡散 領域に対向する第1機能素子領域と、上記半導体基板の上記表面の上方に配設され、上記 第1不純物拡散領域の上方において上記第1不純物拡散領域に沿うように延在する第1幹 線部および上記第1幹線部から上記第1機能素子領域の上方に向かって延在する第1延在 部を含む第1金属層と、を有し、上記第2スタンダードセルは、上記半導体基板の上記表 面に形成され、上記第1不純物拡散領域に連続する帯状の第2不純物拡散領域と、上記半 導体基板の上記表面に形成され、上記第2不純物拡散領域に対向する第2機能素子領域と 上記半導体基板の上記表面における上記第2不純物拡散領域および上記第2機能素子領 域の間に形成され、上記第2不純物拡散領域および上記第2機能素子領域を電気的に接続 する接続用不純物拡散領域と、を有し、上記第1金属層および上記第2機能素子領域は、 上記第1幹線部、上記第1不純物拡散領域、上記第2不純物拡散領域、および上記接続用 不純物拡散領域を通して電気的に接続されており、上記第2スタンダードセルのパターン 情報が格納されたセルライブラリを準備する工程と、所定の回路接続情報を配置配線シス テムに入力する工程と、上記配置配線システムが、上記第2スタンダードセル以外の所定のスタンダードセルの上記パターン情報を上記セルライブラリから読み出し、上記回路接続情報に対応するように複数の上記スタンダードセルの上記パターン情報を配置する工程と、複数の上記スタンダードセル間を結ぶ配線の密度が所定値を超える配線混雑領域の発生を検出する工程と、上記配置配線システムが、上記第2スタンダードセルの上記パターン情報を上記セルライブラリから読み出し、上記配線混雑領域に含まれる上記スタンダードセルを上記第2スタンダードセルに置換する工程と、を備える。

### [0021]

本発明の他の局面に基づくスタンダードセルの配置配線方法は、半導体基板の表面に形 成された第1および第2スタンダードセルを含むスタンダードセルの配置配線方法であっ て、上記第1スタンダードセルは、上記半導体基板の上記表面に形成された第1機能素子 領域と、上記半導体基板の上記表面に形成され、上記第1機能素子領域の両側を挟んで対 向して配置される帯状の第1不純物拡散領域と、上記半導体基板の上記表面の上方に配設 され、各々の上記第1不純物拡散領域の上方において各々の上記第1不純物拡散領域に沿 うように延在する幹線部および各々の上記幹線部から上記第1機能素子領域の上方に向か って延在する延在部を含む金属層と、を有し、上記第2スタンダードセルは、上記半導体 基板の上記表面に形成された第2機能素子領域と、上記半導体基板の上記表面に形成され 、上記第2機能素子領域の両側を挟んで対向して配置されるとともに、上記第1不純物拡 散領域にそれぞれ連続する帯状の第2不純物拡散領域と、上記半導体基板の上記表面に形 成され、各々の上記第2不純物拡散領域と上記第2機能素子領域との間を電気的に接続す る接続用不純物拡散領域と、を有し、上記金属層および上記第2機能素子領域は、上記幹 線部、上記第1不純物拡散領域、上記第2不純物拡散領域、および上記接続用不純物拡散 領域を通して電気的に接続されており、上記第2スタンダードセルのパターン情報が格納 されたセルライブラリを準備する工程と、所定の回路接続情報を配置配線システムに入力 する工程と、上記配置配線システムが、上記第2スタンダードセル以外の所定のスタンダ ードセルの上記パターン情報を上記セルライブラリから読み出し、上記回路接続情報に対 応するように複数の上記スタンダードセルの上記パターン情報を配置する工程と、複数の 上記スタンダードセル間を結ぶ配線の密度が所定値を超える配線混雑領域の発生を検出す る工程と、上記配置配線システムが、上記第2スタンダードセルの上記パターン情報を上 記セルライブラリから読み出し、上記配線混雑領域に含まれる上記スタンダードセルを上 記第2スタンダードセルに置換する工程と、を備える。

# 【発明の効果】

# [0022]

本発明によれば、チップ面積をさらに小さくすることができるスタンダードセル、スタンダードセルを備えた半導体装置、およびスタンダードセルの配置配線方法を得ることができる。

# 【図面の簡単な説明】

- [0023]

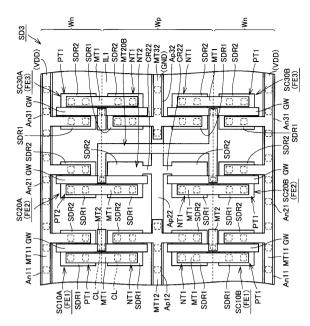

- 【図1】実施の形態1における半導体装置の全体的な構成を示す平面図である。

- 【図2】図1におけるII線で囲まれる領域の拡大平面図である。

- 【図3】実施の形態1の半導体装置における複数のスタンダードセルの一部を示す平面図 である

- 【図4】図3におけるIV-IV線に関する矢視断面図である。

- 【図5】図3におけるV-V線に関する矢視断面図である。

- 【図6】図3における矢印VI方向からスタンダードセルを見た斜視図である。

- 【図7】実施の形態1の他の形態における複数のスタンダードセルの一部を示す平面図である。

- 【図8】実施の形態2における複数のスタンダードセルの一部を示す平面図である。

- 【図9】実施の形態3における複数のスタンダードセルの一部を示す平面図である。

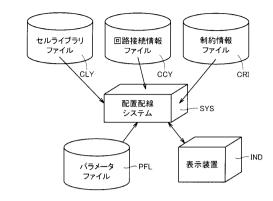

- 【図10】実施の形態4における配置配線方法の構成を模式的に示す図である。

20

10

30

40

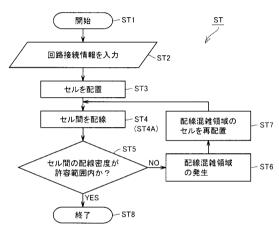

- 【図11】実施の形態4における配置配線方法の各ステップを示す図である。

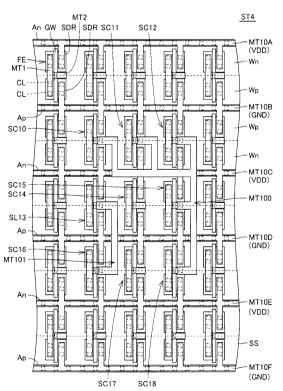

- 【図12】実施の形態4におけるステップST4が完了した状態の一例を示す平面図である。

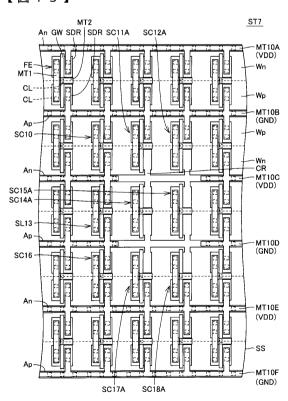

- 【図13】実施の形態4におけるステップST7が完了した状態の一例を示す平面図である。

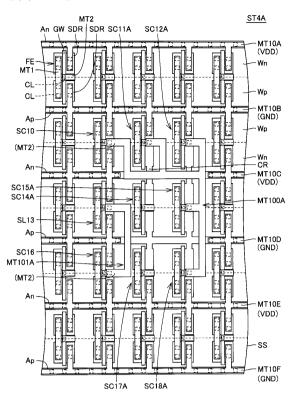

- 【図14】実施の形態4におけるステップST4Aが完了した状態の一例を示す平面図である。

【発明を実施するための形態】

[0024]

本発明に基づいた各実施の形態におけるスタンダードセル、スタンダードセルを備えた 半導体装置およびスタンダードセルの配置配線方法について、以下、図面を参照しながら 説明する。各実施の形態の説明において、個数、量などに言及する場合、特に記載がある 場合を除き、本発明の範囲は必ずしもその個数、量などに限定されない。各実施の形態の 説明において、同一の部品、相当部品に対しては、同一の参照番号を付し、重複する説明 は繰り返さない場合がある。

[0025]

「実施の形態1:半導体装置SD1]

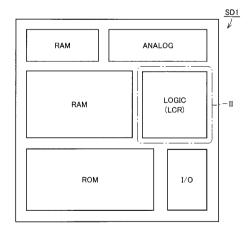

図1~図6を参照して、本実施の形態における半導体装置SD1について説明する。図1は、半導体装置SD1の全体的な構成を示す平面図である。図1を参照して、半導体装置SD1は、その表面に、RAM(Random Access Memory)、ROM(Read Only Memory)、ANALOG、LOGIC(以下、論理回路領域LCRと称する)、および入出力領域I/O等を備えている。

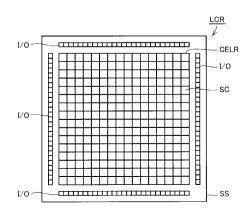

[0026]

図 2 は、図 1 における I I 線で囲まれる領域の拡大平面図であり、半導体装置 S D 1 における論理回路領域 L C R を示している。図 2 を参照して、論理回路領域 L C R は、スタンダードセル領域 C E L R の周囲に位置する入出力領域 I / O、および外部との入出力に用いられるパッド(図示せず)等を有している。

[0027]

スタンダードセル領域 CELRは、半導体基板 SSの表面に規定されている。スタンダードセル SCは、スタンダードセル領域 CELR内における半導体基板 SSの表面に形成されている。各スタンダードセル SCは、略マトリックス状に配列されている。

[0028]

(スタンダードセルSC)

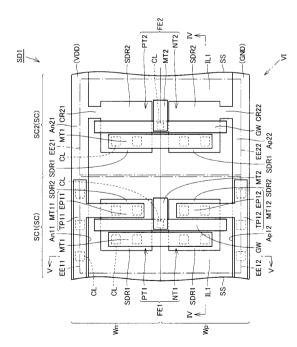

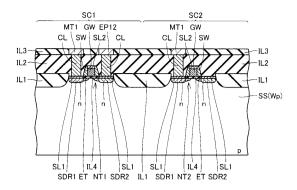

図3は、スタンダードセルSС1(第1スタンダードセル)およびスタンダードセルSС2(第2スタンダードセル)を示す平面図である。図4は、図3におけるIV-IV線に関する矢視断面図である。図5は、図3におけるV-V線に関する矢視断面図である。図6は、図3における矢印VI方向からスタンダードセルSС1,SС2を見た斜視図である。

[0029]

図 3 を参照して、半導体装置 S D 1 は、スタンダードセル S C 1 , S C 2 を備えている。スタンダードセル S C 1 , S C 2 は、半導体装置 S D 1 における複数のスタンダードセル S C の一部である。スタンダードセル S C 1 , S C 2 の各々は、一例として C M O S (Complementary Metal Oxide Semiconductor)構造を呈している。

[0030]

$( \lambda S )$

スタンダードセルSC1は、半導体基板SS、n型ウェル領域Wn、p型ウェル領域Wp、帯状のn <sup>†</sup> 型拡散領域An11(第1不純物拡散領域)、帯状のp <sup>†</sup> 型拡散領域Ap12、絶縁層IL1~IL3(図4参照)、機能素子領域FE1(第1機能素子領域)、金属層MT1、金属層MT1、金属層MT11(第1金属層)、金属層MT12、および複数の導電層CLを有している。

10

20

30

40

20

30

40

#### [0031]

図5を参照して、p型ウェル領域Wpは、半導体基板SSの表面を含むように半導体基板SSに形成されている。n型ウェル領域Wnは、p型ウェル領域Wpの表面に選択的に形成されている。

## [0032]

図3を再び参照して、スタンダードセルSC1は平面視矩形状に構成されている。スタンダードセルSC1は、対向する外縁EE11および外縁EE12を有している。外縁EE11,EE12は、スタンダードセルSC1,SC2が配列されている方向(図3紙面左右方向)に沿って延在している。またスタンダードセルSC1は、外縁EE11および外縁EE12に連続し、紙面上下方向に延在し且つ対向する外縁をも有している。当該外縁は、スタンダードセルSC1,SC2が配列されている方向(図3紙面左右方向)に対して垂直な方向に沿って延在している。

#### [0033]

$n^{+}$ 型拡散領域 A n 1 1 は、外縁 E E 1 1 に沿って n 型ウェル領域 W n の表面に形成されている(図 5 参照)。  $p^{+}$  型拡散領域 A p 1 2 は、外縁 E E 1 2 に沿って p 型ウェル領域 W p の表面に形成されている。各拡散領域 A n 1 1 , A p 1 2 の各表面には、シリサイド層 S L 3 (図 5 参照)が形成されている。シリサイド層 S L 3 は、図 3 および図 6 には記載していない。

## [0034]

## (機能素子領域 F E 1)

機能素子領域 FE1 は、半導体基板 SS の表面に形成され、 $n^{+}$  型拡散領域 An11 と  $p^{+}$  型拡散領域 Ap12 との間に位置している。機能素子領域 FE1 および  $n^{+}$  型拡散領域 An11 は、間隔を空けて対向している。機能素子領域 FE1 および  $p^{+}$  型拡散領域 Ap12 も、間隔を空けて対向している。

#### [0035]

機能素子領域FE1は、nチャネルMOS型のトランジスタNT1と、pチャネルMOS型のトランジスタPT1とを含んでいる。トランジスタNT1は、p型ウェル領域Wpの表面に形成されている。トランジスタPT1は、n型ウェル領域Wnの表面に形成されている。

## [0036]

### [0037]

図4を参照して、トランジスタNT1は、p型ウェル領域Wp、n型のソースドレイン領域SDR1,SDR2、n型のエクステンション領域ET、ゲート電極層GW、ゲート絶縁層IL4、サイドウォールSW、およびシリサイド層SL1,SL2は、図3および図6には記載していない。

# [0038]

ソースドレイン領域SDR1およびソースドレイン領域SDR2は、p型ウェル領域Wpの表面に形成され、間隔を空けて対向している。

# [0039]

エクステンション領域ETは、ソースドレイン領域SDR1およびソースドレイン領域SDR2の間の領域(以下、チャネル領域と称する)に形成されている。一方のエクステンション領域ETはソースドレイン領域SDR1に重なっており、他方のエクステンション領域ETはソースドレイン領域SDR2に重なっている。各エクステンション領域ETは、次述する各サイドウォールSWの下方を含むように延在している。

## [0040]

20

30

50

チャネル領域の表面に、ゲート絶縁層 I L 4 が形成されている。ゲート絶縁層 I L 4 の表面に、ゲート電極層 G W が形成されている。ゲート電極層 G W の表面に、シリサイド層 S L 2 が形成されている。ゲート電極層 G W の両側面に、サイドウォール S W がそれぞれ 形成されている。

### [0041]

トランジスタNT1およびトランジスタPT1(図3参照)は、導電型が異なる他は略同様に構成される。なお、トランジスタNT1およびトランジスタPT1におけるチャネル領域の幅、長さ、深さ等については、各トランジスタNT1,PT1の仕様に応じて、それぞれ同様に構成されていても、それぞれ異なって構成されていてもよい。ゲート電極層GW、ゲート絶縁層IL4、サイドウォールSW、およびシリサイド層SL2は、トランジスタNT1およびトランジスタPT1の双方の構成要素として共通している。

[0042]

図4を参照して、絶縁層IL1は、上述とおり半導体基板SSの表面に形成されている。各ソースドレイン領域SDR1,SDR2(シリサイド層SL1)の表面およびゲート電極層GWの表面は、絶縁層IL1の表面に(次述する絶縁層IL2側に向かって)露出している。

### [0043]

絶縁層IL2は、絶縁層IL1、各ソースドレイン領域SDR1,SDR2、およびゲート電極層GWの各表面を覆うように形成されている。絶縁層IL2および次述する絶縁層IL3は、図3および図6には記載していない。

[0044]

絶縁層IL2には、絶縁層IL2の表面から各ソースドレイン領域SDR1,SDR2(シリサイド層SL1)の表面に到達する複数のコンタクトホールが形成されている。これらの各コンタクトホールの内部に、導電層CLが形成されている。

#### [0045]

絶縁層IL2には、絶縁層IL2の表面からゲート電極層GW(シリサイド層SL2)の表面に到達するコンタクトホールも形成されている(図3参照)。このコンタクトホールの内部にも、導電層CLが形成されている。

[0046]

絶縁層IL3は、絶縁層IL2およびこれらの導電層CLの各表面を覆うように形成されている。絶縁層IL3には、複数の配線用溝が形成されている。各配線用溝の内部の一部において、各導電層CLの表面が露出している。各配線用溝の平面形状は、後述する各金属層MT1,MT2,MT11,MT12(図3参照)の形状に対応している。

[0047]

図5を参照して、n<sup>+</sup>型拡散領域An11(シリサイド層SL3)の表面およびp<sup>+</sup>型拡散領域Ap12(シリサイド層SL3)の表面も、絶縁層IL1の表面に(絶縁層IL2側に向かって)露出している。絶縁層IL2は、各拡散領域An11,Ap12の各表面を覆うように形成されている。

[0048]

絶縁層IL2には、絶縁層IL2の表面から各拡散領域An11,Ap12(シリサイ 40ド層SL3)の表面に到達する複数のコンタクトホールが形成されている。これらのコンタクトホールの内部に、導電層CLが形成されている。

[0049]

絶縁層IL3は、絶縁層IL2およびこれらの導電層CLの各表面を覆うように形成されている。絶縁層IL3には、複数の配線用溝が形成されている。各配線溝の内部の一部において、各導電層CLの表面が露出している。各配線用溝の平面形状は、次述する各金属層MT11,MT12(図3参照)の形状に対応している。

[0050]

(金属層MT1,MT2,MT11,MT12)

図 3 および図 6 を参照して、各金属層 M T 1 , M T 2 , M T 1 1 , M T 1 2 は、上記の

各配線用溝の内部に形成されている。各金属層MT1,MT2,MT11,MT12は、 半導体基板SSの表面の上方(絶縁層IL3が形成されている高さ)に位置している。

### [ 0 0 5 1 ]

金属層MT1は、トランジスタPT1のソースドレイン領域SDR1およびトランジスタNT1のソースドレイン領域SDR1の各上方を跨ぐように配設されている。金属層MT1は、各ソースドレイン領域SDR1の各表面に形成された導電層CLを通して、トランジスタPT1のソースドレイン領域SDR1およびトランジスタNT1のソースドレイン領域SDR1を電気的に接続している。

### [0052]

金属層MT2は、ゲート電極層GWの上方の一部を含むように配設されている。金属層MT2は、ゲート電極層GWの表面に形成された導電層CLを通して、ゲート電極層GWに電気的に接続されている。金属層MT2は、信号線に相当する。

#### [0053]

金属層MT11は、幹線部TP11(第1幹線部)および延在部EP11(第1延在部)を有している。幹線部TP11は、n<sup>+</sup>型拡散領域An11の上方においてn<sup>+</sup>型拡散領域An11に沿うように延在している。延在部EP11は、幹線部TP11からトランジスタPT1のソースドレイン領域SDR2の上方に向かって延在している。

#### [0054]

金属層 M T 1 1 は、 n  $^+$  型拡散領域 A n 1 1 およびトランジスタ P T 1 のソースドレイン領域 S D R 2 の各表面に形成された導電層 C L を通して、 n  $^+$  型拡散領域 A n 1 1 およびトランジスタ P T 1 のソースドレイン領域 S D R 2 を電気的に接続している。金属層 M T 1 1 は、電源線に相当する。

### [0055]

金属層MT11を通して、トランジスタPT1のソースドレイン領域SDR2にVDD電位を印加することができる。金属層MT11を通して、n <sup>†</sup>型拡散領域An11の電位を固定することができる。

#### [0056]

金属層 M T 1 2 は、幹線部 T P 1 2 および延在部 E P 1 2 を有している。幹線部 T P 1 2 は、 p <sup>+</sup> 型拡散領域 A p 1 2 の上方において p <sup>+</sup> 型拡散領域 A p 1 2 に沿うように延在している。延在部 E P 1 2 は、幹線部 T P 1 2 からトランジスタ N T 1 のソースドレイン領域 S D R 2 の上方に向かって延在している。

## [0057]

金属層 M T 1 2 は、 p  $^+$  型拡散領域 A p 1 2 およびトランジスタ N T 1 のソースドレイン領域 S D R 2 の各表面に形成された導電層 C L を通して、 p  $^+$  型拡散領域 A p 1 2 およびトランジスタ N T 1 のソースドレイン領域 S D R 2 を電気的に接続している。金属層 M T 1 2 も、電源線に相当する。

# [0058]

金属層MT12を通して、トランジスタNT1のソースドレイン領域SDR2にGND電位を印加することができる。金属層MT12を通して、p <sup>†</sup> 型拡散領域Ap12の電位を固定することができる。

# [0059]

#### (スタンダードセルSC2)

図3を主として参照して、スタンダードセルSC2は、半導体基板SS、n型ウェル領域Wn、p型ウェル領域Wp、帯状のn゚型拡散領域An21(第2不純物拡散領域)、帯状のp゚型拡散領域Ap22、絶縁層IL1~IL3(図4参照)、機能素子領域FE2(第2機能素子領域)、n゚型拡散領域CR21(接続用不純物拡散領域)、p゚型拡散領域CR22、金属層MT1、金属層MT2、および複数の導電層CLを有している。

#### [0060]

スタンダードセルSC1と同様に、p型ウェル領域Wpは、半導体基板SSの表面を含むように半導体基板SSに形成されている。n型ウェル領域Wnは、p型ウェル領域Wp

10

20

30

40

20

30

40

の表面に選択的に形成されている。

## [0061]

スタンダードセルSC2は、平面視矩形状に構成されている。スタンダードセルSC2は、スタンダードセルSC1の幹線部TP11,TP12が延びる方向側において、スタンダードセルSC1に隣接している。スタンダードセルSC2は、対向する外縁EE21および外縁EE22を有している。外縁EE21,EE22は、スタンダードセルSC1,SC2が配列されている方向(図3紙面左右方向)に沿って延在している。またスタンダードセルSC2は、外縁EE21および外縁EE22に連続し、紙面上下方向に延在し且つ対向する外縁をも有している。当該外縁は、スタンダードセルSC1,SC2が配列されている方向(図3紙面左右方向)に対して垂直な方向に沿って延在している。

[0062]

$n^{+}$  型拡散領域 A  $n^{+}$  2 1 は、外縁 E E 2 1 に沿って  $n^{+}$  型拡散領域 A  $n^{+}$  2 1 は、スタンダードセル S C 1 における  $n^{+}$  型拡散領域 A  $n^{+}$  2 1 に 2 1 に 3 的に接続されている。

## [0063]

$p^{+}$  型拡散領域 A p 2 2 は、外縁 E E 2 2 に沿って p 型ウェル領域 W p の表面に形成されている。  $p^{+}$  型拡散領域 A p 2 2 は、スタンダードセル S C 1 における  $p^{+}$  型拡散領域 A p 1 2 に連続し、  $p^{+}$  型拡散領域 A p 1 2 に電気的に接続されている。

#### [0064]

各拡散領域An21,Ap22の各表面には、スタンダードセルSC1における各拡散 領域An11,Ap12と同様に、シリサイド層(図示せず)が形成されている。

#### [0065]

### (機能素子領域 F E 2)

機能素子領域FE2は、半導体基板SSの表面に形成され、n<sup>+</sup>型拡散領域An21とp<sup>+</sup>型拡散領域Ap22との間に位置している。機能素子領域FE2およびn<sup>+</sup>型拡散領域An21は、間隔を空けて対向している。機能素子領域FE2およびp<sup>+</sup>型拡散領域Ap22も、間隔を空けて対向している。

#### [0066]

機能素子領域FE2は、nチャネルMOS型のトランジスタNT2と、pチャネルMOS型のトランジスタPT2とを含んでいる。トランジスタNT2は、スタンダードセルSC1におけるトランジスタNT1と略同様に構成される。トランジスタPT2は、スタンダードセルSC1におけるトランジスタPT1と略同様に構成される。なお、各トランジスタNT1,NT2,PT1,PT2におけるチャネル領域の幅、長さ、深さ等については、各トランジスタNT1,NT2,PT1,PT2の仕様に応じて、それぞれ同様に構成されていても、それぞれ異なって構成されていてもよい。

#### [0067]

$n^+$  型拡散領域 CR21 は、半導体基板 SS の表面に形成され、 $n^+$  型拡散領域 An2 1 とトランジスタ PT2 との間に位置している。 $n^+$  型拡散領域 CR21 は、 $n^+$  型拡散領域 An21 と、トランジスタ PT2 のソースドレイン領域 SDR2 とを電気的に接続している。 $n^+$  型拡散領域 CR21 の表面には、シリサイド層(図示せず)が形成されているとよい。 $n^+$  型拡散領域 An21 とトランジスタ PT2 との間は、 $n^+$  型拡散領域 CR21 が形成されている領域の他は絶縁層 IL1 によって分離されている。

#### [0068]

$p^+$  型拡散領域 CR22 は、半導体基板 SS の表面に形成され、 $p^+$  型拡散領域 Ap2 2 とトランジスタ NT2 との間に位置している。 $p^+$  型拡散領域 CR22 は、 $p^+$  型拡散領域 CR22 は、 $p^+$  型拡散領域 SDR2 とを電気的に接続している。 $p^+$  型拡散領域 CR22 の表面には、シリサイド層(図示せず)が形成されているとよい。 $p^+$  型拡散領域 SDR2 ととトランジスタ SDR2 との間は、 $p^+$  型拡散領域 SDR2 との間は、 $p^+$  型拡散領域 SDR2 との間は、 $p^+$  型拡散領域 SDR2 との形成されている領域の他は絶縁層 SDR2 によって分離されている。

### [0069]

図 4 を参照して、絶縁層 I L 1 は、半導体基板 S S の表面に形成されている。各ソースドレイン領域 S D R 1 , S D R 2 (シリサイド層 S L 1) の表面およびゲート電極層 G W の表面は、絶縁層 I L 1 の表面に(次述する絶縁層 I L 2 側に向かって)露出している。

## [0070]

絶縁層IL2は、絶縁層IL1、各ソースドレイン領域SDR1,SDR2、およびゲート電極層GWの各表面を覆うように形成されている。絶縁層IL2および次述する絶縁層IL3は、図3および図6には記載していない。

### [0071]

絶縁層IL2には、絶縁層IL2の表面から各ソースドレイン領域SDR1(シリサイド層SL1)の表面に到達する複数のコンタクトホールが形成されている。これらの各コンタクトホールの内部に、導電層CLが形成されている。

#### [0072]

絶縁層IL2には、絶縁層IL2の表面からゲート電極層GW(シリサイド層SL2)の表面に到達するコンタクトホールも形成されている(図3参照)。このコンタクトホールの内部にも、導電層CLが形成されている。

#### [0073]

絶縁層IL3は、絶縁層IL2およびこれらの導電層CLの各表面を覆うように形成されている。絶縁層IL3には、複数の配線用溝が形成されている。各配線用溝の内部の一部において、各導電層CLの表面が露出している。各配線用溝の平面形状は、後述する各金属層MT1,MT2(図3参照)の形状に対応している。

#### [0074]

$n^+$ 型拡散領域 A n 2 1 (シリサイド層)の表面および  $p^+$ 型拡散領域 A p 2 2 (シリサイド層)の表面も、絶縁層 I L 1 の表面に(絶縁層 I L 2 側に向かって)露出している。絶縁層 I L 2 は、各拡散領域 A n 2 1 , A p 2 2 の表面を覆うように形成されている。絶縁層 I L 3 は、絶縁層 I L 2 の表面を覆うように形成されている。

### [0075]

(金属層MT1,MT2)

図3を参照して、各金属層MT1,MT2は、上記の各配線用溝の内部に形成されている。各金属層MT1,MT2は、半導体基板SSの表面の上方(絶縁層IL3が形成されている高さ)に位置している。

### [0076]

金属層MT1は、トランジスタPT2のソースドレイン領域SDR1およびトランジスタNT2のソースドレイン領域SDR1の各上方を跨ぐように配設されている。金属層MT1は、各ソースドレイン領域SDR1の各表面に形成された導電層CLを通して、トランジスタPT2のソースドレイン領域SDR1およびトランジスタNT2のソースドレイン領域SDR1を電気的に接続している。

# [0077]

金属層MT2は、ゲート電極層GWの上方の一部を含むように配設されている。金属層MT2は、ゲート電極層GWの表面に形成された導電層CLを通して、ゲート電極層GWに電気的に接続されている。金属層MT2は、信号線に相当する。

# [0078]

ここで、スタンダードセルSС1における金属層MT11は、スタンダードセルSС2におけるトランジスタPT2のソースドレイン領域SDR2に電気的に接続されている。その電流経路は、金属層MT11の幹線部TP11、金属層MT11の幹線部TP11と $n^+$ 型拡散領域An11との間に形成された導電層СL、 $n^+$ 型拡散領域An11、 $n^+$ 型拡散領域An21、および $n^+$ 型拡散領域CR21の順で構成される。

#### [0079]

この電気的接続によって、金属層MT11を通して、スタンダードセルSC2におけるトランジスタPT2のソースドレイン領域SDR2にVDD電位を印加することができる。金属層MT11を通して、スタンダードセルSC2におけるn <sup>+</sup> 型拡散領域An21の

20

10

30

40

20

30

40

50

電位を固定することができる。  $n^+$ 型拡散領域 A n 2 1 および  $n^+$ 型拡散領域 C R 2 1 等の各表面にシリサイド層が形成されていることによって、この電流経路における電気抵抗値を低減することが可能となる。

#### [0800]

同様に、スタンダードセルSC1における金属層MT12は、スタンダードセルSC2におけるトランジスタNT2のソースドレイン領域SDR2に電気的に接続されている。その電流経路は、金属層MT12の幹線部TP12、金属層MT12の幹線部TP12と $p^+$ 型拡散領域Ap12との間に形成された導電層CL、 $p^+$ 型拡散領域Ap12、 $p^+$ 型拡散領域Ap22、および $p^+$ 型拡散領域CR22の順で構成される。

### [0081]

この電気的接続によって、金属層MT12を通して、スタンダードセルSC2におけるトランジスタNT2のソースドレイン領域SDR2にGND電位を印加することができる。金属層MT12を通して、スタンダードセルSC2におけるp <sup>†</sup> 型拡散領域Ap22の電位を固定することができる。p <sup>†</sup> 型拡散領域Ap22およびp <sup>†</sup> 型拡散領域CR22等の各表面にシリサイド層が形成されていることによって、この電流経路における電気抵抗を低減することが可能となる。

### [0082]

# (効果)

スタンダードセルSC2は、 $n^+$ 型拡散領域An21の上方(絶縁層IL3が形成されている高さ)に、機能素子領域FE2にVDD電位を印加するための金属層(電源線)を有していない。換言すると、 $n^+$ 型拡散領域An21の上方には、スタンダードセルSC2の機能素子領域FE2にVDD電位を印加するための金属層が形成されていない「空き領域」が存在している。

### [0083]

同様に、p<sup>+</sup>型拡散領域Ap22の上方(絶縁層IL3が形成されている高さ)にも、機能素子領域FE2にGND電位を印加するための金属層(電源線)が形成されていない空き領域が存在している。

#### [0084]

本実施の形態における半導体装置SD1によれば、これらの空き領域を活用して、これらの空き領域を含むように他の複数のスタンダードセル間を接続する金属層(図示せず)を配設することができる。半導体装置SD1によれば、他の複数のスタンダードセル間を接続する金属層を配設するためのリソースを増加させることができる。他の複数のスタンダードセル間を接続する金属層を、上述の絶縁層IL3が形成されている高さに配設することにより、この金属層と金属層MT1,MT2,MT11,MT12とを同一の工程において形成することもできる。

### [0085]

仮に、スタンダードセルSC2がこの空き領域を有していないとする。各拡散領域An 21,Ap22の上方には、スタンダードセルSC2の機能素子領域FE2にVDD電位 またはGND電位を印加するための金属層が配設される。この場合、この金属層を迂回す るように他の複数のスタンダードセル間を接続する他の金属層を配設する必要がある。迂 回するように配設された他の金属層によって、チップ面積が増大する。特に、近年のスタ ンダードセルの高集積化に伴い、他の金属層の迂回経路は、平面方向だけでなく高さ方向 にも複雑に広がり、チップ面積が増大するだけでなく、設計上の自由度も低くなる。

# [0086]

本実施の形態における半導体装置SD1によれば、他の複数のスタンダードセル間を接続する金属層が上記の空き領域を含むように配設されることによって、この金属層が迂回する距離(この金属層の全長)を短くすることができる。半導体装置SD1によれば、空き領域を活用することによってチップ面積が増大することを抑制でき、チップ面積がより小さい半導体装置を得ることが可能となる。半導体装置SD1によれば、スタンダードセルを配列するための設計上の自由度を高めることもできる。半導体装置SD1によれば、

スタンダードセルの高集積化を図ることも可能となる。

#### [0087]

半導体装置SD1によれば、空き領域を活用することによって他の複数のスタンダードセル間を接続する金属層の長さを短くすることもできる。他の複数のスタンダードセル間を接続する金属層の電流経路が短くなるため、当該金属層における電気抵抗値を低減することができる。半導体装置SD1によれば、空き領域を活用することによって、他の複数のスタンダードセルに形成されたトランジスタ素子をより高速に動作させることも可能となる。

### [0088]

半導体装置SD1において、トランジスタPT1にVDD電位を印加するための電流経路は、金属層MT11(幹線部TP11、延在部EP11)および導電層CLによって構成される。一方、トランジスタPT2にVDD電位を印加するための電流経路は、金属層MT11、導電層CL、n <sup>†</sup> 型拡散領域An11、n <sup>†</sup> 型拡散領域An21、およびn <sup>†</sup> 型拡散領域CR21である。

#### [0089]

金属層MT11とトランジスタPT2との間の電気抵抗は、金属層MT11とトランジスタPT1との間の電気抵抗よりも大きい。金属層MT11とトランジスタPT2との間には、金属層MT11とトランジスタPT1との間に比べてより大きな電圧降下が発生する。同様に、金属層MT12とトランジスタNT1との間の電気抵抗に比べてより大きな電圧降下が発生する。

#### [0090]

スタンダードセルSC2における当該電圧降下が許容できる範囲内となるように、使用する電圧または回路構成等の仕様に基づいて、スタンダードセルSC1,SC2の構成および配置などを決定するとよい。

### [0091]

「実施の形態1の他の構成:半導体装置SD1A]

図3を参照して、上述の実施の形態1の半導体装置SD1においては、上記の空き領域が、 $n^+$ 型拡散領域An21の上方および $p^+$ 型拡散領域Ap22の上方に存在している。上記の空き領域は、 $n^+$ 型拡散領域An21の上方または $p^+$ 型拡散領域Ap22のいずれか一方にのみ存在していてもよい。

### [0092]

図 7 を参照して、具体的には、半導体装置 SD1AOスタンダードセル SC2AOように、空き領域は  $p^+$ 型拡散領域 Ap22O上方にのみ存在していてもよい。スタンダードセル SC2Aにおいては、金属層 MT11O幹線部 TP11を  $n^+$ 型拡散領域 An21O上方に向かって延長するように幹線部 TP21が形成されている。

### [0093]

幹線部TP21と n <sup>†</sup> 型拡散領域 A n 2 1 との間に、複数の導電層 C L が形成されている。スタンダードセル S C 1 の延在部 E P 1 1 と同様に、幹線部TP21 からトランジスタPT2のソースドレイン領域 S D R 2 の上方に向かって延在する延在部 E P 2 1 が形成されている。

# [0094]

延在部EP21とトランジスタPT2のソースドレイン領域SDR2との間に、複数の 導電層CLが形成されている。スタンダードセルSC2Aにおいては、トランジスタPT 2とn<sup>+</sup>型拡散領域An21とは、絶縁層IL1によって分離されている。

#### [0095]

幹線部 T P 2 1 および延在部 E P 2 1 を通して、トランジスタ P T 2 のソースドレイン 領域 S D R 2 に V D D 電圧を印加する。幹線部 T P 2 1 および延在部 E P 2 1 を通して、 n <sup>+</sup>型拡散領域 A n 2 1 の電位を固定する。

### [0096]

空き領域がp<sup>+</sup>型拡散領域Ap22の上方にのみ存在している場合であっても、この空

10

20

40

30

20

30

40

50

き領域を活用して、この空き領域を含むように他の複数のスタンダードセル間を接続する 金属層 (図示せず)を配設することができる。空き領域を活用することによって、チップ 面積が増大することを抑制でき、チップ面積がより小さい半導体装置を得ることが可能と なる。他の複数のスタンダードセル間を接続する金属層を、上述の絶縁層 IL3が形成されている高さに配設することにより、この金属層と金属層 MT1, MT2, MT11, MT12とを同一の工程において形成することができる。

#### [0097]

[実施の形態2:半導体装置SD2]

図8を参照して、本実施の形態における半導体装置SD2について説明する。半導体装置SD2は、金属層MT20Aと、半導体基板SSの表面に形成されたスタンダードセルSC10A,SC10B,SC30A,SC30Bとを備えている。

#### [0098]

スタンダードセルSC10A,SC10B,SC30A,SC30Bは、上述の実施の形態1の半導体装置SD1におけるスタンダードセルSC1(図3左側参照)と略同様に構成される。スタンダードセルSC10A,SC10Bにおける各機能素子領域FE1、およびスタンダードセルSC30A,SC30Bにおける各機能素子領域FE3も、上述の実施の形態1の半導体装置SD1のスタンダードセルSC1(図3左側参照)における各機能素子領域FE1と略同様に構成される。

# [0099]

図8においては、図示上の便宜のため、スタンダードセルSC1における外縁EE11 , EE12(図3参照)、および外縁EE11 , EE12に連続する(紙面上下方向に延在する)外縁に対応するSC10A,SC10B,SC30A,SC30Bの外縁を記載していない。記載していない外縁は、それぞれ、スタンダードセルSC1における外縁EE11,EE12(図3参照)、および外縁EE11,EE12に連続する(図3紙面上下方向に延在する)外縁と同様に規定される。後述するスタンダードセルSC20A,SC20Bにおいても同様である。また、後述する図9,図12~図14においても同様である。

## [0100]

スタンダードセルSC10A,SC10Bにおける各機能素子領域FE1、およびスタンダードセルSC30A,SC30Bにおける各機能素子領域FE3は、半導体基板SSの表面に形成されている。

#### [0101]

スタンダードセルSC20A,SC20Bは、上述の実施の形態1の他の構成の半導体装置におけるスタンダードセルSC2A(図7右側参照)と略同様に構成される。スタンダードセルSC20A,SC20Bにおける各機能素子領域FE2も、上述の実施の形態1の他の構成の半導体装置SD1AのスタンダードセルSC2A(図7右側参照)における各機能素子領域FE2と略同様に構成される。スタンダードセルSC20A,SC20Bにおける各機能素子領域FE2は、半導体基板SSの表面に形成されている。

### [0102]

スタンダードセルS C 1 0 A , S C 2 0 A は相互に隣接し、スタンダードセルS C 2 0 A は相互に隣接し、スタンダードセルS C 2 0 B は相互に隣接し、スタンダードセルS C 2 0 B は相互に隣接し、スタンダードセルS C 2 0 B , S C 3 0 B も相互に隣接している。

# [0103]

スタンダードセルSC10AおよびスタンダードセルSC10Bは、 $p^+$ 型拡散領域A $p^+$ 12(第1不純物拡散領域)を挟んで略線対称に構成されている。 $p^+$ 型拡散領域A $p^+$ 12は、スタンダードセルSC10AおよびスタンダードセルSC10Bの双方の構成要素として共通している。

### [0104]

p<sup>+</sup>型拡散領域Ap12と、スタンダードセルSC10A,SC10Bにおける各機能

素子領域 F E 1 とは、間隔を空けて対向している。電源線 ( V D D 電位 ) に相当する金属 層 M T 1 2 は、スタンダードセル S C 1 0 A およびスタンダードセル S C 1 0 B の双方の 構成要素として共通している。

### [0105]

スタンダードセルSC20AおよびスタンダードセルSC20Bは、 $p^+$ 型拡散領域A $p^-$ 22(第2不純物拡散領域)を挟んで略線対称に構成されている。 $p^+$ 型拡散領域A $p^-$ 22は、スタンダードセルSC20AおよびスタンダードセルSC20Bの双方の構成要素として共通している。

### [0106]

$p^{+}$  型拡散領域 A p 2 2 と、スタンダードセルSC20 A ,SC20 B における各機能素子領域 F E 2 とは、間隔を空けて対向している。金属層 M T 1 2 、金属層 M T 3 2 、 p  $^{+}$  型拡散領域 A p 1 2 、 p  $^{+}$  型拡散領域 A p 1 2 、 p  $^{+}$  型拡散領域 C R 2 2 を通して、スタンダードセルSC20 A のトランジスタN T 2 のソースドレイン領域SDR2、およびスタンダードセルSC20 B のトランジスタN T 2 のソースドレイン領域SDR2の各々にGND電位が印加される。

## [0107]

スタンダードセルSC30AおよびスタンダードセルSC30Bは、 $p^+$ 型拡散領域A $p^-$ 32(第3不純物拡散領域)を挟んで略線対称に構成されている。 $p^+$ 型拡散領域A $p^-$ 32は、スタンダードセルSC30AおよびスタンダードセルSC30Bの双方の構成要素として共通している。

#### [0108]

p \* 型拡散領域 A p 3 2 と、スタンダードセル S C 3 0 A , S C 3 0 B における各機能素子領域 F E 3 (第 3 機能素子領域)とは、間隔を空けて対向している。電源線 ( V D D 電位 ) に相当する金属層 M T 3 2 は、スタンダードセル S C 3 0 A およびスタンダードセル S C 3 0 B の双方の構成要素として共通している。

### [0109]

スタンダードセルSC10Aにおける  $n^+$  型拡散領域A n 1 1、スタンダードセルSC 2 0 A における  $n^+$  型拡散領域A n 2 1、およびスタンダードセルSC 3 0 A における  $n^+$  型拡散領域A n 3 1 は連続している。  $n^+$  型拡散領域A n 3 1 は、  $n^+$  型拡散領域A n 2 1 を挟んで  $n^+$  型拡散領域A n 1 1 の反対側に位置している。これらは相互に電気的に接続されている。

## [0110]

スタンダードセルSC10Aにおけるp  $^+$  型拡散領域Ap12、スタンダードセルSC20Aにおけるp  $^+$  型拡散領域Ap22、およびスタンダードセルSC30Aにおけるp  $^+$  型拡散領域Ap32は連続している。p  $^+$  型拡散領域Ap32は、p  $^+$  型拡散領域Ap32を挟んでp  $^+$  型拡散領域Ap12の反対側に位置している。これらは相互に電気的に接続されている。

### [0111]

スタンダードセルSC20A,SC20Bは、p<sup>+</sup>型拡散領域Ap22の上方(絶縁層IL3が形成されている高さ)に、各機能素子領域FE2にGND電位を印加するための金属層(電源線)を有していない。換言すると、p<sup>+</sup>型拡散領域Ap22の上方には、スタンダードセルSC20A,SC20Bの各機能素子領域FE2にGND電位を印加するための金属層が形成されていない「空き領域」が存在している。この空き領域を活用して、この空き領域を含むように次述する金属層MT20Aが配設されている。

### [0112]

# (金属層MT20A)

金属層MT20Aは、半導体基板SSの表面の上方(たとえば、絶縁層IL3が形成されている高さ)に位置している。金属層MT20Aは、幹線部TP21(第2幹線部)、延在部EP21(第2延在部)、延在部EP31A(第3延在部)、および延在部EP31Bを有している。

10

20

30

40

#### [0113]

幹線部 TP21 は、 $p^+$ 型拡散領域 Ap22 の上方において  $p^+$ 型拡散領域 Ap22 に沿うように延在している。延在部 EP21 は平面視 L 字状に構成され、幹線部 TP21 からスタンダードセル SC10 Aの機能素子領域 FE1 の上方に到達するまで延在している。延在部 EP21 は、導電層 CL を通して、スタンダードセル SC10 Aの機能素子領域 FE1 におけるゲート電極層 GW と電気的に接続されている。

#### [0114]

延在部EP31Aは平面視L字状に構成され、幹線部TP21からスタンダードセルSC30Aの機能素子領域FE3の上方に到達するまで延在している。延在部EP31Aは、導電層CLを通して、スタンダードセルSC30Aの機能素子領域FE3におけるゲート電極層GWと電気的に接続されている。

#### [0115]

延在部EP31Bは平面視L字状に構成され、幹線部TP21からスタンダードセルSC30Bの機能素子領域FE3の上方に到達するまで延在している。延在部EP31Bは、導電層CLを通して、スタンダードセルSC30Bの機能素子領域FE3におけるゲート電極層GWと電気的に接続されている。

#### [0116]

金属層MT20Aは、スタンダードセルSC10Aの機能素子領域FE1と、スタンダードセルSC30Aの機能素子領域FE3とを電気的に接続している。金属層MT20Aは、スタンダードセルSC10Aの機能素子領域FE1と、スタンダードセルSC30Bの機能素子領域FE3とを電気的に接続している。

#### [0117]

### (効果)

p \* 型拡散領域Ap22の上方には、スタンダードセルSC20A,SC20Bの各機能素子領域FE2にGND電位を印加するための金属層が形成されていない空き領域が存在している。この空き領域を活用して、この空き領域を含むように金属層MT1,MT2,MT11,MT12,MT32と同じ層高さに金属層MT20Aが配設されている。金属層MT20Aを、金属層MT1,MT2,MT11,MT12,MT32と同一の工程において形成することができる。

## [0118]

仮に、スタンダードセルSC20A,SC20Bがこの空き領域を有していないとする。  $p^{+}$ 型拡散領域Ap22の上方には、スタンダードセルSC20A,SC20Bの各機能素子領域FE2にGND電位を印加するための一の金属層が配設される。

## [0119]

この場合、たとえばスタンダードセルSC10Aにおける機能素子領域FE1およびスタンダードセルSC30Aの機能素子領域FE3を電気的に接続するためには、上記一の金属層を迂回するように、他の金属層を配設する必要がある。スタンダードセルSC10Aにおける機能素子領域FE1およびスタンダードセルSC30Bについても同様である

### [0120]

半導体装置SD2によれば、空き領域を活用することによってチップ面積が増大することを抑制でき、チップ面積がより小さい半導体装置を得ることが可能となる。半導体装置SD2によれば、スタンダードセルを配列するための設計上の自由度を高めることもできる。半導体装置SD2によれば、スタンダードセルの高集積化を図ることも可能となる。

#### [0121]

半導体装置SD2によれば、空き領域を活用することによって金属層MT20Aの長さを短くすることもできる。金属層MT20Aにおける電流経路が短くなるため、金属層MT20Aにおける電気抵抗値を低減することができる。半導体装置SD2によれば、空き領域を活用することによって、スタンダードセルSC10Aの各機能素子領域FE1、およびスタンダードセルSC30A,SC30Bの各機能素子領域FE3に形成された各ト

10

20

30

40

ランジスタ素子をより高速に動作させることも可能となる。

### [0122]

「実施の形態2の他の構成]

上述の実施の形態2の半導体装置SD2においては、金属層MT20Aが、スタンダードセルSC30A,SC30Bにおける各機能素子領域FE3の双方に接続されているが、いずれか一方であってもよい。

#### [0123]

#### [0124]

金属層MT20Aが延在している平面高さは、半導体基板SSの表面の上方であれば、金属層MT11,MT12,MT32が形成されている平面高さ以下であってもよい。より好適には、金属層MT20Aの幹線部TP21が延在している平面高さが、金属層MT11,MT12,MT32が形成されている平面高さ以下であるとよい。金属層MT20Aが延在している平面高さが低ければ低いほど、上記の空き領域をより多く確保することができ、他の複数のスタンダードセル間を接続する金属層を配設するためのリソースを増加させることが可能となる。

### [0125]

金属層MT20Aは、金属層MT20Aの下面がゲート電極層GWの表面に接するように配設されていてもよい。この場合、金属層MT20Aとゲート電極層GWとは、導電層CLを介さずに電気的に接続されることが可能となる。

### [0126]

「実施の形態3:半導体装置SD3]

図9を参照して、本実施の形態における半導体装置SD3について説明する。半導体装置SD3は、金属層MT20Bと、半導体基板SSの表面に形成されたスタンダードセルSC10A,SC10B,SC20B,SC30A,SC30Bとを備えている。

### [0127]

各スタンダードセルSC10A,SC10B,SC20A,SC20B,SC30A,SC30Bは、上述の実施の形態2の半導体装置SD2における各スタンダードセルSC10A,SC10B,SC20A,SC20B,SC30A,SC30B(図8参照)と略同様に構成される。

## [0128]

(金属層MT20B)

金属層MT20Bは、半導体基板SSの表面の上方(たとえば、絶縁層IL3が形成されている高さ)に位置している。金属層MT20Bは、スタンダードセルSC20Aにおける機能素子領域FE2と、スタンダードセルSC20Bにおける機能素子領域FE2とを結ぶ方向と平行な方向に延在する部分を有している。当該部分は、 $p^{+}$ 型拡散領域Ap22の上方において $p^{+}$ 型拡散領域Ap22を跨いでいる。

# [0129]

金属層MT20Bの一方(図9紙面上方側)の端部は、平面視L字状に構成され、スタンダードセルSC20Aの機能素子領域FE2の上方に到達するまで延在している。金属層MT20Bの一方の端部は、導電層CLを通して、スタンダードセルSC20Aの機能素子領域FE2におけるゲート電極層GWと電気的に接続されている。

## [0130]

金属層MT20Bの他方(図9紙面下方側)の端部は、平面視T字状に構成され、スタンダードセルSC20Bの機能素子領域FE2の上方、およびスタンダードセルSC30Bの機能素子領域FE3の上方に到達するまで延在している。金属層MT20Bの他方の端部は、導電層CLを通して、スタンダードセルSC20Bの機能素子領域FE2におけ

10

20

30

40

るゲート電極層GW、およびスタンダードセルSC30Bの機能素子領域FE3におけるゲート電極層GWと電気的に接続されている。

#### [0131]

(効果)

$p^{+}$  型拡散領域 A  $p^{-}$  2 2 の上方には、スタンダードセルSC20A,SC20Bの各機能素子領域 F E 2 に G N D 電位を印加するための金属層が形成されていない空き領域が存在している。この空き領域を活用して、この空き領域を含むように金属層 M T 1 , M T 2 , M T 1 1 , M T 1 2 , M T 3 2 と同じ層高さに金属層 M T 2 0 B が配設されている。金属層 M T 2 0 B を、金属層 M T 1 , M T 2 , M T 1 1 , M T 1 2 , M T 1 2 , M T 3 2 と同一の工程において形成することができる。半導体装置 S D 3 によれば、上述の実施の形態 2 における半導体装置 S D 2 と同様の効果を得ることができる。

10

### [0132]

「実施の形態3の他の構成]

上述の実施の形態3の半導体装置SD3においては、金属層MT20Bが、スタンダードセルSC30A,SC30Bの各機能素子領域FE2,FE3の双方に接続されているが、いずれか一方であってもよい。

[0133]

金属層 M T 2 0 B が延在している高さは、半導体基板 S S の表面の上方であれば、金属層 M T 1 1 , M T 1 2 , M T 3 2 が形成されている平面高さ以下であるとよい。より好適には、金属層 M T 2 0 B が  $p^+$  型拡散領域 A p 2 2 を跨いでいる部分の平面高さが、金属層 M T 1 1 , M T 3 2 が形成されている平面高さ以下であるとよい。金属層 M T 2 0 B は、金属層 M T 2 0 B の下面がゲート電極層 G W の表面に接するように配設されていてもよい。

20

### [0134]

[実施の形態4]

図10~図14を参照して、本実施の形態におけるスタンダードセルの配置配線方法ST(図11参照)について説明する。配置配線方法STは、上述の実施の形態1~実施の形態3(各他の構成を含む)の半導体装置におけるスタンダードセルの配置配線方法である。

[0135]

30

図10は、配置配線方法STの構成を模式的に示す図である。配置配線方法STにおいては、まず、配置配線システムSYS、セルライブラリファイルCLY、回路接続情報ファイルCCY、制約情報ファイルCRI、パラメータファイルPFL、および表示装置INDが準備される。

[0136]

配置配線システムSYSは、所定のコマンドを受けて、複数のスタンダードセルおよび 各電源線の配置を設計する。配置配線システムSYSは、所定の他のコマンドを受けて、 複数のスタンダードセルおよび各電源線を結ぶ配線を設計する。

[0137]

セルライブラリファイルCLYは、上述の各実施の形態における各スタンダードセルのパターン情報を格納している。セルライブラリファイルCLYは、上述の実施の形態1におけるスタンダードセルSC2(図3右側参照)のパターン情報、または上述の実施の形態1の他の構成におけるスタンダードセルSC2A(図7右側参照)のパターン情報を格納している。

40

#### [0138]

回路接続情報ファイルCCYは、設計対象である半導体装置を構成する回路情報および各回路間の接続情報(回路図)を格納している。制約情報ファイルCRIは、配置配線に関する各種の制約情報(後述するチップサイズ、配線密度の許容範囲など)を格納している。パラメータファイルPFLは、設計対象である半導体装置に含まれる各トランジスタ素子の動作周波数、動作温度範囲、p型拡散領域、n型拡散領域、および各金属層の層抵

抗等の各情報を格納している。表示装置INDは、配置配線の経過および結果を表示する

### [0139]

図11を参照して、配置配線方法STにおける各ステップST1~ST8について説明する。

#### [0140]

ステップST1において、配置配線システムSYS、セルライブラリファイルCLY、 回路接続情報ファイルCCY、制約情報ファイルCRI、パラメータファイルPFL、お よび表示装置INDが準備される。

#### [0141]

ステップST2において、設計対象である半導体装置の所望の機能に応じて設計された 所定の回路接続情報が、回路接続情報ファイルCCYから配置配線システムSYSに入力 される。

## [0142]

ステップST3において、配置配線システムSYSは、上記の回路接続情報に対応するスタンダードセルのパターン情報をセルライブラリファイルCLYから読み出す。ステップST3において配置配線システムSYSが読み出すスタンダードセルのパターン情報には、上記の実施の形態1におけるスタンダードセルSC2(図3右側参照)のパターン情報および上記の実施の形態1の他の形態におけるスタンダードセルSC2A(図7右側参照)は含まれていない。

#### [0143]

配置配線システムSYSは、読み出したスタンダードセルのパターン情報を、上記の回路接続情報に対応するようにセル毎に配置する。このとき、チップサイズは予め所定の大きさに設定(固定)されているとよい。

#### [0144]

ステップST4において、配置配線システムSYSは、各スタンダードセル間における信号線および電源線を、上記の回路接続情報に対応するように配線する。図12は、配置配線方法STにおけるステップST4が完了した状態の一例を示している。

### [0145]

図12を参照して、スタンダードセルSC10~SC18を含む各スタンダードセルは、半導体基板SSの表面に形成されている。スタンダードセルSC10~SC18は、上述の実施の形態1におけるスタンダードセルSC1(図3参照)と略同様に構成される。 $n^+$ 型拡散領域Anおよび $p^+$ 型拡散領域Apは、半導体基板SSの表面において交互に等間隔で形成され、相互に平行な位置関係となっている。

# [0146]

金属層M T 1 0 A , M T 1 0 C , M T 1 0 E は、 n  $^+$  型拡散領域 A n の各上方において n  $^+$  型拡散領域 A n に沿うようにそれぞれ延在している。金属層 M T 1 0 B , M T 1 0 D , M T 1 0 F は、 p  $^+$  型拡散領域 A p の各上方において p  $^+$  型拡散領域 A p に沿うように それぞれ延在している。

### [0147]

金属層MT100は、スタンダードセルSC10,SC11,SC12,SC15,SC18の各金属層MT2(信号線)を電気的に接続している。金属層MT100は、金属層MT100、MT10Dを跨ぐように、金属層MT10C,MT10Dの上方に配設されている。金属層MT100と各金属層MT2の上方の一部を含むように配設されている。金属層MT100と各金属層MT2とは、金属層MT100と各金属層MT2の間に形成された導電層CLによって電気的に接続されている。

#### [0148]

金属層MT101は、スタンダードセルSC13,SC16の各金属層MT2(信号線)を電気的に接続している。金属層MT101は、金属層MT10Dを跨ぐように金属層MT10Dの上方に配設されている。金属層MT101は、各金属層MT2の上方の一部

10

20

40

30

20

30

40

を含むように配設されている。金属層MT101と各金属層MT2は、金属層MT101 と各金属層MT2の間に形成された導電層CLによって電気的に接続されている。

#### [0149]

ステップST5(図11参照)において、配置配線システムSYSは、複数のスタンダードセル(スタンダードセルSC10~SC18を含む)間を結ぶ配線の密度を測定する。配置配線システムSYSは、この配線密度と、制約情報ファイルCRI(図10参照)に予め設定された所定値(許容範囲)とを対比する。

### [0150]

この配線密度が所定値を超える領域が存在していた場合、配置配線システムSYSはその領域を配線混雑領域として検出する。配置配線システムSYSは、表示装置INDにその結果を表示させる。なお、複数のスタンダードセル間を結ぶ配線の密度がすべて所定値以下である場合、配置配線方法STは終了する(ステップST8)。

#### [0151]

本実施の形態においては、ステップST6において、配置配線システムSYSが金属層MT100,MT101が配設されている領域を配線混雑領域として検出する。

#### [0152]

ステップST7において、配置配線システムSYSは、配線混雑領域内におけるスタンダードセルSC11,SC12,SC14,SC15,SC17,SC18のそれぞれを再配置する。具体的には、配置配線システムSYSは、上記の実施の形態1におけるスタンダードセルSC2(図3右側参照)のパターン情報および上記の実施の形態1の他の形態におけるスタンダードセルSC2A(図7右側参照)のパターン情報を読み出し、スタンダードセルSC11,SC12,SC14,SC15,SC17,SC18のそれぞれを置換する。

#### [ 0 1 5 3 ]

スタンダードセルSC11,SC12,SC14,SC15,SC17,SC18は、スタンダードセルSC11A,SC12A,SC14A,SC15A,SC17A,SC18A(図13参照)に置換される。

# [0154]

スタンダードセルSC11A,SC12A,SC17A,SC18Aは、上述の実施の 形態1の他の構成におけるスタンダードセルSC2Aと略同様に構成される。スタンダー ドセルSC14A,SC15Aは、上述の実施の形態1におけるスタンダードセルSC2 と略同様に構成される。

### [0155]

スタンダードセルSC11A,SC12A,SC14A,SC15A,SC17A,S C18Aの各機能素子領域FEにおけるソースドレイン領域SDRと、各拡散領域An, Apとは、拡散領域CRを通してそれぞれ電気的に接続されている。

#### [0156]

スタンダードセルSC11AとスタンダードセルSC14Aとの間に位置する $n^{+}$ 型拡散領域Anの上方、およびスタンダードセルSC12AとスタンダードセルSC15Aとの間に位置する $n^{+}$ 型拡散領域Anの上方には空き領域が存在している。

# [0157]

同様に、スタンダードセルSC14AとスタンダードセルSC17Aとの間に位置する  $p^+$ 型拡散領域Apの上方、およびスタンダードセルSC15AとスタンダードセルSC18Aとの間に位置する $p^+$ 型拡散領域Apの上方には空き領域が存在している。

### [0158]

ステップST4A(図11参照)において、配置配線システムSYSは、上述の空き領域を活用して、各スタンダードセル間における信号線および電源線を上記の回路接続情報に対応するように再び配線する。図14は、配置配線方法STにおけるステップST4Aが完了した状態の一例を示している。

## [0159]

図 1 4 を参照して、スタンダードセルS C 1 0 ,S C 1 1 A ,S C 1 2 A ,S C 1 5 A ,S C 1 8 A の各金属層MT 2 (信号線)が、金属層MT 1 0 0 A によって電気的に接続されている。各金属層MT 2 と金属層MT 1 0 0 A とは直接連結されることによって電気的に接続され、各金属層MT 2 と各ゲート電極層 G W とは導電層 C L を通して電気的に接続されている。金属層MT 1 0 0 A は、上述の空き領域を活用して、 n <sup>+</sup> 型拡散領域 A n および p <sup>+</sup> 型拡散領域 A p を跨ぐように n <sup>+</sup> 型拡散領域 A p の各上方に配設されている。金属層MT 1 0 0 A は、金属層MT 1 ,MT 2 ,MT 1 0 A ~ MT 1 0 F と同一の工程において形成するとよい。

#### [0160]

同様に、スタンダードセルSC13,SC16の各金属層MT2(信号線)が、金属層MT101Aによって電気的に接続されている。各金属層MT2と金属層MT101Aとは直接連結されることによって電気的に接続され、各金属層MT2と各ゲート電極層GWとは導電層CLを通して電気的に接続されている。金属層MT101Aは、上述の空き領域を活用して、p<sup>+</sup>型拡散領域Apを跨ぐようにp<sup>+</sup>型拡散領域Apの上方に配設されている。

#### [0161]

ステップST5(図11参照)において、配置配線システムSYSは、複数のスタンダードセル間を結ぶ配線の密度を再び測定する。配置配線システムSYSは、すべての配線密度が所定値(許容範囲)以下となるように、再び上記のステップST6,ST7を繰り返すとよい。複数のスタンダードセル間の配線密度がすべて所定値以下となった場合、配置配線方法STは終了する(ステップST8)。

#### [0162]

### (効果)

本実施の形態における配置配線方法STによると、配線混雑領域付近におけるスタンダードセルが、上述のスタンダードセルSC2またはスタンダードセルSC2Aに置換される。他の複数のスタンダードセル間を接続する金属層が上記の空き領域を含むように配設されることによって、この金属層が迂回する距離(この金属層の全長)を短くすることができる。配置配線方法STを使用して得られた半導体装置においては、空き領域を活用することによってチップ面積の増大が抑制される。

# [0163]

金属層MT100Aと金属層MT1,MT2,MT10A~MT10Fとを同一の高さ(たとえば上述の絶縁層IL3が形成されている高さ)に配設することにより、金属層MT100Aを、金属層MT1,MT2,MT10A~MT10Fと同一の工程において形成することが可能となる。すなわち、金属層MT100Aおよび金属層MT1,MT2,MT10A~MT10Fを形成するためにたとえば絶縁層IL3に予めパターニングされた配線溝に対して、一回のまたは連続した処理により、金属層MT100Aおよび金属層MT1,MT2,MT10A~MT10Fを形成することが可能となる。その結果、金属層MT100Aと金属層MT1,MT2,MT10A~MT10Fとが同一の高さに配設される場合、一回のまたは連続した処理によってこれらを形成することによって、製造時間を短縮することが可能となる。

# [0164]

配置配線方法STを使用することにより、チップ面積がより小さい半導体装置を得ることが可能となる。配置配線方法STを使用することにより、スタンダードセルを配列するための設計上の自由度を高めることもできる。配置配線方法STを使用することにより、スタンダードセルの高集積化を図ることも可能となる。

# [0165]

### [実施の形態4の他の構成]

上述の実施の形態 4 のステップST3において、配置配線システムSYSが読み出すスタンダードセルのパターン情報には、上述の実施の形態 1 におけるスタンダードセルSC2 および上述の実施の形態 1 の他の構成におけるスタンダードセルSC2Aは含まれてい

10

20

30

40

20

30

40

50

ない。ステップST3において、配置配線システムSYSが読み出すスタンダードセルの パターン情報には、上記のスタンダードセルSC2,SC2Aが含まれていてもよい。

### [0166]

この場合、配置配線システムSYSは、ステップST3においてスタンダードセルSC2,SC2Aを選択肢に含んだ上で、読み出した複数のスタンダードセルのパターン情報を、上記の回路接続情報に対応するようにセル毎に配置する。スタンダードセルSC2,SC2Aは、たとえば入力が4以上となるセルに対して適用されるとよい。当該構成によれば、上記の配線混雑領域の発生が未然に抑制された状態で、半導体装置が設計される。【0167】

図11を参照して、上述の実施の形態4の配置配線方法STにおいては、ステップST4Aが完了した後、すべての配線密度が所定値(許容範囲)以下となるように再びステップST5~ST7を繰り返される態様を説明した。配置配線方法STにおいては、ステップST4Aが完了した時点で配置配線方法STが終了してもよい(ステップST8)。配線密度を再び測定するか否かは、たとえば表示装置IND(図10参照)を通して入力される所定のコマンドを待って決定されるとよい。

#### [0168]

以上、本発明に基づいた各実施の形態におけるスタンダードセル、スタンダードセルを備えた半導体装置、およびスタンダードセルの配置配線方法について説明したが、今回開示された各実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。

#### [0169]

たとえば、上記の各実施の形態においては、NOTゲート機能を有するCMOS構造を構成する半導体装置を基に説明したが、本発明における実施の形態はこれに限られない。本発明における実施の形態は、NORゲート機能を有する複数のトランジスタ素子、またはNANDゲート機能を有する複数のトランジスタ素子など、種々の論理回路を構成する半導体装置にも適用することができる。

#### [ 0 1 7 0 ]

したがって、本発明の範囲は特許請求の範囲によって示され、特許請求の範囲と均等の 意味および範囲内でのすべての変更が含まれることが意図される。

# 【産業上の利用可能性】

### [0171]

本発明は、複数のスタンダードセルを有する半導体装置、および複数のスタンダードセルを配置しこれらを配線するための方法に特に有利に適用され得る。

## 【符号の説明】

### [0172]

An, An 1 1 , An 2 1 , An 3 1 , Ap , Ap 1 2 , Ap 2 2 , Ap 3 2 , CR , CR 2 1 , CR 2 2 拡散領域、CCY 回路接続情報ファイル、CELR スタンダードセル領域、CL 導電層、CLY セルライブラリファイル、CR I 制約情報ファイル、EE 1 1 , EE 1 2 , EE 2 1 , EE 2 2 外縁、EP 1 1 , EP 1 2 , EP 2 1 , EP 3 1 A , EP 3 1 B 延在部、ET エクステンション領域、FE 機能素子領域、FE 1 ~ FE 3 機能素子領域、GW ゲート電極層、IL 1 ~ IL 3 絶縁層、IL 4 ゲート絶縁層、IND 表示装置、I/O 入出力領域、LCR 論理回路領域、MT 1 , MT 2 , MT 3 2 , MT 2 0 A , MT 1 , MT 1 2 , MT 3 2 , MT 2 0 A , MT 2 0 B , MT 1 0 0 , MT 1 0 E , MT 1 1 , MT 1 2 , MT 3 2 , MT 2 0 A , MT 2 0 B , MT 1 0 0 , MT 1 0 1 A 金属層、NT 1 , NT 2 , PT 1 , PT 2 トランジスタ、PF L パラメータファイル、SC , SC 1 , SC 2 , SC 2 A , SC 1 0 ~ SC 1 8 , SC 1 0 A ~ SC 1 2 A , SC 1 4 A , SC 1 5 A , SC 1 7 A , SC 1 8 A , SC 2 0 A , SC 2 0 B , SC 3 0 A , SC 3 0 B スタンダードセル、SD 1 , SD 1 A , SD 2 , SD 3 半導体装置、SD R , SD R 1 , SD 2 , SD 3 半導体装置、SD R , SD R 1 , SD 2 , SD 3 シリサイド層、SS 半導体基板、ST 配置配線方法、ST 1 ~ ST 8 , ST 4 A ステップ、SW サイドウォール、SY S

配置配線システム、TP11,TP12,TP21 幹線部、VI 矢印、Wn,Wpウェル領域。

# 【図1】

# 【図2】

# 【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

# 【図9】

【図10】

【図11】

【図12】

【図13】

# 【図14】

## フロントページの続き

(51) Int.CI. F I

**HO1L 27/088 (2006.01)** H01L 27/08 102D

H 0 1 L 21/8234 (2006.01)

(74)代理人 100124523

弁理士 佐々木 眞人

(72)発明者 大村 浩史

神奈川県川崎市中原区下沼部1753番地 ルネサスエレクトロニクス株式会社内

## 審査官 宇多川 勉

(56)参考文献 特開2009-032788(JP,A)

特開2007-043004(JP,A)

特開2010-074125(JP,A)

特開2010-087336(JP,A)

特開2008-193070(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/82

H01L 21/822

H01L 21/8234

H01L 21/8238

H01L 27/04

H01L 27/088

H01L 27/092