(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5055721号 (P5055721)

(45) 発行日 平成24年10月24日(2012.10.24)

(24) 登録日 平成24年8月10日(2012.8.10)

(51) Int.Cl. F.1

**GO 1 R 23/14 (2006.01)** GO 1 R 23/14 A GO 1 L 9/00 (2006.01) GO 1 L 9/00 C

請求項の数 2 (全 8 頁)

(21) 出願番号 特願2005-194511 (P2005-194511)

(22) 出願日 平成17年7月4日 (2005.7.4)

(65) 公開番号 特開2007-10593 (P2007-10593A)

(43) 公開日 平成19年1月18日 (2007.1.18) 審査請求日 平成20年3月26日 (2008.3.26)

||(73)特許権者 000006507

横河電機株式会社

東京都武蔵野市中町2丁目9番32号

||(72)発明者 前田 直樹

東京都武蔵野市中町2丁目9番32号 横

河電機株式会社内

審査官 吉田 久

最終頁に続く

### (54) 【発明の名称】振動センサ式差圧・圧力伝送器

### (57)【特許請求の範囲】

#### 【請求項1】

振動式差圧・圧力センサからの被測定信号の周波数に対して近接した周波数の比較信号を発生する比較信号発生回路と、

前記被測定信号と前記比較信号を入力し、両者の差分周波数信号を生成するヘテロダイン回路と、

前記差分周波数信号でゲートされる基準クロックをカウントする周波数カウンタと、

この周波数カウンタのカウント値と前記比較信号の周波数に基づいて前記被測定信号の周波数を演算する演算回路とを備え、

この演算回路は、個々の前記振動式差圧・圧力センサからの被測定信号の周波数スパン に基づいて、前記周波数スパンの下限周波数より低く、かつ前記下限周波数に近接した周 波数の前記比較信号を発生させるための予め設定された分周比の指令を前記比較信号発生 回路に与え、

前記比較信号発生回路は、前記基準クロックを前記指令された分周比で分周した前記比較信号を発生する、

ことを特徴とする振動センサ式差圧・圧力伝送器。

#### 【請求項2】

前記へテロダイン回路は、ローパスフィルタを備えることを特徴とする請求項<u>1</u>に記載の振動センサ式差圧・圧力伝送器。

### 【発明の詳細な説明】

#### 【技術分野】

### [0001]

本発明は、基準クロックを高速化することなく、被測定信号の周波数を高速・高分解能で測定することができる周波数測定回路<u>を</u>利用した振動センサ式差圧・圧力伝送器に関するものである。

#### 【背景技術】

#### [00002]

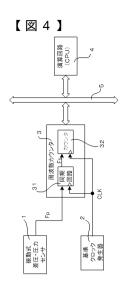

図4は、従来の振動センサ式差圧・圧力伝送器で用いられている周波数測定回路の基本構成を示す機能ブロック図である。振動式圧力・差圧センサ1は、測定圧力または差圧に対応した周波数を有する被測定信号 Fpを出力する。2は基準クロック発生器であり、被測定信号 Fpの周波数よりも高い周波数の基準クロック CL Kを発生する。

#### [0003]

被測定信号 F p は、周波数カウンタ3の同期回路31に入力され、基準クロックCLKの立ち上がりに同期した信号 F s に変換される。この信号 F s および基準クロックCLKは、カウンタ32に入力される。カウンタ32は、基準クロックCLKを信号 F s の1周期またはその整数倍の期間カウントして、被測定信号 F p の周波数を測定する。この周波数データは、CPUの機能で実現される演算回路4に入力され、差圧あるいは圧力が演算される。5は、CPUの内部バスである。

#### [0004]

図5は、同期回路31のタイムチャートである。(A)に示す基準クロックCLKは、一定の周波数を有するパルス信号である。(B)に示す被測定信号Fpは、この基準クロックCLKよりかなり低い周波数の信号であり、かつ基準クロックに同期していない。同期回路31は、基準クロックCLKの立ち上がりで被測定信号Fpをサンプリングする。そのため、同期回路31の出力Fsは、(C)に示すように基準クロックCLKの立ち上がりに同期して変化する。ゲート時間はカウンタ32が信号Fs及び基準クロックCLKをカウントする単位期間を表している。

#### [0005]

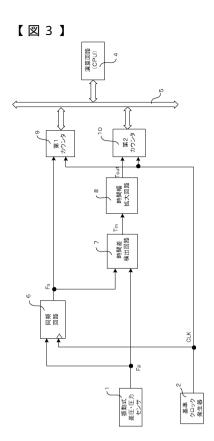

このような基本構成において、伝送器の高速化を図る目的でゲート時間を短くした場合には、同一の分解能を確保するためには基準クロックCLKの周波数を高くしなければならない。周波数を高くすると消費電力が増加するので、2線式の差圧・圧力伝送器に適用することは困難である。図3は、特許文献1に開示されている周波数測定回路の機能ブロック図である。この回路の特徴は、基準クロックCLKの周波数を高くすることなく、高速化を実現したものである。

### [0006]

同期回路6は、図4における同期回路31と同一機能を有する。7は時間差検出回路であり、振動式圧力・差圧センサ1の被測定信号Fp及び同期回路6の出力Fsが入力され、被測定信号Fpの立ち上がりで低レベルになり、その次の出力Fsの立ち上がりで高レベルになる信号Tinを出力する。即ち、時間差検出回路7の出力Tinは、被測定信号FpとFsの時間差のパルス幅を有する信号である。

## [0007]

8 は時間幅拡大回路であり、時間差検出回路 7 の出力 T i n が入力され、この出力 T i n のパルス幅、すなわち低レベル期間を所定の倍率だけ拡大したパルス幅を有する信号 T o u t を出力する。

# [0008]

9 は第 1 カウンタであり、出力 F s の 1 周期またはその整数倍の間基準クロック C L K をカウントする。即ち、このカウンタ 9 は、図 4 で説明したカウンタ 3 2 と同じ動作をする。

### [0009]

10は第2カウンタであり、時間幅拡大回路8の出力Toutおよび基準クロックCLKが入力され、出力Toutのパルス幅、即ち、Toutが低レベルの期間に基準クロッ

10

20

30

40

ク C L K をカウントする。 C P U 機能で実現される演算回路 4 は、バス 5 を介して第 1 カウンタ 9 及び第 2 カウンタ 1 0 のカウント値を取得する。

#### [0010]

演算回路4は、第2カウンタ10のカウント値を時間幅拡大回路8が入力信号のパルス幅を拡大する倍率により除算し、この除算結果を第1カウンタ9のカウント値に加算することによって、振動式圧力・差圧センサ1の被測定信号Fpの周波数を演算する。また、この周波数から圧力値を演算する。

#### [0011]

周波数測定回路及びそれを用いた振動センサ式差圧・圧力伝送器に関連する先行技術文献としては、次のようなものがある。

10

20

### [0012]

【特許文献 1 】特開 2 0 0 4 - 1 9 8 3 9 3 号公報

#### 【発明の開示】

【発明が解決しようとする課題】

### [0013]

従来技術による構成では、次のような問題点がある。

(1)図4に示す基本構成では、高速化するために基準クロックの周波数を高くした場合には、消費電力が増加し2線式の差圧・圧力伝送器に適用することは困難である。

#### [0014]

(2)図3に示す構成では、基準クロックの周波数を高くすることなく測定を高速化することが可能である。しかしながら、高速化に伴ないゲート時間が短くなることで、被測定信号に重畳するノイズ及びジッタが測定精度を悪化させる影響が大きくなるが、この影響を抑制することができない。

[ 0 0 1 5 ]

従って本発明が解決しようとする課題は、基準クロックの周波数を高くすることなく、被測定信号の周波数測定分解能を向上させると共に、高速化に伴ない発生するノイズやジッタの影響を抑制することが可能な周波数測定回路<u>を</u>用いた振動センサ式差圧・圧力伝送器を実現することにある。

【課題を解決するための手段】

### [0019]

30

(<u>1</u>)振動式差圧・圧力センサからの被測定信号の周波数に対して近接した周波数の比較信号を発生する比較信号発生回路と、

前記被測定信号と前記比較信号を入力し、両者の差分周波数信号を生成するヘテロダイン回路と、

前記差分周波数信号でゲートされる基準クロックをカウントする周波数カウンタと、

この周波数カウンタのカウント値と前記比較信号の周波数に基づいて前記被測定信号の周波数を演算する演算回路とを備え、

この演算回路は、個々の前記振動式差圧・圧力センサからの被測定信号の周波数スパン に基づいて、前記周波数スパンの下限周波数より低く、かつ前記下限周波数に近接した周 波数の前記比較信号を発生させるための<u>予め設定された</u>分周比の指令を前記比較信号発生 回路に与え、

40

前記比較信号発生回路は、前記基準クロックを前記指令された分周比で分周した前記比較信号を発生する、

ことを特徴とする振動センサ式差圧・圧力伝送器。

### [0021]

(<u>2</u>)前記へテロダイン回路は、ローパスフィルタを備えることを特徴とする<u>(1)</u>に記載の振動センサ式差圧・圧力伝送器。

### 【発明の効果】

#### [0022]

以上説明したことから明らかなように、本発明によれば次のような効果がある。

(1) ヘテロダイン回路を用いて、被測定信号の周波数と、個々の前記振動式差圧・圧力 センサからの被測定信号の周波数スパンに基づいて、前記周波数スパンの下限周波数より 低くかつ前記下限周波数に近接した周波数の前記比較信号の周波数との差分周波数信号を 生成し、この差分周波数信号でゲートされる基準クロックをカウントした値と比較信号の 周波数に基づいて被測定信号の周波数を演算することで、基準クロックの周波数を高くす ることなく、高速・高分解能を実現できる。

#### [0023]

(2) ノイズやジッタに関しては、ヘテロダイン回路内にあるローパスフィルタによって ジッタの高周波成分を除くことができるため、被測定信号に重畳するノイズ及びジッタが 測定精度を悪化させる影響を抑制することができる。

[0024]

(3)比較信号の周波数は、基準クロックを所定比率で分周することにより正確な周波数 信号を生成することが可能であり、演算精度を確保することができる。

【発明を実施するための最良の形態】

#### [0025]

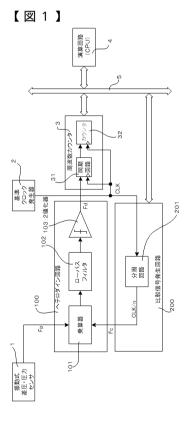

以下、本発明を図面により詳細に説明する。図1は本発明を適用した周波数測定回路及びそれを用いた振動センサ式差圧・圧力伝送器の一実施形態を示す機能ブロック図である。図4で説明した従来回路と同一要素には同一符号を付して説明を省略する。以下、本発明の特徴部につき説明する。

[0026]

図1において、100は、本発明の特徴部を形成するヘテロダイン回路である。このヘテロダイン回路は、乗算器101と、ローパスフィルタ102と、2値化器103を備えている。

[0027]

200は比較信号発生回路であり、この実施形態では分周回路201を備え、基準クロックCLKを所定の分周比nで分周した周波数CLK/nの比較信号Fcを生成してヘテロダイン回路100に出力している。

[0028]

ヘテロダイン回路100の乗算器101は、被測定信号Fpと比較信号Fcを入力し、両者の周波数の和成分(Fp+Fc)及び差成分(Fp-Fc)を生成する。この乗算器101への入力はディジタル信号であるので、乗算器101は排他的論理和演算の素子からなる。

[0029]

乗算器 1 0 1 の出力は、ローパスフィルタ 1 0 2 に入力される。ローパスフィルタ 1 0 2 は、乗算器 1 0 1 によって生成される周波数の和成分と差成分のうち、差成分のみを抽出するためのアナログフィルタである。

[0030]

このローパスフィルタ102で抽出されアナログ信号の差成分は、2値化器103で再びディジタル信号へ戻される。2値化器103は、コンパレータであり、その出力信号の周波数を差分周波数Fd、信号Fs及びFcの周波数をFs及びFcとすれば、差分周波数Fdは、Fd=(Fp-Fc)である。この差分周波数Fdが、周波数カウンタ3に入力される。

[0031]

周波数カウンタ3は、図4で説明した従来回路と同じ機能であり、差分周波数Fdを同期回路31により基準クロックCLKで同期化し、その同期化信号で基準クロックCLKの通過を規制してカウンタ32で基準クロックCLKをカウントする。そのカウント結果は、バス5を通じて演算回路(CPU)4に取り込まれる。

[0032]

比較信号発生回路 2 0 0 の分周回路 2 0 1 は、実施形態のように、基準クロック C L K を分周してヘテロダイン回路 1 0 0 に入力される比較信号 F c を生成する構成を採用する

10

20

40

30

場合には、分周比nはCPU4からバス5を通じて指令される。分周比nは、個々のセンサからの被測定信号Fpの周波数スパンに基づいて所定の差分周波数Fdとなるように予め設定される。

#### [0033]

演算回路(CPU)4は、分周回路201に分周比nの指令を与えると共に、周波数カウンタ3からのデータを取り込んで計算されるヘテロダイン回路100差分周波数Fdと、比較信号発生回路200の比較信号の周波数Fcとから、被測定信号の周波数Fpを、Fp=(Fd+Fc)で計算する。

### [0034]

一般に、周波数カウンタ3によって測定できる周波数は、周波数カウンタ3の時間分解能と測定時間で決まる。基準クロックCLKの周波数が周波数カウンタ3の入力周波数よりも充分高ければ、入力周波数によらず測定結果の有効桁数は一定とみなすことができる

### [0035]

このことは、周波数が低い信号ほどより小さい桁まで測定可能であることを意味する。 従って、ヘテロダイン回路100を通って元の信号周波数Fpよりも周波数が低い差分周 波数Fdを測定した周波数カウンタの測定結果と、既知の周波数Fcとを足し合わせて求 められる元の被測定信号の周波数Fpは、ヘテロダイン回路を用いない時よりも測定結果 の有効桁数が増え、結果として周波数分解能が向上することになる。

#### [0036]

被測定信号 F p の周波数スパンが 1 2 0 ~ 1 3 0 k H z のとき、比較信号 F c の周波数を 1 1 0 k H z に選定した場合には、差分周波数 F d は、 1 0 ~ 2 0 k H z となる。このときに期待される分解能の向上効果は、略 1 0 倍乃至 5 倍となる。

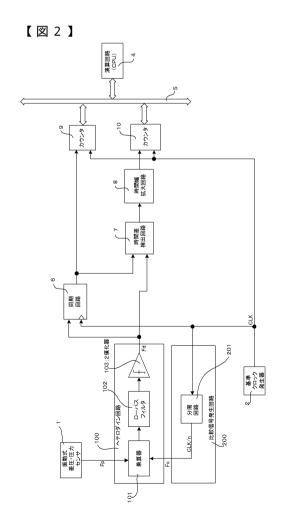

### [ 0 0 3 7 ]

図 2 は、本発明の他の実施形態の構成を示す機能ブロック図である。この構成の特徴は、図 1 で説明した本発明のヘテロダイン回路 1 0 0 の差分周波数 F d を、図 3 で説明した特許文献 1 に開示された周波数測定回路の入力とした、組み合わせ構成にある。このような組み合わせ構成により、分解能を更に向上させることが可能である。

#### [0038]

本発明で導入される、ヘテロダイン回路100におけるローパスフィルタ102の機能は、乗算器101によって生成される周波数の和成分と差成分のうち、差成分のみを抽出するためのアナログフィルタとしての機能に加えて、高速化に伴ない発生するノイズ及びジッタの影響を抑制する機能を有し、図3で説明した特許文献1に開示された従来技術の問題点を解消することができる。

# [0039]

図1の実施形態では、比較信号Fcを生成する手段として基準クロックCLKを分周する分周回路201を例示したが、この構成に限定されるものではなく既知の周波数信号を出力する安定した発振回路を採用することも可能である。

### 【図面の簡単な説明】

#### [0040]

【図1】本発明を適用した周波数測定回路及びそれを用いた振動センサ式差圧・圧力伝送器の一実施形態を示す機能ブロック図である。

【図2】本発明の他の実施形態の構成を示す機能ブロック図である。

【図3】特許文献1に開示されている周波数測定回路の機能ブロック図である。

【図4】従来の振動センサ式差圧・圧力伝送器で用いられている周波数測定回路の基本構成を示す機能プロック図である。

【図5】同期回路のタイムチャートである。

### 【符号の説明】

#### [0041]

1 振動式圧力・差圧センサ

20

10

30

40

- 2 基準クロック発生器

- 3 周波数カウンタ

- 3 1 同期回路

- 32 カウンタ

- 4 演算回路(CPU)

- 5 内部バス

- 100 ヘテロダイン回路

- 101 乗算器

- 102 ローパスフィルタ

- 103 2 値化器

- 200 比較信号発生回路

- 2 0 1 分周回路

### フロントページの続き

# (56)参考文献 特開2004-198393(JP,A)

特開昭62-179227(JP,A)

特開平4-285864(JP,A)

特開平8-15350(JP,A)

特開昭62-82880(JP,A)

特開昭63-135870(JP,A)

特開平7-72188 (JP,A)

特開平6-3385(JP,A)

特開2005-106772(JP,A)

# (58)調査した分野(Int.CI., DB名)

G 0 1 R 2 3 / 0 0 ~ 2 3 / 2 0

G01F 1/00~1/90

G01L 9/00~9/18