# (19) 国家知识产权局

# (12) 实用新型专利

(10) 授权公告号 CN 218918835 U (45) 授权公告日 2023. 04. 25

- (21)申请号 202222380872.8

- (22)申请日 2022.09.07

- (73) 专利权人 日月光半导体制造股份有限公司 地址 中国台湾高雄市楠梓加工区经三路26 号

- (72)发明人 吕文隆

- (74) 专利代理机构 北京植众德本知识产权代理 有限公司 16083

专利代理师 高秀娟

(51) Int.CI.

**H01L 21/768** (2006.01)

权利要求书1页 说明书5页 附图6页

#### (54) 实用新型名称

半导体封装装置

#### (57) 摘要

本申请涉及半导体封装装置。该半导体封装装置包括:硅中介层,包括厚区与薄区,厚区的厚度大于薄区的厚度,硅中介层包括朝向相反的第一表面和第二表面,薄区自第一表面向第二表面方向减薄;导电孔,贯穿薄区并电连接硅中介层的第一表面和第二表面。该半导体封装装置有利于降低硅通孔的制作成本,同时提高半导体封装装置的结构强度和使用寿命。

1.一种半导体封装装置,其特征在于,包括:

硅中介层,包括厚区与薄区,所述厚区的厚度大于所述薄区的厚度,所述硅中介层包括朝向相反的第一表面和第二表面,所述薄区自所述第一表面向所述第二表面方向减薄;

导电孔,贯穿所述薄区并电连接所述硅中介层的第一表面和第二表面。

- 2.根据权利要求1所述的半导体封装装置,其特征在于,所述导电孔的上表面低于所述厚区的上表面。

- 3.根据权利要求2所述的半导体封装装置,其特征在于,所述导电孔和所述薄区侧壁之间设置有隔离层。

- 4.根据权利要求3所述的半导体封装装置,其特征在于,所述隔离层的上表面高于所述 薄区的上表面。

- 5.根据权利要求4所述的半导体封装装置,其特征在于,所述导电孔的上表面高于所述 隔离层的上表面。

- 6.根据权利要求1所述的半导体封装装置,其特征在于,所述薄区的厚度大于零。

- 7.根据权利要求6所述的半导体封装装置,其特征在于,所述导电孔的上表面高于所述 薄区的上表面。

- 8.根据权利要求1所述的半导体封装装置,其特征在于,所述硅中介层的第二表面设置有线路层。

- 9.根据权利要求8所述的半导体封装装置,其特征在于,所述线路层的第一表面与所述 硅中介层的第二表面电连接,所述线路层的第二表面与外部元件电连接。

- 10.根据权利要求9所述的半导体封装装置,其特征在于,所述薄区的厚度为零。

# 半导体封装装置

#### 技术领域

[0001] 本申请涉及半导体封装技术领域,具体涉及半导体封装装置。

#### 背景技术

[0002] 在2.5D/3D封装的硅通孔(through silicon via,TSV)制作过程中,受限于纵横比 (aspect ratio)制程能力以及硅通孔开口直径的规格,会先进行晶圆减薄作业,但是经过减薄的晶圆强度减弱,容易因受到外力而破裂。另外,有不减薄的方法是自晶圆的两端分别制作硅通孔并相互连通,但是在硅通孔的接合处强度较低,容易因外力破裂,并且制作两个硅通孔的成本也会翻倍。

[0003] 因此,有必要提出一种新的技术方案以解决上述至少一个技术问题。

## 实用新型内容

[0004] 本申请提供了一种半导体封装装置。

[0005] 本申请提供的半导体封装装置,其特征在于,包括:

[0006] 硅中介层,包括厚区与薄区,所述厚区的厚度大于所述薄区的厚度,所述硅中介层包括朝向相反的第一表面和第二表面,所述薄区自所述第一表面向所述第二表面方向减薄;

[0007] 导电孔,贯穿所述薄区并电连接所述硅中介层的第一表面和第二表面。

[0008] 在一些可选的实施方式中,所述导电孔的上表面低于所述厚区的上表面。

[0009] 在一些可选的实施方式中,所述导电孔和所述薄区侧壁之间设置有隔离层。

[0010] 在一些可选的实施方式中,所述隔离层的上表面高于所述薄区的上表面。

[0011] 在一些可选的实施方式中,所述导电孔的上表面高于所述隔离层的上表面。

[0012] 在一些可选的实施方式中,所述薄区的厚度大于零。

[0013] 在一些可选的实施方式中,所述导电孔的上表面高于所述薄区的上表面。

[0014] 在一些可选的实施方式中,所述硅中介层的第二表面设置有线路层。

[0015] 在一些可选的实施方式中,所述线路层的第一表面与所述硅中介层的第二表面电连接,所述线路层的第二表面与外部元件电连接。

[0016] 在一些可选的实施方式中,所述线路层为重布线层。

[0017] 在一些可选的实施方式中,所述薄区的厚度为零。

[0018] 在一些可选的实施方式中,所述薄区的第一表面设置有电子元件。

[0019] 本申请提供的半导体封装装置,利用薄区制作硅通孔,降低了硅通孔的深度,同时利用厚区为整体结构提供足够的支撑强度,避免晶圆破裂,有利于降低硅通孔的制作成本,同时提高半导体封装装置的结构强度和使用寿命。

#### 附图说明

[0020] 通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本申请的其它

特征、目的和优点将会变得更明显:

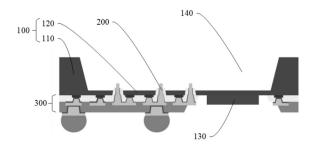

[0021] 图1是现有技术中半导体封装装置的示意图:

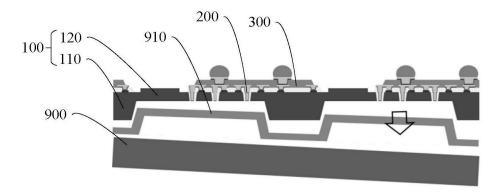

[0022] 图2-图9是根据本申请实施例的半导体封装装置的示意图;

[0023] 图10-图17是根据本申请实施例的半导体封装装置的制造过程的示意图。

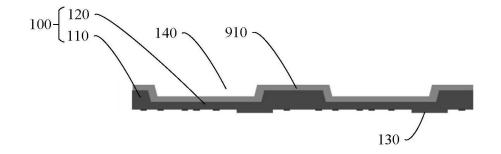

[0024] 符号说明:

[0025] 11、硅中介层;12、绝缘材;13、硅通孔;14、第一导电孔;15、第二导电孔;100、硅中介层;110、厚区;120、薄区;121、第一导电垫;130、第一电子元件;140、凹槽;200、导电孔;210、隔离层;220、种子层;230、焊料;300、线路层;302、第二导电垫;310、电连接孔;400、第二电子元件;500、模塑材;900、载体;910、阻挡层;920、开孔;930、保护层。

## 具体实施方式

[0026] 下面结合附图和实施例对说明本申请的具体实施方式,通过本说明书记载的内容本领域技术人员可以轻易了解本申请所解决的技术问题以及所产生的技术效果。可以理解的是,此处所描述的具体实施例仅仅用于解释相关实用新型,而非对该实用新型的限定。另外,为了便于描述,附图中仅示出了与有关实用新型相关的部分。

[0027] 需要说明的是,说明书附图中所绘示的结构、比例、大小等,仅用于配合说明书所记载的内容,以供本领域技术人员的了解与阅读,并非用以限定本申请可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本申请所能产生的功效及所能达成的目的下,均应仍落在本申请所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如"上"、"第一"、"第二"及"一"等用语,也仅为便于叙述的明了,而非用以限定本申请可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当也视为本申请可实施的范畴。

[0028] 还需要说明的是,本申请的实施例对应的纵向截面可以为对应前视图方向截面, 横向截面可以为对应右视图方向截面,而水平截面可以为对应上视图方向截面。

[0029] 应容易理解,本申请中的"在...上"、"在...之上"和"在...上面"的含义应该以最广义的方式解释,使得"在...上"不仅意味着"直接在某物上",而且还意味着包括存在两者之间的中间部件或层的"在某物上"。

[0030] 此外,为了便于描述,本申请中可能使用诸如"在...下面"、"在...之下"、"下部"、"在...之上"、"上部"等空间相对术语来描述一个元件或部件与附图中所示的另一元件或部件的关系。除了在图中描述的方位之外,空间相对术语还意图涵盖装置在使用或操作中的不同方位。设备可以以其他方式定向(旋转90°或以其他定向),并且在本申请中使用的空间相对描述语可以被同样地相应地解释。

[0031] 另外,在不冲突的情况下,本申请中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本申请。

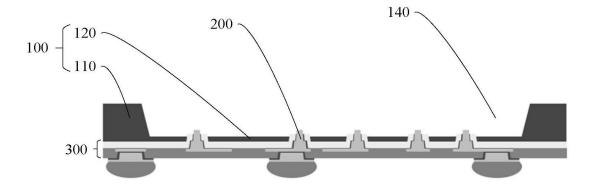

[0032] 图1是现有技术中半导体封装装置的示意图。

[0033] 图1上部示出了第一种制作硅通孔的方式。如图1上部所示,先将硅中介层11减薄(比较图1上部与下部,上部是减薄后的硅中介层11,下部是未减薄的硅中介层11),再在减薄后的硅中介层11上设置绝缘材12以及硅通孔13,实现硅中介层11两侧的电连接。

[0034] 在上述方式中,经过减薄的硅中介层11强度变弱,容易因受到外力而破裂。

[0035] 图1下部示出了第二种制作硅通孔的方式。如图1下部所示,保持硅中介层11的原有厚度,分别自硅中介层11的上表面设置第一导电孔14,自硅中介层11的下表面设置第二导电孔15。第一导电孔14和第二导电孔15在硅中介层11内部连通,共同实现硅中介层11两侧的电连接。

[0036] 在上述方式中,第一导电孔14和第二导电孔15的接合处强度较低,容易因外力破裂,并且制作两个导电孔的成本也会翻倍。

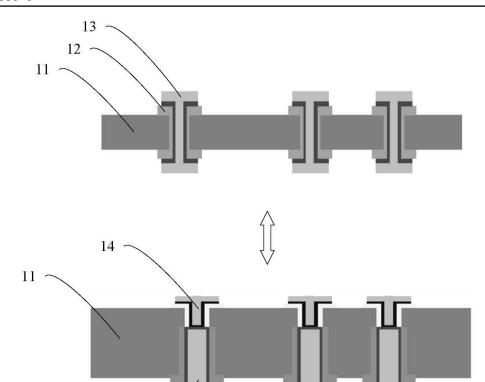

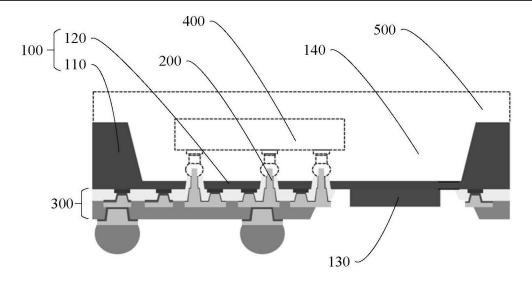

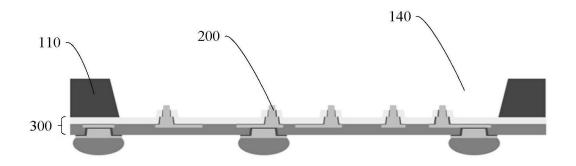

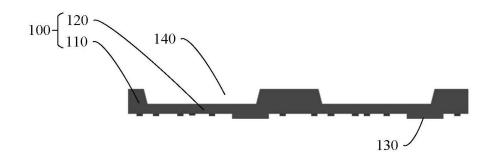

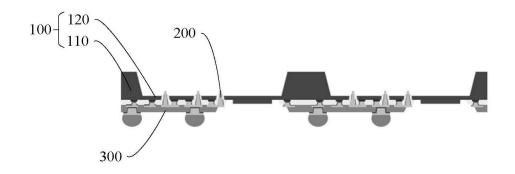

[0037] 图2是根据本申请实施例的半导体封装装置的示意图。如图2所示,该半导体封装装置包括硅中介层100和导电孔200。

[0038] 硅中介层100包括厚区110和薄区120。厚区110的硅材料厚度大于薄区120的硅材料厚度。薄区120自硅中介层100的上表面向硅中介层100的下表面减薄。薄区120的下表面与厚区110的下表面位于同一水平面。薄区120的上表面低于厚区110的上表面。薄区120的上表面和厚区110的内侧壁共同形成凹槽140。

[0039] 导电孔200贯穿薄区120,将硅中介层100的上表面和下表面电连接。

[0040] 在一些实施方式中,如图2所示,硅中介层100的下表面设置有线路层300。线路层300例如是重布线层(Re-distribution Layer,RDL)。线路层300的下表面可以设置外部元件(未示出)。线路层300能够将硅中介层100与外部元件(未示出)进行电连接。

[0041] 在一些实施方式中,如图2所示,硅中介层100的下表面设置有第一电子元件130。第一电子元件130例如是传感器(sensor)。

[0042] 在一些实施方式中,如图2所示,导电孔200的上表面高于薄区120的上表面,导电孔200高于薄区120上表面的部分可以用来连接其他电子元件,例如图5中的第二电子元件400。

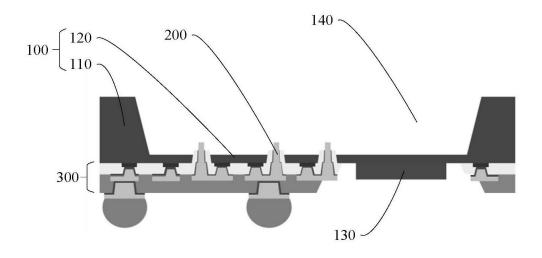

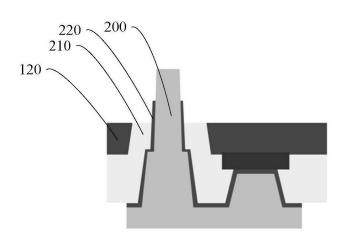

[0043] 图3是图2中半导体封装装置的局部放大图。如图3所示,薄区120的下表面设置有第一导电垫121。线路层300包括电连接孔310和第二导电垫302。电连接孔310将第一导电垫121和第二导电垫302电连接。导电孔200的下端与第二导电垫302电连接,导电孔200的上端设置有焊料230。薄区120的侧壁和导电孔200之间设置有种子层220和隔离层210。

[0044] 导电孔200可以通过电镀工艺制作,种子层220可以用作电镀工艺中金属生长的基层。

[0045] 隔离层210为绝缘材料,用于导电孔200和薄区120之间的电性隔绝。

[0046] 在一些实施方式中,如图3所示,隔离层210的上表面高于薄区120的上表面。如果隔离层210的上表面与薄区120的上表面平齐,由于焊料230在熔融状态下会四处溢流,因此有可能会经过隔离层210的上表面溢流至薄区120的上表面,破坏导电孔200与薄区120之间的电性隔绝。在隔离层210的上表面高于薄区120的上表面的情况下,熔融状态下焊料230的表面张力会将其限制在隔离层210的上表面内,避免焊料230溢流至薄区120的上表面,保证导电孔200与薄区120之间的电性隔绝。

[0047] 在一些实施方式中,如图3所示,导电孔200的上表面高于隔离层210的上表面。导电孔200高出隔离层210的部分可用作焊料230在熔融状态下凝聚的核心,减小焊料230溢流的风险。

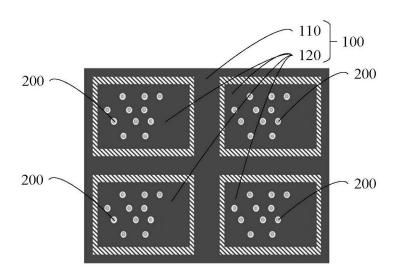

[0048] 图4示出了图2中半导体封装装置及其邻近区域的俯视图。如图4所示, 硅中介层 100包括厚区110和四个薄区120。每个薄区120的上表面与厚区110的侧壁形成一个凹槽

140。每个凹槽140内均设置有多个导电孔200。

[0049] 图5示出了图2中半导体封装装置的一种变形。如图5所示,薄区120的上表面设置有第二电子元件400。第二电子元件400位于薄区120上表面和厚区110内侧壁形成的凹槽140内。第二电子元件400例如是功能芯片。相对于将第二电子元件400设置在厚区110的表面,上述方式有利于减小半导体封装装置的纵向尺寸。

[0050] 如图5所示, 硅中介层100的上方设置有模塑材500。模塑材500用于保护硅中介层100和第二电子元件400。

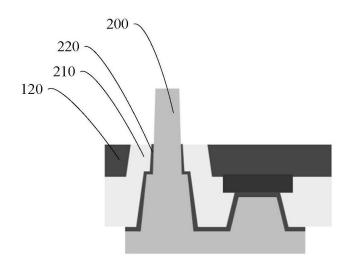

[0051] 图6和图7分别示出了图3中半导体封装装置的变形。在图3中,隔离层210的上表面高于薄区120的上表面,种子层220的上端与隔离层210的上表面平齐。在图6中,隔离层210的上表面与薄区120的上表面平齐,种子层220的上端高于隔离层210的上表面。在图7中,隔离层210的上表面与薄区120的上表面平齐,种子层220的上端与隔离层210的上表面平齐。

[0052] 图8示出了图2中半导体封装装置的一种变形。在图2中,线路层300的横向尺寸小于硅中介层100的横向尺寸。而在图8中,线路层300的横向尺寸等于硅中介层100的横向尺寸。

[0053] 图9示出了图8中半导体封装装置的一种变形。在图8中,薄区120的厚度大于零。而在图9中,薄区120(参见图8)的硅材料厚度为零,凹槽140由厚区110和线路层300共同形成,凹槽140的底面由线路层300的上表面形成。

[0054] 可以在图8所示半导体封装装置的基础上,进一步将薄区120的硅材料全部蚀刻掉,得到图9的半导体封装装置。图9中的导电孔200在薄区120(参见图8)的基础上形成,但是在最终结构中去除了薄区120的硅材料,属于"TSV-less"技术。

[0055] 本实施例中半导体封装装置,利用薄区120制作导电孔200(硅通孔),降低了硅通孔的深度,同时利用厚区110为整体结构提供足够的支撑强度,避免晶圆破裂,有利于降低硅通孔的制作成本,同时提高半导体封装装置的结构强度和使用寿命。

[0056] 在一个例子中,薄区120的厚度在几十微米至基板微米之间。厚区110的外侧壁与最近的内侧壁之间的距离(即"肩宽")大于或者等于10微米并且小于或者等于200微米。相邻导电孔200之间的距离大于或者等于5微米并且小于或者等于50微米。薄区120厚度大于或者等于零并且小于或者等于100微米。导电孔200上端的直径大于或者等于1微米并且小于或者等于20微米。薄区120开孔的直径大于或者等于2微米并且小于或者等于30微米。导电孔200上端的直径与薄区120开孔的直径的比值大于或者等于0.2并且小于或者等于1。薄区120厚度与薄区120开孔的直径的比值大于或者等于0.1并且小于或者等于20。隔离层210上表面与薄区120上表面的高度差大于或者等于1微米并且小于或者等于20微米。导电孔200的上表面与隔离层210的上表面的高度差大于或者等于1微米并且小于或者等于20微米。

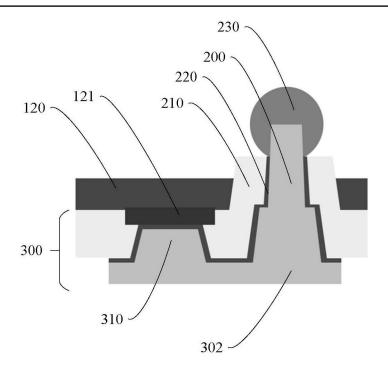

[0057] 图10-图17是根据本申请实施例的半导体封装装置的制造过程的示意图。该制造过程包括以下步骤:

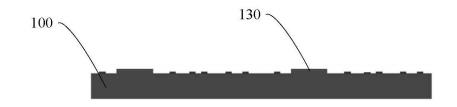

[0058] 第一步,如图10所示,提供一硅中介层100,其中,硅中介层100的上表面设置有第一电子元件130(由于后续步骤中将硅中介层100翻转,因此在最终的结构中,第一电子元件130位于硅中介层100的下表面)。

[0059] 第二步,如图11所示,将硅中介层100翻转,借助涂布光刻胶、曝光、显影和蚀刻等

制程,在硅中介层100的蚀刻出薄区120,未被蚀刻的部分形成厚区110,薄区120的上表面和厚区110的内侧壁共同形成凹槽140。

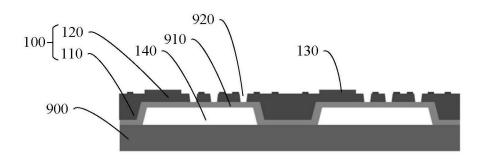

[0060] 第三步,如图12所示,在硅中介层100的上表面设置阻挡层910。阻挡层910的材料例如是聚酰亚胺(Polyimide,PI)。

[0061] 第四步,如图13所示,将硅中介层100再次翻转并放置在载体900上,利用涂布光刻胶、曝光、显影和蚀刻等制程,在硅中介层100的薄区120形成开孔920。其中,阻挡层910能够阻挡蚀刻向下进行,防止厚区110或者载体900被蚀刻。

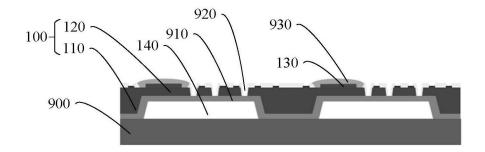

[0062] 第五步,如图14所示,在第一电子元件130的表面设置保护层930。保护层930的材料例如是聚酰亚胺(Polyimide,PI)。保护层930能够在后续制程(例如蚀刻)中保护第一电子元件130。

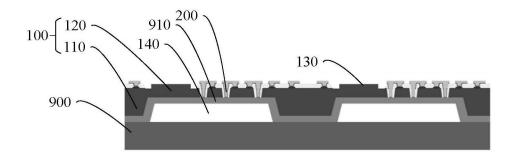

[0063] 第六步,如图15所示,借助物理气相沉积(PVD)、涂布光刻胶、曝光、显影和电镀等制程,在薄区120形成导电孔200。

[0064] 第七步,如图16所示,在硅中介层100的上表面形成线路层300,并去除载体900和保护层930。

[0065] 第八步,如图17所示,将硅中介层100再次翻转,并对薄区120做进一步的减薄(蚀刻),即可得到半导体封装装置,其中导电孔凸出于薄区120的上表面。更进一步的,将薄区120完全消除(完全蚀刻掉),即可得到如图9所示的"TSV-less"结构。

[0066] 尽管已参考本申请的特定实施例描述并说明本申请,但这些描述和说明并不限制本申请。所属领域的技术人员可清楚地理解,可进行各种改变,且可在实施例内替代等效元件而不脱离如由所附权利要求书限定的本申请的真实精神和范围。图示可能未必按比例绘制。归因于制造过程中的变量等等,本申请中的技术再现与实际设备之间可能存在区别。可存在未特定说明的本申请的其它实施例。应将说明书和图式视为说明性的,而非限制性的。可作出修改,以使特定情况、材料、物质组成、方法或过程适应于本申请的目标、精神以及范围。所有此些修改都落入在此所附权利要求书的范围内。虽然已参考按特定次序执行的特定操作描述本申请中所公开的方法,但应理解,可在不脱离本申请的教示的情况下组合、细分或重新排序这些操作以形成等效方法。因此,除非本申请中特别指示,否则操作的次序和分组并不限制本申请。

图1

15 -

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

图14

图15

图16

图17