## (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

HO1L 29/78 (2006.01) HO1L 21/8234 (2006.01) HO1L 29/417 (2006.01) HO1L 29/423 (2006.01)

(52) CPC특허분류

**H01L 29/7855** (2013.01) **H01L 21/823431** (2013.01)

(21) 출원번호 10-2017-0101087(분할)

(22) 출원일자<br/>심사청구일자2017년08월09일(65) 공개번호10-2017-0095174(43) 공개일자2017년08월22일

(62) 원출원 특허 10-2015-0166554

원출원일자 2015년11월26일 심사청구일자 2015년11월26일

(30) 우선권주장

14/714,231 2015년05월15일 미국(US)

(56) 선행기술조사문헌

US20030192012 A1\*

KR1020140006204 A\*

KR1020140111577 A\*

KR1020120012454 A\*

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2017년11월23일

(11) 등록번호 10-1801006

(24) 등록일자 2017년11월17일

(73) 특허권자

**타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드** 중화민국, 타이완, 신추, 신추 사이언스 파크, 리-신 로드 6, 넘버 8

(72) 발명자

### 린 치-한

중화민국, 타이완 300-77, 신츄, 사이언스-베이스 드 인더스트리얼 파크, 리신 로드. 6, 8호

(74) 대리인

김태홍, 김진회

전체 청구항 수 : 총 10 항

심사관 : 최정민

### (54) 발명의 명칭 반도체 디바이스 및 그 제조 방법

#### (57) 요 약

반도체 디바이스는 제1 및 제2 Fin FET 및 절연 재료로 형성되고 제1 및 제2 Fin FET 사이에 배치되는 분리 플러그를 포함한다. 제1 Fin FET은 제1 방향으로 연장되는 제1 핀 구조체, 제1 핀 구조체 위에 형성되는 제1 게이트 유전체 및 제1 게이트 유전체 위에 형성되고 제1 방향에 수직인 제2 방향으로 연장되는 제1 게이트 전극을 포함한다. 제2 Fin FET은 제2 핀 구조체, 제2 핀 구조체 위에 형성되는 제2 게이트 유전체 및 제1 게이트 유전체 위에 형성되고 제2 방향으로 연장되는 제2 게이트 유전체 위에 형성되고 제2 방향으로 연장되는 제2 게이트 전극을 포함한다. 상부에서 볼 때, 분리 플러그의 단부 형상은 오목한 만곡 형상을 갖되, 분리 플러그에 인접한 제1 게이트 전극의 단부는 볼록한 만곡 형상을 가진다.

### 대 표 도 - 도1a

## (52) CPC특허분류

**H01L 21/823481** (2013.01)

**H01L 29/41791** (2013.01)

**H01L 29/4236** (2013.01)

**H01L 29/7831** (2013.01)

**H01L 29/7846** (2013.01)

H01L 2924/13067 (2013.01)

### 명 세 서

### 청구범위

#### 청구항 1

반도체 디바이스에 있어서,

제1 방향으로 연장되는 제1 핀(fin) 구조체, 상기 제1 핀 구조체 위에 형성되는 제1 게이트 유전체 및 상기 제1 게이트 유전체 위에 형성되고 상기 제1 방향에 수직인 제2 방향으로 연장되는 제1 게이트 전극을 포함하는 제1 Fin FET;

제2 핀 구조체, 상기 제2 핀 구조체 위에 형성되는 제2 게이트 유전체 및 상기 제2 게이트 유전체 위에 형성되고 상기 제2 방향으로 연장되는 제2 게이트 전극을 포함하는 제2 Fin FET; 및

절연 재료로 형성되고 상기 제1 Fin FET과 상기 제2 Fin FET 사이에 배치되는 분리 플러그(separation plug)를 포함하고,

상부에서 볼 때, 상기 분리 플러그의 단부 형상은 오목한 만곡 형상(concave curved shape)을 갖되, 상기 분리 플러그에 인접하는 상기 제1 게이트 전극의 단부는 볼록한 만곡 형상(convex curved shape)을 가지는 것인,

#### 청구항 2

제1항에 있어서.

반도체 디바이스.

상기 제2 방향을 따른 그리고 상기 제1 게이트 전극을 가로지르는 단면에서, 상기 분리 플러그는 바닥부 폭보다 작은 최상부 폭을 가지는 테이퍼링 형상(tapered shape)을 가지는 것인,

반도체 디바이스.

#### 청구항 3

제2항에 있어서,

상기 분리 플러그의 바닥부에서 상기 분리 플러그의 테이퍼 각도(taper angle)는 90 도 이상인 것인,

반도체 디바이스.

### 청구항 4

제1항에 있어서,

상기 제1 게이트 전극은 제1 금속 게이트 재료를 포함하고,

상기 제2 게이트 전극은 제2 금속 게이트 재료를 포함하는 것인,

반도체 디바이스.

### 청구항 5

제4항에 있어서,

상기 제1 게이트 전극은 또한, 상기 제1 게이트 유전체 층과 상기 제1 금속 게이트 재료 사이에 배치되는 금속을 조정하는(adjusting) 하나 이상의 제1 일 함수(work function) 층을 포함하고,

상기 제2 게이트 전극은 또한, 상기 제2 게이트 유전체 층과 상기 제2 금속 게이트 재료 사이에 배치되는 금속을 조정하는 하나 이상의 제2 일 함수 층을 포함하는 것인,

반도체 디바이스.

### 청구항 6

반도체 디바이스를 제조하기 위한 방법에 있어서,

더미 게이트 전극 층 및 상기 더미 게이트 전극 층의 양쪽 주된 측면에 배치되는 측벽 절연 층과 상기 더미 게이트 전극 층의 양쪽 주된 측면에 배치되는 층간 유전체 층을 포함하는 더미 전극 구조체를 형성하는 단계;

상기 측벽 절연 층 사이에 제1 전극 공간 및 제2 전극 공간-상기 제1 전극 공간 및 상기 제2 전극 공간은 상기 더미 게이트 전극 층의 나머지 부분인 필라(pillar)에 의해 분리됨-이 형성되도록 상기 더미 게이트 전극 층의 일부분을 제거하는 단계;

상기 제1 전극 공간 및 상기 제2 전극 공간 각각에 제1 게이트 구조체 및 제2 게이트 구조체를 형성하는 단계;

상기 제1 게이트 구조체와 상기 제2 게이트 구조체 사이에 개구가 형성되도록 상기 필라를 제거하는 단계; 및

절연 재료로 상기 개구를 충전함으로써 분리 플러그를 형성하는 단계

를 포함하는,

반도체 디바이스를 제조하기 위한 방법.

#### 청구항 7

제6항에 있어서,

상기 더미 게이트 전극 층의 일부분을 제거하는 단계는,

상기 필라에 대응하는 구역 상에 마스크 패턴을 형성하는 단계; 및

상기 마스크 패턴을 사용함으로써 상기 더미 게이트 전극 층을 에칭하는 단계

를 포함하는 것인,

반도체 디바이스를 제조하기 위한 방법.

## 청구항 8

제7항에 있어서,

상기 마스크 패턴의 폭을 감소시키는 단계를 더 포함하고,

상기 더미 게이트 전극 층을 에칭하는 단계는 상기 감소된 폭을 가지는 상기 마스크 패턴을 사용함으로써 수행되는 것인,

반도체 디바이스를 제조하기 위한 방법.

### 청구항 9

제6항에 있어서,

상기 분리 플러그를 형성하는 단계는,

상기 제1 게이트 구조체 및 상기 제2 게이트 구조체 위에 그리고 상기 개구에 상기 절연 재료를 형성하는 단계; 및

상기 절연 재료의 일부분을 제거하고, 이에 따라 상기 개구에 충전되는 상기 절연 재료의 상기 분리 플러그를 형성하는 단계

를 포함하는 것인,

반도체 디바이스를 제조하기 위한 방법.

### 청구항 10

반도체 디바이스에 있어서,

제1 게이트 유전체 층 및 제1 금속 게이트 전극을 포함하는 제1 Fin FET;

제2 게이트 유전체 층 및 제2 금속 게이트 전극을 포함하는 제2 Fin FET; 및

절연 재료로 형성되고 상기 제1 Fin FET과 상기 제2 Fin FET 사이에 배치되는 분리 플러그

를 포함하고,

상기 제1 금속 게이트 전극의 일 단부와 상기 제2 금속 게이트 전극의 일 단부는 서로 마주보며,

상부에서 볼 때, 상기 분리 플러그의 단부 형상은 오목한 만곡 형상을 갖되, 상기 분리 플러그에 인접하는 상기 제1 금속 게이트 전극의 상기 단부는 볼록한 만곡 형상을 가지는 것인.

반도체 디바이스.

### 발명의 설명

## 기 술 분 야

[0001] 본 개시물은 반도체 집적 회로(semiconductor integrated circuit), 더 구체적으로 핀 구조체(fin structure) 를 가지는 반도체 디바이스 및 그 제조 프로세스에 관한 것이다.

#### 배경기술

[0002] 반도체 산업이 더 높은 디바이스 밀도, 더 높은 성능 및 더 낮은 비용을 추구하면서 나노미터 기술 프로세스 노드로 진보함에 따라, 제조 및 설계 문제양쪽으로부터의 도전과제로 말미암아 핀 전계 효과 트랜지스터(fin field effect transistor: Fin FET)가 개발되었다. Fin FET 디바이스는 전형적으로 고 애스펙트 비(high aspect ratios)를 가지는 반도체 핀을 포함하고, 이 반도체 핀에 반도체 트랜지스터 디바이스의 채널 및 소스/드레인 구역이 형성된다. 더 빠르고, 더 신뢰성있고 더 잘-제어된 반도체 트랜지스터 디바이스를 생산하기 위해 채널 및 소스/드레인 구역의 증가한 표면적의 장점을 활용하여 (예를 들어, 둘러싸서) 핀 구조체의 측면 위에 그리고 측면을 따라 게이트가 형성된다. 높은 전기 유전 상수를 가지는 하이-k(high-k) 게이트 유전체와 함께 금속 게이트 구조체는 종종 Fin FET 디바이스에 사용되고, 게이트-교체 기술에 의해 제조된다.

#### 도면의 간단한 설명

[0003] 본 개시물은 첨부 도면과 함께 숙독될 때 다음의 상세한 설명으로부터 더 잘 이해된다. 산업분야의 표준 실시에 따라, 다양한 피처는 실척으로 그려지지 않고 도시 목적만을 위해 사용됨이 강조된다. 실제로, 다양한 피처의 치수는 논의의 명확성을 위해 임의선택적으로 증가하거나 감소할 수 있다.

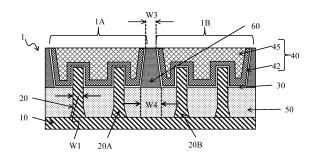

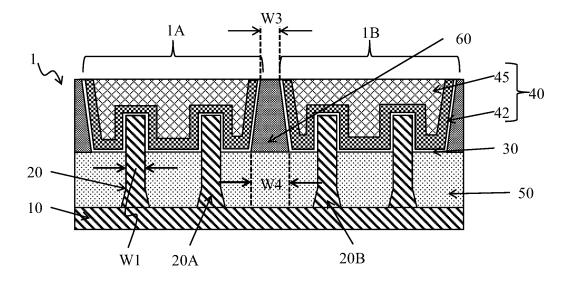

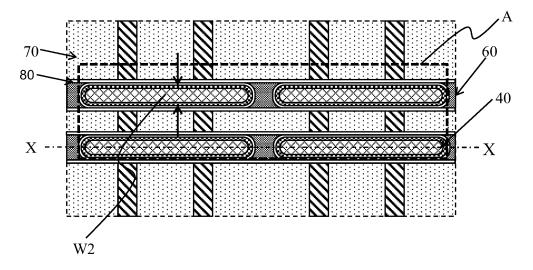

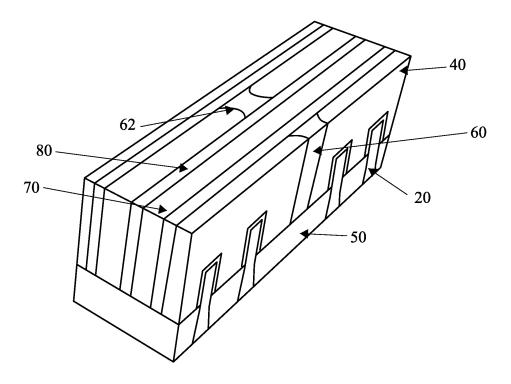

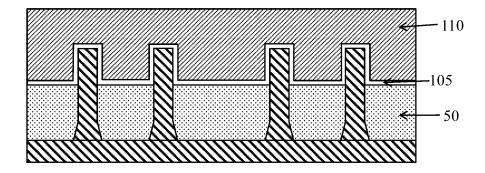

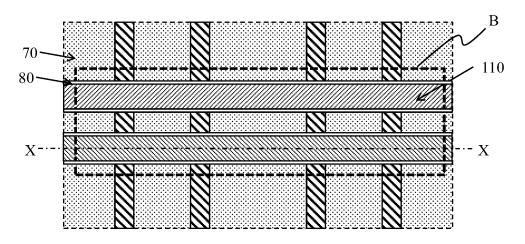

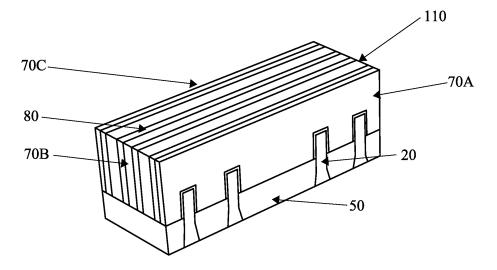

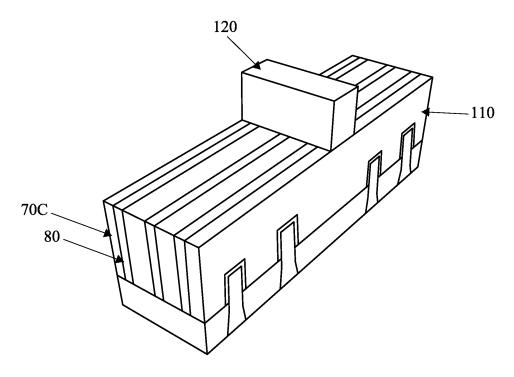

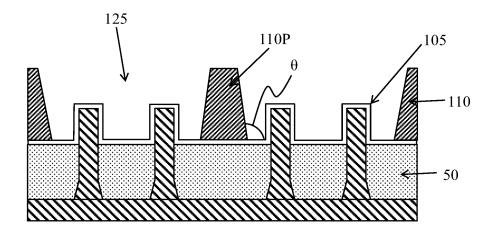

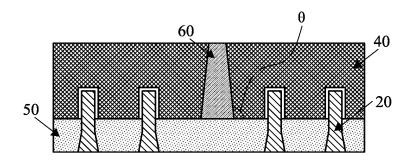

도 1a는 핀 구조체를 가지는 반도체 FET 디바이스(Fin FET)의 예시적인 단면도이고, 도 1b는 핀 구조체를 가지는 반도체 FET 디바이스의 예시적인 최상면도이고, 도 1c는 본 개시물의 일 실시예에 따라, 도 1b의 밀봉 부분에 대응하는 핀 구조체를 가지는 반도체 FET 디바이스의 예시적인 투시도이다.

도 2-12c는 본 개시물의 일 실시예에 따라 Fin FET 디바이스를 제조하기 위한 예시적인 프로세스를 도시한다.

도 13a 및 13b는 Fin FET 디바이스의 비교 예를 도시한다.

## 발명을 실시하기 위한 구체적인 내용

[0004] 다음의 개시물은 본 발명의 다른 피처를 구현하기 위한 많은 서로 다른 실시예 또는 예를 제공함이 이해된다. 본 개시물을 간략화하기 위해 컴포넌트(components) 및 배치의 특정 실시예 또는 예가 이하에 설명된다. 이들은 물론, 단지 예이고 제한하려는 것이 아니다. 예를 들어, 엘리먼트의 치수가 개시된 범위 또는 값에 제한되는 것이 아니라, 프로세스 조건 및/또는 디바이스의 원하는 특성(properties)에 따를 수 있다. 더욱이, 후속하는 설명에서 제2 피처 위의 또는 제2 피처 상의 제1 피처의 형성은 제1 및 제2 피처가 직접 접촉하여 형성되는 실시예를 포함할 수 있으며, 또한 제1 및 제2 피처가 직접 접촉하지 않을 수 있도록, 제1 및 제2 피처 사이에 추가적인 피처가 형성될 수 있는 실시예를 포함할 수 있다. 다양한 피처가 간략성 및 명확성을 위해 서로 다른 스케일로 임의선택적으로 그려질 수 있다.

[0005] 추가로, "밑에(beneath)", "아래(below)", "하부(lower)", "위에(above)", "상부(upper)" 등과 같은 공간적으로 관련한 용어는 도면에 도시된 바와 같이 다른 엘리먼트 또는 피처에 대한 일 엘리먼트 또는 피처의 관계를

설명하기 위해 설명의 편의상 본원에서 사용될 수 있다. 공간적으로 관련된 용어는 도면에 도시되는 배향 (orientation)에 더하여 사용 또는 동작시에 디바이스의 서로 다른 배향을 망라하도록 의도된다. 장치는 달리 (90도로 회전되거나 다른 배향으로) 배향될 수 있고 본원에서 사용되는 공간적으로 관련된 기술어(descriptor s)는 유사하게 그에 따라 해석될 수 있다. 추가로, 용어 "~로 이루어지는(made of)"은 "포함하는(comprising)" 또는 "~로 이루어지는(consisting of)"를 의미할 수 있다.

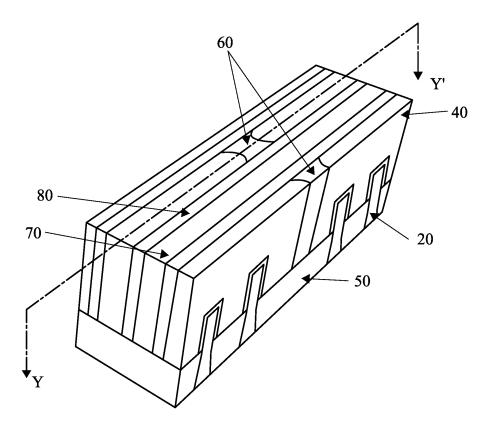

- [0006] 도 1a는 핀 구조체를 가지는 반도체 FET 디바이스(Fin FET)의 예시적인 단면도이고, 도 1b는 핀 구조체를 가지는 반도체 FET 디바이스의 예시적인 최상면도이고, 도 1c는 본 개시물의 일 실시예에 따른 핀 구조체를 가지는 반도체 FET 디바이스의 예시적인 투시도이다. 도 1a는 도 1b에서의 라인 X-X를 따른 단면도이고, 도 1c는 도 1b에서의 밀봉 부분 A에 대응한다. 이 도면에서, 일부 층/피처는 간략화를 위해 생략된다. 도 1a-1c는 금속 게이트 구조체가 형성된 후의 디바이스 구조체를 도시한다.

- [0007] Fin FET 디바이스(1)는 제1 디바이스 구역(1A) 및 제2 디바이스 구역(1B)을 포함한다. 제1 디바이스 구역(1A)은 하나 이상의 제1 Fin FET 디바이스를 포함하고, 제2 디바이스 구역은 하나 이상의 제2 Fin FET 디바이스를 포함한다. 제1 Fin FET의 채널 타입은 제2 Fin FET의 채널 타입과 동일하거나 서로 다르다.

- [0008] 일 실시예에서, 제1 디바이스 구역(1A)은 p-타입 MOS FET를 포함하고 제2 디바이스 구역(1B)은 n-타입 MOS FET을 포함한다. 다른 실시예에서, 제1 및 제2 디바이스 구역은 p-타입 MOS FET을 포함하고, 제1 및 제2 디바이스 구역은 n-타입 MOS FET을 포함하거나 제1 및 제2 디바이스 구역은 p-타입 및 n-타입 MOS FET 둘 다를 포함한다.

- [0009] Fin FET 디바이스(1)는 다른 피처 중에서도, 기판(10), 핀 구조체(20), 게이트 유전체(30) 및 게이트 전극(40)을 포함한다. 본 실시예에서, 기판(10)은 실리콘 기판이다. 대안적으로, 기판(10)은 게르마늄; SiC 및 SiGe와 같은 IV-IV 화합물 반도체, GaAs, GaP, GaN, InP, InAs, InSb, GaAsP, AlGaN, AlInAs, AlGaAs, GaInAs, GaInP 및/또는 GaInAsP와 같은 III-V 화합물 반도체; 또는 그 조합과 같은 다른 원소 반도체를 포함할 수 있다. 일 실시예에서, 기판(10)은 SOI(silicon-on insulator) 기판의 실리콘 층이다. SOI 기판이 사용될 때, 핀 구조체는 SOI 기판의 실리콘 층으로부터 돌출할 수 있거나 SOI 기판의 절연체 층으로부터 돌출할 수 있다. 후자의 경우에, SOI 기판의 실리콘 층은 핀 구조체를 형성하기 위해 사용된다. 아모르퍼스(amorphous) Si 또는 아모르퍼스 SiC와 같은 아모르퍼스 기판, 또는 실리콘 산화물과 같은 절연 재료는 또한 기판(10)으로서 사용될 수 있다. 기판(10)은 불순물(예를 들어, p-타입 또는 n-타입 전도성)로 적합하게 도핑된 다양한 구역을 포함할 수 있다.

- [0010] 핀 구조체(20)는 기판(10) 위에 배치된다. 핀 구조체(20)는 기판(10)에서와 동일한 재료로 이루어질 수 있고 기판(10)으로부터 계속적으로 연장할 수 있다. 본 실시예에서, 핀 구조체는 Si로 이루어진다. 핀 구조체(20)의 실리콘 층은 진성(intrinsic)일 수 있거나, n-타입 불순물 또는 p-타입 불순물로 적합하게 도핑될 수 있다.

- [0011] 도 1a에서, 2개의 핀 구조체(20)가 제1 디바이스 구역(1A) 및 제2 디바이스 구역(1B) 각각에 배치된다. 그러나, 핀 구조체의 수는 2개(또는 4개)로 제한되지 않는다. 숫자는 하나, 둘, 셋 또는 다섯 이상일 수 있다. 추가로, 패턴화 프로세스(patterning processes)에서 패턴 충실도(fidelity)를 개선하기 위해 핀 구조체(20)의 양쪽 측면 근처에 하나 이상의 더미 핀 구조체가 배치될 수 있다. 핀 구조체(20)의 폭(W1)은 일부 실시예에서 약 5 nm 내지 약 40 nm의 범위에 있고, 특정 실시예에서 약 7 nm 내지 약 15 nm의 범위에 있을 수 있다. 핀 구조체(20)의 높이는 일부 실시예에서 약 100 nm 내지 약 300 nm의 범위에 있고, 다른 실시예에서 약 50 nm 내지 100 nm의 범위에 있을 수 있다.

- [0012] 게이트 전극(40) 아래의 핀 구조체(20)의 하부 부분은 웰 층(well layer)으로 지칭되고, 핀 구조체(20)의 상부부분은 채널 층으로 지칭된다. 게이트 전극(40) 아래, 웰 층이 격리 절연 층(50)에 임베디드되고(embedded), 채널 층은 격리 절연 층(50)으로부터 돌출한다. 채널 층의 하부 부분은 또한 약 1 nm 내지 약 5 nm의 깊이까지 격리 절연 층(50)에 임베디드될 수 있다.

- [0013] 웰 층의 높이는 일부 실시예에서 약 60 nm 내지 100 nm의 범위에 있고, 채널 층의 높이는 약 40 nm 내지 60 nm 의 범위에 있다.

- [0014] 또한, 핀 구조체(20) 사이의 공간 및/또는 하나의 핀 구조체와 기판(10) 위에 형성되는 다른 엘리먼트 사이의 공간이 절연 재료를 포함하는 격리 절연 층(50)(또는 소위 "얕은-트렌치-격리(shallow-trench-isolation: STI)" 층), 및 격리 절연 층(50) 위에 배치되는 층간(interlayer) 유전체 층(70)에 의해 충전된다. 격리 절연 층(50) 및 층간 유전체 층(70)을 위한 절연 재료는 실리콘 산화물, 실리콘 질화물, 실리콘 산화질화물(SiON), SiOCN, 플루오르-도핑 실리케이트 유리(fluorine-doped silicate glass: FSG), 또는 로우-K(low-K) 유전체 재료를 포함할 수 있다. 격리 절연 층(50)을 위한 절연 재료는 층간 절연체 층(70)에 대해 동일하거나 서로 다를

수 있다.

- [0015] 격리 절연 충(50)으로부터 돌출하는 핀 구조체(20)의 채널 충은 게이트 유전체 충(30)에 의해 커버되고, 게이트 유전체 충(30)은 게이트 전극(40)에 의해 더 커버된다. 게이트 전극(40)에 의해 커버되지 않는 채널 충의 일부는 MOS FET의 소스 및/또는 드레인으로서 기능한다(도 1b를 참조). 핀 구조체(20)는 제1 방향으로 연장하고 게이트 전극(40)은 제1 방향에 수직인 제2 방향으로 연장한다.

- [0016] 특정 실시예에서, 게이트 유전체 충(30)은 실리콘 산화물, 실리콘 질화물, 또는 하이-k 유전체 재료, 다른 적합한 유전체 재료, 및/또는 그 조합과 같은 유전체 재료를 포함한다. 하이-k 유전체 재료의 예는 HfO<sub>2</sub>, HfSiO, HfSiON, HfTaO, HfTiO, HfZrO, 지르코늄 산화물, 알루미늄 산화물, 티타늄 산화물, 하프늄 이산화물-알루미늄 (HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub>) 합금, 다른 적합한 하이-k 유전체 재료 및/또는 그 조합을 포함한다.

- [0017] 게이트 전극(40)은 폴리실리콘(polysilicon), 알루미늄, 구리, 티타늄(titanium), 탄탈륨(tantalum), 텅스텐 (tungsten), 코발트(cobalt), 몰리브덴(molybdenum), 탄탈륨 질화물, 니켈 규화물(silicide), 코발트 규화물, TiN, WN, TiAl, TiAlN, TaCN, TaC, TaSiN, 금속 합금, 다른 적합한 재료 및/또는 그 조합과 같은 임의의 적합한 재료를 포함한다. 특정 실시예에서, 게이트 전극은 금속 게이트 충(45)을 포함한다.

- [0018] 본 개시물의 특정 실시예에서, 하나 이상의 일 함수 조정 층(work function adjustment layers)(42)이 또한 게 이트 유전체 층(30)과 금속 게이트 층(45) 사이에 배치될 수 있다. 일 함수 조정 층은 단일 층 또는 대안적으 로 디바이스 성능을 강화하기 위해 금속 층과 선택된 일 함수의 다양한 조합(일 함수 금속 층)과 같은 다중-층 (multi-layer) 구조체, 라이너 층(liner layer), 습윤 층(wetting layer), 접착 층, 금속 합금 또는 금속 규화 물을 포함할 수 있다. 일 함수 조정 층은 Ti, Ag, Al, TiAlN, TaC, TaCN, TaSiN, Mn, Zr, TiN, TaN, Ru, Mo, Al, WN, Cu, W, Re, Ir, Co, Ni, 다른 적합한 금속 재료의 단일 층 또는 2개 또는 그 이상의 이들 재료의 다중 층과 같은 전도성 재료로 이루어진다. 일부 실시예에서, 일 함수 조정 층은 (예를 들어, 제1 디바이스 구역 (1A)에서) p-채널 Fin FET을 위한 제1 금속 재료 및 (예를 들어, 제2 디바이스 구역(1B)에서) n-채널 Fin FET 을 위한 제2 금속 재료를 포함할 수 있다. 예를 들어, n-채널 Fin FET을 위한 제1 금속 재료는 기판 전도 대역 의 일 함수와 실질적으로 정렬되거나, 핀 구조체(20)의 채널 층의 전도 대역의 일 함수와 실질적으로 정렬되는 일 함수를 가지는 금속을 포함할 수 있다. 유사하게, 예를 들어, p-채널 Fin FET을 위한 제2 금속 재료는 원자 가 전자대(valence band)의 일 함수와 실질적으로 정렬되거나, 핀 구조체(20)의 채널 층의 원자가 전자대의 일 함수와 적어도 실질적으로 정렬되는 일 함수를 가지는 금속을 포함할 수 있다. 일부 실시예에서, 일 함수 조정 층은 대안적으로 폴리실리콘 층을 포함할 수 있다. 일 함수 조정 층은 ALD(원자 층 증착(atomic layer deposition)), PVD, CVD, e-빔 증착(e-beam evaporation), 또는 다른 적합한 프로세스에 의해 형성될 수 있다. 또한, 일 함수 조정 층은 서로 다른 금속 층을 사용할 수 있는 n-채널 Fin FET 및 p-채널 Fin FET에 대해 별도 로 형성될 수 있다.

- [0019] 소스 및 드레인 구역에 불순물을 적절하게 도핑함으로써, 게이트 전극(40)에 의해 커버되지 않는 핀 구조체에 소스 및 드레인 구역이 또한 형성된다. Si 또는 Ge 및 Co, Ni, W, Ti 또는 Ta와 같은 금속의 합금은 소스 및 드레인 구역(25) 상에 형성될 수 있다. Si 및/또는 SiGe 충은 상승한 소스-드레인 구조체를 형성하고 적절한 응력을 채널 층에 가하기 위해 소스-드레인 구역에 에피택셜로 형성될 수 있다.

- [0020] 또한, 측벽 절연 층(80)이 게이트 전극(40)의 양쪽 측면에 배치된다. 게이트 전극(40) 및 소스/드레인 구역은 층간 절연체 층(70)에 의해 커버되고, 반도체 디바이스를 완성하도록 필요한 배선(wiring) 및/또는 비아(via)/접촉 홀(contact holes)이 배치된다.

- [0021] 일 함수 조정 충(42) 및 금속 게이트 충(45)을 포함하는 게이트 전극(40)의 폭(W2)은 일부 실시예에서 약 20 nm 내지 40 nm의 범위에 있다. 복수의 게이트 전극(40)이 폭 방향(width direction)으로 배치되고(도 1b를 참조), 게이트 전극의 피치는 일부 실시예에서 약 60 nm 내지 100 nm의 범위에 있다.

- [0022] 도 1a-1c에 도시된 바와 같이, 인접한 게이트 전극(40)은 절연 재료로 이루어지는 분리 플러그(60)에 의해 서로 분리된다. 도 1a에 도시되는 단면에서, 분리 플러그(60)는 더 작은 최상부 크기(폭) 및 더 큰 바닥부 크기 (폭)를 가지는 테이퍼링 형상(tapered shape)을 가진다. 분리 플러그의 최상부에서의 폭(W3)은 특정 실시예에서 약 20 mm보다 작고 일부 실시예에서 약 5 nm 내지 약 15 mm의 범위에 있을 수 있다. 분리 플러그의 바닥부 에서의 폭(W4)은 특정 실시예에서 약 35 nm보다 작고 일부 실시예에서 약 10 nm 내지 약 30 nm의 범위에 있을 수 있다. 여기서, 분리 플러그의 최상부는 게이트 전극(40)의 상부 표면에 대응하고 분리 플러그(60)의 바닥부는 게이트 유전체 층(30)의 바닥부 또는 격리 절연 층(50)과 층간 유전체 층(70) 사이의 계면에 대응한다. 분

리 플러그(70)를 위한 절연 재료는 실리콘 산화물, 실리콘 질화물, 실리콘 산화질화물(SiON), SiOCN, 플루오르-도핑 실리케이트 유리(fluorine-doped silicate glass: FSG) 또는 로우-k 유전체 재료를 포함할 수 있고, 격리 절연 층(50) 및/또는 층간 유전체 층(70)을 위한 절연 재료용 재료와 동일하거나 서로 다를 수 있다.

- [0023] 분리 플러그(70)를 위한 절연 재료는 격리 절연 충(50) 및/또는 충간 유전체 충(70)을 위한 절연 재료와 동일하 거나 서로 다를 수 있다.

- [0024] 도 2-12e는 본 개시물의 일 실시예에 따라 Fin FET 디바이스를 제조하는 예시적인 순차적 프로세스의 단면도를 도시한다. 도 2-12e에 의해 도시되는 프로세스 전에, 프로세스 동안 그리고 프로세스 후에 추가적인 동작이 제공될 수 있고, 이하에 설명된 동작 중 일부는 방법의 추가적인 실시예를 위해 교체될 수 있거나 제거될 수 있음이 이해된다. 동작/프로세스의 순서는 상호교환가능할 수 있다. 또한, 게이트 교체 기술에 의해 핀 구조체 위에 금속 게이트 구조체를 제조하기 위한 일반 동작은 미국 특허 공보 제2013/0161762 호에 개시되고, 그 전체 내용은 본원에 인용에 의해 포함된다.

- [0025] 핀 구조체를 제조하기 위해, 예를 들어, 열적 산화 프로세스 및/또는 화학 기상 증착(chemical vapor deposition: CVD) 프로세스에 의해 기판(10) 위에 마스크 층이 형성된다. 기판(10)은 예를 들어, 약 1.12×  $10^{15}$  cm<sup>-3</sup> 내지 약  $1.68 \times 10^{15}$  cm<sup>-3</sup>의 범위에 있는 불순물 농도를 가지는 p-타입 실리콘 기판이다. 다른 실시예에 서, 기판(10)은 약  $0.905 \times 10^{15}$  cm<sup>-3</sup> 내지 약  $2.34 \times 10^{15}$  cm<sup>-3</sup>의 범위에 있는 불순물 농도를 가지는 n-타입 실리콘 기판이다. 마스크 층은 일부 실시예에서 예를 들어, 패드 산화물(pad oxide)(예를 들어, 실리콘 산화물) 층 및 실리콘 질화물 마스크 층을 포함한다.

- [0026] 패드 산화물 층은 열적 산화 또는 CVD 프로세스를 이용함으로써 형성될 수 있다. 실리콘 질화물 마스크 층은 스퍼터링 방법과 같은 물리적 기상 증착(physical vapor deposition: PVD), CVD, 플라즈마-강화 화학 기상 증착(plasma-enhanced chemical vapor deposition: PECVD), 기압 화학 기상 증착(atmospheric pressure chemical vapor deposition: APCVD), 저압 CVD(low-pressure CVD: LPCVD), 고밀도 플라즈마 CVD(high density plasma CVD: HDPCVD), 원자 층 증착(atomic layer deposition: ALD) 및/또는 다른 프로세스에 의해 형성될 수 있다.

- [0027] 패드 산화물 층의 두께는 약 2 nm 내지 약 15 nm의 범위에 있고 일부 실시예에서 실리콘 질화물 마스크 층의 두 께는 약 2 nm 내지 약 50 nm의 범위에 있다. 마스크 층 위에 마스크 패턴이 또한 형성된다. 마스크 패턴은 예를 들어, 포토리소그래피에 의해 형성되는 포토레지스트 패턴이다.

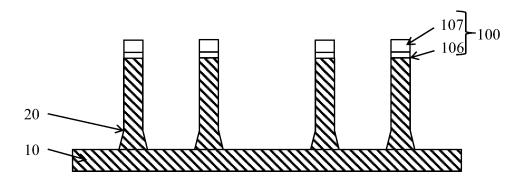

- [0028] 에칭 마스크로서 마스크 패턴을 사용함으로써, 패드 산화물 층(106) 및 실리콘 질화물 마스크 층(107)의 하드 마스크 패턴(100)이 형성된다. 일부 실시예에서 하드 마스크 패턴의 폭은 약 5 nm 내지 약 40 nm의 범위에 있다. 특정 실시예에서, 하드 마스크 패턴의 폭은 약 7 nm 내지 약 12 nm의 범위에 있다.

- [0029] 도 2에 도시된 바와 같이, 하드 마스크 패턴을 에칭 마스크로서 사용함으로써, 드라이 에칭 방법 및/또는 습식에 하 방법을 이용하는 트렌치 에칭에 의해 핀 구조체(20) 내로 기판(10)이 패턴화된다. 핀 구조체(20)의 높이는 약 100 nm 내지 약 300 nm의 범위에 있다. 특정 실시예에서, 높이는 약 50 nm 내지 약 100 nm의 범위에 있다. 핀 구조체의 높이가 균일하지 않을 때, 기판으로부터의 높이는 핀 구조체의 평균 높이에 대응하는 평면으로부터 측정될 수 있다.

- [0030] 본 실시예에서, 벌크 실리콘 웨이퍼가 시작 재료로서 사용되고 기판(10)을 구성한다. 그러나, 일부실시예에서, 다른 타입의 기판이 기판(10)으로서 사용될 수 있다. 예를 들어, 실리콘-온-절연체(silicon-on-insulator: SOI) 웨이퍼가 시작 재료로서 사용될 수 있고, SOI 웨이퍼의 절연체 층은 기판(10)을 구성하고 SOI 웨이퍼의 실리콘 층은 핀 구조체(20)를 위해 사용된다.

- [0031] 도 3에 도시된 바와 같이, 핀 구조체(20)를 완전히 커버하도록 기판(10) 위에 격리 절연 층(50)이 형성된다.

- [0032] 격리 절연 층(50)은 예를 들어, LPCVD(low pressure chemical vapor deposition), 플라즈마-CVD 또는 유동성 CVD에 의해 형성되는 실리콘 이산화물로 이루어진다. 유동성 CVD에서, 실리콘 산화물 대신에 유동성 유전체 재료가 증착된다. 그 명칭이 제시하는 바와 같이, 유동성 유전체 재료는 고 애스펙트 비(high aspect ratio)로 갭(gaps) 또는 공간을 충전하기 위해 증착 동안 "흐를" 수 있다. 대개, 증착된 막이 흐를 수 있게 하기 위해 실리콘-함유 전구체(silicon-containing precursors)에 다양한 화학이 추가된다. 일부 실시예에서, 질소 수소 화물 결합(nitrogen hydride bonds)이 추가된다. 유동성 유전체 전구체, 특히 유동성 실리콘 산화물 전구체의 예는 규산염(silicate), 실록산(siloxane), 메틸 실세스퀴옥산(methyl silsesquioxane: MSQ), 수소 실세스퀴옥

산(hydrogen silsesquioxane: HSQ), MSQ/HSQ, 페르히드로실라잔(perhydrosilazane: TCPS), 페르히드로-폴리실라잔(perhydro-polysilazane: PSZ), 테트라에틸로소실리케이트(tetraethylorthosilicate: TEOS), 또는 트리실릴아민(trisilylamine: TSA)과 같은 실릴-아민(silyl-amine)을 포함한다. 이들 유동성 실리콘 산화물 재료는다중-동작 프로세스에서 형성된다. 유동성 막이 중착된 후에, 실리콘 산화물을 형성하기 위해 바람직하지 않은엘리먼트를 제거하도록 유동성 막이 경화되고 그 후에 어닐링된다. 바람직하지 않은 엘리먼트가 제거될 때, 유동성 막은 치밀하게 되고 수축한다. 일부 실시예에서, 다수의 어닐링 프로세스가 수행된다. 유동성 막은 약1000℃ 내지 약 1200℃의 범위에서와 같은 온도에서, 그리고 총 30 시간 이상과 같은 연장 기간 동안 한번 이상경화되고 어닐링된다. 격리 절연 충(50)은 SOG를 사용함으로써 형성될 수 있다. SiO, SiON, SiOCN 또는 플루오르화물-도핑 실리케이트 유리(fluoride-doped silicate glass: FSG)가 일부 실시예에서 격리 절연 충(50)으로서 사용될 수 있다.

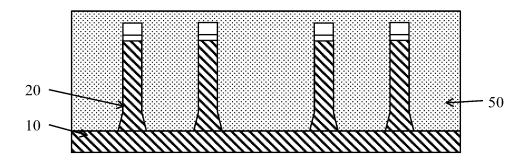

- [0033] 격리 절연 충(50)을 형성한 후에, 격리 절연 충(50) 및 패드 산화물 충(106)과 실리콘 질화물 마스크 충(107)을 포함하는 마스크 충(100)의 일부를 제거하도록 평탄화 동작이 수행된다. 그 후에, 도 4에 도시된 바와 같이, 채널 충이 되는 핀 구조체(20)의 상부 부분이 노출되도록 격리 절연 충(50)이 또한 제거된다.

- [0034] 격리 절연 층(50)을 형성한 후에, 열적 프로세스, 예를 들어, 어닐링 프로세스가 격리 절연 층(50)의 품질을 개선하기 위해 수행될 수 있다. 특정 실시예에서, 불활성 가스 분위기, 예를 들어, №, Ar 또는 He 분위기에서 약 1.5초 내지 약 10초 동안 약 900℃ 내지 약 1050℃ 범위의 온도에서 급격한 열적 어닐링(rapid thermal annealing: RTA)을 이용함으로서 열적 프로세스가 수행된다.

- [0035] 격리 절연 충(50) 및 노출된 핀 구조체(20) 위에 게이트 산화물 충(105) 및 폴리실리콘 충이 형성되고, 그 후에 폴리실리콘으로 이루어지는 폴리 게이트 충(110)을 획득하도록 패턴화 동작이 수행된다. 게이트 산화물 충(105)은 CVD, PVD, ALD, e-빔 중착 또는 다른 적합한 프로세스에 의해 형성되는 실리콘 산화물일 수 있다. 폴리 실리콘 충의 두께는 일부 실시예에서 약 5 내지 약 100 nm의 범위에 있다. 폴리 게이트 충(110) 및 게이트 산화물 충(105)은 게이트-교체 기술에서 지속적으로 제거되는 더미 충이다.

- [0036] 측벽 절연 층(80)이 또한 폴리 게이트 층(110)의 양쪽 측면에 형성된다.

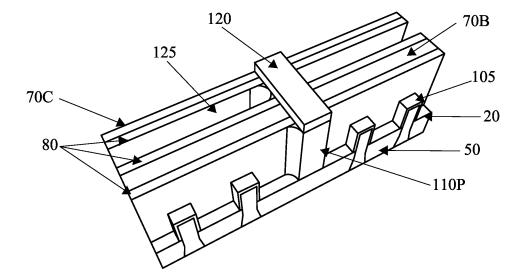

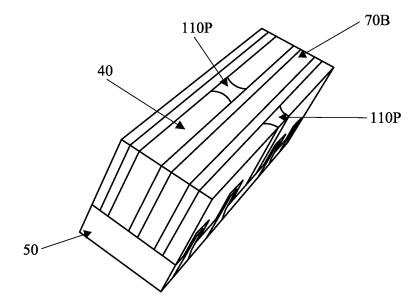

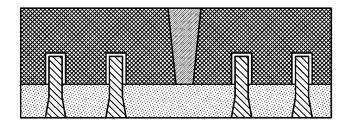

- [0037] 또한, 폴리 게이트 층(110), 측벽 절연 층(80) 사이의 공간에 그리고 폴리 게이트 층(110) 위에 층간 유전체 층 (70)이 형성된다. 도 5a-5c에 도시된 구조체를 획득하도록, 에치 백(etch back) 프로세스 및/또는 화학 기계적 연마(chemical mechanical polighing: CMP) 프로세스와 같은 평탄화 동작이 수행된다. 도 5a는 폴리 게이트 층(110) 및 층간 절연체 층(70)이 형성된 후에 Fin FET 디바이스의 단면도이고, 도 5b는 그 최상면도이고, 도 5c는 그 투시도이다. 도 5a는 도 5b에서의 라인 X-X를 따른 단면도이고, 도 5c는 도 5b에서의 밀봉 부분(B)에 대응한다.

- [0038] 도 5b 및 5c에 도시된 바와 같이, 특정 실시예에서, 일정한 피치(constant pitch)로 일 방향으로 연장되는 라인 -및-공간 배치(line-and-space arrangement)에 폴리 게이트 층(110)이 형성된다. 폴리 게이트 층(110)은 일 방향에 수직인 다른 방향으로 연장되는 다른 라인-및-공간 배치를 포함할 수 있다.

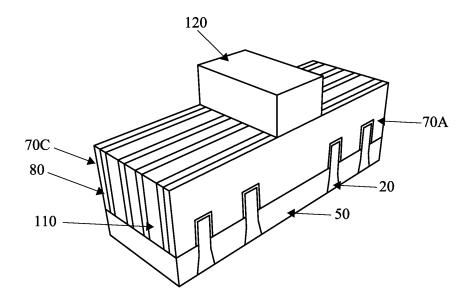

- [0039] 도 6에 도시된 바와 같이, 도 5c에 도시된 구조체 위에 마스크 패턴(120)이 형성된다. 마스크 패턴(120)은 예를 들어, 포토레지스트 층에 의해 형성된다. 형성된 바와 같은 마스크 패턴(120)의 폭은 일부 실시예에서 약 20 nm 내지 약 120 nm의 범위에 있고, 다른 실시예에서 약 40 nm 내지 약 60 nm의 범위에 있을 수 있다.

- [0040] 포토레지스트 충 대신에, 일부 실시예에서 마스크 충(120)은 폴리 실리콘 에칭 동안 높은 에칭 저항성을 가지는 재료에 의해 형성되는 하드 마스크일 수 있다. 하드 마스크 재료는 실리콘 산화물, 실리콘 산화질화물 또는 실리콘 질화물 또는 금속 재료를 포함한다.

- [0041] 도 7에 도시된 바와 같이, 원하는 폭을 획득하기 위해 드라이 에칭 동작을 이용함으로써 마스크 패턴(120)의 폭이 감소된다. 드라이 에칭 후에, 일부 실시예에서 마스크 패턴(120)의 폭은 약 5 nm 내지 약 100 nm 사이의 범위에 있고, 다른 실시예에서 약 10 nm 내지 30 nm 사이의 범위에 있을 수 있다. 마스크 패턴의 폭을 감소시키는 대신에, 원하는 폭을 가지는 마스크 패턴(120)을 직접 형성할 수 있다.

- [0042] 도 8에 도시된 바와 같이, 마스크 패턴(120)을 사용함으로써, 폴리 게이트 층(110)의 일부가 에칭되고, 그에 의해 공간(125)을 형성한다. 도 8에서 그리고 그 후에, 층간 절연체 층(70)의 일 층(70A)은 에칭된 폴리 게이트 층(110) 및 공간(125)을 도시하기 위해 생략되는 한편, 다른 층(70B 및 70C)은 여전히 도시된다. 일부 실시예에서, 3 내지 20 mTorr의 압력 하에서 CH<sub>4</sub>, CF<sub>4</sub>, CH<sub>2</sub>F<sub>2</sub>, CHF<sub>3</sub>, O<sub>2</sub>, HBr, Cl<sub>2</sub>, NF<sub>3</sub>, N<sub>2</sub> 및/또는 He를 포함하는 가

스를 사용하는 플라즈마 에칭에 의해 폴리 게이트 층의 에칭이 수행된다. 폴리 게이트 층(110)의 일부를 제거 함으로써, 공간(125) 사이에 폴리 필라(poly pillar)(110P)가 형성된다.

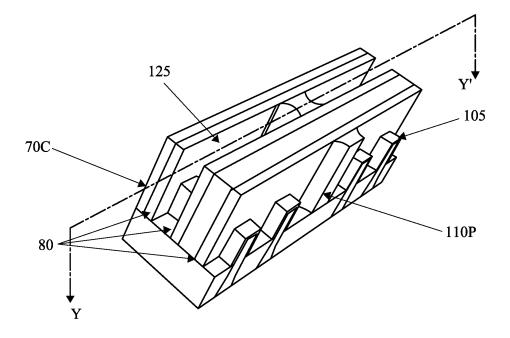

- [0043] 도 9a에 도시된 바와 같이, 마스크 패턴(120)(예를 들어, 포토레지스트 패턴)은 회분화 프로세스(ashing process) 및/또는 웨트 클리닝 프로세스(wet cleaning process)에 의해 제거된다.

- [0044] 도 8에 도시되는 폴리 실리콘 에칭에서, 폴리 게이트 충(110)의 중심에서의 에칭 속도는 폴리 게이트 충(110)과 측벽 절연 충(side-wall insulating layers)(80) 사이의 계면에서의 에칭 속도보다 비교적 더 높다. 따라서, 상기로부터 보이는 폴리 필라의 단부 형상은 도 9b에 도시된 바와 같은 오목한 만곡 형상을 가진다. 다시 말해, 공간(125)은 폴리 필라(110P)에서 볼록한 만곡 형상을 가진다.

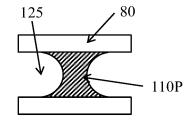

- [0045] 또한, 폴리 실리콘 에칭 후의 폴리 필라(110P)는 도 9c에 도시된 바와 같은 테이퍼링 형상을 가지고, 이는 도 9a의 라인 Y-Y'을 따른 단면도이다. 폴리 필라(110P)의 바닥부에서의 테이퍼 각도(taper angle) Θ는 90 도 이상이고, 특정 실시예에서 약 93 도 내지 약 100 도의 범위에 있을 수 있다. 일부 실시예에서, 폴리 필라(110 P)의 형상/테이퍼 각도를 조정하기 위해 폴리 실리콘 에칭 후에 추가적인 에칭 동작이 수행될 수 있다.

- [0046] 도 10에 도시된 바와 같이, 금속 게이트 전극(40) 및 게이트 유전체 층(30)(도 10에 도시되지 않음)을 포함하는 금속 게이트 구조체는 폴리 게이트 필라(110P) 사이의 공간(125)에 형성된다. 게이트 유전체 층(30)은 CVD, ALD 또는 다른 적합한 막 형성 방법에 의해 형성된다. 금속 게이트 전극(40)은 CVD, (스퍼터링을 포함하는) PVD, ALD, 전기-도금(electro-plating) 또는 다른 적합한 금속 막 형성 방법에 의해 형성된다. 공간(125)은 그 단부에 볼록한 만곡 형상을 가지기 때문에, 금속 게이트 전극(40)을 위한 금속 재료는 공극(void) 또는 층 (seam)을 형성하지 않고서 공간(125)에 충전될 수 있다.

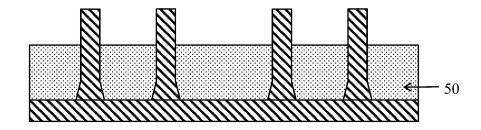

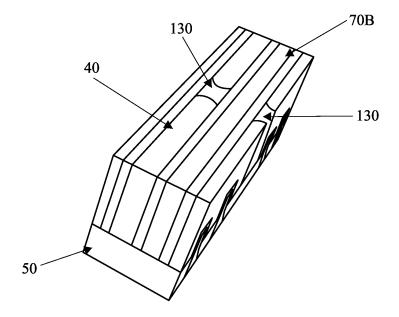

- [0047] 도 11에 도시된 바와 같이, 폴리 필라(110P)는 에칭 동작에 의해 제거됨으로써, 개구(130)를 형성한다. 에칭 동작은 드라이 에칭 및/또는 습식 에칭을 포함할 수 있다.

- [0048] 폴리 필라(110P)를 제거한 후에, 예를 들어, CVD 프로세스를 이용함으로써, 도 11에 도시된 구조체 위에 절연 재료가 형성되고, 개구(130)는 절연 재료로 충전된다. CVD 프로세스는 LPCVD 프로세스, 플라즈마 CVD 프로세스 및/또는 유동성 CVD 프로세스를 포함할 수 있다. 유동성 CVD 프로세스에서, SiH₄, NH₃, N₂, O₂, N₂O, Cl₂ 및/또는 NO₂를 포함하는 가스가 사용될 수 있고 일부 실시예에서, 약 200℃ 내지 약 1000℃ 범위의 온도에서 증착이 수행된다.

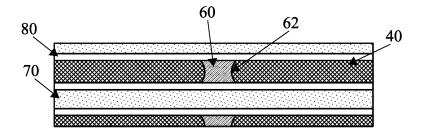

- [0049] 도 12a-12c에 도시된 바와 같이, 금속 게이트 전극(40) 위에 절연 재료의 일부분이 형성된 후에, 측벽 절연 층 (80) 및 충간 유전체 층(70)이 평탄화 동작에 의해 제거되고, 분리 플러그(60)가 획득된다. 평탄화 동작은 CMP 및/또는 에칭-백 프로세스를 포함할 수 있다. 도 12a는 분리 플러그(60)가 형성된 후의 예시적인 투시도이고, 도 12b는 도 12a의 라인 Y-Y'을 따른 예시적인 단면도이고, 도 12c는 예시적인 최상면도이다.

- [0050] 도 12a 및 12c에 도시된 바와 같이, 위로부터 보이는 분리 플러그(60)의 단부 형상(62)이 오목한 만곡 형상을 갖되, 금속 게이트 전극(40)의 단부는 볼록한 만곡 형상을 가진다. 분리 플러그(60)는 도 12b에 도시된 바와 같은 테이퍼링 형상을 가지고, 분리 플러그(60)의 바닥부에서의 테이퍼 각도 θ는 90 도 이상이다. 일부 실시예에서, 테이퍼 각도 θ는 약 93 내지 약 100 도의 범위에 있다.

- [0051] 접촉부/비아(vias), 상호연결 금속 층, 유전체 층, 수동 층(passivation layers) 등과 같은 다양한 피처를 형성하기 위해 Fin FET는 추가적인 CMOS 프로세스를 경험할 수 있음이 이해된다.

- [0052] 또한, 상술한 게이트 교체 기술은 평탄한 타입 FET에 적용될 수 있다.

- [0053] 본원에 설명되는 다양한 실시예 또는 예는 종래 기술을 능가하는 여러 장점을 제공한다. 상기에 설명된 바와 같이, 본 개시물에서, 금속 게이트 전극(40)이 형성된 후에 분리 플러그가 형성된다. 금속 게이트 전극(40)의 단부는 분리 플러그(60)를 향해 볼록한 만곡 형상을 가지고, 분리 플러그(60)는 테이퍼링 형상을 가진다. 반대로, 금속 게이트 전극을 형성하기 전에 분리 플러그가 형성될 때, 분리 플러그의 형상은 도 13a에 도시된 바와같이 역 테이퍼링될 것이고, 분리 플러그의 단부는 도 13b에 도시된 바와 같이 볼록한 형상을 가질 것이다. 그와 같은 경우에, 금속 게이트 전극을 위한 금속 재료가 형성될 때, 공극 또는 층이 분리 플러그 근처에 발생할 것이다.

- [0054] 그러나, 상기에 설명된 바와 같이, 도 1-12c에 도시된 본 기술에서, 금속 게이트 전극(40)을 위한 금속 재료는 공극 또는 층을 형성하지 않고서 공간(125)에 충전될 수 있다.

- [0055] 모든 장점이 반드시 본원에 논의될 필요는 없고, 모든 실시예 또는 예를 위해 특정 장점이 요구되는 것이 아니고, 다른 실시예 또는 예가 서로 다른 장점을 제공할 수 있음이 이해될 것이다.

- [0056] 본 개시물의 일 양상에 따르면, 반도체 디바이스는 제1 및 제2 Fin FET 및, 절연 재료로 형성되고 제1 및 제2 Fin FET 사이에 배치되는 분리 플러그를 포함한다. 제1 Fin FET은 제1 방향으로 연장되는 제1 핀 구조체, 제1 핀 구조체 위에 형성되는 제1 게이트 유전체 및 제1 게이트 유전체 위에 형성되고 제1 방향에 수직인 제2 방향으로 연장되는 제1 게이트 전극을 포함한다. 제2 Fin FET은 제2 핀 구조체, 제2 핀 구조체 위에 형성되는 제2 게이트 유전체 및, 제1 게이트 유전체 위에 형성되고 제2 방향으로 연장되는 제2 게이트 전극을 포함한다. 상 부에서 볼 때, 분리 플러그의 단부 형상은 오목한 만곡 형상을 갖되, 분리 플러그에 인접한 제1 게이트 전극의 단부는 볼록한 만곡 형상을 가진다.

- [0057] 본 개시물의 다른 양상에 따르면, 반도체 디바이스를 제조하기 위한 방법에서, 더미 전극 구조체 및 층간 유전체 층이 형성된다. 더미 전극 구조체는 더미 게이트 전극 층 및 더미 게이트 전극 층의 양쪽 주된 측면에 배치되는 측벽 절연 층을 포함한다. 더미 전극 층의 양쪽 주된 측면에 층간 유전체 층이 배치된다. 제1 공간 및 제2 공간이 측벽 절연 층 사이에 형성되도록 더미 게이트 전극 층의 일부가 제거된다. 제1 전극 공간 및 제2 전극 공간은 더미 게이트 전극 층의 나머지 부분인 필라에 의해 분리된다. 제1 게이트 구조체 및 제2 게이트 구조체는 제1 전극 공간 및 제2 전극 공간 각각에 형성된다. 제1 게이트 구조체와 제2 게이트 구조체 사이에 개구가 형성되도록 필라가 제거된다. 절연 재료로 개구를 충전함으로써 분리 플러그가 형성된다.

- [0058] 본 개시물의 다른 양상에 따르면, 반도체 디바이스는 제1 게이트 유전체 층 및 금속 게이트 전극을 포함하는 FET 및 절연 재료로 형성되고 FET에 근접하게 배치되는 분리 플러그를 포함한다. 상부에서 볼 때, 분리 플러그의 단부 형상은 오목한 만곡 형상을 갖되, 분리 플러그에 인접하는 금속 게이트 전극의 단부는 볼록한 만곡 형상을 가진다.

- [0059] 전술한 바는 당업자가 본 개시물의 양상을 더 잘 이해할 수 있도록 여러 실시예 또는 예의 피처를 개략한다. 당업자는 본원에 도입되는 실시예 또는 예의 동일한 목적을 실행하고 및/또는 동일한 장점을 달성하기 위한 다른 프로세스 및 구조체를 설계하거나 수정하기 위한 기반으로서 본 개시물을 용이하게 이용할 수 있음을 인식해야 한다. 당업자는 또한 그와 같은 동등한 구성이 본 개시물의 정신 및 범위로부터 이탈하지 않는 것이고, 본 개시물의 정신 및 범위를 이탈하지 않고서 본원에 다양한 변경, 치환 및 개조를 수행할 수 있음을 깨달아야 한다.

### 도면1a

# *도면1b*

# *도면1c*

도면4

## 도면5a

*도면5b*

# *도면5c*

# 도면9a

# *도면9b*

# 도면9c

도면10

## 도면12a

# 도면12b

## 도면12c

# 도면13a

## 도면13b