10-2021-0041931

2021년04월16일

# (19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

H01L 27/15 (2006.01) H01L 21/324 (2017.01) H01L 29/778 (2006.01) H01L 33/02 (2010.01)

(52) CPC특허분류

H01L 27/156 (2013.01) H01L 21/3065 (2013.01)

(21) 출원번호

10-2019-0124776

(22) 출원일자

2019년10월08일

심사청구일자 없음

(43) 공개일자 (71) 출원인

(11) 공개번호

삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

(72) 발명자

박진주

경기도 용인시 수지구 신수로683번길 19, 108동 804호 (풍덕천동, 래미안수지이스트파크)

최준희

경기도 성남시 분당구 미금로 177, 314동 402호 (구미동, 까치마을)

(뒷면에 계속)

(74) 대리인

리앤목특허법인

전체 청구항 수 : 총 17 항

# (54) 발명의 명칭 반도체 장치, 그 제조 방법 및 이를 포함하는 디스플레이 장치

### (57) 요 약

일 예시에 따른 반도체 장치는 상면을 따라 구별되는 제1 영역 및 제2 영역을 포함하는 기판, 상기 제1 영역 및 상기 제2 영역 상에 배치되는 에칭 방지층, 상기 에칭 방지층의 상부 중 상기 제1 영역에 배치되는 분리층, 상기 기판의 상면에 수직한 제1 방향을 따라 상기 분리층의 상부에 배치되는 HEMT(High Electron Mobility Transistor) 소자, 상기 기판과 상기 에칭 방지층의 사이에서, 상기 제2 영역에 배치되는 발광 소자 및 상기 HEMT 소자의 측면을 덮으며, 상기 에칭 방지층까지 연장되는 제1 절연 패턴을 포함할 수 있다.

# 대 표 도 - 도1

#### (52) CPC특허분류

H01L 21/324 (2013.01) H01L 29/778 (2013.01) H01L 33/02 (2013.01)

H01L 2924/10323 (2013.01) H01L 2924/10344 (2013.01)

(72) 발명자

#### 공기호

경기도 수원시 권선구 동수원로177번길 90, 902동 509호 (권선동, 수원아이파크시티아파트)

### 한주헌

경기도 화성시 동탄기흥로 393-15, 1505동 404호 (오산동, 동탄역 반도유보라 아이비파크 5.0)

#### 김낙현

경기도 수원시 영통구 삼성로 130 ,연구2동(매탄 동,삼성전자공업단지)

#### 박정훈

경기도 용인시 수지구 수풍로 89, 104동 1303호 ( 동천동, 더샵 동천이스트포레)

# 명 세 서

### 청구범위

#### 청구항 1

상면을 따라 구별되는 제1 영역 및 제2 영역을 포함하는 기판;

상기 제1 영역 및 상기 제2 영역 상에 배치되는 에칭 방지층;

상기 에칭 방지층의 상부 중 상기 제1 영역에 배치되는 분리층;

상기 기판의 상면에 수직한 제1 방향을 따라 상기 분리층의 상부에 배치되는 HEMT(High Electron Mobility Transistor) 소자;

상기 기판과 상기 에칭 방지층의 사이에서, 상기 제2 영역에 배치되는 발광 소자; 및

상기 HEMT 소자의 측면을 덮으며, 상기 에칭 방지층까지 연장되는 제1 절연 패턴; 을 포함하는,

반도체 장치.

#### 청구항 2

제 1 항에 있어서,

상기 에칭 방지층은 플라즈마 에칭 공정으로부터 하부에 배치된 상기 발광 소자를 보호하기 위한 AlGaN, AlN 중하나 이상을 포함하는,

반도체 장치.

#### 청구항 3

제 2 항에 있어서,

상기 에칭 방지층은 P-형 도핑 물질로서 마그네슘을 포함하는,

반도체 장치.

### 청구항 4

제 1 항에 있어서,

상기 발광 소자는:

상기 기판의 상기 제1 영역 및 상기 제2 영역에 배치되는 하부 반도체층;

상기 하부 반도체층의 상부 중 상기 제2 영역에 배치되는 활성층;

상기 활성층의 상부에 배치되는 상부 반도체층; 을 포함하는,

반도체 장치.

#### 청구항 5

제 4 항에 있어서,

상기 제1 방향을 따라 연장되며 상기 에칭 방지층, 상기 상부 반도체층 및 상기 활성층의 측면을 덮는 제2 절연 패턴;을 더 포함하는,

반도체 장치.

#### 청구항 6

제 4 항에 있어서,

상기 HEMT 소자는 소스 전극, 게이트 전극 및 드레인 전극을 포함하고, 상기 발광 소자는 상기 드레인 전극에 연결되는 상부 전극을 포함하며,

상기 상부 전극은 상기 에칭 방지층을 관통하여 상기 발광소자에 연결되는,

반도체 장치.

#### 청구항 7

제 4 항에 있어서,

상기 분리층과 상기 기판 사이에 제공되는 상부 스페이서 층; 및

상기 상부 스페이서 층과 상기 기판 사이에 제공되는 하부 스페이서 층;을 더 포함하며,

상기 하부 반도체 층은 상기 상기 하부 스페이서 층과 상기 기판 사이에 배치되는,

반도체 장치.

#### 청구항 8

기판;

상기 기판 상에 소정의 간격을 사이에 두고 이격되도록 배치되는 발광 소자들;

상기 발광 소자들 사이에 각각 제공되는 분리층들;

상기 기판의 상면에 수직한 일 방향을 따라 상기 분리층들 상부에 각각 배치되는 HEMT 소자들;

상기 분리층들의 하부에 각각 배치되며, 상기 발광소자들의 상부에 각각 배치되는 에칭 방지층;

상기 HEMT 소자들의 측면들 및 상기 에칭 방지층들의 측면들 상에 각각 제공되는 제1 절연 패턴들; 및

상기 발광 소자들의 측면들 및 상기 에칭 방지층들의 측면들 상에 각각 제공되는 제2 절연 패턴들;을 포함하는, 디스플레이 장치.

#### 청구항 9

제 8 항에 있어서,

상기 에칭 방지층은 플라즈마 에칭 공정으로부터 하부에 배치된 상기 발광 소자를 보호하기 위한 AlGaN, AlN 중하나 이상을 포함하는,

디스플레이 장치.

#### 청구항 10

제 9 항에 있어서,

상기 에칭 방지층은 P-형 도핑 물질로서 마그네슘을 포함하는,

디스플레이 장치.

#### 청구항 11

제1 영역 및 제2 영역으로 구별되는 기판의 상부 영역에 하부 반도체층, 활성층, 상부 반도체층, 분리층, 에칭 방지층, 채널층 및 채널 공급층을 적층시키는 단계;

상기 제2 영역에 배치된 상기 채널 공급층, 상기 채널층, 및 상기 분리층 을 상기 기판의 상면에 수직하는 제1 방향을 따라 식각시키는 단계;

상기 에칭 방지층에 고온의 열처리 공정을 수행하는 단계;

상기 제1 영역에 배치된 상기 채널 공급층, 상기 채널층, 상기 분리층 및 상기 에칭 방지층의 측부에 제1 분술물을 주입하여 제1 절연 패턴을 형성하고, 상기 제2 영역에 배치된 상기 에칭 방지층, 상부 반도체층 및 상기

활성층의 측부에 제2 분술물을 주입하여 제2 절연 패턴을 형성하는 단계;를 포함하는 반도체 장치의 제조 방법.

### 청구항 12

제 11 항에 있어서,

상기 식각 공정은 선택적 플라즈마 에칭 공정으로 진행되며, 상기 에칭 방지층은 상기 선택적 플라즈마 에칭 공정으로부터 하부에 배치된 상기 발광 소자를 보호하기 위한 AlGaN, AlN 중 하나 이상을 포함하는,

반도체 장치의 제조 방법.

#### 청구항 13

제12 항에 있어서,

상기 에칭 방지층은 P-형 도핑 물질로서 마그네슘을 포함하며, 상기 열처리 공정에서 상기 마그네슘은 상기 상부 반도체층으로 분산되고, 상기 상부 반도체층에 포함된 수소 가스가 외부로 방출되는,

반도체 장치의 제조 방법.

#### 청구항 14

제13 항에 있어서.

상기 열처리 공정은 질소 분위기하에서 700 °C 이상 1000 °C 이하에서 3분 이하의 시간 동안 진행되는.

반도체 장치의 제조 방법.

#### 청구항 15

제 11 항에 있어서,

상기 에칭 방지층의 상부에 증착 물질을 증착시키는 단계;

상기 증착 물질을 고온에서 어닐링 시키는 단계;를 더 포함하며,

상기 어닐링된 금속 또는 금속 화합물은 상기 에칭 방지층을 관통하여 상기 상부 반도체층에 접촉하는 상부 전 극을 형성하는

반도체 장치의 제조 방법.

#### 청구항 16

제 15 항에 있어서,

상기 증착 물질은 티타늄(Ti), 알루미늄(Al), 니켈(Ni), 금(Au) 중 하나 이상을 포함하며, 상기 어닐링 단계는  $400^{\circ}$ C 이상의 온도에서 3분 이하의 시간동안 어닐링되는,

반도체 장치의 제조 방법.

#### 청구항 17

제 15 항에 있어서,

상기 채널 공급층의 상부에 소스 전극, 드레인 전극 및 게이트 전극이 배치되며, 상기 상부 전극은 상기 드레인 전극에 연결되는,

반도체 장치의 제조 방법.

#### 발명의 설명

# 기 술 분 야

[0001] 본 개시는 반도체 장치, 반도체 장치의 제조 방법, 및 디스플레이 장치에 관한 것이다.

# 배경기술

[0002] LED(Light Emitting Diode) 장치는 백라이트 유닛(Back Light Unit)의 광원으로사용되었으며, 이후, 서로 다른 파장의 광을 발광하는 LED들이 그룹화되어 하나의 픽셀을 구성하고, 이렇게 구성된 픽셀들이 매트릭스 형태로 배열되어 구현된 풀-컬러(full color) LED 디스플레이 장치에 사용되었다. 더 나아가, 하나의 픽셀을 구성하는 칩들의 크기(칩의 크기는 칩의 한 면의 길이임)가 100 마이크로미터 이하인 마이크로 LED(micro-light emitting diode)를 이용하여 고해상도 디스플레이 장치를 제작하는 기술이 각광을 받고 있다. 그러나, 마이크로 -LED를 이용한 고해상도 디스플레이 장치를 제작하기 위해서는 고효율의 소형 LED 칩들 제작하여야 하며, 소형 LED 칩들을 적절한 위치에 배열시키기 위해서 고난이도의 전사(transfer) 기술이 요구된다.

### 발명의 내용

### 해결하려는 과제

- [0003] 일 측면은 플라즈마 에칭 공정에 의해 LED 발광부가 손상되는 것을 방지할 수 있는 고해상도를 갖는 디스플레이 장치를 제공하는 것에 있다.

- [0004] 다른 일 측면은 플라즈마 에칭 공정에 의해 LED 발광부가 손상되는 것을 방지할 수 있는 디스플레이 장치의 제조 방법을 제공하는 것에 있다.

- [0005] 다만, 해결하고자 하는 과제는 상기 개시에 한정되지 않는다.

### 과제의 해결 수단

- [0006] 일 측면을 따른 반도체 장치는, 상면을 따라 구별되는 제1 영역 및 제2 영역을 포함하는 기판, 상기 제1 영역 및 상기 제2 영역 상에 배치되는 에칭 방지층, 상기 에칭 방지층의 상부 중 상기 제1 영역에 배치되는 분리층, 상기 기판의 상면에 수직한 제1 방향을 따라 상기 분리층의 상부에 배치되는 HEMT(High Electron Mobility Transistor) 소자, 상기 기판과 상기 에칭 방지층의 사이에서, 상기 제2 영역에 배치되는 발광 소자, 및 상기 HEMT 소자의 측면을 덮으며, 상기 에칭 방지층까지 연장되는 제1 절연 패턴을 포함할 수 있다.

- [0007] 상기 에칭 방지층은 플라즈마 에칭 공정으로부터 하부에 배치된 상기 발광 소자를 보호하기 위한 AlGaN, AlN 중하나 이상을 포함할 수 있다.

- [0008] 상기 에칭 방지층은 P-형 도핑 물질로서 마그네슘을 포함할 수 있다

- [0009] 상기 발광 소자는: 상기 기판의 상기 제1 영역 및 상기 제2 영역에 배치되는 하부 반도체층; 상기 하부 반도체층의 상부 중 상기 제2 영역에 배치되는 활성층; 상기 활성층의 상부에 배치되는 상부 반도체층을 포함할 수 있다.

- [0010] 상기 제1 방향을 따라 연장되며 상기 에칭 방지층, 상기 상부 반도체층 및 상기 활성층의 측면을 덮는 제2 절연 패턴을 더 포함할 수 있다.

- [0011] 상기 HEMT 소자는 소스 전극, 게이트 전극 및 드레인 전극을 포함하고, 상기 발광 소자는 상기 드레인 전극에 연결되는 상부 전극을 포함하며, 상기 상부 전극은 상기 에칭 방지층을 관통하여 상기 발광소자에 연결될 수 있다.

- [0012] 상기 분리층과 상기 기판 사이에 제공되는 상부 스페이서 층 및, 상기 상부 스페이서 층과 상기 기판 사이에 제공되는 하부 스페이서 층을 더 포함하며, 상기 하부 반도체 층은 상기 상기 하부 스페이서 층과 상기 기판 사이에 배치될 수 있다.

- [0013] 일 측면에 따른 디스플레이 장치는 기판, 상기 기판 상에 소정의 간격을 사이에 두고 이격되도록 배치되는 발광 소자들, 상기 발광 소자들 사이에 각각 제공되는 분리층들, 상기 기판의 상면에 수직한 일 방향을 따라 상기 분리층들 상부에 각각 배치되는 HEMT 소자들, 상기 분리층들의 하부에 각각 배치되며, 상기 발광소자들의 상부에 각각 배치되는 에칭 방지층, 상기 HEMT 소자들의 측면들 및 상기 에칭 방지층들의 측면들 상에 각각 제공되는 제1 절연 패턴들 및 상기 발광 소자들의 측면들 및 상기 에칭 방지층들의 측면들 상에 각각 제공되는 제2 절연 패턴들을 포함할 수 있다.

- [0014] 상기 에칭 방지층은 플라즈마 에칭 공정으로부터 하부에 배치된 상기 발광 소자를 보호하기 위한 AlGaN, AlN 중하나 이상을 포함할 수 있다.

- [0015] 상기 에칭 방지층은 P-형 도핑 물질로서 마그네슘을 포함할 수 있다.

- [0016] 일 측면에 따른 반도체 장치의 제조 방법은, 제1 영역 및 제2 영역으로 구별되는 기판의 상부 영역에 하부 반도 체충, 활성층, 상부 반도체층, 분리층, 에칭 방지층, 채널층 및 채널 공급층을 적층시키는 단계, 상기 제2 영역에 배치된 상기 채널 공급층, 상기 채널층, 및 상기 분리층 을 상기 기판의 상면에 수직하는 제1 방향을 따라 식각시키는 단계, 상기 에칭 방지층에 고온의 열처리 공정을 수행하는 단계, 상기 제1 영역에 배치된 상기 채널 공급층, 상기 채널층, 상기 분리층 및 상기 에칭 방지층의 측부에 제1 분술물을 주입하여 제1 절연 패턴을 형성하고, 상기 제2 영역에 배치된 상기 에칭 방지층, 상부 반도체층 및 상기 활성층의 측부에 제2 분술물을 주입하여 제2 절연 패턴을 형성하는 단계를 포함할 수 있다.

- [0017] 상기 식각 공정은 선택적 플라즈마 에칭 공정으로 진행되며, 상기 에칭 방지층은 상기 선택적 플라즈마 에칭 공 정으로부터 하부에 배치된 상기 발광 소자를 보호하기 위한 AlGaN, AlN 중 하나 이상을 포함할 수 있다.

- [0018] 상기 에칭 방지층은 P-형 도핑 물질로서 마그네슘을 포함하며, 상기 열처리 공정에서 상기 마그네슘은 상기 상부 반도체층으로 분산되고, 상기 상부 반도체층에 포함된 수소 가스가 외부로 방출될 수 있다.

- [0019] 상기 열처리 공정은 질소 분위기하에서 700°C 이상 1000°C 이하에서 3분 이하의 시간 동안 진행될 수 있다.

- [0020] 상기 에칭 방지층의 상부에 증착 물질을 증착시키는 단계, 상기 증착 물질을 고온에서 어닐링 시키는 단계를 더 포함하며, 상기 어닐링된 금속 또는 금속 화합물은 상기 에칭 방지층을 관통하여 상기 상부 반도체층에 접촉하는 상부 전극을 형성할 수 있다.

- [0021] 상기 중착 물질은 티타늄(Ti), 알루미늄(Al), 니켈(Ni), 금(Au) 중 하나 이상을 포함하며, 상기 어닐링 단계는  $400^{\circ}$ C 이상의 온도에서 3분 이하의 시간동안 어닐링될 수 있다.

- [0022] 상기 채널 공급층의 상부에 소스 전극, 드레인 전극 및 게이트 전극이 배치되며, 상기 상부 전극은 상기 드레인 전극에 연결될 수 있다.

#### 발명의 효과

- [0023] 본 개시는 하나의 기판 상에 모놀리식(Monolithic)하게 집적된 고 전자 이동도 트랜지스터(HEMT) 소자 및 발광 소자를 포함하는 반도체 장치를 제공할 수 있다.

- [0024] 본 개시는 플라즈마 에칭 공정에 의해 발광부가 손상되는 것을 방지할 수 있는 고해상도를 갖는 반도체 장치를 제공할 수 있다.

- [0025] 본 개시는 하나의 기판 상에 모놀리식하게 집적된 고 전자 이동도 트랜지스터 소자 및 발광 소자를 포함하는 반 도체 장치의 제조 방법을 제공할 수 있다.

- [0026] 본 개시는 플라즈마 에칭 공정에 의해 발광부가 손상되는 것을 방지할 수 있는 반도체 장치의 제조 방법을 제공할 수 있다.

- [0027] 다만, 발명의 효과는 상기 개시에 한정되지 않는다.

#### 도면의 간단한 설명

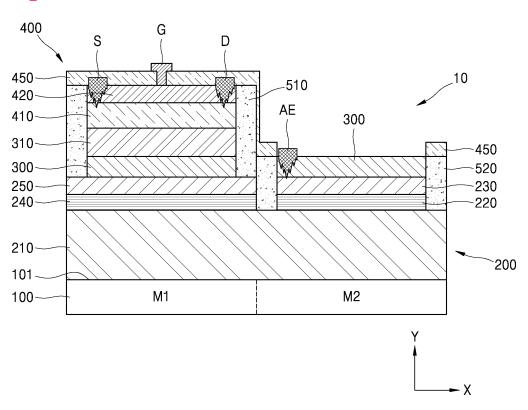

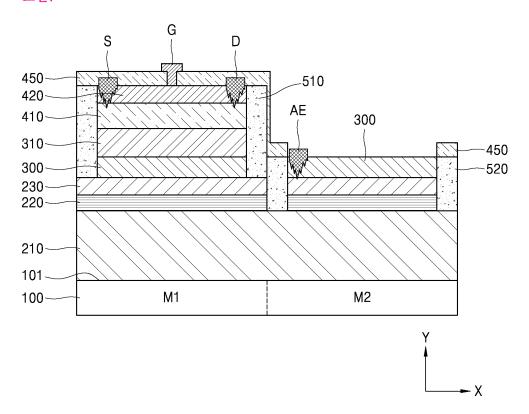

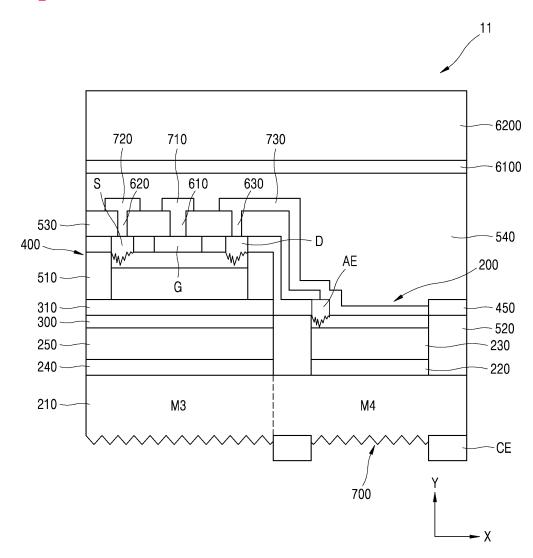

[0028] 도 1은 일 실시예에 따른 반도체 장치를 나타내는 도면이다.

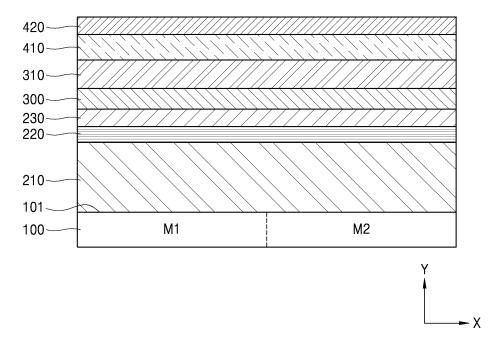

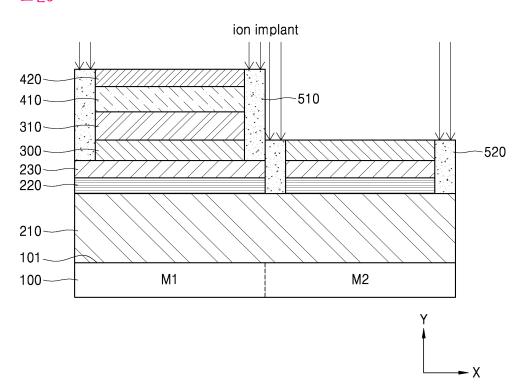

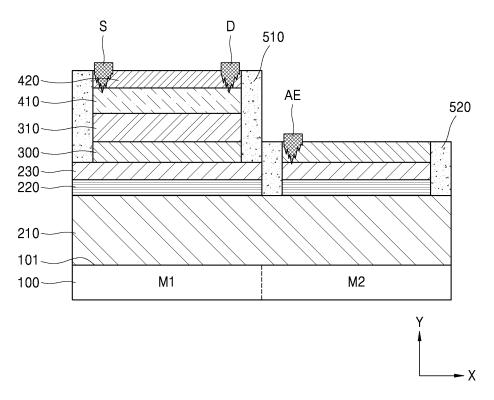

도 2는 도 1을 참조하여 설명된 반도체 장치의 제조 방법을 각 단계별로 설명하기 위한 도면이다.

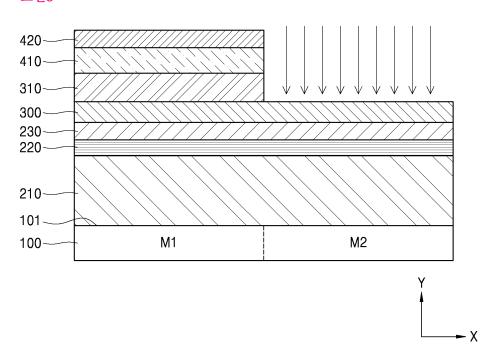

도 3은 도 1을 참조하여 설명된 반도체 장치의 제조 방법을 각 단계별로 설명하기 위한 도면이다.

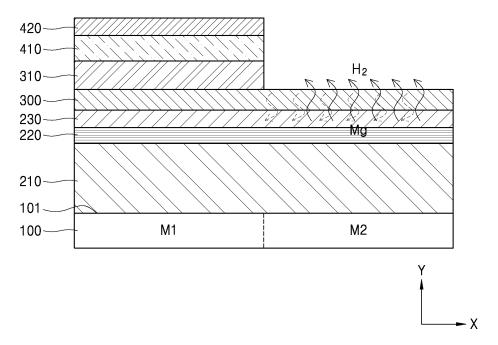

도 4는 도 1을 참조하여 설명된 반도체 장치의 제조 방법을 각 단계별로 설명하기 위한 도면이다.

도 5는 도 1을 참조하여 설명된 반도체 장치의 제조 방법을 각 단계별로 설명하기 위한 도면이다.

도 6은 도 1을 참조하여 설명된 반도체 장치의 제조 방법을 각 단계별로 설명하기 위한 도면이다.

도 7은 도 1을 참조하여 설명된 반도체 장치의 제조 방법을 각 단계별로 설명하기 위한 도면이다.

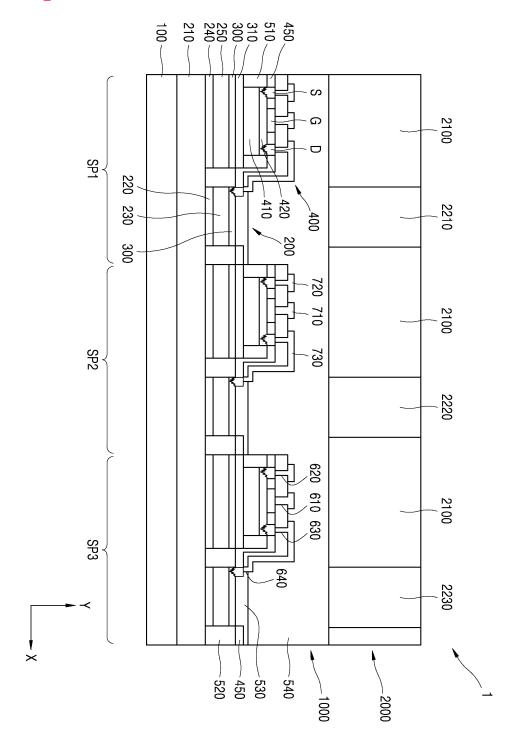

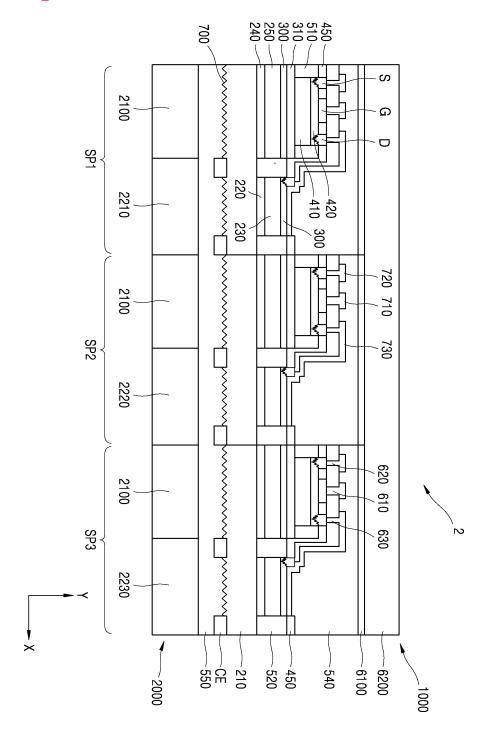

도 8은 일 실시예들에 따른 디스플레이 장치를 나타내는 도면이다.

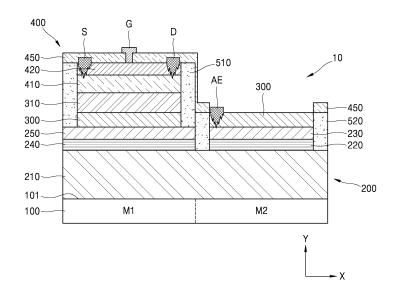

도 9는 다른 실시예에 따른 반도체 장치를 나타내는 도면이다.

도 10은 다른 실시예에 따른 디스플레이 장치를 나타내는 도면이다.

### 발명을 실시하기 위한 구체적인 내용

- [0029] 이하, 첨부된 도면을 참조하여 본 발명의 실시예들에 대해 상세히 설명하기로 한다. 이하의 도면들에서 동일한 참조부호는 동일한 구성요소를 지칭하며, 도면상에서 각 구성요소의 크기는 설명의 명료성과 편의상 과장되어 있을 수 있다. 한편, 이하에 설명되는 실시예는 단지 예시적인 것에 불과하며, 이러한 실시예들로부터 다양한 변형이 가능하다.

- [0030] 이하에서, "상부" 나 "상"이라고 기재된 것은 접촉하여 바로 위에 있는 것뿐만 아니라 비접촉으로 위에 있는 것 도 포함할 수 있다.

- [0031] 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 또한 어떤 부분이 어떤 구성 요소를 "포함"한다고 할 때, 이는 특별히 반대되는 기재가 없는 한 다른 구성요소를 제외하는 것이 아니라 다른 구성요소를 더 포함할 수 있는 것을 의미한다.

- [0032] 또한, 명세서에 기재된 "...부" 등의 용어는 적어도 하나의 기능이나 동작을 처리하는 단위를 의미하며, 이는 하드웨어 또는 소프트웨어로 구현되거나 하드웨어와 소프트웨어의 결합으로 구현될 수 있다.

- [0033] 도 1은 일 실시예에 따른 반도체 장치를 나타내는 도면이다.

- [0034] 도 1을 참조하면, 일 예시에 따른 반도체 장치(10)는 기판(100), 발광 소자(200), 분리층(310), 에칭 방지층 (300), 고전자 이동도 트랜지스터(High Electron Mobility Transistor, 이하 HEMT) 소자(400), 제1 절연 패턴 들(510), 및 제2 절연 패턴들(520)을 포함할 수 있다. 일 예시에 따른 기판(100)은 기판의 상면(101)을 따라 구 별되는 제1 영역(M1) 및 제2 영역(M2)을 포함할 수 있다. 일 예로서, 제1 영역(M1) 및 제2 영역(M2)은 기판 (100)의 연장 방향을 따라 소정의 영역에 인접하게 배치될 수 있다. 또한 일 예로서, 기판(100)은 실리콘 기판, 글라스 기판, 사파이어 기판, SiO2가 코팅된 실리콘 기판일 수 있다.

- [0035] 에칭 방지층(300)은 기판(100)의 상면(101) 보다 구체적으로 제1 영역(M1) 및 제2 영역(M2)의 상부에 배치될 수 있다. 일 예시에 따른 에칭 방지층(300)은 플라즈마 에칭 공정으로부터 후술하게 될 발광 소자(200)의 발광 영역을 보호할 수 있는 보호층일 수 있다. 일 예로서, 에칭 방지층(300)은 AlGaN, AlN 중 적어도 어느 하나를 포함할 수 있고, Mg와 같은 p형 불순물로 도핑될 수 있다. 이때, 에칭 방지층(300)에 포함된 AlGaN, AlN 의 물질은 후술하게 될 에칭 가스로부터 식각공정이 발생되는 것을 방지할 수 있다. 에칭 방지층(300)이 상부 반도체층 (230)의 상부에 배치됨으로써 플라즈마 에칭 공정에 의해 발광소자(200)가 손상을 입어 발광 소자(200)의 발광특성이 저하되는 문제를 방지할 수 있다.

- [0036] 또한, 에칭 방지층(300)은 상술한 바와 같이 Mg와 같은 p형 불순물로 도핑될 수 있으며, 이때 p형 불순물은  $10^{16} \sim 10^{19} ~{\rm cm}^{-3}$ 의 비율로 도핑될 수 있다. 상술한 p형 불순물인 Mg가 포함된 에칭 방지층(300)에 후술하게 될 고 온 열처리가 인가되는 경우, 에칭 방지층(300)에 포함된 p형 도핑 물질인 Mg가 상부 반도체층(230)에 추가적으로 공급됨으로써, p형 도핑 물질을 추가적으로 공급할 수 있다. 이에 따라 p형 불순물로 도핑된 상부 반도체층(230)의 p-GaN 특성이 추가적으로 강화되어 발광 소자(200)의 발광 휘도를 향상시킬 수 있다.

- [0037] 분리층(310)은 기판(100)의 제1 영역(M1)의 상부에 배치될 수 있다. 일 예시에따른 분리층(310)은, 분리층(310) 상에 배치되는 HEMT 소자(400)와 분리층(310) 아래의 층을 전기적으로 분리시킬 수 있다. 분리층(310)은 절연 물질을 포함할 수 있다. 예를 들어, 분리층(310)은 도핑되지 않은 GaN(Undoped GaN) 또는 탄소가 도핑된 GaN(Carbon doped GaN)을 포함할 수 있다.

- [0038] 분리층(310) 상에 HEMT 소자(400)가 제공될 수 있다. HEMT 소자(400)는 채널층(410), 채널 공급층(420), 게이 트 전극(G), 소스 전극(S), 및 드레인 전극(D)을 포함할 수 있다. 일 예시에 따른 채널층(410)은 Ⅲ-V족 계열 의 화합물 반도체를 포함할 수 있다. 예를 들어, 채널층(410)은 GaN를 포함할 수 있다.

- [0039] 채널 공급층(420)은 채널층(410)과 다른 반도체 층일 수 있다. 일 예로서, 채널 공급층(420)은 채널층(410)과 분극 특성, 에너지 밴드갭(bandgap), 및/또는 격자상수가 다를 수 있다. 예를 들어, 채널 공급층(420)은 채널층 (410)보다 분극률 및/또는 에너지 밴드갭이 클 수 있다. 채널 공급층(420)은 A1, Ga, In 및 B 중 적어도 하나를

포함하는 질화물들 중 에서 선택된 하나 이상의 물질을 포함할 수 있다. 예를 들어, 채널 공급층(420)은 AlGaN, AlInN, InGaN, AlN, 및 AlInGaN 중 적어도 하나를 포함할 수 있다. 채널 공급층(420)은 단층 구조 또는 다층 구조를 가질 수 있다.

- [0040] 게이트 전극(G), 소스 전극(S) 및 드레인 전극(D)이 채널 공급층(420)상에 배치될 수 있다. 게이트 전극(G), 소스 전극(S) 및 드레인 전극(D)은 다양한 금속 또는 금속 화합물, 예를 들어 티타늄(Ti), 알루미늄(A1), 니켈(Ni), 금(Au) 중 하나 이상을 포함할 수 있다. 일 예시에 따른 소스 전극(S) 및 드레인 전극(D)은 채널 공급층 (420)과 오믹 접촉(ohmic contact)할 수 있다. 일 예로서, 게이트 전극(G)은 패터닝 공법을 이용하여 채널 공급층(420)상에 배치될 수 있다. 이때, 소스 전극(S) 및 드레인 전극(D)은 스파이크(spike) 공법을 이용하여 채널 공급층(420) 내부에 박히도록 배치될 수도 있다. 스파이크 공법을 이용하여 소스 전극(S) 및 드레인 전극(D)을 채널 공급층(420)에 배치하는 방법은 제조 방법과 관련하여 보다 자세하게 설명한다.

- [0041] 제1 절연 패턴들(510)은 HEMT 소자(400)의 측면을 덮으며, 에칭 방지층(300)까지 연장되도록 배치될 수 있다. 일 예로서, 제1 절연 패턴들(510)은 에칭 방지층(300), 의 바닥면부터 분리층(310) 및 채널층(410)을 거쳐 채널 공급층(420)의 상면까지 제1 방향(Y)을 따라 연장할 수 있다. 일 예시에 따른 제1 절연 패턴들(510)은 채널 공급층(420), 채널층(410), 분리층(310) 및 에칭 방지층(300)에 제1 불순물이 주입되어 형성될 수 있다. 예를 들어, 제1 불순물은 아르곤(Ar) 원소를 포함할 수 있다.

- [0042] 발광 소자(200)는 기판(100)의 제2 영역(M2)의 상부에 배치될 수 있다. 일 예로서, 발광 소자(200)는 마이크로 LED일 수 있다. 예를 들어 발광 소자(200)는 하부 반도체 층(210), 활성층(220), 상부 반도체 층(230)을 포함할 수 있다.

- [0043] 하부 반도체 층(210)은 제1 도전형을 갖는 III-V 화합물 반도체를 포함할 수 있다. 예를 들어, 하부 반도체 층 (210)은 기판(100)의 상부 즉, 제1 영역(M1) 및 제2 영역(M2)에 걸쳐 배치될 수 있다. 일 예로서 하부 반도체층 (210)은 n형 GaN를 포함할 수 있다.

- [0044] 활성층(220)은 하부 반도체 층(210)의 일부 영역, 보다 구체적으로 제2 영역(M2)에 배치될 수 있다. 활성층 (220)은 하부 반도체 층(210)과 후술하게 될 상부 반도체 층(230)으로부터 제공된 전자 및 정공을 수용하여, 광을 생성할 수 있다. 활성층(220)은 단일 양자 우물(Single Quantum Well, SQW), 다중 양자 우물(Multi Quantum Well, MQW), 초격자(Super Lattices, SLs), 또는 이들의 조합을 포함할 수 있다. 예를 들어, 활성층(220)은 In<sub>x</sub>Ga<sub>1-x</sub>N/GaN(0≤x<1)를 포함할 수 있다.

- [0045] 상부 반도체 층(230)은 활성층(220)의 상부 영역, 예를 들어 제2 영역(M2)에 제공될 수 있다. 상부 반도체 층 (230)은 제1 도전형과 다른 제2 도전형을 갖는 III-V 화합물 반도체를 포함할 수 있다. 예를 들어, 상부 반도체 층(230)은 p형 GaN를 포함할 수 있다. 상부 반도체층(230)의 상부에는 상술한 바와 같이 플라즈마 에칭 공정으로부터 발광 영역을 보호할 수 있는 에칭 방지층(300)이 배치될 수 있다.

- [0046] 상부전극(AE)은 에칭 방지층(300)에 배치될 수 있으며, 이때, 상부전극(AE)의 일부는 에칭 방지층(300)을 관통하여 상부 반도체 층(230)에 전기적으로 연결될 수 있다. 일 예로서, 상부전극(AE)은 스파이크(spike) 공법을 이용하여 에칭 방지층(300) 내부에 박히도록 배치될 수도 있다. 스파이크 공법을 이용하여 상부전극(AE)을 에칭 방지층(300)에 배치하는 방법은 제조 방법과 관련하여 보다 자세하게 설명한다. 또한, 예시적인 실시예들에서, 드레인 전극(D)과 상부전극(AE)은 전기적으로 연결될 수 있다. 이 경우, HEMT 소자(400)는 발광 소자(200)를 작동시키는 구동 소자일 수 있다. 상부전극(AE)은 게이트 전극(G), 소스 전극(S), 및 드레인 전극(D)과 실질적으로 동일한 물질을 포함할 수 있다. 예를 들어, 상부전극(AE)은 다양한 금속 또는 금속 화합물, 예를 들어 티타늄(Ti), 알루미늄(A1), 니켈(Ni), 금(Au) 중 하나 이상을 포함할 수 있다.

- [0047] 발광 소자(200)의 측면들 상에 제2 절연 패턴들(520)이 각각 제공될 수 있다. 제2 절연 패턴들(520)은 활성층 (220)의 바닥면부터 상부 반도체 층(230)을 거쳐 에칭 방지층(300)의 상면까지 제1 방향(Y 방향)을 따라 연장할 수 있다. 제2 절연 패턴들(520)은 하부 반도체 층(210) 상에 제공될 수 있다. 즉, 제2 절연 패턴들(520)은 제1 방향(Y 방향)을 따라 하부 반도체 층(210)에 중첩할 수 있으며, 제2 절연 패턴들(520)의 바닥면들은 활성층 (220)의 바닥면과 공면을 이룰 수 있다. 일 예로서, 제2 절연 패턴들(520)은 에칭 방지층(300), 상부 반도체 층 (230) 및 활성층(220)에 제2 불순물이 주입되어 형성될 수 있다. 제2 불순물은 제1 불순물과 실질적으로 동일할수 있다. 예를 들어, 제2 불순물은 아르곤(Ar) 원소를 포함할 수 있다.

- [0048] 분리층(310)과 하부 반도체 층(210) 사이에 상부 스페이서 층(250)이 제공될 수 있다. 상부 스페이서 층(250)은 상부 반도체 층(230)과 제2 방향(X 방향)을 따라 중첩할 수 있다. 상부 스페이서 층(250)은 상부 반도체 층

(230)과 실질적으로 동일한 두께를 가질 수 있다. 상부 스페이서 층(250)은 상부 반도체 층(230)과 실질적으로 동일한 물질을 포함할 수 있다. 예를 들어, 상부 스페이서 층(250)은 p형 GaN를 포함할 수 있다.

- [0049] 상부 스페이서 층(250)과 하부 반도체 층(210) 사이에 하부 스페이서 층(240)이 제공될 수 있다. 하부 스페이서 층(240)은 활성층(220)과 제2 방향(X 방향)을 따라 중첩할 수 있다. 하부 스페이서 층(240)은 활성층(220)과 실질적으로 동일한 두께를 가질 수 있다. 하부 스페이서 층(240)은 활성층(220)과 실질적으로 동일한 물질을 포함할 수 있다. 하부 스페이서 층(240)은 단일 양자 우물, 다중 양자 우물, 초격자, 또는 이들의 조합을 포함할 수 있다. 예를 들어, 하부 스페이서 층(240)은 In<sub>x</sub>Ga<sub>1-x</sub>N/GaN(0≤x<1)를 포함할 수 있다.

- [0050] HEMT 소자(400), 제1 절연 패턴들(510), 및 제2 절연 패턴들(520) 상에 패시베이션 층(450)이 제공될 수 있다. 일 예시에 따른 패시베이션 층(450)은 절연 물질을 포함할 수 있다. 예를 들어, 패시베이션 층(450)은 실리콘 산화물 또는 실리콘 질화물을 포함할 수 있다. 패시베이션 층(450)은 단층 구조 또는 다층 구조를 가질 수 있다.

- [0051] 상술한 바와 같이 본 개시의 일 실시예에 따르면 서로 다른 HEMT 소자(400)와 발광 소자(200)가 하나의 기판 (100) 상에 모놀리식(monolithic)하게 집적된 반도체 장치(10)를 제공할 수 있다. 이하에서는 본 개시의 일 실시예에 따른 반도체 장치(10)의 제조 방법에 대해 서술한다.

- [0052] 도 2 내지 도 10은 도 1을 참조하여 설명된 반도체 장치의 제조 방법을 각 단계별로 설명하기 위한 도면이다.

- [0053] 도 2를 참조하면, 평판 형상의 기판(100)이 준비될 수 있다. 기판(100)은 제1 영역(M1) 및 제2 영역(M2)을 포함할 수 있다. 일 예시에 따른 제1 영역(M1) 및 제2 영역(M2)은 기판(100)의 상면(101)을 따라 소정의 구역으로 구획될 수 있다. 예를 들어 제1 영역(M1) 및 제2 영역(M2)은 제2 방향(X 방향)을 따라 구별될 수도 있다.

- [0054] 기판(100) 상에 차례로 하부 반도체 층(210), 활성층(220), 상부 반도체 층(230), 에칭 방지층(300), 분리층 (310), 채널층(410) 및 채널 공급층(420)이 적층될 수 있다. 예를 들어, 하부 반도체 층(210), 활성층(220), 상부 반도체 층(230), 분리층(310), 에칭 방지층(300), 채널층(410) 및 채널 공급층(420)은 에피택시얼 성장 (Epitaxial Growth) 공정에 의해 형성될 수 있다. 하부 반도체 층(210), 활성층(220), 상부 반도체 층(230), 분리층(310), 에칭 방지층(300), 채널층(410) 및 채널 공급층(420)은 기판(100)의 상면(101)에 수직한 제1 방향 (Y 방향)을 따라 제1 영역(M1) 및 제2 영역(M2)과 중첩할 수 있다.

- [0055] 하부 반도체 층(210)은 제1 도전형을 갖는 III-V 화합물 반도체를 포함할 수 있다. 예를 들어, 하부 반도체 층 (210)은 n형 GaN를 포함할 수 있다.

- [0056] 활성층(220)은 단일 양자 우물, 다중 양자 우물, 초격자, 또는 이들의 조합을 포함할 수 있다. 예를 들어, 활성 층(220)은 In<sub>x</sub>Ga<sub>1-x</sub>N/GaN(0≤x<1)를 포함할 수 있다.

- [0057] 상부 반도체 층(230)은 제1 도전형과 다른 제2 도전형을 갖는 III-V 화합물 반도체를 포함할 수 있다. 예를 들어, 상부 반도체 층(230)은 p형 GaN를 포함할 수 있다.

- [0058] 에칭 방지층(300)은 플라즈마 에칭 공정으로부터 후술하게 될 발광 소자(200)의 발광 영역을 보호할 수 있는 보호층일 수 있다. 일 예로서, 에칭 방지층(300)은 AlGaN, AlN 중 적어도 어느 하나를 포함할 수 있고, Mg와 같은 p형 불순물로 도핑될 수 있다. 이때, 에칭 방지층(300)에 포함된 AlGaN, AlN 의 물질은 후술하게 될 에칭 가스로부터 식각공정이 발생되는 것을 방지할 수 있다. 이때 p형 불순물은  $10^{16} \sim 10^{19}$  cm<sup>-3</sup>의 비율로 도핑될 수 있다. 상술한 p형 불순물인 Mg가 포함된 에칭 방지층(300)에 후술하게 될 고온 열처리가 인가되는 경우, 에칭 방지층(300)에 포함된 p형 도핑 물질인 Mg가 상부 반도체층(230)에 추가적으로 공급됨으로써, p형 도핑 물질을 추가적으로 공급할 수 있다. 이에 따라 p형 불순물로 도핑된 상부 반도체층(230)의 p-GaN 특성이 추가적으로 강화되어 발광 소자(200)의 발광 휘도를 향상시킬 수 있다.

- [0059] 분리층(310)은 절연 물질을 포함할 수 있다. 예를 들어, 분리층(310)은 도핑되지 않은 GaN(Undoped GaN) 또는 탄소가 도핑된 GaN(Carbon doped GaN)을 포함할 수 있다.

- [0060] 채널층(410)은 Ⅲ-V족 계열의 화합물 반도체를 포함할 수 있다. 예를 들어, 채널층(410)은 GaN를 포함할 수 있다.

- [0061] 채널 공급층(420)은 Al, Ga, In 및 B 중 적어도 하나를 포함하는 질화물들 중 에서 선택된 하나 이상의 물질을 포함할 수 있다. 예를 들어, 채널 공급층(420)은 AlGaN, AlInN, InGaN, AlN, 및 AlInGaN 중 적어도 하나를 포

함할 수 있다.

- [0062] 도 3을 참조하면, 일 실시예에 따른 채널 공급층(420), 채널층(410), 및 분리층(310)이 패터닝될 수 있다. 일예로서, 채널 공급층(420), 채널층(410), 및 분리층(310)의 일부 영역, 즉 제2 영역(M2)에 배치되는 채널 공급층(420), 채널층(410), 및 분리층(310)이 제1 방향(Y 방향)을 따라 제거될 수 있다. 예를 들어, 상기 일 부분들에 선택적 식각 공정이 이용될 수 있다. 이때, 선택적 식각 공정은 에칭 방지층(300)까지 진행될 수 있으며, 이에 따라 채널 공급층(420), 채널층(410), 및 분리층(310)이 제거될 수 있다. 예를 들어, 상기 선택적 식각 공정은 선택적 유도 결합 플라즈마 에칭(Selective Inductive Coupled Plasma Etching) 공정을 포함할 수 있다. 일예로서, 선택적 유도 결합 플라즈마 에칭 공정에는 Cl<sub>2</sub>, BCl<sub>3</sub>, CHF<sub>3</sub>, CF<sub>4</sub> 또는 SF<sub>6</sub> 계열의 가스가 사용될 수 있다. 이때, 에칭 방지층(300)에는 AlGaN, AlN 의 물질이 포함되어 에칭 가스로부터 식각공정이 발생되는 것을 방지할 수 있다. 에칭 방지층(300)이 상부 반도체층(230)의 상부에 배치됨으로써 플라즈마 에칭 공정에 의해 발광소자(200)가 손상을 입어 발광 소자(200)의 발광 특성이 저하되는 문제를 방지할 수 있다.

- [0063] 다만, 플라즈마 에칭 공정에서 수소 가스(H₂)가 존재하거나 포토레지스트 마스크 등에서 수소 가스(H₂)가 공급되어 상부 반도체층(230)의 GaN 내부에 침투할 수 있다. 이 경우, Mg와 같은 p형 불순물로 도핑된 p-GaN층에서 GaN 내부에 침투한 수소 가스(H₂)가 Mg와 결합할 수 있으며 이에 따라 Mg이 도펀트로서 기능을 수행하지 못할수 있다. 이와 같은 문제점을 방지하기 위해 별도의 탈수소화 공정이 필요할 수 있다.

- [0064] 도 4를 참조하면, 일 실시예에 따라 소정의 온도에서 열처리 공정이 수행될 수 있다. 일 예로서, 도 3에 개시된 플라즈마 에칭 공정이 수행된 복수 개의 기판층을 질소(№) 분위기 하에서 소정의 고온, 예를 들어 700°C 이상 1000°C 이하의 온도에서 3분 이하의 시간 동안 열처리 공정을 수행할 수 있다. 일 예로서, 상술한 열처리 공정을 수행하는 경우, 상부 반도체층(230)의 GaN 내부에 침투한 수소 가스(№)가 상부 반도체층(230)으로부터 방출되어 질소 가스(№)와 결합하여 제거될 수 있다. 이에 따라 p형 불순물로 도핑된 상부 반도체층(230)의 p-GaN 특성이 회복될 수 있다.

- [0065] 또한, Mg와 같은 p형 불순물이 고농도로 도핑된 에칭 방지층(300)에 고온 열처리가 인가되는 경우, 에칭 방지층 (300)에 포함된 p형 도핑 물질인 Mg가 상부 반도체층(230)에 추가적으로 공급됨으로써, p형 도핑 물질을 추가적으로 공급할 수 있다. 이에 따라 p형 불순물로 도핑된 상부 반도체층(230)의 p-GaN 특성이 추가적으로 강화되어 발광 소자(200)의 발광 휘도를 향상시킬 수 있다.

- [0066] 도 5를 참조하면, 일 실시예에 따라 채널 공급층(420) 채널층(410), 분리층(310) 및 에칭 방지층(300)의 제1 영역(M1)의 경계에 인접한 영역들에 제1 불순물이 주입되어, 제1 절연 패턴들(510)을 형성할 수 있다. 예를 들어, 제1 불순물을 주입하는 공정은 이온 주입(Ion Implantation) 공정을 포함할 수 있다. 제1 불순물을 주입하는 공정은 에칭 방지층(300)의 바닥면까지 수행될 수 있다. 즉, 제1 불순물은 채널 공급층(420)의 상면부터 에칭 방지층(300)의 바닥면까지 주입될 수 있다. 예를 들어, 제1 불순물은 아르곤(Ar) 원소를 포함할 수 있다.

- [0067] 일 실시예에 따른 제2 영역(M2) 상의 에칭 방지층(300), 상부 반도체 층(230) 및 활성층(220)에 제2 불순물이 주입되어, 제2 절연 패턴들(520)을 형성할 수 있다. 제2 불순물은 에칭 방지층(300), 상부 반도체 층(230) 및 활성층(220)의 제2 영역(M2)의 경계에 인접한 영역들에 주입될 수 있다. 예를 들어, 제2 불순물을 주입하는 공정은 이온 주입 공정을 포함할 수 있다. 제2 불순물을 주입하는 공정은 활성층(220)의 바닥면까지 수행될 수 있다. 즉, 제2 불순물은 에칭 방지층(300)의 상면부터 활성층(220)의 바닥면까지 주입될 수 있다. 예를 들어, 제2 불순물은 아르곤(Ar) 원소를 포함할 수 있다. 일 예에서, 제1 불순물을 주입하는 공정 및 제2 불순물을 주입하는 공정은 동시에 수행될 수 있다. 제1 영역(M1) 상의 상부 반도체 층(230)과 활성층(220)은 각각 상부 스페이서 층(250) 및 하부 스페이서 층(240)으로 지칭될 수 있다.

- [0068] 도 6을 참조하면, 일 실시예에 따라 스파이크 공정을 이용하여 채널 공급층(420)의 상부 영역에 소스 전극(S), 드레인 전극(D)이 형성되고, 에칭 방지층(300)의 상부 영역에 상부 전극(AE)이 형성될 수 있다. 일 예로서, 마스크를 이용하여 채널 공급층(420)의 상부 영역 중 특정 영역 및 에칭 방지층(300)의 상부 영역 중 특정 영역에 중착 물질, 예를 들어 다양한 금속 또는 금속 화합물, 예를 들어 티타늄(Ti), 알루미늄(AI), 니켈(Ni), 금(Au) 중 하나 이상을 중착시킬 수 있다. 채널 공급층(420) 및 에칭 방지층(300)에 중착된 물질에 소정의 온도, 예를 들어  $400^{\circ}$ C 이상의 고온에서 3분 이하의 어닐링 공정을 수행하는 경우, 중착 물질 중 일부가 채널 공급층(420) 및 에칭 방지층(300)에 삽입되도록 배치될 수 있다. 이때, 상부 전극(AE)은 에칭 방지층(300)을 관통하여 상부

반도체층(230)에 접촉될 수 있다. 이와 같은 스파이크 공정을 이용하여 에칭 방지층(300)이 최상단에 배치된 경우에도 상부 전극(AE)과 상부 반도체층(230)이 전기적으로 연결될 수 있다. 또한, 단일 공정을 이용하여 소스전극(S), 드레인 전극(D) 및 상부 전극(AE)을 형성하여 공정을 보다 단순화시킬 수 있다. 다만, 본 개시가 이에 제한되는 것은 아니며, 소스 전극(S) 및 드레인 전극(D)은 별도의 패터닝 공정을 이용하여 채널 공급층(420)상에 배치될 수도 있다.

- [0069] 도 7을 참조하면, 채널 공급층(420), 소스 전극(S), 드레인 전극(D), 상부 반도체 층(230), 제1 절연 패턴들 (510), 상부전극(AE) 및 제2 절연 패턴들(520) 상에 패시베이션 층(450)이 형성될 수 있다. 예를 들어, 패시베이션 층(450)은 화학 기상 증착(Chemical Vapor Deposition, 이하 CVD) 공정, 물리 기상 증착(Physical Vapor Deposition, 이하 PVD) 공정, 또는 원자 층 증착(Atom Layer Deposition, 이하 ALD) 공정에 의해 형성될 수 있다. 패시베이션 층(450)은 채널 공급층(420), 소스 전극(S), 드레인 전극(D), 상부 반도체 층(230), 제1 절연 패턴들(510), 상부전극(AE) 및 제2 절연 패턴들(520)의 표면들을 따라 연장할 수 있다.

- [0070] 게이트 전극(G)은 패시베이션층(450) 상에 형성될 수 있다. 일 실시예에 따른 게이트 전극(G)은 패시베이션 층 (450)을 패터닝하여 채널 공급층(420)을 노출하는 개구들을 형성한 후, 패시베이션 층(450) 상에 상기 개구들을 채우는 다양한 금속 또는 금속 화합물, 예를 들어 티타늄(Ti), 알루미늄(Al), 니켈(Ni), 금(Au) 중 하나 이상을 포함하는 전도성 막을 형성한 후, 상기 전도성 물질 막을 패터닝하여 개구들 사이의 패시베이션 층(450)을 노출하는 것을 포함할 수 있다.

- [0071] 일 실시예에 따른 제2 영역(M2) 상에 형성된 하부 반도체 층(210), 활성층(220), 상부 반도체 층(230), 및 상부 전극(AE)은 발광 소자(도 1의 200)로 구성할 수 있다. 제1 영역(M1) 상의 채널층(410), 채널 공급층(420), 게이 트 전극(G), 소스 전극(S), 및 드레인 전극(D)은 HEMT 소자(도 1의 400)를 구성할 수 있다.

- [0072] 본 개시의 일 실시예는 발광 소자(도 1의 200)와 HEMT 소자(도 1의 400)를 하나의 기판(100) 상에 모놀리식하게 형성하는 반도체 장치의 제조 방법을 제공할 수 있다.

- [0073] 도 8은 일 실시예들에 따른 디스플레이 장치를 나타내는 도면이다. 설명의 간결함을 위해, 도 1을 참조하여 설명된 것들과 실질적으로 동일한 내용들은 설명되지 않을 수 있다.

- [0074] 도 8을 참조하면, 복합 충(1000) 및 광 제어 충(2000)을 포함하는 디스플레이 장치(1)가 제공될 수 있다. 디스플레이 장치(1)는 복수의 픽셀들을 포함할 수 있다. 다만, 설명의 편의를 위해 하나의 픽셀이 도시되었다. 픽셀은 서로 다른 색들을 갖는 광들을 각각 방출하는 제1 서브 픽셀(SP1), 제2 서브 픽셀(SP2), 및 제3 서브 픽셀(SP3)을 포함할 수 있다. 예를 들어, 제1 내지 제3 서브 픽셀들(SP1, SP2, SP3)은 각각 적색 광, 녹색 광, 및 청색 광을 방출할 수 있다.

- [0075] 복합 층(1000)은 기판(100), 발광 소자들(200), 하부 스페이서 층들(240), 상부 스페이서 층들(250), 예칭 방지 충들(300), 분리층들(310), HEMT 소자들(400), 제1 절연 패턴들(510), 제2 절연 패턴들(520), 하부 절연층 (530), 상부 절연층(540), 제1 내지 제4 콘택들(610, 620, 630, 640) 및 제1 내지 제3 배선들(710, 720, 730) 을 포함할 수 있다. 기판(100), 발광 소자들(200), 하부 스페이서 층들(240), 상부 스페이서 층들(250), 예칭 방지층들(300), 분리층들(310), HEMT 소자들(400), 제1 절연 패턴들(510), 및 제2 절연 패턴들(520)은 도 1을 참조하여 설명된 것들과 실질적으로 동일할 수 있다. 다만, 기판(100) 및 하부 반도체 층(210)은 제1 내지 제3 서브 픽셀들(SP1, SP2, SP3)을 가로지르도록 연장될 수 있다.

- [0076] 하부 절연충(530)은 패시베이션 충(450) 상에 제공될 수 있다. 하부 절연충(530)은 패시베이션 충(450)의 표면을 따라 연장될 수 있다. 하부 절연충(530)은 발광 소자(200) 상에서 에칭 방지충(300)의 상면을 덮을 수 있다. 예를 들어, 하부 절연충(530)은 에칭 방지충(300)의 상면에 직접 접할 수 있다. 예를 들어, 하부 절연충(530)은 실리콘 산화물 또는 실리콘 질화물을 포함할 수 있다.

- [0077] 게이트 전극(G) 상에 제1 콘택(610) 및 제1 배선(710)이 제공될 수 있다. 제1 배선(710)은 제1 콘택(610)에 의해 게이트 전극(G)과 전기적으로 연결될 수 있다. 제1 배선(710)은 게이트 전극(G)에 인가되는 전압을 전송할수 있다. 예를 들어, HEMT 소자(400)가 발광 소자(200)를 작동시키는 구동 소자인 경우, 제1 배선(710)은 스위청 소자(미도시)의 드레인 전극에 전기적으로 연결될 수 있다. 제1 콘택(610) 및 제1 배선(710)은 전도성 물질을 포함할 수 있다. 예를 들어, 제1 콘택(610) 및 제1 배선(710)은 금속을 포함할 수 있다.

- [0078] 소스 전극(S) 상에 제2 콘택(620) 및 제2 배선(720)이 제공될 수 있다. 제2 배선(720)은 제2 콘택(620)에 의해 소스 전극(S)과 전기적으로 연결될 수 있다. 제2 배선(720)은 소스 전극(S)에 인가되는 전압을 전송할 수 있다. 예를 들어, HEMT 소자(400)가 발광 소자(200)를 작동시키는 구동 소자인 경우, 제2 배선(720)은 전원 라인(미도

시)에 전기적으로 연결될 수 있다. 제2 콘택(620) 및 제2 배선(720)은 전도성 물질을 포함할 수 있다. 예를 들어, 제2 콘택(620) 및 제2 배선(720)은 금속을 포함할 수 있다.

- [0079] 드레인 전극(D) 및 상부전극(AE) 상에 각각 제3 콘택(630) 및 제4 콘택(640)이 제공될 수 있다. 제3 배선(730)은 하부 절연층(530)의 상면을 따라 제3 콘택(630) 상에서 제4 콘택(640) 상으로 연장될 수 있다. 드레인 전극(D)은 제3 콘택(630)에 의해 제3 배선(730)에 전기적으로 연결될 수 있다. 상부전극(AE)은 제4 콘택(640)에 의해 제3 배선(730)에 전기적으로 연결될 수 있다. 이에 따라, 드레인 전극(D)과 상부전극(AE)은 서로 전기적으로 연결될 수 있다. 예를 들어, 발광 소자(200)는 제3 배선(730)에 의해 상부전극(AE)에 전압이 인가될 때 광을 방출할 수 있다.

- [0080] 하부 절연충(530), 제1 내지 제4 콘택들(610, 620, 630, 640), 및 제1 내지 제3 배선들(710, 720, 730) 상에 상부 절연충(540)이 제공될 수 있다. 상부 절연충(540)의 상면은 평평할 수 있다. 예를 들어, 상부 절연충(540)은 이)의 상면은 기판(100)의 상면(101)과 평행하도록 형성된 평탄화충일 수 있다. 예를 들어, 하부 절연충(540)은 실리콘 산화물 또는 실리콘 질화물을 포함할 수 있다.

- [0081] 광 제어 층(2000)은 상부 절연층(540) 상에 제공될 수 있다. 광 제어 층(2000)은 블랙 매트릭스(black matri x)들(2100) 및 상기 블랙 매트릭스들(2100) 사이에 각각 배치된 제1 내지 제3 광 제어 패턴들(2210, 2220, 2230)을 포함할 수 있다. 제1 내지 제3 광 제어 패턴들(2210, 2220, 2230)은 제1 내지 제3 서브 픽셀들(SP1, SP2, SP3) 내에 각각 제공될 수 있다. 제1 내지 제3 광 제어 패턴들(2210, 2220, 2230)은 발광 소자들(200)에 각각 대응될 수 있다.

- [0082] 제1 광 제어 패턴(2210)은 제1 서브 픽셀(SP1) 내의 발광 소자(200)에서 방출된 광을 수용하여 적색 광을 방출할 수 있다. 상기 발광 소자(200)이 청색 광을 방출하는 경우, 제1 광 제어 패턴(2210)은 상기 청색 광에 의해여기되어 적색 광을 방출하는 양자점들(Quantum Dots, 이하 QD) 또는 형광체(phosphor)을 포함할 수 있다. 양자점은 코어부와 껍질부를 갖는 코어-쉘(core-shell) 구조를 가질 수 있으며, 또한 쉘(shell)이 없는 입자 구조를 가질 수도 있다. 코어-쉘(core-shell) 구조는 싱글-쉘(single-shell) 또는 멀티-쉘(multi-shell)을 가질 수 있다. 예를 들어, 멀티-쉘(multi-shell)은 더블-쉘(double-shell)일 수 있다. 예시적인 실시예들에서, 양자점은 II-VI 화합물 반도체, III-V 화합물 반도체, IV-VI 화합물 반도체, IV족 계열 반도체, 및 그래핀 양자점 중 적어도 하나를 포함할 수 있다. 예를 들어, 양자점의 지름은 약 10 nm 이하일 수 있다. 제1 광 제어 패턴(2210)은 포토레지스트(photoresist) 및 광 산란제를 더 포함할 수 있다.

- [0083] 제2 광 제어 패턴(2220)은 제2 서브 픽셀(SP2) 내의 발광 소자(200)에서 방출된 광을 수용하여 녹색 광을 방출할 수 있다. 상기 발광 소자(200)이 청색 광을 방출하는 경우, 제2 광 제어 패턴(2220)은 상기 청색 광에 의해여기되어 녹색 광을 방출하는 양자점들(QD) 또는 형광체를 포함할 수 있다. 제2 광 제어 패턴(2220)은 포토레지스트 및 광 산란제를 더 포함할 수 있다.

- [0084] 제3 광 제어 패턴(2230)은 제3 서브 픽셀(SP3) 내의 발광 소자(200)에서 방출된 광을 수용하여 동일한 색의 광을 방출할 수 있다. 상기 발광 소자(200)에서 청색 광이 방출된 경우, 제3 광 제어 패턴(2230)은 상기 발광 소자(200)에서 방출된 광을 수용하여 청색 광을 방출할 수 있다. 제3 광 제어 패턴(2230)은 포토레지스트 및 광산란제를 포함할 수 있다.

- [0085] 블랙 매트릭스들(2100)의 각각은 서로 바로 인접한 한 쌍의 서브 픽셀들(예를 들어, 제1 및 제2 서브 픽셀들 (SP1, SP2) 및 제2 및 제3 서브 픽셀들(SP2, SP3)에 걸쳐 제공될 수 있다. 블랙 매트릭스들(2100)은 HEMT 소자 들(400)에 각각 대응될 수 있다. 블랙 매트릭스들(2100)은 제1 내지 제3 서브 픽셀들(SP1, SP2, SP3) 사이에서 크로스토크(crosstalk)가 발생하는 것을 방지하도록 광을 흡수할 수 있다.

- [0086] 본 개시는 서로 다른 HEMT 소자(400)와 발광 소자(200)가 하나의 기판(100) 상에 모놀리식(monolithic)하게 집 적된 반도체 장치를 포함하는 디스플레이 장치(1)를 제공할 수 있다.

- [0087] 도 9는 다른 실시예에 따른 반도체 장치를 나타내는 도면이다. 설명의 간결함을 위해, 도 1을 참조하여 설명된 것 및 도 8을 참조하여 설명된 것과 실질적으로 동일한 내용은 설명되지 않을 수 있다.

- [0088] 도 9를 참조하면, 다른 실시예에 따른 반도체 장치(11)는 발광 소자(200), 에칭 방지층(300), 분리층(310), HEMT 소자(400), 제1 절연 패턴들(510), 제2 절연 패턴들(520), 하부 절연층(530), 제1 내지 제3 콘택들(610, 620, 630), 제1 내지 제3 배선들(710, 720, 730), 상부 절연층(540), 접합층(6100), 후속 기판(6200), 및 하부

전극(CE)을 포함하는 가 제공될 수 있다.

- [0089] 발광 소자(200), 에칭 방지층(300), 분리층(310), HEMT 소자(400), 제1 절연 패턴들(510), 및 제2 절연 패턴들 (520)은 도 1을 참조하여 설명된 것과 실질적으로 동일할 수 있다.

- [0090] 도 1을 참조하여 설명된 기판(도 1의 100)은 후속 기판(620)까지 형성 후 제거될 수 있다. 하부 반도체 층(21 0)은 제3 영역(M3) 및 제4 영역(M4)을 포함할 수 있다. 제3 영역(M3)은 기판(도 1의 100)의 제1 영역(도 1의 M1) 상에 제공될 수 있다. 제4 영역(M4)은 기판(도 1의 100)의 제2 영역(도 1의 M2) 상에 제공될 수 있다.

- [0091] 하부 절연층(530), 제1 내지 제3 콘택들(610, 620, 630), 제1 내지 제3 배선들(710, 720, 730), 및 상부 절연 충(540)은 도 8을 참조하여 설명된 것과 실질적으로 동일할 수 있다. 다만, 제3 배선(730)은 상부전극(AE)을 넘어 에칭 방지층(300) 상으로 연장할 수 있다. 제3 배선(730)은 에칭 방지층(300)의 상면을 덮을 수 있다. 제3 배선(730)은 광을 반사할 수 있다. 예를 들어, 제3 배선(730)은 활성층(220)으로부터 방출된 광 중, 상부 반도체 층(230) 및 에칭 방지층(300)을 지나는 일부를 하부 반도체 층(210)으로 반사할 수 있다.

- [0092] 상부 절연층(540) 상에 후속 기판(6200)이 제공될 수 있다. 후속 기판(6200)은 도 1을 참조하여 설명된 기판 (100)과 실질적으로 동일할 수 있다. 예를 들어, 후속 기판(6200)은 실리콘 기판, 글라스 기판, 사파이어 기판, SiO<sub>2</sub>가 코팅된 실리콘 기판일 수 있다. 다만, 기판(100)은 상기 예시된 것들로 한정되지 않는다.

- [0093] 접합층(6100)은 상부 절연층(540)과 후속 기판(6200)을 접합시킬 수 있다. 예를 들어, 접합층(6100)은 실리콘 계열 접합 물질을 포함할 수 있다. 식각을 통해 두께가 줄어든 하부 반도체 층(210) 아래에 하부 전극들(CE)이 제공될 수 있다. 하부 전극(CE)은 제4 영역(M4) 아래에 제공될 수 있다. 하부 전극들(CE)은 하부 반도체 층(210)에 전기적으로 연결될 수 있다. 하부 전극들(CE)은 하부 반도체 층(210)에 접지 전압을 인가할 수 있다. 하부 전극들(CE)은 제2 절연 패턴들(520)과 각각 제1 방향(Y 방향)을 따라 중첩하도록 배치될 수 있다.

- [0094] 일 예로서, 하부 반도체 층(210)의 바닥면은 요철 구조를 가질 수 있다. 상기 요철 구조는 광 추출 패턴들(70 0)로 지칭될 수 있다. 즉, 광 추출 패턴들(700)은 하부 반도체 층(210)의 하부에 제공될 수 있다. 광 추출 패턴들(700)은 하부 반도체 층(210)의 하부가 패터닝되어 형성된 것일 수 있다. 광 추출 패턴들(700)은 발광 소자 (200)으로부터 방출된 광이 반도체 장치(11) 외부로 방출되는 효율을 높일 수 있다. 다른 예에서, 광 추출 패턴들(700)은 하부 반도체 층(210)과 다른 구조체일 수 있다. 이 경우, 광 추출 패턴들(700)과 하부 반도체 층 (210) 사이에 경계면이 제공될 수 있다.

- [0095] 상부전극(AE)과 하부 전극(CE)에 각각 구동 전압과 접지 전압이 인가된 때, 활성층(220)으로부터 광이 방출될 수 있다. 상기 광의 일부는 제3 배선(730)에 의해 반사된 후 하부 반도체 층(210)의 바닥면을 통해 방출되고, 상기 광의 다른 일부는 방출 후 바로 하부 반도체 층(210)의 바닥면을 통해 방출될 수 있다.

- [0096] 본 개시는 서로 다른 HEMT 소자(400)와 발광 소자(200)가 하나의 기판(100) 상에 모놀리식(monolithic)하게 집 적된 반도체 장치(11)를 제공할 수 있다.

- [0097] 도 10은 다른 실시예에 따른 디스플레이 장치를 나타내는 도면이다. 설명의 간결함을 위해, 도 8을 참조하여 설명된 것 및 도 9을 참조하여 설명된 것과 실질적으로 동일한 내용들은 설명되지 않을 수 있다.

- [0098] 도 10을 참조하면, 복합 층(1000) 및 광 제어 층(2000)을 포함하는 디스플레이 장치(2)가 제공될 수 있다.

- [0099] 복합 층(1000)은 발광 소자(200), 분리층(310), HEMT 소자(400), 제1 절연 패턴들(510), 제2 절연 패턴들 (520), 하부 절연층(530), 제1 내지 제4 콘택들(610, 620, 630, 640), 제1 내지 제3 배선들(710, 720, 730), 상부 절연층(540), 접합층(610), 후속 기판(620), 하부 전극(CE), 광 추출 패턴들(700), 및 층간 절연층(550)을 포함할 수 있다. 발광 소자(200), 분리층(310), HEMT 소자(400), 제1 절연 패턴들(510), 제2 절연 패턴들 (520), 하부 절연층(530), 제1 내지 제3 콘택들(610, 620, 630), 제1 내지 제3 배선들(710, 720, 730), 상부 절연층(540), 접합층(6100), 후속 기판(6200), 하부 전극(CE), 및 광 추출 패턴들(700)은 도 9를 참조하여 설명된 것들과 실질적으로 동일할 수 있다.

- [0100] 다만, 하부 반도체 충(210), 접합충(6100), 및 후속 기판(6200)은 제1 내지 제3 서브 픽셀들(SP1, SP2, SP3)을 가로지르도록 연장될 수 있다. 다만 본 개시가 이에 제한되는 것은 아니며, 다른 실시예에서, 도 9에 도시된 것과 같이 광 추출 패턴들(700)이 제공되지 않을 수 있다.

- [0101] 충간 절연충(550)은 하부 반도체 충(210) 아래에 제공될 수 있다. 충간 절연충(550)은 하부 반도체 충(210)의 바닥면을 덮을 수 있다. 하부 전극들(CE)은 하부 반도체 충(210)과 충간 절연충(550) 사이에 제공될 수 있다.

충간 절연충(550)의 바닥면은 평평할 수 있다. 예를 들어, 충간 절연충(550)은 실리콘 산화물 또는 실리콘 질화물을 포함할 수 있다.

[0102] 광 제어 충(2000)은 충간 절연충(550)을 사이에 두고 하부 반도체 충(210)의 반대편에 제공될 수 있다. 광 제어 충(2000)은 충간 절연충(550)의 바닥면을 덮을 수 있다. 광 제어 충(2000)은 도 8을 참조하여 설명된 것과 실질 적으로 동일할 수 있다.

본 발명의 기술적 사상의 실시예들에 대한 이상의 설명은 본 발명의 기술적 사상의 설명을 위한 예시를 제공한다. 따라서 본 발명의 기술적 사상은 이상의 실시예들에 한정되지 않으며, 본 발명의 기술적 사상 내에서 당해기술 분야의 통상의 지식을 가진 자에 의하여 상기 실시예들을 조합하여 실시하는 등 여러 가지 많은 수정 및 변경이 가능함은 명백하다.

#### 도면

[0103]