(19) **日本国特許庁(JP)**

(51) Int. Cl.

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4836304号 (P4836304)

(45) 発行日 平成23年12月14日(2011.12.14)

(24) 登録日 平成23年10月7日(2011.10.7)

HO1L 21/76 (2006.01)

HO1L 21/76

FL

L

請求項の数 18 (全 14 頁)

(21) 出願番号 特願平11-355645

(22) 出願日 平成11年12月15日 (1999.12.15)

(65) 公開番号 特開2001-176959 (P2001-176959A)

(43) 公開日 平成13年6月29日 (2001. 6. 29) 審査請求日 平成18年12月5日 (2006. 12. 5)

|(73)特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

||(74)代理人 100064746

弁理士 深見 久郎

|(74)代理人 100085132

弁理士 森田 俊雄

(74)代理人 100083703

弁理士 仲村 義平

|(74)代理人 100096781

弁理士 堀井 豊

(74)代理人 100109162

弁理士 酒井 將行

|(74)代理人 100111246

弁理士 荒川 伸夫

最終頁に続く

(54) 【発明の名称】半導体装置

# (57)【特許請求の範囲】

# 【請求項1】

半導体基板と、

半導体基板の主表面上に形成されたアクティブデバイス領域と、

上記アクティブデバイス領域の周りにある分離領域と、

上記アクティブデバイス領域に隣接する上記分離領域内に第一ピッチで第一の方向と上記第一の方向と異なる第二の方向に配置され、それぞれが等しい平面形状および平面積を有する複数の第一アクティブダミーパターンと、

上記分離領域内に第二ピッチで配置され、それぞれが等しい平面形状および平面積を有する複数の第二アクティブダミーパターンとを備え、

上記第一のピッチは上記第二のピッチより小さく、上記第一アクティブダミーパターンは上記第二アクティブダミーパターンよりも平面積が小さく、

上記複数の第二アクティブダミーパターンは、上記複数の第一アクティブダミーパターンのうち上記第一方向に配置されたものに隣接するパターンと、上記複数の第一アクティブダミーパターンのうち上記第二方向に配置されたものに隣接するパターンとを含み、

上記複数の第二アクティブダミーパターンの少なくとも一部は、上記第一アクティブダミーパターンを介さずに上記アクティブデバイス領域に隣接していることを特徴とする半導体装置。

## 【請求項2】

請求項1に記載の半導体装置において、

上記分離領域は上記半導体基板の主表面上の溝内の酸化膜で形成されていることを特徴とする半導体装置。

### 【請求項3】

請求項2に記載の半導体装置において、

上記第一及び第二アクティブダミーパターンは上記酸化膜に囲まれていることを特徴と する半導体装置。

#### 【請求項4】

請求項1に記載の半導体装置において、

上記第一アクティブダミーパターンと上記第二アクティブダミーパターンは相似型であることを特徴とする半導体装置。

10

### 【請求項5】

請求項1に記載の半導体装置において、

上記アクティブデバイス領域に隣接する上記第一アクティブダミーパターンと、上記アクティブデバイス領域に隣接する上記第二アクティブダミーパターンとによって、上記アクティブデバイス領域が挟まれていることを特徴とする半導体装置。

#### 【請求項6】

請求項1に記載の半導体装置において、

上記アクティブデバイス領域に隣接している上記第二アクティブダミーパターンは、さらに、上記アクティブデバイス領域に隣接する方向と異なる方向において、上記第一アクティブダミーパターンに隣接していることを特徴とする、半導体装置。

20

## 【請求項7】

請求項1~6に記載の半導体装置において、

上記アクティブデバイス領域はメモリセルを構成していることを特徴とする半導体装置

# 【請求項8】

請求項1~6に記載の半導体装置において、

上記第一および第二アクティブダミーパターンは同一の導電型を有することを特徴とする半導体装置。

#### 【請求項9】

請求項8に記載の半導体装置において、

上記導電型はp型であることを特徴とする半導体装置。

30

# 【請求項10】

半導体基板と、

半導体基板の主表面上に形成されたメモリセル用の微細本番パターンとしての第一アクティブデバイス領域と、

メモリセル以外に用いられ、上記微細本番パターンよりもパターン寸法が大きい第二アクティブデバイス領域と、

上記第一及び第二アクティブデバイス領域の間及び周りにある分離領域と、

上記分離領域内に第一ピッチで第一の方向と上記第一の方向と異なる第二の方向に配置され、それぞれが等しい平面形状を有する複数の第一アクティブダミーパターンと、

40

上記分離領域内に第二ピッチで第三の方向と上記第三の方向と異なる第四の方向に配置され、それぞれが等しい平面形状を有する複数の第二アクティブダミーパターンとを有し

上記第一のピッチは上記第二のピッチより小さく、上記第一アクティブダミーパターンは上記第二アクティブダミーパターンよりも平面積が小さく、

上記複数の第二アクティブダミーパターンの少なくとも一部は、上記第一アクティブダミーパターンを介さずに、上記第一および第二アクティブデバイス領域の少なくともいずれかに隣接しており、

上記複数の第二アクティブダミーパターンは、上記複数の第一アクティブダミーパターンのうち上記第一方向に配置されたものに隣接するパターンと、上記複数の第一アクティ

<u>ブダミーパターンのうち上記第二方向に配置されたものに隣接するパターンとを含む</u>ことを特徴とする半導体装置。

### 【請求項11】

請求項10に記載の半導体装置において、

上記分離領域は上記半導体基板の主表面上の溝内の酸化膜で形成されていることを特徴とする半導体装置。

#### 【請求項12】

請求項11に記載の半導体装置において、

第一及び第二アクティブダミーパターンは上記酸化膜に囲まれていることを特徴とする 半導体装置。

10

# 【請求項13】

請求項10に記載の半導体装置において、

上記複数の第一アクティブダミーパターンの少なくとも一部は、上記第二アクティブダミーパターンを介さずに、上記第一および第二アクティブデバイス領域の少なくともいずれかに隣接していることを特徴とする半導体装置。

#### 【請求項14】

請求項10に記載の半導体装置において、

上記第一の方向は上記第三の方向であり、上記第二の方向は上記第四の方向であり、上記第一アクティブダミーパターンと上記第二アクティブダミーパターンは相似型であることを特徴とする半導体装置。

20

30

### 【請求項15】

請求項10~14に記載の半導体装置において、

上記第一および第二アクティブダミーパターンは同一の導電型を有することを特徴とする半導体装置。

### 【請求項16】

請求項15に記載の半導体装置において、

上記導電型はp型であることを特徴とする半導体装置。

# 【請求項17】

半導体基板と、

半導体基板の主表面上に形成されたアクティブデバイス領域と、

上記アクティブデバイス領域の周りにある分離領域と、

上記アクティブデバイス領域に隣接する上記分離領域内に第一ピッチで第一の方向と上記第一の方向と異なる第二の方向に配置され、それぞれが等しい平面形状および平面積を有する複数の第一アクティブダミーパターンと、

上記分離領域内に第二ピッチで配置され、それぞれが等しい平面形状および平面積を有する複数の第二アクティブダミーパターンとを備え、

上記第一のピッチは上記第二のピッチより小さく、上記第一アクティブダミーパターンは上記第二アクティブダミーパターンよりも平面積が小さく、

上記複数の第二アクティブダミーパターンは、上記複数の第一アクティブダミーパターンのうち上記第一方向に配置されたものに隣接するパターン(ただしウェル境界を介して隣接するものを除く)と、上記複数の第一アクティブダミーパターンのうち上記第二方向に配置されたものに隣接するパターン(ただしウェル境界を介して隣接するものを除く)とを含み、

40

上記複数の第二アクティブダミーパターンの少なくとも一部は、上記第一アクティブダミーパターンを介さずに上記アクティブデバイス領域に隣接していることを特徴とする半導体装置。

### 【請求項18】

半導体基板と、

半導体基板の主表面上に形成されたメモリセル用の微細本番パターンとしての第一アクティブデバイス領域と、

メモリセル以外に用いられ、上記微細本番パターンよりもパターン寸法が大きい第二ア クティブデバイス領域と、

上記第一及び第二アクティブデバイス領域の間及び周りにある分離領域と、

上記分離領域内に第一ピッチで第一の方向と上記第一の方向と異なる第二の方向に配置 され、それぞれが等しい平面形状を有する複数の第一アクティブダミーパターンと、

上記分離領域内に第二ピッチで第三の方向と上記第三の方向と異なる第四の方向に配置 され、それぞれが等しい平面形状を有する複数の第二アクティブダミーパターンとを有し

上記第一のピッチは上記第二のピッチより小さく、上記第一アクティブダミーパターン は上記第二アクティブダミーパターンよりも平面積が小さく、

上記複数の第二アクティブダミーパターンの少なくとも一部は、上記第一アクティブダ ミーパターンを介さずに、上記第一および第二アクティブデバイス領域の少なくともいず れかに隣接しており(ただしウェル境界を介して隣接している場合を除く)、

上記複数の第二アクティブダミーパターンは、上記複数の第一アクティブダミーパター ンのうち上記第一方向に配置されたものに隣接するパターンと、上記複数の第一アクティ ブダミーパターンのうち上記第二方向に配置されたものに隣接するパターンとを含むこと を特徴とする半導体装置。

# 【発明の詳細な説明】

#### [0001]

### 【発明の属する技術分野】

この発明は、半導体装置に関し、特に半導体集積回路装置における分離酸化膜とそれに囲 まれる電気的アクティブ領域のパターンに関するものである。

# [0002]

### 【従来の技術】

近年、半導体集積回路装置では素子の微細化、高集積化に伴い、そのデザインルールはま すます微細になり、プロセスにおいても大変複雑になってきている。特に、素子間分離で は、微細化に適したトレンチ型分離酸化膜が広く用いられるようになり、電気的アクティ ブデバイス領域の性能を損なうことなく、分離酸化膜をトレンチ内に良好に埋め込み、信 頼性良くCMP法による研磨を行うことが非常に重要である。

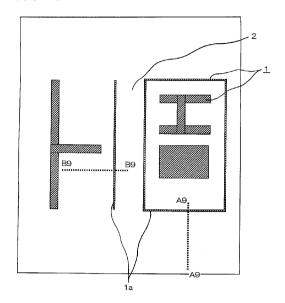

図9は、従来の半導体装置の素子分離形成後の平面図である。図に示すように、素子形成 される電気的アクティブデバイス領域のパターン1(以下、本番パターン1と称す)が分 離領域2に囲まれて配置される。特に、1aは電気的アクティブデバイス領域の微細幅パ ターン(以下、微細本番パターン1aと称す)である。

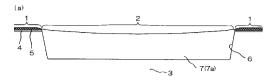

図10は図9に示した従来の半導体装置の素子分離形成後の断面図である。図10(a) は図9のA9-A9線における断面図であり比較的広い分離領域2を示すもの、図10( b)は図9のB9-B9線における断面図であり分離領域2に両側を挟まれた微細本番パ ターン 1 a を示すものである。

#### [0003]

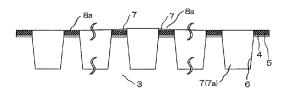

半導体装置における素子分離は、まず半導体基板3上に下敷き酸化膜4、窒化膜5を順次 形成する。その後、分離領域2となる領域の窒化膜5を選択的にエッチング除去した後、 室化膜5マスクを用いて半導体基板3をエッチングすることによりトレンチ6を所定の深 さに形成する。次いで、トレンチ6内を埋め込んで全面に分離酸化膜7を形成した後、C MP法により分離酸化膜7を研磨して窒化膜5上の分離酸化膜7を除去してトレンチ6内 のみに残存させ、トレンチ型分離酸化膜7aを形成する。なお、窒化膜5および下敷き酸 化膜4は、素子分離の後で除去するものである。

#### [0004]

### 【発明が解決しようとする課題】

従来の半導体装置では、CMP法を用いた研磨により窒化膜5上の分離酸化膜7を除去す るが、室化膜5の研磨速度は遅いため、窒化膜5の形成領域の周辺では、窒化膜5の影響 で研磨速度が減少する。逆に、図10(a)に示すような広い分離領域2(トレンチ型分 10

20

30

40

離酸化膜7a)では、研磨速度が速くなり、特に中央部でディッシング(dishing)による膜厚の落ち込みが発生する。このため表面の平坦性が悪くなり、後工程でリソグラフィ技術を用いたパターニングが良好に行えないという問題点があった。

さらに、図10(b)に示すように、広い分離領域2(トレンチ型分離酸化膜7a)に微細本番パターン1aが挟まれている場合、図11に示すように、トレンチ型分離酸化膜7aで研磨速度が速いために、オーバーポリッシュにより微細本番パターン1aの窒化膜5の一部もしくは全部を研磨してしまうこともあった。これにより、トレンチ型分離酸化膜7aの膜厚の落ち込みがさらに大きくなり、例えば、トランジスタ特性における逆ナロー効果によるしきい値の低下や、リーク電流の増大など素子の電気的特性の劣化を招くという問題点があった。

10

20

# [0005]

上記のような問題点を改善するために、従来から、ダミーのアクティブ領域となるダミー パターンを分離領域 2 内に設けて、 C M P 法による研磨速度の均一性の向上を図るものが あった。

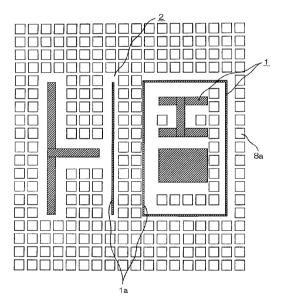

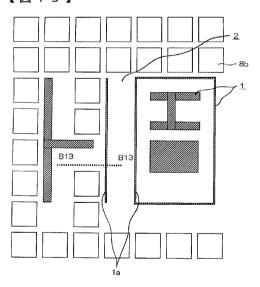

図12および図13は従来の半導体装置の改善例を示す平面図であり、図9で示した半導体装置の分離領域2にダミーパターン8(ダミーのアクティブ領域)を配置したものである。図12では比較的小さなダミーパターン8aを、図13では比較的大きなダミーパターン8bを分離領域2内に敷き詰めるように配置した。

[0006]

CMP法による分離酸化膜7研磨の際、図12で示した場合には、小さなダミーパターン8aが密集した領域で研磨速度が遅くなり、断面図である図14に示すように、アンダーポリッシュによりダミーパターン8aの窒化膜5上に分離酸化膜7が残存することがある。このような場合には、分離酸化膜7だけでなく下層の窒化膜5および下敷き酸化膜4もその後の除去工程で除去されずに残存し、著しく表面平坦性を損ない、後工程でのパターニングが困難になる。

また、図13で示した場合には、ダミーパターン8bが大きいために、本番パターン1の周辺で、配置できない領域がある。特に、微細本番パターン1aの周辺にダミーパターン8bがない場合、B13・B13線における断面図は図10(b)と同様であり、トレンチ型分離酸化膜7aで研磨速度が速いために、オーバーポリッシュにより微細本番パターン1aの窒化膜5の一部もしくは全部を研磨してしまうことがあった(図11参照)。これにより、上述したようにトレンチ型分離酸化膜7aの膜厚の落ち込みがさらに大きくなり素子の電気的特性の劣化を招く。

30

#### [0007]

この発明は、上記のような問題点を解消するために成されたものであって、分離領域にトレンチ型分離酸化膜を形成して素子分離する半導体装置において、分離酸化膜を CMP法を用いて研磨する際、研磨速度の均一性を向上してオーバーポリッシュやアンダーポリッシュを抑制し、表面平坦性の良好な信頼性の高い半導体装置を得ることを目的とする。

[0008]

# 【課題を解決するための手段】

この発明<u>の一の局面に従う</u>半導体装置は、<u>半導体基板と、半導体基板の主表面上に形成されたアクティブデバイス領域と、上記アクティブデバイス領域と</u>、上記アクティブデバイス領域に隣接する上記分離領域内に第一ピッチで第一の方向と上記第一の方向と異なる第二の方向に配置され、それぞれが等しい平面形状および平面積を有する複数の第一アクティブダミーパターンと、上記分離領域内に第二ピッチで配置され、それぞれが等しい平面形状および平面積を有する複数の第二アクティブダミーパターンとを備える。上記第一のピッチは上記第二のピッチより小さく、上記第一アクティブダミーパターンは上記第二アクティブダミーパターンよりも平面積が小さい。上記複数の第二アクティブダミーパターンは、上記複数の第一アクティブダミーパターンのうち上記第一方向に配置されたものに隣接するパターンとを含む。上記複数の第二アクのうち上記第二方向に配置されたものに隣接するパターンとを含む。上記複数の第二アクの

40

<u>ティブダミーパターンの少なくとも一部は、上記第一アクティブダミーパターンを介さず</u>に上記アクティブデバイス領域に隣接している。

### [0009]

またこの発明<u>の他の局面に従う</u>半導体装置は、半導体基板と、半導体基板の主表面上に 形成されたメモリセル用の微細本番パターンとしての第一アクティブデバイス領域と、メ モリセル以外に用いられ、上記微細本番パターンよりもパターン寸法が大きい第ニアクティブデバイス領域と、上記第一及び第ニアクティブデバイス領域の間及び周りにある分離 領域と、上記分離領域内に第一ピッチで第一の方向と上記第一の方向と異なる第二の方向 に配置され、それぞれが等しい平面形状を有する複数の第一アクティブダミーパターンと 、上記分離領域内に第二ピッチで第三の方向と上記第三の方向と異なる第四の方向に配置 され、それぞれが等しい平面形状を有する複数の第二アクティブダミーパターンとを有す る。上記第一のピッチは上記第二のピッチより小さく、上記第一アクティブダミーパター ンは上記第二アクティブダミーパターンよりも平面積が小さい。上記複数の第二アクティ ブダミーパターンの少なくとも一部は、上記第一アクティブダミーパターンを介さずに、 上記第一および第二アクティブデバイス領域の少なくともいずれかに隣接している。上記 複数の第二アクティブダミーパターンは、上記複数の第一アクティブダミーパターンのう ち上記第一方向に配置されたものに隣接するパターンとを含む。

[0013]

# 【発明の実施の形態】

実施の形態1.

以下、この発明の実施の形態1を図によって説明する。

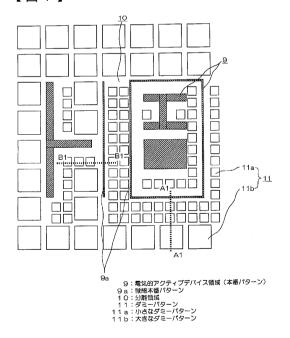

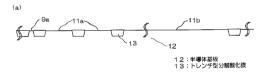

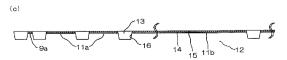

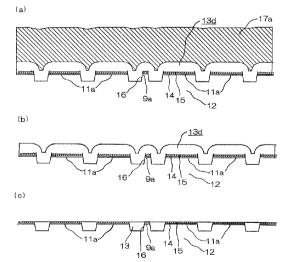

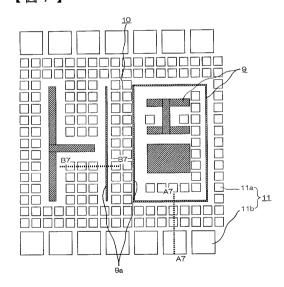

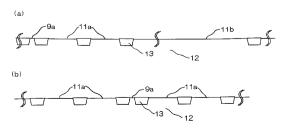

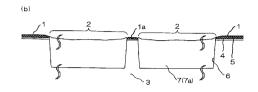

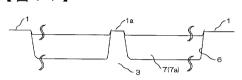

図1はこの発明の実施の形態1による半導体装置の平面図、図2(a)は図1のA1-A1線における断面図、図2(b)は図1のB1-B1線における断面図である。図において、9は素子形成される電気的アクティブデバイス領域のパターン(以下、本番パターン9と称す)で分離領域10に囲まれて配置される。特に、9aは電気的アクティブデバイス領域の微細幅パターン(以下、微細本番パターン9aと称す)である。11は分離領域10内に配置されたダミーのアクティブ領域となるダミーパターンで、11aは比較的小さなダミーパターン、11bは比較的大きなダミーパターンである。また、12は半導体基板、13はトレンチ型分離酸化膜である。

[0014]

図に示すように、本番パターン 9 を囲む分離領域 1 0 内に面積の異なる 2 種のダミーパターン 1 1 ( 1 1 a 、 1 1 b )を配置する。このダミーパターン 1 1 の配置方法は、まず、本番パターン 9 から離れた領域から大きなダミーパターン 1 1 b を敷き詰めるように規則的に配列させて、本番パターン 9 の近くまで配置する。例えば、 1 8  $\mu$  m角のダミーパターン 1 1 b を 2 0  $\mu$  m ピッチでアレイする。

本番パターン 9 の周辺で、大きなダミーパターン 1 1 b が配置できない隙間領域に、小さなダミーパターン 1 1 a を挿入し、規則的に配列させて配置する。例えば、 3  $\mu$  m 角のダミーパターン 1 1 a を 5  $\mu$  m ピッチでアレイする。

### [0015]

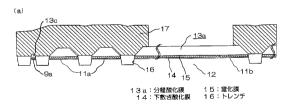

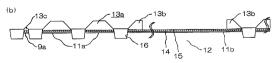

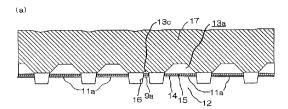

このような半導体装置の素子分離工程を図 3 、図 4 を用いて説明する。図 3 は図 2 ( a ) に対応する部分、図 4 は図 2 ( b ) に対応する部分の工程をそれぞれ示す断面図である。まず、例えば 1 0 ・ c mの比抵抗を有する p 型の単結晶シリコン等からなる半導体基板 1 2 上に下敷き酸化膜 1 4 を、例えば約 1 0 n mの膜厚で形成し、さらに窒化膜 1 5 を約 0 . 1  $\mu$  mの膜厚で形成する。その後、本番パターン 9 とダミーパターン 1 1 とのアクティブ領域 9 、 1 1 を除く領域の窒化膜 1 5 を選択的にエッチング除去した後、窒化膜 1 5 マスクを用いて半導体基板 1 2 を約 0 . 3  $\mu$  mの深さまでエッチングすることによりトレンチ 1 6 を形成する。次いで、トレンチ 1 6 内を埋め込んで全面に H D P (ハイデンシティプラズマ)酸化膜から成る分離酸化膜 1 3 a を、例えば約 0 . 4  $\mu$  mの膜厚で堆積した後、所定のパターン寸法より大きいアクティブ領域 9 、 1 1 の分離酸化膜 1 3 a をエッチ

10

20

30

40

ングするためのレジストパターン 1 7 を分離酸化膜 1 3 a 上に形成する。このレジストパターン 1 7 は、対象となるアクティブ領域 9 、 1 1 より、例えば約 1 . 5 μ m アンダーサイシングして形成する(図 3 ( a )、図 4 ( a ))。

#### [0016]

次に、レジストパターン17をマスクとして分離酸化膜13aを窒化膜15に到達するまでエッチングして開口する。これにより、比較的広いアクティブ領域9、11、即ち、大きなダミーパターン11bおよび比較的広い本番パターン9の領域上の分離酸化膜13aは中央部が開口され端部13bのみが残存する。このときのエッチングは、ドライでもウェットでも良い。なお、微細本番パターン9a上に形成されるHDP酸化膜13cは図に示すように小さな三角形状となり、例えば、DRAM部のメモリセルなどの微細本番パターン9aの密集領域においても、小さな三角形状の多数のHDP酸化膜13cが密集する状態となる(図3(b)、図4(b))。

次に C M P 法により分離酸化膜 1 3 a を研磨して窒化膜 1 5 上の分離酸化膜 1 3 a を除去してトレンチ 1 6 内のみに残存させ、トレンチ型分離酸化膜 1 3 を形成する(図 3 ( c )、図 4 ( c ) )。

次に、窒化膜15、下敷き酸化膜14を順次ウェットエッチングにより除去して、所定の 処理を施して図2(a)、図2(b)で示した素子分離が完成する。

# [0017]

この実施の形態では、本番パターン9から離れた領域から大きなダミーパターン11bを敷き詰めるように規則的に配列させて配置し、本番パターン9の周辺で、大きなダミーパターン11bが配置できない隙間領域に、小さなダミーパターン11aを挿入し、規則的に配列させて配置したため、トレンチ型分離酸化膜13の幅が所定の幅を超えて大きくならない。このため、CMP法による分離酸化膜13aを研磨する際、研磨速度が速くなることが抑えられ、ディッシング(dishing)による膜厚の落ち込みが防止できる。

また、微細本番パターン9aの両側のトレンチ型分離酸化膜13の幅も、小さなダミーパターン11aを挿入することにより狭く抑えられるので、オーバーポリッシュにより微細本番パターン9aの窒化膜15が研磨されるのが防止でき、隣接するトレンチ型分離酸化膜13aの膜厚の落ち込みも防止できて、トランジスタ特性における逆ナロー効果によるしきい値の低下や、リーク電流の増大など素子の電気的特性の劣化を招くことがなくなる。このような微細本番パターン9aの両側のトレンチ型分離酸化膜13の幅は、微細本番パターン9aの1~10倍程度が望ましく、CMP法による研磨速度の均一性が向上して上記のような効果が確実に得られる。

### [0018]

さらに、大きなダミーパターン11 b と小さなダミーパターン11 a とを配置することにより、小さなダミーパターン11 a が密集した領域がなくなり、 C M P 法による研磨速度の均一性が向上するため、アンダーポリッシュにより窒化膜15上に分離酸化膜13 a が残存することが防止できる。大きなダミーパターン11 b および比較的広い本番パターン9の領域上の分離酸化膜13 a は、 C M P 法による研磨工程の前に、予めエッチング(プリエッチング)して中央部を開口しているため、容易に研磨できてアンダーポリッシュによる問題は無い。

また、ダミーパターン 1 1 の配置によりアクティブ領域 9 、 1 1 の分離酸化膜 1 3 a と合わせた全体に対する面積占有率は、5割~8割程度の範囲で、本番パターン 9 の密集した領域と同等程度にできる。これにより、CMP法による研磨速度は、半導体基板 1 2 の面内全体において均一性がさらに向上する。

上述したように、この実施の形態では、素子分離の際の分離酸化膜 1 3 a の C M P 法による研磨の際、研磨速度の均一性が向上するため、表面平坦性が良好で信頼性の高い半導体装置が得られる。

# [0019]

なお、ダミーパターン11の寸法は、小さなダミーパターン11aが本番パターン9の最小寸法の1~100倍程度、大きなダミーパターン11bが本番パターン9の最小寸法の

10

20

30

40

10~1000倍程度の範囲で適宜設定して用い、矩形パターンに限らず、短冊形、かぎ型、あるいはラインandスペース形状でも良いが、、プロセス制御が容易な規則的に配列されたものとする。

また、分離酸化膜 1 3 a のプリエッチングマスクとなるレジストパターン 1 7 はアクティブ領域より約 1 . 5 μ m のアンダーサイシングとしたが、アンダーサイシング量はこれに限るものではなく、プリエッチング後にアクティブ領域の端部に分離酸化膜 1 3 a が残存すればよい。

さらに、分離酸化膜13aのプリエッチングは、窒化膜15表面に到達するまでとしたが、到達する前でプリエッチングを終了し、その後のCMP法による研磨工程で調整しても良い。

10

# [0020]

実施の形態2.

次に、上記実施の形態1による図1および図2で示した半導体装置の素子分離構造を、分離酸化膜にTEOS酸化膜を用いて形成したものについて、図5、図6に基づいて以下に説明する。

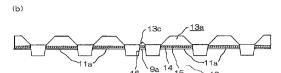

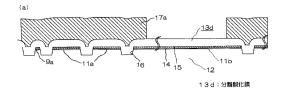

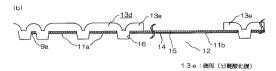

図 5 は図 2 (a)に対応する部分、図 6 は図 2 (b)に対応する部分の素子分離工程をそれぞれ示す断面図である。

まず、上記実施の形態 1 と同様に、半導体基板 1 2 上に下敷き酸化膜 1 4 、さらに窒化膜 1 5 を形成した後、本番パターン 9 とダミーパターン 1 1 とのアクティブ領域 9 、 1 1 を除く領域の窒化膜 1 5 を選択的にエッチング除去し、窒化膜 1 5 マスクを用いて半導体基板 1 2 にトレンチ 1 6 を形成する。

20

次いで、トレンチ16内を埋め込んで全面にTEOS酸化膜から成る分離酸化膜13dを堆積した後、レジストパターン17aを分離酸化膜13d上に形成する。このレジストパターン17aは、所定のパターン寸法より大きいアクティブ領域9、11、および例えばDRAM部のメモリセルなど、微細本番パターン9aが密集した領域の分離酸化膜13dをエッチングするためのマスクパターンとして形成され、対象となる領域より、例えば約1.5μmアンダーサイシングして形成する(図5(a)、図6(a))。

#### [0021]

次に、レジストパターン17aをマスクとして分離酸化膜13dを、窒化膜15表面が露出しないところの所定の深さまでエッチングして開口する。これにより、比較的広いアクティブ領域9、11、即ち、大きなダミーパターン11b、比較的広い本番パターン9および微細本番パターン9aの密集領域の分離酸化膜13dは、中央部が下地窒化膜15を露出しない程度に開口され端部13eが残存する。このときのエッチングは、ドライでもウェットでも良い(図5(b)、図6(b))。

30

この後、上記実施の形態1と同様に、CMP法により分離酸化膜13dを研磨して窒化膜15上の分離酸化膜13dを除去してトレンチ16内のみに残存させ、トレンチ型分離酸化膜13を形成する(図5(c)、図6(c))。

次に、窒化膜15、下敷き酸化膜14を順次ウェットエッチングにより除去して、所定の処理を施して図2(a)、図2(b)で示した素子分離が完成する。

### [0022]

40

この実施の形態においても、上記実施の形態1と同様に、素子分離の際の分離酸化膜13dのCMP法による研磨の際、研磨速度の均一性が向上するため、表面平坦性が良好で信頼性の高い半導体装置が得られる。

また、TEOS酸化膜から成る分離酸化膜13dのプリエッチングを比較的広いアクティブ領域9、11のみでなく微細本番パターン9aの密集領域でも行うものとした。これは、TEOS酸化膜13dでは、微細本番パターン9a上でも膜厚が減少することなく、微細本番パターン9aの密集領域では、微細本番パターン9a上のTEOS酸化膜13dが、隣接するトレンチ16上層にも延在して大きな面積のものとなってしまい、CMP法による研磨の際、アンダーポリッシュを招き易いためである。

[0023]

### 実施の形態3.

次に、この発明の実施の形態3を説明する。

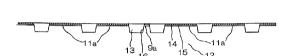

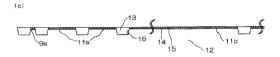

図7はこの発明の実施の形態3による半導体装置の平面図、図8(a)は図7のA7-A7線における断面図、図8(b)は図7のB7-B7線における断面図である。

図に示すように、本番パターン 9 を囲む分離領域 1 0 内に面積の異なる 2 種のダミーパターン 1 1 ( 1 1 a 、 1 1 b )を配置する。このダミーパターン 1 1 の配置方法は、まず、本番パターン 9 周囲に小さなダミーパターン 1 1 a を規則的に配列させる。例えば、 3  $\mu$  m角のダミーパターン 1 1 a を 5  $\mu$  m ピッチでアレイする。

本番パターン 9 とその周囲の小さなダミーパターン 1 1 a のさらに周囲に、大きなダミーパターン 1 1 b を敷き詰めるように規則的に配列させて配置する。例えば、 1 8  $\mu$  m角のダミーパターン 1 1 b を 2 0  $\mu$  mピッチでアレイする。

#### [0024]

このような半導体装置の素子分離工程は、分離酸化膜にHDP酸化膜13aを用いた場合は上記実施の形態1と同様に(図3、図4参照)、また、分離酸化膜にTEOS酸化膜13dを用いた場合は上記実施の形態2と同様に(図5、図6参照)行う。

#### [0025]

この実施の形態では、本番パターン9周囲に小さなダミーパターン11aを配置し、さらにその周囲に大きなダミーパターン11bを規則的に配列させて配置したため、トレンチ型分離酸化膜13の幅が所定の幅を超えて大きくならない。このため、上記実施の形態1および2と同様に、CMP法による分離酸化膜13a(13d)を研磨する際、研磨速度が速くなることが抑えられ、ディッシング(dishing)による膜厚の落ち込みが防止できる。

また、微細本番パターン9aの両側のトレンチ型分離酸化膜13の幅も、周囲に小さなダミーパターン11aが配置されているため狭く抑えられるので、オーバーポリッシュにより微細本番パターン9aの窒化膜15が研磨されるのが防止でき、素子の電気的特性の劣化を招くことがなくなる。さらに、大きなダミーパターン11bと小さなダミーパターン11aが密集した領域がなくなり、アンダーポリッシュも防止できる。大きなダミーパターン11bおよび比較的広い本番パターン9の領域上の分離酸化膜13a(13d)は、CMP法による研磨工程の前に、予めエッチング(プリエッチング)して中央部を開口しているため、容易に研磨できてアンダーポリッシュによる問題は無い。

# [0026]

上述したように、この実施の形態においても、上記実施の形態 1 および 2 と同様に、素子分離の際の分離酸化膜 1 3 a ( 1 3 d ) の C M P 法による研磨の際、研磨速度の均一性が向上するため、表面平坦性が良好で信頼性の高い半導体装置が得られる。

#### [0027]

なお、上記実施の形態 1 ~ 3 では、ダミーパターン 1 1 は大小 2 種類のものとしたが、 3 種類以上にしても良く、上記実施の形態 1 のように、本番パターン 9 から遠方位置に一番大きいダミーパターン 1 1 を配置し、本番パターン 9 に向かってダミーパターン 1 1 の面積を徐々に小さいものを配置するか、あるいは、上記実施の形態 3 のように、本番パターン 9 の周囲に一番小さいダミーパターン 1 1 を配置し、遠方位置に向かってダミーパターン 1 1 の面積を徐々に大きいものを配置する。

このように、本番パターン9との位置関係によってダミーパターン11の面積を設定して配置し、トレンチ型分離酸化膜13の幅が必要以上に大きくなることを抑えることにより、CMP法による分離酸化膜13a(13d)の研磨の際、研磨速度の均一性が向上でき、表面平坦性が良好で信頼性の高い半導体装置が得られる。

### [0028]

# 【発明の効果】

以上のように、この発明に係る請求項 1 記載の半導体装置は、トレンチ型分離酸化膜パターンが所定の幅を超えて大きくならないように、該トレンチ型分離酸化膜パターンに囲ま

10

20

30

40

れるダミーのアクティブ領域となる面積の異なる複数種のダミーパターンを分離領域内に備え、該ダミーパターンを電気的アクティブデバイス領域のパターンとの位置関係に応じて面積を設定して規則的に配列したため、CMP法による分離酸化膜研磨の際、研磨速度の均一性が向上でき、表面平坦性が良好で信頼性の高い半導体装置が得られる。

### [0029]

またこの発明に係る請求項 2 記載の半導体装置は、請求項 1 において、電気的アクティブデバイスのパターン周囲には比較的小さい面積のダミーパターンを配置し、これらの周囲にさらに比較的大きい面積のダミーパターンを配置したため、トレンチ型分離酸化膜パターンの幅が必要以上に大きくなることが確実に抑えられ、CMP法による分離酸化膜研磨の際、研磨速度の均一性が向上でき、表面平坦性が良好で信頼性の高い半導体装置が得られる。

10

#### [0030]

またこの発明に係る請求項3記載の半導体装置は、請求項1において、電気的アクティブデバイスのパターンの遠方位置から該パターンに向かって比較的大きいダミーパターンを配置し、該電気的アクティブデバイスのパターン周辺にできた間隙に比較的小さいダミーパターンを挿入して配置したため、トレンチ型分離酸化膜パターンの幅が必要以上に大きくなることが確実に抑えられ、CMP法による分離酸化膜研磨の際、研磨速度の均一性が向上でき、表面平坦性が良好で信頼性の高い半導体装置が得られる。

20

30

40

# [0031]

またこの発明に係る請求項4記載の半導体装置は、請求項1~3のいずれかにおいて、電気的アクティブデバイスの微細幅パターンの両側にトレンチ型分離酸化膜パターンを介してダミーパターンが配置され、上記トレンチ型分離酸化膜パターンの幅が、上記微細幅パターンの約1~10倍であるため、素子の電気的特性を劣化させることなく、表面平坦性が良好で信頼性の高い半導体装置が得られる。

[0032]

またこの発明に係る請求項 5 記載の半導体装置の製造方法は、半導体基板上に酸化膜を介して窒化膜を形成した後、分離領域内の所定の領域に所定の深さのトレンチを形成し、上記分離領域内に上記トレンチ領域とダミーパターンとなるダミーのアクティブ領域とを形成する第 1 の工程と、上記トレンチを埋め込んで全面に分離酸化膜を堆積する第 2 の工程と、所定のパターン寸法よりも大きい上記ダミーパターン領域上の上記分離酸化膜を、該パターン端部領域を所定の幅で残存させて選択的にエッチングする第 3 の工程と、 C M P 法により上記窒化膜上の上記分離酸化膜を研磨して除去する第 4 の工程とを有するため、表面平坦性が良好で信頼性の高い半導体装置が容易で確実に得られる。

【図面の簡単な説明】

- 【図1】 この発明の実施の形態1による半導体装置の平面図である。

- 【図2】 この発明の実施の形態1による半導体装置の断面図である。

- 【図3】 この発明の実施の形態1による半導体装置の製造方法を示す断面図である。

- 【図4】 この発明の実施の形態1による半導体装置の製造方法を示す断面図である。

- 【図5】 この発明の実施の形態2による半導体装置の製造方法を示す断面図である。

- 【図6】 この発明の実施の形態2による半導体装置の製造方法を示す断面図である。

- 【図7】 この発明の実施の形態3による半導体装置の平面図である。

- 【図8】 図7の断面図である。

- 【図9】 従来の半導体装置の平面図である。

- 【図10】 従来の半導体装置の断面図である。

- 【図11】 従来の半導体装置の問題点を示す断面図である。

- 【図12】 従来の別例による半導体装置の平面図である。

- 【図13】 従来の別例による半導体装置の平面図である。

- 【図14】 図12に示す半導体装置の断面図である。

## 【符号の説明】

9 電気的アクティブデバイス領域、

- 9 a 電気的アクティブデバイスの微細幅パターンとしての微細本番パターン、

- 10 分離領域、11 ダミーパターン、11a 小さなダミーパターン、

- 11b 大きなダミーパターン、12 半導体基板、

- 13 トレンチ型分離酸化膜、13a,13d 分離酸化膜、

- 13b,13e 端部(分離酸化膜)、14 下敷き酸化膜、15 窒化膜、

- 16 トレンチ。

# 【図1】

# 【図2】

# 【図3】

13b:端部(分離酸化膜)

# 【図4】

(c)

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

# フロントページの続き

(74)代理人 100124523

弁理士 佐々木 眞人

(74)代理人 100098316

弁理士 野田 久登

(72)発明者 冨田 和朗

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 三浦 尊裕

(56)参考文献 特開平09-306996 (JP,A)

特開平10-092921(JP,A)

特開2001-144171(JP,A)

特開平05-275527(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/76