(10) **DE 43 26 133 B4** 2008.07.31

(12)

# **Patentschrift**

(21) Aktenzeichen: P 43 26 133.7

(22) Anmeldetag: **04.08.1993** (43) Offenlegungstag: **24.02.1994**

(45) Veröffentlichungstag

der Patenterteilung: 31.07.2008

(51) Int Cl.8: **H03K 19/003** (2006.01) **G11C 7/06** (2006.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten(§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

07/932,427 19.08.1992 US

(73) Patentinhaber:

Hyundai Electronics America Inc., San Jose, Calif., US

(74) Vertreter:

Sparing · Röhl · Henseler, 40237 Düsseldorf

(72) Erfinder:

Fong, Vincent L., Fremont, Calif., US

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

US 49 82 363 A

US 49 35 649 A

US 49 18 341 A

US 47 71 194 A

JP 62-2 23 883 A

JP 03-2 12 897 A

#### (54) Bezeichnung: Schneller Strom-Leseverstärker

(57) Hauptanspruch: Leseverstärker, angeschlossen zwischen einer ersten und einer zweiten Leistungsversorgungsschiene und mit einer Eingangsklemme (30) sowie einer Ausgangsklemme (40) versehen, wobei der Leseverstärker umfasst:

einen ersten und einen zweiten als Diode arbeitenden Transistor (34, 36), die in Serie zwischen die erste und die zweite Leistungsversorgungsschiene gelegt sind, wobei die Eingangsklemme (30) an einen Knoten (39) in der Reihenschaltung zwischen dem ersten und dem zweiten Transistor (34, 36) angeschlossen ist,

einen ersten Inverter (41, 42), der mit einem Eingangsknoten an den Knoten (39) und mit seinem Ausgangsknoten an die Ausgangsklemme (40) angeschlossen ist, wobei der erste Inverter (41, 42) im Ansprechen auf eine Spannung an dem Knoten (39) in einen von zwei logischen Zuständen versetzt wird, wodurch ein Strom an der Eingangsklemme (30) einen Logikzustand an der Ausgangsklemme (40) bestimmt, und wobei der erste Inverter (41, 42) zwei in Reihe geschaltete Transistoren (41, 42) umfasst, deren Gates jeweils mit dem...

### **Beschreibung**

**[0001]** Die vorliegende Erfindung bezieht sich auf einen integrierten Leseverstärkerschaltkreis und insbesondere auf einen schnellen Strom-Leseverstärkerschaltkreis.

[0002] Leseverstärker sind erforderlich für Schaltungen, die die Diskriminierung von Signalen in Signale unterschiedlichen Zustands erfordern, d. h. ein deutlicher logischer Zustand eins oder logischer Zustand null. Beispielsweise werden diese Verstärker in alle integrierten Speicherschaltkreisen verwendet zum Erkennen des digitalen Zustands einer Speicherzelle. Die Leseverstärkerschaltkreise können verwendet werden, um die Differenz in gespeicherten Ladungen, Zellenströmen oder Zellenspannungen zu bestimmen. Für jede Schaltung in einer integrierten Schaltkreiskomponente ist es wünschenswert, daß der Schaltkreis robust sei, d. h. in der Lage, unter einer Mehrzahl von Bedingungen zu funktionieren. Typischerweise ist es wünschenswert, daß ein Leseverstärker in der Lage sei, bei Fluktuationen der Leistungsversorgungsspannungen zu arbeiten. Darüber hinaus sollte die Zahl von Transistoren, verwendet bei der Konstruktion des Leseverstärkerschaltkreises, minimal sein, um Platz auf der integrierten Schaltung zu sparen. Aufgabe der vorliegenden Erfindung ist die Schaffung eines solchen Leseverstärkers.

[0003] Aus US 4 771 194 A ist ein Leseverstärker bekannt, der zwischen einer ersten und einer zweiten Leistungsversorgungsschiene angeschlossen ist. Der Leseverstärker ist mit einer Eingangsklemme sowie einer Ausgangsklemme versehen und umfasst eine erste und eine zweite als Diode arbeitende Komponente, die in Serie zwischen die erste und die zweite Leistungsversorgungsschiene gelegt sind. Die Eingangsklemme ist an einen Knoten in der Reihenschaltung zwischen der ersten und der zweiten Komponente angeschlossen. Der Leseverstärker umfasst weiter einen ersten Inverter, der mit einem Eingangsknoten an den Serienknoten und mit seinem Ausgangsknoten an die Ausgangsklemme angeschlossen ist. Der erste Inverter wird im Ansprechen auf eine Spannung an dem Eingangsknoten in einen von zwei logischen Zuständen versetzt, wodurch ein Strom an der Eingangsklemme einen Logikzustand an der Ausgangsklemme bestimmt.

**[0004]** Aus JP 62-223 883 A ist ein Leseverstärker bekannt, der zwischen einer ersten und einer zweiten Leistungsversorgungsschiene angeschlossen und mit einer Eingangsklemme sowie einer Ausgangsklemme versehen ist. Der Leseverstärker umfasst einen ersten und einen zweiten als Diode arbeitenden Transistor, die in Serie zwischen die erste und die zweite Leistungsversorgungsschiene gelegt sind, wobei die Leistungsklemme an einen Knoten in der

Reihenschaltung zwischen dem ersten und dem zweiten Transistor angeschlossen ist. Der Leseverstärker umfasst ferner einen ersten Inverter, der mit einem Eingangsknoten an den Knoten und mit seinem Ausgangsknoten an die Ausgangsklemme angeschlossen ist, wobei der erste Inverter im Ansprechen auf eine Spannung an dem Knoten in einen von zwei logischen Zuständen versetzt wird, wodurch ein Strom an der Eingangsklemme einen Logikzustand an der Ausgangsklemme bestimmt, und wobei der erste Inverter zwei in Reihe geschaltete Transistoren umfasst, deren Gates jeweils mit dem Knoten verbunden sind. Ferner ist bei dem Leseverstärker eine einen ersten Schalter umfassende Sperranordnung vorgesehen, wobei der erste Schalter im Ansprechen auf ein Signal an einer Steuerklemme öffnet.

**[0005]** Die vorgenannte Aufgabe der Erfindung wird durch die Merkmale des Anspruchs 1 gelöst.

**[0006]** Die Erfindung wird nachstehend anhand der in den beigefügten Abbildungen dargestellten Ausführungsbeispiele näher erläutert.

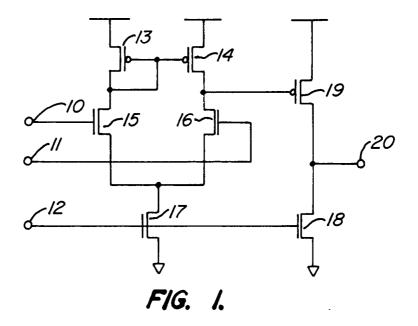

[0007] Fig. 1 ist ein Schaltungsdiagramm eines Leseverstärkerschaltkreises nach dem Stand der Technik

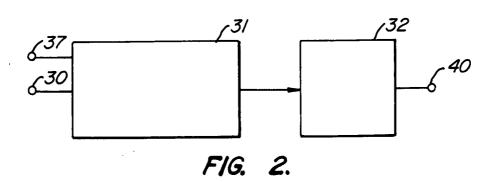

[0008] Fig. 2 ist ein Blockdiagramm eines Differentialschaltkreises gemäß der vorliegenden Erfindung.

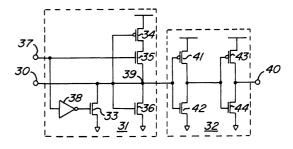

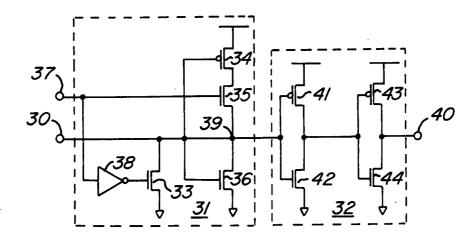

[0009] Fig. 3 ist ein Schaltungsdiagramm des Schaltkreises gemäß Fig. 2.

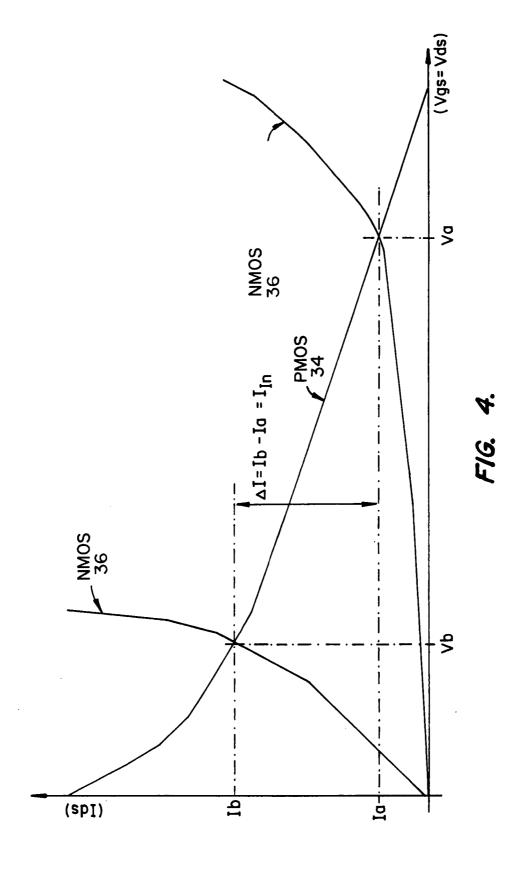

[0010] Fig. 4 zeigt ein Stromspannungsdiagramm verschiedener Elemente der Schaltung nach Fig. 3.

[0011] Fig. 1 zeigt einen Leseverstärker, der gewöhnlich unter der Bezeichnung Stromspiegeldifferentialverstärker bekannt ist. Dieser Typ von Leseverstärker ist typisch für den Stand der Technik. Der Leseverstärker besitzt eine Eingangsklemme 10 für den Empfang eines Eingangssignals und zwei Referenzspannungsklemmen 11 und 12. Typpischerweise werden Spannungen von 2,5 Volt für Klemme 11 und 1,5 Volt für Klemme 12 angewandt.

[0012] Dieser Typ von Leseverstärker funktioniert so, daß bei Anlegen einer Spannung an die Eingangsklemme 10, die höher ist als die Referenzspannung an Klemme 11, das Gate des NMOS-Transistors 15 auf einer höheren Spannung liegt als das Gate des NMOS-Transistors 16. Dies zieht den Knoten 20 weiter nach unten als die Spannung am Knoten 21. Dies wiederum bewirkt, daß der PMOS-Transistor 19 weniger stark eingeschaltet wird als der NMOS-Transistor 18. Das Ergebnis ist, daß der Ausgangsknoten 20 auf logisch null gezogen wird durch den NMOS-Transistor 18.

[0013] Wenn in ähnlicher Weise die Spannung an der Eingangsklemme 10 niedriger ist als die Spannung an der Referenzklemme 11, liegt der Knoten 20 höher als der Knoten 21. Der PMOS-Transistor 19 wird weiter durchgeschaltet als der NMOS-Transistor 18, und der Ausgangsknoten 20 wird hochgezogen durch die Wirkung des PMOS-Transistors 19.

[0014] Dieser Typ eines relativ einfachen Schaltkreises hat jedoch einige Nachteile. Der typische normale Betriebsbereich für die Schaltung ist etwa 4 bis 6 Volt, d. h. die Differenz in den beiden Spannungsversorgungsschienen beträgt normalerweise zwischen 4 und 6 Volt. Darüber hinaus begrenzen die Fehlanpassung der Stromspiegeltransistoren und Gleichtaktfehler die Empfindlichkeit dieses Typs von Leseverstärkerschaltkreis. Die Belastungen auf den Transistoren 15 und 16 sind nicht vollkommen angepaßt infolge der unterschiedlichen Verschaltung der Lasttransistoren 13 und 14. Wenn die Leistungsversorgungsspannung  $V_{\text{CC}}$  sich aus irgendeinem Grunde ändert, sind die Änderungen in den Strömen durch die Transistoren 13 und 14 nicht aneinander angepaßt, da die Transistoren 13 und 14 nicht angepaßt sind. Zusätzlich erhöhen die erforderlichen Referenzspannungen für die Klemmen 11 und 12 die Möglichkeit von Fehlern und begrenzen darüber hinaus die Effektivität dieses Schaltkreises unter verschiedenen elektrischen Bedingungen. Schließlich arbeiten alle Transistoren 13, 15, 14, 16 und 17 in dem aktiven Modus, was noch mehr den Funktionsbereich und die Geschwindigkeit dieses Leseverstärkerschaltkreises begrenzt.

[0015] Andererseits ist die vorliegende Erfindung so ausgelegt, daß die Transistoren im Sättigungsmodus arbeiten für den Betrieb, der toleranter ist gegenüber Leistungsversorgungsfluktuationen und Prozeßabweichungen. Fig. 2 zeigt die generelle Konfiguration der vorliegenden Erfindung. Die vorliegende Erfindung sieht eine Eingangsklemme 30 zu einem Stromspannungswandlerblock 31 vor, der seinerseits einen Pufferschaltkreis 32 beaufschlagt, der das Signal an einer Ausgangsklemme 40 erzeugt.

[0016] Fig. 3 zeigt die Einzelheiten der Blöcke 31 und 32. Die Steuerklemme 37, die ein Entsperrsignal empfängt, ist mit der Gate-Klemme eines NMOS-Transistors 35 verbunden, der ein Teil eines Satzes von in Serie geschalteten Transistoren zwischen der höheren positiveren Spannungsversorgung bei  $V_{\rm CC}$  und der niedrigeren Spannungsversorgung bei Masse ist. Ein PMOS-Transistor 34 ist mit seiner Source an  $V_{\rm CC}$  angeschlossen und mit seinem Drain mit der Source des Transistors 35 verbunden. Das Drain des NMOS-Transistors 35 ist mit dem Drain des NMOS-Transistors 36 verbunden, der mit seiner Source an Masse liegt.

[0017] Die Steuerklemme 37 ist ferner verbunden

mit einem Eingangsknoten eines Inverters 38, dessen Ausgangsknoten mit dem Gate des NMOS-Transistors 33 verbunden ist. Die Source des NMOS-Transistors 33 liegt an Masse, und sein Drain ist mit der Eingangsklemme 30 des Leseverstärkers verbunden. Die Klemme 30 empfangt das Signal, das "zu lesen" ist. Das Drain des Transistors 33 ist außerdem verbunden mit den Gates des PMOS-Transistors 34 und des NMOS-Transistors 36 und einem Ausgangsknoten 39 des Strom-Spannungs-Umsetzerblocks 31. Der Knoten 39 wird gebildet von der Source des Transistors 35 und dem Drain des Transistors 36.

[0018] Die NMOS-Transistoren 33 und 35 arbeiten als einfache Schalter, welche den Block 31 entsperren in Abhängigkeit von einem Entsperrsignal an Klemme 37. Ein logisch hochliegendes Signal entsperrt den Block 31, und ein tiefliegendes Signal sperrt den Block 31. Der Transistor 35 verbindet die beiden Transistoren 34 und 36, während der Transistor 33 den Ausgangsknoten 39 und die Eingangsklemme 30 von Masse trennt. Der Puffer 32 wird von zwei in Serie geschalteten Invertern gebildet. Der erste Inverter wird von einem Paar komplementärer Transistoren 41 und 42 gebildet. Die Gates der Transistoren 41 und 42 sind mit dem Ausgangsknoten 39 Block 31 verbunden. Die Source des PMOS-Transistors **41** ist mit  $V_{CC}$  verbunden, und sein Drain ist verbunden mit dem Drain des NMOS-Tranistors 42. Die Source des NMOS-Transistors ist mit Masse verbunden. Der Ausgangsknoten des ersten Inverters, gebildet durch die gemeinsame Verbindung der Drains des PMOS-Transistors 41 und NMOS-Transistors 42, sind mit dem Eingangsknoten des zweiten Inverters verbunden.

[0019] Der PMOS-Transistor 43 und NMOS-Transistor 44 bilden den zweiten Inverter. Die Transistoren 43, 44 sind mit den beiden Leistungsversorgungsschienen in gleicher Weise verbunden wie die Transistoren 41, 42 des ersten Inverters. Die zusammengeschalteten Gates der Transistoren 43, 44 bilden den Eingangsknoten des zweiten Inverters, und die Zusammenschaltung zwischen den Drains von PMOS-Transistor 43 und NMOS-Transistor 44 bildet den Ausgangsknoten zur Ausgangsklemme 40 des Leseverstärkers.

[0020] Wenn der Block 31 entsperrt ist, arbeiten der PMOS-Transistor 34 und der NMOS-Transistor 36 im Sättigungsmodus. Die beiden Transistoren 34, 36 können als in Diodenkonfiguration geschaltete Transistoren angesehen werden, bei denen das Gate und Drain jedes Transistors auf der gleichen Spannung liegt. Die Stromspannungskurven für beide Transistoren 34 und 36 sind in Fig. 4 gezeigt.

[0021] Wenn kein Eingangsstrom durch die Eingangsklemme 30 fließt, bleibt die Klemme 30 auf ei-

ner Spannung Va. Der Transistor **34** wird von demselben Strom la durchflossen. Wenn ein Strom Δl über die Eingangsklemme **30** eingespeist wird, verlagert sich der Punkt a zu Punkt b, so daß die Eingangsklemme **30** (und der Ausgangsknoten **39**) nun auf einer Spannung Vb liegen. Der Transistor **34** wird von einem Strom lb durchflossen. Demgemäß fluktuiert der Ausgangsknoten **39**, wie man in Fig. 4 sehen kann, in einem Spannungsbereich in Abhängigkeit von der Höhe des Stromes, der durch die Eingangsklemme **30** fließt.

[0022] Der PMOS-Transistor 41 und von NMOS-Transistor 42 gebildete erste Inverter ist ausgelegt für einen Schaltpunkt zwischen den Spannungen Va und Vb. In typischen Anwendungen sollte der Schaltpunkt bei der Spannung liegen, bei welcher (la + Ib)/2 ist, obwohl der Schaltpunkt abweichen kann, je nach dem besonderen Anwendungsfall. Die Bestimmung eines Schaltpunktes ist Konstrukteuren von integrierten Schaltkreisen bekannt. Durch Auswählen der Abmessung und der Betriebsparameter der beiden Transistoren, die typischerweise einen Inverter bilden, kann der Schaltpunkt des Inverters vorgegeben werden. Demgemäß wird der Ausgang vom Block 31 in der einen oder anderen Weise in eine logische Eins oder eine logische Null umgesetzt.

[0023] Da der Betrieb der Schaltung einfach von den Transistoren 34 und 36 abhängt, die mehr oder weniger Transistoren in einer Diodenkonfiguration sind, ist dieser Schaltkreis sehr tolerant gegenüber Abweichungen in der Layout-Orientierung, Leistungsversorgungsfluktuationen und Herstellungsprozeßvariationen. Der Strom-Leseverstärker hat eine kleine Anzahl von Elementen und funktioniert über einen breiten Bereich von Versorgungsspannungsfluktuationen.

## Patentansprüche

1. Leseverstärker, angeschlossen zwischen einer ersten und einer zweiten Leistungsversorgungsschiene und mit einer Eingangsklemme (30) sowie einer Ausgangsklemme (40) versehen, wobei der Leseverstärker umfasst:

einen ersten und einen zweiten als Diode arbeitenden Transistor (34, 36), die in Serie zwischen die erste und die zweite Leistungsversorgungsschiene gelegt sind, wobei die Eingangsklemme (30) an einen Knoten (39) in der Reihenschaltung zwischen dem ersten und dem zweiten Transistor (34, 36) angeschlossen ist,

einen ersten Inverter (41, 42), der mit einem Eingangsknoten an den Knoten (39) und mit seinem Ausgangsknoten an die Ausgangsklemme (40) angeschlossen ist, wobei der erste Inverter (41, 42) im Ansprechen auf eine Spannung an dem Knoten (39) in einen von zwei logischen Zuständen versetzt wird, wodurch ein Strom an der Eingangsklemme (30) ei-

nen Logikzustand an der Ausgangsklemme (40) bestimmt, und wobei der erste Inverter (41, 42) zwei in Reihe geschaltete Transistoren (41, 42) umfasst, deren Gates jeweils mit dem Knoten (39) verbunden sind, und

eine einen ersten und einen zweiten Schalter (33, 35) umfassende Sperranordnung, wobei der erste Schalter (35) in Reihe zwischen den ersten und den zweiten Transistor (34, 36) geschaltet ist und im Ansprechen auf ein Signal an einer Steuerklemme öffnet, und wobei der zweite Schalter (33) mit dem Knoten (39) verbunden ist und im Ansprechen auf das Signal an der Steuerklemme den Knoten (39) auf eine der Leistungsversorgungsschienen klemmt.

- 2. Leseverstärker nach Anspruch 1, bei dem der erste und zweite Transistor (34, 36) jeweils ein MOS-Transistor ist, dessen Drain jeweils an dessen Gate angeschlossen ist.

- 3. Leseverstärker nach Anspruch 1 oder 2, bei dem der erste Transistor (34) ein PMOS-Transistor ist, der mit einer ersten Source/Drain an die erste Leistungsversorgungsschiene angeschlossen ist, die eine höhere Spannung führt als die zweite Leistungsversorgungsschiene, und bei dem der zweite Transistor (36) ein NMOS-Transistor ist mit einer ersten Source/Drain, die an die zweite Leistungsversorgungsschiene angeschlossen ist.

- 4. Leseverstärker nach einem der Ansprüche 1 bis 3, ferner umfassend einen zweiten Inverter (43, 44), der mit einem Eingangsknoten mit dem Ausgangsknoten des ersten Inverters (41, 42) und mit seinem Ausgangsknoten mit der Ausgangsklemme (40) verbunden ist.

- 5. Leseverstärker nach Anspruch 1, bei dem die Charakteristiken des ersten und des zweiten Transistors (34, 36) so gewählt sind, dass sie in einem vorbestimmten Spannungsbereich im Ansprechen auf den Strom an der Eingangsklemme (30) arbeiten.

- 6. Leseverstärker nach einem der Ansprüche 1 bis 5, wobei der erste und der zweite Schalter (**35**, **33**) als MOS-Transistoren ausgebildet sind.

Es folgen 2 Blatt Zeichnungen

## Anhängende Zeichnungen

FIG. 3.