# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(45) 공고일자 2022년09월27일

(11) 등록번호 10-2447407

(24) 등록일자 2022년09월21일

(51) 국제특허분류(Int. Cl.)

**H01L 33/36** (2010.01) **H01L 25/075** (2006.01)

(52) CPC특허분류

**H01L 33/36** (2013.01) **H01L 25/0753** (2013.01)

(21) 출원번호 10-2020-0150841

(22) 출원일자2020년11월12일

심사청구일자 **2020년11월12일**

(65) 공개번호 **10-2022-0064596**

(43) 공개일자 2022년05월19일

(56) 선행기술조사문헌 CN105280665 A\*

(뒷면에 계속) 전체 청구항 수 : 총 6 항 (73) 특허권자

## 주식회사 에스엘바이오닉스

경기 용인시 기흥구 원고매로2번길 49, 3층 (고매동)

(72) 발명자

#### 김태현

경기도 오산시 남부대로 486-23, 113동 703호(청호동, 휴먼시아 아파트)

#### 이성찬

경기도 용인시 기흥구 구성로 90, 203동 301호(언남동, 삼성래미안2차아파트)

(74) 대리인

안상정

심사관 : 이용배

(54) 발명의 명칭 **반도체 발광소자**

#### (34) 글 3기 33 원고제

#### (57) 요 약

본 발명은 반도체 발광소자에 관한 것으로, 특히 전기적으로 연결된 복수의 발광부 제조시 발광영역의 신뢰성을 개선할 수 있는 반도체 발광소자에 관한 것이다. 본 발명에 따르는 반도체 발광소자에 있어서, 제1 상부전극 및 제2 상부전극 중 적어도 하나는 제1 패드전극 또는 제2 패드전극에 의해 적어도 일부가 덮인 복수의 발광부 각각의 상부의 적어도 일부에서 각각 제1 패드전극 또는 제2 패드전극과 전기적으로 연결되도록 구성된다.

#### 대 표 도 - 도7

(56) 선행기술조사문헌

KR1020120031473 A

KR1020160046010 A

KR101868518 B1

KR1020160054693 A

KR1020180096546 A

\*는 심사관에 의하여 인용된 문헌

## 명세서

# 청구범위

#### 청구항 1

반도체 발광소자에 있어서,

기판 위에 서로 떨어져 형성된 제1 발광부 및 제2 발광부를 포함하는 제1 발광부 어레이;

기판 위에 서로 떨어져 형성된 제3 발광부 및 제4 발광부를 포함하는 제2 발광부 어레이;

제1 발광부에 전기적으로 연결된 제1 패드전극;

제4 발광부에 전기적으로 연결된 제2 패드전극;

제1 패드전극 상부에 위치하며 제1 패드전극에 전기적으로 연결된 제1 상부전극; 및

제2 패드전극 상부에 위치하며 제2 패드전극에 전기적으로 연결된 제2 상부전극;

을 포함하며,

제1 발광부 내지 제4 발광부 각각은 제1 도전성을 가지는 제1 반도체층, 제1 도전성과 다른 제2 도전성을 가지는 제2 반도체층, 및 제1 반도체층과 제2 반도체층의 사이에 개재되어 전자와 정공의 재결합에 의해 빛을 생성하는 활성층을 포함하며,

제1 발광부 내지 제4 발광부는 서로 전기적으로 연결되며,

제1 패드전극은 제1 발광부와 제2 발광부를 함께 덮도록 배치되며,

제1 상부전극은 제1 발광부 상부와 제2 발광부 상부에서 제1 패드전극의 상부에 위치하도록 배치되며.

제1 발광부 상부와 제2 발광부 상부 각각에 형성된 전극연결부에 의해 제1 상부전극과 제1 패드전극이 전기적으로 연결되는, 반도체 발광소자.

## 청구항 2

삭제

#### 청구항 3

삭제

## 청구항 4

청구항 1에 있어서,

제1 발광부와 제2 발광부를 전기적으로 연결하는 제1 연결전극을 더욱 포함하고,

제1 연결전극은 제1 하부연결부, 제1 수평연결부, 및 제2 하부연결부를 포함하며,

제1 수평연결부는 제1 발광부 상부와 제2 발광부 상부에 걸쳐서 배치되며,

제1 하부연결부는 제1 수평연결부의 일단을 제1 발광부의 제2 반도체층과 전기적으로 연결하며,

제2 하부연결부는 제1 수평연결부의 타단을 제2 발광부의 제1 반도체층과 전기적으로 연결하는, 반도체 발광소자.

# 청구항 5

청구항 4에 있어서,

제1 수평연결부와 제1 패드전극은 동일 높이의 층에 형성되는 것을 특징으로 하는, 반도체 발광소자.

#### 청구항 6

청구항 4에 있어서,

제1 패드전극은 제1 발광부 및 제2 발광부 각각의 상부의 가운데 영역을 가로질러 배치되어 제1 발광부와 제2 발광부를 함께 덮도록 배치되며,

제1 수평연결부는 제1 패드전극과 이격되어 배치되되 제1 발광부 및 제2 발광부 각각의 상부의 좌측 가장자리 또는 우측 가장자리를 따라 배치되는, 반도체 발광소자.

#### 청구항 7

청구항 4에 있어서.

제1 발광부의 제2 반도체층에 제2 반도체층의 수평 방향으로 제1 가지전극이 형성되거나 또는 제2 발광부의 제1 반도체층에 제1 반도체층의 수평 방향으로 제2 가지전극이 형성되며,

제1 가지전극 또는 제2 가지전극은 제1 패드전극 및 제1 상부전극에 의해 덮히도록 배치되는, 반도체 발광소자.

## 청구항 8

청구항 4에 있어서,

제2 발광부와 제3 발광부을 연결하는 제2 연결전극을 더욱 포함하며,

제2 연결전극은 제1a 하부연결부, 제2 수평연결부, 및 제2a 하부연결부를 포함하며,

제2 수평연결부는 제2 발광부 상부와 제3 발광부 상부에 걸쳐서 배치되며,

제1a 하부연결부는 제2 수평연결부의 일단을 제2 발광부의 제2 반도체층과 전기적으로 연결하며,

제2a 하부연결부는 제2 수평연결부의 타단을 제3 발광부의 제1 반도체층과 전기적으로 연결하며,

제2 수평연결부는 제1 패드전극이 덮지 않는 제2 발광부의 상부에서 제1 패드전극과 동일 높이의 층에서 형성되는, 반도체 발광소자.

## 발명의 설명

## 기술분야

[0001] 본 개시(Disclosure)는 전체적으로 반도체 발광소자에 관한 것으로, 특히 전기적으로 연결된 복수의 발광부 제조시 발광영역의 신뢰성을 개선할 수 있는 반도체 발광소자에 관한 것이다.

## 배경기술

- [0002] 여기서는, 본 개시에 관한 배경기술이 제공되며, 이들이 반드시 공지기술을 의미하는 것은 아니다(This section provides background information related to the present disclosure which is not necessarily prior art).

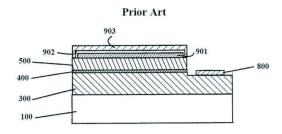

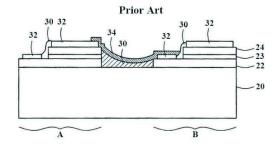

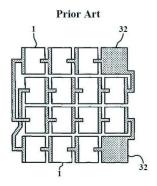

- [0003] 도 1은 미국 등록특허공보 제7,262,436호에 개시된 반도체 발광소자의 일 예를 나타내는 도면으로서, 반도체 발광소자는 기판(100), 기판(100) 위에 성장되는 위에 성장되는 n형 반도체층(300), n형 반도체층(300) 위에 성장되는 활성층(400), 활성층(400) 위에 성장되는 p형 반도체층(500), p형 반도체층(500) 위에 형성되는 반사막으로 기능하는 전극(901,902,903) 그리고 식각되어 노출된 n형 반도체층(300) 위에 형성되는 n측 본딩 패드(800)를 포함한다.

- [0004] 이러한 구조의 칩, 즉 기판(100)의 일 측에 전극(901,902,903) 및 전극(800) 모두가 형성되어 있고, 전극 (901,902,903)이 반사막으로 기능하는 형태의 칩을 플립 칩(filp chip)이라 한다. 전극(901,902,903)은 반사율이 높은 전극(901; 예: Ag), 본딩을 위한 전극(903; 예: Au) 그리고 전극(901) 물질과 전극(903) 물질 사이의 확산을 방지하는 전극(902; 예: Ni)으로 이루어진다. 이러한 금속 반사막 구조는 반사율이 높고, 전류 확산에 이점을 가지지만, 금속에 의한 빛 흡수라는 단점을 가진다.

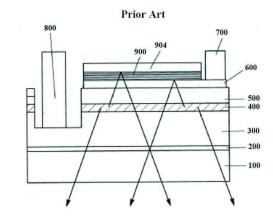

- [0005] 도 2는 일본 공개특허공보 제2006-20913호에 개시된 반도체 발광소자의 일 예를 나타내는 도면으로서, 반도체 발광소자는 기판(100), 기판(100) 위에 성장되는 버퍼층(200), 버퍼층(200) 위에 성장되는 n형 반도체층(300),

n형 반도체층(300) 위에 성장되는 활성층(400), 활성층(400) 위에 성장되는 p형 반도체층(500), p형 반도체층 (500) 위에 형성되며, 전류 확산 기능을 하는 투광성 도전막(600), 투광성 도전막(600) 위에 형성되는 p측 본딩 패드(700) 그리고 식각되어 노출된 n형 반도체층(300) 위에 형성되는 n측 본딩 패드(800)를 포함한다. 그리고 투광성 도전막(600) 위에는 분포 브래그 리플렉터(900; DBR: Distributed Bragg Reflector)와 금속 반사막(904)이 구비되어 있다. 이러한 구성에 의하면, 금속 반사막(904)에 의한 빛 흡수를 감소하지만, 전극 (901,902,903)을 이용하는 것보다 상대적으로 전류 확산이 원활치 못한 단점이 있다.

- [0006] 도 3은 미국 등록특허공보 제6,547,249호에 개시된 직렬연결된 LED(A,B)의 일 예를 나타내는 도면으로서, 여러 가지 장점 때문에 도 3에 도시된 것과 같이 복수의 LED(A,B)가 직렬연결되어 사용된다. 예를 들어, 복수의 LED(A,B)를 직렬연결하면 외부 회로와 와이어 연결의 개수가 감소하며, 와이어로 인한 광흡수 손실이 감소된다. 또한, 직렬연결된 LED(A,B) 전체의 동작전압이 상승하기 때문에 전원 공급 회로가 보다 단순화될 수 있다.

- [0007] 한편, 복수의 LED(A,B)를 직렬연결하기 위해서 인터커넥터(34)를 증착하여 이웃한 LED(A,B)의 p측 전극(32)과 n 측 전극(32)을 연결한다. 그러나 복수의 LED (A,B)를 전기적으로 절연하는 분리(isolation) 공정에서 사파이어 기판(20)이 노출되도록 복수의 반도체층을 식각해야 하는데, 그 식각 깊이가 깊어서 시간이 오래 걸리고 단차가 크기 때문에 인터커넥터(34)를 형성하기가 어렵다. 절연체(30)를 사용하여 도 3에 도시된 것과 같이 인터커넥터 (34)를 완만한 경사를 이루도록 형성하는 경우 LED(A,B)들 사이 간격이 증가하여 집적도 향상에 문제가 있다.

- [0008] 도 4는 미국 등록특허공보 제7,417,259호에 개시된 엘이디 어레이의 일 예를 나타내는 도면으로서, 고전압(high drive voltage), 저전류 구동을 위해 절연기판 위에 2차원 배열된 엘이디 어레이가 형성되어 있다. 절연기판은 사파이어 모노리식(monolithically) 기판이 사용되었고, 기판 위에 2개의 엘이디 어레이가 역방향으로 병렬연결되어 있다. 따라서, AC 전원이 직접 구동전원으로 사용될 수 있다.

## 선행기술문헌

# 특허문헌

[0009] (특허문헌 0001) 미국 등록특허 제7,262,436호(2007.08.28)

(특허문헌 0002) 미국 등록특허 제6,547,249호(2003.04.15)

(특허문헌 0003) 미국 등록특허 제7,417,259호(2008.08.26)

(특허문헌 0004) 한국 등록특허 제10-1643688호(2016.07.22)

# 발명의 내용

## 해결하려는 과제

[0010] 이에 대하여 '발명의 실시를 위한 구체적인 내용'의 후단에 기술한다.

#### 과제의 해결 수단

- [0011] 여기서는, 본 개시의 전체적인 요약(Summary)이 제공되며, 이것이 본 개시의 외연을 제한하는 것으로 이해되어 서는 아니된다(This section provides a general summary of the disclosure and is not a comprehensive disclosure of its full scope or all of its features).

- [0012] 본 개시에 따른 일 태양에 의하면(According to one aspect of the present disclosure), 반도체 발광소자에 있어서, 기판 위에 서로 떨어져 형성된 제1 발광부(101) 및 제2 발광부(102)를 포함하는 제1 발광부 어레이 (1000); 기판 위에 서로 떨어져 형성된 제3 발광부(103) 및 제4 발광부(104)를 포함하는 제2 발광부 어레이 (2000); 제1 발광부(101)에 전기적으로 연결된 제1 패드전극(70a); 제4 발광부(104)에 전기적으로 연결된 제2 패드전극(70b); 제1 패드전극(70a) 상부에 위치하며 제1 패드전극(70a)에 전기적으로 연결된 제1 상부전극(80a); 및 제2 패드전극(70b) 상부에 위치하며 제2 패드전극(70b)에 전기적으로 연결된 제2 상부전극(80b);을 포함하며, 제1 발광부(101) 내지 제4 발광부(104) 각각은 제1 도전성을 가지는 제1 반도체층(30), 제1 도전성과 다른 제2 도전성을 가지는 제2 반도체층(50), 및 제1 반도체층(30)과 제2 반도체층(50)의 사이에 개재되어 전자 와 정공의 재결합에 의해 빛을 생성하는 활성층(40)을 포함하며, 제1 발광부(101) 내지 제4 발광부(104)는 서로

전기적으로 연결되며, 제1 패드전극(70a)은 제1 발광부(101)와 제2 발광부(102)를 함께 덮도록 배치되는, 반도 체 발광소자가 제공될 수 있다.

## 발명의 효과

[0013] 이에 대하여 '발명의 실시를 위한 구체적인 내용'의 후단에 기술한다.

#### 도면의 간단한 설명

[0014] 도 1은 미국 등록특허공보 제7,262,436호에 개시된 반도체 발광소자의 일 예를 나타내는 도면이다.

도 2는 일본 공개특허공보 제2006-20913호에 개시된 반도체 발광소자의 일 예를 나타내는 도면이다.

도 3은 미국 등록특허공보 제6,547,249호에 개시된 직렬연결된 LED(A, B)의 일 예를 나타내는 도면이다.

도 4는 미국 등록특허공보 제7,417,259호에 개시된 엘이디 어레이의 일 예를 나타내는 도면이다.

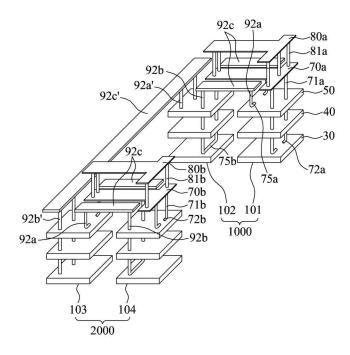

도 5는 본 발명의 하나의 구체예에 따르는 반도체 발광소자의 입체 구조를 개략적으로 제시한 도면이다.

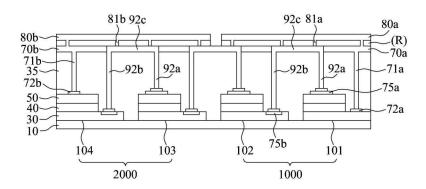

도 6은 본 발명의 하나의 구체에에 따르는 반도체 발광소자의 측면 구조를 개략적으로 제시한 도면이다.

도 7은 본 발명의 하나의 구체예에 따르는 반도체 발광소자의 평면도를 개략적으로 제시한 도면이다.

# 발명을 실시하기 위한 구체적인 내용

- [0015] 이하 첨부된 도면을 참고하여 본 발명을 더욱 자세하게 설명한다(The present disclosure will now be described in detail with reference to the accompanying drawing(s)).

- [0016] 도 5는 본 발명의 하나의 구체예에 따르는 반도체 발광소자의 입체 구조를 개략적으로 제시한 도면이다.

- [0017] 도 6은 본 발명의 하나의 구체예에 따르는 반도체 발광소자의 측면 구조를 개략적으로 제시한 도면이다.

- [0018] 도 5 및 도 6을 참조하면, 본 발명의 하나의 구체예에 따르는 반도체 발광소자는 기판 위에 서로 떨어져 형성된 제1 발광부(101) 및 제2 발광부(102)를 포함하는 제1 발광부 어레이(1000), 기판 위에 서로 떨어져 형성된 제3 발광부(103) 및 제4 발광부(104)를 포함하는 제2 발광부 어레이(2000), 제1 발광부(101)에 전기적으로 연결된 제1 패드전극(70a), 제4 발광부(104)에 전기적으로 연결된 제2 패드전극(70b), 제1 패드전극(70a) 상부에 위치하며 제1 패드전극(70a)에 전기적으로 연결된 제1 상부전극(80a), 및 제2 패드전극(70b) 상부에 위치하며 제2 패드전극(70b)에 전기적으로 연결된 제2 상부전극(80b)을 포함하며, 제1 발광부(101) 내지 제4 발광부(104) 각 각은 제1 도전성을 가지는 제1 반도체층(30), 제1 도전성과 다른 제2 도전성을 가지는 제2 반도체층(50), 및 제1 반도체층(30)과 제2 반도체층(50)의 사이에 개재되어 전자와 정공의 재결합에 의해 빛을 생성하는 활성층(40)을 포함하며, 제1 발광부(101) 내지 제4 발광부(104)는 서로 전기적으로 연결되며, 제1 패드전극(70a)은 제1 발광부(101)와 제2 발광부(102)를 함께 덮도록 배치될 수 있다.

- [0019] 본 발명의 하나의 구체예에 따른 반도체 발광소자는 기판 위에 서로 떨어져 형성된 제1 발광부(101) 및 제2 발 광부(102)를 포함하는 제1 발광부 어레이(1000), 그리고 기판 위에 서로 떨어져 형성된 제3 발광부(103) 및 제4 발광부(104)를 포함하는 제2 발광부 어레이(2000)를 포함할 수 있다.

- [0020] 제1 발광부(101) 내지 제4 발광부(104)는 서로 전기적으로 연결될 수 있다.

- [0021] 제1 발광부(101) 내지 제4 발광부(104) 각각은 제1 도전성을 가지는 제1 반도체층(30), 제1 도전성과 다른 제2 도전성을 가지는 제2 반도체층(50), 및 제1 반도체층(30)과 제2 반도체층(50)의 사이에 개재되어 전자와 정공의 재결합에 의해 빛을 생성하는 활성층(40)을 포함하는 복수의 반도체층을 포함할 수 있다.

- [0022] 기판(10)으로는 사파이어, SiC, Si, GaN 등이 이용될 수 있으며, 기판(10)은 최종적으로 제거될 수 있다.

- [0023] 복수의 반도체층은 기판(10) 위에 형성된 버퍼층(도시되지 않음), 제1 도전성을 가지는 제1 반도체층(30) 예컨 대 Si 도핑된 GaN 층, 제1 도전성과 다른 제2 도전성을 가지는 제2 반도체층(50) 예컨대 Mg 도핑된 GaN 층, 및 제1 반도체층(30)과 제2 반도체층(50) 사이에 개재되며 전자와 정공의 재결합을 통해 빛을 생성하는 활성층(40) 예컨대 다중양자우물구조의 InGaN/(In)GaN 층을 포함할 수 있다. 복수의 반도체층 각각은 다층으로 이루어질 수 있고, 버퍼층은 생략될 수 있다. 제1 반도체층(30)과 제2 반도체층(50)은 그 위치가 바뀔 수 있으며, 3족 질화물 반도체 발광소자의 경우 GaN으로 이루어질 수 있다.

- [0024] 본 발명의 하나의 구체예에 따른 반도체 발광소자는 제1 발광부(101)에 전기적으로 연결된 제1 패드전극(70a) 및 제4 발광부(104)에 전기적으로 연결된 제2 패드전극(70b)을 포함할 수 있다.

- [0025] 도 5 및 도 6을 참조하면, 제1 패드전극(70a)은 제1 발광부(101)에 전기적으로 연결되도록 구성될 수 있으며, 제2 패드전극(70b)은 제4 발광부(104)에 전기적으로 연결되도록 구성될 수 있다.

- [0026] 도 5 및 도 6을 참조하여 더욱 상세하게 설명하면, 제1 패드전극(70a)은 복수의 반도체층 중 제2 반도체층(50) 및 활성층(40)을 관통하는 제1 전기적 연결부(71a)에 의해 제1 발광부(101)의 제1 반도체층(30)과 전기적으로 연통될 수 있다. 한편 제2 패드전극(70b)은 제2 전기적 연결부(71b)에 의해 제4 발광부(104)의 제2 반도체층 (50)과 전기적으로 연통될 수 있다.

- [0027] 한편 후술하는 바와 같이 복수의 발광부 사이에 절연층(35)이 형성되는 경우 제1 전기적 연결부(71a) 및 제2 전기적 연결부(71b)는 절연층(35)을 관통하여 각각 제1 발광부(101)의 제1 반도체층(30)과 제6 발광부(106)의 제2 반도체층(50)에 전기적으로 연통될 수 있다.

- [0028] 따라서 제1 패드전극(70a) 및 제2 패드전극(70b)은 각각 후술하는 절연층(35)을 관통하는 제1 전기적 연결부 (71a) 및 제2 전기적 연결부(71b)에 의해 각각 제1 발광부(101)의 제1 반도체층(30) 및 제4 발광부(104)의 제2 반도체층(50)과 전기적으로 연통될 수 있다.

- [0029] 본 발명의 또 다른 구체예에서, 제1 패드전극(70a)은 제1 발광부(101)와 제2 발광부(102)를 함께 덮도록 배치될 수 있다. 이와 유사하게, 제2 패드전극(70b)은 제3 발광부(103)와 제4 발광부(104)를 함께 덮도록 배치될 수 있다.

- [0030] 본 발명에 따르는 패드전극(70)의 이러한 구성으로 인하여 다이 본딩 과정 중에 발생되는 칩 표면과 다층 간의 충격이나 스크래치를 완화시킬 수 있어 제조 공정시 발생되는 잠재적인 불량을 사전에 검출할 수 있다. 또한 HV(High-Voltage) 칩 구조에서 발생할 수 있는 발광영역 일부의 약점등/미점등의 불량을 감소시켜 신뢰성 불량을 개선할 수 있다.

- [0031] 본 발명에 따른 반도체 발광소자는 제1 패드전극(70a) 상부에 위치하며 제1 패드전극(70a)에 전기적으로 연결된 제1 상부전극(80a) 및 제2 패드전극(70b) 상부에 위치하며 제2 패드전극(70b)에 전기적으로 연결된 제2 상부전 극(80b)을 포함할 수 있다.

- [0032] 도 5 및 도 6을 참조하여 더욱 상세하게 설명하면, 제1 상부전극(80a)은 제1 패드전극(70a)의 상부에 위치하며 제1 패드전극(70a)에 전기적으로 연결될 수 있다. 따라서 제1 상부전극(80a)은 제1 패드전극(70a)을 덮도록 배치될 수 있다. 이와 유사하게, 제2 상부전극(80b)은 제2 패드전극(70b)의 상부에 위치하며 제2 패드전극(70b)에 전기적으로 연결될 수 있다. 따라서 제2 상부전극(80b)은 제2 패드전극(70b)을 덮도록 배치될 수 있다.

- [0033] 또 다른 구체예에서 제1 상부전극(80a)은 제1 발광부(101) 상부와 제2 발광부(102) 상부에서 제1 패드전극(70 a)의 상부에 위치하도록 배치될 수 있다. 이와 유사하게 제2 상부전극(80b)은 제3 발광부(103) 상부와 제4 발광부(104) 상부에서 제2 패드전극(70b)의 상부에 위치하도록 배치될 수 있다.

- [0034] 또 다른 구체예에서, 본 발명에 따른 반도체 발광소자에 있어서 제1 발광부(101) 상부와 제2 발광부(102) 상부 각각에 형성된 전극연결부(81)에 의해 제1 상부전극(80a)과 제1 패드전극(70a)이 전기적으로 연결될 수 있다. 이와 유사하게 제3 발광부(103) 상부와 제4 발광부(104) 상부 각각에 형성된 전극연결부(81)에 의해 제2 상부전 극(80b)과 제2 패드전극(70b)이 전기적으로 연결될 수 있다.

- [0035] 도 5 및 도 6을 참조하여 더욱 상세하게 설명하면, 제1 패드전극(70a)이 제1 발광부(101) 및 제2 발광부(102)를 함께 덮도록 배치되는 경우, 제1 패드전극(70a)의 상부에 위치하는 제1 상부전극(80a)은 제1 발광부(101) 및 제2 발광부(102) 각각의 상부에서 제1 패드전극(70a)과 전기적으로 연결되도록 구성될 수 있다. 도 5 및 도 6을 참조하면 제1 상부전극(80a)과 제1 패드전극(70a)은 제1 발광부(101) 및 제2 발광부(102) 각각의 상부에서 제1 전극연결부(81a)에 의해 전기적으로 연결될 수 있다.

- [0036] 이와 유사하게 제2 패드전극(70b)이 제3 발광부(103) 및 제4 발광부(104)를 함께 덮도록 배치되는 경우, 제2 패드전극(70b)의 상부에 위치하는 제2 상부전극(80b)은 제3 발광부(103) 및 제4 발광부(104) 각각의 상부의 제2 패드전극(70b)과 전기적으로 연결되도록 구성될 수 있다. 도 5 및 도 6을 참조하면 제2 상부전극(80b)과 제2 패드전극(70b)은 제3 발광부(103) 및 제4 발광부(104) 각각의 상부에서 제2 전극연결부(81b)에 의해 전기적으로 연결될 수 있다.

- [0037] 본 발명에 따른 반도체 발광소자는 제1 발광부(101)와 제2 발광부(102)를 전기적으로 연결하는 제1 연결전극 (92)을 더욱 포함할 수 있다. 제1 연결전극(92)은 제3 발광부(103)와 제4 발광부(104)를 전기적으로 연결하는 제1 연결전극(92)을 의미할 수도 있다.

- [0038] 도 5 및 도 6을 참조하면, 제1 연결전극(92)은 제1 하부연결부(92a), 제1 수평연결부(92c), 및 제2 하부연결부 (92b)를 포함할 수 있다.

- [0039] 제1 수평연결부(92c)는 제1 발광부(101) 상부와 제2 발광부(102) 상부에 걸쳐서 배치되며, 제1 하부연결부(92 a)는 제1 수평연결부(92c)의 일단을 제1 발광부(101)의 제2 반도체층(50)과 전기적으로 연결하며, 제2 하부연결부(92b)는 제1 수평연결부(92c)의 타단을 제2 발광부(102)의 제1 반도체층(30)과 전기적으로 연결할 수 있다.

- [0040] 한편, 제1 발광부(101)와 제2 발광부(102) 사이에 절연층(35)이 형성되는 경우 제1 하부연결부(92a) 및 제2 하 부연결부(92b)는 절연층(35)을 관통하여 각각 제1 발광부(101)의 제2 반도체층(50)과 제2 발광부(102)의 제1 반 도체층(30)에 전기적으로 연통될 수 있다.

- [0041] 또 다른 구체예에서 제1 수평연결부(92c)와 제1 패드전극(70a)은 동일 높이의 층에 형성될 수 있다.

- [0042] 또 다른 구체예에 따르는 반도체 발광소자에서, 제1 패드전극(70a)은 제1 발광부(101) 및 제2 발광부(102) 각각 의 상부의 가운데 영역을 가로질러 배치되어 제1 발광부(101)와 제2 발광부(102)를 함께 덮도록 배치되며, 제1 수평연결부(92c)는 제1 패드전극(70a)과 이격되어 배치되되 제1 발광부(101) 및 제2 발광부(102) 각각의 상부의 좌측 가장자리 및/또는 우측 가장자리를 따라 배치될 수 있다.

- [0043] 도 5 및 도 6을 참조하여 더욱 상세하게 설명하면, 제1 패드전극(70a)은 제1 발광부(101) 및 제2 발광부(102) 각각의 상부의 가운데 영역을 가로질러 배치되어 제1 발광부(101) 및 제2 발광부(102)를 함께 덮도록 배치될 수 있다. 이러한 경우 제1 수평연결부(92c)는 제1 패드전극(70a)과 이격되어 배치되되 제1 발광부(101) 및 제2 발 광부(102) 각각의 상부의 좌우 가장자리 및/또는 우측 가장자리를 따라(즉 짧은 변을 따라) 배치되어 제1 발광부(101)와 제2 발광부(102)를 전기적으로 연결할 수 있다.

- [0044] 이와 유사하게 제2 패드전극(70b)은 제3 발광부(103) 및 제4 발광부(104) 각각의 상부의 가운데 영역을 가로질 러 배치되어 제3 발광부(103) 및 제4 발광부(104)를 함께 덮도록 배치될 수 있다. 이러한 경우 제1 수평연결부(92c)는 제2 패드전극(70b)과 이격되어 배치되되 제3 발광부(103) 및 제4 발광부(104) 각각의 상부의 좌우 가장 자리 및/또는 우측 가장자리를 따라(즉 짧은 변을 따라) 배치되어 제3 발광부(103)와 제4 발광부(104)를 전기적으로 연결할 수 있다.

- [0045] 한편 제1 연결전극(92)의 제1 수평연결부(92c)는 패드전극(70)이 형성되는 층과 동일 높이의 층에 형성될 수 있다. 따라서 패드전극(70)이 제1 발광부(101)와 제2 발광부(102)를 함께 덮도록 배치되는 경우, 제1 연결전극(92)의 제1 수평연결부(92c)는 패드전극(70)이 형성되는 층과 동일 높이의 층에 형성되어 제1 발광부(101)와 제2 발광부(102)를 전기적으로 연결하도록 배치될 수 있다. 따라서 제1 연결전극(92)의 제1 수평연결부(92c)와 패드전극(70)은 동일 높이의 층에서는 상호 전기적으로 절연되어 형성되며, 서로 겹쳐지지 않게 배치될 수 있다.

- [0046] 본 발명의 또 다른 구체예에 따르는 반도체 발광소자에서, 제1 발광부(101)의 제2 반도체층(50)에 제2 반도체층 (50)의 수평 방향으로 제1 가지전극(75a)이 형성될 수 있다. 이와 유사하게 제2 발광부(102)의 제1 반도체층 (30)에 제1 반도체층(30)의 수평 방향으로 제2 가지전극(75b)이 형성될 수 있다.

- [0047] 바람직한 구체예에서, 제1 가지전극(75a) 및/또는 제2 가지전극(75b)은 제1 패드전극(70a) 및 제1 상부전극 (80a)에 의해 덮히도록 배치되는 것이 바람직하다.

- [0048] 도 5 및 도 6을 참조하면, 제1 하부연결부(92a)의 하단에는 제2 반도체층(50) 상부에서 제1 가지전극(75a)이 형성될 수 있으며, 제2 하부연결부(92b)의 하단에는 제1 반도체층(30) 상부에서 제2 가지전극(75b)이 형성될 수 있다.

- [0049] 바람직한 구체예에서, 제1 연결전극(92)의 제1 수평연결부(92c)가 발광부 각각의 좌우측 가장자리를 따라(즉 짧은 변을 따라) 형성되는 경우 제2 가지전극(75b)은 발광부 각각의 좌우측 가장자리를 따라 형성된 제1 연결전극(92)의 제2 하부연결부(92b)를 서로 연결하도록 형성될 수도 있다.

- [0050] 또 다른 구체예에 따른 반도체 발광소자에 있어서, 제2 발광부(102)와 제3 발광부(103)를 연결하는 제2 연결전 극(92')을 더욱 포함할 수 있다. 제2 연결전극(92')은 제1a 하부연결부(92a'), 제2 수평연결부(92c'), 및 제2a 하부연결부(92b')를 포함할 수 있다.

- [0051] 제2 수평연결부(92c')는 제2 발광부(102) 상부와 제3 발광부(103) 상부에 걸쳐서 배치되며, 제1a 하부연결부 (92a')는 제2 수평연결부(92c')의 일단을 제2 발광부(102)의 제2 반도체층(50)과 전기적으로 연결하며, 제2a 하부연결부(92b')는 제2 수평연결부(92c')의 타단을 제3 발광부(103)의 제1 반도체층(30)과 전기적으로 연결할 수 있다.

- [0052] 제2 수평연결부(92c')는 제1 패드전극(70a)이 덮지 않는 제2 발광부(102)의 상부에서 제1 패드전극(70a)과 동일 높이의 층에서 형성될 수 있다.

- [0053] 또한 제2 수평연결부(92c')는 제2 패드전극(70b)이 덮지 않는 제3 발광부(103)의 상부에서 제2 패드전극(70b)과 동일 높이의 층에서 형성될 수 있다.

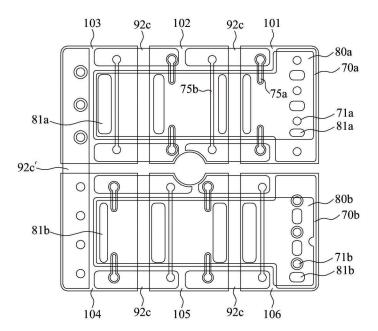

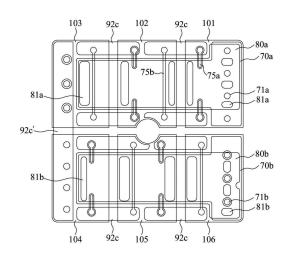

- [0054] 도 7은 본 발명의 하나의 구체예에 따르는 반도체 발광소자의 평면도를 개략적으로 제시한 도면이다.

- [0055] 도 7에 제시된 본 발명의 하나의 구체에에 따른 반도체 발광소자는 기판 위에 서로 떨어져 형성된 제1, 제2, 및 제3 발광부(101, 102, 103)를 포함하는 제1 발광부 어레이, 기판 위에 서로 떨어져 형성된 제4, 제5, 제6 발광부(104, 105, 106)를 포함하는 제2 발광부 어레이, 제1 발광부(101)에 전기적으로 연결된 제1 패드전극(70a), 제6 발광부(106)에 전기적으로 연결된 제2 패드전극(70b), 제1 패드전극(70a) 상부에 위치하며 제1 패드전극(70a)에 전기적으로 연결된 제1 상부전극(80a), 및 제2 패드전극(70b) 상부에 위치하며 제2 패드전극(70b)에 전기적으로 연결된 제2 상부전극(80b)을 포함할 수 있다.

- [0056] 다른 구성요소에 대한 설명은 도 5 및 도 6에 도시된 구성요소의 설명과 동일하며, 다만 제3 발광부(103)와 제4 발광부(104)를 연결하는 제2 연결전극(92')을 더욱 포함할 수 있다. 제2 연결전극(92')은 제1a 하부연결부(92a'), 제2 수평연결부(92c'), 및 제2a 하부연결부(92b')를 포함할 수 있다. 도 7에서는 하부연결부가 도시되어 있지 않다.

- [0057] 제2 수평연결부(92c')는 제3 발광부(103) 상부와 제4 발광부(104) 상부에 걸쳐서 배치되며, 제1a 하부연결부 (92a')는 제2 수평연결부(92c')의 일단을 제3 발광부(103)의 제2 반도체층(50)과 전기적으로 연결하며, 제2a 하부연결부(92b')는 제2 수평연결부(92c')의 타단을 제4 발광부(104)의 제1 반도체층(30)과 전기적으로 연결할 수 있다.

- [0058] 제2 수평연결부(92c')는 제1 패드전극(70a)이 덮지 않는 제3 발광부(103)의 상부에서 제1 패드전극(70a)과 동일 높이의 층에서 형성될 수 있다.

- [0059] 또한 제2 수평연결부(92c')는 제2 패드전극(70b)이 덮지 않는 제4 발광부(104)의 상부에서 제2 패드전극(70b)과 동일 높이의 층에서 형성될 수 있다.

- [0060] 이하, 3쪽 질화물 반도체 발광소자를 예로 하여 본 발명의 하나의 구체예에 따른 반도체 발광소자의 제조 방법을 설명한다.

- [0061] 먼저 기판(10) 위에 복수의 반도체층(30,40,50)을 형성하고, 메사식각 등의 방법으로 각 발광부별로 분리 (isolation)한다. 본 실시예에서, 반도체 발광소자는 제1 내지 제4 발광부(101,102,103,104)를 포함한다. 물론 발광부의 개수는 변경될 수 있으며, 3개의 발광부 또는 5개 이상의 발광부를 구비하는 것도 가능하다.

- [0062] 각 발광부는 복수의 반도체충(30,40,50)의 주변이 제거(예: 메사식각)되어 트렌치(trench)가 형성되며, 따라서 각 발광부는 자체로는 서로 전기적으로 분리(isolation) 또는 절연되어 있다. 본 실시예에서, 위에서 볼 때, 각 발광부는 대략 사각형 형상일 수 있으며, 한 변이 서로 마주하도록 형성될 수 있다. 본 실시예에서 서로 마주하는 한 쌍의 변(긴 변)을 연결하는 나머지 한 쌍의 변(짧은 변)은 서로 마주하는 한 쌍의 변들보다 길이가 더 짧게 형성되어 있다.

- [0063] 계속해서, 복수의 발광부 사이에 절연층(35)을 형성한다. 본 실시예에서 절연층(35)은 제1 연결전극(92)의 제1 수평연결부(92c) 아래에 형성될 수 있다. 절연층(35)은 투광성을 가지는 패시베이션(passivation)층으로서, SiO<sub>2</sub>, TiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>와 같은 물질로 바람직하게는 서로 마주하는 복수의 발광부 사이 전체에 형성된다. 복수의 발광부 사이가 좁은 경우 복수의 발광부를 직렬연결하여 high-voltage로 동작하는 반도체 발광소자에서는 본 예와 같이 절연층(35)을 형성하는 것이 전기적 절연 측면에서 유리한 점이 많다. 또한, 바람직하게는, 절연층(35)은 복수의 발광부의 테두리의 노출된 기판(10)까지 형성되어 전기적 절연의 신뢰성을 더 향상하고, 후술될 절연성 반사층(R) 형성시 단차 또는 높이차를 완화하거나 균일하게 하는 데에 도움을 줄 수 있다.

- [0064] 후술될 가지전극(75) 및 오믹전극(72)이 제2 반도체층(50) 위에 형성될 수 있으며, 이들의 아래에 빛을 반사하

는 또는 전류를 바로 아래로 흐르지 못하게 하는 광흡수 방지막을 형성하는 것이 바람직하다. 본 실시예에서, 절연층(35)이 연장되어 있어서 광흡수 방지막 기능도 할 수 있다.

- [0065] 다음으로, 절연층(35)이 형성된 이후 바람직하게는 제2 반도체층(50) 위에 전류 확산 도전막이 형성될 수 있다. p형 GaN의 경우에 전류 확산 능력이 떨어지며, p형 반도체층(50)이 GaN으로 이루어지는 경우에, 대부분 전류 확산 도전막의 도움을 받아야 한다. 예를 들어, ITO, Ni/Au와 같은 물질이 전류 확산 도전막으로 사용될 수 있다.

- [0066] 계속해서, 제1 연결전극(92), 가지전극(75), 및 오믹전극(72)이 형성된다.

- [0067] 복수의 제1 연결전극(92)의 형성 방식은 동일하므로, 제1 발광부(101)와 제2 발광부(102)를 연결하는 제1 연결 전극(92)을 중심으로 설명한다. 제1 연결전극(92)은 제1 하부연결부(92a), 제1 수평연결부(92c), 및 제2 하부연 결부(92b)를 포함한다.

- [0068] 절연층(35)에 개구를 형성한 다음 개구에 제1 하부연결부(92a)를 형성하며, 절연층(35), 제2 반도체층(50) 및 활성층(40)에 개구를 형성한 다음 개구에 제2 하부연결부(92b)를 형성한다. 제1 수평연결부(92c)는 제1 발광부 (101)의 상부와 제2 발광부(102)의 상부에 걸쳐서 배치되도록 절연층(35) 위에 형성된다. 이에 따라 제1 하부연 결부(92a)는 절연층(35)을 관통하여 제1 수평연결부(92c)를 제1 발광부(101)의 제1 반도체층(30)과 전기적으로 연결하며, 제2 하부연결부(92b)는 절연층(35), 제2 반도체층(50) 및 활성층(40)을 관통하여 제1 수평연결부(92c)를 제2 발광부(102)의 제2 반도체층(50)과 전기적으로 연결하도록 형성된다. 한편 제1 연결전극(92)의 제1 수평연결부(92c)는 후술하는 패드전극(70)이 형성되는 층과 동일 높이의 층에 형성될 수 있다.

- [0069] 한편 제1 연결전극(92)의 제1 수평연결부(92c)는 제1 발광부(101) 및 제2 발광부(102)가 연결되는 길이 방향에서 제1 발광부(101) 및 제2 발광부(102) 각각의 좌우측 가장자리를 따라(즉 짧은 변을 따라) 그리고 후술하는 제1 패드전극(70a)과 동일 높이의 층에 형성되어 제1 발광부(101) 및 제2 발광부(102)를 전기적으로 연결할 수 있다.

- [0070] 한편 도 5를 참조하면, 제3 발광부(103)와 제4 발광부(104)는 제2 연결전극(92')에 의해 전기적으로 연결될 수 있다. 제3 발광부(103)와 제4 발광부(104)를 전기적으로 연결하는 제2 연결전극(92')의 제2 제1 수평연결부 (92c)는 제1 패드전극(70a) 및 제2 패드전극(70b)이 덮이지 않은 제3 발광부(103)와 제4 발광부(104) 각각의 긴 변을 따라 그리고 제1 패드전극(70a) 및 제2 패드전극(70b)과 동일 높이의 층에서 형성될 수 있다.

- [0071] 한편 제1 연결전극(92)의 제1 하부연결부(92a) 및 제2 하부연결부(92b) 각각의 하단에는 가지전극(75)이 형성된다. 즉 제1 발광부(101)와 제2 발광부(102)를 예로 설명하면, 제1 하부연결부(92a)의 하단에는 제2 반도체층(50) 상부에서 제1 가지전극(75a)이 형성되며, 제2 하부연결부(92b)의 하단에는 제1 반도체층(30) 상부에서 제2 가지전극(75b)이 형성된다.

- [0072] 또 다른 구체예에서, 제1 연결전극(92)의 제1 수평연결부(92c)가 발광부 각각의 좌우측 가장자리를 따라(즉 짧은 변을 따라) 형성되며, 이 경우 제2 가지전극(75b)은 발광부 각각의 좌우측 가장자리를 따라 형성된 제1 연결 전극(92)의 제2 하부연결부(92b)를 서로 연결하도록 형성된다.

- [0073] 또 다른 구체예에서, 제1 및 제2 가지전극(75a, 75b)은 적어도 일부가 후술하는 패드전극(70) 및 상부전극에 의해 덮히도록 형성될 수 있다. 바람직한 구체예에서, 제1 및 제2 가지전극(75a, 75b)은 패드전극(70) 및 상부전 극(80)의 수직 아래에 위치하도록 배치될 수 있다.

- [0074] 다음으로 제1 연결전극(92)의 제1 수평연결부(92c)와 동일한 높이의 층에 패드전극(70)을 형성한다. 제1 발광부 (101)의 절연층(35), 제2 반도체층(50) 및 활성층(40)에 개구를 형성하고 개구에 제1 전기적 연결부(71a)를 형성하며, 제4 발광부(104)의 절연층(35)에 개구를 형성하고 개구에 제2 전기적 연결부(71b)를 형성한다. 이에 따라 제1 패드전극(70a)은 제1 발광부(101)의 절연층(35), 제2 반도체층(50) 및 활성층(40)을 관통하는 제1 전기적 연결부(71a)에 의해 제1 발광부(101)의 제1 반도체층(30)과 전기적으로 연통될 수 있다. 한편 제2 패드전극 (70b)은 절연층(35)을 관통하는 제2 전기적 연결부(71b)에 의해 제4 발광부(104)의 제2 반도체층(50)과 전기적으로 연통될 수 있다.

- [0075] 여기서 제1 반도체층(30) 및 제2 반도체층(50)의 상부에 오믹전극(72)이 형성되고 오믹전극(72)에 각각 제1 전 기적 연결부(71a)와 제2 전기적 연결부(71b)가 연결된다. 오믹전극(72)은 생략될 수 있지만, 접촉저항을 감소하고 전기적 연결의 안정성을 위해 구비되는 것이 바람직하다.

- [0076] 한편 제1 패드전극(70a)이 전기적으로 연결된 제1 발광부(101) 및 제2 발광부(102)를 함께 덮고, 제2 패드전극

(70b)이 전기적으로 연결된 제3 발광부(103) 및 제4 발광부(104)를 함께 덮도록 배치된다.

- [0077] 여기서 제1 연결전극(92)의 제1 수평연결부(92c)와 패드전극(70)은 동일 높이의 층에서는 상호 전기적으로 절연되어 형성되며, 서로 겹쳐지지 않게 배치된다.

- [0078] 또한 제1 패드전극(70a)은 제1 발광부(101) 및 제2 발광부(102) 각각의 상부의 가운데 영역을 가로질러 배치되어 제1 발광부(101) 및 제2 발광부(102)를 함께 덮도록 배치되고, 이때 제1 연결전극(92)의 제1 수평연결부 (92c)는 제1 발광부(101) 및 제2 발광부(102)가 전기적으로 연결되는 길이 방향에서 제1 발광부(101) 및 제2 발광부(102)가 전기적으로 연결되는 길이 방향에서 제1 발광부(101) 및 제2 발광부(102)를 전기적으로 연결할 수 있다. 이와 유사하게 제2 패드전극(70a) 형에 형성되어 제1 발광부(101) 및 제2 발광부(102)를 전기적으로 연결할 수 있다. 이와 유사하게 제2 패드전극(70b)은 제3 발광부(103) 및 제4 발광부(104) 각각의 상부의 가운데 영역을 가로질러 배치되어 제3 발광부(103)(104) 및 제4 발광부(104)가 전기적으로 연결되는 길이 방향에서 제3 발광부(103) 및 제4 발광부(104) 각 각의 좌우측 가장자리를 따라(즉 짧은 변을 따라) 그리고 제2 패드전극(70b)과 동일 높이의 층에 형성되어 제3 발광부(103) 및 제4 발광부(104)를 전기적으로 연결할 수 있다.

- [0079] 다음으로 복수의 발광부, 절연층(35), 제1 연결전극(92)의 제1 수평연결부(92c), 및 패드전극(70)을 덮도록 절 연성 반사층(R)이 형성된다.

- [0080] 절연성 반사층(R)은 활성층(40)으로부터의 빛을 기판(10) 측으로 반사한다. 본 실시예에서 절연성 반사층(R)은 금속 반사막에 의한 광흡수 감소를 위해 절연성 물질로 형성되며, 단일층으로 형성될 수도 있지만, 바람직하게 는 DBR(Distributed Bragg Reflector) 또는 ODR(Omni-Directional Reflector)을 포함하는 다층 구조일 수 있다. 예를 들어, 절연성 반사층(R)은 순차로 적층된 유전체막, DBR, 및 클래드막을 포함할 수 있다.

- [0081] 절연성 반사층(R) 아래의 구조물들, 예를 들어, 복수의 발광부 사이와 주변과의 높이차, 제1 연결전극(92), 가지전극(75), 오믹전극(72) 등으로 인한 요철 구조 등으로 인해 절연성 반사층(R) 형성시 더욱 주의가 필요하다. 예를 들어, 절연성 반사층(R)이 분포 브래그 리플렉터(DBR)를 구비하는 다층 구조인 경우, 절연성 반사층(R)이 잘 기능하기 위해서는 각 물질층이 특별히 설계된 두께로 잘 형성되어야 한다. 예를 들어, 분포 브래그 리플렉터는 SiO₂/TiO₂, SiO₂/Ta₂O₂, 또는 SiO₂/HfO의 반복 적층으로 이루어 질 수 있으며, Blue 빛에 대해서는 SiO₂/TiO₂가 반사효율이 좋고, UV 빛에 대해서는 SiO₂/Ta₂O₂, 또는 SiO₂/HfO가 반사효율이 좋을 수 있다. 분포 브래그 리플렉터는 물리 증착법(PVD; Physical Vapor Deposition), 그 중에서도 전자선 증착법(E-Beam Evaporation) 또는, 스퍼터링법(Sputtering) 또는 열 증착법(Thermal Evaporation)에 의해 형성하는 것이 바람 직하다. 정밀성을 요하는 분포 브래그 리플렉터의 중착에 앞서, 일정 두께의 유전체막을 형성함으로써, 분포 브래그 리플렉터를 안정적으로 제조할 수 있게 되며, 빛의 반사에도 도움을 줄 수 있다. 유전체막의 재질은 SiO₂가 적당하며, 그 두께는 일 예로, 0.2μm ~ 1.0μm일 수 있다. 클래드막은 Al₂O₃, SiO₂, SiON, MgF, CaF 등으로 이루 어질 수 있다. 절연성 반사층(R)은 일 예로, 전체 두께가 1 ~ 8μm일 수 있다.

- [0082] 다음으로, 절연성 반사층(R)에 개구를 형성하고, 개구에 전극연결부를 형성하고, 절연성 반사층(R) 위에 제1 상부전극(80a) 및 제2 상부전극(80b)을 형성한다.

- [0083] 여기서 제1 상부전극(80a) 및 제2 상부전극(80b)은 각각 제1 패드전극(70a) 및 제2 패드전극(70b) 각각을 덮도록 배치되고 이들 각각에 제1 전극연결부(81a) 및 제2 전극연결부(81b)에 의해 전기적으로 연결되도록 형성된다. 한편 제1 상부전극(80a) 및 제2 상부전극(80b)은 각각 그 하부에 위치하는 제1 패드전극(70a) 및 제2 패드전극(70b)의 상부에만 위치하도록 배치된다.

- [0084] 또한 제1 패드전극(70a)이 제1 발광부(101) 및 제2 발광부(102)를 함께 덮도록 배치되며, 이때 제1 상부전극 (80a)은 제1 발광부(101) 및 제2 발광부(102) 각각의 상부에서 제1 패드전극(70a)과 제1 전극연결부(81a)에 의해 전기적으로 연결되도록 형성된다. 즉 제1 발광부(101) 및 제2 발광부(102) 각각의 상부의 위치하는 절연성 반사층(R)에 복수의 개구를 형성하고, 각 개구에 제1 전극연결부(81a)를 형성하고, 절연성 반사층(R) 위에 제1 상부전극(80a)을 형성한다.

- [0085] 이와 유사하게, 제2 패드전극(70b)이 제3 발광부(103) 및 제4 발광부(104)를 함께 덮도록 배치되며, 이때 제2 상부전극(80b)은 제3 발광부(103) 및 제4 발광부(104) 각각의 상부에서 제2 패드전극(70b)과 제2 전극연결부(81b)에 의해 전기적으로 연결되도록 형성된다. 즉 제3 발광부(103) 및 제4 발광부(104) 각각의 상부의 위치하는 절연성 반사층(R)에 복수의 개구를 형성하고, 각 개구에 제2 전극연결부(81b)를 형성하고, 절연성 반사층(R)위에 제2 상부전극(80b)을 형성한다.

- [0086] 전극연결부와 상부 전극은 동일 공정에서 함께 형성될 수 있다.

- [0087] 본 실시예에서 반도체 발광소자는 상부 전극이 절연성 반사층(R)을 기준으로 복수의 반도체층(30,40,50)의 반대 측에 구비되는 플립칩(flip chip)으로서, 복수의 발광부가 직렬 연결된 구조를 가진다.

- [0088] 이하 본 개시의 다양한 실시 형태에 대하여 설명한다.

- [0089] (1) 반도체 발광소자에 있어서, 기판 위에 서로 떨어져 형성된 제1 발광부 및 제2 발광부를 포함하는 제1 발광부 어레이; 기판 위에 서로 떨어져 형성된 제3 발광부 및 제4 발광부를 포함하는 제2 발광부 어레이; 제1 발광부에 전기적으로 연결된 제1 패드전극; 제4 발광부에 전기적으로 연결된 제2 패드전극; 제1 패드전극 상부에 위치하며 제1 패드전극에 전기적으로 연결된 제1 상부전극; 및 제2 패드전극 상부에 위치하며 제2 패드전극에 전기적으로 연결된 제2 상부전극;을 포함하며, 제1 발광부 내지 제4 발광부 각각은 제1 도전성을 가지는 제1 반도체충, 제1 도전성과 다른 제2 도전성을 가지는 제2 반도체충, 및 제1 반도체충과 제2 반도체충의 사이에 개재되어 전자와 정공의 재결합에 의해 빛을 생성하는 활성충을 포함하며, 제1 발광부 내지 제4 발광부는 서로 전기적으로 연결되며, 제1 패드전극은 제1 발광부와 제2 발광부를 함께 덮도록 배치되는, 반도체 발광소자.

- [0090] (2) 제1 상부전극은 제1 발광부 상부와 제2 발광부 상부에서 제1 패드전극의 상부에 위치하도록 배치되는, 반도 체 발광소자.

- [0091] (3) 제1 발광부 상부와 제2 발광부 상부 각각에 형성된 전극연결부에 의해 제1 상부전극과 제1 패드전극이 전기적으로 연결되는, 반도체 발광소자.

- [0092] (4) 제1 발광부와 제2 발광부를 전기적으로 연결하는 제1 연결전극을 더욱 포함하고, 제1 연결전극은 제1 하부 연결부, 제1 수평연결부, 및 제2 하부연결부를 포함하며, 제1 수평연결부는 제1 발광부 상부와 제2 발광부 상부에 걸쳐서 배치되며, 제1 하부연결부는 제1 수평연결부의 일단을 제1 발광부의 제2 반도체층과 전기적으로 연결하며, 제2 하부연결부는 제1 수평연결부의 타단을 제2 발광부의 제1 반도체층과 전기적으로 연결하는, 반도체발광소자.

- [0093] (5) 제1 수평연결부와 제1 패드전극은 동일 높이의 층에 형성되는 것을 특징으로 하는, 반도체 발광소자.

- [0094] (6) 제1 패드전극은 제1 발광부 및 제2 발광부 각각의 상부의 가운데 영역을 가로질러 배치되어 제1 발광부와 제2 발광부를 함께 덮도록 배치되며, 제1 수평연결부는 제1 패드전극과 이격되어 배치되되 제1 발광부 및 제2 발광부 각각의 상부의 좌측 가장자리 및/또는 우측 가장자리를 따라 배치되는, 반도체 발광소자.

- [0095] (7) 제1 발광부의 제2 반도체층에 제2 반도체층의 수평 방향으로 제1 가지전극이 형성되거나 및/또는 제2 발광부의 제1 반도체층에 제1 반도체층의 수평 방향으로 제2 가지전극이 형성되며, 제1 가지전극 및/또는 제2 가지전극은 제1 패드전극 및 제1 상부전극에 의해 덮히도록 배치되는, 반도체 발광소자.

- [0096] (8) 제2 발광부와 제3 발광부을 연결하는 제2 연결전극을 더욱 포함하며, 제2 연결전극은 제1a 하부연결부, 제2 수평연결부, 및 제2a 하부연결부를 포함하며, 제2 수평연결부는 제2 발광부 상부와 제3 발광부 상부에 걸쳐서 배치되며, 제1a 하부연결부는 제2 수평연결부의 일단을 제2 발광부의 제2 반도체층과 전기적으로 연결하며, 제2 하부연결부는 제2 수평연결부의 타단을 제3 발광부의 제1 반도체층과 전기적으로 연결하며, 제2 수평연결부는 제1 패드전극이 덮지 않는 제2 발광부의 상부에서 제1 패드전극과 동일 높이의 층에서 형성되는, 반도체 발광소자.

# 부호의 설명

[0097] 제1 내지 제4 발광부(101, 102, 103, 104), 기판(10), 제1 반도체층(30), 절연층(35), 활성층(40), 제2 반도체 층(50), 패드전극(70), 전기적연결부(71), 오믹전극(72), 가지전극(75), 상부전극(80), 전극연결부(81), 제1 연 결전극(92), 절연성반사층(R)

# 도면

# 도면1

# 도면2

# 도면3

# 도면4

# 도면5

# 도면6

# 도면7