# (19) World Intellectual Property Organization International Bureau

# - | 1888 | 1888 | 1888 | 1888 | 1884 | 1884 | 1884 | 1884 | 1885 | 1885 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 | 1886 |

(43) International Publication Date 16 March 2006 (16.03.2006)

# **PCT**

# (10) International Publication Number $WO\ 2006/028421\ A1$

- (51) International Patent Classification<sup>7</sup>: H01L 25/065, 23/02, 23/495, 23/28, 21/56

- (21) International Application Number:

PCT/SG2005/000310

(22) International Filing Date:

9 September 2005 (09.09.2005)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

60/609,199

9 September 2004 (09.09.2004) US

- (71) Applicant (for all designated States except US): UNITED TEST AND ASSEMBLY CENTER (S) PTE LTD [SG/SG]; 52 Serangoon Road Avenue 5, #06-00, Singapore 555853 (SG).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): WANG, Chuen Khiang [SG/SG]; Blk 315C Anchorvale Road #09-180, Singapore 543315 (SG). LIU, Hao [SG/SG]; No. 387 Ang Mo Kio Ave 2, Singapore 567849 (SG). TAN, Hien Boon [MY/SG]; Blk 61 Choa Chu Kang Loop, #12-01, Singapore 689668 (SG). LAW, Teik Lyk, Clifton [MY/SG]; 357C Admiralty Drive, #11-122, Singapore 753357 (SG).

- **BIDIN, Rahamat** [SG/SG]; 10A Jalan Ulu, Singapore 457135 (SG). **SUN, Yi Sheng, Anthony** [—/SG]; 19 Fort Road #07-04, Singapore 439088 (SG).

- (74) Agent: ALLEN & GLEDHILL; One Marina Boulevard #28-00, Singapore 018989 (SG).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

[Continued on next page]

(54) Title: MULTI-DIE IC PACKAGE AND MANUFACTURING METHOD

(57) Abstract: A method for manufacturing integrated circuit packages (100, 200, 300) and a muli-chip integrated circuit package (100, 200, 300) are disclosed. A first die (110) is attached onto a first side of a set of leads of a leadframe (130), an adhesive (350) is applied onto the set of leads at a second side opposite to the first side. A second die (120) is attached onto the adhesive (350). The adhesive fills into the gaps between the leads. The adhesive is then cured. The adhesive attaching the second die fills the a s between the leads so that to avoid formation of internal cavities in the package

####

#### Published:

with international search report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

## **MULTI-DIE IC PACKAGE AND MANUFACTURING METHOD**

#### **FIELD OF INVENTION**

The present invention relates to semiconductor Integrated Circuits (IC) structure and method of manufacturing. In particular, it relates to Integrated Circuits packages having multiple dies and a method of manufacturing of the same.

#### **BACKGROUND OF INVENTION**

ICs having multiple dies or chips made in a single package increase the capacity of the package without substantially increasing the overall size or dimension of the package. In one example, two or more memory chips may be encapsulated in a single package so as to double or increase the memory capacity of the package without doubling or multiplying the physical size / dimension of the package.

One approach is disclosed in US Patent 6,498,391namely, a dual-chip integrated circuit package with unaligned chip arrangement and a method of manufacturing such a package. According to this patent, both chips are mounted to a leadframe simply by an insulative adhesive layer covering the full mounting area of each chip.

Mounting a chip onto a leadframe in the above manner may cause problems. For example, since the adhesive is formed as a layer between the leadframe and each chip, there left voids, gaps and/or cavities between the lead portions, which are sandwiched between the adhesive layers. These voids, gaps and/or cavities, within which air may be trapped, are sources of potential device failure.

In view of the foregoing, it is desirable to provide an Integrated Circuits package structure having stacked dies and method of manufacturing of the same, so that to at least partly overcome the drawbacks mentioned above.

#### SUMMARY

Described herein is a method for of manufacturing integrated circuit packages. The method avoids the drawbacks of conventional methods described above, for example by eliminating the internal cavities / voids, or at least substantially reduces the size thereof, formed in integrated circuit packages by the conventional method. In one aspect, a first die is attached onto a first side of a set of leads of a leadframe, and an adhesive is applied onto the set of leads at a second side opposite to the first side. A second die is attached onto the adhesive. The adhesive fills into the gaps defined by the set of leads. The adhesive is thereafter cured.

In one embodiment, the first die is attached to the first side of the set of leads with a plurality of tape strips. The adhesive further fills the spaces defined by the plurality of tape strips. The adhesive maybe applied at the second side at a first region covering the spaces and a second region covering the plurality of tapes. The adhesive may partially overlap the first region and the second region.

In another embodiment, first die is attached to the set of leads via a single piece of tape, and the single piece of tape separates the adhesive from the first die.

According to a further aspect of the present invention, there is disclosed a multi-chip integrated circuit package, in which a set of leads is disposed in a plane having a first side and an opposite second side, and the set of leads defining a plurality of gaps between each lead. A first die is attached to the set of leads at the first side with a first bond, and a second die is attached to the set of leads at the second side with a second bond. The second bond fills the plurality of gaps.

In one embodiment, the first bond includes a plurality of separated tapes sandwiched between the first die and the set of leads, and the second bond fills the spaces.

In another embodiment, the first bond is a single piece of tape separating the second bond from the first die.

Other aspects and advantages of the present invention will become apparent from the following detailed description, taken in conjunction with the accompanying drawings, illustrating by way of example the inventive concept of the present invention.

#### BRIEF DESCRIPTION OF THE DRAWINGS

These and other aspects and advantages of the present invention will be described in detail with reference to the accompanying drawings, in which:

Fig. 1 is a partial cross sectional of a multi-die IC package according to one embodiment of the present invention.

Fig. 2 is a partial top view of Fig. 1;

Fig. 3 a partial perspective view of Fig. 1;

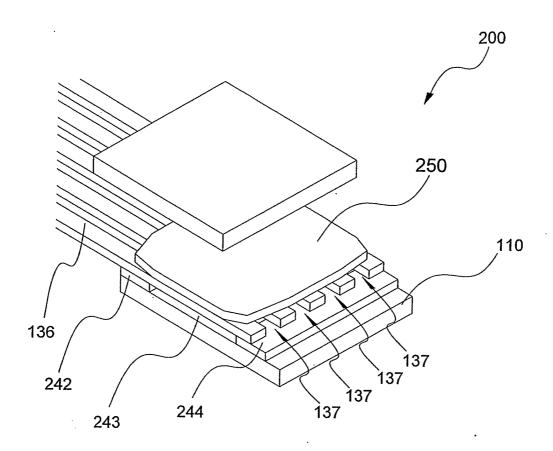

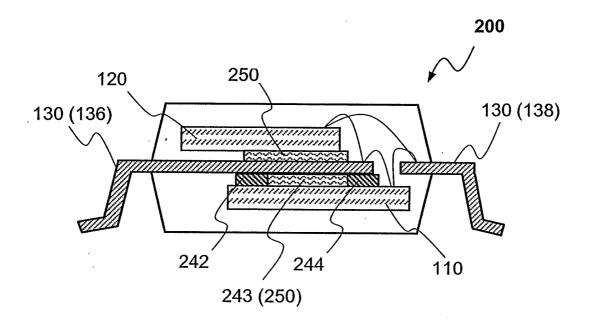

Fig. 4 is a partial perspective view of a multi-die IC package according to another embodiment of the present invention showing a first die attached to the leadframe and prior to attachment of a second die;

Fig. 5 is an enlarged view of Fig. 4;

- 4 -

Fig. 6 is a partial perspective view of Fig. 4 showing adhesive applied to the leadframe for attaching the second die;

- Fig. 7 is a cross sectional view of Fig. 4 showing an encapsulated package;

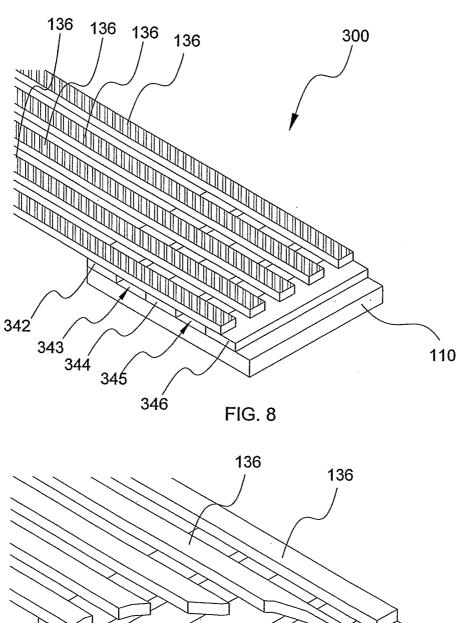

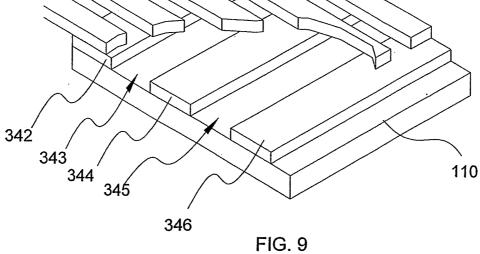

- Fig. 8 is a partial perspective view of a multi-die IC package according to a further embodiment of the present invention showing a first die attached to the leadframe and prior to attachment of a second die;

- Fig. 9 is an enlarged view of Fig. 8;

- Fig. 10 is a partial perspective view of Fig. 8 showing adhesive applied to the leadframe for attaching the second die;

- Fig. 11 is a cross sectional view of Fig. 8 showing an encapsulated package;

- Fig. 12 is a partial cross sectional top view of Fig. 8 showing adhesive dispensed on leads for attaching the second die;

- Fig. 13 is a flowchart showing a method according to an embodiment of the present invention.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

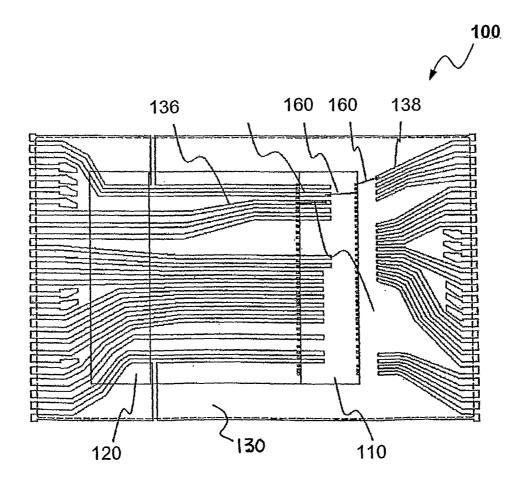

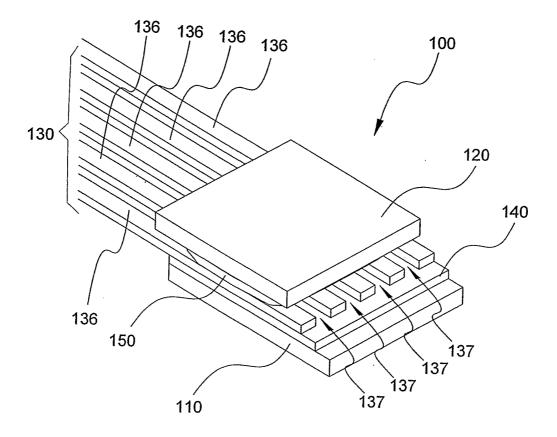

As shown in Figs. 1, 2 and 3, a multi-die IC package 100 according to one embodiment of the present invention has a first die 110, a second die 120 and a plurality of long leads 136 of a leadframe 130 onto which first and second dies 110 and 120 are attached. First die 110 is attached to bottom side 132 of leads 136, via a single piece of tape 140. Second die 120 is attached to top side 134 of leads 136, via an adhesive 150. Wire bonds 160 are formed between first and second dies 110, 120 and long leads 136 and short leads 138.

As shown in Figs. 2 and 3, long leads 136 are disposed spaced apart from each other, defining gaps 137 therebetween. Upon applying adhesive 150, and during attachment of second die 120, adhesive 150 flows to fill gaps 137. Formation of internal cavities is therefore eliminated or, at least the sizes of the internal cavities are substantially reduced in multi-die IC packages.

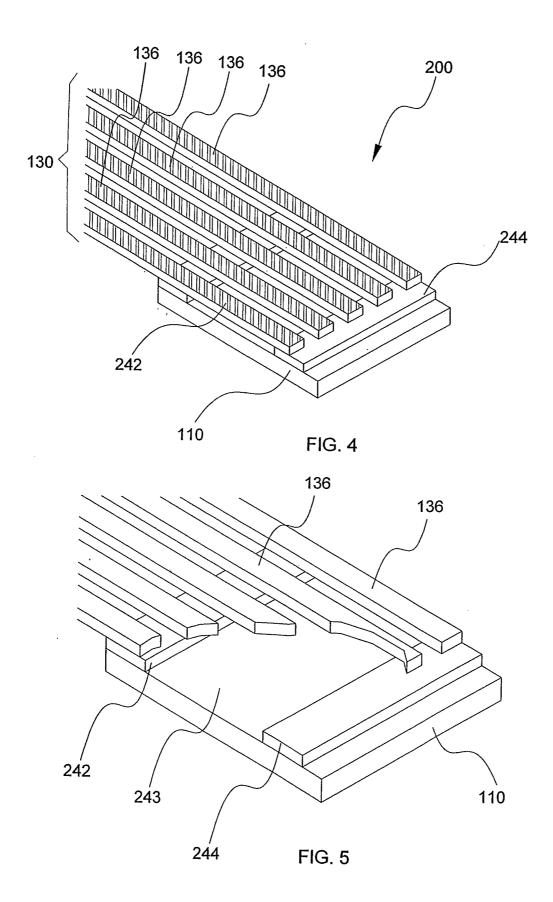

Figs. 4 to 7 show a multi-die IC package 200 according to another embodiment of the present invention. IC package 200 is different from IC package 100 in that, instead of providing a single piece of tape to attach first die to the leads, IC package 200 has two tape strips 242 and 244, disposed spacedapart from each other. Tape strips 242 and 244 therefore define a space 243 therebetween, and both serve the purpose of attaching first die 110 to leads 136.

Upon applying adhesive 250, and/or during attachment of second die 120, adhesive 250 flows to fill gaps 137. Further, adhesive 250 also flows to fill space 243. Internal cavities of the package are therefore avoided or, at least the sizes of the internal cavities are substantially reduced in multi-die IC packages.

During actual production process, leads 136 may not be perfectly disposed within a plane as designed. Using separate tape strips 242 and 244 helps accommodate to the actual uncoplanar situation of the leads, hence eases the process and/or operation to attach the tape strips and first die to leads 136.

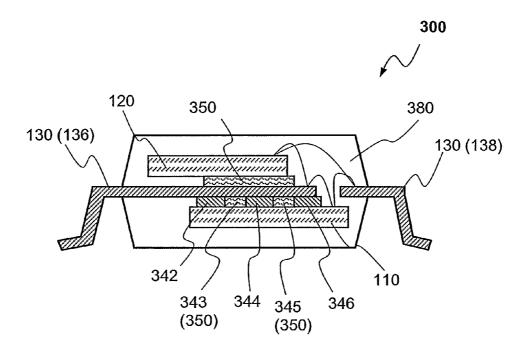

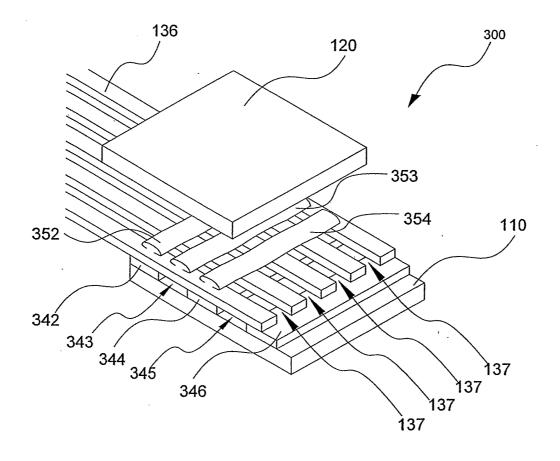

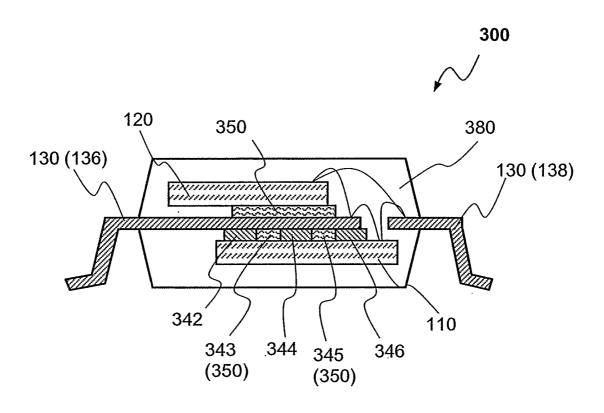

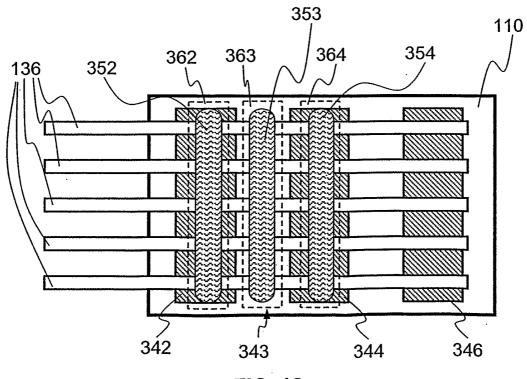

Figs. 8 – 11 show a multi-die IC package 300 according to a further embodiment of the present invention. Fig. 12 shows the package with adhesive dispensed on the leads for attaching the second die. IC package 300 differentiates from IC packages 100 and 200 in that, three tape strips 342, 344 and 346 are disposed spaced-apart from each other, to attach first die 110 to leads 136. Tape strips 342, 344 and 346 therefore define spaces 343 and 345 therebetween.

Adhesive is applied in the form of separate strips 352, 353 and 354, at locations opposite to first tape stripe 342, first space 343 and second tape strip 344, respectively, as shown in Figs. 11 and 12. Adhesive strip 353 may be applied or dispensed within first region 363 which overlaps space 343, adhesive strips 352 and 354 may be applied or dispensed within second region 362, 364 which overlaps tape strips 342 and 344. Adhesive strip 353 may be applied with a volume greater than that of adhesive strips 352 and 354, thus providing a sufficient amount to fill both the gaps 137 and space 343. During attachment of second die 120, adhesive strips 352, 353 and 354 flow to fill gaps 137. Further, adhesive strips 352, 353 and 354 also flow to fill space 343. Internal cavities in the package are therefore avoided or, at least the sizes of the internal cavities are substantially reduced in multi-die IC packages. It should be appreciated that in this embodiment, space 345 will be filled by encapsulant 380 during the subsequent molding / encapsulation process.

Using separate tape strips 342 and 344 helps accommodate to the actual uncoplanar situation of the leads, hence eases the process and/operation to attach the tape strips and first die to leads 136. A multi-die IC package configured according to this embodiment has a further advantage in that since the spaces between the tape stripes are narrowed, by providing three tape strips, dispensing of adhesive strips 352, 353 and 354 becomes easy to control. This eliminates or at least reduces the possibility of contaminating surrounding package areas during adhesive dispensing.

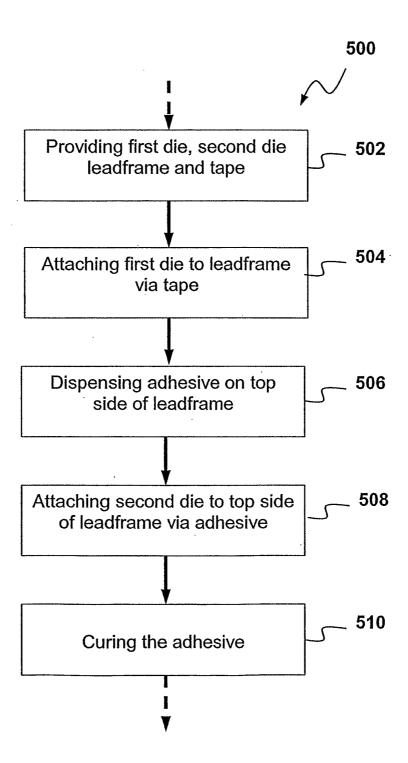

Fig. 13 is a flow chart showing a method of manufacturing integrated circuit packages according an embodiment of the present invention. Under block 502, first and second dies as well as leadframe are provided. First die is then attached to bottom side of leadframe, as shown in block 504, via one or more pieces of tapes. Thereafter, adhesive is applied or dispensed at top side of the leadframe, shown in block 506. The second die is then attached to the adhesive, shown in block 508. During the dispensing and/or second die attachment, the adhesive flows to fill the gaps between the leads. Should two or more tape strips are used,

for example to make devices shown in Figs. 7 and 12, the adhesive also flows into the spaces between the two or more tape strips. As these gaps and/or spaced are filled by the adhesive, fully or at least partly, the internal cavity or void within the package is eliminated, or at least substantially reduced. IC packages formed according to the above method therefore are more reliable that that formed by conventional method.

After the second die is attached, the adhesive is cured so as to form a bond between the first die, the leadframe and the second die, as shown in block 510. The package is now ready to undergo further processes, such as wire bonding, molding/encapsulation, trimming, plating and marking, etc. so as to form the final IC device.

Although embodiments of the present invention have been illustrated in conjunction with the accompanying drawings and described in the foregoing detailed description, it should be appreciated that the invention is not limited to the embodiments disclosed, and is capable of numerous rearrangements, modifications, alternatives and substitutions without departing from the spirit of the invention as set forth and recited by the following claims.

#### **CLAIMS**

- A method of manufacturing integrated circuit packages, comprising:

attaching a first die onto a first side of a set of leads;

applying an adhesive onto the set of leads at a second side opposite to the first side, wherein the adhesive is to fill into gaps defined by the set of leads;

- attaching a second die onto the adhesive; and curing the adhesive.

- 2. The method as recited in claim 1, wherein the first die is attached to the first side of the set of leads with a plurality of tape strips.

- 3. The method as recited in claim 2, wherein the plurality of tape strips define a plurality of spaces, wherein the adhesive fills the spaces.

- 4. The method as recited in claim 3, wherein the adhesive is in contact with the first die.

- 5. The method as recited in claim 2, wherein the adhesive is applied at the second side at a first region overlapping the spaces and a second region overlapping the plurality of tapes.

- 6. The method as recited in claim 5, wherein the adhesive partially covers the first region and the second region.

- 7. The method as recited in claim 1 wherein the first die is attached to the set of leads via a single piece of tape, wherein the single piece of tape separates the adhesive from the first die.

- 8. The method as recited in claim 7, wherein the adhesive is in contact with the single piece of tape.

- 9. An integrated circuit package, comprising:

- a set of leads disposed in a plane having a first side and an opposite second side, the set of leads defining a plurality of gaps between each lead;

- a first die attached to the set of leads at the first side with a first bond;

- a second die attached to the set of leads at the second side with a second bond:

- wherein the second bond is to fill the plurality of gaps.

- 10. The integrated circuit package as recited in claim 9, wherein the first bond comprises a plurality of separated tapes sandwiched between the first die and the set of leads.

- 11. The integrated circuit package as recited in claim 10, wherein the plurality of tapes are separated from each other forming spaces therebetween.

- 12. The integrated circuit package as recited in claim 11, wherein the second bond fills the spaces.

- 13. The integrated circuit package as recited in claim 9, wherein the first bond is a single piece of tape separating the second bond from the first die.

- 14. The integrated circuit package as recited in claim 13, wherein the second bond is in contact with the single piece of tape.

- 15. The integrated circuit package as recited in claim 9, further comprising an encapsulation to cover the first die, the second die and a portion of the leads.

FIG. 1

FIG. 2

FIG. 3

FIG. 6

FIG. 7

FIG. 10

FIG. 11

FIG. 12

FIG. 13

#### INTERNATIONAL SEARCH REPORT

International application No.

PCT/SG2005/000310

#### A. CLASSIFICATION OF SUBJECT MATTER

Int. Cl. 7: H01L 25/065, 23/02, 23/495, 23/28, 21/56

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

DWPI: lead+; adhesive, adher+, glu+, cement+, attach+, bond+, +epoxy, resin?; chip?, die?, dice, multitier,

microchip?, wafer?; cur+, heat+, thermoset+, harden+; fill+, (forc+, push+, flow+)w(between, into); gap? spacing?,

interspac?, space? between; tape?; stack+, packag+ and similar key words;/ic H01L and in particular 25/065

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. |

|-----------|------------------------------------------------------------------------------------|-----------------------|

| 32        | US 4437235 A (MCIVER) 20 March 1984                                                |                       |

| Χ.        | Columns 4-6 and Figure 4                                                           | 1-15                  |

|           | US 5086018 A (CONRU et al.) 4 February 1992                                        |                       |

| X         | Columns 3-5 and Figure 6                                                           | 1-15                  |

|           | US 5572068 A (CHUN) 5 November 1996                                                |                       |

| X         | Whole document                                                                     | 1-15                  |

|           |                                                                                    |                       |

| X         | US 2004/0113280 A1 (KIM) 17 June 2004<br>Pages 1-3                                 |                       |

| Λ         | 1 ages 1-3                                                                         | 1-15                  |

|           | 1 4 5 5 7 5                                                                        |                       |

| X | Further documents are listed in the continuation of Box C  | x          | See patent family annex  |

|---|------------------------------------------------------------|------------|--------------------------|

|   | t di mer decements die fisied in the continuation of box C | ~ <b>x</b> | Dee parent mining armore |

- \* Special categories of cited documents:

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

- later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

- "&" document member of the same patent family

Date of the actual completion of the international search

23 November 2005

Name and mailing address of the ISA/AU

AUSTRALIAN PATENT OFFICE

PO BOX 200, WODEN ACT 2606, AUSTRALIA

E-mail address: pct@ipaustralia.gov.au

Facsimile No. (02) 6285 3929

Date of mailing of the international search report

2 5 NOV 2005

Authorized officer

EVA DE KOOL

Telephone No. (02) 6283 2477

Form PCT/ISA/210 (second sheet) (January 2004)

## INTERNATIONAL SEARCH REPORT

International application No. PCT/SG2005/000310

| Category* | Citation of document, with indication, where appropriate, of the relevant passages            | Relevant to claim No. |  |

|-----------|-----------------------------------------------------------------------------------------------|-----------------------|--|

| X         | US 5689135 A (BALL) 18 November 1997<br>Column 4 and Figure 1                                 | 1-15                  |  |

| X         | US 5677567 A (MA et al.) 14 October 1997<br>Columns 6-7 and Figure 5                          | 1-15                  |  |

| X         | US 5012323 A (FARNWORTH) 30 April 1991<br>Figure 5                                            | 1-15                  |  |

| X         | US 5804874 A (AN et al.) 8 September 1998 Figures 4 and 14                                    | 1-15                  |  |

| A         | US 6498391 B1 (HUANG et al.) 24 December 2002<br>Figure 2                                     |                       |  |

| A         | Patent Abstracts of Japan, JP 06-216313 A (OKI ELECTRIC IND CO LTD) 5 August 1994<br>Abstract |                       |  |

|           |                                                                                               |                       |  |

|           |                                                                                               |                       |  |

|           |                                                                                               |                       |  |

|           |                                                                                               |                       |  |

|           |                                                                                               |                       |  |

|           |                                                                                               |                       |  |

#### INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No.

PCT/SG2005/000310

This Annex lists the known "A" publication level patent family members relating to the patent documents cited in the above-mentioned international search report. The Australian Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

| 1  | Patent Document Cited in<br>Search Report |    |            | Pate | nt Family Member |             |         |

|----|-------------------------------------------|----|------------|------|------------------|-------------|---------|

| US | 4437235                                   | US | 4363076    |      |                  | <del></del> |         |

| US | 5086018                                   | EP | 0513521    | JP   | 5109801          | US          | 5151559 |

| US | 5572068                                   | DE | 4215467    | JP   | 5129517          |             |         |

| US | 2004113280                                | JР | 2004200683 | US   | 6838754          |             |         |

| US | 5689135                                   | AU | 13397/97   | EP   | 0972307          | US          | 5898220 |

|    |                                           | WO | 9722996    |      |                  |             |         |

| US | 5677567                                   | US | 5770480    | US   | 5894165          | US          | 6232148 |

| US | 5012323                                   |    | NONE       |      |                  |             |         |

| US | 5804874                                   | JР | 9246465    |      |                  |             |         |

| US | 6498391                                   | US | 6753206    | US   | 2003057566       | -           |         |

| JP | 6216313                                   |    | NONE       |      |                  |             |         |

Due to data integration issues this family listing may not include 10 digit Australian applications filed since May 2001.

END OF ANNEX