(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4135284号 (P4135284)

(45) 発行日 平成20年8月20日(2008.8.20)

(24) 登録日 平成20年6月13日(2008.6.13)

(51) Int. Cl. F. L.

HO 1 L 25/065 (2006.01)

HO1L 25/07 (2006.01) HO1L 25/18 (2006.01) HO1L 25/08 Z

請求項の数 6 (全 16 頁)

(21) 出願番号 特願平11-348059

(22) 出願日 平成11年12月7日 (1999.12.7) (65) 公開番号 特開2001-168268 (P2001-168268A)

(43) 公開日 平成13年6月22日 (2001.6.22)

審査請求日 平成18年3月15日(2006.3.15)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

|(74)代理人 100094053

弁理士 佐藤 隆久

|(72)発明者 柳田 敏治

東京都品川区北品川6丁目7番35号 ソ

二一株式会社内

審査官 酒井 英夫

最終頁に続く

(54) 【発明の名称】半導体モジュールおよび電子回路装置

### (57)【特許請求の範囲】

# 【請求項1】

実装基板に実装される半導体モジュールであって、

- 一方の面と他方の面との両面に配線部が形成されている可撓性基板と、

- 一方の面が前記可撓性基板の一方の面に対面しており、前記可撓性基板の一方の面に形成された配線部に電極が接続されている第1半導体チップと、

前記可撓性基板の一方の面にて前記第1半導体チップが設けられた位置とは異なる位置 において、一方の面が前記可撓性基板の一方の面に対面しており、前記可撓性基板の一方 の面に形成された配線部に電極が接続されている第2半導体チップと、

前記可撓性基板の他方の面において前記可撓性基板を介して一方の面が前記第1半導体 チップに対面しており、前記可撓性基板の他方の面に形成された配線部に電極が接続され ている第3半導体チップと、

前記可撓性基板の他方の面において前記第3半導体チップを介在するように配置されており、前記可撓性基板の他方の面に形成された配線部に接続されており、前記実装基板に形成された配線に接続される一対の突起電極と

# を有し、

前記可撓性基板は、前記第1半導体チップの他方の面と前記第2半導体チップの他方の面とが互いに対面するように、前記第1半導体チップと前記第2半導体チップとが設けられた部分の間において湾曲されており、前記第1半導体チップおよび前記第2半導体チップの他方の面が対面する間に放熱性基板が配置されており、

<u>前記一対の突起電極は、前記可撓性基板の他方の面において、前記第3半導体チップよりも高さが高くなるように形成されている</u>

半導体モジュール。

### 【請求項2】

前記第3半導体チップは、前記可撓性基板の他方の面において、200µm以下の高さになるように形成されており、

<u>前記一対の突起電極は、前記可撓性基板の他方の面において、300μm以上の高さに</u>なるように形成されている、

請求項1に記載の半導体モジュール。

# 【請求項3】

\_\_前記第1半導体チップおよび第2半導体チップは、絶縁性接着剤によって、前記放熱性 基板に固着されている、

請求項1または2に記載の半導体モジュール。

### 【請求項4】

実装基板と、前記実装基板の面に実装された半導体モジュールとを含む電子回路装置で あって、

前記半導体モジュールは、

- 一方の面と他方の面との両面に配線部が形成されている可撓性基板と、

- 一方の面が前記可撓性基板の一方の面に対面しており、前記可撓性基板の一方の面に形成された配線部に電極が接続されている第1半導体チップと、

前記可撓性基板の一方の面にて前記第1半導体チップが設けられた位置とは異なる位置 において、一方の面が前記可撓性基板の一方の面に対面しており、前記可撓性基板の一方 の面に形成された配線部に電極が接続されている第2半導体チップと、

前記可撓性基板の他方の面において前記可撓性基板を介して一方の面が前記第1半導体 チップに対面しており、前記可撓性基板の他方の面に形成された配線部に電極が接続され ている第3半導体チップと、

前記可撓性基板の他方の面において前記第3半導体チップを介在するように配置されて おり、前記可撓性基板の他方の面に形成された配線部に接続されており、前記実装基板に 形成された配線に接続されている一対の突起電極と

を有し、

前記可撓性基板は、前記第1半導体チップの他方の面と前記第2半導体チップの他方の面とが互いに対面するように、前記第1半導体チップと前記第2半導体チップとが設けられた部分の間において湾曲されており、前記第1半導体チップおよび前記第2半導体チップの他方の面が対面する間に放熱性基板が配置されており、

<u>前記一対の突起電極は、前記可撓性基板の他方の面において、前記第3半導体チップよ</u>りも高さが高くなるように形成されており、

前記第3半導体チップの他方の面と、前記記実装基板の面との間に空間が設けられている

電子回路装置。

### 【請求項5】

\_ 前記第3半導体チップは、前記可撓性基板の他方の面において、200μm以下の高さになるように形成されており、

前記一対の突起電極は、前記可撓性基板の他方の面において、300µm以上の高さになるように形成されている、

請求項4に記載の電子回路装置。

# 【請求項6】

前記第1半導体チップおよび第2半導体チップは、絶縁性接着剤によって、前記放熱性 基板に固着されている、

請求項4または5に記載の電子回路装置。

# 【発明の詳細な説明】

20

10

30

40

### [0001]

# 【発明の属する技術分野】

本発明は半導体モジュールおよび電子回路装置に関し、特に、小型化および高密度化されたパッケージ形態を有する半導体装置をモジュール化した半導体モジュールと、当該半導体モジュールを実装基板上に実装した電子回路装置に関する。

### [00002]

### 【従来の技術】

デジタルビデオカメラ、ICカード、デジタル携帯電話、ノートパソコンあるいはPDA(Personal Digital Assistant)など、携帯用電子機器の小型化、薄型化、軽量化に対する要求は強くなる一方であり、これに応えるために近年のVLSIなどの半導体装置においては3年で7割の縮小化を実現してきた一方で、実装基板上の部品実装密度をいかに向上させるかが重要な課題として研究および開発がなされてきた。

### [0003]

従来、半導体装置のパッケージ形態としては、DIP (Dual In-line Package) あるいは PGA (Pin Grid Array) などのプリント基板に設けたスルーホールにリード線を挿入して実装するリード挿入型 (THD: Through Hole Mount Device ) や、QFP (Quad Flat Package) あるいはTCP (Tape Carrier Package) などのリード線を基板の表面にハンダ付けして実装する表面実装型 (SMD: Surface Mount Device) が用いられてきた。

### [0004]

上記のように装置の小型化および高密度化を進めるために、半導体装置のパッケージ形態は、パッケージサイズを半導体チップの大きさに限りなく近づけたチップサイズパッケージ(CSP: Chip Size Package )と呼ばれるパッケージ形態へと移行し、さらには、はんだや金などからなる突起電極(バンプ)をパッド電極に接続するように設けてCSP化した半導体装置のバンプ形成面側を実装基板に向け、フェースダウンで実装するフリップチップ実装形態へと移行してきている。

さらなる小型化および高密度化のために、パッド電極に接続するように突起電極(バンプ)を設けた半導体チップを、ベアチップ状態でフリップチップ実装する方法が開発され、現在までに活発に研究がなされ、多くの提案が示されている。

# [0005]

上記のベアチップ状態で半導体チップを実装基板に実装した電子回路装置について、図面 を参照して説明する。

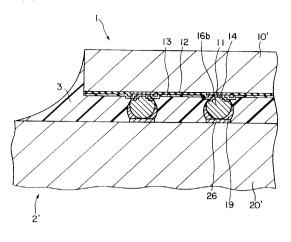

図8は上記のベアチップ実装用の半導体チップの断面図である。

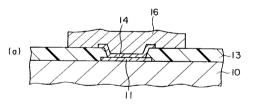

半導体チップ10'のアルミニウムなどからなるパッド電極11形成面は、例えば窒化シリコン層からなる第1表面保護膜12とポリイミド膜からなる第2表面保護膜13が被覆しており、パッド電極11部分が開口しており、この開口部においてクロム、銅、金の積層膜などからなる導電膜14がパッド電極11に接続して形成されている。この導電膜は、BLM(Ball Limitting Metal)膜と呼ばれることがある。

さらに導電膜(BLM膜)14に接続して例えば高融点はんだボールからなるバンプ16bが形成されている。

以上のようにベアチップ実装用の半導体チップ 1 が構成されている。

# [0006]

一方、実装基板 2 'は、例えばガラスエポキシ系材料よりなる実装基板基材 2 0 'の上面において、実装する半導体チップ 1 のバンプ 1 6 b の形成位置に対応する位置に形成された銅などからなるランド(電極)を含み、実装基板基材 2 0 'の表面上あるいは裏面上、もしくは両面上に形成されている配線部 2 6 を有している。配線部 2 6 部分を除く実装基板基材 2 0 '表面は例えば不図示のソルダーレジストにより被覆されている。

### [0007]

上記の半導体チップ1は、バンプ16bとランドを対応させて実装基板2′上にマウントされており、共晶はんだ層19あるいはバンプ16b自身によりバンプ16bとランドとが機械的、電気的に接続されている。

10

20

30

40

10

20

30

50

さらに、半導体チップ1と実装基板2 'の間隙部は、エポキシ樹脂などからなる封止樹脂3 により封止されている。

### [0008]

上記の半導体装置において、はんだバンプを所定の位置に形成する方法としては、例えば電解メッキを用いる方法が知られているが、この場合にはバンプの下地となる材料層の表面状態や電気抵抗のわずかなばらつきにより成膜されるはんだバンプの膜厚が影響を受け、半導体チップ内に均一で高さの揃ったはんだボールバンプを形成することが非常に難しいという問題点を有している。

### [0009]

真空蒸着によるはんだ層の成膜とフォトレジスト膜のリフトオフとを用いて、はんだボールバンプを高さを揃えて形成する方法が開発されている。この方法について、図面を参照 して以下に説明する。

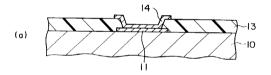

まず、図9(a)に示すように、例えばスパッタリング法やエッチングなどにより半導体チップの回路パターンが形成された半導体ウェーハ10上にアルミニウム - 銅合金などからなるパッド電極11をパターン形成し、その上層に例えば窒化シリコン層あるいはポリイミド膜などからなる表面保護膜13を全面に被覆して形成する。

表面保護膜13のパッド電極11部分を開口した後、例えばスパッタリング法によりクロム、銅、金の積層体である導電膜(BLM膜)14をパッド電極11に接続するようにパターン形成する。

# [0010]

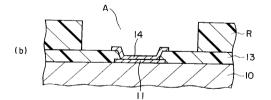

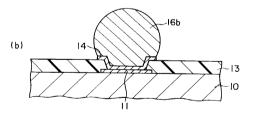

次に、図9(b)に示すように、フォトリソグラフィー工程により、導電膜(BLM膜) 14形成領域にパターン開口部Aを有するレジスト膜Rをパターン形成する。

次に、図9(c)に示すように、例えば真空蒸着法により全面にはんだ層を成膜することで、レジスト膜Rのパターン開口部A内にはんだ層16を形成する。このとき、レジスト膜Rの上層にもはんだ層16aが形成される。

# [0011]

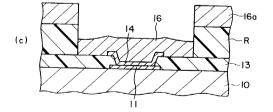

次に、図10(a)に示すように、リフトオフによりレジスト膜Rを除去することで、レジスト膜Rの上層に形成されたはんだ層16aを同時に除去する。これにより、レジスト膜Rのパターン開口部A内に形成されたはんだ層16のみを残すことができる。

次に、図10(b)に示すように、熱処理を行ってはんだ層16を溶融させ、表面張力により球形となった状態で冷却、固化することではんだボールのバンプ16bを形成する。

# [0012]

### 【発明が解決しようとする課題】

しかしながら、上記のような半導体装置を用いたICカード、デジタル携帯電話あるいは P D A などの携帯用電子機器としては、デバイスの実装スペースはできるだけ小型化する ことが望まれており、 2 次元的な縮小に加えて 3 次元的な縮小、即ち薄型化ができるよう な半導体デバイスの高密度な 3 次元実装技術を確立して、より一層の高密度化、高機能化を実現することが切望されている。

# [ 0 0 1 3 ]

上記の半導体デバイスを3次元に実装する技術が、例えば、特開平6-244360号公 40報に開示されている。

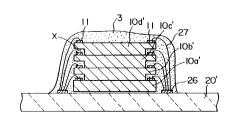

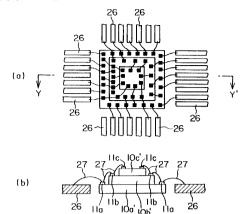

即ち、図11に示すように、実装基板基材20′とその表面に形成された配線部26から構成されている実装基板上に、表面に電極11が形成され、大きさがほぼ等しい4個の半導体チップ(10a′,10b′,10c′,10d′)が、各電極11形成面を上側にして積層されている。上側から3個の各半導体装置には、各半導体チップの周辺部(ペリフェラル領域)に形成された各電極11を露出させるために切欠部×が設けられている。半導体チップの各電極11と実装基板の配線部26とがワイヤボンディング27により接続されており、積層された半導体チップ全体を封止樹脂3が被覆している。

### [0014]

また、同様に半導体デバイスを3次元に実装する技術が、例えば、特開昭60-9475

10

20

30

40

50

6号公報に開示されている。

即ち、図12((a)は平面図であり、(b)は(a)中のY-Y'における断面図)に示すように、表面に電極(11a,11b,11c)が形成された3個の半導体チップ(10a',10b',10c')が、各電極形成面を上側にして積層されている。ここで、3個の各半導体チップは大きさは上側程小さくなっており、これにより各半導体チップの周辺部に形成された各電極が露出している。半導体チップの各電極間、あるいは各電極11とその外周領域に設けられている配線部26とがワイヤボンディング27により接続されている。

# [0015]

しかしながら、上記の半導体デバイスを 3 次元に実装した電子回路装置はワイヤボンディングの引回しのために余分な空間を必要としており、さらに長いワイヤボンディングによるインダクタンスのために高周波デバイスを実装する場合には信号遅延を顕在化させるという問題があった。

さらにまた、半導体デバイスを直接積層させているために放熱が十分でない場合があり、 ロジック系デバイスなどの消費電力の大きなデバイスに適用した場合には発熱量が多いた めに半導体デバイスが高温となってしまい、電気特性に支障を来すことがあるという問題 があった。

### [0016]

本発明は上記の問題を鑑みなされたものであり、本発明は、実装基板への接続部のインダクタンスによる信号遅延の問題を改善でき、各半導体デバイスからの放熱量を確保して半導体デバイスが高温となることを回避することが可能である、複数個の半導体チップを積層してモジュール化した半導体モジュールと、当該半導体モジュールを実装した電子回路装置を提供することを目的とする。

### [0017]

### 【課題を解決するための手段】

上記の目的を達成するため、本発明の半導体モジュールは、両面に配線部を有する可撓性基板と、半導体装置の回路パターンと、前記回路パターンに接続する第1突起電極を有し、前記第1突起電極形成面側から前記配線部に接続するように前記可撓性基板の一方の面上に実装された第1半導体装置および第2半導体装置と、前記第1半導体装置の上面に固着された放熱性基板とを有し、前記第1半導体装置と前記第2半導体装置の実装部分の間における前記可撓性基板が湾曲しており、前記第2半導体装置の上面が前記放熱性基板の前記第1半導体装置固着面の反対側の面に固着されている。

### [0018]

上記の本発明の半導体モジュールは、好適には、前記半導体モジュールを実装基板に実装するために、前記配線部に接続するように第 2 突起電極が形成されている。

### [0019]

上記の本発明の半導体モジュールは、好適には、前記第1半導体装置および前記第2半導体装置がそれぞれ200μm以下の高さである。

# [0020]

上記の本発明の半導体モジュールは、好適には、前記配線部に接続するように前記可撓性 基板の他方の面上に第 3 半導体装置が実装されている。

さらに好適には、前記半導体モジュールを実装基板に実装するために、前記配線部に接続するように第2突起電極が形成されており、前記第1、前記第2および第3半導体装置の高さがそれぞれ200µm以下であり、前記第2突起電極の高さが300µm以上である

# [0021]

上記の本発明の半導体モジュールは、好適には、前記第1および第2半導体装置のそれぞれの上面が、絶縁性接着剤により前記放熱性基板に固着されている。

### [0022]

上記の本発明の半導体モジュールは、半導体装置の回路パターンに接続する第1突起電極

を有する第1半導体装置および第2半導体装置の第1突起電極形成面の反対側の面同士が放熱性基板を介して固着されており、第1半導体装置と第2半導体装置の実装部分の間において湾曲している可撓性基板に形成された配線部に第1半導体装置および第2半導体装置の各第1突起電極が接続して、モジュール化されており、可撓性基板に形成された配線部に第2突起電極が形成されている構成とすることで、モジュール状態で実装基板に実装することができる。

### [0023]

上記の本発明の半導体モジュールによれば、ワイヤボンディングを用いずに実装可能であり、実装基板への接続部のインダクタンスによる信号遅延の問題を改善できる。

また、第1半導体装置および第2半導体装置は放熱性基板を介して積層された形態であり、各半導体デバイスからの放熱量を確保して半導体デバイスが高温となることを回避することが可能である。

#### [0024]

上記の目的を達成するため、本発明の電子回路装置は、両面に第1配線部を有する可撓性基板と、半導体装置の回路パターンと、前記回路パターンに接続する第1突起電極を有し、前記第1突起電極形成面側から前記第1配線部に接続するように前記可撓性基板の一方の面上に実装された第1半導体装置および第2半導体装置と、前記第1半導体装置の上面に固着された放熱性基板とを有し、前記第1半導体装置と前記第2半導体装置の実装部分の間における前記可撓性基板が湾曲しており、前記第2半導体装置の上面が前記放熱性基板の前記第1半導体装置固着面の反対側の面に固着されている半導体モジュールと、第2配線部を有する実装基板とを有し、前記第1配線部と前記第2配線部が接続して、前記半導体モジュールが前記実装基板上に実装されている。

### [0025]

上記の本発明の電子回路装置は、好適には、前記第1配線部と前記第2配線部が第2突起電極により接続されている。

### [0026]

上記の本発明の電子回路装置は、好適には、前記第1半導体装置および前記第2半導体装置がそれぞれ200μm以下の高さである。

# [0027]

上記の本発明の電子回路装置は、好適には、前記第 1 配線部に接続するように前記可撓性 基板の他方の面上に第 3 半導体装置が実装されている。

さらに好適には、前記第1配線部と前記第2配線部が第2突起電極により接続されており、前記第1、前記第2および第3半導体装置の高さがそれぞれ200µm以下であり、前記第2突起電極の高さが300µm以上である。

# [0028]

上記の本発明の電子回路装置は、好適には、前記第1および第2半導体装置のそれぞれの上面が、絶縁性接着剤により前記放熱性基板に固着されている。

### [0029]

上記の本発明の電子回路装置は、半導体装置の回路パターンに接続する第1突起電極を有する第1半導体装置および第2半導体装置の第1突起電極形成面の反対側の面同士が放熱性基板を介して固着されており、第1半導体装置と第2半導体装置の実装部分の間において湾曲している可撓性基板に形成された第1配線部に第1半導体装置および第2半導体装置の各第1突起電極が接続して、モジュール化された半導体モジュールが、可撓性基板に形成された配線部に第2突起電極などにより第2配線部を有する実装基板に実装されている。

# [0030]

上記の本発明の電子回路装置によれば、ワイヤボンディングを用いずに実装しており、実 装基板への接続部のインダクタンスによる信号遅延の問題を改善できる。

また、第1半導体装置および第2半導体装置は放熱性基板を介して積層された形態であり、各半導体デバイスからの放熱量を確保して半導体デバイスが高温となることを回避する

10

20

30

40

ことが可能である。

### [0031]

### 【発明の実施の形態】

以下に、本発明の半導体装置の製造方法の実施の形態について、図面を参照して説明する

#### [0032]

### 第1実施形態

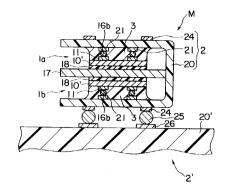

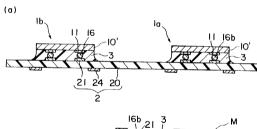

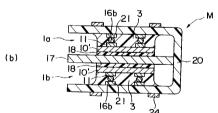

図1は本実施形態に係る電子回路装置の断面図であり、図2は図1に示す電子回路装置におけるベアチップ実装用の半導体チップと可撓性基板との接続部の拡大断面図である。

図2に示すように、半導体チップ10′のアルミニウムなどからなるパッド電極11形成面は、例えば窒化シリコン層からなる第1表面保護膜12とポリイミド膜からなる第2表面保護膜13が被覆しており、パッド電極11部分が開口しており、この開口部においてクロム、銅、金の積層膜などからなる導電膜14がパッド電極11に接続して形成されている。この導電膜は、BLM(Ball Limitting Metal)膜と呼ばれることがある。

さらに導電膜(BLM膜)14に接続して例えば高融点はんだボールからなる第1バンプ (突起電極)16bが形成されている。

以上のようにベアチップ実装用の半導体チップ1(1a,1b)が構成されている。

ここで、半導体チップ1(1a,1b)はそれぞれ200μm以下に薄膜化されている。

### [0033]

上記のベアチップ実装用の半導体チップ(1 a , 1 b ) は、可撓性基板 2 の一方の面(第 1 面)上に実装されている。

可撓性基板 2 は、例えばポリイミドあるいはエポキシ系材料よりなる 5 0  $\mu$  mの膜厚の可撓性基板基材 2 0 の一方の面(第 1 面)上において、実装する半導体チップ(1 a , 1 b )の第 1 バンプ 1 6 b の形成位置に対応する位置に形成された銅などからなるランド(電極)などを含む第 1 面第 1 配線部 2 1 が形成され、さらに可撓性基板基材 2 0 の他方の面(第 2 面)上において、第 1 面第 1 配線部 2 1 に接続する第 2 面第 1 配線部 2 4 が形成されて構成されている。

半導体チップ(1a,1b)は、第1バンプ16bと第1面第1配線部21とが対応するように可撓性基板2上にマウントされ、さらに共晶はんだ層19により第1バンプ16bと第1面第1配線部21とが機械的、電気的に接続されており、さらに、半導体チップ(1a,1b)と可撓性基板2の間隙部は、エポキシ樹脂などからなる封止樹脂3により封止されている。

### [0034]

上記の可撓性基板 2 は半導体チップ(1 a , 1 b )の実装部分の間において湾曲されており、可撓性基板 2 上に実装された半導体チップ(1 a , 1 b )の第 1 バンプ 1 6 b 形成面の反対側の面同士が、銅あるいはクロム鋼など金属材料などからなる放熱性基板 1 7 を挟んで対向するように絶縁性ペーストなどの接着剤層 1 8 により放熱性基板 1 7 に固着されており、以上のようにして 2 個の半導体チップ(1 a , 1 b )を積層させた半導体モジュール M が構成されている。

### [0035]

上記の半導体モジュールMは、第2面第1配線部24に接続するように、はんだボールなどからなり、例えば300μm以上の直径を有する第2バンプ25が形成されており、実装基板基材20′とその表面に形成された第2配線部26から構成される実装基板2′上に、第2バンプ25と第2配線部26とが対応するようにマウントされ、不図示の共晶はんだ層あるいは第2バンプ25自身により第2バンプ25と第2配線部26とが機械的、電気的に接続されている。

### [0036]

上記の本実施形態の電子回路装置によれば、2個の半導体チップ(1a,1b)を積層させたモジュールとして実装基板上にワイヤボンディングを用いずに実装することにより、 デバイスチップ間の配線長を短縮して、実装基板への接続部のインダクタンスを低減して 10

20

30

40

高速処理が可能であり、高周波デバイスにおいても信号遅延の問題を改善できる。

また、2個の半導体チップ(1a,1b)は放熱性基板17を介して積層されており、各 半導体デバイスからの放熱量を確保して半導体デバイスが高温となることを回避すること が可能である。

上記の 2 個の半導体チップ (1 a , 1 b ) は 2 0 0 μ m 以下に薄膜化されているため、上記のようにそれらを積層させた半導体モジュールとしても薄膜化を実現できる。

### [0037]

上記の電子回路装置の製造方法について図面を参照して説明する。

各半導体チップのはんだバンプの形成工程までは、従来方法と同様にして行う。

即ち、まず、図9(a)に示すように、例えばスパッタリング法やエッチングなどにより 半導体チップの回路パターンが形成された半導体ウェーハ10上にアルミニウム - 銅合金 などからなるパッド電極11をパターン形成し、その上層に例えば窒化シリコン層あるい はポリイミド膜などからなる表面保護膜13を全面に被覆して形成する。

表面保護膜13のパッド電極11部分を開口した後、例えばスパッタリング法によりクロム、銅、金の積層体である導電膜(BLM膜)14をパッド電極11に接続するようにパターン形成する。

### [0038]

次に、図9(b)に示すように、フォトリソグラフィー工程により、導電膜(BLM膜) 14形成領域にパターン開口部Aを有するレジスト膜Rをパターン形成する。

次に、図9(c)に示すように、例えば真空蒸着法により全面にはんだ層を成膜することで、レジスト膜Rのパターン開口部A内にはんだ層16を形成する。このとき、レジスト膜Rの上層にもはんだ層16aが形成される。

### [0039]

次に、図10(a)に示すように、リフトオフによりレジスト膜Rを除去することで、レジスト膜Rの上層に形成されたはんだ層16aを同時に除去する。これにより、レジスト膜Rのパターン開口部A内に形成されたはんだ層16のみを残すことができる。

次に、図10(b)に示すように、熱処理を行ってはんだ層16を溶融させ、表面張力により球形となった状態で冷却、固化することで高さが例えば60μmのはんだボールからなる第1バンプ16bを形成する。

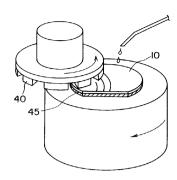

# [0040]

次に、半導体ウェーハ(ウェーハ膜厚は例えば620μm)をデバイス形成面の反対の面から、機械研削法、化学的機械研磨法あるいはエッチング法などにより、膜厚が200μm以下(例えば100μm程度)となるまで半導体ウェーハを薄膜化する。

上記の薄膜化工程としては、まず、上記半導体ウェーハ10の第1バンプ16b形成面の全面に保護テープ45を貼付し、例えば図3に示す研削装置において、装置基台上に保護テープ45貼付面を下にして半導体ウェーハ10を戴置し、例えば、その上側から砥石を2500rpmの回転数で回転させながら、150μm/分の速度で下方へ送り、例えば510μmの膜厚分研削し、110μmの膜厚の半導体ウェーハとする。

このとき、これまでの半導体ウェーハに半導体チップの回路パターンなどを形成する工程 を経ることにより、通常、半導体ウェーハ 1 0 の裏面に形成されてしまっているキズを研 削除去できる。

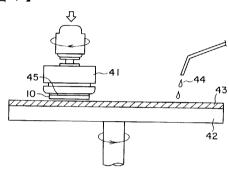

### [0041]

次に、例えば図 4 に示す化学的機械研磨装置において、ウェーハキャリア 4 1 に上記保護テープ 4 5 を貼付した半導体ウェーハ 1 0 を取り付け、例えば、テーブル(定盤) 4 2 上に設けられた研磨布(クロス) 4 3 上に、研磨スラリ 4 4 を 4 0 m 1 / 分の供給速度で供給しながら、研磨圧力 4 0 0 g / c m² で押圧し、ウェーハキャリア 4 1 を 8 0 r p m、テーブルを 8 0 r p mで回転させ、かつ 2 m m / 秒の揺動速度で揺動させ、 1 0  $\mu$  m の膜厚分研磨して裏面ポリッシュ仕上げとし、 1 0 0  $\mu$  m の膜厚の半導体ウェーハ 1 0 とする

このとき、ポリッシュ研磨仕上げとすることで半導体ウェーハ10の裏面の細かなキズ(

20

10

30

40

研削処理時のダメージ)までも除去でき、薄膜化しても機械的強度の高いウェーハとする ことができる。

この後の工程としては、上記半導体ウェーハから表面保護テープを剥離し、ダイシング工程により個々の半導体チップに分離して、本実施形態において実装するベアチップ実装用の半導体チップとする。

上記工程においては、ダイシング工程により個々の半導体チップに分離した後に、上記のように薄膜化することも可能である。

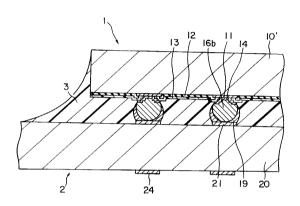

# [0042]

次に、図5(a)に示すように、上記の半導体チップを可撓性基板2上に実装する。

可撓性基板 2 は、例えばポリイミドあるいはエポキシ系材料よりなる 5 0  $\mu$  mの膜厚の可撓性基板基材 2 0 の一方の面(第 1 面)上において、実装する半導体チップ(1 a , 1 b )の第 1 バンプ 1 6 b の形成位置に対応する位置に形成された銅などからなるランド(電極)などを含む第 1 面第 1 配線部 2 1 が形成され、さらに可撓性基板基材 2 0 の他方の面(第 2 面)上において、第 1 面第 1 配線部 2 1 に接続する第 2 面第 1 配線部 2 4 が形成されて構成されている。

上記の第1バンプ16 b と第1配線層21のランドを対応させて半導体チップ(1a,1b)を可撓性基板2上にマウントし、共晶はんだ層(不図示)あるいは第1バンプ自身により第1バンプ16 b と第1配線層21のランドとを機械的、電気的に接続し、さらに、半導体チップ(1a,1b)と可撓性基板2の間隙部を、エポキシ樹脂などからなる封止樹脂3により封止する。

### [0043]

次に、図5(b)に示すように、半導体チップ1bの上面に、銅あるいはクロム鋼など金属材料などからなる放熱性基板17を絶縁性ペーストなどにより固着し、2個の半導体チップ(1a,1b)の実装部分の間における可撓性基板2を湾曲させ、半導体チップ1aの上面を放熱性基板17の半導体チップ1b固着面の反対側の面に、同様に絶縁性ペーストなどにより固着する。

以上で、 2 個の半導体チップ( 1 a , 1 b )を積層させた半導体モジュール M を形成することができる。

以降の工程としては、例えば第2面第1配線部24に接続するように、はんだボールなどからなり、例えば300μm以上の直径を有する第2バンプ25を形成し、実装基板基材20′とその表面に形成された第2配線部26とから構成される実装基板2′上に、第2バンプ25と第2配線部26とを対応させてマウントし、不図示の共晶はんだ層あるいは第2バンプ25自身により第2バンプ25と第2配線部26とを機械的、電気的に接続して、図1に示す電子回路装置を形成することができる。

上記の第2バンプを形成する代わりに、実装基板2 'の第2配線部26上に予めはんだペースト(クリームはんだ)を供給しておき、上記半導体モジュールを戴置してリフローさせることにより同様の構成とすることもできる。

### [0044]

### 第2実施形態

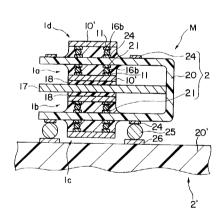

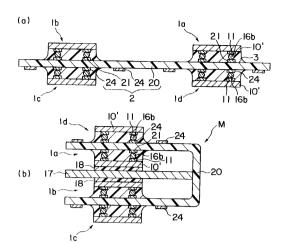

図 6 は本実施形態に係る電子回路装置の断面図である。この電子回路装置におけるベアチップ実装用の半導体チップと可撓性基板との接続部は、第 1 実施形態と同様であり、図 2 にその拡大断面図を示す。

本実施形態に係る電子回路装置は、実質的に第1実施形態の電子回路装置と同様であるが、可撓性基板基材20の一方の面(第1面)上に第1面第1配線部21が形成され、他方の面(第2面)上に第2面第1配線部24が形成された可撓性基板2の上記一方の面(第1面)上に、第1面第1配線部21に接続するように半導体チップ(1a,1b)に対向する位置に、第2面第1配線部24に接続するように半導体チップ(1a,1b)に対向する位置に、第2面第1配線部24に接続するように半導体チップ(1c,1d)が実装されていることが異なる。

上記の半導体チップ(1a,1b,1c,1d)はそれぞれ200μm以下に薄膜化され

10

20

30

40

ている。

### [0045]

上記の半導体チップ(1 c , 1 d ) は、半導体チップ(1 a , 1 b ) と同様に可撓性基板 2 上に実装されている。即ち、半導体チップ(1 c , 1 d ) の第 1 バンプ 1 6 b と第 2 面 第 1 配線部 2 4 とが対応するようにマウントされ、さらに共晶はんだ層(不図示)あるいは第 1 バンプ 1 6 b 自身により第 1 バンプ 1 6 b と第 1 配線部 2 4 とが機械的、電気的に接続されており、さらに、半導体チップ(1 c , 1 d ) と可撓性基板 2 の間隙部は、エポキシ樹脂などからなる封止樹脂 3 により封止されている。

### [0046]

上記の可撓性基板 2 は半導体チップ(1a,1d)と半導体チップ(1b,1c)の実装部分の間において湾曲されており、可撓性基板 2 の一方の面上に実装された半導体チップ(1a,1b)の第1バンプ16b形成面の反対側の面同士が、銅あるいはクロム鋼など金属材料などからなる放熱性基板 1 7 を挟んで対向するように絶縁性ペーストなどの接着剤層 1 8 により放熱性基板 1 7 に固着されている。このとき、可撓性基板 2 の他方の面上に実装された半導体チップ(1c,1d)は、それぞれ、図 6 に示すように最上部および最下部に配置される。

以上のようにして4個の半導体チップ(1a,1b,1c,1d)を積層させた半導体モジュールMが構成されている。

### [0047]

上記の半導体モジュールMは、例えば半導体チップ1cの実装位置の外周部において形成された第2面第1配線部24に接続するように、はんだボールなどからなり、例えば300μm以上の直径を有する第2バンプ25が形成されており、実装基板基材20′とその表面に形成された第2配線部26とから構成される実装基板2′上に、第2バンプ25と第2配線部26とが対応するようにマウントされ、不図示の共晶はんだ層あるいは第2バンプ25自身により第2バンプ25と第2配線部26とが機械的、電気的に接続されて、モジュール形態で実装されている。

### [0048]

上記の本実施形態の電子回路装置によれば、4個の半導体チップ(1a,1b,1c,1d)を積層させたモジュールとして実装基板上にワイヤボンディングを用いずに実装されており、デバイスチップ間の配線長を短縮して、実装基板への接続部のインダクタンスを低減して高速処理が可能であり、高周波デバイスにおいても信号遅延の問題を改善できる

また、4個のうちの2個の半導体チップ(1 a , 1 b ) は放熱性基板17を介して積層されており、他の2個の半導体チップ(1 c , 1 d ) は他の半導体チップと直接接触しておらず、各半導体デバイスからの放熱量を確保して半導体デバイスが高温となることを回避することが可能である。

上記の4個の半導体チップ(1 a , 1 b , 1 c , 1 d ) は 2 0 0 μ m以下に薄膜化されているため、上記のようにそれらを積層させた半導体モジュールとしても薄膜化を実現できる。また、第 2 バンプ 2 5 により半導体モジュールと実装基板の間に生じる空間にも半導体チップ 1 c を実装しており、余分な空間を排除して最小限の高さで効率の良い高密度の3 次元実装を実現できる。

### [0049]

上記の電子回路装置の製造方法について図面を参照して説明する。

各半導体チップの回路パターンを形成した半導体ウェーハにはんだからなる第1バンプ16 b を形成し、膜厚が200μm以下(例えば100μm程度)となるまで薄膜化し、さらにダイシング処理により個々の半導体チップに分割する工程までは、第1実施形態と同様にして行う。

# [0050]

次に、図 7 (a)に示すように、上記の半導体チップを可撓性基板 2 上に実装する。 可撓性基板 2 は、例えばポリイミドあるいはエポキシ系材料よりなる 5 0 μ m の膜厚の可 10

20

30

40

撓性基板基材20の一方の面(第1面)上において、実装する半導体チップ(1a,1b)の第1バンプ16bの形成位置に対応する位置に形成された銅などからなるランド(電極)などを含む第1面第1配線部21が形成され、さらに可撓性基板基材20の他方の面(第2面)上において、実装する半導体チップ(1c,1d)の第1バンプ16bの形成位置に対応する位置に形成された銅などからなるランド(電極)などを含み、第1面第1配線部21に接続する第2面第1配線部24が形成されて構成されている。

半導体チップ(1 a , 1 b ) の第1バンプ16 b と第1面第1配線層21のランドを対応させて、半導体チップ(1 a , 1 b ) を可撓性基板2上にマウントし、共晶はんだ層(不図示) あるいは第1バンプ自身により第1バンプ16 b と第1面第1配線層21のランドとを機械的、電気的に接続し、さらに、半導体チップ(1 a , 1 b ) と可撓性基板2の間隙部を、エポキシ樹脂などからなる封止樹脂3により封止する。

さらに、上記と同様に、半導体チップ(1c,1d)の第1バンプ16bと第2面第1配線層24のランドとを機械的、電気的に接続し、さらに、半導体チップ(1c,1d)と可撓性基板2の間隙部を、エポキシ樹脂などからなる封止樹脂3により封止する。

### [0051]

次に、図7(b)に示すように、半導体チップ1bの上面に、銅あるいはクロム鋼など金属材料などからなる放熱性基板17を絶縁性ペーストなどにより固着し、半導体チップ(1a,1d)と半導体チップ(1b,1c)の実装部分の間における可撓性基板2を湾曲させ、放熱性基板17の半導体チップ1b固着面の反対側の面と半導体チップ1aの上面とを、上記と同様に絶縁性ペーストなどにより固着する。

以上で、 4 個の半導体チップ( 1 a , 1 b , 1 c , 1 d )を積層させた半導体モジュール Mを形成することができる。

# [0052]

本発明により積層して実装する半導体装置としては、MOSトランジスタ系半導体装置、 バイポーラ系半導体装置、BiCMOS系半導体装置、ロジックとメモリを搭載した半導 体装置など、半導体装置であれば何でも適用可能である。

### [0053]

本発明の半導体モジュールおよび電子回路装置は上記の実施の形態に限定されない。 例えば、半導体ウェーハの薄膜化工程など、各プロセスの条件や材料の種類や膜厚などは

上記の半導体モジュールを実装基板上に実装するために、半導体モジュールにはんだボールからなる第 2 バンプを形成しているが、金スタッドバンプ、銅メッキバンプ、異方性導電膜、導電性ペーストなどの種々の接合手段を用いて実装してもよい。

また、例えば第2実施形態において、第2面第1配線部に接続する半導体チップとしては 1個でもよい。

また、半導体ウェーハ上への第1バンプの形成方法としては、真空蒸着により成膜とリフトオフによるパターニングによる方法により説明したが、スクリーン印刷法、電解メッキ法、はんだボール転写法など、種々の方法を用いることができる。

その他、本発明の要旨を逸脱しない範囲で種々の変更が可能である。

上記の実施の形態で説明した内容に限らない。

### [0054]

# 【発明の効果】

上記のように、本発明の半導体モジュールおよびそれを実装した電子回路装置によれば、 ワイヤボンディングを用いずに実装されており、半導体チップ間の配線長を短縮し、実装 10

20

30

40

基板への接続部のインダクタンスを低減して高速処理が可能であり、高周波デバイスにおいても信号遅延の問題を改善でき、各半導体デバイスからの放熱量を確保して半導体デバイスが高温となることを回避することが可能で、さらに各半導体チップを積層させた半導体モジュールとしても薄膜化を実現でき、効率の良い高密度の3次元実装を実現できる。本発明の半導体モジュールを実装して組み立てられる最終的な製品デバイスとして、ICカード、携帯電話あるいはPDAなどの携帯電子機器の更なる高機能化や小型化を実現できる。

### 【図面の簡単な説明】

- 【図1】図1は第1実施形態に係る電子回路装置の断面図である。

- 【図2】図2は第1および第2実施形態に係る電子回路装置における半導体チップと可撓性基板との接続部の拡大断面図である。

- 【図3】図3は研削装置の概略構成を示す斜視図である。

- 【図4】図4は化学的機械研磨装置の概略構成を示す図である。

- 【図5】図5は第1実施形態に係る電子回路装置の製造方法の製造工程を示す断面図であり、(a)は半導体チップを可撓性基板上に実装する工程まで、(b)は放熱性基板の両面上に2個の半導体チップの上面を固着する工程までを示す。

- 【図6】図6は第2実施形態に係る電子回路装置の断面図である。

- 【図7】図7は第2実施形態に係る電子回路装置の製造方法の製造工程を示す断面図であり、(a)は半導体チップを可撓性基板上に実装する工程まで、(b)は放熱性基板の両面上に2個の半導体チップの上面を固着する工程までを示す。

- 【図8】図8は第1従来例に係る電子回路装置の断面図である。

- 【図9】図9は本発明および第1従来例に係る半導体装置の製造方法の製造工程を示す断面図であり、(a)は導電膜(BLM膜)の形成工程まで、(b)はレジスト膜の形成工程まで、(c)ははんだ層の堆積工程までを示す。

- 【図10】図10は図9の続きの工程を示し、(a)はリフトオフによるレジスト膜上のはんだ層の除去工程まで、(b)はリフローによりはんだボールバンプの形成工程までを示す。

- 【図11】図11は第2従来例に係る電子回路装置の断面図である。

- 【図12】図12(a)は第3従来例に係る電子回路装置の平面図であり、(b)は(a)中のY-Y'における断面図である。

### 【符号の説明】

1 (1 a , 1 b , 1 c , 1 d ) …ベアチップ実装用半導体チップ、2 …可撓性基板、2 ′ …実装基板、3 …封止樹脂、10 …半導体ウェーハ、10 ′ (10 a ′ , 10 b ′ , 10 c ′ 10 d ′ ) …半導体チップ、11(11 a , 11 b , 11 c ) …(パッド)電極、12 , 13 …表面保護膜、14 …導電膜(BLM膜)、16 , 16 a …はんだ層、16 b …(第1)バンプ、17 …放熱性基板、18 …接着剤層、19 …共晶はんだ層、20 …可撓性基板基材、20 ′ …実装基板基材、21 …第1面第1配線部、24 …第2面第1配線部、25 …第2バンプ、26 …(第2)配線部、27 …ワイヤボンディング、40 …砥石、41 …ウェーハキャリア、42 …テーブル、43 …研磨布、44 …研磨スラリ、45 …保護テープ、R …レジスト膜、A …開口部、M …半導体モジュール、X …切欠部。

30

10

20

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

# 【図12】

# フロントページの続き

(56)参考文献 特開平11-135715 (JP,A)

特開平09-199665(JP,A)

特開平10-242379 (JP,A)

特開平09-181215 (JP,A)

特開平04-234157(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 25/00-25/18