## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2005-11920 (P2005-11920A)

(43) 公開日 平成17年1月13日(2005.1.13)

千葉県茂原市早野3300番地 株式会社

千葉県茂原市早野3300番地 株式会社

最終頁に続く

日立ディスプレイズ内

日立ディスプレイズ内

(72) 発明者 落合 孝洋

| (51) Int.C1.' | F 1                          |          | テーマコード(参考              | .)  |  |

|---------------|------------------------------|----------|------------------------|-----|--|

| HO1L 29/78    | <b>6</b> HO1L                | 29/78    | 619A 2H092             |     |  |

| GO2F 1/13     | <b>68</b> GO2 F              | 1/1368   | 3K007                  |     |  |

| HO1L 21/3     | 6 HO1L                       | 21/316   | M 5FO33                |     |  |

| HO1L 21/3     | <b>6</b> но 5 в              | 33/10    | 5F058                  |     |  |

| HO1L 21/70    | <b>8</b> но 5 в              | 33/14    | A 5F110                |     |  |

|               | 審査請求 未                       | 請求 請求項   | Îの数 10 OL (全 16 頁) 最終頁 | に続く |  |

| (21) 出願番号     | 特願2003-173062 (P2003-173062) | (71) 出願人 | 502356528              |     |  |

| (22) 出願日      | 平成15年6月18日 (2003.6.18)       |          | 株式会社 日立ディスプレイズ         |     |  |

|               |                              |          | 千葉県茂原市早野3300番地         |     |  |

|               |                              | (74) 代理人 | 100083552              |     |  |

|               |                              |          | 弁理士 秋田 収喜              |     |  |

|               |                              | (72) 発明者 | 野村 秀次                  |     |  |

|               |                              |          | 千葉県茂原市早野3300番地 株       | 式会社 |  |

|               |                              |          | 日立ディスプレイズ内             |     |  |

|               |                              | (72) 発明者 | 田中 政博                  |     |  |

(54) 【発明の名称】表示装置とその製造方法

## (57)【要約】

【課題】表示装置において、コンタクトホールをシリコン酸化膜、シリコン窒化膜、およびシリコン酸化膜の順次積層体に形成する場合に、該コンタクトホールの側壁のテーパを理想的な形状に構成する。

【解決手段】第1のシリコン酸化膜と、前記第1のシリコン酸化膜の上に積層されたシリコン窒化膜と、前記シリコン窒化膜の上に積層された第2のシリコン酸化膜と、前記第1のシリコン酸化膜、前記シリコン窒化膜および前記第2のシリコン酸化膜を含む少なくとも3層を共通に貫通するコンタクトホールとを備えた表示装置であって、

前記コンタクトホールは、前記シリコン窒化膜の膜厚をd2、前記第2のシリコン酸化膜の膜厚をd3としたとき、d2<d3であり、かつ、くびれのないテーパ形状を有する。

【選択図】 図1

#### 【特許請求の範囲】

### 【請求項1】

第 1 のシリコン酸化膜と、前記第 1 のシリコン酸化膜の上に積層されたシリコン窒化膜と 、 前 記 シ リ コ ン 窒 化 膜 の 上 に 積 層 さ れ た 第 2 の シ リ コ ン 酸 化 膜 と 、 前 記 第 1 の シ リ コ ン 酸 化 膜 、 前 記 シ リ コ ン 窒 化 膜 お よ び 前 記 第 2 の シ リ コ ン 酸 化 膜 を 含 む 少 な く と も 3 層 を 共 通 に貫通するコンタクトホールとを備えた表示装置であって、

前 記 コ ン タ ク ト ホ ー ル は 、 前 記 シ リ コ ン 窒 化 膜 の 膜 厚 を d 2 、 前 記 第 2 の シ リ コ ン 酸 化 膜 の膜厚をd3としたとき、d2<d3であり、かつ、くびれのないテーパ形状を有するこ とを特徴とする表示装置。

#### 【請求項2】

前記コンタクトホールは、前記第1のシリコン酸化膜のテーパ角を 1、前記シリコン窒 化膜のテーパ角を 2、前記第2のシリコン酸化膜のテーパ角を 3としたとき、 1 < 9 0 ° かつ 2 < 3 < 9 0 ° であることを特徴とする請求項 1 に記載の表示装置

### 【請求項3】

前 記 第 1 の シ リ コ ン 酸 化 膜 の エ ッ チ ン グ レ ー ト を E r 1 、 前 記 シ リ コ ン 窒 化 膜 の エ ッ チ ン グレートをEr2、前記第2のシリコン酸化膜のエッチングレートをEr3としたとき、 Er1 < Er3、Er2 < Er3、かつ、Er2 < Er1であることを特徴とする請求項 1 または 2 に記載の表示装置。

### 【請求項4】

前記第1のシリコン酸化膜のエッチングレートをEr1、前記シリコン窒化膜のエッチン グレートをEr2、前記第2のシリコン酸化膜のエッチングレートをEr3としたとき、 Erl Er3、Er2 < Er3、かつ、Er2 < Er1であることを特徴とする請求項 1または2に記載の表示装置。

#### 【請求項5】

前 記 コ ン タ ク ト ホ ー ル は 、 前 記 第 1 の シ リ コ ン 酸 化 膜 、 前 記 シ リ コ ン 窒 化 膜 及 び 前 記 第 2 のシリコン酸化膜を一括でウエットエッチングすることにより形成されていることを特徴 とする請求項1から4のいずれかに記載の表示装置。

### 【請求項6】

前 記 第 1 の シ リ コ ン 酸 化 膜 は 薄 膜 ト ラ ン ジ ス タ の ゲ ー ト 酸 化 膜 で あ り 、 前 記 シ リ コ ン 窒 化 膜および前記第2のシリコン酸化膜は層間絶縁膜であり、前記コンタクトホールは前記薄 膜トランジスタのソース・ドレイン領域上に形成されていることを特徴とする請求項1か ら5のいずれかに記載の表示装置。

## 【請求項7】

第 1 のシリコン酸化膜と、前記第 1 のシリコン酸化膜の上に積層されたシリコン窒化膜と 、前記シリコン窒化膜の上に積層された第2のシリコン酸化膜と、前記第1のシリコン酸 化 膜 、 前 記 シ リ コ ン 窒 化 膜 及 び 前 記 第 2 の シ リ コ ン 酸 化 膜 を 含 む 3 層 を 共 通 に 貫 通 す る コ ンタクトホールとを備えた表示装置の製造方法であって、

前記シリコン窒化膜の膜厚をd2、前記第2のシリコン酸化膜の膜厚をd3としたとき、 d 2 < d 3 となる膜厚で積層し、前記第 1 のシリコン酸化膜、前記シリコン窒化膜及び前 記 第 2 の シ リ コ ン 酸 化 膜 を 一 括 で ウ エ ッ ト エ ッ チ ン グ す る こ と に よ り く び れ の な い テ ー パ 形状を有する前記コンタクトホールを形成することを特徴とする表示装置の製造方法。

### 【請求項8】

前 記 コン タ ク ト ホ ー ル は 、 前 記 第 1 の シ リ コ ン 酸 化 膜 の テ ー パ 角 を 1 、 前 記 シ リ コ ン 窒 化膜のテーパ角を 2、前記第2のシリコン酸化膜のテーパ角を 3としたとき、 1 < 9 0 ° かつ 2 < 3 < 9 0 ° であることを特徴とする請求項 7 に記載の表示装置 の製造方法。

## 【請求項9】

前 記 第 1 の シ リ コ ン 酸 化 膜 の エ ッ チ ン グ レ ー ト を E r 1 、 前 記 シ リ コ ン 窒 化 膜 の エ ッ チ ン グレートをEr2、前記第2のシリコン酸化膜のエッチングレートをEr3としたとき、

10

20

30

40

Er1 < Er3 、 Er2 < Er3 、かつ、 Er2 < Er1 であることを特徴とする請求項7または8に記載の表示装置の製造方法。

### 【請求項10】

前記第1のシリコン酸化膜のエッチングレートをEr1、前記シリコン窒化膜のエッチングレートをEr2、前記第2のシリコン酸化膜のエッチングレートをEr3としたとき、Er1 Er3、Er2<Er1であることを特徴とする請求項7または8に記載の表示装置の製造方法。

## 【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は表示装置に係り、たとえばアクティブ・マトリクス型の液晶表示装置等の表示装置に関する。

### [0002]

【従来の技術】

アクティブ・マトリクス型の液晶表示装置は、液晶を介して対向配置される各基板のうち一方の基板の液晶側の面に、たとえば×方向に延在しy方向に並設される複数のゲート信号線、およびy方向に延在し×方向に並設される複数のドレイン信号線が形成され、これら各信号線で囲まれる領域を画素領域とし、これら各画素領域の集合体を液晶表示部として構成している。

### [0003]

そして、各画素領域は一方の側のゲート信号線からの走査信号によって駆動される薄膜トランジスタと、この薄膜トラジスタを介して一方の側のドレイン信号線からの映像信号が供給される画素電極とを備えている。

#### [0004]

この画素電極は前記各基板のうちいずれかの基板の液晶側の面に形成した対向電極との間に電界を発生せしめ、この電界の強弱によって当該画素領域の液晶の光透過率を制御するようにしている。

### [0005]

また、前記各信号線、薄膜トランジスタ、および電極等は、層状に形成した導電層、絶縁層、あるいは半導体層等をいわゆるフォトリソグラフィ技術による選択エッチングによって微細加工がなされている。

## [0006]

この場合、絶縁膜を介した異なる層の各導電層を電気的に接続させる場合、該絶縁膜に形成したコンタクトホールを通して行なうのが通常である。しかし、該絶縁膜が多層からなっている場合、それらのエッチングレート、あるいは膜厚等の相違によって該コンタクトホールの側壁において滑らかな形状を形成することが困難でその工夫がなされている。このコンタクトホールを通して接続を図る場合に、その側壁に及んで形成する導電層に断切れ等が形成され易いからである。

### [0007]

たとえば、薄膜トランジスタがいわゆるトップゲート構造であって、その電極を形成する ためのコンタクトホールをシリコン酸化膜、シリコン窒化膜、およびシリコン酸化膜の順 次積層体に形成する場合、ウエットエッチングでテーパ加工するものが知られている(特 許文献 1 参照)。

## [0008]

また、コンタクトホールを形成する多層の絶縁膜において、その各絶縁膜のエッチングレートを下層から上層に及ぶにしたがい段階的にあるいは連続的に増加するように各材料を 選定するものも知られている(特許文献 2 参照)。

#### [00009]

さらに、酸化シリコン膜と窒化シリコン膜とからなる積層体におけるコンタクトホールの 形成を単一のエッチング処理により行なうものが知られている(特許文献3参照)。

10

20

30

40

[0010]

【特許文献1】

特開平11-11990号公報

【特許文献2】

特開平9-251996号公報

【特許文献3】

特開平11-258634号公報

[0011]

【発明が解決しようとする課題】

しかし、上記特許文献 1 の場合、多層の絶縁膜の中間層として形成されるシリコン窒化膜の膜厚が比較的厚く形成されているため、コンタクトホールの側壁面のテーパ形状において理想的な形状ではなく、まだ改善の余地があるものとなっている。

[0012]

上記特許文献 2 の場合、多層の絶縁膜の各材料が特定されるため、表示装置の画素の形成においてそれが不適な場合が生じるという不都合がある。

[ 0 0 1 3 ]

上記特許文献3の場合も、特定の条件を満たす酸化シリコン膜と窒化シリコン膜とからなる積層体にコンタクトホールを形成するものに特定されるため、表示装置の画素の形成においてそれが不適な場合が生じるという不都合がある。

[0014]

本発明は、コンタクトホールをシリコン酸化膜、シリコン窒化膜、およびシリコン酸化膜の順次積層体に形成する場合に、該コンタクトホールの側壁のテーパを理想的な形状に構成した表示装置を提供することにある。

[ 0 0 1 5 ]

【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

[0016]

手段1.

本発明による表示装置は、たとえば、第1のシリコン酸化膜と、前記第1のシリコン酸化膜の上に積層されたシリコン窒化膜と、前記シリコン窒化膜の上に積層された第2のシリコン酸化膜と、前記第1のシリコン酸化膜、前記シリコン窒化膜および前記第2のシリコン酸化膜を含む少なくとも3層を共通に貫通するコンタクトホールとを備えた表示装置であって、

前記コンタクトホールは、前記シリコン窒化膜の膜厚をd2、前記第2のシリコン酸化膜の膜厚をd3としたとき、d2<d3であり、かつ、くびれのないテーパ形状を有することを特徴とするものである。

[0017]

手段 2 .

本発明による表示装置は、たとえば、手段 1 の構成を前提とし、前記コンタクトホールは 40、前記第 1 のシリコン酸化膜のテーパ角を 1、前記シリコン窒化膜のテーパ角を 2、前記第 2 のシリコン酸化膜のテーパ角を 3 としたとき、 2 < 1 < 9 0 ° かつ 2 < 3 < 9 0 ° であることを特徴とするものである。

[0018]

手段3.

本発明による表示装置は、たとえば、手段1または2の構成を前提とし、前記第1のシリコン酸化膜のエッチングレートをEr1、前記シリコン窒化膜のエッチングレートをEr2、前記第2のシリコン酸化膜のエッチングレートをEr3としたとき、Er1<Er3、Er2<Er3、かつ、Er2<Er1であることを特徴とするものである。

[0019]

50

20

手段4.

本発明による表示装置は、たとえば、手段1または2の構成を前提とし、前記第1のシリコン酸化膜のエッチングレートをEr1、前記シリコン窒化膜のエッチングレートをEr2、前記第2のシリコン酸化膜のエッチングレートをEr3としたとき、Er1 Er3、Er2<Er3、かつ、Er2<Er1であることを特徴とするものである。

[0020]

手段5.

本発明による表示装置は、たとえば、手段 1 から 4 のいずれかの構成を前提とし、前記コンタクトホールは、前記第 1 のシリコン酸化膜、前記シリコン窒化膜及び前記第 2 のシリコン酸化膜を一括でウエットエッチングすることにより形成されていることを特徴とするものである。

10

20

[0021]

手段 6.

本発明による表示装置は、たとえば、手段 1 から 5 のいずれかの構成を前提とし、前記第 1 のシリコン酸化膜は薄膜トランジスタのゲート酸化膜であり、前記シリコン窒化膜および前記第 2 のシリコン酸化膜は層間絶縁膜であり、前記コンタクトホールは前記薄膜トランジスタのソース・ドレイン領域上に形成されていることを特徴とするものである。

[0022]

手段7.

本発明による表示装置の製造方法は、たとえば、第 1 のシリコン酸化膜と、前記第 1 のシリコン酸化膜の上に積層されたシリコン窒化膜と、前記シリコン窒化膜の上に積層された第 2 のシリコン酸化膜と、前記第 1 のシリコン酸化膜、前記シリコン窒化膜及び前記第 2 のシリコン酸化膜を含む 3 層を共通に貫通するコンタクトホールとを備えた表示装置の製造方法であって、

前記シリコン窒化膜の膜厚を d 2、前記第 2 のシリコン酸化膜の膜厚を d 3 としたとき、 d 2 < d 3 となる膜厚で積層し、前記第 1 のシリコン酸化膜、前記シリコン窒化膜及び前記第 2 のシリコン酸化膜を一括でウエットエッチングすることによりくびれのないテーパ形状を有する前記コンタクトホールを形成することを特徴とするものである。

[0023]

手段8.

本発明による表示装置の製造方法は、たとえば、手段 7 の構成を前提とし、前記コンタクトホールは、前記第 1 のシリコン酸化膜のテーパ角を 1 、前記シリコン窒化膜のテーパ角を 2 、前記第 2 のシリコン酸化膜のテーパ角を 3 としたとき、 2 < 1 < 9 0 ° かつ 2 < 3 < 9 0 ° であることを特徴とするものである。

[0024]

手段9.

本発明による表示装置の製造方法は、たとえば、手段 7 または 8 の構成を前提とし、前記第 1 のシリコン酸化膜のエッチングレートを E r 1、前記シリコン窒化膜のエッチングレートを E r 2、前記第 2 のシリコン酸化膜のエッチングレートを E r 3 としたとき、 E r 1 く E r 3、 E r 2 く E r 3、 かつ、 E r 2 く E r 1 であることを特徴とするものである

40

50

30

[0025]

手段10.

本発明による表示装置の製造方法は、たとえば、手段 7 または 8 の構成を前提とし、前記第 1 のシリコン酸化膜のエッチングレートを E r 1、前記シリコン窒化膜のエッチングレートを E r 2、前記第 2 のシリコン酸化膜のエッチングレートを E r 3 としたとき、 E r 1 E r 3、 E r 2 < E r 3、 かつ、 E r 2 < E r 1 であることを特徴とするものである

[0026]

なお、本発明は以上の構成に限定されず、本発明の技術思想を逸脱しない範囲で種々の変

更が可能である。

[0027]

【発明の実施の形態】

以下、本発明による表示装置の実施例を図面を用いて説明をする。

[0028]

実施例1.

《全体の等価回路》

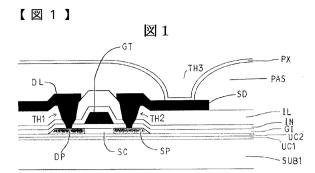

図 2 は、本発明による表示装置、たとえば液晶表示装置の一実施例を示す等価回路図である。図 2 は等価回路図であるが、実際の幾何学的配置に対応させて描いている。

[0029]

10

20

30

40

50

まず、液晶を介して互いに対向配置される一対の透明基板 S U B 1 、 S U B 2 があり、該液晶は一方の透明基板 S U B 1 に対する他方の透明基板 S U B 2 の固定を兼ねるシール材 S L によって封入されている。

[ 0 0 3 0 ]

シール材SLによって囲まれた前記一方の透明基板SUB1の液晶側の面には、その×方向に延在しy方向に並設されたゲート信号線(走査信号線)GLとy方向に延在し×方向に並設されたドレイン信号線(映像信号線)DLとが形成されている。

[0031]

各ゲート信号線 G L と各ドレイン信号線 D L とで囲まれた領域は画素領域を構成するとともに、これら各画素領域のマトリクス状の集合体は液晶表示部 A R を構成するようになっている。

[0032]

また、 x 方向に並設される各画素領域のそれぞれにはそれら各画素領域内に走行された共通の容量信号線 C L が形成されている。この容量信号線 C L は各画素領域ごとに形成される後述の容量素子 C s t g の一方の電極に接続されるもので、たとえば一定の電圧が印加されるようになっている。

[0033]

各画素領域には、その片側のゲート信号線GLからの走査信号によって作動される薄膜トランジスタTFTと、この薄膜トランジスタTFTを介して片側のドレイン信号線DLからの映像信号が供給される画素電極PXが形成されている。そして、この画素電極PXと前記容量信号線CLとの間には前記容量素子Cstgが接続されている。この容量素子Cstgは画素電極PXに供給された映像信号を比較的長い時間蓄積させるため等に設けられたものである。

[0034]

該薄膜トランジスタTFTはその半導体層が多結晶のたとえばSi(p-Si)から構成されたものとなっている。

[0035]

また、画素電極 P X は、他方の透明基板 S U B 2 の液晶側の面に各画素領域に共通に形成した対向電極 C T (図示せず)との間に電界を発生させ、この電界によって液晶の光透過率を制御させるようになっている。

[ 0 0 3 6 ]

前記ゲート信号線 G L のそれぞれの一端は前記液晶表示部 A R を超えて延在され、その延在端は透明基板 S U B 1 の表面に形成された走査信号駆動回路 V に接続されるようになっている。この走査信号駆動回路 V は多数の M I S ( M e t a l I n s u l a t o r S e m i c o n d u c t o r )型トランジスタとそれらを接続させる配線層等で形成されている。

[0037]

同様に、前記ドレイン信号線 D L のそれぞれの一端は前記液晶表示部 A R を超えて延在され、その延在端は透明基板 S U B 1 の表面に形成された映像信号駆動回路 H e に接続されるようになっている。この映像信号駆動回路 H e も多数の M I S 型トランジスタとそれら

を接続させる配線層等で形成されている。

#### [0038]

ここで、前記走査信号駆動回路 V および映像信号駆動回路 H e を構成する M I S 型トランジスタは、その半導体層が各画素領域における前記薄膜トランジスタ T F T のそれと同様に多結晶層で形成されている。このため、該 M I S 型トランジスタの形成においては該薄膜トランジスタ T F T の形成と並行してなされるのが通常である。

#### [0039]

また、×方向に併設された各画素領域に共通な前記容量信号線CLはたとえば図中右側の端部で共通に接続され、その接続線はシール材SLを超えて延在され、その延在端において端子CLTを構成している。

## [0040]

前記各ゲート信号線GLは、走査信号駆動回路Vからの走査信号によって、その一つが順次選択されるようになっている。

### [0041]

また、前記各ドレイン信号線DLのそれぞれには、映像信号駆動回路Heによって、前記ゲート信号線GLの選択のタイミングに合わせて映像信号が供給されるようになっている

### [0042]

## 《画素の構成》

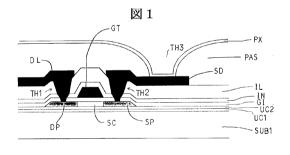

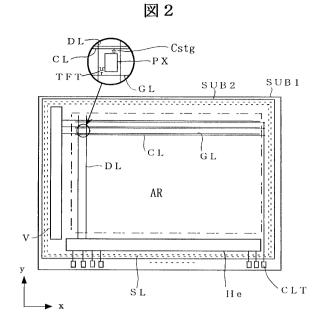

図3は、前記画素領域における画素の一実施例を示す平面図で、そのI・I線における断面図を図1に示している。

#### [ 0 0 4 3 ]

図1に示すように、まず、透明基板SUB1の液晶側の面には、まずシリコン窒化膜からなる第1アンダーコート膜UC1とシリコン酸化膜からなる第2アンダーコート膜UC2の順次積層体がたとえばプラズマCVD法等によって形成されている。これらアンダーコート膜UC1、UC2は透明基板SUB1からの不純物が後述の薄膜トラジスタTFTへ浸透するのを防止するための膜となるものである。

#### [0044]

アンダーコート膜UC2の上面であって、その各画素領域の周囲の一部、たとえば図3の左下の部分に半導体層SCが形成されている。この半導体層SCは、薄膜トランジスタTFTのそれであり、たとえばポリシリコン層で構成されている。このポリシリコン層は、たとえばアモルファスシリコン層をレーザーアニールで結晶化することにより形成される

## [0045]

そして、透明基板SUB1の表面には、前記半導体層SCをも被ってたとえばシリコン酸化膜からなる第1絶縁膜GIが形成されている。この第1絶縁膜GIは前記薄膜トランジスタTFTのゲート絶縁膜としての機能を有するものである。なお、製造において、この第1絶縁膜GIの形成後にこの第1絶縁膜GIを通して前記半導体層SCに低濃度のたとえば燐(P)が注入され、これにより該半導体層SCには低濃度にn型化されるようになっている。

## [0046]

第1 絶縁膜GIの表面には、ゲート信号線GLが形成され、このゲート信号線GLの一部は前記半導体層SCのほぼ中央を横切るようにして延在部を備え、この延在部は前記薄膜トラジスタTFTのゲート電極GTとして機能させている。ゲート信号線GLおよびゲート電極GTはたとえばMoW等の金属層から形成され、該金属層の成膜後にフォトリソグラフィ技術による選択エッチングでパターン化することによって形成される。

#### [0047]

なお、製造において、該ゲート信号線GLおよびゲート電極GTの形成後にこれらをマスクとして高濃度のたとえばボロン(B)を注入する工程が行なわれる。前記半導体層SCにおいてゲート電極GTの直下の領域を除く他の領域を高濃度にp型化させるためである

10

20

30

40

30

40

50

。これにより、 半導体層 S C のゲート電極 G T の両側の各領域には薄膜トランジスタ T F T のドレイン領域 D P 、ソース領域 S P が形成されることになる。

### [0048]

第1 絶縁膜GIの表面には、ゲート信号線GLおよびゲート電極GTをも被って、たとえばシリコン窒化膜等からなる第2 絶縁膜INおよびたとえばシリコン酸化膜等からなる第3 絶縁膜ILが形成されている。これら絶縁膜はたとえばプラズマCVD法等により形成され、第2 絶縁膜INは50~200nmの範囲の厚さで形成されている。また、第2 絶縁膜INは、400 以下のプラズマCVD法により形成され、可視領域に吸収端を持たないような成膜条件で成膜され、膜中水素量は2E21~2E22atom/cm³となっている。なお、製造において、これら絶縁膜の形成の後には、たとえば400~500 の範囲の温度で、たとえば400 の温度で約1時間の熱処理を行ない、これにより、前記半導体層SC内の不純物の活性化と水素終端化を同時に行なうようにする。

### [0049]

そして、前記第3絶縁膜ILの表面にはドレイン信号線DLが形成され、その一部は該第3絶縁膜IL、その下層の第2絶縁膜IN、さらにその下層の第1絶縁膜GIを貫通して設けられたコンタクトホールTH1を通して薄膜トランジスタTFTのドレイン領域DPに接続されている。これにより、ドレイン信号線DLの該ドレイン領域DPの接続部は薄膜トランジスタTFTのドレイン電極を兼ねるようになる。

### [0050]

また、該ドレイン信号線DLの形成の際に同時に形成されるものであって、第3絶縁膜ILの表面には薄膜トランジスタTFTのソース領域SPに接続されるソース電極SDが形成されている。この場合にあっても、該ソース電極SDは、第3絶縁膜IL、その下層の第2絶縁膜IN、さらにその下層の第1絶縁膜GIを貫通して設けられたコンタクトホールTH2を通して薄膜トランジスタTFTのソース領域SPに接続されている。このソース電極SDは後述する画素電極PXと電気的に接続されるものである。

### [ 0 0 5 1 ]

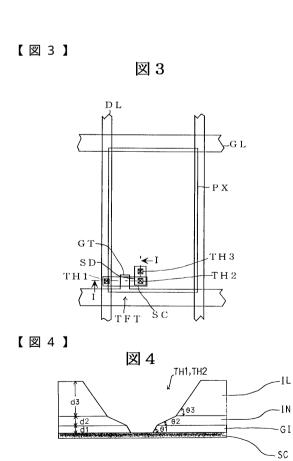

ここで、前記コンタクトホールTH1およびTH2は、そのいずれの断面形状が図4に示すように、第1絶縁膜GIにおける該コンタクトホールの側壁は半導体層SCの表面に対して 1(<90°)の角度(テーパ角)を、第2絶縁膜INにおける該コンタクトホールの側壁は第1絶縁膜GIの表面に対して 2(<90°)の角度(テーパ角)を、第3絶縁膜ILにおける該コンタクトホールの側壁は第2絶縁膜INの表面に対して 3(<90°)の角度(テーパ角)を有して形成され、これらは 2< 1<90°かつ 2<3<90°の関係を満足するようになっている。

### [0052]

また、第 1 絶縁膜 G I の膜厚を d 1 、第 2 絶縁膜 I N の膜厚を d 2 、さらに第 3 絶縁膜 I L の膜厚を d 3 とした場合、 d 2 < d 1 < d 3 の関係となっており、少なくとも d 2 < d 3 の関係を満足するようになっている。

### [0053]

前記コンタクトホールTH1およびTH2の形成は、たとえばバッファードフッ酸(BHF)を用いたウエットエッチングによって行なう。この際、第3絶縁膜ILおよび第1絶縁膜GIからなるシリコン酸化膜は10~30nm/sのエッチング速度でエッチングされる。また、第2絶縁膜INからなるシリコン窒化膜は、上述したように400 以下でプラズマCVD法により形成されたものであり、可視領域に吸収端を持たないような成膜条件で成膜され、膜中水素量は2E21~2E22atom/cm³となっているものである。このような第2絶縁膜INは、現実的なレートでエッチングでき、そのエッチング速度は3~10nm/sである。

## [0054]

ちなみに、前記コンタクトホールTH1およびTH2をドライエッチングで形成しようと した場合、次に示すような不都合が生じる。すなわち、第3絶縁膜ILおよび第1絶縁膜

20

30

40

50

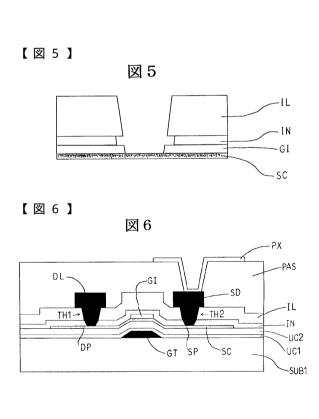

GIからなるシリコン酸化膜はインオ照射下でエッチングが進行するので、いわゆるRIEモードによるドライエッチングが必要となり、その側面のテーパ角は90~80°となってしまう。そして、エッチングに用いるガスとしてたとえばCF₄等のPFCガスを用いるが、第2絶縁膜INからなるシリコン窒化膜において、図5に示すように、第1絶縁膜GIおよび第3絶縁膜ILの側面に対してそれよりも内側へ大きくエッチングされ、いわゆるアンダーカット(本明細書において「くびれ」と呼んでいるものの一つがこれである)が発生し易くなる。シリコン窒化膜はイオン照射下でなくともエッチングされる性質を有するからである。さらに、第2絶縁膜INの下層である第1絶縁膜GIをエッチングする際にはその下地の半導体層SCに対する高選択ドライエッチングが必要となる。

#### [0055]

このようにしてドレイン信号線DL、ソース電極SDが形成された透明基板SUB1の表面には、該ドレイン信号線DL、ソース電極SDをも被って、たとえば有機材料からなる保護膜PASが形成されている。保護膜PASの材料として有機材料を用いたのはそれ自体の誘電率の低下を図るもので、この保護膜PASの上面に形成する後述の画素電極PXと該保護膜PASの下に形成されるドレイン信号線DLとの間に発生する寄生容量を低減させるためである。なお、この保護膜PASにはコンタクトホールTH3が露光現像によって形成され、このコンタクトホールTH3からは前記ソース電極SDの一部が露出されるように構成されている。

#### [0056]

保護膜PASの上面には画素電極PXが形成されている。この画素電極PXは、ITO(Indium Tin Oxide)、ITZO(Indium Tin Zinc Oxide)、SnO₂(酸化スズ)、In₂О₃(酸化インジウム)等の光透過性の導電層から構成され、画素の大部分の領域を被って形成されている。この場合、隣接する画素領域の画素電極PXとの電気的分離が図れる限り、当該画素電極PXの周辺は前記ドレイン信号線DLあるいはゲート信号線GLに重畳されて形成されていてもよい。それらの間に介在される保護膜PASは低誘電率の材料で構成されているからである。

#### [ 0 0 5 7 ]

このように構成された液晶表示装置は、その薄膜トランジスタTFTのコンタクトホールTH1、TH2において、いわゆるくびれのない滑らかなテーパ角を有して形成されるようになる。

## [ 0 0 5 8 ]

特に、この構成は、シリコン酸化膜、シリコン窒化膜、シリコン酸化膜の順次積層体において、コンタクトホールを貫通して形成するもので、たとえばエッチングレートの相違から生じる弊害を解消するものとなっている。

## [0059]

本発明では、第1のシリコン酸化膜と、前記第1のシリコン酸化膜の上に積層されたシリコン窒化膜と、前記シリコン窒化膜の上に積層された第2のシリコン酸化膜とを含む少なくとも3層を共通に貫通するコンタクトホールを、一括でウエットエッチングする際に、前記シリコン窒化膜の膜厚をd2、前記第2のシリコン酸化膜の膜厚をd3としたとき、d2<d3という膜厚の条件の下でそれぞれを一括でウエットエッチングすることにより、くびれのないテーパ形状を有するコンタクトホールを形成することが可能となっている

## [0060]

図 5 を用いて説明した通り、ウエットエッチングではなくドライエッチングでコンタクトホールを形成した場合には、シリコン窒化膜がその上下にある第 1 および第 2 のシリコン酸化膜よりも後退した形状となってしまう。これが、本明細書でいう、くびれた形状の一例である。

### [0061]

また、特許文献 1 の図 2 に示されているように、シリコン酸化膜、シリコン窒化膜、シリ

30

40

50

コン酸化膜の順次積層体で構成された層間絶縁膜を一括でウエットエッチングする際に、シリコン窒化膜の膜厚がその上層にあるシリコン酸化膜の膜厚よりも厚い条件、即ち、本願発明と比較した場合にd2>d3という膜厚の条件の下でウエットエッチングを行なった場合、上層のシリコン酸化膜、並びに、下層のシリコン酸化膜は、その側壁の一部がくぼんだ形状となってしまう。言い換えれば、部分的に側壁のテーパ角が90°を越える形状となってしまう。これが、本明細書でいう、くびれた形状の他の例である。

[0062]

一般的に、ウエットエッチングする場合には、シリコン窒化膜のエッチングレートはシリコン酸化膜のエッチングレートよりも小さい(すなわち、エッチング速度が遅い)。従って、第1のシリコン酸化膜のエッチングレートをEr1、シリコン窒化膜のエッチングレートをEr2、第2のシリコン酸化膜のエッチングレートをEr3としたとき、Er2<Er3、かつ、Er2<Er1である。

[0063]

d 2 > d 3 という膜厚の条件の下でウエットエッチングを行なった場合、エッチングの遅いシリコン窒化膜の膜厚が厚いので、エッチングに時間がかかってしまう。さらに、その上層、及び下層にある第 1 および第 2 のシリコン酸化膜はエッチングされすぎてしまうため、コンタクトホールの側壁がくびれた形状となってしまう。

[0064]

これに対して、本発明のようにd2 < d3 という膜厚の条件の下でウエットエッチングを行なうことにより、シリコン窒化膜のエッチング時間が短時間で済むので、その上層、及び下層にある第1 および第2 のシリコン酸化膜がエッチングされすぎてしまうことなく、くびれのないテーパ形状を有するコンタクトホールを形成することが可能となっている。

[0065]

また、このエッチングレートの差から、第1のシリコン酸化膜のテーパ角を 1、シリコン窒化膜のテーパ角を 2、第2のシリコン酸化膜のテーパ角を 3としたとき、 2 < 1 < 9 0 ° かつ 2 < 3 < 9 0 ° となる。

[0066]

なお、第1及び第2のシリコン酸化膜のエッチングレートの関係は、理想的なテーパ形状を実現するためにはEr1<Er3であった方がより好ましいが、Er1 Er3であってもよい。

[0067]

上述した実施例では、画素領域内に形成される薄膜トランジスタTFTのコンタクトホールTH1、TH2について説明したものであるが、周辺回路、たとえば、前記走査信号駆動回路V、あるいは映像信号駆動回路Heに組み込まれて形成されるMISトランジスタのコンタクトホールにおいても適用できるものである。

[0068]

上述したように、該MISトランジスタは画素領域内の薄膜トランジスタTFTとほぼ同様の構成を採用し、該薄膜トランジスタTFTと並行して形成するからである。すなわち、薄膜トランジスタTFTの半導体層SC等を形成する際には、MISトランジスタの半導体層も形成し、第1絶縁膜GI等を形成する際には、液晶表示部ARの領域のみに限らず、走査信号駆動回路Vおよび映像信号駆動回路Heの形成領域にも及んで形成するようにするからである。

[0069]

実施例2.

上述した実施例における薄膜トランジスタTFTは、そのゲート電極GTが半導体層SCに対して上側に形成されたいわゆるトップゲート型と称されるものである。しかし、薄膜トランジスタTFTの他の構成として、ゲート電極GTが半導体層SCに対して下側に形成されるいわゆるボトムゲート型のものを用いることもできる。

[0070]

この場合、前記ゲート電極GTとたとえば一体に形成されるゲート信号線GLの信号供給

20

30

40

50

端子においてその一部を露出させるコンタクトホールにも、実施例1に示した構成を適用 することができる。

[0071]

ゲート信号線 G L の信号供給端子の前記コンタクトホールを、実施例 1 に示した薄膜トランジスタTFTのコンタクトホールTH1、TH2と同様の構成とすることができるからである。

[0072]

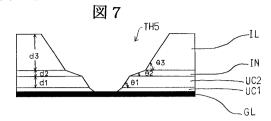

図 6 は、液晶表示装置の各画素に形成されるボトムゲート型の薄膜トランジスタを示すもので、図 1 に対応した図となっている。

[0073]

すなわち、透明基板SUB1の液晶側の面に、まず、ゲート電極GTが形成されている。 このゲート電極GTはゲート信号線GLとたとえば一体に形成されるものである。

[ 0 0 7 4 ]

そして、透明基板SUB1の表面に、前記ゲート電極GT、ゲート信号線GLをも被って、シリコン窒化膜からなるアンダーコート膜UC1とシリコン酸化膜からなるアンダーコート膜UC2の順次積層体がたとえばプラズマCVD法等によって形成されている。ここで、アンダーコート膜UC1、UC2は、透明基板SUB1からの不純物が後述の薄膜トラジスタTFTへ浸透するのを防止する機能を有するが、薄膜トラジスタTFTのゲート絶縁膜としての機能をも有するようになっている。

[0075]

アンダーコート膜UC2の上面であって、薄膜トランジスタTFTの形成領域に、半導体層SCが形成されている。この半導体層SCは、たとえばポリシリコン層で構成され、前記ゲート電極GTを横切るようにして形成されている。このポリシリコン層は、たとえばアモルファスシリコン層をレーザーアニールで結晶化することにより形成される。

[0076]

そして、該半導体層SCの上面であって前記ゲート電極GTが横切る部分にたとえばシリコン酸化膜からなる第1絶縁膜GIが形成されている。この第1絶縁膜GIは半導体層SCに不純物ドープの際のマスクとして機能させるものである。これにより、前記半導体層SCはゲート電極GTの直下を除く他の領域において、高濃度のたとえばn型不純物層として構成することができる。

[0077]

透明基板SUB1の表面には、前記半導体層SCおよび第1絶縁膜GIをも被って、たとえばシリコン窒化膜等からなる第2絶縁膜INおよびたとえばシリコン酸化膜等からなる第3絶縁膜ILが形成されている。これら絶縁膜はたとえばプラズマCVD法等により形成され、第2絶縁膜INは50~200nmの厚さ、たとえば50nmの厚さで形成され、第3絶縁膜ILは400~500nmの範囲の厚さで形成されている。また、第2絶縁膜INは、400 以下のプラズマCVD法により形成され、可視領域に吸収端を持たないような成膜条件で成膜され、膜中水素量は2E21~2E22atom/cm³となっている。なお、製造において、これら絶縁膜の形成の後には、たとえば400~500の範囲の温度で、たとえば400 の温度で約1時間の熱処理を行ない、これにより、前記半導体層SC内の不純物の活性化と水素終端化を同時に行なうようにする。

[0078]

そして、前記第3絶縁膜ILの表面にはドレイン信号線DLが形成され、その一部は該第3絶縁膜IL、その下層の第2絶縁膜INを貫通して設けられたコンタクトホールTH1を通して薄膜トランジスタTFTのドレイン領域DPに接続されている。また、該ドレイン信号線DLの形成の際に同時に形成されるものであって、第3絶縁膜ILの表面には薄膜トランジスタTFTのソース領域SPに接続されるソース電極SDが形成されている。この場合にあっても、該ソース電極SDは、第3絶縁膜IL、その下層の第2絶縁膜INを貫通して設けられたコンタクトホールTH2を通して薄膜トランジスタTFTのソース領域SPに接続されている。このソース電極SDは後述する画素電極PXと電気的に接続

されるものである。

## [0079]

このようにしてドレイン信号線 D L、ソース電極 S D が形成された透明基板 S U B 1 の表面には、該ドレイン信号線 D L、ソース電極 S D をも被って、たとえば有機材料からなる保護膜 P A S が形成されている。この保護膜 P A S の上面には画素電極 P X が形成されている。この画素電極 P X は、たとえば I T O (I n d i u m T i n O x i d e)等の光透過性の導電層から構成され、画素の大部分の領域を被って形成されている。

### [0800]

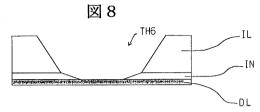

このような構成の薄膜トランジスタTFTを有する液晶表示装置は、そのゲート信号線GLの信号供給端子においてその一部を露出させるコンタクトホールは図7に示すようになっている。すなわち、ゲート信号線GLの上面には第1アンダーコート膜UC1、第2アンダーコート膜UC2、第2絶縁膜IN、および第3絶縁膜ILが順次積層され、それに形成されたコンタクトホールTH5はその側壁が滑らかな傾斜を有して形成されている。なお、このコンタクトホールTH5はたとえば前記薄膜トランジスタTFTのそれと同時に形成するようにしてなされるが、この図7において、その構成と製造方法を示す。

#### [0081]

該コンタクトホールは、図7に示すように、積層された第2アンダーコート膜UC2における該コンタクトホールの側壁は、第1アンダーコート膜UC1の表面に対して 1(<90°)の角度(テーパ角)を、第2絶縁膜INにおける該コンタクトホールの側壁は第1絶縁膜GIの表面に対して 2(<90°)の角度(テーパ角)を、第3絶縁膜ILにおける該コンタクトホールの側壁は第2絶縁膜INの表面に対して 3(<90°)の角度(テーパ角)を有して形成され、これらは 2< 1<90°かつ 2< 3<90°の関係を満足するようになっている。

#### [0082]

また、第 2 アンダーコート膜 U C 2 のシリコン酸化膜の膜厚を d 1 、第 2 絶縁膜 I N の膜厚を d 2 、さらに第 3 絶縁膜 I L の膜厚を d 3 とした場合、 d 2 < d 1 < d 3 の関係となっており、少なくとも d 2 < d 3 の関係を満足するようになっている。

#### [0083]

前記コンタクトホールTH5の形成は、たとえばバッファードフッ酸(BHF)を用いたウエットエッチングによって行なう。この際、第3絶縁膜ILおよび第2アンダーコート膜UC2からなるシリコン酸化膜は10~30nm/sのエッチング速度でエッチングされる。また、第2絶縁膜INからなるシリコン窒化膜は、上述したように400 以下でプラズマCVD法により形成されたものであり、可視領域に吸収端を持たないような成膜条件で成膜され、膜中水素量は2E21~2E22atom/cm³となっているものである。このような第2絶縁膜INは、現実的なレートでエッチングでき、そのエッチング速度は3~10nm/sである。

#### [0084]

ちなみに、図8はドレイン信号線DLの信号供給端子においてその一部を露出させるコンタクトホールTH6の断面を示す図であるが、この場合においても該コンタクトホールTH6の側壁は滑らかな傾斜を有して形成される。

## [ 0 0 8 5 ]

上述した各実施例は、そのいずれも液晶表示装置について示したものである。しかし、たとえば有機 EL(Electro Luminescence)表示装置等の他の表示装置にも適用できることはいうまでもない。

#### [0086]

例えば、有機 E L 表示装置の場合、各画素に一方の電極、発光材料層、他方の電極が積層されて形成され、前記発光材料層に電流を流すことにより、その値に応じて発光するようになっている。そして、各画素には薄膜トランジスタを備え、映像信号に応じて発光を制御している。

## [0087]

50

40

20

このような他の表示装置においても、画素内、あるいは周辺回路(例えば駆動回路など)において、シリコン酸化膜、シリコン窒化膜、およびシリコン酸化膜の順次積層体にコンタクトホールを形成する場合があるからである。

#### [0088]

上述した各実施例はそれぞれ単独に、あるいは組み合わせて用いても良い。それぞれの実施例での効果を単独であるいは相乗して奏することができるからである。

#### [0089]

## 【発明の効果】

以上説明したことから明らかなように、本発明による表示装置によれば、コンタクトホールをシリコン酸化膜、シリコン窒化膜、およびシリコン酸化膜の順次積層体に形成する場合に、該コンタクトホールの側壁のテーパを理想的な形状に構成することができる。

#### 【図面の簡単な説明】

【図1】本発明による表示装置の薄膜トランジスタおよびその近傍の構成の一実施例を示す構成図で、図3のI-I線における断面図である。

【図2】本発明による表示装置の全体の一実施例を示す等価回路図である。

【図3】本発明による表示装置の画素の一実施例を示す平面図である。

【図4】本発明による表示装置の薄膜トランジスタに形成するコンタクトホールの一実施例を示す断面図である。

【図 5 】表示装置の薄膜トランジスタに形成するコンタクトホールであって本願発明を適用しない場合の一例を示す断面図である。

【図 6 】本発明による表示装置の薄膜トランジスタおよびその近傍の構成の他の実施例を示す断面図である。

【図7】図6に示す薄膜トランジスタを形成した場合のゲート信号線の信号供給端子に形成されるコンタクトホールの一実施例を示す断面図である。

【図8】図6に示す薄膜トランジスタを形成した場合のドレイン信号線の信号供給端子に 形成されるコンタクトホールの一実施例を示す断面図である。

## 【符号の説明】

S U B 1 , S U B 2 ...透明基板、 G L ...ゲート信号線、 D L ...ドレイン信号線、 T F T ... 薄膜トランジスタ、 P X ...画素電極、 U C 1 , U C 2 ...アンダーコート膜、 G I ...第 1 絶 縁膜、 I N ...第 2 絶縁膜、 I L ...第 3 絶縁膜、 P A S ...保護膜。

30

20

【図2】

【図7】

【図8】

# フロントページの続き

QQ23

| (51) Int.CI. <sup>7</sup> H 0 5 B 33/10 H 0 5 B 33/14 |           | F I<br>H 0 1 L<br>H 0 1 L<br>H 0 1 L | 29/78     | M<br>6 1 6 S<br>6 1 6 K | テーマコード(参考) |

|-------------------------------------------------------|-----------|--------------------------------------|-----------|-------------------------|------------|

| F ターム(参考) 2H092 GA29<br>NA29                          | HA04 JA24 | JA46 KB25 M                          | MA08 MA13 | MA17 MA18               | MA19       |

| 3K007 AB11                                            | BA06 FA01 | GA00                                 |           |                         |            |

| 5F033 GG04                                            | HH22 HH38 | JJ01 JJ38 K                          | KK01 NN32 | QQ08 QQ09               | QQ10       |

| QQ19                                                  | QQ34 QQ35 | QQ37 QQ74 R                          | RR04 RR06 | RR21 SS15               | TT02       |

| VV06                                                  | VV15 WW00 | XX02 XX24                            |           |                         |            |

| 5F058 BA09                                            | BB04 BD04 | BD10 BF07 B                          | 3H01 BJ05 |                         |            |

| 5F110 AA26                                            | BB02 CC02 | CCO8 DD13 D                          | DD14 DD17 | EE06 FF02               | FF03       |

| FF09                                                  | FF30 GG02 | GG13 GG32 H                          | HJ01 HJ13 | HJ23 HL14               | NN03       |

| NN04                                                  | NN15 NN23 | NN24 NN27 N                          | NN28 NN35 | NN72 PP03               | QQ05       |