# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-244383 (P2008-244383A)

最終頁に続く

(43) 公開日 平成20年10月9日(2008.10.9)

| (51) Int.Cl. | F I                        |                 | テーマコード(参考)                    |                   |  |

|--------------|----------------------------|-----------------|-------------------------------|-------------------|--|

| HO1L 23/12   | <b>(2006.01)</b> HO1L      | 23/12           | 5 O 1 P                       | 5F033             |  |

| HO1L 21/320  | <b>5 (2006.01)</b> HO1L    | 21/88           | $\mathbf{T}$                  |                   |  |

| HO1L 23/52   | <b>(2006.01)</b> HO1L      | 21/90           | S                             |                   |  |

| HO1L 21/768  | (2006.01)                  |                 |                               |                   |  |

| HO1L 23/522  | (2006.01)                  |                 |                               |                   |  |

|              |                            | 審査請求            | 未請求 請求項の                      | 数 13 O L (全 12 頁) |  |

| (21) 出願番号    | 特願2007-86418 (P2007-86418) | (71) 出願人        | 000001443                     |                   |  |

| (22) 出願日     | 平成19年3月29日 (2007.3.29)     |                 | カシオ計算機株式会社                    |                   |  |

|              |                            | 東京都渋谷区本町1丁目6番2号 |                               |                   |  |

|              |                            | (72)発明者         | 者 若林 猛                        |                   |  |

|              |                            |                 | 東京都青梅市藤橋3丁目3番地の2<br>カシオ計算機株式会 |                   |  |

|              |                            |                 |                               |                   |  |

|              |                            |                 | 社青梅事業所第二                      | 二工場内              |  |

|              |                            | (72)発明者         | 三原 一郎                         |                   |  |

|              |                            |                 | 東京都青梅市藤橋3丁目3番地の2              |                   |  |

|              |                            |                 | カシオ計算機株式会                     |                   |  |

|              |                            |                 | 社 <b>青梅事業</b> 所第二             | 二工場内              |  |

(54) 【発明の名称】半導体装置およびその製造方法

# (57)【要約】

【課題】 CSPと呼ばれる半導体装置において、配線相互間のエレクトロマイグレーションに起因するショートを防止する。

【解決手段】 配線10の接続パッド部上面には柱状電極11が設けられている。配線8の表面および柱状電極11の外周面は、ポリイミド系樹脂、PBO系樹脂等からなるエレクトロマイグレーション防止膜12によって覆われている。これにより、配線8相互間のエレクトロマイグレーションに起因するショートを防止することができる。

【選択図】 図1

#### 【特許請求の範囲】

### 【請求項1】

半導体基板と、前記半導体基板上に設けられた複数の配線と、前記配線の接続パッド部上に設けられた柱状電極と、少なくとも前記配線の表面に設けられたエレクトロマイグレーション防止膜と、前記柱状電極の周囲に設けられた封止膜とを備えていることを特徴とする半導体装置。

#### 【請求項2】

請求項1に記載の発明において、前記エレクトロマイグレーション防止膜は、少なくとも、前記配線の表面および前記柱状電極の外周面に設けられていることを特徴とする半導体装置。

【請求項3】

請求項1に記載の発明において、前記エレクトロマイグレーション防止膜は、少なくとも、前記配線の表面および前記柱状電極の下部外周面に設けられ、前記柱状電極の上部外周面は前記封止膜で覆われていることを特徴とする半導体装置。

#### 【請求項4】

請求項1に記載の発明において、前記配線は銅を含む金属によって形成され、前記柱状電極は銅によって形成されていることを特徴とする半導体装置。

#### 【請求項5】

請求項4に記載の発明において、前記エレクトロマイグレーション防止膜はポリイミド系樹脂またはPBO系樹脂によって形成されていることを特徴とする半導体装置。

【請求項6】

請求項4に記載の発明において、前記封止膜はフィラー入りのエポキシ系樹脂によって 形成されていることを特徴とする半導体装置。

#### 【請求項7】

請求項1に記載の発明において、前記柱状電極上に半田ボールが設けられていることを特徴とする半導体装置。

#### 【請求項8】

半導体基板上に複数の配線を形成する工程と、

前記配線の接続パッド部上に柱状電極を形成する工程と、

前記配線の表面、前記 柱状電極の表面および前記半導体基板上にエレクトロマイグレーション防止膜を形成する工程と、

前記エレクトロマイグレーション防止膜上に封止膜を形成する工程と、

前記柱状電極の上面に形成された前記エレクトロマイグレーション防止膜を含む前記封止膜の上面側を研削して前記柱状電極の上面を露出させる工程と、

を有することを特徴とする半導体装置の製造方法。

# 【請求項9】

半導体基板上に複数の配線を形成する工程と、

前記配線の接続パッド部上に柱状電極を形成する工程と、

前記配線の表面、前記 柱状電極の表面および前記半導体基板上にエレクトロマイグレーション防止膜を形成する工程と、

前記柱状電極の上部表面に形成された前記エレクトロマイグレーション防止膜を除去する工程と、

前記エレクトロマイグレーション防止膜および前記柱状電極上に封止膜を形成する工程と、

前記封止膜の上面側を研削して前記柱状電極の上面を露出させる工程と、

を有することを特徴とする半導体装置の製造方法。

# 【請求項10】

請求項8または9に記載の発明において、前記配線は銅を含む金属によって形成し、前記柱状電極は銅によって形成することを特徴とする半導体装置の製造方法。

# 【請求項11】

50

40

10

20

請求項10に記載の発明において、前記エレクトロマイグレーション防止膜はポリイミド系樹脂またはPBO系樹脂によって形成することを特徴とする半導体装置の製造方法。

#### 【請求項12】

請求項10に記載の発明において、前記封止膜はフィラー入りのエポキシ系樹脂によって形成することを特徴とする半導体装置の製造方法。

# 【請求項13】

請求項8または9に記載の発明において、前記柱状電極上に半田ボールを形成する工程 を有することを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

# 【技術分野】

[0001]

この発明は半導体装置およびその製造方法に関する。

#### 【背景技術】

[0002]

従来の半導体装置には、CSP(chip size package)と呼ばれるものがある(例えば、特許文献 1 参照)。この半導体装置は、上面に複数の接続パッドが設けられた半導体基板を備えている。半導体基板上に設けられた絶縁膜の上面には配線が接続パッドに接続されて設けられている。配線の接続パッド部上面には柱状電極が設けられている。配線を含む絶縁膜の上面には封止膜がその上面が柱状電極の上面と面一となるように設けられている。柱状電極の上面には半田ボールが設けられている。

[00003]

【特許文献1】特開2004-207306号公報

【発明の開示】

【発明が解決しようとする課題】

[0004]

ところで、上記従来の半導体装置では、配線を直接覆う封止膜をエポキシ系樹脂によって形成しているので、エレクトロマイグレーションの発生により、配線中の金属(銅)イオンが封止膜中に拡散し、配線相互間でショートが発生する要因の一つになるという問題があった。

[0005]

また、封止膜の材料として、エポキシ系樹脂中にシリカ等からなるフィラーを混入した ものを用いることがある。このような半導体装置では、配線がフィラーによる機械的ダメ ージを受けることがあるため、当該機械的ダメージによる配線の断線を防止するには、配 線の微細化に限界があるという問題があった。

[0006]

そこで、この発明は、配線相互間のエレクトロマイグレーションに起因するショートを防止することができ、且つ、封止膜の材料としてフィラー入りの樹脂を用いても、配線がフィラーによる機械的ダメージを受けにくいようにすることができる半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

[0007]

請求項1に記載の発明に係る半導体装置は、半導体基板と、前記半導体基板上に設けられた複数の配線と、前記配線の接続パッド部上に設けられた柱状電極と、少なくとも前記配線の表面に設けられたエレクトロマイグレーション防止膜と、前記柱状電極の周囲に設けられた封止膜とを備えていることを特徴とするものである。

請求項2に記載の発明に係る半導体装置は、請求項1に記載の発明において、前記エレクトロマイグレーション防止膜は、少なくとも、前記配線の表面および前記柱状電極の外周面に設けられていることを特徴とするものである。

請求項3に記載の発明に係る半導体装置は、請求項1に記載の発明において、前記エレクトロマイグレーション防止膜は、少なくとも、前記配線の表面および前記柱状電極の下

10

20

30

40

部外周面に設けられ、前記柱状電極の上部外周面は前記封止膜で覆われていることを特徴とするものである。

請求項4に記載の発明に係る半導体装置は、請求項1に記載の発明において、前記配線は銅を含む金属によって形成され、前記柱状電極は銅によって形成されていることを特徴とするものである。

請求項5に記載の発明に係る半導体装置は、請求項4に記載の発明において、前記エレクトロマイグレーション防止膜はポリイミド系樹脂またはPBO系樹脂によって形成されていることを特徴とするものである。

請求項 6 に記載の発明に係る半導体装置は、請求項 4 に記載の発明において、前記封止膜はフィラー入りのエポキシ系樹脂によって形成されていることを特徴とするものである

請求項7に記載の発明に係る半導体装置は、請求項1に記載の発明において、前記柱状電極上に半田ボールが設けられていることを特徴とするものである。

請求項8に記載の発明に係る発明の製造方法は、半導体基板上に複数の配線を形成する工程と、前記配線の接続パッド部上に柱状電極を形成する工程と、前記配線の表面、前記柱状電極の表面および前記半導体基板上にエレクトロマイグレーション防止膜を形成する工程と、前記エレクトロマイグレーション防止膜を形成する工程と、前記柱状電極の上面に形成された前記エレクトロマイグレーション防止膜を含む前記封止膜の上面側を研削して前記柱状電極の上面を露出させる工程と、を有することを特徴とするものである。

請求項9に記載の発明に係る発明の製造方法は、半導体基板上に複数の配線を形成する工程と、前記配線の接続パッド部上に柱状電極を形成する工程と、前記配線の表面、前記柱状電極の表面および前記半導体基板上にエレクトロマイグレーション防止膜を形成する工程と、前記柱状電極の上部表面に形成された前記エレクトロマイグレーション防止膜を除去する工程と、前記エレクトロマイグレーション防止膜および前記柱状電極上に封止膜を形成する工程と、前記封止膜の上面側を研削して前記柱状電極の上面を露出させる工程と、を有することを特徴とするものである。

請求項10に記載の発明に係る発明の製造方法は、請求項8または9に記載の発明において、前記配線は銅を含む金属によって形成し、前記柱状電極は銅によって形成することを特徴とするものである。

請求項11に記載の発明に係る発明の製造方法は、請求項10に記載の発明において、前記エレクトロマイグレーション防止膜はポリイミド系樹脂またはPBO系樹脂によって 形成することを特徴とするものである。

請求項12に記載の発明に係る発明の製造方法は、請求項10に記載の発明において、前記封止膜はフィラー入りのエポキシ系樹脂によって形成することを特徴とするものである。

請求項13に記載の発明に係る発明の製造方法は、請求項8または9に記載の発明において、前記柱状電極上に半田ボールを形成する工程を有することを特徴とするものである

# 【発明の効果】

[ 0 0 0 8 ]

この発明によれば、少なくとも配線の表面にエレクトロマイグレーション防止膜をもうけているので、配線相互間のエレクトロマイグレーションに起因するショートを防止することができる。また、エレクトロマイグレーション防止膜が保護膜として機能することにより、封止膜の材料としてフィラー入りの樹脂を用いても、配線がフィラーによる機械的ダメージを受けにくいようにすることができる。

【発明を実施するための最良の形態】

[0009]

(第1実施形態)

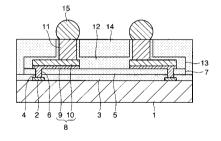

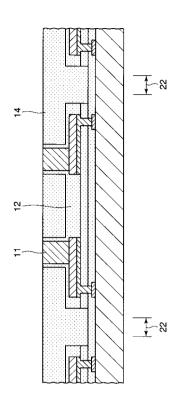

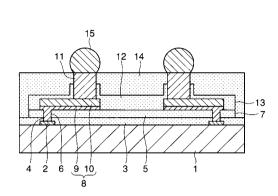

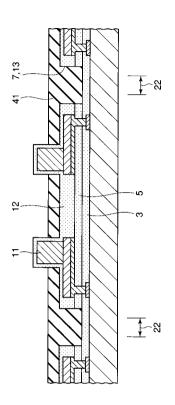

図1はこの発明の第1実施形態としての半導体装置の断面図を示す。この半導体装置は

20

10

30

40

、 C S P と呼ばれるもので、シリコン基板(半導体基板) 1 を備えている。シリコン基板 1 の上面には集積回路(図示せず)が設けられ、上面周辺部にはアルミニウム系金属等からなる複数の接続パッド 2 が集積回路に接続されて設けられている。

#### [0010]

接続パッド2の中央部を除くシリコン基板1の上面には酸化シリコンや窒化シリコン等の無機材料からなる絶縁膜3が設けられ、接続パッド2の中央部は絶縁膜3に設けられた開口部4を介して露出されている。絶縁膜3の上面にはポリイミド系樹脂、PBO(Poly Benzo Oxysazole)系樹脂等の有機樹脂からなる保護膜5が設けられている。絶縁膜3の開口部4に対応する部分における保護膜5には開口部6が設けられている。保護膜5の周辺部には凹部7が設けられている。

[0011]

保護膜5の上面には配線8が設けられている。配線8は、保護膜5の上面に設けられた銅等からなる下地金属層9と、下地金属層9の上面に設けられた銅からなる上部金属層10との2層構造となっている。配線8の一端部は、絶縁膜3および保護膜5の開口部4、6を介して接続パッド2に接続されている。配線8の接続パッド部上面には銅からなる柱状電極11が設けられている。

[0012]

配線 8 の表面、柱状電極 1 1 の外周面および保護膜 5 の上面にはポリイミド系樹脂、 P B O 系樹脂等からなるエレクトロマイグレーション防止膜 1 2 が設けられている。保護膜 5 の凹部 7 に対応する部分におけるエレクトロマイグレーション防止膜 1 2 の周辺部には凹部 1 3 が設けられている。

[0013]

保護膜5およびエレクトロマイグレーション防止膜12の凹部7、13を介した露出された絶縁膜3の上面およびエレクトロマイグレーション防止膜12の上面にはシリカ等からなるフィラー入りのエポキシ系樹脂からなる封止膜14がその上面が柱状電極11の上面と面一となるように設けられている。柱状電極11の上面には半田ボール15が設けられている。

[0014]

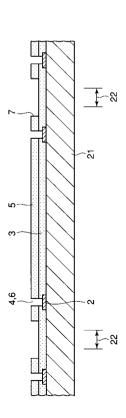

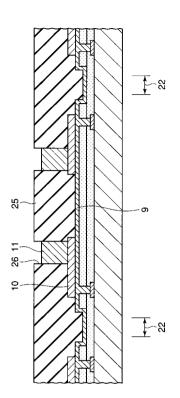

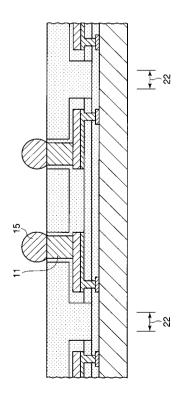

次に、この半導体装置の製造方法の一例について説明する。まず、図2に示すように、ウエハ状態のシリコン基板(以下、半導体ウエハ21という)の上面にアルミニウム系金属等からなる接続パッド2、酸化シリコンや窒化シリコン等からなる絶縁膜3およびポリイミド系樹脂、PBO系樹脂等からなる保護膜5が形成され、接続パッド2の中央部が絶縁膜3および保護膜5に形成された開口部4、6を介して露出されたものを用意する。

[0015]

この場合、半導体ウエハ 2 1 の上面において各半導体装置が形成される領域には所定の機能の集積回路(図示せず)が形成され、接続パッド 2 はそれぞれ対応する部分に形成された集積回路に電気的に接続されている。なお、図 2 において、符号 2 2 で示す領域はダイシングラインに対応する領域である。そして、ダイシングライン 2 2 およびその両側に対応する部分における保護膜 5 には凹部 7 が形成されている。

[0016]

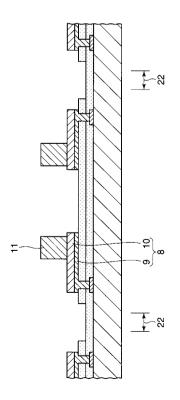

次に、図3に示すように、絶縁膜3および保護膜5の開口部4、6を介して露出された接続パッド2の上面を含む保護膜5の上面全体に下地金属層9を形成する。この場合、下地金属層9は、無電解メッキにより形成された銅層のみであってもよく、またスパッタにより形成された銅層のみであってもよく、さらにスパッタにより形成されたチタン等の薄膜層上にスパッタにより銅層を形成したものであってもよい。

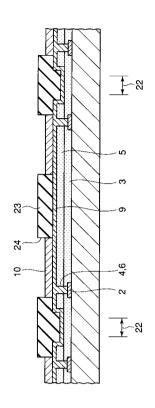

[0017]

次に、下地金属層9の上面にメッキレジスト膜23をパターン形成する。この場合、上部金属層10形成領域に対応する部分におけるメッキレジスト膜23には開口部24が形成されている。次に、下地金属層9をメッキ電流路とした銅の電解メッキを行なうことにより、メッキレジスト膜23の開口部24内の下地金属層9の上面に上部金属層10を形

10

20

30

40

成する。次に、メッキレジスト膜23を剥離する。

### [0018]

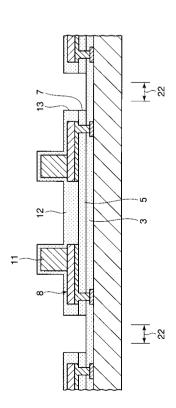

次に、図4に示すように、上部金属層10を含む下地金属層9の上面にメッキレジスト膜25をパターン形成する。この場合、上部金属層10の接続パッド部つまり柱状電極11形成領域に対応する部分におけるメッキレジスト膜25には開口部26が形成されている。次に、下地金属層9をメッキ電流路とした銅の電解メッキを行なうことにより、メッキレジスト膜25の開口部26内の上部金属層10の接続パッド部上面に柱状電極11を形成する。

# [0019]

次に、メッキレジスト膜25を剥離し、次いで、上部金属層10をマスクとして上部金属層10下以外の領域における下地金属層9をエッチングして除去すると、図5に示すように、上部金属層10下にのみ下地金属層9が残存される。この状態では、下地金属層9 およびその上面に形成された上部金属層10により、配線8が形成されている。

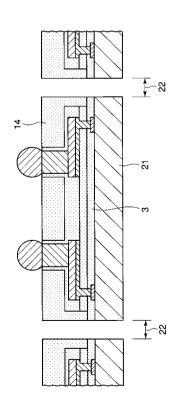

# [0020]

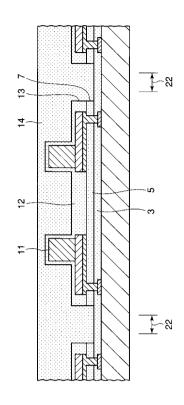

次に、図6に示すように、配線8の表面、柱状電極11の外周面および保護膜5の上面に、スピンコート法等により、ポリイミド系樹脂、PBO系樹脂等からなるエレクトロマイグレーション防止膜12を形成する。次に、保護膜5の凹部7に対応する部分におけるエレクトロマイグレーション防止膜12に、フォトリソグラフィ法により、凹部13を形成する。

# [0021]

次に、図7に示すように、保護膜5およびエレクトロマイグレーション防止膜12の凹部7、13を介した露出された絶縁膜3の上面およびエレクトロマイグレーション防止膜12の上面に、スクリーン印刷法、スピンコート法等により、シリカ等からなるフィラー入りのエポキシ系樹脂からなる封止膜14をその厚さが柱状電極11の高さ(柱状電極11の上面に形成されたエレクトロマイグレーション防止膜12の厚さを含む)よりも厚くなるように形成する。

# [0022]

次に、柱状電極11の上面に形成されたエレクトロマイグレーション防止膜12を含む 封止膜14の上面側を適宜に研削して除去することにより、図8に示すように、柱状電極 11の上面およびその外周面に形成されたエレクトロマイグレーション防止膜12の上面 を露出させるとともに、これらの露出面を含む封止膜14の上面を平坦化する。

# [0023]

次に、図9に示すように、柱状電極11の上面に半田ボール15を形成する。次に、図10に示すように、半導体ウエハ21、絶縁膜3および封止膜14をダイシングライン22に沿って切断すると、図1に示す半導体装置が複数個得られる。

# [0024]

このようにして得られた半導体装置では、図1に示すように、配線8の表面および柱状電極11の外周面をポリイミド系樹脂、PBO系樹脂等からなるエレクトロマイグレーション防止膜12で覆っているので、配線8相互間でエレクトロマイグレーションが発生することがなく、配線8のエレクトロマイグレーションに起因するショートを防止することができる。

#### [0025]

また、図1に示す半導体装置では、配線8の表面をポリイミド系樹脂、PBO系樹脂等からなるエレクトロマイグレーション防止膜12で覆っているので、エレクトロマイグレーション防止膜12が保護膜として機能することにより、封止膜14の材料としてシリカ等からなるフィラー入りのエポキシ系樹脂を用いても、配線8がフィラーによる機械的ダメージを受けにくいようにすることができる。

# [0026]

ところで、図1に示す半導体装置では、柱状電極11の外周面全体をエレクトロマイグレーション防止膜12で覆い、柱状電極11の上面に半田ボール15を設けているので、

10

20

30

40

柱状電極11の外周面を覆っているエレクトロマイグレーション防止膜12の上面が露出されている。この場合、エレクトロマイグレーション防止膜12をポリイミド系樹脂または PBO系樹脂によって形成すると、これらの樹脂が吸湿性を有するため、耐湿信頼性が低下してしまう。そこで、次に、耐湿信頼性を向上することができるこの発明の第2実施形態について説明する。

# [0027]

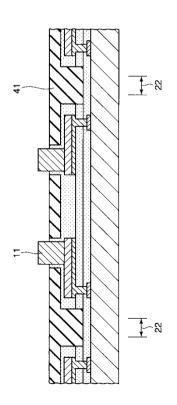

(第2実施形態)

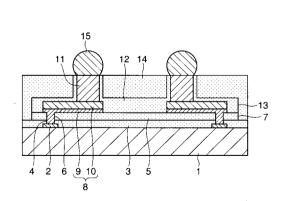

図11はこの発明の第2実施形態としての半導体装置の断面図を示す。この半導体装置において、図1に示す半導体装置と異なる点は、柱状電極11の下部外周面をエレクトロマイグレーション防止膜12で覆い、柱状電極11の上部外周面を封止膜14で覆った点である。

[0028]

次に、この半導体装置の製造方法の一例について説明する。この場合、図6に示す工程後に、図12に示すように、絶縁膜5およびエレクトロマイグレーション防止膜12の凹部7、13を介して露出された絶縁膜3の上面および柱状電極11の外周面に形成されたエレクトロマイグレーション防止膜12を除くエレクトロマイグレーション防止膜12の上面に、スピンコート法等により、レジスト膜41を形成する。この場合、柱状電極11の周囲におけるエレクトロマイグレーション防止膜12の上面に形成されたレジスト膜41の厚さは柱状電極11の高さのほぼ半分となっている。

[0029]

次に、レジスト膜41の上面よりも上側に突出された柱状電極11の上部外周面に形成されたエレクトロマイグレーション防止膜12をエッチングして除去すると、図13に示すように、レジスト膜41の上面よりも上側に突出された柱状電極11の上部外周面が露出される。以下、上記第1実施形態における製造方法と同様に、封止膜形成工程、半田ボール形成工程およびダイシング工程を経ると、図11に示すように、柱状電極11の上部外周面が封止膜14で覆われた構造の半導体装置が複数個得られる。

[0030]

このようにして得られた半導体装置では、図11に示すように、柱状電極11の上部外周面を水分を通さないエポキシ系樹脂からなる封止膜14で覆っているので、耐湿信頼性を向上することができる。なお、封止膜14をシリカ等からなるフィラー入りのエポキシ系樹脂によって形成しても、同様に、耐湿信頼性を向上することができる。

【図面の簡単な説明】

[0031]

- 【図1】この発明の第1実施形態としての半導体装置の断面図。

- 【図2】図1に示す半導体装置の製造方法の一例において、当初用意したものの断面図。

- 【図3】図2に続く工程の断面図。

- 【図4】図3に続く工程の断面図。

- 【図5】図4に続く工程の断面図。

- 【図6】図5に続く工程の断面図。

- 【図7】図6に続く工程の断面図。

- 【図8】図7に続く工程の断面図。

- 【図9】図8に続く工程の断面図。

- 【図10】図9に続く工程の断面図。

- 【図11】この発明の第2実施形態としての半導体装置の断面図。

- 【図12】図11に示す半導体装置の製造方法の一例において、所定の工程の断面図。

- 【図13】図12に続く工程の断面図。

【符号の説明】

[0032]

- 1 シリコン基板

- 2 接続パッド

20

10

30

40

- 3 絶縁膜

- 5 保護膜

- 8 配線

- 1 1 柱状電極

- 12 エレクトロマイグレーション防止膜

- 1 4 封止膜

- 15 半田ボール

【図1】 【図2】

【図3】 【図4】

【図5】 【図6】

【図7】 【図8】

【図9】 【図10】

【図11】 【図12】

【図13】

# フロントページの続き

F ターム(参考) 5F033 HH11 HH18 JJ11 JJ18 KK08 KK11 KK18 MM05 MM13 NN06 NN07 NN19 PP15 PP27 PP28 QQ27 QQ42 RR04 RR06 RR22

RR25 SS21 TT04 VV07 XX05 XX31