# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

**G09G 3/36** (2006.01) **G09G 3/3266** (2016.01)

(52) CPC특허분류

**G09G 3/3674** (2013.01) **G09G 3/3266** (2013.01)

(21) 출원번호 10-2022-7042045

(22) 출원일자(국제) **2022년06월09일** 심사청구일자 **2022년11월30일**

(85) 번역문제출일자 **2022년11월30일**

(86) 국제출원번호 PCT/CN2022/097860

(87) 국제공개번호 **WO 2023/005443** 국제공개일자 **2023년02월02일**

(30) 우선권주장

202110876023.9 2021년07월30일 중국(CN)

(11) 공개번호 10-2023-0019251

(43) 공개일자 2023년02월07일

(71) 출원인

#### 에이치케이씨 코포레이션 리미티드

중국 선전 보우안 디스트릭트 스룽 커뮤니티 스옌 스트리트 후이커 인더스트리얼 파크 넘버 1 인더 스트리얼 세컨드 로드, 7 에프 오브 팩토리 빌딩 6, 5 에프-7 에프 오브 팩토리 빌딩 1, 제 1-3 에 프

(72) 발명자

#### 쉔, 팅팅

중국 518000 광동 센젠 보우안 디스트릭트 스룽커뮤니티 스옌 스트리트 후이커 인더스트리얼 파크 넘버 1 인더스트리얼 세컨드 로드 7 에프 오브 팩토리 빌딩 6 5 에프-7 에프 오브 팩토리 빌딩 1 1-3 에프

#### 캉, 바오홍

중국 518000 광동 센젠 보우안 디스트릭트 스롱 커뮤니티 스옌 스트리트 후이커 인더스트리얼 파 크 넘버 1 인더스트리얼 세컨드 로드 7 에프 오브 팩토리 빌딩 6 5 에프-7 에프 오브 팩토리 빌딩 1 1-3 에프

(74) 대리인

이창훈

전체 청구항 수 : 총 15 항

## (54) 발명의 명칭 디스플레이 패널 제어 회로 및 디스플레이 장치

#### (57) 요 약

본 발명은 디스플레이 패널(2)의 제어 회로(10) 및 디스플레이 장치(1)를 개시하며, 해당 디스플레이 패널의 제어 회로(10)는 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호를 수신하는 데 사용되며, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라, 상기 제1 클럭 신호에 대한 위상변위를 통해 획득한 제2 클럭 신호를 게이트 구동 회로(20)로 출력하여, 클럭 신호의 위상변위를 구현하여 단일 클럭 신호의 부하를 감소시키고, 디스플레이 패널(2)에 있는 클럭 발생기의 수량을 줄여주고, 디스플레이 패널(2)의 생산 원가를 줄일 수 있다.

#### 대 표 도 - 도1

(52) CPC특허분류 *G09G 2310/0267* (2013.01)

G09G 2310/08 (2013.01)

## 명세서

## 청구범위

#### 청구항 1

디스플레이 패널 제어 회로에 있어서,

상기 제어 회로는 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호를 수신하는 데 사용되며, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라, 상기 제1 클럭 신호를 위상변위시켜 제2 클럭 신호를 얻어 게이트 구동 회로로 출력하며; 이 중, 상기 제2 클럭 신호는 제3 레벨 신호와 제4 레벨 신호를 포함하며, 상기 제3 레벨 신호와 상기 제4 레벨 신호의 레벨은 고저가 상이하며;

상기 제어 회로는 제1 스위치 유닛과 제2 스위치 유닛을 포함하며, 상기 제1 스위치 유닛은 상기 제2 스위치 유닛에 접속되며;

상기 제1 스위치 유닛은, 상기 제1 클럭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호를 수신하고, 상기 제 1 클럭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라 제3 레벨 신호를 상기 게이트 구동 회로로 출 력하는 데 사용되며;

상기 제2 스위치 유닛은, 상기 제1 클럭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호를 수신하고, 상기 제 1 클럭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라 제4 레벨 신호를 상기 게이트 구동 회로로 출 력하는 데 사용되는 것을 특징으로 하는 디스플레이 패널 제어 회로.

### 청구항 2

제1항에 있어서,

상기 제1 스위치 유닛은, 상기 제1 클럭 신호가 로우 레벨일 때, 상기 제1 클럭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라 상기 게이트 구동 회로를 도통시키고 제3 레벨 신호를 해당 회로로 출력하는 데에도 사용되며,상기 제3 레벨 신호는 하이 레벨인 것을 특징으로 하는 디스플레이 패널 제어 회로.

### 청구항 3

제1항에 있어서,

상기 제1 스위치 유닛은, 상기 제1 클럭 신호가 하이 레벨일 경우, 상기 제1 클럭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라, 상기 게이트 구동 회로를 차단하고 해당 회로에 대한 상기 제3 레벨 신호 출력을 중단하는 데에도 사용하는 것을 특징으로 하는 디스플레이 패널 제어 회로.

## 청구항 4

제1항에 있어서,

상기 제2 스위치 유닛은, 상기 제1 클럭 신호가 하이 레벨일 경우, 상기 제1 클럭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라 상기 게이트 구동 회로를 도통시켜 해당 회로로 제4 레벨 신호를 출력하는 데에도 사용되고 상기 제4 레벨 신호는 로우 레벨인 것을 특징으로 하는 디스플레이 패널 제어 회로.

### 청구항 5

제1항에 있어서,

상기 제2 스위치 유닛은, 상기 제1 클럭 신호가 로우 레벨일 경우, 상기 제1 클럭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라 상기 게이트 구동 회로를 차단하고 해당 회로에 대한 상기 제4 레벨 신호 출력을 중 단하는 데에도 사용하는 것을 특징으로 하는 디스플레이 패널 제어 회로.

#### 청구항 6

제1항에 있어서,

상기 제1 스위치 유닛은 제1 전자 스위치, 제2 전자 스위치, 제3 전자 스위치, 제4 전자 스위치, 제5 전자 스위치 및 제1 커패시터를 포함하며;

상기 제1 전자 스위치의 드레인은 상기 제2 전자 스위치의 게이트와 접속되며, 상기 제1 전자 스위치의 게이트 와 소스는 상기 제1 클럭 신호를 수신하는 데 사용되며;

상기 제2 전자 스위치의 드레인은 상기 제4 전자 스위치의 소스와 접속되며, 상기 제2 전자 스위치의 소스는 상기 제1 레벨 신호를 수신하는 데 사용되며;

상기 제3 전자 스위치의 드레인은 상기 제5 전자 스위치의 소스 및 제4 전자 스위치의 게이트에 각각 접속되며, 상기 제3 전자 스위치의 소스는 상기 제1 레벨 신호를 수신하는 데 사용되며;

상기 제1 커패시터의 제1극은 상기 제1 전자 스위치의 드레인 및 상기 제2 전자 스위치의 게이트에 각각 접속되고, 상기 제5 전자 스위치의 드레인은 상기 제2 레벨 신호를 수신하는 데 사용되며;

상기 제3 전자 스위치의 게이트, 상기 제5 전자 스위치의 드레인, 상기 제4 전자 스위치의 드레인 및 상기 제1 캐패시터의 제2극은 각각 상기 제2 스위치 유닛과 전기적으로 접속되는 것을 특징으로 하는 디스플레이 패널 제 어 회로.

#### 청구항 7

제1항에 있어서,

상기 제2 스위치 유닛은 제6 전자 스위치, 제7 전자 스위치 및 제8의 전자 스위치를 포함하며;

상기 제6 전자 스위치의 드레인은 제3 전자 스위치의 게이트 및 상기 제7 전자 스위치 소스에 각각 접속되며, 상기 제6 전자 스위치의 게이트 및 소스는 상기 제1 레벨 신호를 수신하는 데 사용되며;

상기 제7 전자 스위치의 드레인은 제5 전자 스위치의 드레인 및 상기 제8 전자 스위치의 소스에 각각 접속되며, 상기 제7 전자 스위치의 게이트는 상기 제1 클럭 신호를 수신하는 데 사용되며, 상기 제7 전자 스위치의 드레인 은 상기 제2 레벨 신호를 수신하는 데 사용되며;

상기 제8 전자 스위치의 드레인은 상기 제5 전자 스위치의 드레인 및 제1 커패시터의 제2극과 각각 접속되며, 상기 제8 전자 스위치의 게이트는 상기 제1 클럭 신호를 수신하는 데 사용되는 것을 특징으로 하는 디스플레이 패널 제어 회로.

### 청구항 8

제1항에 있어서,

상기 제어 회로는:

상기 제1 클럭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호를 수신하는 데 사용되며, 상기 제1 클럭 신호 가 하이 레벨일 경우, 상기 제1 클럭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라, 상기 게이트 구동 회로를 도통시켜 제5 레벨 신호를 해당 회로로 출력하며, 상기 제5 레벨 신호는 하이 레벨이며; 또한, 상기 제1 클럭 신호가 로우 레벨일 경우, 상기 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호에 따라, 상기 게이트 구동 회로를 도통시키고 제5 레벨 신호를 해당 회로로 출력하는 데에도 사용하며, 상기 제5 레벨 신호는 로우 레벨인 제3 스위치 유닛을 포함하는 것을 특징으로 하는 디스플레이 패널 제어 회로.

#### 청구항 9

제1항에 있어서,

상기 제어 회로는: 제3 스위치 유닛과 연결되어, 상기 제1 클릭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호를 수신하는 데 사용되며, 상기 제1 클릭 신호가 하이 레벨일 경우, 상기 제1 클릭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라 상기 게이트 구동 회로를 도통 시키고 제6 레벨 신호를 해당 회로로 출력하며, 상기 제6 레벨 신호는 로우 레벨이며; 또한, 제1 클릭 신호가 로우 레벨일 경우, 상기 제1 클릭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라, 회로 차단 및 상기 제6 레벨 신호 출력을 중단하는 데에도 사용하는 제4 스위치 유닛을 포함하며;

이 중, 상기 제2 클럭 신호는 제5 레벨 신호 및 제6 레벨 신호를 포함하는 것을 특징으로 하는 디스플레이 패널 제어 회로.

### 청구항 10

제8항에 있어서,

상기 제3 스위치 유닛은 제9 전자 스위치, 제10 전자 스위치, 제11 전자 스위치, 제12 전자 스위치, 제13 전자 스위치, 제2 캐패시터 및 제3 캐패시터를 포함하며;

상기 제9 전자 스위치의 드레인은 상기 제10 전자 스위치의 게이트,상기 제13 전자 스위치의 소스 및 상기 제2 커패시터의 제1 극에 각각 접속되며, 제9 전자 스위치의 소스는 상기 제1 레벨 신호를 수신하는 데 사용되며;

상기 제10 전자 스위치의 드레인은 상기 제2 커패시터의 제2극 및 제12 전자 스위치의 소스에 접속되며, 상기 제10 전자 스위치의 소스는 상기 제1 레벨 신호를 수신하는 데 사용되며;

상기 제11 전자 스위치의 드레인과 소스는 상기 제1 클럭 신호를 수신하는 데 사용되며;

상기 제12 전자 스위치의 게이트는 상기 제3 커패시터의 제1극 및 상기 제11 전자 스위치의 드레인에 각각 접속하며;

상기 제13 전자 스위치의 게이트는 상기 제1 클럭 신호를 수신하는 데 사용되며;

상기 제9 전자 스위치의 게이트, 상기 제12 전자 스위치의 드레인, 상기 제13 전자 스위치의 드레인 및 상기 제3 캐패시터의 제2극은 각각 제4 스위치 유닛과 전기적으로 연결되는 것을 특징으로 하는 디스플레이 패널 제어회로.

#### 청구항 11

제9항에 있어서,

제4 스위치 유닛은 제14 전자 스위치, 제15 전자 스위치 및 제16 전자 스위치를 포함하며;

상기 제14 전자 스위치의 드레인은 상기 제9 전자 스위치의 게이트 및 상기 제15 전자 스위치 소스에 각각 접속되며, 상기 제14 전자 스위치의 게이트 및 소스는 상기 제1 레벨 신호를 수신하는 데 사용되며;

상기 제15 전자 스위치의 드레인은 상기 제13 전자 스위치의 드레인 및 제16 전자 스위치의 소스에 각각 접속되며, 상기 제15 전자 스위치의 게이트는 상기 제1 클럭 신호를 수신하는 데 사용되며, 상기 제15 전자 스위치의 드레인은 상기 제2 레벨 신호를 수신하는 데 사용되며;

상기 제16 전자 스위치의 드레인은 제12 전자 스위치의 드레인 및 제3 커패시터의 제2극과 각각 접속되며, 상기 제16 전자 스위치의 게이트는 상기 제1 클럭 신호를 수신하는 데 사용되는 것을 특징으로 하는 디스플레이 패널 제어 회로.

### 청구항 12

제1항에 있어서,

상기 제1 레벨 신호는 하이 레벨 신호이고, 상기 제2 레벨 신호는 로우 레벨 신호인 것을 특징으로 하는 디스플 레이 패널 제어 회로.

#### 청구항 13

제1항에 있어서,

상기 제2 클럭 신호와 상기 제1 클럭 신호의 위상차 범위는 0°내지 180°인 것을 특징으로 하는 디스플레이 패널 제어 회로.

#### 청구항 14

제1항에 있어서,

상기 제어 회로는 상기 제1 레벨 신호 및 상기 제2 레벨 신호의 타이밍에 따라 상기 제2 클럭 신호와 상기 제1 클럭 신호의 위상차를 확정하는 것을 특징으로 하는 디스플레이 패널 제어 회로.

### 청구항 15

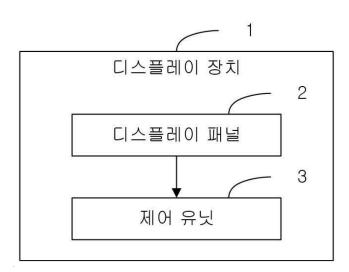

디스플레이 장치에 있어서,

이 중에는:

디스플레이 패널;

및 제어 유닛을 포함하며, 이 중, 상기 제어 유닛은 청구항 제1항에 기재된 제어 회로를 포함하는 것을 특징으로 하는 디스플레이 장치.

### 발명의 설명

#### 기술분야

- [0001] 본 발명은 2021년 07월 30일,중화인민공화국 특허청에 제출된 출원번호 202110876023.9, 명칭이 "디스플레이 패널 제어 회로 및 디스플레이 장치"인 발명에 대한 중국특허출원의 우선권을 청구하며, 해당 발명의 전부 내용은 인용의 방식으로 본 발명에 포함된다.

- [0002] 본 발명은 디스플레이 기술 분야에 관한 것으로, 특히 디스플레이 패널 제어 회로 및 디스플레이 장치에 관한 것이다.

#### 배경기술

- [0003] 디스플레이 기술의 빠른 발전으로 디스플레이 패널은 엔터테인먼트, 교육, 보안 등과 같은 다양한 분야에서 널리 사용되고 있다. GDL(Gate Driver Less, 어레이 기판 행구동) 기술은 어레이(Array) 기판 상에 게이트 구동 회로(Gate driver IC)를 직접 제작하고, 행구동 신호를 출력하여 게이트 행을 순차적으로 스캔하는 것을 지칭한다. GDL 기술은 디스플레이 패널의 제작 과정을 단순화하고, 수평 주사선 방향을 따른 칩 본딩(Bonding) 작업 과정을 제거하며, 생산 원가를 절감하며, 디스플레이 패널의 집적도를 향상시켜 디스플레이 패널을 더욱 가볍고얇게 제작할 수 있다.

- [0004] GDL 기술을 채택한 디스플레이 패널은 행 구동 신호를 출력하기 위해 다수 클럭 신호를 사용하여 게이트 구동 회로를 제어해야 하며, 디스플레이 패널의 사이즈 및 해상도가 지속적으로 개선됨에 따라 디스플레이 패널별 게

이트 구동 회로 수량도 지속적으로 증가되어 단일 클럭 신호의 과부하로 이어져 디스플레이 패널의 실행 안정성 이 저하된다.

## 발명의 내용

## 해결하려는 과제

[0005] 본 발명의 실시예의 목적 중 하나로: 디스플레이 패널의 제어 회로 및 디스플레이 장치를 제공하는 것으로, GDL 기술을 이용한 기존 디스플레이 패널의 게이트 구동 회로 수가 지속적으로 증가하여 단일 클럭 신호의 과부하로 이어져, 디스플레이 패널 실행 안전성이 저하되는 문제점을 해결하는 데 있다.

### 과제의 해결 수단

- [0006] 본 발명의 실시예에서 채택된 기술방안은 다음과 같다:

- [0007] 첫번째 측면에서, 디스플레이 패널의 제어 회로를 제공하며, 상기 제어 회로는 제1 클릭 신호, 제1 레벨 신호 및 제2 레벨 신호를 수신하는 데 사용되며, 상기 제1 레벨 신호 및 제2 레벨 신호에 따라, 제1 클릭 신호를 위상변위 시켜 제2 클릭 신호를 얻어 게이트 구동 회로로 출력하며; 이 중, 상기 제2 클릭 신호는 제3 레벨 신호와 사기 제4 레벨 신호의 레벨은 고저가 상이하며;

- [0008] 상기 제어 회로는 제1 스위치 유닛과 제2 스위치 유닛을 포함하며, 상기 제1 스위치 유닛은 상기 제2 스위치 유닛에 접속되며;

- [0009] 상기 제1 스위치 유닛은 상기 제1 클럭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호를 수신하고, 상기 제1 클럭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라 제3 레벨 신호를 게이트 구동 회로로 출력하는데 사용되며;

- [0010] 상기 제2 스위치 유닛은 상기 제1 클럭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호를 수신하고, 상기 제1 클럭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라 제4 레벨 신호를 상기 게이트 구동 회로로 출력하는 데 사용된다.

- [0011] 두번째 측면에서, 디스플레이 패널를 포함하는 표시 장치;

- [0012] 및 상기 제어 유닛을 제공하며, 이 중, 상기 제어 유닛은 첫번째 측면에 기재된 제어 회로를 포함한다.

### 발명의 효과

- [0013] 본 발명의 실시예는 첫번째 측면을 통해 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호를 수신하는 데 사용되는 디스플레이 패널 제어 회로를 제공하며, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라, 상기 제1 클럭 신호에 대한 위상변위를 통해 획득한 제2 클럭 신호를 게이트 구동 회로로 출력하여, 클럭 신호의 위상변위를 구현하여 단일 클럭 신호의 부하를 감소시키고, 디스플레이 패널에 있는 클럭 발생기의 수량을 줄여주고, 디스플레이 패널의 생산 원가를 줄일 수 있다.

- [0014] 상기 두번째 측면의 유익한 효과는 상기 첫번째 측면의 관련 설명을 참조할 수 있으며 이 부분에서 더 이상 설명하지 않음은 자명하다.

## 도면의 간단한 설명

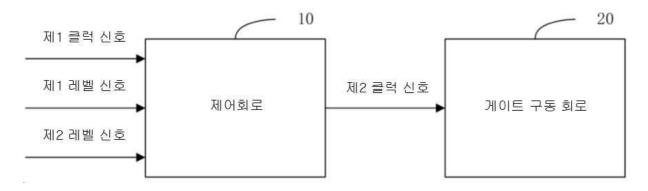

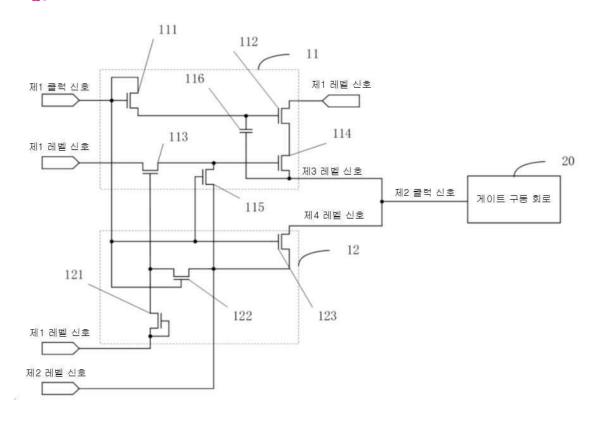

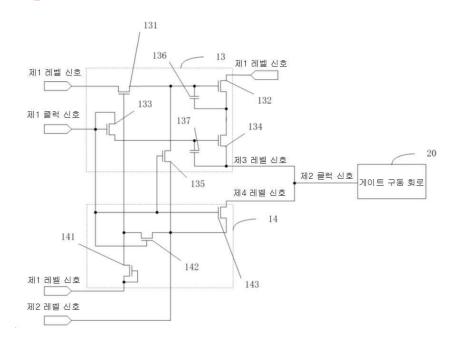

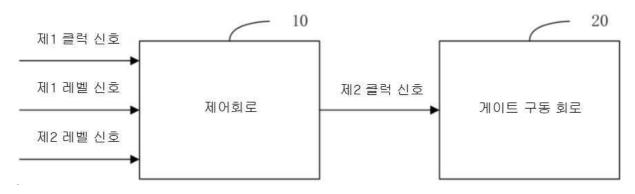

[0015] 도 1은 본 발명의 실시예에 따른 디스플레이 패널 제어 회로의 제1 유형의 구조 개략도;

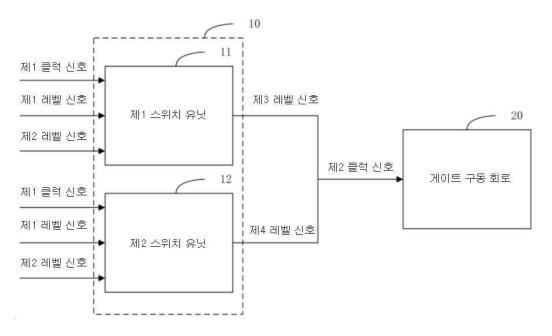

도 2는 본 발명의 실시예에 따른 디스플레이 패널 제어 회로의 제2 유형의 구조 개략도;

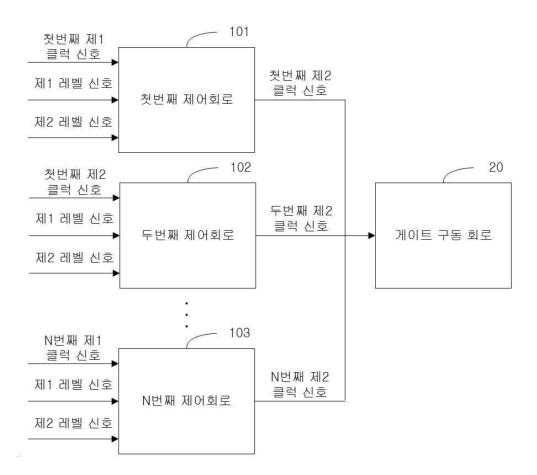

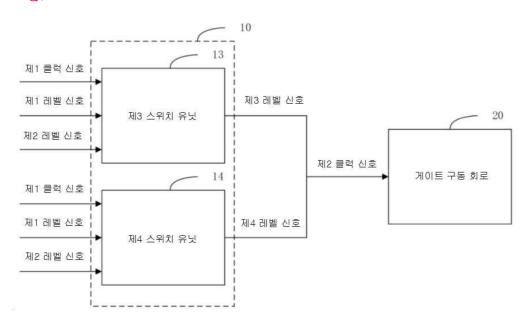

도 3은 본 발명의 실시예에 따른 디스플레이 패널 제어 회로의 제3 유형의 구조 개략도;

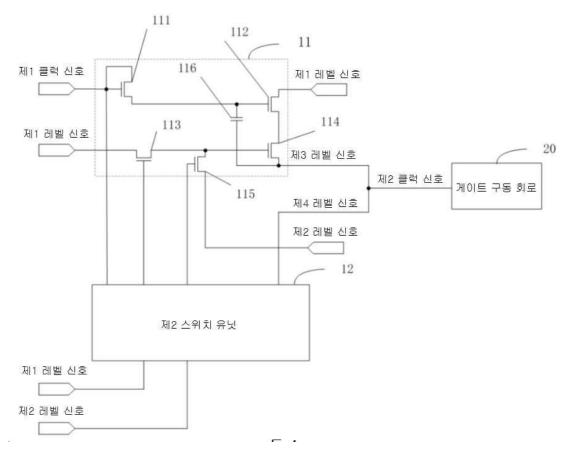

도 4는 본 발명의 실시예에 따른 디스플레이 패널 제어 회로의 제4 유형의 구조 개략도;

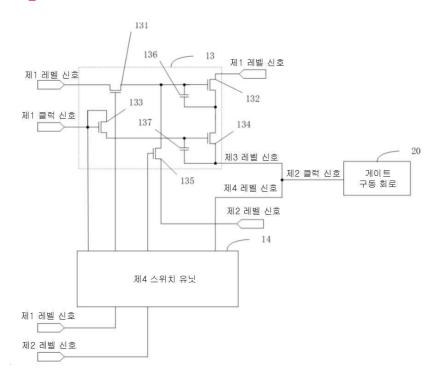

도 5는 본 발명의 실시예에 따른 디스플레이 패널 제어 회로의 제5 유형의 구조 개략도;

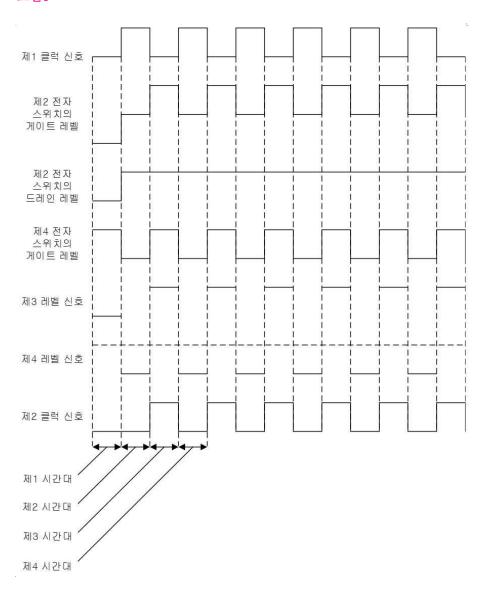

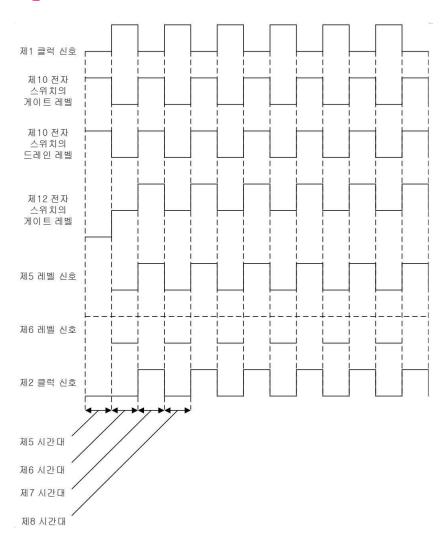

도 6은 본 발명의 실시예에 따른 제1 클럭 신호, 제2 전자 스위치의 게이트 레벨, 제2 전자 스위치의 드레인 레벨, 제4 전자 스위치의 게이트 레벨, 제3 레벨 신호, 제4 레벨 신호 및 제2 클럭 신호의 타이밍 다이어그램;

도 7은 본 발명의 실시예에 따른 디스플레이 패널 제어 회로의 제6 유형의 구조 개략도;

도 8은 본 발명의 실시예에 따른 디스플레이 패널 제어 회로의 제7 유형의 구조 개략도;

도 9는 본 발명의 실시예에 따른 디스플레이 패널 제어 회로의 제8 유형의 구조 개략도;

도 10은 본 발명의 실시예에 따른 제1 클럭 신호, 제10 전자 스위치의 게이트 레벨, 제10 전자 스위치의 드레인 레벨, 제12 전자 스위치의 게이트 레벨, 제5 레벨 신호, 제6 레벨 신호 및 제2 클럭 신호의 타이밍 다이어그램;.

도 11은 본 발명의 실시예에 따른 표시 장치 구조 개략도.

#### 발명을 실시하기 위한 구체적인 내용

- [0016] 하기의 내용은 본 발명을 한정하기 위함이 아니라 본 발명의 실시예를 보다 충분히 이해할 수 있도록 특정 시스템 구조, 기술 등의 구체적인 내용을 안출한다. 단, 본 업계의 당업자라면 이러한 구체적인 세부 사항이 없는다른 실시예를 통해서도 본 발명을 구현할 수 있음은 자명하다. 다른 경우에, 본 발명에 대한 설명을 방해하는 불필요한 세부 사항을 피하기 위해 주지하는 시스템, 장치, 회로 및 방법에 대한 자세한 설명을 생략한다.

- [0017] 별도로, 본 발명의 명세서 및 첨부된 청구항들에 있어서, "제1", "제2", "제3" 등의 용어는 설명을 구분하기 위한 것일 뿐, 상대적 중요성을 나타내거나 암시하는 것으로 이해하지 말아야 한다.

- [0018] 본 발명의 명세서에 기재된 "일 실시예", "일부 실시예" 등은 본 발명의 1개 또는 다수 실시예에 이와 같은 실시예가 설명하는 특정 특징, 구조 또는 특성에 대한 결합을 포함함을 의미한다. 따라서, 본 명세서의 상이한 단락에 나타난 "일 실시예에서", "일부 실시예에서", "다른 일부 실시예에서", "또 다른 일부 실시예에서" 등과 같은 문구는 반드시 전부 동일한 실시예를 참조하고 있음을 의미하지 않으며, 기타 방식을 통해 특별 강조하지 않는 한 "1개 또는 다수지만 전부가 아닌 실시예"를 의미한다. "포괄", "포함", "구비" 등의 용어 및 이들의 변형은 특별히 강조되지 않는 한 모두 "포함하지만 이에 제한되지 않음"을 의미한다.

- [0019] 본 발명의 실시예는 디스플레이 패널에 적용될 수 있는 디스플레이 패널 제어 회로를 제공하며, 디스플레이 패널은 TFT-LCD(Thin Film Transistor Liquid Crystal Display, 박막 트랜지스터 액정 디스플레이) 기술 기반의 액정 디스플레이 패널, LCD(Liquid Crystal Display, 액정 디스플레이) 기술 기반의 액정 디스플레이 패널, OLED(Organic Light-Emitting Diode, 유기 발광 다이오드) 기술 기반의 유기 전자레이저 디스플레이 패널, QLED(Quantum Dot Light Emitting Diode,양자점 발광 다이오드) 기술 기반 양자점 발광 다이오드 디스플레이 패널 또는 곡면 디스플레이 패널 등이 있다.

- [0020] 도 1 또는 도 2에 도시된 바와 같이, 본 발명의 실시예를 통해 제공되는 디스플레이 패널의 제어 회로(10)는 제 1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호를 수신하기 위해 사용되며, 제1 레벨 신호와 제2 레벨 신호에 따라, 제1 클럭 신호를 위상변위하여 얻은 제2 클럭 신호를 게이트 구동 회로(20)로 출력하며; 이 중, 제2 클럭 신호는 제3 레벨 신호와 제4 레벨 신호와 제4 레벨 신호의 레벨은 고저가 상이하며;

- [0021] 제어 회로(10)는 제1 스위치 유닛(11)과 제2 스위치 유닛(12)을 포함하며, 제1 스위치 유닛(11)은 제2 스위치 유닛(12)에 접속되며;

- [0022] 제1 스위치 유닛(11)은 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호를 수신하는 데 사용되며, 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호에 따라 제3 레벨 신호를 게이트 구동 회로(20)로 출력하며;

- [0023] 제2 스위치 유닛(12)은 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호를 수신하는 데 사용되며, 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호에 따라 제4 레벨 신호를 게이트 구동 회로(20)로 출력한다.

- [0024] 이 중, 도 1은 제어 회로와 게이트 구동 회로 사이의 접속관계, 제어 회로의 입출력 신호 및 게이트 구동 회로 의 입력신호를 예시적으로 나타낸 것에 한하며; 도 2는 도 1에 기반하여 제어 회로가 포함하는 제1 스위치 유닛 과 제2 스위치 유닛, 및 제1 스위치 유닛과 제2 스위치 유닛의 입출력 신호를 예시적으로 도시한 것이다.

- [0025] 실제 응용에 있어서, 제어 회로는 다수 트랜지스터, 비교기, 로직 게이트, 저항, 커패시터 또는 인덕터 등과 같은 전자 소자를 포함할 수 있으며; 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호는 타이밍 컨트롤러(Timer Control Register, TCON) 또는 시스템 온 칩(System on Chip, SOC)에 의해 제어 회로에 입력될 수 있으며; 제어 회로는 제1 레벨 신호 및 제2 레벨 신호에 따라 제1 클럭 신호에 대한 위상변위를 구현할 수 있으며, 위상변위에 의해 획득된 제2 클럭 신호와 제1 클럭 신호의 위상차 범위는 0° 내지 180°일 수 있으며. 제2 클럭 신호와

제1 클럭 신호 사이의 위상차는 제1 클럭 신호와 제2 클럭 신호의 타이밍에 의해 결정될 수 있으며; 제1 클럭 신호와 제2 클럭 신호는 게이트 구동 회로에 출력되어 행 구동 신호를 출력하도록 게이트 구동 회로를 제어하여 디스플레이 패널의 게이트를 한행씩 스캔하도록 사용될 수 있으며; 상세하게는, 1개의 디스플레이 패널은 적어도 하나의 제어 회로를 포함할 수 있으며, 제어 회로의 수량은 상기 디스플레이 패널에 의해 사용되는 클럭 신호의 수량에 의해 확정되며, 각 제어 회로는 각 제1 클럭 신호에 일일이 대응되며, n번째 제어 회로는 n번째 제1 클럭 신호를 수신하고, n번째 제1 클럭 신호에 대한 위상변위를 통해 얻은 n번째 제1 클럭 신호에 대응되는 n번째 제2 클럭 신호를 얻으며; 각 제어 회로를 위상변위하여 얻은 제2 클럭 신호를 게이트 구동 회로로 출력한후, 게이트 구동 회로는 실제 필요에 따라 임의 수량의 행 구동 신호 출력을 제어하여, 디스플레이 패널의 게이트를 한행씩 스캔하며, n개의 제1클럭신호를 사용하여 게이트 구동 회로에 입력하는 경우에 비해, 제어 회로를 통해 n개의 제1 클럭 신호에 일일이 대응되는 n개의 제2 클럭 신호를 생성한 후, n개의 제1 클럭 신호와 n개의 제2 클럭 신호 총 2n개의 클럭 신호를 사용하여 게이트 구동 회로에 입력할 수 있으며, 단일 클럭 신호는 다수의 게이트 구동 회로에 입력될 수 있어, 클럭 신호의 수량이 증가되면, 단일 클럭 신호는 입력할 게이트 구동 회로의 수량을 감소시켜, 단일 클럭 신호의 부하를 감소시킬 수 있고, 클럭 신호의 생성에 사용되는 클럭 발생기의 수량을 감소시킬 수 있어, 디스플레이 패널의 실제 필요에 따라 제어 회로의 수량을 설정할 수 있다.

- [0026] 도 3은 게이트 구동 회로(20)에 접속된 제1 제어 회로(101), 제2 제어 회로(102) 내지 제n 제어 회로(103)의 예 시적인 구조 개략도를 도시한다.

- [0027] 실제 응용에 있어서, 제어 회로는 다수의 스위치 유닛을 포함할 수 있으며, 각 스위치 유닛은 제1 클럭 신호의 레벨 고저에 따라 해당 스위치 유닛이 레벨 신호를 출력하는지 여부를 제어할 수 있으며, 구체적으로, 제어 회로는 제1 스위치 유닛과 제2 스위치 유닛을 포함할 수 있으며, 이 중, 제1 스위치 유닛은 제1 클럭 신호에 따라 제3 레벨 신호의 출력을 제어하는 데 사용되며, 제2 스위치 유닛은 제1 클럭 신호에 따라 제4 레벨 신호의 출력을 제어하는 데 사용된다. 예를 들어, 제1 클럭 신호가 하이 레벨인 경우, 제1 스위치 유닛은 제3 레벨 신호를 제어하여 출력을 정지하고, 제2 스위치 유닛은 제4 레벨 신호를 제어하여 출력을 시작할 수 있으며, 제1 클럭 신호가 로우 레벨인 경우, 제1 스위치 유닛은 제3 레벨 신호를 제어하여 출력을 시작할 수 있으며, 제2 스위치 유닛은 제4 레벨 신호를 제어하여 출력을 시작할 수 있으며, 제2 스위치 유닛은 제4 레벨 신호를 제어하여 출력을 중지할 수 있다. 이 경우, 디스플레이 패널이 작동 상태로 들어간 후, 제3 레벨 신호와 제4 레벨 신호의 레벨이 상이하다는 점에 유의해야 한다. 구체적으로, 제3 레벨 신호가 하이 레벨이 경우, 제4 레벨 신호는 로우 레벨이며, 또는 제3 레벨 신호가 로우 레벨일 경우, 제4 레벨 신호는 로우 레벨이며, 또는 제3 레벨 신호와 제2 스위치 유닛에 의해 출력되는 제4 레벨 신호를 정합시켜, 중단없이 연속적인 제2 클럭 신호를 얻을 수 있다.

- [0028] 일 실시예에서, 상기 제1 레벨 신호는 하이 레벨 신호이고, 상기 제2 레벨 신호는 로우 레벨 신호이다.

- [0029] 일 실시예에서, 제1 스위치 유닛(11)은 상기 제1 클럭 신호가 로우 레벨일 때, 상기 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호에 따라 상기 게이트 구동 회로(20)를 도통시키고 해당 회로로 제3 레벨 신호를 출력하는 데에도 사용되며,상기 제3 레벨 신호는 하이 레벨이며; 또한, 상기 제1 클럭 신호가 하이 레벨일 경우, 상기 제1 클럭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라, 게이트 구동 회로(20)를 차단하여 해당 회로에 대한 제3 레벨 신호 출력을 중단하는 데에도 사용되며;

- [0030] 제2 스위치 유닛(12)은 제1 클릭 신호가 하이 레벨일 경우, 상기 제1 클릭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라 상기 게이트 구동 회로(20)를 도통시켜 해당 회로로 제4 레벨 신호를 출력하는 데에도 사용되며, 상기 제4 레벨 신호는 로우 레벨이며; 또한, 상기 제1 클릭 신호가 로우 레벨일 경우, 상기 제1 클릭 신호, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라, 게이트 구동 회로(20)를 차단하고 해당 회로에 대한 제4 레벨 신호 출력을 중단하는 데에도 사용된다.

- [0031] 실제 응용에 있어서, 제어 회로가 작동 상태로 진입한 후, 제1 클럭 신호가 로우 레벨일 경우, 제1 스위치 유닛은 게이트 구동 회로를 도통하면서 제3 레벨 신호를 해당 회로로 출력하며, 이 경우, 제3 레벨 신호는 하이 레벨이며, 제2 스위치 유닛은 게이트 구동 회로를 차단하고 제4 레벨 신호를 해당 회로로 출력하는 것을 정지하며, 이 경우, 제4 레벨 신호는 출력되지 않기에, 제2 클럭 신호는 하이 레벨이며; 제1 클럭 신호가 하이 레벨일 경우, 제1 스위치 유닛은 상기 게이트 구동 회로를 차단하고 제3 레벨 신호를 해당 회로로 출력하는 것을 정지하며, 이 경우, 제3 레벨 신호는 출력되지 않기에, 제2 스위치 유닛은 게이트 구동 회로를 도통하면서 제4 레벨 신호를 해당 회로로 출력하며, 이 경우, 제4 레벨 신호는 로우 레벨이기에, 제2 클럭 신호는 로우 레벨에 있어, 제1 클럭 신호에 대한 위상변위를 구현하게 되고, 위상변위를 통해 얻은 제2 클럭 신호와 제1 클럭

신호의 위상차는 90°이다.

- [0032] 도 4에 도시된 바와 같이, 일 실시예에서, 도2 대응된 실시예에 기반하여, 상기 제1 스위치 유닛(11)은 제1 전 자 스위치(111), 제2 전자 스위치(112), 제3 전자 스위치(113), 제4 전자 스위치(114), 제5 전자 스위치(115) 및 제1 캐패시터(116)를 포함하며;

- [0033] 상기 제1 전자 스위치(111)의 드레인은 상기 제2 전자 스위치(112)의 게이트와 접속되며, 상기 제1 전자 스위치 (111)의 게이트와 소스는 상기 제1 클럭 신호를 수신하는 데 사용되며;

- [0034] 상기 제2 전자 스위치(112)의 드레인은 상기 제4 전자 스위치(114)의 소스와 접속되며, 상기 제2 전자 스위치(112)의 소스는 상기 제1 레벨 신호를 수신하는 데 사용된다.

- [0035] 상기 제3 전자 스위치(113)의 드레인은 상기 제5 전자 스위치(115)의 소스 및 제4 전자 스위치(114)의 게이트에 각각 접속되며, 상기 제3 전자 스위치(113)의 소스는 상기 제1 레벨 신호를 수신하는 데 사용되며;

- [0036] 상기 제1 커패시터(116)의 제1극은 상기 제1 전자 스위치(111)의 드레인 및 상기 제2 전자 스위치(112)의 게이 트에 각각 접속되고, 상기 제5 전자 스위치(115)의 드레인은 상기 제2 레벨 신호를 수신하는 데 사용되며;

- [0037] 상기 제3 전자 스위치(113)의 게이트, 상기 제5 전자 스위치(115)의 드레인, 상기 제4 전자 스위치(114)의 드레인 및 상기 제1 캐패시터(116)의 제2극은 각각 상기 제2 스위치 유닛과 전기적으로 접속된다.

- [0038] 실제 응용에 있어서, 제1 전자 스위치 내지 제5 전자 스위치는 전자 스위칭 기능을 갖는 임의 부재 또는 회로, 예를 들어, 트라이오드 또는 금속산화물 반도체 전계효과 트랜지스터(Metal Oxide Semiconductor Field Effect Transistor, MOSFET), 구체적으로, 박막 전계효과 트랜지스터(Thin Film Transistor, TFT)일 수 있으며; 제1 커패시터는 세라믹 커패시터, 알루미늄 전해 커패시터, 운모 커패시터, 종이 유전 커패시터, 탄탈 니오븀 전해 커패시터 또는 필름 커패시터와 같은 상이한 종류의 커패시터일 수 있으며, 제1 커패시터의 유형 및 용량값은 실제 필요에 따라 선택될 수 있다.

- [0039] 도 5에 도시된 바와 같이, 일 실시예에서, 도 4에 대응된 실시예에 기반하여, 제2 스위치 유닛(12)은 제6 전자 스위치(121), 제7 전자 스위치(122) 및 제8 전자 스위치(123)를 포함한다.

- [0040] 상기 제6 전자 스위치(121)의 드레인은 상기 제3 전자 스위치의 게이트 및 상기 제7 전자 스위치(122) 소스에 각각 접속되며, 상기 제6 전자 스위치(121)의 게이트 및 소스는 상기 제1 레벨 신호를 수신하는 데 사용된다.

- [0041] 상기 제7 전자 스위치(122)의 드레인은 상기 제5 전자 스위치의 드레인 및 상기 제8 전자 스위치(123)의 소스에 각각 접속되며, 상기 제7 전자 스위치(122)의 게이트는 상기 제1 클럭 신호를 수신하는 데 사용되며, 상기 제7 전자 스위치(122)의 드레인은 상기 제2 레벨 신호를 수신하는 데 사용된다.

- [0042] 상기 제8 전자 스위치(123)의 드레인은 제5 전자 스위치의 드레인 및 제1 커패시터의 제2극에 각각 접속되며, 상기 제8 전자 스위치(123)의 게이트는 상기 제1 클럭 신호를 수신하는 데 사용된다.

- [0043] 실제 응용에 있어서, 제6 전자 스위치로부터 제8 전자 스위치까지의 부재 유형 및 상기 제1 전자 스위치로부터 제5 전자 스위치까지의 부재 유형은 일치하며, 여기서 설명을 반복하지 아니한다.

- [0044] 도 6은 제1 클럭 신호, 제2 전자 스위치의 게이트 레벨, 제2 전자 스위치의 드레인 레벨, 제4 전자 스위치의 게이트 레벨, 제3 레벨 신호, 제4 레벨 신호 및 제2 클럭 신호의 타이밍 다이어그램을 예시적으로 나타낸다.

- [0045] 실제 응용에 있어서, 제1 레벨 신호는 항상 하이 레벨 신호를 출력하고, 제2 레벨 신호는 항상 로우 레벨 신호를 출력하며, 제1 클럭 신호는 주기성 클럭 신호이며, 제1 클럭 신호의 인접한 상승 에지 및 하강 에지 간의 위상차는 90°이며; 제어 회로가 작동 상태로 진입하기 전에 준비 상태를 거쳐야 하며; 제1 시간대 내로 제어 회로는 제1 준비 상태로 진입하고, 제1 클럭 신호는 로우 레벨을 수신하기에, 제1 전자 스위치는 제1 시간대 동안차단되고, 제1 전자 스위치의 드레인 레벨은 로우 레벨이 되어, 제2 전자 스위치의 게이트 레벨도 로우 레벨이되게 하며, 제2 전자 스위치가 차단되면, 제2 전자 스위치의 드레인 레벨이로우 레벨리로 되어, 제4 전자 스위치의 의소스 레벨도 로우 레벨이되어, 제3 전자 스위치의 게이트와 소스 모두는 제1 레벨 신호를 수신하여, 제6 전자스위치가 도통되고 드레인 레벨이하이 레벨이되어, 제3 전자스위치의 게이트 레벨도 하이 레벨이되게 하며, 제3 전자스위치가도통되고, 제3 전자스위치의 소스는 제1 레벨 신호를 수신하므로, 제3 전자스위치의드레인 레벨이하이 레벨이로어, 제4 전자스위치의 게이트 레벨도하이 레벨이되게하며, 제4 전자스위치를도통시키며, 제4 전자스위치의소스 레벨이로우 레벨인이유로, 제4 전자스위치의드레인레벨도로우 레벨이되며, 제4 전자스위치의드레인레벨은 제3 레벨 신호이므로, 제3 레벨 신호는 로우레벨이되며; 제1 클럭

신호가 로우 레벨을 입력하기 때문에, 제5 전자 스위치, 제7 전자 스위치 및 제8 전자 스위치는 제1 시간대 동안 차단되며, 제8 전자 스위치는 제4 레벨 신호를 출력하지 않으며; 제3 레벨 신호는 로우 레벨이고, 제4 레벨 신호는 출력되지 않으므로 제2 클럭 신호는 로우 레벨이 된다. 제1 준비 상태에서는 제3 레벨 신호와 제4 레벨 신호의 전압 크기는 상이하다는 점에 유의해야 한다. 구체적으로, 제3 레벨 신호는 로우 레벨일 수 있고, 로우레벨은 구체적으로 -3V, -5V, -6V 또는 -8V일 수 있으며, 제4 레벨 신호의 전압은 0V일 수 있으며; 본 발명의 실시예는 로우 레벨 및 하이 레벨의 특정 전압 값에 대하여 그 어떤 제한도 하지 않는다.

[0046] 실제 응용에 있어서, 제2 시간대 동안 제어 회로는 제2 준비 상태로 진입하고, 제1 클릭 신호는 제1 시간대의로우 레벨에서 하이 레벨 입력으로 변경되기에, 제2 시간대 동안, 제1 전자 스위치는 도통되고 드레인 레벨이하이 레벨로 되어, 제2 전자 스위치의 게이트 레벨이하이 레벨이되고, 제2 전자 스위치가 도통되며, 제2 전자스위치의 소스는 제1 레벨 신호를 수신하므로, 제2 전자스위치의 드레인 레벨은 하이 레벨이되며; 제7 전자스위치의 게이트는 하이 레벨의 제1 클릭 신호를 수신하여도통되며, 제6 전자스위치의 드레인이 출력한하이레벨은 제7 전자스위치 및 제2 레벨 신호를 경과하여방출될수 있으므로, 제3 전자스위치의 게이트 레벨은하이 레벨에서로우 레벨로 내려가며, 제3 전자스위치가 차단되고, 또한, 제5 전자스위치의 게이트는 하이 레벨의 제1 클릭 신호를 수신하여도통되기에, 제5 전자스위치의 소스부위의하이 레벨은 제5 전자스위치 및 제2 레벨 신호를 경과하여방출되고, 제3 전자스위치의 차단과함께, 제5 전자스위치의소스레벨이하이레벨에서로우레벨로내려가면, 제4 전자스위치의 케이트레벨은하이레벨에서로우레벨로내려가고, 제4 전자스위치의케이트레벨은하이레벨에서로우레벨로내려가고, 제4 전자스위치는 차단되고, 제3 레벨 신호의 출력을 정지하며; 제8 전자스위치의 게이트는하이레벨의 제1 클릭신호를수신하여제8 전자스위치가도통되게하며,제8 전자스위치의소는 제2 레벨 신호를수신하여로우레벨이되면,제8 전자스위치의드레인레벨은로우레벨이되어,제2 클릭신호도로우레벨이되며;제3 레벨신호단로우레벨이되면,제8 전자스위치의드레인레벨은로우레벨이되어,제2 클릭신호도로우레벨이되다.

[0047]

[0048]

실제 응용에 있어서, 제3 시간대는 제2 클럭 신호가 하이 레벨을 출력하는 시간대이며, 제어 회로는 제1 작동 상태로 진입하며, 제1 클럭 신호는 제2 시간대의 하이 레벨 입력에서 로우 레벨 입력으로 변경되며, 따라서, 제 1 전자 스위치는 제3 시간대 동안 차단되며, 단, 제2 전자 스위치의 게이트 부위 전압이 부동 상태에 있어, 제2 전자 스위치의 게이트 부위 전압은 제1 전압으로 가정하여, 제2 전자 스위치의 게이트 레벨은 여전히 하이 레벨 이며, 제2 전자 스위치가 도통되며, 제2 전자 스위치의 드레인 레벨이 제2 시간대 동안의 제2 전자 스위치의 드 레인 레벨과 일치하게 모두 하이 레벨이며, 제3 전자 스위치의 도통 상태는 상기 제1 시간대 동안의 제3 전자 스위치의 도통 상태와 일치하며, 이와 관련하여 이 부분에서 반복 설명하지 않으며, 제1 클럭 신호가 로우 레벨 로 입력되기 때문에, 제5 전자 스위치의 게이트 레벨도 로우 레벨이며, 제5 전자 스위치가 차단되면, 제4 전자 스위치의 게이트 레벨은 하이 레벨이 되며,제4 전자 스위치의 소스 레벨은 하이 레벨이 되어, 제3 레벨 신호도 하이 레벨이 되며; 제1 클럭 신호가 로우 레벨을 입력하기에. 제7 전자 스위치와 제8 전자 스위치의 게이트 레 벨도 로우 레벨이며, 제7 전자 스위치가 차단되고, 제8 전자 스위치가 차단되면서 제4 레벨 신호 출력을 중단하 며; 제3 레벨 신호는 하이 레벨이므로, 제4 레벨 신호는 출력을 정지하게 되기에, 제2 클럭 신호는 하이 레벨이 고; 이 외에, 제3 레벨 신호는 하이 레벨이고, 제2 전자 스위치 게이트 부위의 전압은 부동 상태에 있으며, 제1 커패시터의 커플링 작용에 의해 제2 전자 스위치 게이트 부위의 제1 전압은 제2 전압으로 상승하게 되며, 제1 전압의 전압값은 제1 클럭 신호가 하이 레벨을 입력할 때의 전압값에 의해 확정되며, 제2 전압의 전압값은 제1 클럭 신호에 의해 하이 레벨을 출력할 때의 전압값과 제1 커패시터의 커플링 작용에 의해 확정된다.

실제 응용에 있어서, 제4 시간대는 제2 클릭 신호가 로우 레벨을 출력하는 시간대이며, 제어 회로는 제2 준비 상태로 진입하고, 제1 클릭 신호는 제3 시간대의 로우 레벨 입력에서 하이 레벨 입력으로 변경되기에, 제3 시간대 동안, 제1 전자 스위치는 도통되고, 제2 전자 스위치 게이트 부위 전압은 부동 상태가 해제되며, 제2 전자스위치 게이트 부위의 전압은 제2 전압에서 제1 전압으로 복구되며, 제2 전자스위치가 도통되며, 제4 시간대동안의 제2 전자스위치의 드레인 레벨과 제3 시간대동안의 제2 전자스위치의 드레인 레벨은 일치하게 하이레벨이 되며; 제7 전자스위치의 게이트는 하이 레벨의 제1 클릭 신호를 수신하여 제7 전자스위치를 도통하며, 제6 전자스위치의 드레인이 출력한 하이 레벨은 제7 전자스위치 및 제2 레벨 신호를 경과하여 방출되어, 제3 전자스위치의 게이트 레벨은 하이 레벨에서로우레벨로 내려가며, 제3 전자스위치가 차단되고, 또한, 제5 전자스위치의 게이트는 하이 레벨의 제1 클릭 신호를 수신하여도통되기에, 제5 전자스위치의 소스부위의하이레벨은 제5 전자스위치 및 제2 레벨 신호를 경과하여방출되고, 제3 전자스위치의 차단과함께, 제5 전자스위치의 소스 부위의하이레벨은 제5 전자스위치 및 제2 레벨 신호를 경과하여방출되고, 제3 전자스위치의 차단과함께, 제5 전자스위치의소스 레벨에서로우레벨로 내려가고, 제4 전자스위치는 차단되고, 제3 레벨 신호의출력을 정지하며; 제8 전자스위치의게이트는 하이레벨의 제1클릭 신호를 수신하여로통되며, 제8 전자스위치의소는 제2 레벨 신호를 수신하여로우레벨이되면, 제8 전자스위치의드레인 레벨은로우레벨이되어, 제4 레벨 신호도로우레벨이되며; 제3

레벨 신호가 출력을 정지하므로, 제4 레벨 신호는 로우 레벨이 되어, 제2 클럭 신호도 로우 레벨이 된다.

- [0049] 실제 응용에 있어서, 제어 회로는 제1 시간대와 제2 시간대에 준비 과정을 완료한 후, 제1 클릭 신호의 레벨 변화에 따라 제어 회로의 작동 상태가 변화하며, 구체적으로, 제1 클릭 신호가 로우 레벨일 경우, 제어 회로의 작동 상태는 상기 제3 시간대의 제1 작동 상태와 일치하며, 제1 클릭 신호는 하이 레벨일 경우, 제어 회로의 작동 상태는 상기 제4 시간대의 제2 작동 상태와 일치하여, 제어 회로에 의해 출력되는 제2 클릭 신호와 제1 클릭 신호의 위상차는 90°로 되며, 클릭 신호에 대한 위상변위를 구현하여, 단일 클릭 신호의 부하를 감소시키고, 디스플레이 패널에 있는 클릭 발생기 수량을 감소시키고, 디스플레이 패널의 생산원가를 절감할 수 있다.

- [0050] 도 7에 도시된 바와 같이, 일 실시예에서, 도 1에 대응된 실시예에 기반하여, 제어 회로(10)는:

- [0051] 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호를 수신하는 데 사용되며, 제1 클럭 신호가 하이 레벨일 경우, 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호에 따라 게이트 구동 회로(20)를 도통시켜 제5 레벨 신호를 해당 회로로 출력하며, 제5 레벨 신호는 하이 레벨이며; 또한, 제1 클럭 신호가 로우 레벨일 경우, 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호에 따라, 게이트 구동 회로(20)를 도통시키고 제5 레벨 신호를 해당 회로로 출력하는 데에도 사용되며, 제5 레벨 신호는 로우 레벨인 제3 스위치 유닛(13)과;

- [0052] 제3 스위치 유닛(13)과 연결되어, 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호를 수신하는 데 사용되며, 제 1 클럭 신호가 하이 레벨일 경우, 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호에 따라 게이트 구동 회로 (20)를 도통 시키고 제6 레벨 신호를 해당 회로로 출력하며, 제6 레벨 신호는 로우 레벨이며; 또한, 제1 클럭 신호가 로우 레벨일 경우, 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호에 따라, 회로 차단 및 제6 레벨 신호 출력을 중단하는 데에도 사용되는 제4 스위치 유닛(14)을 포함한다.

- [0053] 이 중, 제2 클럭 신호는 제5 레벨 신호 및 제6 레벨 신호를 포함한다.

- [0054] 실제 응용에 있어서, 제어 회로가 작동 상태로 진입한 후, 제1 클럭 신호가 로우 레벨일 경우, 제3 스위치 유닛은 게이트 구동 회로를 도통하면서 제5 레벨 신호를 해당 회로로 출력하며, 이 경우, 제5 레벨 신호는 하이 레벨이며, 제4 스위치 유닛은 게이트 구동 회로를 차단하고 제6 레벨 신호를 해당 회로로 출력하는 것을 정지하며, 이 경우, 제6 레벨 신호는 출력되지 않기에, 제2 클럭 신호는 하이 레벨이며; 제1 클럭 신호가 하이레벨일 경우, 제3 스위치 유닛은 상기 게이트 구동 회로를 도통하면서 상기 제5 레벨 신호를 해당 회로로 출력하며, 이 경우, 제5 레벨 신호는 로우 레벨이며, 제4 스위치 유닛은 상기 게이트 구동 회로를 도통하면서 제6 레벨 신호를 해당 회로로 출력하며, 이 경우, 제6 레벨 신호를 해당 최로로 출력하면, 제1 클럭 신호에 대한 위상변위를 구현하게 되고, 위상변위를 통해 얻은 제2 클럭 신호와 제1 클럭 신호의 위상차는 90°이다.

- [0055] 도 8에 도시된 바와 같이, 일 실시예에서, 도7 대응된 실시예에 기반하여, 제3 스위치 유닛(13)은 제9 전자 스위치(131), 제10 전자 스위치(132), 제11 전자 스위치(133), 제12 전자 스위치(134), 제13 전자 스위치(135), 제2 캐패시터(136) 및 제3 캐패시터(137)를 포함하며;

- [0056] 제9 전자 스위치(131)의 드레인은 제10 전자 스위치(132)의 게이트, 제13 전자 스위치(135)의 소스 및 제2 커패 시터(136)의 제1 극에 각각 접속되며, 제9 전자 스위치(131)의 소스는 제1 레벨 신호를 수신하는 데 사용되며;

- [0057] 제10 전자 스위치(132)의 드레인은 제2 커패시터(136)의 제2극 및 제12 전자 스위치(134)의 소스에 접속되며, 제10 전자 스위치(132)의 소스는 제1 레벨 신호를 수신하는 데 사용되며;

- [0058] 제11 전자 스위치(133)의 게이트와 소스는 제1 클럭 신호를 수신하는 데 사용되며;

- [0059] 제12 전자 스위치(134)의 게이트는 제3 커패시터(137)의 제1극 및 제11 전자 스위치(133)의 드레인에 각각 접속 되며;

- [0060] 제13 전자 스위치(135)의 게이트는 제1 클럭 신호를 수신하는 데 사용되며;

- [0061] 제9 전자 스위치(131)의 게이트, 제12 전자 스위치(134)의 드레인, 제13 전자 스위치(135)의 드레인 및 제3 캐 패시터(137)의 제2극은 각각 상기 제4 스위치 유닛과 전기적으로 접속된다.

- [0062] 실제 응용에 있어서, 제9 전자 스위치로부터 제13 전자 스위치까지의 부재 유형 및 상기 제1 전자 스위치로부터 제5 전자 스위치까지의 부재 유형은 일치하며, 또한, 제2 캐패시터 및 제3 커패시터의 유형은 상기 제1 캐패시터의 유형과 일치하며, 여기서 설명을 반복하지 아니하며, 제2 캐패시터와 제3 캐패시터의 용량값 크기는 실제수요에 따라 설정할 수 있다.

- [0063] 도 9에 도시된 바와 같이, 일 실시예에서, 도 8에 대응된 실시예에 기반하여, 제4 스위치 유닛(14)은 제14 전자 스위치(141), 제15 전자 스위치(142) 및 제16 전자 스위치(143)를 포함하며;

- [0064] 제14 전자 스위치(141)의 드레인은 제9 전자 스위치의 게이트 및 제15 전자 스위치(142) 소스에 접속되며, 제14 전자 스위치(141)의 게이트 및 소스는 제1 레벨 신호를 수신하는 데 사용되며;

- [0065] 제15 전자 스위치(142)의 드레인은 제13 전자 스위치의 드레인 및 제16 전자 스위치(143)의 소스에 각각 접속되며, 제15 전자 스위치(142)의 게이트는 제1 클럭 신호를 수신하는 데 사용되며, 제15자 스위치(142)의 드레인은 제2 레벨 신호를 수신하는 데 사용되며;

- [0066] 제16 전자 스위치(143)의 드레인은 제12 전자 스위치의 드레인 및 제3 커패시터의 제2극에 각각 접속되며, 제16 전자 스위치(143)의 게이트는 제1 클럭 신호를 수신하는 데 사용된다.

- [0067] 실제 응용에 있어서, 제14 전자 스위치로부터 제16 전자 스위치까지의 부재 유형 및 상기 제1 전자 스위치로부터 제5 전자 스위치까지의 부재 유형은 일치하며, 여기서 설명을 반복하지 아니한다.

- [0068] 도 10은 제1 클럭 신호, 제10 전자 스위치의 게이트 레벨, 제10 전자 스위치의 드레인 레벨, 제12 전자 스위치의 의 게이트 레벨, 제5 레벨 신호, 제6 레벨 신호 및 제2 클럭 신호의 타이밍 다이어그램을 예시적으로 나타낸다.

- [0069] 실제 응용에 있어서, 제1 레벨 신호는 항상 하이 레벨 신호를 출력하고, 제2 레벨 신호는 항상 로우 레벨 신호를 출력하며, 제1 클럭 신호는 주기성 클럭 신호이며, 제1 클럭 신호의 인접한 상승 에지 및 하강 에지 간의 위상차는 90°이며; 제14 전자 스위치의 게이트와 소스는 항상 제1 레벨 신호를 수신하기 때문에, 제14 전자 스위치의 드레인 레벨은 항상 하이 레벨이며; 제어 회로가 작동 상태로 진입하기 전에 준비 상태를 거쳐야 하며; 제5 시간대 내로 제어 회로는 제1 준비 상태로 진입하고, 제1 클럭 신호는 로우 레벨을 입력하여, 제11 전자 스위치, 제13 전자 스위치, 제15 전자 스위치 및 제16 전자 스위치는 차단되고; 제14 전자 스위치 드레인의 하이 레벨은 제9 전자 스위치의 게이트로 출력되어, 제9 전자 스위치가 도통되고, 제9 전자 스위치의 소스는 제1 레벨 신호를 수신하여, 제9 전자 스위치의 드레인 레벨도 하이 레벨이 되어, 제10 전자 스위치의 게이트 레벨도 하이 레벨이 되며, 제10 전자 스위치가 도통되고, 제10 전자 스위치의 드레인 레벨은 하이 레벨이 되며; 제11전자 스위치가 차단되면 제12 전자 스위치의 게이트 레벨이 로우 레벨이 되고, 제12 전자 스위치가 차단되며, 제12 전자 스위치가 차단되며, 제16 전자 스위치가 차단되고, 제16전자 드레인 레벨은 제6 레벨 신호가 되어, 제16 전자 스위치는 제6 레벨 신호를 출력하지 않으며; 제5 레벨 신호와 제6 레벨 신호 모두를 출력하지 않기에 제2 클럭 신호는 로우 레벨이 된다.

- [0070] 실제 응용에 있어서, 제어 회로는 제6시간대 내로 제2 준비 상태로 진입하고, 제1클릭 신호는 제5시간대의 로우 레벨 입력에서 하이 레벨 입력으로 변환되며, 제15 전자 스위치의 게이트는 하이 레벨의 제1클릭 신호를 수신하기에, 제15 전자 스위치는 도통되고, 제14 전자 스위치의 드레인이 출력한 하이 레벨은 제15 전자 스위치, 제2 레벨 신호를 경과하여 방출되어, 제9 전자 스위치의 게이트 레벨을 하이 레벨에서 로우 레벨로 낮춰 주고, 제9 전자 스위치를 차단하며, 또한, 제13 전자 스위치의 게이트가 하이 레벨의 제1클릭 신호를 수신하기 때문에, 제13 전자 스위치가 도통되고, 제13 전자 스위치의 소스 부위의 하이 레벨은 제13 전자 스위치, 제2 레벨 신호를 경과하여 방출되고, 제9 전자 스위치의 차단과 함께 제10 전자 스위치의 게이트 레벨을 하이 레벨에서 로우 레벨로 낮춰주고, 제10 전자 스위치가 차단되고, 제10 전자 스위치의 드레인 부위의 전압은 제2커패시터의 커플링 작용에 의해 저하되므로, 제10 전자 스위치의 드레인 전압은 로우 레벨이 되며; 제1클릭신호가 하이 레벨이기 때문에, 제11 전자 스위치가 도통되고, 제12 전자 스위치의 게이트 레벨이 하이 레벨이 되며, 제12 전자 스위치는 도통되고, 제10 전자 스위치의 드레인 레벨은 로우 레벨이 되어 제5 레벨 신호가 로우 레벨이 되며; 제1 클릭 신호가 하이 레벨이기 때문에, 제16 전자 스위치는 도통되고, 제16 전자 스위치의 소스는 제2레벨 신호를 수신하므로, 제16 전자 스위치의 드레인 레벨은 로우 레벨이 되고, 따라서 제6 레벨 신호는 로우 레벨이 되며; 제5 레벨 신호와 제6 레벨 신호 모두가 로우 레벨이므로 제2 클릭 신호는 로우 레벨이 된다.

- [0071] 실제 응용에 있어서, 제7시간대는 제2 클럭 신호가 하이 레벨을 출력하는 시간대로, 제어 회로는 제1작동 상태로 진입하고, 제1클럭 신호는 제6시간대의 하이 레벨 입력에서 로우 레벨로 입력으로 변환되기 때문에 제15 전자 스위치가 차단되고, 제9 전자 스위치가 도통되며, 이 경우 제10 전자 스위치의 게이트 레벨은 하이 레벨이되며, 제10 전자 스위치가 도통되며, 제10 전자 스위치의 소스가 제1 레벨 신호를 수신하기 때문에, 제10 전자스위치의 드레인 레벨은 하이 레벨이되고, 제3커페시터의 커플링 작용으로 제10 전자스위치의 게이트 부위 전압은 진일보로 높아지며, 제10 전자스위치의 도통은 보다 충분하게 진행되며; 제1클럭 신호는 로우 레벨을 입력이기 때문에, 제11 전자스위치는 차단되지만, 제12 전자스위치 게이트 부위의 전압은 부동 상태이며, 이 경

우의 제12 전자 스위치 게이트 부위의 전압을 제3 전압이라고 가정하여, 제12 전자 스위치의 게이트 레벨은 여전히 하이 레벨이고, 제12 전자 스위치는 도통되고, 제12 전자 스위치의 드레인 레벨은 하이 레벨이므로, 제5 레벨 신호는 하이 레벨이 되며; 제1클럭 신호가 로우 레벨이기 때문에, 제13 전자 스위치, 제15 전자 스위치, 제16 전자 스위치가 차단되고, 제16 전자 스위치의 차단에 의해, 제6 레벨 신호의 출력이 정지되며; 제5 레벨 신호는 하이 레벨이기 때문에, 제6 레벨 신호는 출력을 정지하고 제2 클럭 신호는 하이 레벨이 되며; 또한, 제5 레벨 신호가 하이 레벨이고, 제12 전자 스위치 게이트 부위의 전압이 부동 상태이기 때문에, 이 경우의 제12 전자 스위치 게이트 부위 전압은 제3 전압이며, 제3 커페시터의 커플링 작용으로 제12 전자 스위치 게이트 부위의 전압은 제4 전압까지 상승하여, 제12 전자 스위치가 보다 충분하게 도통되며, 제3 전압의 전압값은 제1 클럭 신호가 하이 레벨을 출력할 때의 전압값에 의해 확정되고, 제4 전압의 전압값은 제1 클럭 신호가 하이 레벨을 출력할 때의 전압값에 의해 확정되고, 제4 전압의 전압값은 제1 클럭 신호가 하이 레벨을 출력할 때의 전압값이 되었다.

- [0072] 실제 응용에 있어서, 제8 시간대는 제2 클럭 신호가 로우 레벨을 출력하는 시간대로, 제어 회로는 제2 작동 상태에 있으며, 제어 회로의 제2 작동 상태와 상기 제어 회로의 제1 준비 상태는 일치하므로, 이 부분에서 더 이상 설명을 반복하지 않으며, 양자의 차이점이라면, 제1 클럭 신호가 하이 레벨을 입력하기 때문에, 제11 전자스위치는 도통되고, 제12 전자 스위치의 게이트 부위 전압은 부동 상태를 해제하고, 제12 전자 스위치의 게이트 부위 전압은 제4 전압에서 제3 전압으로 복구된다.

- [0073] 실제 응용에 있어서, 제어 회로는 제5 시간대와 제6 시간대의 준비 과정을 완료한 후, 제1 클럭 신호의 레벨 변화에 따라 제어 회로의 작동 상태가 변화하며, 구체적으로, 제1 클럭 신호가 로우 레벨일 경우, 제어 회로의 작동 상태는 상기 제7 시간대의 제1 작동 상태와 일치하며, 제1 클럭 신호는 하이 레벨일 경우, 제어 회로의 작동 상태는 상기 제4 시간대의 제2 작동 상태와 일치하여, 제어 회로에 의해 출력되는 제2 클럭 신호와 제1 클럭 신호의 위상차는 90°로 되며, 제1 스위치 유닛과 제2 스위치 유닛으로 구성된 제어 회로에 비해, 제3 스위치 유닛과 제4 스위치 유닛으로 구성된 제어 회로는 제1 작동 상태에서 제3 스위치 유닛을 보다 충분히 온 해주어 위상변위에 의한 클럭 신호 출력의 안정성을 보장할 수 있다.

- [0074] 본 발명의 실시예는 제1 클럭 신호, 제1 레벨 신호 및 제2 레벨 신호를 수신하는 데 사용되는 디스플레이 패널 제어 회로를 제공하며, 상기 제1 레벨 신호 및 상기 제2 레벨 신호에 따라, 상기 제1 클럭 신호에 대한 위상변 위를 통해 획득한 제2 클럭 신호를 게이트 구동 회로로 출력하여, 클럭 신호의 위상변위를 구현하여 단일 클럭 신호의 부하를 감소시키고, 디스플레이 패널에 있는 클럭 발생기의 수량을 줄여주고, 디스플레이 패널의 생산원가를 줄일 수 있다.

- [0075] 도 11에 도시된 바와 같이, 본 발명의 실시예는 디스플레이 장치(1)를 더 제공하며, 디스플레이 장치(1)는 디스플레이 패널(2) 및 제어 유닛(3)을 포함하며, 이 중, 제어 유닛(3)은 상기 각 제어 회로를 포함한다.

- [0076] 제어 유닛은 스토리지, 프로세서 및 스토리지에 저장되어 프로세서 상에서 실행 가능한 컴퓨터 프로그램을 포함 하며, 프로세서가 컴퓨터 프로그램을 실행할 때 상기 각 디스플레이 패널의 제어 회로 실시예에 기재된 기능을 구현한다.

- [0077] 실제 응용에 있어서, 프로세서는 타이밍 컨트롤러(Timer Control Register, TCON) 또는 시스템 온 칩(System on Chip,SOC) 또는 중앙 처리 장치(Central Processing Unit, CPU)일 수 있으며, 해당 프로세서는 다른 범용 프로세서, 디지털 신호 프로세서(Digital Signal Processor, DSP), 주문형 집적회로(Application Specific Integrated Circuit, ASIC),필드 프로그래머블 게이트 어레이(Field-Programmable Gate Array, FPGA) 또는 기타 프로그래머블 로직 소자, 이산 게이트 또는 트랜지스터 로직 소자, 이산 하드웨어 그룹웨어 등일 수 있다. 범용 프로세서는 마이크로프로세서 또는 임의 통상적인 프로세서 등일 수 있다.

- [0078] 실제 응용에 있어서, 스토리지는 일부 실시예에서 단말 장비의 내부 저장 유닛, 예를 들어 단말 장비의 하드 디스크 또는 메모리일 수 있다. 다른 일부 실시예에서 스토리지는 단말 장비에 장착된 외부 저장 장치 예를 들어, 단말 장비에 장착된 플러그인 하드 디스크, 스마트 미디어 카드(Smart Media Card, SMC), 보안 디지털(Secure Digital, SD) 카드, 플래시 카드(Flash Card) 등일 수도 있다. 진일보로, 스토리지는 단말 장비의 내부 저장 유닛을 포함할 수 있고, 외부 저장 장치도 포함할 수 있다. 스토리지는 운영 체제, 애플리케이션, 부트 로더 (BootLoader), 데이터 및 컴퓨터 프로그램 코드와 같은 기타 프로그램 등을 저장하는 데 사용된다. 스토리지는 이미 출력되었거나 출력하게 될 데이터를 일시적으로 저장하는 데 사용될 수도 있다.

- [0079] 상기 실시예는 단지 본 발명의 기술 방안을 설명하기 위함이고, 이를 한정하려는 의도가 아님에 유의하여야 한다; 전술한 실시예를 참조하여 본 발명을 상세히 설명하였지만, 본 분야의 통상의 지식을 가진 기술자라면: 전

술한 각 실시예에 기재된 기술방안은 수정하거나 이 중에 있는 기술적 특징 중 일부에 대해 동등한 교체를 수행할 수 있으며; 이와 같은 수정 또는 교체에 따른 해당 기술 방안은 본 발명의 각 실시예에 기재된 기술방안의 요지와 범위를 본질적으로 초과하지 않으며, 전부 본 발명의 보호 범위 내에 듬은 자명하다.

### 도면

## 도면1