### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2019-117847 (P2019-117847A)

(43) 公開日 令和1年7月18日(2019.7.18)

| (51) Int.Cl. | FΙ                           |                    | テーマコード(参考)        |

|--------------|------------------------------|--------------------|-------------------|

| HO1L 25/069  | 5 <b>(2006.01)</b> HO1L      | , 25/08 Y          | 4M1O9             |

| HO1L 25/07   | ( <b>2006.01)</b> HO 1 L     | , 23/30 R          |                   |

| HO1L 25/18   | ( <b>2006.01)</b> HO1L       | . 25/08 E          |                   |

| HO1L 23/29   | (2006.01)                    |                    |                   |

| HO1L 23/31   | (2006.01)                    |                    |                   |

|              |                              | 審查請求 未請求 請求項       | の数 10 OL (全 18 頁) |

| (21) 出願番号    | 特願2017-250328 (P2017-250328) | (71) 出願人 318010018 |                   |

| (22) 出願日     | 平成29年12月27日 (2017.12.27)     | 東芝メモリ株式会社          |                   |

|              |                              | 東京都港区芝浦一丁目1番1号     |                   |

|              |                              | (74)代理人 100119035  |                   |

|              |                              | 弁理士 池上             | 徹真                |

|              |                              | (74)代理人 100141036  |                   |

|              |                              | 弁理士 須藤             | 章                 |

|              |                              | (74)代理人 100178984  |                   |

東京都港区芝浦一丁目1番1号 東芝メモ

リ株式会社内

(74)代理人 100088487

(72) 発明者 小野 美隆

弁理士 高下 雅弘

弁理士 松山 允之

最終頁に続く

# (54) 【発明の名称】半導体装置

# (57)【要約】

(37) 【安祝3』 【課題】封止樹脂の密着性が向上する半導体装置を提供 🖺 🄨

【解決手段】実施形態の半導体装置は、配線板と、配線 板に固定され、表面に第1の表面膜を有する第1の半導 体チップと、配線板との間に第1の半導体チップを挟ん で設けられ、表面に第2の表面膜を有する第2の半導体 チップと、第1の半導体チップと第2の半導体チップと の間に設けられ、第1の面と第1の面の反対側に位置す る第2の面とを有し、第2の面が第1の半導体チップに 対向し、第1の面の側に第2の半導体チップを支持する 支持板と、配線板と支持板との間に設けられたスペーサ ーと、第1の面の上に設けられ、第2の表面膜と同一材 料の表面層と、第2の半導体チップ、及び、支持板を覆 い、第2の表面膜及び表面層に接する封止樹脂と、を備 える。

【選択図】図1

### 【特許請求の範囲】

### 【請求項1】

配線板と、

前記配線板に固定され、表面に第1の表面膜を有する第1の半導体チップと、

前記配線板との間に前記第1の半導体チップを挟んで設けられ、表面に第2の表面膜を有する第2の半導体チップと、

前記第1の半導体チップと前記第2の半導体チップとの間に設けられ、第1の面と前記第1の面の反対側に位置する第2の面とを有し、前記第2の面が前記第1の半導体チップに対向し、前記第1の面の側に前記第2の半導体チップを支持する支持板と、

前記配線板と前記支持板との間に設けられたスペーサーと、

前記第1の面の上に設けられ、前記第2の表面膜と同一材料の表面層と、

前記第2の半導体チップ、及び、前記支持板を覆い、前記第2の表面膜及び前記表面層に接する封止樹脂と、

を備える半導体装置。

### 【請求項2】

前記第1の表面膜と前記表面層とが同一材料である請求項1記載の半導体装置。

### 【請求項3】

前記支持板の前記第1の面の側に支持され、表面に前記第2の表面膜と同一材料の第3の表面膜を有する第3の半導体チップを、更に有し、

前記表面層は、前記第2の半導体チップと前記第3の半導体チップとの間の領域に設けられ、

前記封止樹脂は前記第3の表面膜に接する請求項1又は請求項2記載の半導体装置。

### 【請求項4】

前記支持板と前記第2の半導体チップとの間に設けられ、前記支持板の前記第1の面の側に支持された第4の半導体チップと、

前記支持板と前記第3の半導体チップとの間に設けられ、前記支持板の前記第1の面の側に支持された第5の半導体チップと、を更に備え、

前記第4の半導体チップと前記第5の半導体チップとの距離は、前記第2の半導体チップと前記第3の半導体チップとの距離よりも大きい請求項3記載の半導体装置。

# 【請求項5】

前記第1の半導体チップと前記配線板とを電気的に接続する第1のボンディングワイヤと、

前記第2の半導体チップと前記配線板とを電気的に接続する第2のボンディングワイヤと

を更に備える請求項1ないし請求項4いずれか一項記載の半導体装置。

### 【請求項6】

前記第1の半導体チップのサイズは、前記第2の半導体チップのサイズよりも小さい請求項1ないし請求項5いずれか一項記載の半導体装置。

### 【請求頃7】

前記表面層の材料はポリイミド又は窒化シリコンである請求項1ないし請求項6いずれか一項記載の半導体装置。

### 【請求項8】

前記支持板と前記表面層との間に窒化シリコン膜を更に備え、前記支持板の材料はシリコンであり、前記表面層の材料はポリイミドである請求項 1 ないし請求項 7 いずれか一項記載の半導体装置。

# 【請求項9】

前記スペーサーが前記第1の半導体チップを覆う請求項1ないし請求項8いずれか一項記載の半導体装置。

### 【請求項10】

前記スペーサーの材料は、前記封止樹脂と異なる材料の樹脂である請求項9記載の半導

10

20

30

40

体装置。

【発明の詳細な説明】

【技術分野】

[0001]

本発明の実施形態は、半導体装置に関する。

【背景技術】

[0002]

複数の半導体チップを一つのパッケージ内に納めた半導体装置がある。例えば、機能の異なる複数の半導体チップが一つのパッケージ内に納められる。機能の異なる半導体チップはサイズが異なる場合がある。サイズの異なる半導体チップを積層してパッケージする場合に、例えば、半導体チップの間に支持板を設け、一部の半導体チップを支持板の上に支持する。

[00003]

パッケージ内の半導体チップや支持板は、封止樹脂によって覆われる。半導体チップの表面と封止樹脂との密着性や、支持板の表面と封止樹脂との密着性が悪いと、半導体チップと封止樹脂との界面や、支持板と封止樹脂との界面に水が浸入する。界面に侵入した水は、例えば、半導体装置の実装時のリフロー工程で加えられる熱により膨張する。界面で水が膨張することにより、パッケージのクラックが生じるおそれがある。また、界面で水が膨張することにより、封止樹脂が剥離して半導体装置の耐湿性が低下し、信頼性不良が生じるおそれがある。

【先行技術文献】

【特許文献】

[0004]

【特許文献 1 】米国特許出願公開第 2 0 0 2 / 0 1 4 0 0 7 3 号明細書

【発明の概要】

【発明が解決しようとする課題】

[0005]

本発明が解決しようとする課題は、封止樹脂の密着性が向上する半導体装置を提供することにある。

【課題を解決するための手段】

[0006]

実施形態の半導体装置は、配線板と、前記配線板に固定され、表面に第1の表面膜を有する第1の半導体チップと、前記配線板との間に前記第1の半導体チップを挟んで設けられ、表面に第2の表面膜を有する第2の半導体チップと、前記第1の半導体チップと前記第2の半導体チップとの間に設けられ、第1の面と前記第1の面の反対側に位置する第2の面とを有し、前記第2の面が前記第1の半導体チップに対向し、前記第1の面の側に前記第2の半導体チップを支持する支持板と、前記配線板と前記支持板との間に設けられたスペーサーと、前記第1の面の上に設けられ、前記第2の表面膜と同一材料の表面層と、前記第2の半導体チップ、及び、前記支持板を覆い、前記第2の表面膜及び前記表面層に接する封止樹脂と、を備える。

【図面の簡単な説明】

[0007]

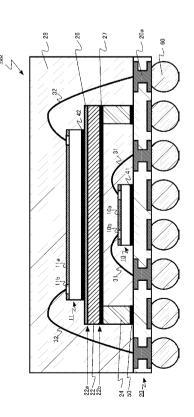

【図1】第1の実施形態の半導体装置の模式断面図。

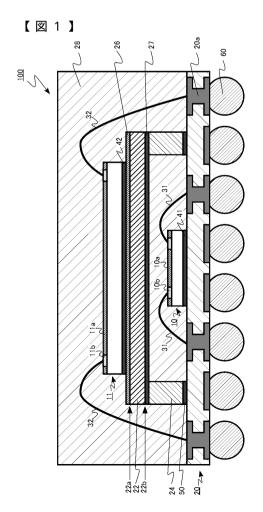

【図2】比較例の半導体装置の模式断面図。

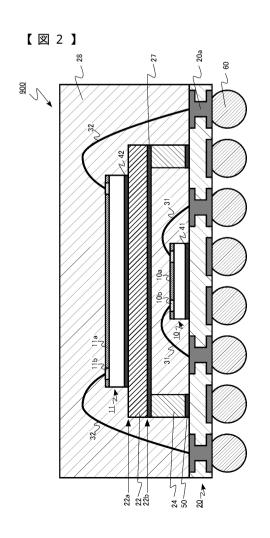

【図3】第2の実施形態の半導体装置の模式断面図。

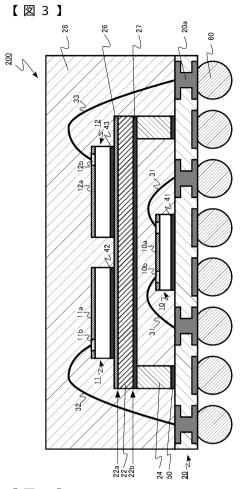

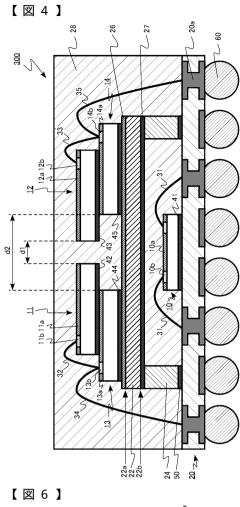

【図4】第3の実施形態の半導体装置の模式断面図。

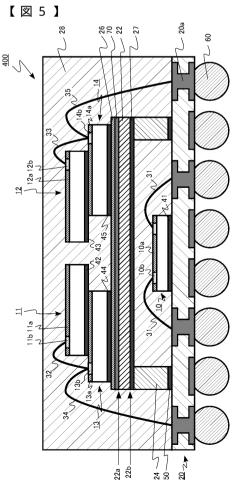

【図5】第4の実施形態の半導体装置の模式断面図。

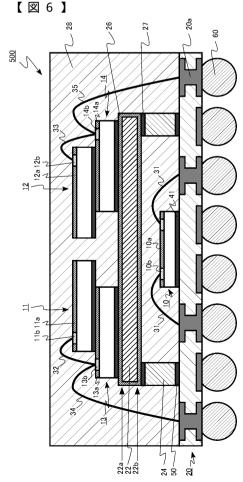

【図6】第5の実施形態の半導体装置の模式断面図。

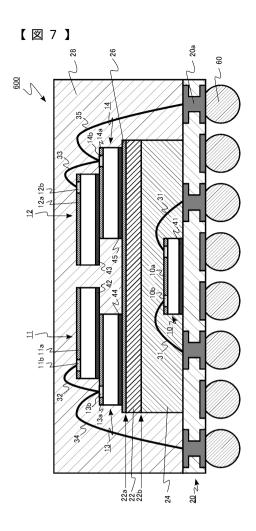

【図7】第6の実施形態の半導体装置の模式断面図。

10

20

30

40

### 【発明を実施するための形態】

### [0008]

以下、図面を参照しつつ本発明の実施形態を説明する。なお、以下の説明では、同一又は類似の部材には同一の符号を付し、一度説明した部材などについては適宜その説明を省略する。

# [0009]

また、本明細書中、便宜上「上」、又は、「下」という用語を用いる場合がある。「上」、又は、「下」とはあくまで図面内での相対的位置関係を示す用語であり、重力に対する位置関係を規定する用語ではない。

# [ 0 0 1 0 ]

以下、実施形態の半導体装置を、図面を参照して説明する。

### [0011]

### (第1の実施形態)

第1の実施形態の半導体装置は、配線板と、配線板に固定され、表面に第1の表面膜を有する第1の半導体チップと、配線板との間に第1の半導体チップを挟んで設けられ、表面に第2の表面膜を有する第2の半導体チップと、第1の半導体チップと第2の半導体チップとの間に設けられ、第1の面と第1の面の反対側に位置する第2の面とを有し、第2の面が第1の半導体チップに対向し、第1の面の側に第2の半導体チップを支持する支持板と、配線板と支持板との間に設けられたスペーサーと、第1の面の上に設けられ、第2の表面膜と同一材料の表面層と、第2の半導体チップ、及び、支持板を覆い、第2の表面膜及び表面層に接する封止樹脂と、を備える。

#### [0012]

図 1 は、第 1 の実施形態の半導体装置の模式断面図である。第 1 の実施形態の半導体装置は、半導体メモリ 1 0 0 である。

### [ 0 0 1 3 ]

半導体メモリ100は、ロジックチップ10(第1の半導体チップ)、第1のメモリチップ11(第2の半導体チップ)、プリント基板20(配線板)、支持板22、スペーサー24、表面層26、裏面層27、封止樹脂28、第1のボンディングワイヤ31、第2の接着層41、第2の接着層42、固定層50、外部端子60を備える。

### [0014]

半導体メモリ 1 0 0 は、 2 個の半導体チップが一つのパッケージ内に納められたマルチチップパッケージ(M C P )である。

# [ 0 0 1 5 ]

ロジックチップ10は、プリント基板20の上に第1の接着層41を用いて固定される。ロジックチップ10は、表面に第1の表面膜10aと電極パッド10bを有する。

# [0016]

ロジックチップ 1 0 は、演算機能を備える。ロジックチップ 1 0 は、例えば、第 1 のメモリチップ 1 1 を制御するメモリコントローラチップである。ロジックチップ 1 0 は、例えば、単結晶シリコンを用いて製造されている。

# [0017]

第1の表面膜10aは、ロジックチップ10の保護膜として機能する。第1の表面膜10aは、絶縁膜である。第1の表面膜10aの材料は、例えば、ポリイミド、又は、窒化シリコンである。第1の表面膜10aの材料は、例えば、酸化シリコン等、その他の絶縁体であっても構わない。第1の表面膜10aの膜厚は、例えば、200nm以上5μm以下である。

### [0018]

第 1 の接着層 4 1 は、例えば、樹脂層である。第 1 の接着層 4 1 は、例えば、ダイアタッチメントフィルム(DAF)である。

# [0019]

50

10

20

30

プリント基板 2 0 は、配線層 2 0 a を有する。ロジックチップ 1 0 とプリント基板 2 0 は、第 1 のボンディングワイヤ 3 1 により、電気的に接続される。第 1 のボンディングワイヤ 3 1 の一端は電極パッド 1 0 b に接続され、他端は配線層 2 0 a に接続される。

[0020]

第 1 のメモリチップ 1 1 は、プリント基板 2 0 との間にロジックチップ 1 0 を挟んで設けられる。第 1 のメモリチップ 1 1 は、支持板 2 2 に第 2 の接着層 4 2 を用いて固定される。第 1 のメモリチップ 1 1 は、表面に第 2 の表面膜 1 1 a と電極パッド 1 1 b を有する

[0021]

第 1 のメモリチップ 1 1 は、メモリ機能を備える。第 1 のメモリチップ 1 1 は、例えば、N A N D 型フラッシュメモリである。第 1 のメモリチップ 1 1 は、例えば、単結晶シリコンを用いて製造されている。

[0022]

ロジックチップ 1 0 のサイズは、第 1 のメモリチップ 1 1 のサイズよりも小さい。ここで、サイズとは、チップ面積を意味するものとする。

[ 0 0 2 3 ]

第2の表面膜11aは、第1のメモリチップ11の保護膜として機能する。第2の表面膜11aは、絶縁膜である。第2の表面膜11aの材料は、例えば、ポリイミド、又は、窒化シリコンである。第2の表面膜11aの材料は、例えば、酸化シリコン等、その他の絶縁体であっても構わない。第2の表面膜11aの膜厚は、例えば、200nm以上5μm以下である。

[0024]

第2の表面膜11aは、例えば、第1の表面膜10aと同一の材料である。

[0025]

第2の接着層42は、例えば、樹脂層である。第2の接着層42は、例えば、ダイアタッチメントフィルム(DAF)である。

[0026]

支持板 2 2 は、ロジックチップ 1 0 と第 1 のメモリチップ 1 1 との間に設けられる。支持板 2 2 は、第 1 の面 2 2 a と第 2 の面 2 2 b とを有する。第 2 の面 2 2 b は第 1 の面 2 2 a の反対側に位置する。第 2 の面 2 2 b は、ロジックチップ 1 0 に対向する。支持板 2 2 は、第 1 の面 2 2 a の側に第 1 のメモリチップ 1 1 を支持する機能を有する。

[0027]

支持板22の材料は、例えば、半導体である。支持板22の材料は、例えば、単結晶シリコンである。支持板22の材料は、例えば、金属、セラミックス、又は、樹脂であって も構わない。

[0028]

支持板22の第1の面22aの上には、表面層26が設けられる。表面層26は、第1の面22aの少なくとも一部の領域に設けられる。表面層26は、例えば、第1の面22 aの第1のメモリチップ11が載置されない領域に設けられる。表面層26は、例えば、図1に示すように、第1の面22aの全面に設けられても構わない。

[0029]

表面層 2 6 は、封止樹脂 2 8 と支持板 2 2 との間の密着性を向上させる機能を有する。表面層 2 6 は、第 2 の表面膜 1 1 a と同一材料である。表面層 2 6 の厚さは、例えば、 2 0 0 n m以上 5 μ m以下である。

[0030]

支持板 2 2 の第 2 の面 2 2 b の下には、裏面層 2 7 が設けられる。支持板 2 2 は、裏面層 2 7 を用いてスペーサー 2 4 に固定される。

[0031]

裏面層 2 7 は、例えば、樹脂層である。裏面層 2 7 は、例えば、ダイアタッチメントフィルム(DAF)である。

10

20

30

40

### [0032]

スペーサー 2 4 は、プリント基板 2 0 と支持板 2 2 との間に設けられる。スペーサー 2 4 は、固定層 5 0 を用いて、プリント基板 2 0 に固定される。

### [0033]

スペーサー 2 4 をプリント基板 2 0 と支持板 2 2 との間に設けることにより、支持板 2 2 はロジックチップ 1 0 と離間している。スペーサー 2 4 をプリント基板 2 0 と支持板 2 2 との間に設けることにより、プリント基板 2 0 と支持板 2 2 との間、及び、ロジックチップ 1 0 と支持板 2 2 との間に所定の距離が確保できる。所定の距離が確保できるため、第 1 のボンディングワイヤ 3 1 の形成が容易となる。

### [0034]

スペーサー24の材料は、例えば、半導体である。スペーサー24の材料は、例えば、単結晶シリコンである。スペーサー24の材料は、例えば、金属、セラミックス、又は、樹脂であっても構わない。

# [0035]

第 1 のメモリチップ 1 1 とプリント基板 2 0 は、第 2 のボンディングワイヤ 3 2 により、電気的に接続される。第 2 のボンディングワイヤ 3 2 の一端は電極パッド 1 1 b に接続され、他端は配線層 2 0 a に接続される。

### [0036]

封止樹脂28は、ロジックチップ10、第1のメモリチップ11、支持板22、スペーサー24、及び、プリント基板20を覆う。封止樹脂28は、ロジックチップ10の第1の表面膜10a、第1のメモリチップ11の第2の表面膜11a、及び、表面層26に接する。

### [0037]

封止樹脂 2 8 は、ロジックチップ 1 0 、第 1 のメモリチップ 1 1 を保護する機能を有する。封止樹脂 2 8 は、例えば、エポキシ樹脂を主成分とする。封止樹脂 2 8 には、例えば、フィラ が含まれる。フィラ は、例えば、シリカ粒子である。

### [0038]

外部端子60は、プリント基板20の下側に設けられる。外部端子60は、配線層20aに接続される。外部端子60は、例えば、はんだボールである。

# [0039]

次に、第1の実施形態の半導体装置の作用及び効果について説明する。

# [0040]

第1の実施形態の半導体メモリ100は、機能が異なりサイズの異なる2個の半導体チップが積層されてパッケージ内に納められる。サイズの小さいロジックチップ10を下に、サイズの大きい第1のメモリチップ11を上に置くため、プリント基板20上にスペーサー24と支持板22が設けられる。

# [0041]

図2は、比較例の半導体装置の模式断面図である。比較例の半導体装置は、半導体メモリ900である。

### [0042]

半導体メモリ900は、支持板22の第1の面22aの上に、表面層26が設けられない点で、第1の実施形態の半導体メモリ100と異なっている。支持板22の第1の面22aが封止樹脂28に接している。

# [0043]

第1のメモリチップ11の第2の表面膜11aの材料と、支持板22の第1の面22aの材料とは異なる材料である。例えば、第2の表面膜11aの材料はポリイミドであり、第1の面22aの材料はシリコンである。

# [0044]

封止樹脂 2 8 の材料は、第 1 のメモリチップ 1 1 の第 2 の表面膜 1 1 a との密着性、及び、支持板 2 2 の第 1 の面 2 2 a との密着性の双方が良好になるように選定される。しか

10

20

30

40

しながら、異なる材質の両方に対する密着性を良好にする材料が必ずしも存在しない場合がある。

### [0045]

このため、半導体メモリ900のように、第1のメモリチップ11の第2の表面膜11aの材料と、支持板22の第1の面22aの材料とが異なる場合、第2の表面膜11aと 封止樹脂28との密着性、又は、第1の面22aと封止樹脂28との密着性が悪くなるおそれがある。特に、第2の表面膜11aの材料がポリイミド又は窒化シリコンであり、第1の面22aの材料がシリコンの場合、第2の表面膜11aとの密着性が良好な封止樹脂28を選択すると、第1の面22aと封止樹脂28との密着性が格段に悪くなる。

### [0046]

第2の表面膜11aと封止樹脂28との密着性、又は、第1の面22aと封止樹脂28との密着性が悪いと、第2の表面膜11aと封止樹脂28との界面や、第1の面22aと封止樹脂28との界面に水が浸入する。界面に侵入した水は、例えば、半導体メモリ900の実装時のリフロー工程で加えられる熱により膨張する。界面で水が膨張することにより、パッケージのクラックが生じるおそれがある。また、界面で水が膨張することにより、封止樹脂28が剥離して半導体メモリ900の耐湿性が低下し、信頼性不良が生じるおそれがある。

# [0047]

第1の実施形態の半導体メモリ100は、支持板22の第1の面22aの上に、表面層26が設けられる。表面層26の材料は、第2の表面膜11aの材料と同一である。したがって、封止樹脂28の材料を、第1のメモリチップ11の第2の表面膜11aとの密着性が良好になるように選定すれば、表面層26と封止樹脂28との密着性も良好となる。よって、比較例の半導体メモリ900と比較して封止樹脂28の密着性が向上し、パッケージのクラックや信頼性不良の発生を抑制することができる。

### [0048]

第1のメモリチップ11の第2の表面膜11aの材料は、ポリイミド又は窒化シリコンであることが好ましい。第2の表面膜11aの材料を、ポリイミド又は窒化シリコンとすることで第1のメモリチップ11の耐湿性が向上する。

### [0049]

ロジックチップ10の第1の表面膜10aと表面層26とは、同一材料であることが好ましい。封止樹脂28の材料を表面層26との密着性が良好になるように選定すれば、第1の表面膜10aと封止樹脂28との密着性も良好になる。

### [0050]

支持板 2 2 の第 2 の面 2 2 b の下には、樹脂層の裏面層 2 7 が設けられることが好ましい。樹脂層の裏面層 2 7 を設けることで、第 2 の面 2 2 b が直接に封止樹脂 2 8 に接することがなくなる。樹脂層と封止樹脂 2 8 との密着性は比較的高いため、支持板 2 2 の第 2 の面 2 2 b の側での封止樹脂 2 8 の密着性が向上する。

### [0051]

以上、第1の実施形態の半導体メモリ100によれば、封止樹脂の密着性が向上し、パッケージのクラックや信頼性不良の発生を抑制できる。

# [ 0 0 5 2 ]

### (第2の実施形態)

第2の実施形態の半導体装置は、支持板の第1の面の側に支持され、表面に第2の表面膜と同一材料の第3の表面膜を有する第3の半導体チップを、更に有し、表面層は、第2の半導体チップと第3の半導体チップとの間の領域に設けられ、封止樹脂は第3の表面膜に接する点で、第1の実施形態の半導体装置と異なっている。以下、第1の実施形態と重複する内容については一部記述を省略する。

### [0053]

図3は、第2の実施形態の半導体装置の模式断面図である。第2の実施形態の半導体装置は、半導体メモリ200である。

10

20

30

40

### [0054]

半導体メモリ200は、ロジックチップ10(第1の半導体チップ)、第1のメモリチップ11(第2の半導体チップ)、第2のメモリチップ12(第3の半導体チップ)、プリント基板20(配線板)、支持板22、スペーサー24、表面層26、裏面層27、封止樹脂28、第1のボンディングワイヤ31、第2のボンディングワイヤ32、第3のボンディングワイヤ33、第1の接着層41、第2の接着層42、第3の接着層43、固定層50、外部端子60を備える。

### [0055]

半導体メモリ 2 0 0 は、 3 個の半導体チップが一つのパッケージ内に納められたマルチチップパッケージ ( M C P ) である。

[0056]

第 1 のメモリチップ 1 1 は、プリント基板 2 0 との間にロジックチップ 1 0 を挟んで設けられる。第 1 のメモリチップ 1 1 は、支持板 2 2 に第 2 の接着層 4 2 を用いて固定される。第 1 のメモリチップ 1 1 は、表面に第 2 の表面膜 1 1 a と電極パッド 1 1 b を有する

[0057]

第1のメモリチップ11は、メモリ機能を備える。第1のメモリチップ11は、例えば、NAND型フラッシュメモリである。第1のメモリチップ11は、例えば、単結晶シリコンを用いて製造されている。

[0058]

第2のメモリチップ12は、プリント基板20との間にロジックチップ10を挟んで設けられる。第2のメモリチップ12は、支持板22の第1の面22aの側に設けられる。第2のメモリチップ12は、支持板22に第3の接着層43を用いて固定される。

[0059]

第 2 のメモリチップ 1 2 は、支持板 2 2 の上に第 1 のメモリチップ 1 1 と並んで設けられる。第 2 のメモリチップ 1 2 は、表面に第 3 の表面膜 1 2 a と電極パッド 1 2 b を有する。

[0060]

第 2 のメモリチップ 1 2 は、メモリ機能を備える。第 2 のメモリチップ 1 2 は、例えば、NAND型フラッシュメモリである。第 2 のメモリチップ 1 2 は、例えば、単結晶シリコンを用いて製造されている。

[0061]

第2のメモリチップ12は、例えば、第1のメモリチップ11と同一の機能を有する。 第2のメモリチップ12は、例えば、第1のメモリチップ11と異なる機能を有する半導 体チップであっても構わない。

[0062]

ロジックチップ 1 0 のサイズは、第 1 のメモリチップ 1 1 のサイズ及び第 2 のメモリチップ 1 2 のサイズよりも小さい。ここで、サイズとは、チップ面積を意味するものとする

[0063]

第3の表面膜12 a は、第2のメモリチップ12の保護膜として機能する。第3の表面膜12 a は、絶縁膜である。第3の表面膜12 a の材料は、例えば、ポリイミド、又は、窒化シリコンである。第3の表面膜12 a の材料は、例えば、酸化シリコン等、その他の絶縁体であっても構わない。第3の表面膜12 a の膜厚は、例えば、200 n m以上5μm以下である。

[0064]

第3の表面膜12aは、第2の表面膜11aと同一の材料である。また、第3の表面膜12aは、例えば、第1の表面膜10aと同一の材料である。

[0065]

表面層26は、少なくとも、第1のメモリチップ11と第2のメモリチップ12との間

20

10

30

40

10

20

30

40

50

の領域に設けられる。表面層 2 6 は、第 1 のメモリチップ 1 1 と第 2 のメモリチップ 1 2 との間の支持板 2 2 の第 1 の面 2 2 a の上に設けられる。

[0066]

第2のメモリチップ12とプリント基板20は、第3のボンディングワイヤ33により、電気的に接続される。第3のボンディングワイヤ33の一端は電極パッド12bに接続され、他端は配線層20aに接続される。

[0067]

封止樹脂28は、第2のメモリチップ12を覆う。封止樹脂28は、第3の表面膜12 aに接する。

[0068]

次に、第2の実施形態の半導体装置の作用及び効果について説明する。

[0069]

第2の実施形態の半導体メモリ200は、支持板22の第1の面22aの上に、表面層26が設けられる。表面層26の材料は、第2の表面膜11a及び第3の表面膜12aの材料と同一である。したがって、封止樹脂28の材料を、第1のメモリチップ11の第2の表面膜11a及び第3の表面膜12aとの密着性が良好になるように選定すれば、表面層26と封止樹脂28との密着性が良好となる。

[0070]

また、第2の実施形態の半導体メモリ200は、第2のメモリチップ12を備えることにより、半導体メモリ200中に含まれる半導体チップが3個となる。したがって、第1の実施形態の半導体メモリ100に比べて、機能が向上する。例えば、メモリ容量が増大する。

[0071]

以上、第2の実施形態の半導体メモリ200によれば、封止樹脂の密着性が向上し、パッケージのクラックや信頼性不良の発生を抑制できる。また、半導体チップの数が3個となることで半導体メモリ200の機能が向上する。

- [0072]

- (第3の実施形態)

第3の実施形態の半導体装置は、支持板と第2の半導体チップとの間に設けられ、支持板の第1の面の側に支持された第4の半導体チップと、支持板と第3の半導体チップとの間に設けられ、支持板の第1の面の側に支持された第5の半導体チップと、を更に備え、第4の半導体チップと第5の半導体チップとの距離は、第2の半導体チップと第3の半導体チップとの距離よりも大きい点で、第2の実施形態の半導体装置と異なっている。以下、第2の実施形態と重複する内容については一部記述を省略する。

[0073]

図4は、第3の実施形態の半導体装置の模式断面図である。第3の実施形態の半導体装置は、半導体メモリ300である。

[0074]

半導体メモリ300は、ロジックチップ10(第1の半導体チップ)、第1のメモリチップ11(第2の半導体チップ)、第2のメモリチップ12(第3の半導体チップ)、第3のメモリチップ13(第4の半導体チップ)、第4のメモリチップ14(第5の半導体チップ)、プリント基板20(配線板)、支持板22、スペーサー24、表面層26、裏面層27、封止樹脂28、第1のボンディングワイヤ31、第2のボンディングワイヤ32、第3のボンディングワイヤ33、第4のボンディングワイヤ34、第5の接着層41、第2の接着層42、第3の接着層43、第4の接着層44、第5の接着層45、固定層50、外部端子60を備える。

[0075]

半導体メモリ 3 0 0 は、 5 個の半導体チップが一つのパッケージ内に納められたマルチチップパッケージ(M C P )である。

[0076]

10

20

30

40

50

第1のメモリチップ11は、第3のメモリチップ13の上に第2の接着層42を用いて固定される。第1のメモリチップ11は、表面に第2の表面膜11aと電極パッド11bを有する。

# [0077]

第2のメモリチップ12は、第4のメモリチップ14の上に第3の接着層43を用いて固定される。第2のメモリチップ12は、第1のメモリチップ11と並んで設けられる。第2のメモリチップ12は、表面に第3の表面膜12aと電極パッド12bを有する。

### [0078]

第3のメモリチップ13は、支持板22に第4の接着層44を用いて固定される。第3のメモリチップ13は、表面に第4の表面膜13aと電極パッド13bを有する。

# [0079]

第4のメモリチップ14は、支持板22に第5の接着層45を用いて固定される。第4のメモリチップ14は、第3のメモリチップ13と並んで設けられる。第4のメモリチップ14は、表面に第5の表面膜14aと電極パッド14bを有する。

### [0800]

第3のメモリチップ13と第4のメモリチップ14との距離(図4中のd2)は、第1のメモリチップ11と第2のメモリチップ12との距離(図4中のd1)よりも大きい。第3のメモリチップ13と第4のメモリチップ14との距離は、例えば、300μm以上3mm以下である。第1のメモリチップ11と第2のメモリチップ12との距離は、例えば、50μm以上200μm以下である。

#### [0081]

第1のメモリチップ11、第2のメモリチップ12、第3のメモリチップ13、及び、第4のメモリチップ14は、メモリ機能を備える。第1のメモリチップ11、第2のメモリチップ12、第3のメモリチップ13、及び、第4のメモリチップ14は、例えば、NAND型フラッシュメモリである。第1のメモリチップ11、第2のメモリチップ12、第3のメモリチップ13、及び、第4のメモリチップ14は、例えば、単結晶シリコンを用いて製造されている。

### [0082]

第4の表面膜13 a は、第3のメモリチップ13の保護膜として機能する。第4の表面膜13 a は、絶縁膜である。第4の表面膜13 a の材料は、例えば、ポリイミド、又は、窒化シリコンである。第4の表面膜13 a の材料は、例えば、酸化シリコン等、その他の絶縁体であっても構わない。第4の表面膜13 a の膜厚は、例えば、200 n m以上5 μ m 以下である。

# [ 0 0 8 3 ]

第5の表面膜14aは、第4のメモリチップ14の保護膜として機能する。第5の表面膜14aは、絶縁膜である。第5の表面膜14aの材料は、例えば、ポリイミド、又は、窒化シリコンである。第5の表面膜14aの材料は、例えば、酸化シリコン等、その他の絶縁体であっても構わない。第5の表面膜14aの膜厚は、例えば、200nm以上5μm以下である。

### [0084]

第4の表面膜13a及び第5の表面膜14aは、例えば、第2の表面膜11a及び第3の表面膜12aと同一の材料である。また、第4の表面膜13a及び第5の表面膜14aは、例えば、第1の表面膜10aと同一の材料である。

# [0085]

表面層 2 6 は、少なくとも第 3 のメモリチップ 1 3 と第 4 のメモリチップ 1 4 との間の 領域に設けられる。表面層 2 6 は、第 3 のメモリチップ 1 3 と第 4 のメモリチップ 1 4 と の間の支持板 2 2 の第 1 の面 2 2 a の上に設けられる。

### [0086]

第 3 のメモリチップ 1 3 とプリント基板 2 0 は、第 4 のボンディングワイヤ 3 4 により、電気的に接続される。第 4 のボンディングワイヤ 3 4 の一端は電極パッド 1 3 b に接続

(11)

され、他端は配線層20aに接続される。

### [0087]

第4のメモリチップ14とプリント基板20は、第5のボンディングワイヤ35により、電気的に接続される。第5のボンディングワイヤ35の一端は電極パッド14bに接続され、他端は配線層20aに接続される。

### [0088]

なお、第2のボンディングワイヤ32の一端は電極パッド11bに接続され、他端は電極パッド13bに接続される。第1のメモリチップ11は、第2のボンディングワイヤ32と第4のボンディングワイヤ34により、プリント基板20に接続される。なお、第1のメモリチップ11を、第2のボンディングワイヤ32で直接プリント基板20に接続する形態としても構わない。

[0089]

また、第3のボンディングワイヤ33の一端は電極パッド12bに接続され、他端は電極パッド14bに接続される。第2のメモリチップ12は、第3のボンディングワイヤ33と第5のボンディングワイヤ35により、プリント基板20に電気的に接続される。なお第2のメモリチップ12を、第3のボンディングワイヤ33で直接プリント基板20に接続する形態としても構わない。

[0090]

封止樹脂 2 8 は、第 3 のメモリチップ 1 3 及び第 4 のメモリチップ 1 4 を覆う。封止樹脂 2 8 は、第 4 の表面膜 1 3 a 及び第 5 の表面膜 1 4 a に接する。

[0091]

次に、第3の実施形態の半導体装置の作用及び効果について説明する。

[0092]

第3の実施形態の半導体メモリ300は、第2の実施形態の半導体メモリ200と同様、支持板22の第1の面22aの上に、表面層26が設けられる。表面層26の材料は、第2の表面膜11a及び第3の表面膜12aの材料と同一である。したがって、封止樹脂28の材料を、第1のメモリチップ11の第2の表面膜11aとの密着性が良好になるように選定すれば、表面層26と封止樹脂28との密着性が良好となる。

[0093]

第3の実施形態の半導体メモリ300では、第3のメモリチップ13、及び、第4のメモリチップ14をボンディングワイヤでプリント基板20に接続するために、第1のメモリチップ11を第3のメモリチップ13に対して横方向にずらせて積層する。同様に、第2のメモリチップ12を第4のメモリチップ14に対して横方向にずらせて積層する。

[0094]

このため、第3のメモリチップ13と第4のメモリチップ14との距離(図4中のd2)が大きくなり、封止樹脂28と表面層26が接する面積が大きくなる。したがって、表面層26と封止樹脂28との密着性を向上させることが、特に、パッケージのクラックや信頼性不良の発生を抑制する観点から有効である。

[0095]

第4の表面膜13a及び第5の表面膜14aを、第2の表面膜11a及び第3の表面膜12aの材料と同一とすることが好ましい。第4の表面膜13a及び第5の表面膜14aと封止樹脂28との密着性が向上し、更に、パッケージのクラックや信頼性不良の発生を抑制できる。

[0096]

また、第3の実施形態の半導体メモリ300は、第3のメモリチップ13、及び、第4のメモリチップ14を備えることにより、半導体メモリ300中に含まれる半導体チップが5個となる。したがって、第2の実施形態の半導体メモリ200に比べて、機能が向上する。例えば、メモリ容量が増大する。

[0097]

以上、第3の実施形態の半導体メモリ300によれば、封止樹脂の密着性が向上し、パ

10

20

30

40

ッケージのクラックや信頼性不良の発生を抑制できる。また、半導体チップの数が 5 個となることで半導体メモリ 3 0 0 の機能が向上する。

### [0098]

(第4の実施形態)

第4の実施形態の半導体装置は、支持板と表面層との間に窒化シリコン膜を更に備え、 支持板の材料はシリコンであり、表面層の材料はポリイミドである点で、第3の実施形態 の半導体装置と異なっている。以下、第3の実施形態と重複する内容については一部記述 を省略する。

[0099]

図 5 は、第 4 の実施形態の半導体装置の模式断面図である。第 4 の実施形態の半導体装置は、半導体メモリ 4 0 0 である。

[0100]

半導体メモリ400は、ロジックチップ10(第1の半導体チップ)、第1のメモリチップ11(第2の半導体チップ)、第2のメモリチップ12(第3の半導体チップ)、第3のメモリチップ14(第5の半導体チップ)、第4のメモリチップ14(第5の半導体チップ)、プリント基板20(配線板)、支持板22、スペーサー24、表面層26、裏面層27、封止樹脂28、第1のボンディングワイヤ31、第2のボンディングワイヤ32、第3のボンディングワイヤ33、第4のボンディングワイヤ34、第5のボンディングワイヤ35、第1の接着層41、第2の接着層42、第3の接着層43、第4の接着層44、第5の接着層45、固定層50、外部端子60、窒化シリコン膜70を備える。

[0 1 0 1]

半導体メモリ 4 0 0 は、 5 個の半導体チップが一つのパッケージ内に納められたマルチチップパッケージ(MCP)である。

[ 0 1 0 2 ]

支持板 2 2 と表面層 2 6 の間に窒化シリコン膜 7 0 が設けられる。窒化シリコン膜 7 0 の膜厚は、例えば、 2 0 0 n m 以上 5 0 0 n m 以下である。

[0103]

支持板22の材料はシリコンである。表面層26の材料は、第2の表面膜11a及び第3の表面膜12aの材料と同一である。表面層26、第2の表面膜11a、及び、第3の表面膜12aの材料はポリイミドである。

[0104]

窒化シリコン膜 7 0 をシリコンとポリイミドの間に挟むことによりシリコンとポリイミドの密着性が向上する。したがって、支持板 2 2 と表面層 2 6 の間の剥がれが抑制される。したがって、半導体メモリ 4 0 0 の信頼性が向上する。

[0105]

以上、第4の実施形態の半導体メモリ400によれば、第3の実施形態の半導体メモリ300の効果に加え、更に信頼性が向上するという効果が得られる。

[0106]

(第5の実施形態)

第5の実施形態の半導体装置は、表面層が支持板の第1の面、第2の面、及び、側面を 覆う点で、第3の実施形態の半導体装置と異なっている。以下、第3の実施形態と重複す る内容については一部記述を省略する。

[0107]

図 6 は、第 5 の実施形態の半導体装置の模式断面図である。第 5 の実施形態の半導体装置は、半導体メモリ 5 0 0 である。

[0108]

半導体メモリ 5 0 0 は、ロジックチップ 1 0 (第 1 の半導体チップ)、第 1 のメモリチップ 1 1 (第 2 の半導体チップ)、第 2 のメモリチップ 1 2 (第 3 の半導体チップ)、第 3 のメモリチップ 1 3 (第 4 の半導体チップ)、第 4 のメモリチップ 1 4 (第 5 の半導体チップ)、プリント基板 2 0 (配線板)、支持板 2 2、スペーサー 2 4、表面層 2 6、裏

20

10

30

40

面層 2 7、封止樹脂 2 8、第 1 のボンディングワイヤ 3 1、第 2 のボンディングワイヤ 3 2、第 3 のボンディングワイヤ 3 3、第 4 のボンディングワイヤ 3 4、第 5 のボンディングワイヤ 3 5、第 1 の接着層 4 1、第 2 の接着層 4 2、第 3 の接着層 4 3、第 4 の接着層 4 4、第 5 の接着層 4 5、固定層 5 0、外部端子 6 0を備える。

[0109]

半導体メモリ 5 0 0 は、 5 個の半導体チップが一つのパッケージ内に納められたマルチチップパッケージ(M C P )である。

[0110]

表面層 2 6 は、支持板 2 2 の第 1 の面 2 2 a、第 2 の面 2 2 b、及び、側面を覆っている。表面層 2 6 は、例えば、支持板 2 2 の全面を覆っている。

[0111]

表面層 2 6 の材料は、第 2 の表面膜 1 1 a 及び第 3 の表面膜 1 2 a の材料と同一である。表面層 2 6 、第 2 の表面膜 1 1 a 、及び、第 3 の表面膜 1 2 a の材料は、例えば、ポリイミド又は窒化シリコンである。

[0112]

表面層 2 6 が、支持板 2 2 の第 1 の面 2 2 a、第 2 の面 2 2 b、及び、側面を覆うことにより、支持板 2 2 の第 1 の面 2 2 a側と封止樹脂 2 8 との密着性、支持板 2 2 の第 2 の面 2 2 b側と封止樹脂 2 8 との密着性、及び、支持板 2 2 の側面側と封止樹脂 2 8 との密着性が向上する。したがって、パッケージのクラックや信頼性不良の発生を更に抑制できる。

[0113]

以上、第5の実施形態の半導体メモリ500によれば、パッケージのクラックや信頼性 不良の発生を更に抑制できる。

[0114]

(第6の実施形態)

第6の実施形態の半導体装置は、スペーサーが第1の半導体チップを覆う点で、第3の 実施形態の半導体装置と異なっている。以下、第3の実施形態と重複する内容については 一部記述を省略する。

[0115]

図7は、第6の実施形態の半導体装置の模式断面図である。第6の実施形態の半導体装置は、半導体メモリ600である。

[0116]

半導体メモリ600は、ロジックチップ10(第1の半導体チップ)、第1のメモリチップ11(第2の半導体チップ)、第2のメモリチップ12(第3の半導体チップ)、第3のメモリチップ14(第5の半導体チップ)、プリント基板20(配線板)、支持板22、スペーサー24、表面層26、封止樹脂28、第1のボンディングワイヤ31、第2のボンディングワイヤ32、第3のボンディングワイヤ33、第4のボンディングワイヤ35、第1の接着層41、第2の接着層42、第3の接着層43、第4の接着層44、第5の接着層45、外部端子60を備える。

[0117]

スペーサー 2 4 は、ロジックチップ 1 0 、及び、第 1 のボンディングワイヤ 3 1 を覆う。スペーサー 2 4 の材料は、例えば、樹脂である。スペーサー 2 4 の材料は、例えば、封止樹脂 2 8 と異なる材料の樹脂である。スペーサー 2 4 は、例えば、樹脂フィルムである

[0118]

支持板 2 2 は、スペーサー 2 4 が設けられることで、ロジックチップ 1 0 と離間している。例えば、スペーサー 2 4 を樹脂フィルムとすることにより、ロジックチップ 1 0 と離間した支持板 2 2 の形成が容易となる。

[0119]

10

20

30

40

10

20

50

以上、第6の実施形態の半導体メモリ600によれば、第3の実施形態の半導体メモリ と同様、パッケージのクラックや信頼性不良の発生を抑制できる。また、第3の実施形態 の半導体メモリと比較して、容易に製造することが可能となる。

### [ 0 1 2 0 ]

第 1 ないし第 6 の実施形態では、配線板がプリント基板 2 0 である場合を例に説明した が、配線板は、配線層を備える板状の部材であれば、プリント基板20に限られない。例 えば、配線板として、シリコンインターポーザーを適用することも可能である。

### [0121]

第1ないし第6の実施形態では、2個、3個、又は、5個の半導体チップが一つのパッ ケ ー ジ 内 に 納 め ら れ 場 合 を 例 に 説 明 し た が 、 パ ッ ケ ー ジ 内 に 納 め ら れ 半 導 体 チ ッ プ は 、 4 個、あるいは、6個以上であってもかまわない。

### [0122]

第1ないし第6の実施形態では、半導体チップとしてロジックチップとメモリチップと がパッケージされる場合を例に説明したが、パッケージされる複数の半導体チップの種類 は特に限定されるものではない。例えば、異なる種類のメモリチップが複数パッケージさ れても良いし、異なる種類のロジックチップが複数パッケージされても良い。

### [0123]

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示 したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は .その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、 種々の省略、置き換え、変更を行うことができる。例えば、一実施形態の構成要素を他の 実施形態の構成要素と置き換え又は変更してもよい。これら実施形態やその変形は、発明 の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に 含まれる。

### 【符号の説明】

7 0

1 0 0

2 0 0

3 0 0

4 0 0

窒化シリコン膜

半導体メモリ(半導体装置)

半導体メモリ(半導体装置)

半導体メモリ(半導体装置)

半導体メモリ(半導体装置)

```

[0124]

1 0

ロジックチップ(第1の半導体チップ)

1 0 a

第1の表面膜

1 1

第1のメモリチップ(第2の半導体チップ)

30

第2の表面膜

1 1 a

1 2

第2のメモリチップ(第3の半導体チップ)

1 2 a

第3の表面膜

第3のメモリチップ(第4の半導体チップ)

1 3

第4の表面膜

1 3 a

第4のメモリチップ(第5の半導体チップ)

1 4

1 4 a

第5の表面膜

2 0

プリント基板(配線板)

2 2

支持板

2 2 a

第1の面

40

2 2 b

第2の面

2 4

スペーサー

2 6

表面層

2 8

封 止 樹 脂

3 1

第1のボンディングワイヤ

3 2

第2のボンディングワイヤ

```

5 0 0 半導体メモリ(半導体装置) 6 0 0 半導体メモリ(半導体装置)

# フロントページの続き

(72)発明者 押切 雅光

東京都港区芝浦一丁目 1 番 1 号 東芝メモリ株式会社内 F ターム(参考) 4M109 AA01 BA04 DB16 EA02 EB13 EC09 GA02