# (10) **DE 10 2005 060 700 B4** 2010.08.05

(12)

## **Patentschrift**

(21) Aktenzeichen: 10 2005 060 700.4

(22) Anmeldetag: 19.12.2005(43) Offenlegungstag: 20.07.2006

(45) Veröffentlichungstag

der Patenterteilung: 05.08.2010

(51) Int Cl.8: *H01L 27/146* (2006.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten(§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

10-2004-0115761 29.12.2004 KR

(73) Patentinhaber:

DongbuAnam Semiconductor Inc., Seoul/Soul, KR

(74) Vertreter:

Mitscherlich & Partner, Patent- und Rechtsanwälte, 80331 München

(72) Erfinder:

Jeon, In Gyun, Icheon, KR

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

US 63 00 678 B1

(54) Bezeichnung: CMOS-Bildsensor und Verfahren zur Herstellung

(57) Hauptanspruch: Verfahren zum Herstellen eines CMOS-Bildsensors, welches aufweist:

Bilden eines Photodiodenbereiches (PD) entsprechend einem ersten Source- und Drain-Bereich (150, 190) eines Transistors und einem leitfähigen Ionenbereich zweiter Art (150) auf einer Fläche eines leitfähigen Substrats (100) erster Art durch Implantation eines leitfähigen Verunreinigungsions zweiter Art (134) in einer Gesamtfläche des Substrats, wo der Transistor zu bilden ist;

Bilden eines leitfähigen schwach-dotierten Ionenbereichs zweiter Art (170) im Substrat entsprechend dem Photodiodenbereich durch niedrig-konzentriertes Implantieren eines leitfähigen Verunreinigungsions zweiter Art (138) lediglich in einem Bereich, wo der Photodiodenbereich geöffnet ist; und

Diffundieren des leitfähigen schwach-dotierten Ionenbereichs zweiter Art (170) in den leitfähigen Ionenbereich zweiter Art (150) durch einen Thermoprozess.

#### **Beschreibung**

[0001] Die vorliegende Erfindung bezieht sich auf einen komplementären Metalloxid-Halbleiter-Bildsensor (CMOS), insbesondere auf einen CMOS-Bildsensor und auf ein Verfahren zum Herstellen dieses Sensors, wobei die Transferkenndaten verbessert werden.

[0002] Ein CMOS-Bildsensor ist eine Halbleitereinrichtung, welche in einer integrierten Schaltung eingebettet ist, die mehrere Pixel aufweist, die Lichtenergie in elektrische Signale umformen. CMOS-Bildsensoren werden bei Digitalkameras, PC-Kameras, Fingerabdruck-Erkennungssystemen, Zellulartelefonen, Spielen, Raumfahrzeugen, Bildabtasteinrichtungen von Subminiatur-Flugobjekten, usw. breit verwendet. Die US 6 306 678 B1 offenbart einen CMOS-Bildsensor und ein Verfahren zu seiner Herstellung.

[0003] Ein CMOS-Bildsensor mit einem 4-Tr-Aufbau wird am verbreitesten verwendet, bei dem ein Pixel aus vier Transistoren (Tr) und einer Photodiode besteht. Beim CMOS-Bildsensor mit einem 4-Tr-Aufbau nach dem Stand der Technik ist es, da ein Fließdiffusionsknoten als ein Ausgangsanschluss wie bei einer ladungsgekoppelten Einrichtung (CCD) verwendet wird, wahrscheinlich, dass Probleme, beispielsweise das Nacheilen eines Bilds, auftreten. Um diese Probleme zu lösen, wurde ein Aufbau, bei dem eine Photo-Gate-Elektrode auf einer Photodiode gebildet ist, um ein akkumuliertes Signal zu einem Ausgangsknoten zu übertragen, vorgeschlagen. Wenn jedoch die Photo-Gate als Poly-Elektrode verwendet wird, wird die Photoansprechcharakteristik einer hergestellten Einrichtung verschlechtert. Um die Photoansprechcharakteristik zu verbessern, bringt die Verwendung einer Übertragungselektrode jedoch Schwierigkeiten mit sich.

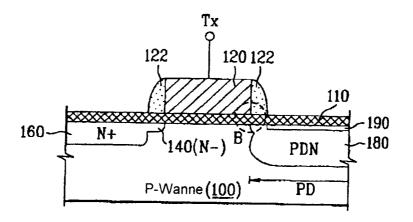

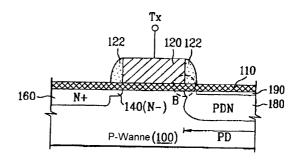

**[0004]** Bei einem CMOS-Bildsensor-Pixel mit einem 4-Tr-Aufbau nach internem Know-How werden ein Transfertransistor und eine Photodiode gebildet, wie in Fig. 1 gezeigt ist.

[0005] Wie in Fig. 1 gezeigt ist, weist der Transfertransistor 5 nach einem Stand der Technik ein CMOS-Bildsensor-Pixel mit einem 4-TR-Aufbau einen Isolationsoxidfilm oder einen Gate-Oxidfilm 2, der auf einer P-Wanne 10 eines Substrats gebildet ist, auf. Es ist der Bereich A gezeigt. Das Sensorpixel weist außerdem eine Gate-Elektrode 4 auf, welche auf dem Gate-Oxidfilm 2 gebildet ist, und erste und zweite Source- und Drain-Bereiche 12 und 14, der in der P-Wanne durch Ionenimplantation gebildet sind, auf. Der erste Source- und Drain-Bereich 12 des Transfertransistors 5 entspricht einem PD-Photodioden-Bereich. Der zweite Source- und Drain-Bereich 14 des Transfertransistors besitzt eine schwach-do-

tierte Drain-Struktur (LDD). Die LDD-Struktur kann so ausgebildet sein, dass Isolations-Abstandsstücke 6, welche an Seitenwänden der Gate-Elektrode 4 gebildet sind, als Barrieren dienen, die verhindern, dass Ionen in einige Bereiche des Substrats während der Ionenimplantation implantiert werden. Bei dem Transfertransistor 5 werden ein stark-dotierter N+-Bereich und ein schwach-dotierter N(-)-Bereich im zweiten Source- und Drain-Bereich 14 durch das Abstandsstück an der linken Seite der Gate-Elektrode 4 gebildet. Der N+-Bereich im zweiten Sourceund Drain-Bereich 14 besitzt eine Dotierkonzentration von 1 × E<sup>20-21</sup> Atome pro cm<sup>3</sup>, während der N(-)-Bereich eine Dotierkonzentration von 1  $\times$  E<sup>19-20</sup> Atome pro cm3 hat. Dann wird das N-Dotieren im ersten Source- und Drain-Bereich 12 mit der gleichen Konzentration wie mit der des N-Bereichs ausgeführt. Dies verhindert, dass Leckstrom der Photodiode aufgrund eines starken Dotierens auftritt. Der N-Dotierbereich wird als PDN-Bereich bezeichnet. Anschließend wird ein P-PDP-Bereich 18 durch Implantieren schwach-dotierter P-lonen in eine Fläche des Substrats entsprechend des PD-Photodiodenbereichs gebildet, wobei das Abstandsstück an der rechten Seite der Gate-Elektrode 4 als Barriere verwendet wird. Der PDP-Bereich 18 reduziert Oberflächenleckstellen.

[0006] Bei der oben erläuterten bekannten Struktur hat der PDN-Bereich 12, der einem Kanalbereich benachbart ist (d. h., ein Substratbereich unter der Gate-Elektrode 4) an der Fläche des Substrats eine relativ geringe Konzentration. Damit ist die Ladung, beispielsweise Elektronenladungs-Transferfähigkeit nicht zufriedenstellend, wenn ein Kanal des Transfertransistors 5 gebildet wird. Dies kann die Kenndaten des CMOS-Bildsensors nachteilig beeinträchtigen.

[0007] Die Ladungstransferfähigkeit kann durch Steuern der Dotierkonzentration oder Energie verbessert werden, um die PDN-Konzentration an der Fläche eines Siliziumsubstrats zu steigern. Dies kann jedoch unmittelbar die spezielle Ladungsspeicherfähigkeit der Photodiode und deren Photoelektroden-Sammelfähigkeit beeinträchtigen. Daher ist es nicht wünschenswert, ein Verfahren auszuwählen, welches die Dotierkonzentration oder Energie steuert.

[0008] Folglich richtet sich die vorliegende Erfindung auf einen CMOS-Bildsensor und ein Verfahren zum Herstellen dieses Sensors, mit denen eines oder mehrere der Probleme aufgrund von Begrenzungen und Nachteilen des Standes der Technik vermieden werden.

**[0009]** Ein Vorteil der vorliegenden Erfindung besteht darin, einen CMOS-Bildsensor und ein Verfahren zum Herstellen des Sensors bereitzustellen, wobei Transfer-Kenndaten verbessert werden, ohne die

### DE 10 2005 060 700 B4 2010.08.05

Ladungsspeicherfähigkeit einer Photodiode zu reduzieren.

[0010] Weitere Merkmale und Vorteile der Erfindung sind in der Beschreibung, die folgt, herausgestellt und werden teilweise aus der Beschreibung deutlich oder können durch die Ausübung der Erfindung erlernt werden. Die Aufgaben und weiteren Vorteile der Erfindung werden durch den Aufbau und das Verfahren realisiert und erreicht, die insbesondere in der schriftlichen Beschreibung und deren Patentansprüche wie auch in den angehängten Zeichnungen herausgestellt sind.

**[0011]** Um diese und weitere Vorteile zu erreichen und gemäß dem Zweck der vorliegenden Erfindung, wie sie hier verkörpert und breit beschrieben wird, umfasst das Verfahren zum Herstellen eines CMOS-Bildsensors gemäß Anspruch 1 das

Bilden eines Photodiodenbereiches entsprechend einem ersten Source- und Drain-Bereich eines Transistors und einem leitfähigen Ionenbereich zweiter Art auf einer Fläche eines leitfähigen Substrats erster Art durch Implantation eines leitfähigen Verunreinigungsions zweiter Art in einer Gesamtfläche des Substrats, wo der Transistor zu bilden ist;

Bilden eines leitfähigen schwach-dotierten Ionenbereichs zweiter Art im Substrat entsprechend dem Photodiodenbereich durch schwaches Implantieren eines leitfähigen Verunreinigungsions zweiter Art lediglich in einem Bereich, wo der Photodiodenbereich geöffnet ist; und

Diffundieren des leitfähigen leicht-dotierten Ionenbereichs zweiter Art in den leitfähigen Ionenbereich zweiter Art durch einen Thermoprozess.

**[0012]** Gemäß der vorliegenden Erfindung umfasst ein CMOS-Bildsensor gemäß Anspruch 14 ein leitfähiges Halbleitersubstrat erster Art, welches einen Transistorbereich und einen Photodiodenbereich aufweist, der einem ersten Source- und Drain-Bereich eines Transistors entspricht;

einen leitfähigen Diffusionsbereich zweiter Art, der im Substrat gebildet ist, der dem Photodiodenbereich entspricht, und der einen leitfähigen Ionenbereich zweiter Art in einem oberen Bereich und einen leitfähigen schwach-dotierten Ionenbereich zweiter Art in einem unteren Bereich umfasst; und

einen leitfähigen Ionenbereich erster Art, der in einer Fläche des Substrats gebildet ist, der dem Photodiodenbereich entspricht.

**[0013]** Es soll verstanden sein, dass sowohl die obige Allgemeinbeschreibung als auch die nachfolgende Detailbeschreibung beispielhaft und erläuternd sind und beabsichtigt ist, weitere Erläuterung der Erfindung, wie diese beansprucht ist, bereitzustellen.

**[0014]** Die beiliegenden Zeichnungen, die beigefügt sind, um ein weiteres Verständnis der Erfindung be-

reitzustellen, und die einen Teil dieser Beschreibung bilden, zeigen eine Ausführungsform (Ausführungsformen) der Erfindung und dienen zusammen mit der Beschreibung dazu, das Prinzip der Erfindung zu erläutern.

**[0015]** Fig. 1 ist eine Querschnittsansicht, die einen CMOS-Bildsensor nach dem Stand der Technik zeigt;

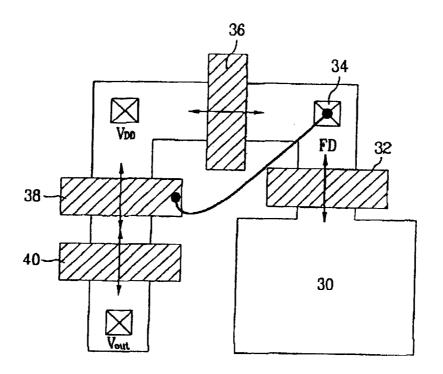

**[0016]** Fig. 2 ist ein Schaltungsdiagramm, welches einen CMOS-Bildsensor nach der vorliegenden Erfindung zeigt;

[0017] Fig. 3 ist ein Layout, welches einen CMOS-Bildsensor nach der vorliegenden Erfindung zeigt;

**[0018]** Fig. 4A bis Fig. 4E sind Querschnittsansichten, welche Prozessschritte zum Herstellen eines CMOS-Bildsensors nach der vorliegenden Erfindung zeigen; und

**[0019]** Fig. 5 ist eine Querschnittsansicht, die einen CMOS-Bildsensor zeigt, der gemäß der vorliegenden Erfindung hergestellt ist.

**[0020]** Es wird nun ausführlich auf Ausführungsformen der vorliegenden Erfindung bezuggenommen, von denen Beispiele in den beiliegenden Zeichnungen gezeigt sind. Wenn immer möglich werden die gleichen Bezugszeichen durchwegs in den Zeichnungen verwendet, um gleiche oder ähnliche Teile zu bezeichnen.

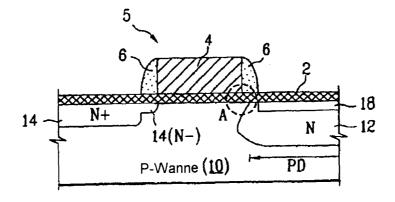

**[0021]** Fig. 2 ist ein Schaltungsdiagramm, welches ein Einheitspixel eines CMOS-Bildsensors gemäß der vorliegenden Erfindung zeigt, und Fig. 3 ist ein Layout, welches das Einheitspixel zeigt.

**[0022]** Die Arbeitsweise der Einheitspixel des CMOS-Bildsensors gemäß der vorliegenden Erfindung wird mit Hilfe von <u>Fig. 2</u> und <u>Fig. 3</u> beschrieben.

[0023] Wie in Fig. 2 und Fig. 3 gezeigt ist, besitzt das Einheitspixel des CMOS-Bildsensors eine Photodiode 30 und vier Transistoren, d. h., einen Transfertransistor 32, einen Reset-Transistor 36, einen Ansteuertransistor 38 und einen Auswahltransistor 40. Wenn der Transfertransistor 32 und der Reset-Transistor 36 eingeschaltet sind, wird eine Spannung  $V_{\rm DD}$ zur Photodiode 30 übertragen. Danach werden der Transfertransistor 32 und der Reset-Transistor 36 ausgeschaltet. Die Photodiode 30 sammelt Licht für eine bestimmte Zeitperiode in einer Weise, dass Elektronenlochpaare EHP oder Signalladungen proportional zum einfallenden Licht auf die Photodiode 30 erzeugt werden. Ein Source-Potential des Transfertransistors 32 wird proportional zu den erzeugten Signalladungen variiert. Wenn der Transfertransistor 32 durch ein Signal Tx eingeschaltet wird, beispielsweise ein Signal Tx mit einer hohen Spannung, welche einem Gate des Transfertransistors 32 zugeführt wird, werden die akkumulierten Signalladungen zu einem Fließdiffusionsknoten (FD) 34 übertragen. Das Potential des FD-Knotens 34 wird proportional zu den übertragenen Signalladungen variiert. Das Source-Potential des Ansteuertransistors 38 wird in Abhängigkeit vom variierten Potential des FD-Knotens 34 variiert. Der Ansteuertransistor 38 wird wie ein Source-Folger-Transistor und dient als Signalverstärker. Außerdem dient der Ansteuertransistor 38 dazu, Rauschen oder Restladungen zu verbessern. Wenn der Auswahltransistor 40 nun durch ein Gate-Signal Sx eingeschaltet wird, liest der Auswahltransistor 40 Daten über einen Ausgangsanschluss V<sub>out</sub>. Der Reset-Transistor 36 wird durch das Gate-Signal Rx einund ausgeschaltet. Wenn der Reset-Transistor 36 eingeschaltet ist, nimmt der FD-Knoten 34 die Spannung V<sub>DD</sub> an, um einen Referenzwert zu ermitteln und wartet auf das ermittelte Signal. Das heißt, der Reset-Transistor dient dazu, das Einheitspixel des CMOS-Bildsensors zu initialisieren.

[0024] Damit ist die Ladungstransferfähigkeit des Transfertransistors 32 signifikant, da das Signal, welches durch die Photodiode 30 ermittelt wird, als ein elektrisches Signal über den Ausgangsanschluss Vout ausgegeben wird. Dies beeinträchtigt die Kenndaten des CMOS-Bildsensors. Insbesondere wird das EHP, welches durch die Photodiode erzeugt wird, der Source des Transfertransistors 32 zugeführt, sobald der Transfertransistors 32 eingeschaltet ist, und wird zum Drain (d. h., FD-Knoten) des Transfertransistors 32 über einen Kanal übertragen. Wenn die EHP-Transfer-Kenndaten des Transfertransistors 32 gering sind, können Ladungen während der Transferoperation verloren oder verformt werden.

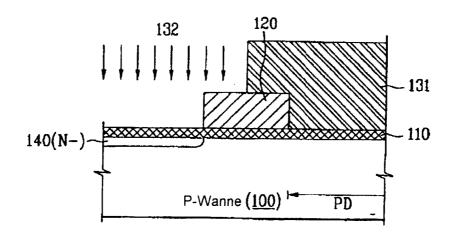

**[0025]** Fig. 4A bis Fig. 4E sind Querschnittsansichten, welche Prozessschritte zum Herstellen des CMOS-Bildsensors nach der vorliegenden Erfindung zeigen.

[0026] Zunächst wird, wie in Fig. 4A gezeigt ist, ein Isolationsoxidfilm oder ein Gate-Oxidfilm 110 auf einem Substrat oder eine P-Wanne 100 aufgebracht, und eine Gate-Elektrode 120 wird auf dem Gate-Oxidfilm 110 gebildet. Der Gate-Oxidfilm 110 und die Gate-Elektrode 120 können durch ein herkömmliches Verfahren gebildet werden. Anschließend wird ein Photolackfilm aufgebracht und dann durch Belichtungs- und Entwicklungsprozesse bemustert, um eine Photolack-Filmmusterschicht 131 zu bilden, die lediglich einen zweiten Source- und Drain-Bereich 140 öffnet. Ein N-Bereich 140 ist im zweiten Source- und Drain-Bereich 140 durch eine erste Ionenimplantation 132 gebildet. Die erste Ionenimplantation 132 kann bei einer Konzentration von 3 × E<sup>14</sup> Atome pro cm<sup>3</sup>, oder E<sup>19</sup> Atome pro cm<sup>3</sup> und einer Ionenimplantationsenergie von 10 KeV unter Verwendung von Arsen als Ion durchgeführt werden

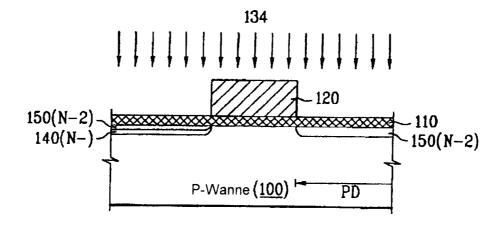

**[0027]** Nachfolgend wird, wie in Fig. 4B gezeigt ist, die Photolackfilm-Musterschicht 131 entfernt, und es wird ein N – 2-Bereich 150 durch eine zweite Ionenimplantation 134 auf einer gesamten Fläche des Substrats gebildet. Die zweite Ionenimplantation 134 kann bei einer niedrigen Dotierkonzentration von ungefähr 1 ×  $E^{16}$  Atome pro cm³ – 1 ×  $E^{17}$  Atome pro cm³ oder ungefähr 1 ×  $E^{11}$  Atome pro cm³ – 5 ×  $E^{11}$  Atome pro cm³ ausgeführt werden. Da die zweite Ionenimplantation 134 auf der gesamten Fläche des Substrats ohne zusätzliche Photolithografie-Verarbeitung ausgeführt wird, wird der N – 2-Bereich 150 in sowohl dem zweiten Source- und Drain-Bereich 140 als auch einem PD-Bereich gebildet, was dem ersten Source- und Drain-Bereich entspricht.

**[0028]** Die zweite lonenimplantation **134** zum Bilden des N – 2-Bereichs **150** kann bei einer Dotierkonzentration von ungefähr  $1 \times E^{16}$  Atome pro cm³ –  $1 \times E^{17}$  Atome pro cm³ und einer lonen-implantationsenergie von 10 KeV bis 50 KeV durchgeführt werden, wenn Phosphor als Implantationsion verwendet wird. Die zweite lonenimplantation **134** kann mit einer Dotierkonzentration von ungefähr  $1 \times E^{16}$  Atome pro cm³ –  $1 \times E^{17}$  Atome pro cm³ und einer lonenimplantationsenergie von 30 KeV ausgeführt werden, wobei Arsen als Implantationsion verwendet wird.

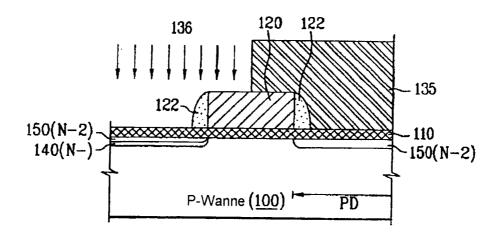

[0029] Anschließend werden, wie in Fig. 4C gezeigt ist, Abstandstücke 122 an Seitenwänden der Gate-Elektrode 120 gebildet. Danach wird ein N+-Bereich durch eine dritte Ionenimplantation 136 in einem Bereich gebildet, wo ein Photolackfilm 135 nicht gebildet ist und bedeckt den PD-Bereich und gibt den zweiten Source- und Drain-Bereich frei. Der N+-Bereich entspricht einem herkömmlichen Source- und Drain-Bereich eines MOS-Transistors und besitzt eine LDD-Struktur. Die dritte Ionenimplantation 136 kann mit einer Dotierkonzentration von ungefähr 1 ×  $E^{20}$  Atome pro cm<sup>3</sup> – 1 ×  $E^{21}$  Atome pro cm<sup>3</sup> und einer Ionenimplantationsenergie von 65 KeV unter Verwendung von Arsen als ein Ion ausgeführt werden. Die Abstandsstücke 122 der Gate-Elektrode 120 können durch ein herkömmliches Verfahren gebildet werden, wobei ein Oxidfilm auf einer Gate-Elektrode abgelagert wird und durch anisotropes Ätzen geätzt wird, um lediglich an Seitenwänden zu verbleiben.

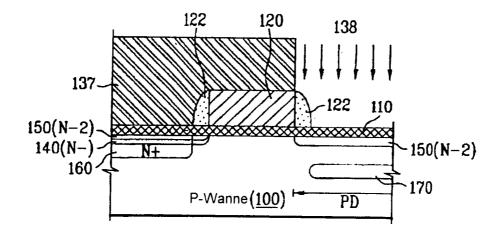

[0030] Gemäß Fig. 4D wird ein Photolackfilmmuster 137 so gebildet, dass der zweite Source- und Drain-Bereich des Transfertransistors abgeschaltet ist. Ein PDN-Bereich 170 ist im Substrat des ersten Source- und Drain-Bereichs durch eine vierte Ionenimplantation 138 in einem Bereich gebildet, wo der PD-Bereich geöffnet ist. Die vierte Ionenimplantation 138 kann bei einer Dotierkonzentration von 1 × E<sup>16</sup>

Atome pro cm³ oder 3 × E¹² Atome pro cm³ oder weniger und einer Ionenimplantationsenergie von 100 KeV bis 160 KeV unter Verwendung von Phosphor als Ion durchgeführt werden.

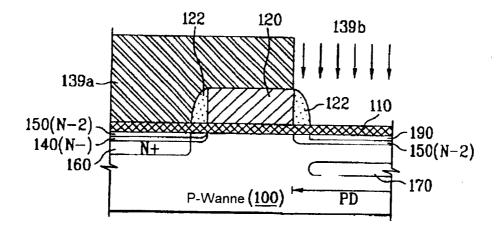

[0031] Ein Photolackfilmmuster 139a ist so ausgebildet, dass der zweite Source- und Drain-Bereich des Transfertransistors ausgeschaltet ist. Ein schwach dotierter PDP-Bereich 190 ist in der Fläche des Substrats durch eine fünfte Ionenimplantation 139b in einem Bereich gebildet, wo der PD-Bereich geöffnet ist. Die fünfte Ionenimplantation 139a kann bei einer Dotierkonzentration von 1 ×  $E^{16}$  Atome pro cm³ oder 2 ×  $E^{12}$  Atome pro cm³ oder weniger und einer Ionenimplantationsenergie von 20 KeV unter Verwendung von BF $_2$  als Ion durchgeführt werden. Es ist unwesentlich, wenn die Gate-Elektrode 120 teilweise durch die fünfte Ionenimplantation 139b teilweise freigelegt wird.

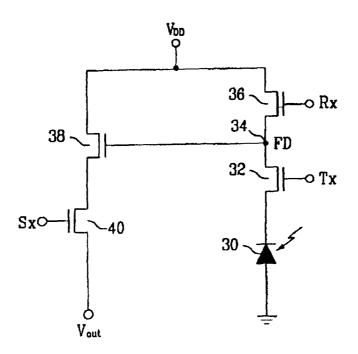

[0032] Nachdem der PDP-Bereich 190 gebildet ist, wird ein Thermoprozess ausgeführt. Ein Dotierungsprofil des Transfertransistors und des PD-Bereich wird gebildet, wie in Fig. 5 gezeigt ist. Danach wird nach dem Thermoprozess ein PDN/N - 2 Diffusionsbereich **180** gebildet, wie im Profil von Fig. 5 gezeigt ist. Der Grund dafür ist der, dass der PDN-Bereich 170, der im Substrat bei einer bestimmten Tiefe gebildet ist, nach oben und nach unten in einer Gauss-Verteilung aufgrund des Thermoprozesses diffundiert. Da die anderen Dotierbereiche 140, 150 und 190 auf der Fläche des Siliziumsubstrats 100 gebildet sind, diffundieren diese, während ihre Profile beibehalten werden, sogar nach dem Thermoprozess. Im Gegensatz dazu wird der PDN/N - 2-Diffusionsbereich 180 gebildet, wenn der PDN-Bereich 170 nach oben und nach unten im Substrat diffundiert. Daher wird der PDN/N - 2-Diffusionsbereich 180 so ausgebildet, wie im Profil von Fig. 5 gezeigt ist.

[0033] Wie in Fig. 5 gezeigt ist, weist der Transfertransistor in dem Einheitspixel des CMOS-Bildsensors nach der vorliegenden Erfindung den ersten Source- und Drain-Bereich entsprechend einer Photodiodenbereich (PD-Bereich) auf, der im P-Substrat 100 gebildet ist, den zweiten Source- und Drain-Bereich und die Gate-Elektrode 120, die auf dem Substrat gebildet ist. Es ist der Bereich B gezeigt. Wenn eine vorher festgelegte Vorspannung an die Gate-Elektrode 120 angelegt wird, wird ein Kanalbereich zwischen den ersten Source- und Drain-Bereichen 140 und 160 und dem zweiten Source- und Drain-Bereich gebildet. Der PDN/N – 2-Diffusionsbereich, der in die Fläche des Substrats diffundiert ist. wird in den ersten Source- und Drain-Bereichen 140 und 160 gebildet. Der Kanalbereich schließt sich an den PDN/N - 2-Diffusionsbereich an, der in der Fläche des Substrats im Photodiodenbereich gebildet ist. Außerdem erstreckt der N - 2-Bereich zum Kanalbereich unterhalb der Gate-Elektrode 120, nachdem er durch den Substratbereich unterhalb der Abstandsstücke 122 der Gate-Elektrode 120 gelaufen ist

[0034] Bei einer weiteren Ausführungsform der vorliegenden Erfindung kann die N – 2-Ionenimplantation durchgeführt werden, nachdem der PDN-Bereich 170 im Substrat gebildet ist. Nachdem der PDN-Bereich 170 gebildet ist, wird der zweite Source- und Drain-Bereich der Transfertransistors ausgeschaltet, und das Photolackfilmmuster 137 wird gebildet, um lediglich den PD-Bereich zu öffnen. Danach wird die N - 2-Ionenimplantation ausgeführt. Bei dieser Ausführungsform wird der Bereich, der durch die N -2-Ionenimplantation gebildet wird, lediglich im ersten Source- und Drain-Bereich entsprechend dem PD-Bereich ungleich Fig. 4B gebildet, welche den N - 2-Ionenimplantationsbereich zeigt, der im sowohl dem ersten Source- und Drain-Bereich als auch im zweiten Source- und Drain-Bereich gebildet wird.

**[0035]** Bei einer noch weiteren Ausführungsform der vorliegenden Erfindung kann die N+-Ionenimplantation im zweiten Source- und Drain-Bereich ausgeführt werden, nachdem der PDN-Bereich **170** im Substrat gebildet ist. Bei dieser Ausführungsform wird, nachdem der PDN-Bereich **170** im Substrat durch den Thermoprozess diffundiert ist, die N – 2-Ionenimplantation durchgeführt, um den PDN/N – 2-Diffusionsbereich **180** zu bilden.

[0036] Da die obigen Ausführungsformen auf der Basis der Source- und Drain-Bereiche der LDD-Struktur beschrieben wurden, waren die Schritte zum Implantieren des N-lons in den zweiten Source- und Drain-Bereich und das Bilden der Abstandsstücke an den Seitenwänden der Gate-Elektrode erforderlich. Da die vorliegende Erfindung jedoch nicht auf die LDD-Struktur beschränkt ist, können die obigen Schritte ausgelassen werden.

[0037] Wie oben beschrieben haben der CMOS-Bildsensor und das Verfahren zum Herstellen dieses Sensors nach der vorliegenden Erfindung die folgenden Vorteile:

Da der PDN/N – 2-Diffusionsbereich, in den der N – 2-Bereich und der PDN-Bereich diffundieren, im ersten Source- und Drain-Bereich entsprechend dem PD-Bereich benachbart zum Kanalbereich des Transfertransistors existieren, ist es möglich, den Kanalwiderstand der Source- und Drain-Bereiche zu vermindern und das Potential zu steigern, ohne die Ladungsspeicherfähigkeit der Photodiode zu reduzieren. Daher kann die Ladungsübertragungsfähigkeit verbessert werden. Somit ist es möglich, die Kenndaten des CMOS-Bildsensors zu verbessern.

[0038] Es wird deutlich, das der Fachmann verschiedene Modifikationen und Variationen bei der vorliegenden Erfindung ausführen kann, ohne den

### DE 10 2005 060 700 B4 2010.08.05

Rahmen der Erfindung zu verlassen. Somit ist beabsichtigt, dass die vorliegende Erfindung alle Modifikationen und Variationen dieser Erfindung abdeckt, vorausgesetzt, dass sie in den Rahmen der angehängten Patentansprüche und deren Äquivalente fallen.

#### Patentansprüche

1. Verfahren zum Herstellen eines CMOS-Bildsensors, welches aufweist:

Bilden eines Photodiodenbereiches (PD) entsprechend einem ersten Source- und Drain-Bereich (150, 190) eines Transistors und einem leitfähigen Ionenbereich zweiter Art (150) auf einer Fläche eines leitfähigen Substrats (100) erster Art durch Implantation eines leitfähigen Verunreinigungsions zweiter Art (134) in einer Gesamtfläche des Substrats, wo der Transistor zu bilden ist;

Bilden eines leitfähigen schwach-dotierten Ionenbereichs zweiter Art (170) im Substrat entsprechend dem Photodiodenbereich durch niedrig-konzentriertes Implantieren eines leitfähigen Verunreinigungsions zweiter Art (138) lediglich in einem Bereich, wo der Photodiodenbereich geöffnet ist; und

Diffundieren des leitfähigen schwach-dotierten lonenbereichs zweiter Art (170) in den leitfähigen lonenbereich zweiter Art (150) durch einen Thermoprozess.

- 2. Verfahren nach Anspruch 1, welches außerdem das Bilden von Abstandsstücken (122) auf beiden Seiten einer Gate-Elektrode (120) des Transistors aufweist, nachdem der leitfähige Ionenbereich zweiter Art (150) gebildet ist.

- 3. Verfahren nach Anspruch 2, welches außerdem das Bilden eines Photolackfilms aufweist, der als eine Maske bemustert ist, um lediglich einen Source- und Drain-Bereich zweiter Art des Transistors zu öffnen, und um einen leitfähigen stark-dotierten Ionenbereichs zweiter Art (160) im zweiten Source- und Drain-Bereich (140) durch hoch-konzentriertes Implantieren einer leitfähigen Verunreinigung (136) erster Art unter Verwendung des Abstandsstücks (122) zu bilden, welches auf einer Seite der Gate-Elektrode verwendet wird.

- 4. Verfahren nach Anspruch 3, wobei der leitfähige stark-dotierte Ionenbereich zweiter Art (**160**) tiefer ist als der leitfähige Ionenbereich zweiter Art (**150**).

- 5. Verfahren nach Anspruch 1, wobei der leitfähige schwach-dotierte Ionenbereich zweiter Art (170) des Photodiodenbereichs tiefer ist als der leitfähige Ionenbereich zweiter Art (150).

- 6. Verfahren nach Anspruch 1, welches außerdem das Bilden eines leitfähigen Ionenbereichs erster Art (190) umfasst, der dünner ist als der leitfähige Ionenbereich zweiter Art (150), auf der Fläche des

Substrats entsprechend dem Photodiodenbereich durch Implantieren eines leitfähigen Verunreinigungsions erster Art (139b) lediglich in einem Bereich, wo der Photodiodenbereich geöffnet ist, bevor der leitfähige schwach-dotierte Ionenbereich zweiter Art (170) durch den Thermoprozess diffundiert wird.

- 7. Verfahren nach Anspruch 1, welches außerdem das Bilden eines leitfähigen Ionenbereichs erster Art (190) umfasst, der dünner ist als der leitfähige Ionenbereich zweiter Art (150), auf der Fläche des Substrats entsprechend dem Photodiodenbereich durch Implantation eines leitfähigen Verunreinigungsions erster Art (139b) lediglich in einem Bereich, wo der Photodiodenbereich geöffnet ist, nachdem der leitfähige schwach-dotierte Ionenbereich zweiter Art (170) durch den Thermoprozess diffundiert ist.

- 8. Verfahren nach Anspruch 6, wobei der leitfähige Ionenbereich erster Art (**190**) durch Implantation des leitfähigen Verunreinigungsions erster Art mit einer Dotierkonzentration von 1  $\times$  E<sup>16</sup> Atome pro cm<sup>3</sup> oder kleiner gebildet ist.

- 9. Verfahren nach Anspruch 7, wobei der leitfähige lonenbereich erster Art (**190**) durch Implantation des leitfähigen Verunreinigungsions erster Art mit einer Dotierkonzentration von  $1 \times E^{16}$  Atome pro cm³ oder kleiner gebildet ist.

- 10. Verfahren nach Anspruch 1, wobei der leitfähige Ionenbereich zweiter Art (**150**) durch Implantation des leitfähigen Verunreinigungsions zweiter Art bei einer Dotierkonzentration von ungefähr 1  $\times$  E<sup>16</sup> Atome pro cm<sup>3</sup> 1  $\times$  E<sup>17</sup> Atome pro cm<sup>3</sup> gebildet wird.

- 11. Verfahren nach Anspruch 10, wobei der leitfähige Ionenbereich zweiter Art (150) unter Verwendung von Phosphor oder Arsen als leitfähiges Verunreinigungsion zweiter Art gebildet wird.

- 12. Verfahren nach Anspruch 11, wobei der leitfähige schwach-dotierte Ionenbereich zweiter Art (**170**) durch Implantation des leitfähigen Verunreinigungsions zweiter Art bei einer Dotierkonzentration von  $1 \times E^{16}$  Atome pro cm³ oder kleiner gebildet wird.

- 13. Verfahren nach Anspruch 1, wobei der Transistor ein Transfertransistor ist.

- 14. CMOS-Bildsensor, der aufweist:

ein leitfähiges Halbleitersubstrat erster Art (100), welches einen Transistorbereich und einen Photodiodenbereich (PD) aufweist, der einem ersten Sourceund Drain-Bereich eines Transistors (150, 190) entspricht;

einen leitfähigen Diffusionsbereich zweiter Art (180), der im Substrat gebildet ist, der dem Photodiodenbereich entspricht, und der einen leitfähigen Ionenbereich zweiter Art (150) in einem oberen Bereich des

Photodiodenbereiches in dem Substrat und einen leitfähigen schwach-dotierten Ionenbereich zweiter Art (170) in einem unteren Bereich des Photodiodenbereiches in dem Substrat umfasst; und einen leitfähigen Ionenbereich erster Art (190), der in einer Fläche des Substrats gebildet ist, der dem Photodiodenbereich entspricht.

- 15. CMOS-Bildsensor nach Anspruch 14, wobei der Transistor eine Gate-Elektrode (120) aufweist, welche auf dem Substrat gebildet ist, und wobei die Gate-Elektrode mit Abstandsstücken (122) an beiden Seitenwänden versehen ist, und der leitfähige Ionenbereich zweiter Art (150) sich in einem Bereich unter das Abstandsstück im ersten Source- und Drain-Bereich erstreckt.

- 16. CMOS-Bildsensor nach Anspruch 14, wobei der leitfähige Ionenbereich zweiter Art (**150**) ein leitfähiges Verunreinigungsion zweiter Art aufweist, welches eine Dotierkonzentration von ungefähr 1 ×  $E^{16}$  Atome pro cm³ 1 ×  $E^{17}$  Atome pro cm³ hat.

- 17. CMOS-Bildsensor nach Anspruch 16, wobei der leitfähige Ionenbereich zweiter Art (**150**) Phosphor oder Arsen aufweist.

- 18. CMOS-Bildsensor nach Anspruch 16, wobei der leitfähige schwach-dotierte Ionenbereich zweiter Art (170) ein leitfähiges Verunreinigungsion zweiter Art aufweist, welches eine Dotierkonzentration von 1 × E<sup>16</sup> Atome pro cm<sup>3</sup> oder weniger hat.

- 19. CMOS-Bildsensor nach Anspruch 14, wobei der Transistor ein Transfertransistor ist.

Es folgen 6 Blatt Zeichnungen

## Anhängende Zeichnungen

FIG. 1 Stand der Technik

FIG. 2

FIG. 3

FIG. 4A

FIG. 4B

FIG. 4C

FIG. 4D

FIG. 4E

FIG. 5