# (19) 国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 116488657 A (43) 申请公布日 2023.07.25

(21)申请号 202310732195.8

(22) 申请日 2023.06.20

(71) 申请人 南方电网数字电网研究院有限公司 地址 510700 广东省广州市黄埔区中新广 州知识城亿创街1号406房之86

(72) 发明人 李鹏 吕前程 田兵 韦杰 骆柏锋 张佳明 樊小鹏 刘仲 王志明 尹旭 谭泽杰 徐振恒 李立浧 林跃欢 刘胜荣

(74) 专利代理机构 华进联合专利商标代理有限 公司 44224

专利代理师 唐彩琴

(51) Int.CI.

**HO3M** 3/00 (2006.01) **HO3M** 1/12 (2006.01)

权利要求书2页 说明书9页 附图5页

#### (54) 发明名称

积分器电路、西格玛-德尔塔调制器及模数 转换器

#### (57) 摘要

本申请涉及一种积分器电路、西格玛-德尔塔调制器及模数转换器。该积分器电路包括:依次连接的第一斩波模块、第二斩波模块、放大器、第三斩波模块以及连接于第三斩波模块的输出端和第一斩波模块的输入端之间的反馈模块。通过使第三斩波信号和第二斩波信号的频率为大于第一斩波信号频率的相同值,且第三斩波信号和第二斩波信号相位相同的时间与相反的时间相同,使得电路中的为正的偏移尖峰与为负的偏移尖峰的总数相等,从而平均偏移值为0。由此,降低了积分器输出信号的总偏移量,进而通过后续的低通滤波处理,可以显著降低积分器输出信号的总偏移量,进而通过后续的低通滤波处理,可以显著降低积分器输出信号的总偏移量,从而提升sigma-delta模数转换器的转换结果的准确性。

CN 116488657 A

1.一种积分器电路,其特征在于,包括:

第一斩波模块,用于接入输入信号和第一斩波信号,并根据所述第一斩波信号调制所述输入信号,得到第一调制信号;

第二斩波模块,连接所述第一斩波模块的输出端,还用于接入第二斩波信号,并根据所述第二斩波信号调制所述第一调制信号,得到第二调制信号;所述第二斩波信号的频率的预设倍数,所述预设倍数为大于1倍的整数倍;

放大器,连接所述第二斩波模块的输出端,用于对所述第二调制信号进行放大,得到调制放大信号:

第三斩波模块,连接所述放大器的输出端,还用于接入第三斩波信号,并根据所述第三 斩波信号调制所述调制放大信号,得到第三调制信号;所述第三斩波信号的频率与所述第 二斩波信号的频率相同,且所述第三斩波信号与所述第二斩波信号相位相同的时间与相位 相反的时间相等;

反馈模块,连接于所述第三斩波模块的输出端和所述第一斩波模块的输入端之间,用 于将所述第三调制信号反馈至所述第一斩波模块,以使所述第一斩波模块、所述第二斩波 模块和所述放大器对所述第三调制信号进行解调放大处理,得到解调放大信号;

所述第三斩波模块,还用于根据所述第三斩波信号对所述解调放大信号进行调制得到 输出信号,所述输出信号包括有用信号,所述有用信号为所述输入信号经过调制、解调和放 大处理后的信号。

2.根据权利要求1所述的积分器电路,其特征在于,所述第三斩波模块包括第一斩波单元和第二斩波单元;所述第一斩波单元的输入端和所述第二斩波单元的输入端均连接所述放大器的输出端,所述第一斩波单元的输出端连接所述反馈模块;

所述第一斩波单元和所述第二斩波单元还用于接入所述第三斩波信号;所述第一斩波单元用于根据所述第三斩波信号调制所述调制放大信号得到所述第三调制信号;所述第二 斩波单元用于根据所述第三斩波信号调制所述解调放大信号得到所述输出信号。

- 3.根据权利要求1所述的积分器电路,其特征在于,所述第一斩波信号的频率大于所述 输入信号的频率。

- 4.根据权利要求1所述的积分器电路,其特征在于,所述第二斩波信号的频率为所述第一斩波信号的频率的三倍以上。

- 5.根据权利要求1至4中任一项所述的积分器电路,其特征在于,在所述第一斩波信号为高电平时,所述第三斩波信号与所述第二斩波信号相位相同;在所述第一斩波信号为低电平时,所述第三斩波信号与所述第二斩波信号相位相反。

- 6.根据权利要求5所述的积分器电路,其特征在于,还包括采样电路,所述采样电路的输入端接入外部信号,所述采样电路的输出端连接所述第一斩波模块的输入端,所述采样电路用于对所述外部信号进行采样,并输出所述输入信号至所述第一斩波模块。

- 7.根据权利要求6所述的积分器电路,其特征在于,所述第一斩波模块的输入端包括正极和负极,所述第一斩波单元的输出端包括正极和负极,所述反馈模块包括:第一反馈单元和第二反馈单元,所述第一反馈单元连接于所述第一斩波单元的输出端正极和所述第一斩波模块的输入端正极之间;所述第二反馈单元连接于所述第一斩波单元的输出端负极和所述第一斩波模块的输入端负极之间。

- 8.根据权利要求7所述的积分器电路,其特征在于,所述第一反馈单元包括第一电容, 所述第二反馈单元包括第二电容;所述第一电容连接于所述第一斩波单元的输出端正极和 所述第一斩波模块的输入端正极之间,所述第二电容连接于所述第一斩波单元的输出端负 极和所述第一斩波模块的输入端负极之间。

- 9.一种西格玛-德尔塔调制器,其特征在于,包括:依次连接的积分器电路、低通滤波电路和量化器电路,所述积分器电路为如权利要求1-8任意一项所述的积分器电路;

所述低通滤波电路用于对所述积分器电路输出的输出信号进行低通滤波处理,以得到 所述输出信号中的有用信号;

所述量化器电路用于将所述有用信号转换为多位数字信号并输出。

10.一种模数转换器,其特征在于,包括如权利要求9所述的西格玛-德尔塔调制器。

# 积分器电路、西格玛-德尔塔调制器及模数转换器

#### 技术领域

[0001] 本申请涉及集成电路技术领域,特别是涉及一种积分器电路、西格玛-德尔塔调制器及模数转换器。

## 背景技术

[0002] 模数转换器 (Analog-to-digital Converter, ADC) 用于将模拟信号转换为数字信号。Sigma-Delta (西格玛-德尔塔) 模数转换器因具有高分辨率、高集成度、低成本等优势,在各种模数转换器中脱颖而出,在集成电路领域得到了广泛的应用。

[0003] 但是,sigma-delta模数转换器在处理低频、低电平信号时,易受到直流偏置、闪烁噪声的影响,因此sigma-delta模数转换器中的重要组成部分sigma-delta调制器(sigma-delta Modulator,SDM)需要具有降低直流偏置和低频噪声的功能。

[0004] 斩波稳定技术作为一种提高运算放大器低频性能的方法,常被用于sigma-delta调制器的积分器。相关技术中,积分器大多采用镜像积分结构,利用斩波器消除积分器中的运算放大器本身产生的直流失调和闪烁噪声。但是,由于制作工艺的原因,斩波开关处的电荷注入和时钟馈通对积分器的运算放大器的作用,使得运算放大器产生了较大的残余偏移量,该残余偏移量与输入信号放大处理后的信号混合,增加了积分器输出信号的总偏移量,导致sigma-delta模数转换器最终的转换结果出现偏差。

#### 发明内容

[0005] 基于此,有必要提供一种能够降低残余偏移量的积分器电路、西格玛-德尔塔调制器及模数转换器。

[0006] 一种积分器电路,包括:

第一斩波模块,用于接入输入信号和第一斩波信号,并根据所述第一斩波信号调制所述输入信号,得到第一调制信号:

第二斩波模块,连接所述第一斩波模块的输出端,还用于接入第二斩波信号,并根据所述第二斩波信号调制所述第一调制信号,得到第二调制信号;所述第二斩波信号的频率的预设倍数,所述预设倍数为大于1倍的整数倍;

放大器,连接所述第二斩波模块的输出端,用于对所述第二调制信号进行放大,得 到调制放大信号;

第三斩波模块,连接所述放大器的输出端,还用于接入第三斩波信号,并根据所述 第三斩波信号调制所述调制放大信号,得到第三调制信号;所述第三斩波信号的频率与所 述第二斩波信号的频率相同,且所述第三斩波信号与所述第二斩波信号相位相同的时间与 相位相反的时间相等;

反馈模块,连接于所述第三斩波模块的输出端和所述第一斩波模块的输入端之间,用于将所述第三调制信号反馈至所述第一斩波模块,以使所述第一斩波模块、所述第二斩波模块和所述放大器对所述第三调制信号进行解调放大处理,得到解调放大信号;

所述第三斩波模块,还用于根据所述第三斩波信号对所述解调放大信号进行调制 得到输出信号,所述输出信号包括有用信号,所述有用信号为所述输入信号经过调制、解调 和放大处理后的信号。

[0007] 在其中一个实施例中,所述第三斩波模块包括第一斩波单元和第二斩波单元;所述第一斩波单元的输入端和所述第二斩波单元的输入端均连接所述放大器的输出端,所述第一斩波单元的输出端连接所述反馈模块;

所述第一斩波单元和所述第二斩波单元还用于接入所述第三斩波信号;所述第一 斩波单元用于根据所述第三斩波信号调制所述调制放大信号得到所述第三调制信号;所述 第二斩波单元用于根据所述第三斩波信号调制所述解调放大信号得到所述输出信号。

[0008] 在其中一个实施例中,所述第一斩波信号的频率大于所述输入信号的频率。

[0009] 在其中一个实施例中,所述第二斩波信号的频率为所述第一斩波信号的频率的三倍以上。

[0010] 在其中一个实施例中,在所述第一斩波信号为高电平时,所述第三斩波信号与所述第二斩波信号相位相同;在所述第一斩波信号为低电平时,所述第三斩波信号与所述第二斩波信号相位相反。

[0011] 在其中一个实施例中,还包括采样电路,所述采样电路的输入端接入外部信号,所述采样电路的输出端连接所述第一斩波模块的输入端,所述采样电路用于对所述外部信号进行采样,并输出所述输入信号至所述第一斩波模块。

[0012] 在其中一个实施例中,所述第一斩波模块的输入端包括正极和负极,所述第一斩波单元的输出端包括正极和负极,所述反馈模块包括:第一反馈单元和第二反馈单元,所述第一反馈单元连接于所述第一斩波单元的输出端正极和所述第一斩波模块的输入端正极之间;所述第二反馈单元连接于所述第一斩波单元的输出端负极和所述第一斩波模块的输入端负极之间。

[0013] 在其中一个实施例中,所述第一反馈单元包括第一电容,所述第二反馈单元包括第二电容;所述第一电容连接于所述第一斩波单元的输出端正极和所述第一斩波模块的输入端正极之间,所述第二电容连接于所述第一斩波单元的输出端负极和所述第一斩波模块的输入端负极之间。

[0014] 一种西格玛-德尔塔调制器,包括:依次连接的积分器电路、低通滤波电路和量化器电路,所述积分器电路为如上述的积分器电路;

所述低通滤波电路用于对所述积分器电路输出的输出信号进行低通滤波处理,以 得到所述输出信号中的有用信号:

所述量化器电路用于将所述有用信号转换为多位数字信号并输出。

[0015] 一种模数转换器,包括如上述的西格玛-德尔塔调制器。

[0016] 上述积分器电路、西格玛-德尔塔调制器及模数转换器,包括依次连接的第一斩波模块、第二斩波模块、放大器、第三斩波模块以及连接于第三斩波模块和第一斩波模块之间的反馈模块。通过使第三斩波信号和第二斩波信号的频率为大于第一斩波信号频率的相同值,且相位相同的时间与相反的时间相同,由此,第一斩波模块和第二斩波模块产生的偏移尖峰(电压信号)经过放大器放大后,通过第三斩波模块的调制,接下来经过反馈模块反馈至第一斩波模块和第二斩波模块,由第一斩波模块将其进行相位调制,第二斩波模块进行

高频调制,再经过第三斩波模块进行再次调制,此时,在第三斩波信号与第二斩波信号相位相同时,脉冲上升沿与为正的偏移尖峰,得到为正的偏移尖峰;脉冲下降沿与为负的偏移尖峰,得到为正的偏移尖峰;在第三斩波信号与第二斩波信号之间有180度相移的情况下,脉冲上升沿与为负的偏移尖峰,得到为负的偏移尖峰;脉冲下降沿与为正的偏移尖峰,得到为负的偏移尖峰,从而使得为正的偏移尖峰与为负的偏移尖峰的总数相等,平均偏移值为0。由此,降低了积分器输出信号的总偏移量,进而通过后续的低通滤波处理,可以显著降低积分器输出信号的总偏移量,从而提升sigma-delta模数转换器的转换结果的准确性。

## 附图说明

[0017] 为了更清楚地说明本申请实施例或传统技术中的技术方案,下面将对实施例或传统技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

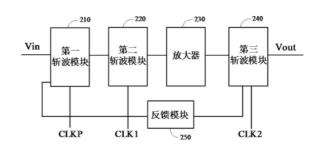

[0018] 图1为一个实施例中现有技术中的积分器的结构示意图;

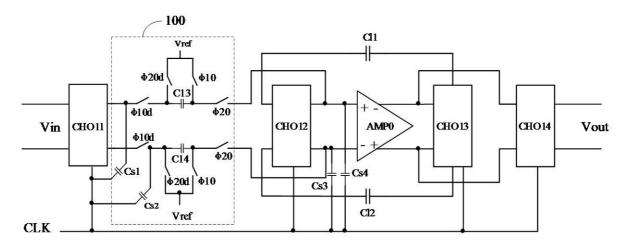

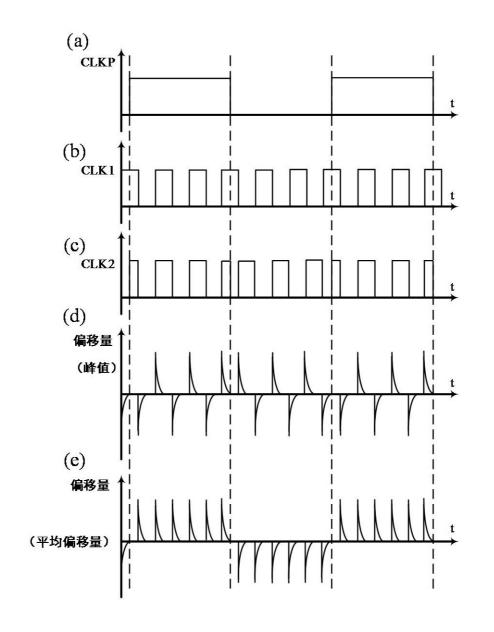

图2为图1所示实施例中的积分器的时序以及偏置的示意图;

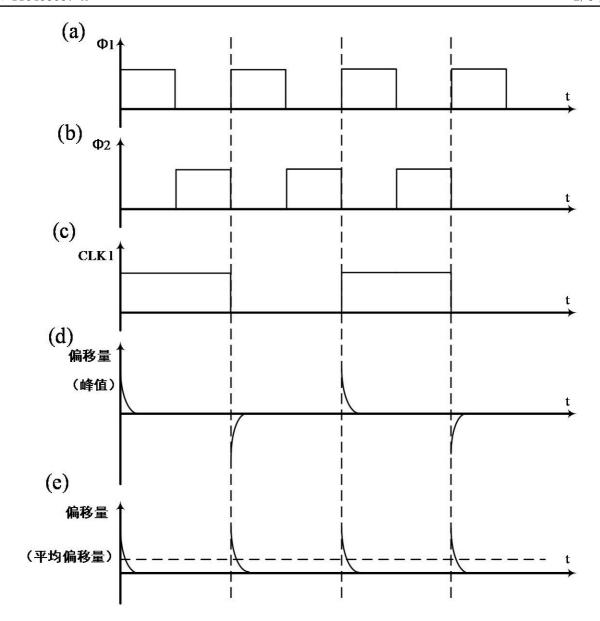

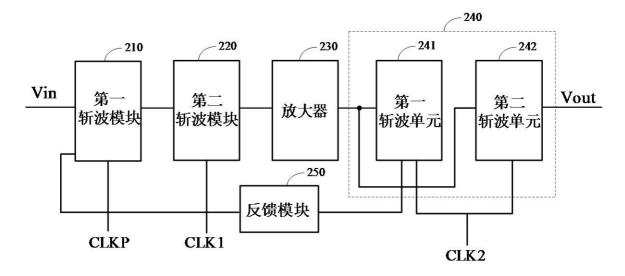

图3为一个实施例中积分器电路的模块示意图;

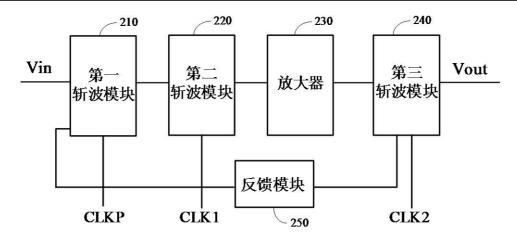

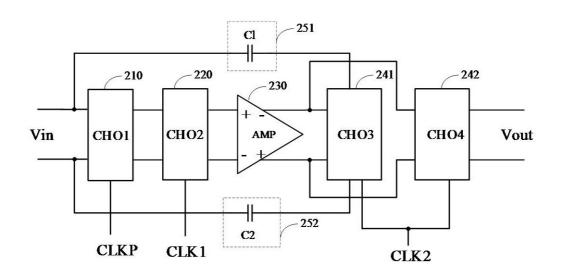

图4为一个实施例中积分器电路的时序以及偏置的示意图;

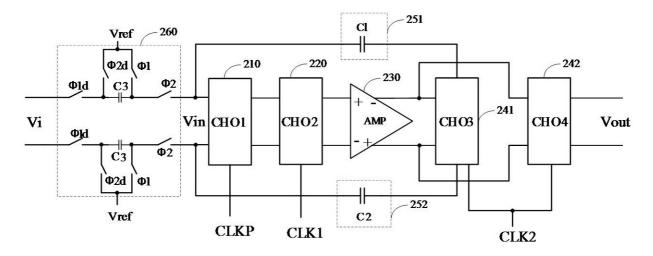

图5为另一个实施例中积分器电路的模块示意图;

图6为一个实施例中积分器电路的结构示意图:

图7为另一个实施例中积分器电路的结构示意图:

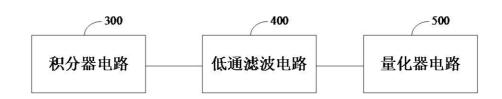

图8为一个实施例中西格玛-德尔塔调制器的结构示意图。

## 具体实施方式

[0019] 为了便于理解本申请,下面将参照相关附图对本申请进行更全面的描述。附图中给出了本申请的实施例。但是,本申请可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使本申请的公开内容更加透彻全面。

[0020] 除非另有定义,本文所使用的所有的技术和科学术语与属于本申请的技术领域的技术人员通常理解的含义相同。本文中在本申请的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本申请。

[0021] 可以理解,本申请所使用的术语"第一"、"第二"等可在本文中用于描述各种元件,但这些元件不受这些术语限制。这些术语仅用于将第一个元件与另一个元件区分。举例来说,在不脱离本申请的范围的情况下,可以将第一电阻称为第二电阻,且类似地,可将第二电阻称为第一电阻。第一电阻和第二电阻两者都是电阻,但其不是同一电阻。

[0022] 可以理解,以下实施例中的"连接",如果被连接的电路、模块、单元等相互之间具有电信号或数据的传递,则应理解为"电连接"、"通信连接"等。

[0023] 可以理解,"至少一个"是指一个或多个,"多个"是指两个或两个以上。"元件的至少部分"是指元件的部分或全部。

[0024] 在此使用时,单数形式的"一"、"一个"和"所述/该"也可以包括复数形式,除非上下文清楚指出另外的方式。还应当理解的是,术语"包括/包含"或"具有"等指定所陈述的特

征、整体、步骤、操作、组件、部分或它们的组合的存在,但是不排除存在或添加一个或更多个其他特征、整体、步骤、操作、组件、部分或它们的组合的可能性。同时,在本说明书中使用的术语"和/或"包括相关所列项目的任何及所有组合。

[0025] 正如背景技术所述,相关技术中sigma-delta模数转换器的积分器中,存在运算放大器的残余偏移量较大,增加了积分器输出信号的总偏移量,导致sigma-delta模数转换器最终的转换结果准确性不高的技术问题。如图1所示,为相关技术中的镜像积分结构的积分器,其包括斩波器CH011、采样电路100、斩波器CH012、斩波器CH013、斩波器CH014、运算放大器AMP0、反馈电容C11和反馈电容C12。输入信号Vin首先由时钟信号CLK控制的斩波器CH011进行调制,斩波信号CLK工作频率在fs/2(fs为采样频率),最后由斩波器CH014解调回基带。运算放大器AMP0的直流偏置和1/f噪声(闪烁噪声)通过斩波器CH014调制到斩波频率,以通过低通滤波器消除。

[0026] 其中,电容Cs1和电容Cs2为时钟路径和信号路径之间斩波器CH011的寄生电容,电容Cs3和电容Cs4为斩波器CH012对应的寄生电容。理想情况下,电容Cs1和电容Cs2的电容值相同,电容Cs3和电容Cs4的电容值相同。因此,输入信号在经过运算放大器AMP0后的输出没有出现差模峰值(电压),也将没有残余偏移(尖峰电压)。但由于实际工艺的因素,电容Cs1和电容Cs2的电容值、电容Cs3和电容Cs4的电容值都会存在偏差。当斩波信号CLK的时钟每次由开启到关闭的转换时刻,由于寄生电容的不匹配,斩波器CH011和斩波器CH012注入通道电荷将会不同,导致输入至运算放大器AMP0的信号的两端产生不对称,输入的信号的不对称导致运算放大器AMP0输出信号产生偏移尖峰(电压),经过斩波器CH014解调后,积分器的输出会出现无法与输入信号区分开来的残余偏置(尖峰电压)。

[0027] 如图2所示,图2为图1中的积分器的时序以及偏置的偏移值示意图,信号经过图1中的斩波器CH011、斩波器CH012,以频率为图2(c)的频率进行斩波后,产生的偏移尖峰如图2(d)所示;之后再经过同样的图2(c)的脉冲信号解调,脉冲上升沿与为正的偏移尖峰,得到为正的偏移尖峰;脉冲下降沿与为负的偏移尖峰,得到为正的偏移尖峰,从而得到图2(e)的偏移尖峰图,此时偏置的偏移值(即平均偏移值/残余偏移值)如图2(e)的虚线所示。因此,相关技术中sigma-delta模数转换器的积分器中,存在运算放大器的残余偏移量较大的现象。

[0028] 基于上述技术问题,发明人研究发现,通过对图1中斩波器CH011和斩波器CH012的各自寄生电容Cs1和Cs2、Cs3和Cs4所引起的偏移量进行抑制,可以有效抑制运算放大器的残余偏移量,进而使得sigma-delta模数转换器最终的转换结果准确性更高。基于此,发明人进一步研究出本发明实施例的技术方案。具体地,本发明实施例提供一种积分器电路,包括:第一斩波模块,用于接入输入信号和第一斩波信号,并根据第一斩波信号调制输入信号得到第一调制信号;第二斩波模块,连接第一斩波模块的输出端,还用于接入第二斩波信号,并根据第二斩波信号的频率为第一斩波信号的频率的预设倍数,预设倍数为大于1倍的整数倍;放大器,连接第二斩波模块的输出端,用于对第二调制信号进行放大,得到调制放大信号;第三斩波模块,连接放大器的输出端,还用于接入第三斩波信号,并根据第三斩波信号调制调制放大信号得到第三调制信号;第三斩波信号的频率与第二斩波信号的频率相同,且第三斩波信号与第二斩波信号相位相同的时间与相位相反的时间相等;反馈模块,连接于第三斩波模块的输出端和第

一斩波模块的输入端之间,用于将第三调制信号反馈至第一斩波模块,以使第一斩波模块、第二斩波模块和放大器对第三调制信号进行解调放大处理,得到解调放大信号;第三斩波模块,还用于根据第三斩波信号对解调放大信号进行调制得到输出信号,输出信号包括有用信号,有用信号为输入信号经过调制、解调和放大处理后的信号。

[0029] 采用上述技术方案,通过使第三斩波信号和第二斩波信号的频率为大于第一斩波信号频率的相同值,且相位相同的时间与相反的时间相同,由此,第一斩波模块和第二斩波模块产生的偏移尖峰(电压信号)经过放大器放大后,通过第三斩波模块的调制,接下来经过反馈模块反馈至第一斩波模块和第二斩波模块,由第一斩波模块将其进行相位调制,第二斩波模块进行高频调制,再经过第三斩波模块进行再次调制,此时,在第三斩波信号CLK2与第二斩波信号CLK2与第二斩波信号CLK1和位相同时,脉冲上升沿与为正的偏移尖峰,得到为正的偏移尖峰;脉冲下降沿与为负的偏移尖峰,得到为正的偏移尖峰;在第三斩波信号CLK2与第二斩波信号CLK1之间有180度相移的情况下,脉冲上升沿与为负的偏移尖峰,得到为负的偏移尖峰,持到为负的偏移尖峰,协冲下降沿与为正的偏移尖峰,得到为负的偏移尖峰,从而使得为正的偏移尖峰与为负的偏移尖峰的总数相等,平均偏移值为0。由此,降低了积分器输出信号的总偏移量,进而通过后续的低通滤波处理,可以显著降低积分器输出信号的总偏移量,从而提升sigma-delta模数转换器的转换结果的准确性。

[0030] 以上是本发明的核心思想,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下,所获得的所有其他实施例,都属于本发明保护的范围。

[0031] 图3为本发明实施例提供的一种积分器电路的结构示意图,如图3所示,本发明实施例提供的积分器电路包括:第一斩波模块210、第二斩波模块220、放大器230、第三斩波模块240和反馈模块250。

[0032] 第一斩波模块210用于接入输入信号Vin和第一斩波信号CLKP,并根据第一斩波信号CLKP调制输入信号Vin得到第一调制信号。第二斩波模块220连接第一斩波模块210的输出端,第二斩波模块220还用于接入第二斩波信号CLK1,并根据第二斩波信号CLK1调制第一调制信号得到第二调制信号;第二斩波信号CLK1的频率为第一斩波信号CLKP的频率的预设倍数,预设倍数为大于1倍的整数倍。

[0033] 放大器230连接第二斩波模块220的输出端,用于对第二调制信号进行放大,得到调制放大信号。第三斩波模块240连接放大器230的输出端,第三斩波模块240还用于接入第三斩波信号CLK2,并根据第三斩波信号CLK2对调制放大信号进行调制,得到第三调制信号。第三斩波信号CLK2的频率与第二斩波信号CLK1的频率相同,且第三斩波信号CLK2与第二斩波信号CLK1相位相同的时间与相位相反的时间相等。

[0034] 反馈模块250连接于第三斩波模块240的输出端和第一斩波模块210的输入端之间,用于将第三调制信号反馈至第一斩波模块210,以使第一斩波模块210、第二斩波模块220和放大器230对第三调制信号进行解调放大处理,得到解调放大信号。第三斩波模块240还用于根据第三斩波信号CLK2对解调放大信号进行再次调制得到输出信号Vout,输出信号Vout包括有用信号,有用信号为输入信号Vin经过调制、解调和放大处理后的信号。

[0035] 其中,输入信号Vin为模拟信号,具体信号类型不需要限定。在实际实施时,第一斩波信号CLKP、第二斩波信号CLK1和第三斩波信号CLK2可以为高低电平交替变化的脉冲信

号,第一斩波信号CLKP、第二斩波信号CLK1和第三斩波信号CLK2的频率可以根据实际情况设置。

[0036] 优选地,第一斩波模块210采用低频调制,第一斩波信号CLKP的时钟频率可以远低于图1所示实施例中的斩波信号CLK的频率,在一个实施例中,第一斩波信号CLKP的频率大于输入信号Vin的频率,在设置第一斩波信号CLKP的频率时,只需要使其大于输入信号Vin的最高频率即可,示例性地,第一斩波信号CLKP的频率为输入信号Vin的频率的两倍以上。可以理解,通过采用时钟频率更低的第一斩波信号CLKP也可以降低第一斩波模块210自身的偏置值。

[0037] 进一步地,第二斩波模块220可以采用高频调制,具体地,第二斩波信号CLK1的频率至少为第一斩波信号CLKP的频率1倍以上,在实际实施时,第二斩波信号CLK1的频率在放大器230允许的范围内越高越好,因为最后的输出信号Vout要经过低通滤波处理才能得到有用信号,第二斩波信号CLK1的频率越高,低通滤波时的滤波效果越好,且截止频率要求比较窄,低通滤波器也越易于实现。在一个实施例中,第二斩波信号CLK1的频率为第一斩波信号CLKP的频率的三倍以上,如第二斩波信号CLK1的频率为第一斩波信号CLKP的频率的三倍、第二斩波信号CLKP的频率为第一斩波信号CLKP的频率的五倍等。

[0038] 第三斩波模块240也为高频调制,其接入的第三斩波信号CLK2的频率与第二斩波信号CLK1的频率相同,第三斩波信号CLK2与第二斩波信号CLK1相位相同的时间与相位相反的时间相等,在一个实施例中,可以是在第一斩波信号CLKP为高电平时,第三斩波信号CLK2与第二斩波信号CLK1相位相反;在第一斩波信号CLKP为低电平时,第三斩波信号CLK2与第二斩波信号CLK1相位相同。在另一个实施例中,还可以是在第一斩波信号CLKP为高电平时,第三斩波信号CLK2与第二斩波信号CLK1相位相同;在第一斩波信号CLKP为低电平时,第三斩波信号CLK2与第二斩波信号CLK1相位相反。在实际实施时,本领域技术人员可以结合实际情况灵活设置,只要使得第三斩波信号CLK2与第二斩波信号CLK1相位相同的时间与相位相反的时间相等即可。

[0039] 下述结合图3-图4对本实施例的原理进行说明,以第二斩波信号CLK1的频率为第一斩波信号CLKP的频率的三倍为例,假设当第一斩波信号CLKP处于高电平时,第三斩波信号CLK2的时序与第二斩波信号CLK1的时序相同,而当第一斩波信号CLKP处于低电平时,第三斩波信号CLK2与第二斩波信号CLK1之间有180度的相移。

[0040] 本实施例中,当前输入信号Vin首先由第一斩波模块210进行低频调制,实现对信号的相位调制,得到低频的第一调制信号;再由第二斩波模块220调制为高频的第二调制信号,之后经放大器230进行放大,放大器230为运算放大器,其放大后输出的调制放大信号包括:输入信号Vin经过第一斩波模块210、第二斩波模块220两次调制和放大器230放大后得到的信号,为了便于描述,假设该信号为"第一过程信号"。

[0041] 调制放大信号再经过第三斩波模块240高频调制得到第三调制信号,可以理解,第三调制信号包括:"第一过程信号"再次经过第三斩波模块240的调制得到的"第二过程信号"(第二过程信号为,输入信号Vin经过第一斩波模块210、第二斩波模块220两次调制、放大器230放大和第三斩波模块240调制后得到的信号)。

[0042] 第三调制信号经反馈模块250反馈至第一斩波模块210的输入端,从而由第一斩波模块210、第二斩波模块220对"第二过程信号"进行解调,之后放大器230进行二次放大,使

其幅值增大,接下来第三斩波模块240再次进行解调,得到输出信号Vout,此时输出信号Vout中的有用信号,即输入信号Vin经过第一斩波模块210、第二斩波模块220两次调制、放大器230放大、第三斩波模块240调制后、再次经过第一斩波模块210、第二斩波模块220两次解调、放大器230放大、第三斩波模块240解调后的信号,该有用信号的频率已经解调回输入信号Vin的原频率,幅值为输入信号Vin经过两次放大后的幅值。

[0043] 在上述处理过程中,输入到放大器230的第二调制信号包括输入信号Vin经高频调制后的信号和前端斩波模块的噪声信号(包括偏移尖峰电压)等信号,各信号都会被放大,但是输入信号Vin经过处理后会解调回原频率,只是幅值被放大,噪声中的偏移尖峰经过处理后平均偏移量已经为0,而噪声中的其他信号被调制成了高频,所以再经过后续的低通滤波时,可以仅保留有用信号,使得最后的模数转换结果更为精确可靠。

关于偏移尖峰,本实施例中,通过使第三斩波信号CLK2与第二斩波信号CLK1的频 率相同,相位设置为随第一斩波信号CLKP的电压状态变化,这样输入信号Vin经过第二斩波 模块220后,第二斩波模块220产生的偏移尖峰经放大后被反馈至第一斩波模块210和第二 斩波模块220,虽然被第二斩波模块220调制到高频,但是也被频率较低的第一斩波信号 CLKP的频率所调制,得到图4(d)的偏移尖峰图。由于偏置的大小与偏移尖峰数量成正比,所 以需要使第三斩波信号CLK2与第二斩波信号CLK1相位相同的时间和相位相反的时间相同, 以在第三斩波信号CLK2与第二斩波信号CLK1之间有180度相移的情况下,能够使得第二斩 波模块220产生的偏移尖峰的频率与斩波信号有所区分。此时信号再次经过图4(b)的脉冲 信号解调,在第三斩波信号CLK2与第二斩波信号CLK1相位相同时,脉冲上升沿与为正的偏 移尖峰,得到为正的偏移尖峰;脉冲下降沿与为负的偏移尖峰,得到为正的偏移尖峰;在第 三斩波信号CLK2与第二斩波信号CLK1之间有180度相移的情况下,脉冲上升沿与为负的偏 移尖峰,得到为负的偏移尖峰;脉冲下降沿与为正的偏移尖峰,得到为负的偏移尖峰;从而 得到图4(e)的偏移尖峰图,可见,此时的偏置平均值为0。因此由斩波模块产生的高频峰值 偏移被调制到频率较低的CLKP的频率上,虽然该频低于第三斩波信号CLK2与第二斩波信号 CLK1频率,但仍高于输入信号Vin的频率,后续通过低通滤波器后,该积分器电路输出处的 平均残留偏移将为零。

[0045] 上述积分器电路,包括依次连接的第一斩波模块210、第二斩波模块220、放大器230、第三斩波模块240以及连接于第三斩波模块240的输出端和第一斩波模块210的输入端之间的反馈模块250。通过使第三斩波信号CLK2和第二斩波信号CLK1的频率为大于第一斩波信号CLKP频率的相同值,且相位相同的时间与相反的时间相同,由此,第一斩波模块210和第二斩波模块220产生的偏移尖峰(电压信号)经过放大器230放大后,通过第三斩波模块240的调制,接下来经过反馈模块250反馈至第一斩波模块210和第二斩波模块220,由第一斩波模块210将其进行相位调制,第二斩波模块220进行高频调制,再经过第三斩波模块240进行再次调制,此时,在第三斩波信号CLK2与第二斩波信号CLK1相位相同时,脉冲上升沿与为正的偏移尖峰,得到为正的偏移尖峰;脉冲下降沿与为负的偏移尖峰,得到为正的偏移尖峰。在第三斩波信号CLK2与第二斩波信号CLK1之间有180度相移的情况下,脉冲上升沿与为的偏移尖峰,得到为负的偏移尖峰;脉冲下降沿与为正的偏移尖峰,得到为负的偏移尖峰,从而使得为正的偏移尖峰与为负的偏移尖峰的总数相等,平均偏移值为0。由此,降低了积分器输出信号的总偏移量,进而提升sigma-delta模数转换器的转换结果的准确性。

[0046] 在一个实施例中,如图5所示,第三斩波模块240包括第一斩波单元241和第二斩波单元242。第一斩波单元241的输入端和第二斩波单元242的输入端均连接放大器230的输出端,第一斩波单元241的输出端连接反馈模块250。

[0047] 第一斩波单元241和第二斩波单元242还用于接入第三斩波信号CLK2;第一斩波单元241用于根据第三斩波信号CLK2调制调制放大信号得到第三调制信号;第二斩波单元242用于根据第三斩波信号CLK2调制解调放大信号得到输出信号Vout。

[0048] 第一斩波单元241、第二斩波单元242、第一斩波模块210和第二斩波模块220的结构可以根据实际需要设置,例如,均为斩波器。具体地,请参照图6,第一斩波模块210包括第一斩波器CH01,第二斩波模块220包括第二斩波器CH02,第一斩波单元241包括第三斩波器CH03,第二斩波单元242包括第四斩波器CH04,放大器230包括运算放大器AMP,第一斩波器CH01、第二斩波器CH02、第三斩波器CH03和第四斩波器CH04的结构可以相同。

[0049] 在实际实施时,第一斩波器CH01的输入端正极和输入端负极用于接入输入信号 Vin,第一斩波器CH01的输出端正极连接第二斩波器CH02的输入端正极,第一斩波器CH01的输出端负极连接第二斩波器CH02的输入端负极,第一斩波器CH01的控制端接入第一斩波信号CLKP;第二斩波器CH02的输出端正极连接运算放大器AMP的同相输入端,第二斩波器CH02的输出端负极连接运算放大器AMP的反相输入端;运算放大器AMP的反相输出端连接第三斩波器CH03的输入端正极和第四斩波器CH04的输入端正极,运算放大器AMP的同相输出端连接第三斩波器CH03的输入端负极和第四斩波器CH04的输入端负极。其中,第三斩波器CH03的输出端正极和第三斩波器CH03的输出端负极还连接反馈模块250。

[0050] 需要说明的是,虽然第三斩波器CH03和第四斩波器CH04也会产生寄生电容,但第三斩波器CH03对应的尖峰产生的残留偏移,会随着反馈回路回到运算放大器AMP0的前端,并不直接传向输出端,由于运算放大器AMP的开环增益,第三斩波器CH03带来的误差都被前面的增益所抑制,因此电荷注入误差显著降低;而第四斩波器CH04的不匹配寄生电容产生的尖峰处于第三斩波信号CLK2频段,此时的信号经过再次斩波,信号调制回基带,从而通过后续的低通滤波可以滤除掉第四斩波器CH04的尖峰。因此,第三斩波器CH03和第四斩波器CH04引起的残留偏移可以忽略。

[0051] 在一个实施例中,第一斩波模块210的输入端包括正极和负极,第一斩波单元241的输出端包括正极和负极,反馈模块250包括第一反馈单元251和第二反馈单元252,第一反馈单元251连接于第一斩波单元241的输出端正极和第一斩波模块210的输入端正极之间;第二反馈单元252连接于第一斩波单元241的输出端负极和第一斩波模块210的输入端负极之间。

[0052] 具体地,第一反馈单元251可以包括第一电容C1,第二反馈单元252可以包括第二电容C2;第一电容C1连接于第一斩波单元241的输出端正极和第一斩波模块210的输入端正极之间,第二电容C2连接于第一斩波单元241的输出端负极和第一斩波模块210的输入端负极之间。

[0053] 仍以图6所示实施例进行说明,第一电容C1连接于第三斩波器CH03的输出端正极和第一斩波器CH01的输入端正极之间,第二电容C2连接于第三斩波器CH03的输出端负极和第一斩波器CH01的输入端负极之间,从而通过第一电容C1和第二电容C2实现反馈。

[0054] 进一步地,在一些实施例中,该积分器电路还包括采样电路260,采样电路260的输

入端接入外部信号Vi,采样电路260的输出端连接第一斩波模块210的输入端,采样电路260用于对外部信号Vi进行采样,并输出输入信号Vin至第一斩波模块210。

[0055] 采样电路260的具体结构可以根据实际需要设置,例如包括两个开关采样单元,两个开关采样单元分别设置于第一斩波器CH01的输入端正极和第一斩波器CH01的输入端负极,每个开关采样单元均包括开关 $\phi$ 1、开关 $\phi$ 2、开关 $\phi$ 1d、开关 $\phi$ 2d及电容C3,开关 $\phi$ 1d的第一端用于接入外部信号Vi,开关 $\phi$ 1d的第二端经电容C3连接开关 $\phi$ 2的第一端,开关 $\phi$ 2的第二端连接第一斩波器CH01的输入端。开关 $\phi$ 2d的第一端连接电容C3的一端,开关 $\phi$ 1的第一端连接电容C3的另一端,开关 $\phi$ 2d的第二端与开关 $\phi$ 1的第二端用于接入外部输入的参考电压信号Vref。其中,开关 $\phi$ 1、开关 $\phi$ 2、开关 $\phi$ 1d、开关 $\phi$ 2d均受控于外部电路,具体控制方式无需进行限定,本领域技术人员可以参考本领域常用技术进行设置。

[0056] 上述积分器电路,可以通过斩波去除低频的1/f噪声和失调电压的同时,通过调整电路结构及各斩波信号的频率和相位,能够进一步降低输出处斩波带来的平均残余偏置,从而提升整个系统的信噪比。

[0057] 在一个实施例中,如图8所示,提供了一种西格玛-德尔塔调制器,包括:依次连接的积分器电路300、低通滤波电路400和量化器电路500。积分器电路300可以参照上述各实施例的积分器电路进行设置,低通滤波电路400用于对积分器电路300输出的输出信号进行低通滤波处理,以得到输出信号中的有用信号;量化器电路500用于将有用信号转换为多位数字信号并输出。

[0058] 在实际实施时,西格玛-德尔塔调制器的结构还可以根据实际需要进行调整,例如还包括数模转换器等,本领域技术人员可以参考本领域常用技术进行设置,本实施例对此不进行赘述。

[0059] 在一个实施例中,提供了一种模数转换器,包括西格玛-德尔塔调制器,西格玛-德尔塔调制器的结构可以参照上述实施例的Sigma-delta调制器设置。

[0060] 在本说明书的描述中,参考术语"有些实施例"、"其他实施例"等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特征包含于本申请的至少一个实施例或示例中。在本说明书中,对上述术语的示意性描述不一定指的是相同的实施例或示例。

[0061] 以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0062] 以上所述实施例仅表达了本申请的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本申请范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本申请构思的前提下,还可以做出若干变形和改进,这些都属于本申请的保护范围。因此,本申请的保护范围应以所附权利要求为准。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8