#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

### (19) World Intellectual Property **Organization**

International Bureau

#

(10) International Publication Number WO 2017/218898 A2

- (51) International Patent Classification: A61B 6/00 (2006.01)

- (21) International Application Number:

PCT/US2017/037882

(22) International Filing Date:

16 June 2017 (16.06.2017)

(25) Filing Language:

**English**

(26) Publication Language:

English

(30) Priority Data:

62/351,171

16 June 2016 (16.06.2016)

- (71) Applicant: ARIZONA BOARD OF REGENTS ON BE-HALF OF ARIZONA STATE UNIVERSITY [US/US]; 1475 North Scottsdale Road, Sky Song - Suite 200, Scottsdale, Arizona 85257 (US).

- (72) Inventors: HENDERSON, Xan; 1016 North 113th Place, Mesa, Arizona 85207 (US). MARRS, Michael; 4525 East Grandview Road, Phoenix, Arizona 85032 (US).

- (74) Agent: BENYI, Stephen; Bryan Cave, LLP, Two North Central Avenue, Suite 2100, Phoenix, Arizona 85004 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO,

DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### Published:

without international search report and to be republished upon receipt of that report (Rule 48.2(g))

#### (54) Title: ELECTRONIC DEVICES AND RELATED METHODS

FIG. 43

(57) Abstract: Some embodiments include an electronic device. The electronic device includes a first scintillator layer, a transistor, and one or more device elements over the transistor, and the one or more device elements include a photodetector. Meanwhile, the first scintillator layer is monolithically integrated with at least one of the transistor or the one or more device elements. Other embodiments of related systems, devices, and methods are also disclosed.

## ELECTRONIC DEVICES AND RELATED METHODS

# STATEMENT REGARDING FEDERALLY SPONSORED RESEARCH OR DEVELOPMENT

[0001] This invention was made with government support under W911NF-04-2-0005 awarded by the Army Research Office. The government has certain rights in the invention.

#### CROSS-REFERENCE TO RELATED APPLICATIONS

[0002] This application claims the benefit of United States Provisional Patent Application No. 62/351,171, filed June 16, 2016. United States Provisional Patent Application No. 62/351,171 is incorporated herein by reference in its entirety.

#### FIELD OF THE INVENTION

[0003] This invention relates generally to electronic devices, and relates more particularly to electronic devices having one or more processed and/or integrated scintillator layers and methods of manufacturing the same.

#### DESCRIPTION OF THE BACKGROUND

[0004] An increasing demand exists for imaging systems (e.g., radiography systems). For example, as the average age of the world's population increases, the need for medical imaging systems is expected to rise dramatically. Meanwhile, imaging systems are also increasingly being used in non-medical applications, such as, for example, for security applications (e.g., transportation security) and/or engineering applications. In an exemplary engineering application, imaging systems may be used to conduct non-destructive testing for integrity analysis of a structure (e.g., a pipe, an airframe, an airfoil, etc.) in order to identify micro-cracks and crack initiation in the structure.

[0005] Conventional imaging systems, which may be based on rigid substrates, may be unsuitable for performing imaging (i) in remote locations, such as, for example, in less developed countries, and/or (ii) in restricted (e.g., confined) spaces. For example, conventional imaging systems may be insufficiently portable (e.g., by size, volume, and/or weight), flexible, and/or durable to perform imaging under such circumstances. Nonetheless, medical personnel (e.g., first responders), military personnel, security personnel, etc. may find it desirable and/or advantageous to perform imaging under these circumstances.

[0006] Accordingly, a need or potential for benefit exists for portable, flexible, and/or durable imaging systems and methods of manufacturing the same.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0007] To facilitate further description of the embodiments, the following drawings are provided in which:

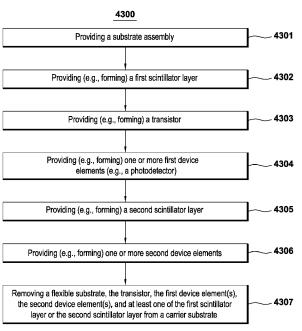

- [0008] FIG. 1 illustrates an example of a method of providing a semiconductor device, according to an embodiment;

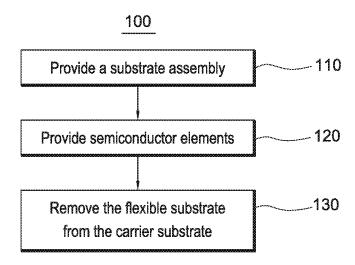

- [0009] FIG. 2 illustrates an example is an activity of providing a substrate assembly, according to the embodiment of FIG. 1;

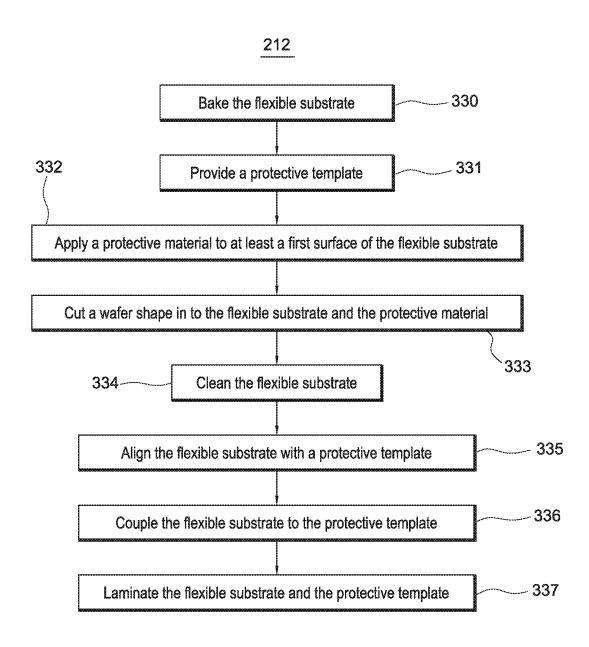

- [0010] FIG. 3 illustrates an example of an activity of preparing a flexible substrate, according to the embodiment of FIG. 1;

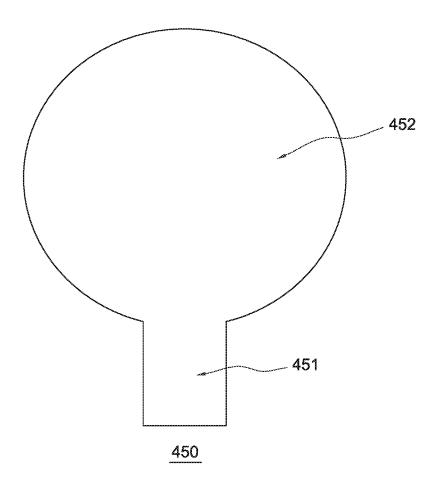

- [0011] FIG. 4 illustrates a top view of an example of the flexible substrate of FIG. 3, according to the embodiment of FIG. 1;

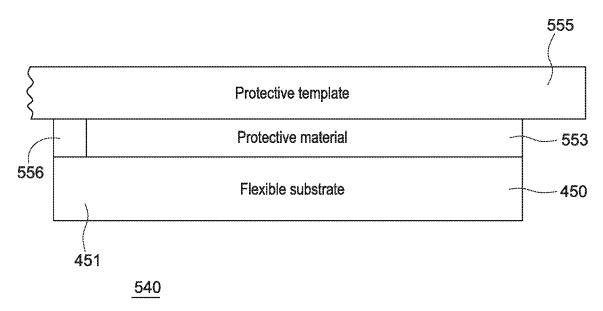

- [0012] FIG. 5 illustrates a partial cross-sectional view of an example of the substrate assembly of FIG. 2 after attaching the flexible substrate of FIG. 3 to a protective template, according to the embodiment of FIG. 1;

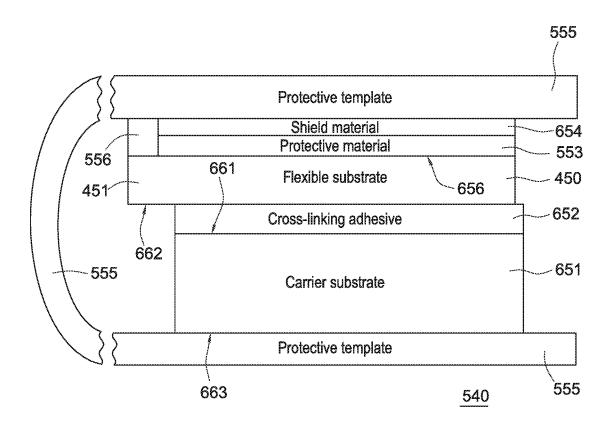

- [0013] FIG. 6 illustrates a partial cross-sectional view of an example of the substrate assembly of FIG. 2 after coupling a carrier substrate to the flexible substrate, according to the embodiment of FIG. 1;

- [0014] FIG. 7 illustrates an example of an activity of processing the substrate assembly of FIG. 2, according to the embodiment of FIG. 1;

- [0015] FIG. 8 illustrates a cross-sectional view of an example of the substrate assembly of FIG. 2 after cutting the substrate assembly and removing the protective template of FIG. 5, according to the embodiment of FIG. 1;

- [0016] FIG. 9 illustrates a cross-sectional view of an example of the substrate assembly of FIG. 2 after removing an alignment tab, according to the embodiment of FIG. 1;

- [0017] FIG. 10 illustrates a cross-sectional view of an example of the substrate assembly of FIG. 2 after removing a protective material from the substrate assembly, according to the embodiment of FIG. 1;

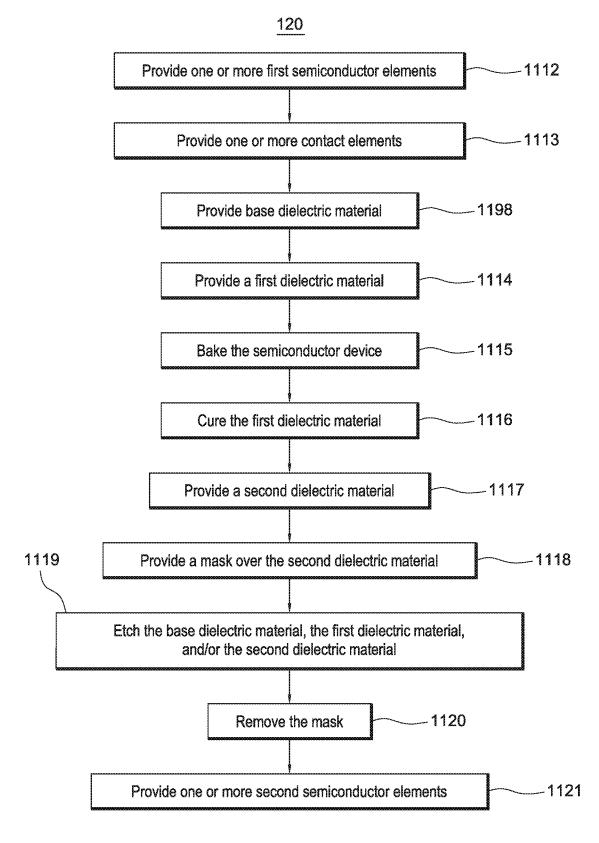

- [0018] FIG. 11 illustrates an example of an activity of providing semiconductor elements, according to the embodiment of FIG. 1;

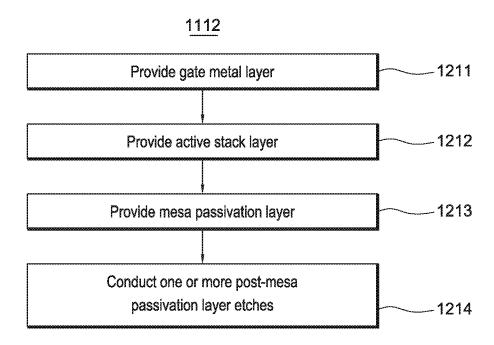

- [0019] FIG. 12 illustrates an example of an activity of providing one or more first semiconductor elements, according to the embodiment of FIG. 1;

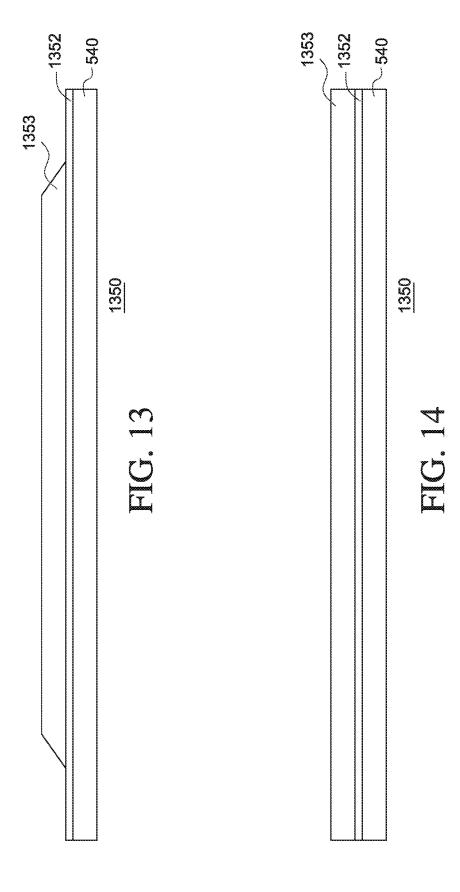

- [0020] FIG. 13 illustrates a cross-sectional view of an example of a device build area of an example of a semiconductor device after providing a gate metal layer, according to the embodiment of FIG. 1;

[0021] FIG. 14 illustrates a cross-sectional view of an example of a gate contact build area of an example of the semiconductor device of FIG. 13 after providing the gate metal layer, according to the embodiment of FIG. 1;

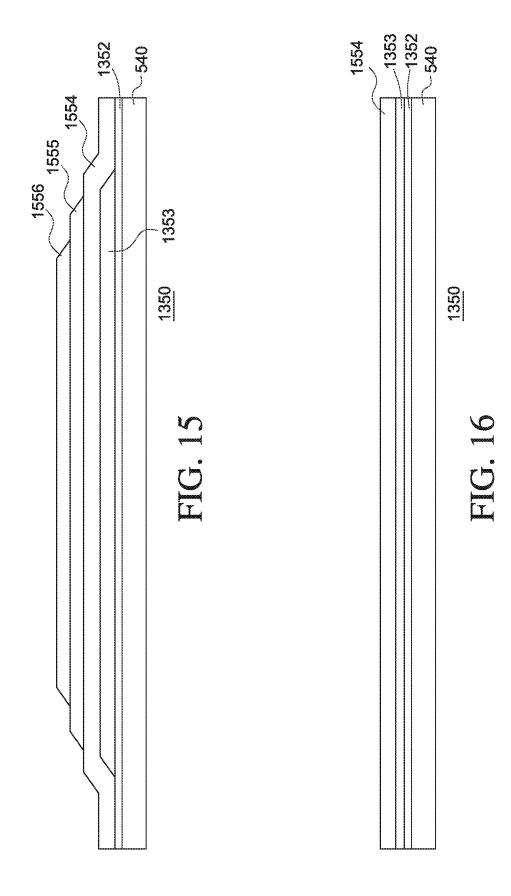

- [0022] FIG. 15 illustrates a cross-sectional view of an example of the device build area of the semiconductor device of FIG. 13 after providing an active stack layer, according to the embodiment of FIG. 1;

- [0023] FIG. 16 illustrates a cross-sectional view of an example of the gate contact build area of the semiconductor device of FIG. 14 after providing the active stack layer, according to the embodiment of FIG. 1;

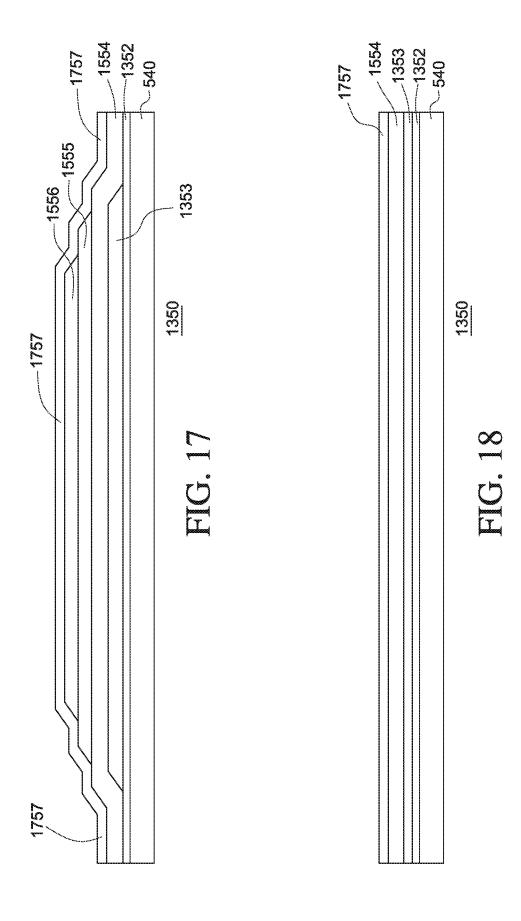

- [0024] FIG. 17 illustrates a cross-sectional view of an example of the device build area of the semiconductor device of FIG. 13 after providing a mesa passivation layer, according to the embodiment of FIG. 1;

- [0025] FIG. 18 illustrates a cross-sectional view of an example of the gate contact build area of the semiconductor device of FIG. 14 after providing the mesa passivation layer, according to the embodiment of FIG. 1;

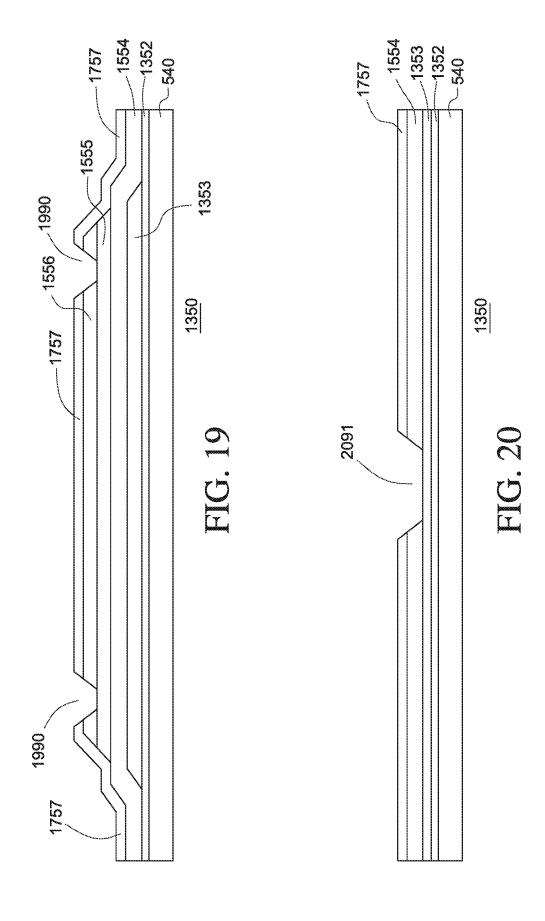

- [0026] FIG. 19 illustrates a cross-sectional view of an example of the device build area of the semiconductor device of FIG. 13 after conducting one or more post-mesa passivation layer etches, according to the embodiment of FIG. 1;

- [0027] FIG. 20 illustrates a cross-sectional view of an example of the gate contact build area of the semiconductor device of FIG. 14 after conducting one or more post-mesa passivation layer etches, according to the embodiment of FIG. 1;

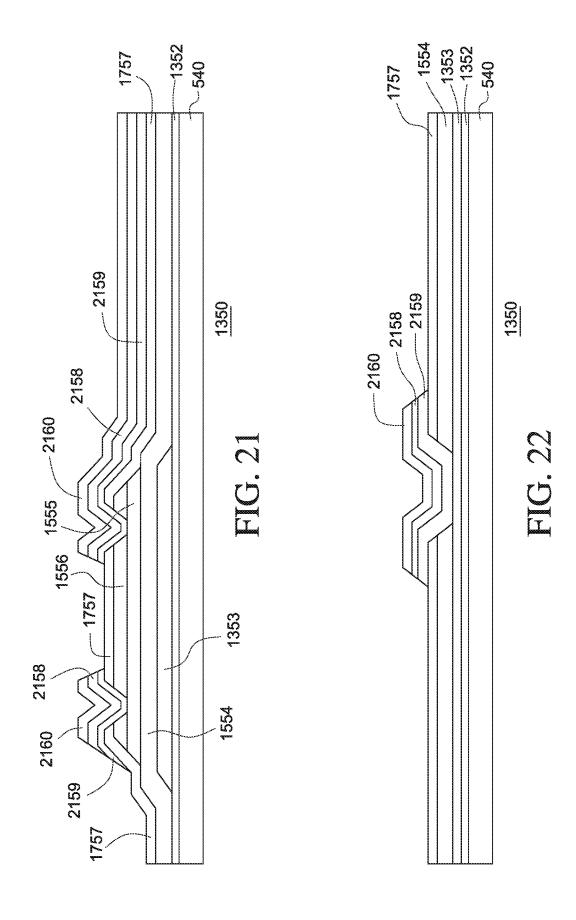

- [0028] FIG. 21 illustrates a cross-sectional view of an example of the device build area of the semiconductor device of FIG. 13 after providing one or more contact elements, according to the embodiment of FIG. 1;

- [0029] FIG. 22 illustrates a cross-sectional view of an example of the gate contact build area of the semiconductor device of FIG. 14 after providing one or more contact elements, according to the embodiment of FIG. 1;

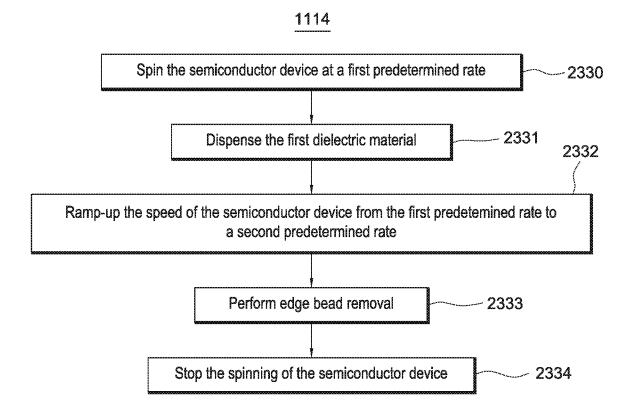

- [0030] FIG. 23 illustrates an example of an activity of providing a first dielectric material, according to the embodiment of FIG. 1;

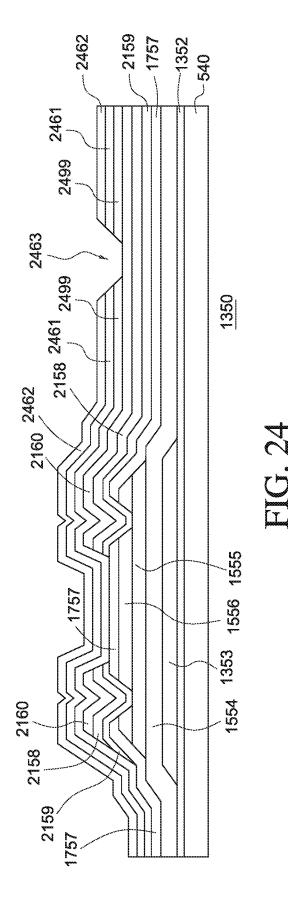

- [0031] FIG. 24 illustrates a cross-sectional view of an example of the device build area of the semiconductor device of FIG. 13 after etching a base dielectric material, a first dielectric material, and a second dielectric material, according to the embodiment of FIG. 1;

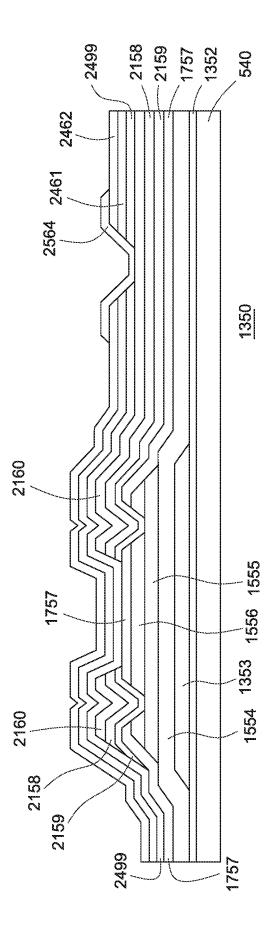

[0032] FIG. 25 illustrates a cross-sectional view of an example of the device build area of the example of the semiconductor device of FIG. 13 after providing an N-type layer, according to the embodiment of FIG. 1;

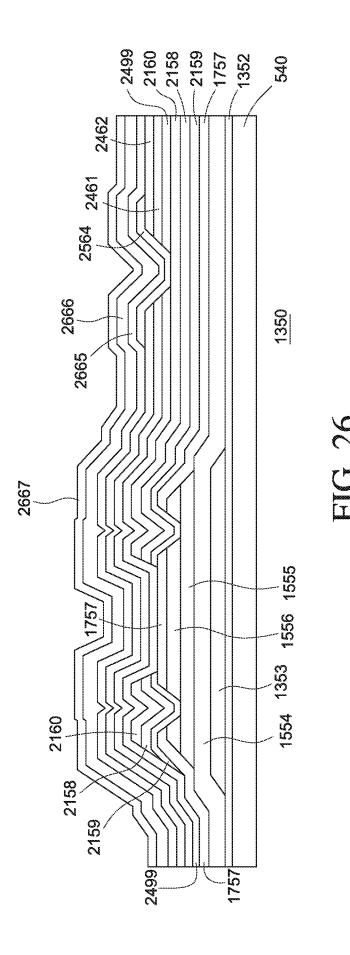

- [0033] FIG. 26 illustrates a cross-sectional view of an example of the device build area of the example of the semiconductor device of FIG. 13 after providing an intrinsic layer, a P-type layer, and an ITO layer, according to the embodiment of FIG. 1;

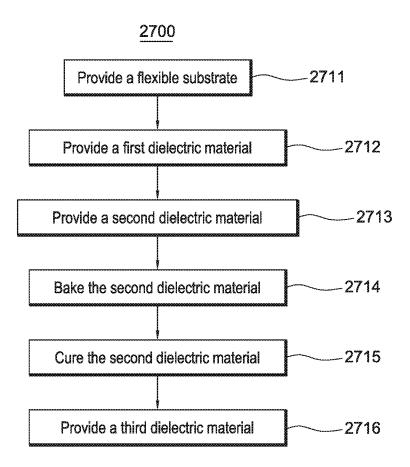

- [0034] FIG. 27 illustrates an example of a method of planarizing a flexible substrate, according to another embodiment;

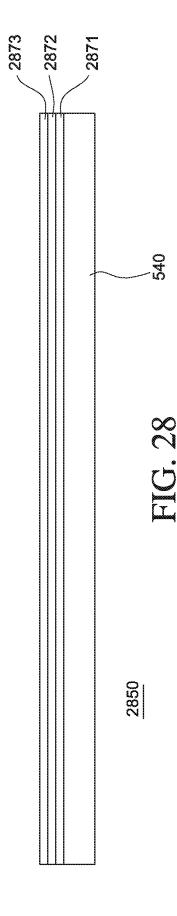

- [0035] FIG. 28 illustrates a cross-sectional view of an example of a semiconductor device according to the method of FIG. 27, according to the embodiment of FIG. 27;

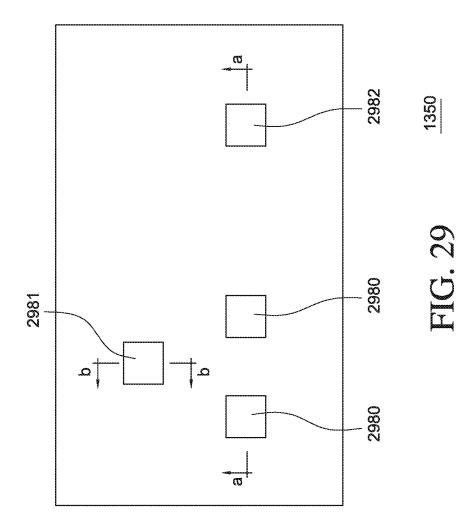

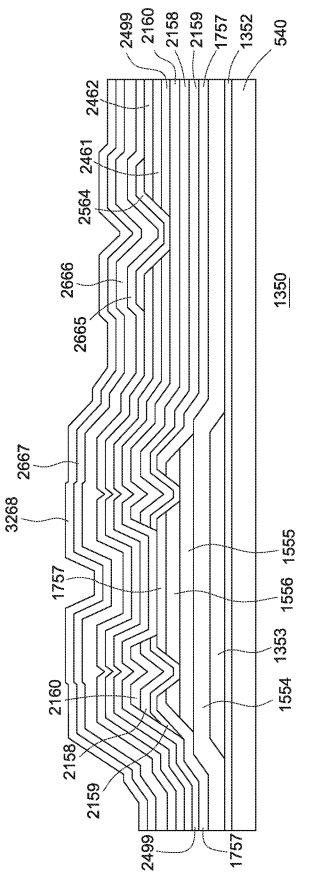

- [0036] FIG. 29 illustrates a top view of portions of the semiconductor device represented in FIGs. 13 and 14, according to the embodiment of FIG. 1;

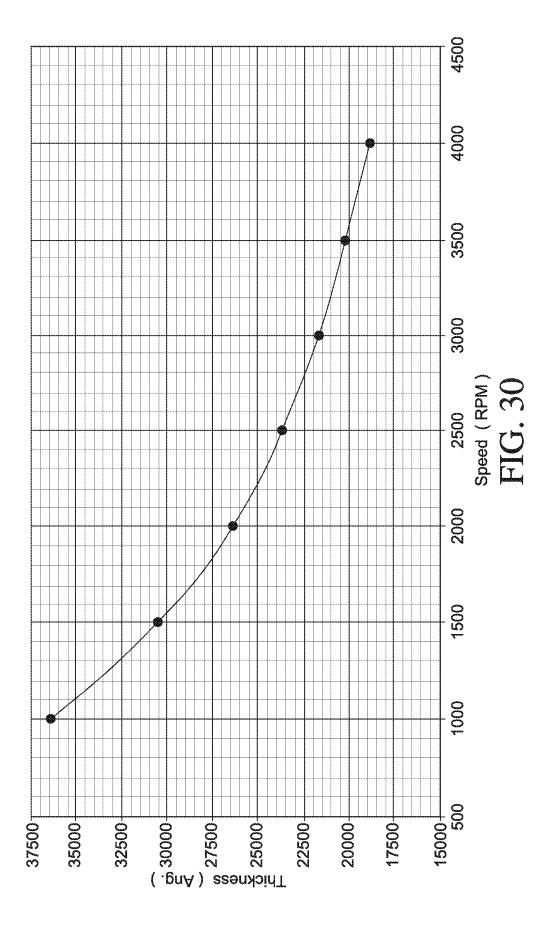

- [0037] FIG. 30 illustrates a graph of thickness of a dielectric material versus spin rate of a substrate;

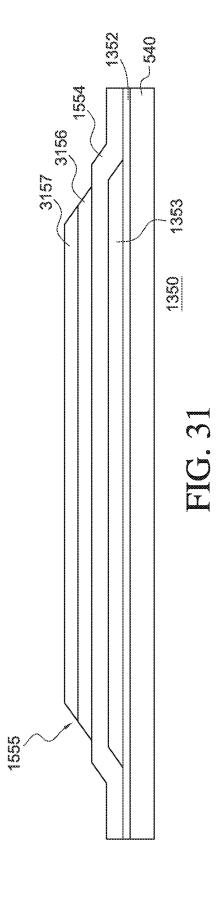

- [0038] FIG. 31 illustrates a patterned active layer when the patterned active layer comprises multiple constituent active layers, according the embodiment of FIG. 1;

- [0039] FIG. 32 illustrates a cross-sectional view of an example of the device build area of the example of the semiconductor device of FIG. 13 after providing a silicon nitride layer, according the embodiment of FIG. 1;

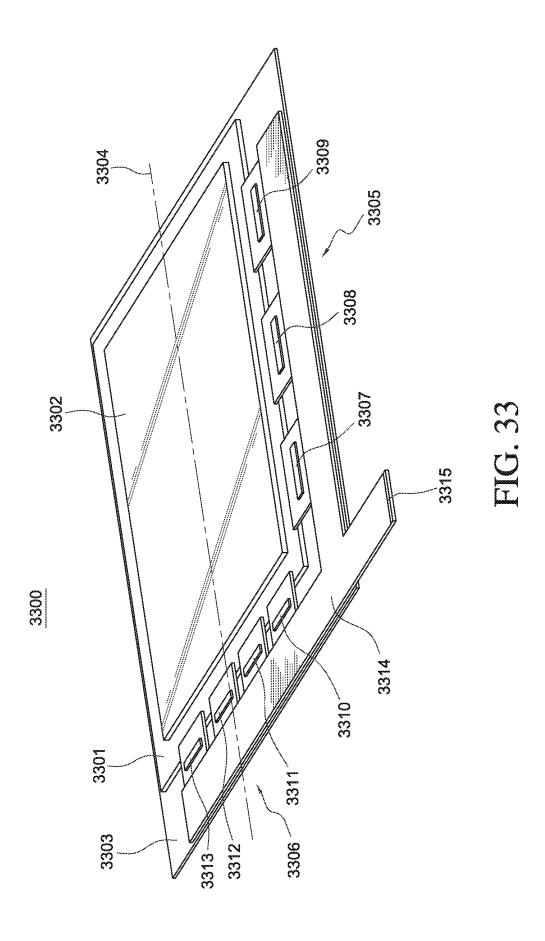

- [0040] FIG. 33 illustrates an exemplary imaging system implementing the semiconductor device of FIGs. 1, 26, 29, & 32, according to an embodiment;

- [0041] FIG. 34 illustrates an exemplary circuit diagram modeling a pixel, according to the embodiment of FIG. 33;

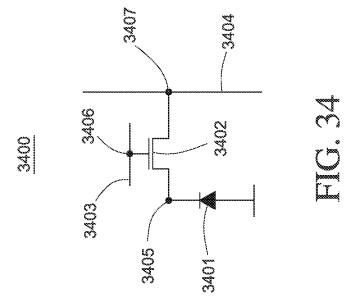

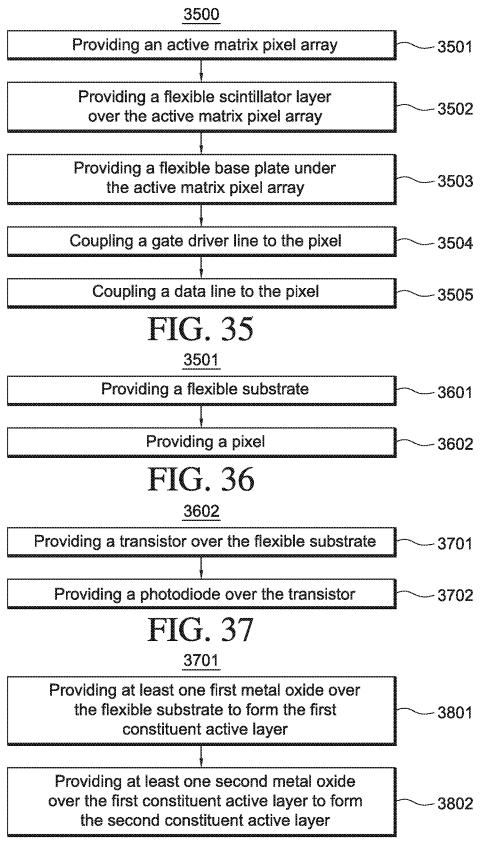

- [0042] FIG. 35 illustrates a flow chart for an embodiment of a method of manufacturing an imaging system;

- [0043] FIG. 36 illustrates an exemplary activity of providing an active matrix pixel array, according to the embodiment of FIG. 35;

- [0044] FIG. 37 illustrates an exemplary activity of providing a pixel, according to the embodiment of FIG. 35;

- [0045] FIG. 38 illustrates an exemplary activity of providing a transistor over the flexible substrate, according to the embodiment of FIG. 35;

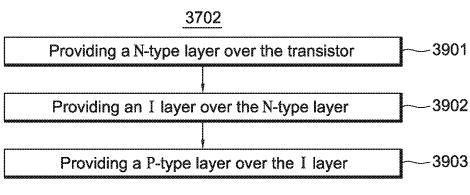

- [0046] FIG. 39 illustrates an exemplary activity of providing a photodiode over the transistor, according to the embodiment of FIG. 35;

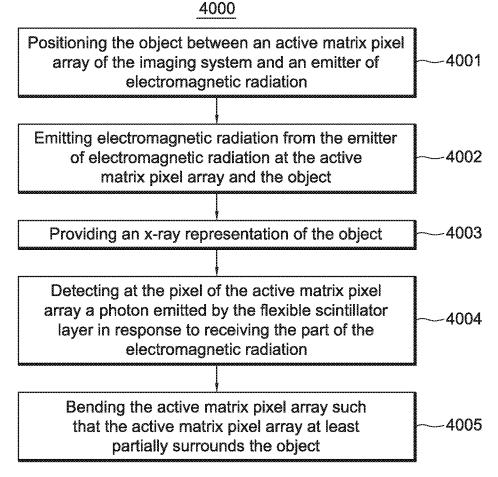

[0047] FIG. 40 illustrates a flow chart for an embodiment of a method of imaging an object with an imaging system;

- [0048] FIG. 41 illustrates a computer system that is suitable for implementing part of the functionality of the imaging system of FIG. 33 and/or the methods of FIGs. 35 and/or 40;

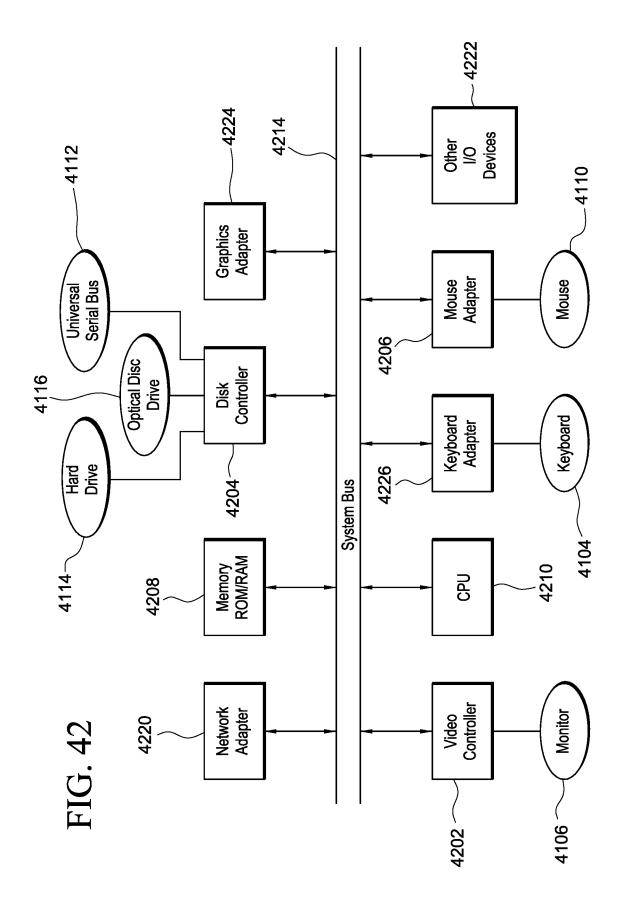

- [0049] FIG. 42 illustrates a representative block diagram of an example of the elements included in the circuit boards inside chassis of the computer system of FIG. 41;

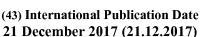

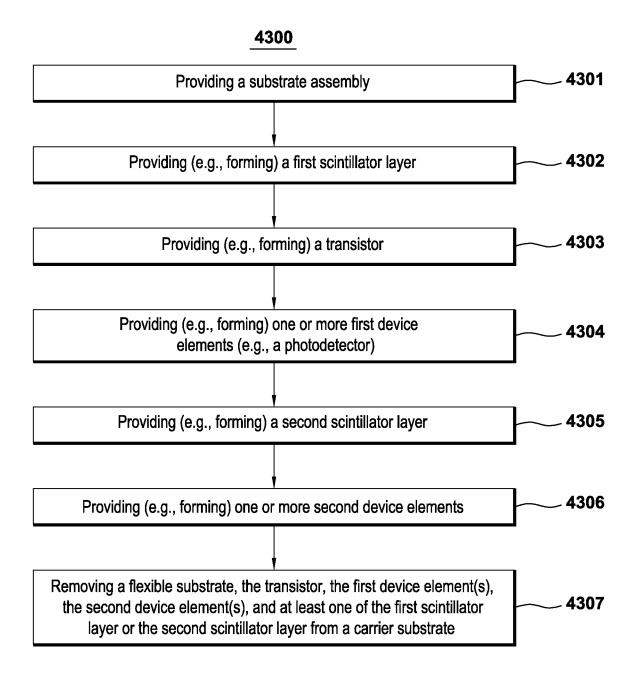

- [0050] FIG. 43 illustrates a flow chart for a method, according to an embodiment;

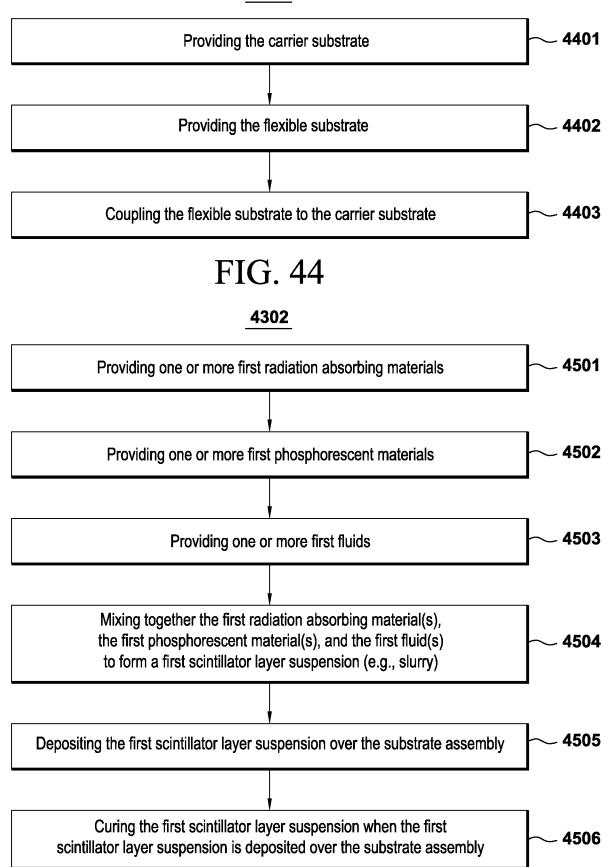

- [0051] FIG. 44 illustrates an exemplary activity of providing a substrate assembly, according to the embodiment of FIG. 43;

- [0052] FIG. 45 illustrates an exemplary activity of providing (e.g., forming) a first scintillator layer, according to the embodiment of FIG. 43;

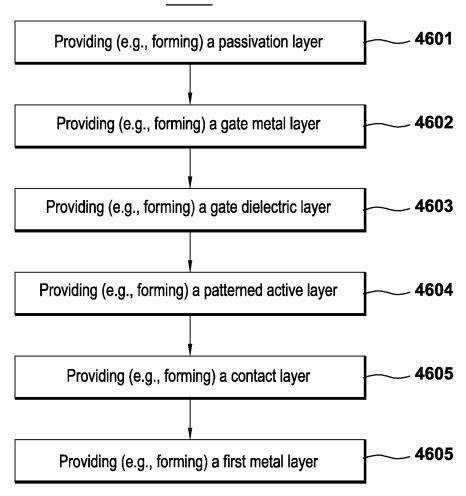

- [0053] FIG. 46 illustrates an exemplary activity of providing (e.g., forming) a transistor, according to the embodiment of FIG. 43;

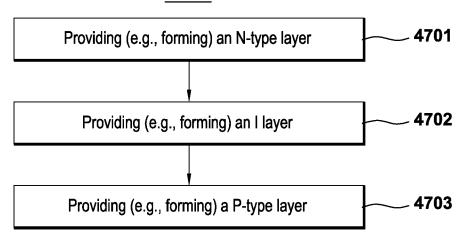

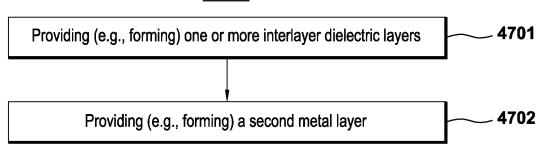

- [0054] FIG. 47 illustrates an exemplary activity of providing (e.g., forming) one or more first device elements, according to the embodiment of FIG. 43;

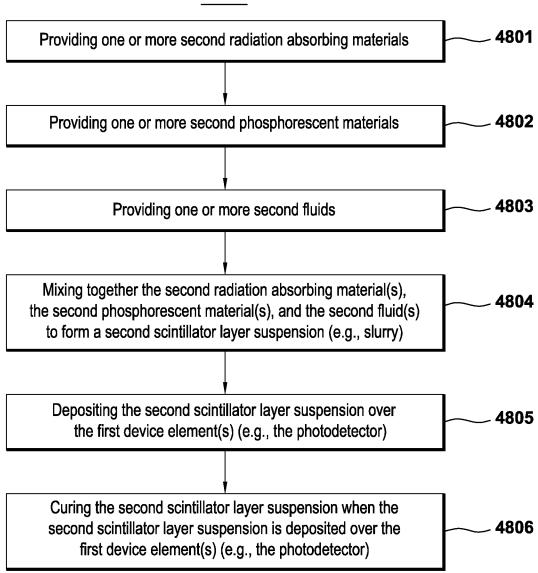

- [0055] FIG. 48 illustrates an exemplary activity of providing (e.g., forming) a second scintillator layer, according to the embodiment of FIG. 43;

- [0056] FIG. 49 illustrates an exemplary activity of providing (e.g., forming) one or more second device elements, according to the embodiment of FIG. 43; and

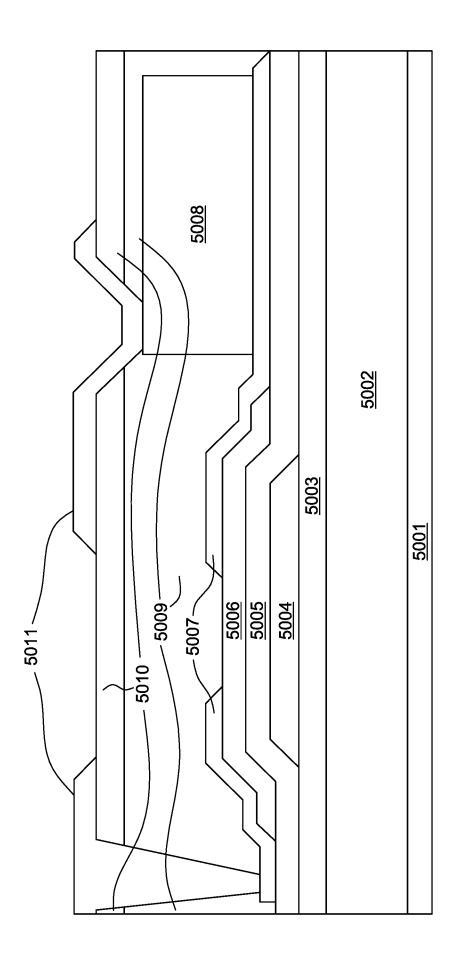

- [0057] FIG. 50 illustrates a cross-sectional view of a device build area of an electronic device, according to an embodiment.

- [0058] For simplicity and clarity of illustration, the drawing figures illustrate the general manner of construction, and descriptions and details of well-known features and techniques may be omitted to avoid unnecessarily obscuring the invention. Additionally, elements in the drawing figures are not necessarily drawn to scale. For example, the dimensions of some of the elements in the figures may be exaggerated relative to other elements to help improve understanding of embodiments of the present invention. The same reference numerals in different figures denote the same elements.

- [0059] The terms "first," "second," "third," "fourth," and the like in the description and in the claims, if any, are used for distinguishing between similar elements and not necessarily for describing a particular sequential or chronological order. It is to be understood that the terms so used are interchangeable under appropriate circumstances such that the embodiments described herein are, for example, capable of operation in sequences other than those illustrated or otherwise described herein. Furthermore, the terms "include," and "have," and any variations

thereof, are intended to cover a non-exclusive inclusion, such that an activity, method, system, article, device, or apparatus that comprises a list of elements is not necessarily limited to those elements, but may include other elements not expressly listed or inherent to such activity, method, system, article, device, or apparatus.

[0060] The terms "left," "right," "front," "back," "top," "bottom," "over," "under," and the like in the description and in the claims, if any, are used for descriptive purposes and not necessarily for describing permanent relative positions. It is to be understood that the terms so used are interchangeable under appropriate circumstances such that the embodiments of the invention described herein are, for example, capable of operation in other orientations than those illustrated or otherwise described herein.

[0061] The terms "couple," "coupled," "couples," "coupling," and the like should be broadly understood and refer to connecting two or more elements or signals, electrically, mechanically and/or otherwise. Two or more electrical elements may be electrically coupled but not be mechanically or otherwise coupled; two or more mechanical elements may be mechanically coupled, but not be electrically or otherwise coupled; two or more electrical elements may be mechanically coupled, but not be electrically or otherwise coupled. Coupling may be for any length of time, e.g., permanent or semi-permanent or only for an instant.

[0062] "Electrical coupling" and the like should be broadly understood and include coupling involving any electrical signal, whether a power signal, a data signal, and/or other types or combinations of electrical signals. "Mechanical coupling" and the like should be broadly understood and include mechanical coupling of all types.

[0063] The absence of the word "removably," "removable," and the like near the word "coupled," and the like does not mean that the coupling, etc. in question is or is not removable.

[0064] The terms "bow" and/or "bowing" as used herein can mean the curvature of a layer and/or multiple layers about a median plane, which is parallel to the top and bottom sides, or major (e.g., outermost) surfaces of the layer and/or layer(s). The term "warping" as used herein can mean the linear displacement of the surface of a layer and/or multiple layers with respect to a z-axis, which is perpendicular to the top and bottom sides, or major (e.g., outermost) surfaces of the layer and/or layer(s). The term "distortion" as used herein can mean the displacement of a layer and/or multiple layers in-plane (i.e., the x-y plane, which is parallel to the top and bottom sides, or major (e.g., outermost) surfaces of the layer and/or layer(s)). For example, distortion could include shrinkage in the x-y plane of a layer and/or multiple layers and/or expansion in the x-y plane of the layer and/or layer(s).

[0065] The term "CTE matched material" as used herein can mean a material that has a coefficient of thermal expansion (CTE) which differs from the CTE of a reference material by less than about 20 percent (%). Preferably, the CTEs differ by less than about 10%, 5%, 3%, or 1%. As used herein, "polish" can mean to lap and polish a surface or to only lap the surface.

The term "flexible substrate" as used herein means a free-standing [0066] substrate that readily adapts its shape. Accordingly, in many embodiments, the flexible substrate can comprise (e.g., consist of) a flexible material, and/or can comprise a thickness (e.g., an average thickness) that is sufficiently thin so that the substrate readily adapts in shape. In these or other embodiments, a flexible material can refer to a material having a low elastic Further, a low elastic modulus can refer to an elastic modulus of less than approximately five GigaPascals (GPa). In some embodiments, a substrate that is a flexible substrate because it is sufficiently thin so that it readily adapts in shape, may not be a flexible substrate if implemented with a greater thickness, and/or the substrate may have an elastic modulus exceeding five GPa. For example, the elastic modulus could be greater than or equal to approximately five GPa but less than or equal to approximately twenty GPa, fifty GPa, seventy GPa, or eighty GPa. Exemplary materials for a substrate that is a flexible substrate because it is sufficiently thin so that it readily adapts in shape, but that may not be a flexible substrate if implemented with a greater thickness, can comprise certain glasses (e.g., fluorosilicate glass, borosilicate glass, Corning® glass, Willow™ glass, and/or Vitrelle glass, etc., such as, for example, as manufactured by Corning Inc. of Corning, New York, United States of America, etc.) or silicon having a thickness greater than or equal to approximately 25 micrometers and less than or equal to approximately 100 micrometers.

[0067] Meanwhile, the term "rigid substrate" as used herein can mean a free-standing substrate that does not readily adapt its shape and/or a substrate that is not a flexible substrate. In some embodiments, the rigid substrate can be devoid of flexible material and/or can comprise a material having an elastic modulus greater than the elastic modulus of a flexible substrate. In various embodiments, the rigid substrate can be implemented with a thickness that is sufficiently thick so that the substrate does not readily adapt its shape. In these or other examples, the increase in rigidity of the rigid substrate provided by increasing the thickness of the rigid substrate can be balanced against the increase in cost and weight provided by increasing the thickness of the rigid substrate.

[0068] As used herein, "polish" can mean to lap and polish a surface or to only lap the surface.

#### DETAILED DESCRIPTION OF EXAMPLES OF EMBODIMENTS

[0069] Some embodiments include an electronic device. The electronic device can comprise a first scintillator layer, a transistor, and one or more device elements over the transistor, and the one or more device elements can comprise a photodetector. Meanwhile, the first scintillator layer can be monolithically integrated with at least one of the transistor or the one or more device elements.

[0070] Further embodiments include a method of manufacturing an electronic device. The method can comprise: providing a first scintillator layer; providing a transistor; and providing one or more device elements over the transistor. Providing the one or more device elements can comprise providing a photodetector. Meanwhile, the first scintillator layer is monolithically integrated with at least one of the transistor or the one or more device elements.

[0071] Further embodiments include an electronic device. The electronic device can comprise a substrate assembly, and the substrate assembly can comprise a carrier substrate and a flexible substrate coupled to the carrier substrate. Further, the electronic device can comprise a transistor over the substrate assembly, one or more device elements over the transistor, and a first scintillator layer over the one or more device elements. Meanwhile, the one or more device elements can comprise a photodetector, and the first scintillator layer can comprise one or more first radiation absorbing materials and one or more first phosphorescent materials. The first scintillator layer can directly contact the photodetector, and the first scintillator layer can be monolithically integrated with the transistor and the photodetector.

[0072] Turning to the drawings, FIG. 1 illustrates an example of method 100 of providing a semiconductor device, according to an embodiment. In the same or different embodiments, method 100 can be considered a method of providing a thin film transistor on a flexible substrate. Method 100 is merely exemplary and is not limited to the embodiments presented herein. Method 100 can be employed in many different embodiments or examples not specifically depicted or described herein.

[0073] Method 100 comprises activity 110 of providing a substrate assembly. In some embodiments, the substrate assembly can comprise a flexible substrate. In other embodiments, the substrate assembly may be devoid of a flexible substrate, such as, for example, where the substrate assembly comprises a rigid substrate but not a flexible substrate. FIG. 2 is a flow chart illustrating activity 110 of providing the substrate assembly, according to the embodiment of FIG. 1. Where the substrate assembly comprises a rigid substrate but not a flexible substrate, activities 211, 212, and 214-218, as described below, can be omitted. In these examples, the rigid substrate can comprise the carrier substrate, as described below with respect to activity 213.

[0074] Activity 110 can comprise activity 211 of furnishing a flexible substrate. In some embodiments, the flexible substrate can comprise a plastic substrate. The flexible substrate can comprise any suitable material(s) having the characteristics of a flexible substrate as defined above. In many embodiments, exemplary material(s) of the flexible substrate can comprise polyethylene naphthalate (PEN), polyethylene terephthalate (PET), polyethersulfone (PES), polyimide, polycarbonate, cyclic olefin copolymer, liquid crystal polymer, any other suitable polymer, glass (e.g., fluorosilicate glass, borosilicate glass, Corning® glass, Willow<sup>TM</sup> glass, and/or Vitrelle glass, etc., such as, for example, as manufactured by Corning Inc. of Corning, New York, United States of America, etc.), metal foil (e.g., aluminum foil, etc.), etc.

In many examples, the flexible substrate can comprise a coating at one or more sides of the flexible substrate. The coating can improve the scratch resistance of the flexible substrate and/or help prevent outgassing or oligomer crystallization on the surface of the substrate. Moreover, the coating can planarize the side of the flexible substrate over which it is located. The coating also can help decrease distortion. In some examples, the coating can be located only at the side of the flexible substrate where the electrical device will be fabricated. In other examples, the coating can be at both sides of the flexible substrate. In various embodiments the flexible substrate can be provided pre-planarized. For example, the flexible substrate can comprise a PEN substrate from DuPont Teijin Films of Tokyo, Japan, sold under the tradename "planarized Teonex® Q65." In other embodiments, a flexible substrate can be planarized after being provided. For example, method 2700 (FIG. 27) provides a method of planarizing a flexible substrate.

[0076] The thickness of the flexible substrate can be in the range of approximately 25 micrometers ( $\mu m$ ) to approximately 300  $\mu m$ . In the same or different embodiments, the thickness of the flexible substrate can be in the range of approximately 100  $\mu m$  to approximately 200  $\mu m$ .

[0077] In some examples, the flexible substrate can be provided by cutting a sheet of a plastic substrate from a roll of the plastic material using a paper cutter or a pair of ceramic scissors. In various examples, after cutting the plastic substrate, the cut sheet can be blown clean with a nitrogen gun. In some embodiments of activity 110, either or both of the cutting and blowing activities can be part of an activity 212, described below, instead of being part of activity 211.

[0078] In many embodiments, activity 110 can comprise activity 212 of preparing the flexible substrate. FIG. 3 is a flow chart illustrating activity 212 of preparing the flexible substrate, according to the embodiment of FIG. 1.

[0079] In some embodiments, activity 212 can comprise activity 330 of baking the flexible substrate. Baking the flexible substrate can help release oligomers and other chemicals in the flexible substrate that could potentially leach out later during method 100 (FIG. 1).

[0080] In some examples, the flexible substrate can be baked using a vacuum bake activity. For example, the temperature in an oven containing the flexible substrate can be ramped up over approximately two to three hours to approximately 160 degrees Celsius (°C) to approximately 200°C. The flexible substrate can be baked for one hour at approximately 160°C to approximately 200°C and at a pressure of approximately one milliTorr (mTorr) to approximately ten mTorr. Then, the temperature in the oven can be lowered to between approximately 90°C to approximately 115°C, and the flexible substrate can be baked for approximately eight more hours. Other baking activities can be also be used. After the baking activity is complete, the flexible substrate can be wiped clean of any residues or chemicals that were baked off.

[0081] In some embodiments, activity 212 can comprise activity 331 of providing a protective template. The protective template can act as both a guide for the placement of the flexible substrate as well as a protective layer between the flexible substrate and the rollers and/or handling mechanisms of various processing equipment. In some examples, the protective template can comprise a sheet of mylar or any inexpensive plastic. In other embodiments, the protective template can comprise tape (e.g., a low tack tape). In these embodiments, one or more of activity 332-335 and activity 337, as described below, can be omitted.

[0082] The protective template can be 50 µm to 15 mm thick and cut to a length of approximately 0.5 m (meters) to approximately 1.5 m. In various embodiments, as part of activity 331, the protective template can be folded in half and run through rollers (e.g., a hot roll laminator) to help lock in the fold. A line trace of a carrier substrate can also be made on the back side of the protective sheet as part of activity 331. Additionally, the protective template can be baked at approximately 90°C to approximately 110°C for approximately five minutes to approximately ten minutes to help flatten the protective template.

[0083] In some embodiments, activity 212 can comprise activity 332 of applying a protective material to at least a portion of a first surface of the flexible substrate. In some embodiments, a protective material can be applied over at least a portion of a planarized surface of the flexible substrate. In some examples, the protective material is not applied to a portion of the flexible substrate.

[0084] The protective material can prevent scratches and adhesive from covering the planarized surface of the flexible substrate and, thus, reduces defects. In some examples, blue low tack tape (e.g., from Semiconductor Equipment Corporation, part number 18133-7.50) or

mylar could be used as the protective material. The protective material can be approximately 25 µm to approximately 100 µm thick. For example, the protective material can be approximately 70 µm thick. In some examples, the protective material is applied by rolling the protective material onto the planarized surface of the flexible substrate using a roller to remove air bubbles between the protective material and the flexible substrate.

[0085] In some embodiments, activity 212 can comprise activity 333 of cutting the flexible substrate and protective material into the shape of a wafer. A punch cut template can be used to press the wafer shape into the flexible substrate (with the planarized side, if any, up) and/or the protective material. In one embodiment, the punch cut template can be used to create a temporary or permanent impression in the protective material and the flexible substrate at the same time.

[0086] If the pressing of the punch cut template cuts completely through the flexible substrate, the flexible substrate can be scrapped because the press cut can create cracks in a coating on the flexible substrate that propagate throughout the flexible substrate. After the wafer shape is outlined into the flexible substrate and/or the protective material using the press, the flexible substrate and the protective material can be cut simultaneously with each other. In some examples, the flexible substrate and protective material can be cut using ceramic scissors approximately one millimeter outside the impression made by the punch cut template.

In some examples, the flexible substrate can comprise a tab extending from the wafer shape in the flexible substrate and the protective material. The tab can be used to help align the flexible substrate to a carrier substrate when traveling through a laminator in activity 217 (FIG. 2). FIG. 4 illustrates a top view of flexible substrate 450, according to the embodiment of FIG. 1. Flexible substrate 450 can comprise body 452 and tab 451. In many examples, body 452 can have a circular shape. Although not illustrated in FIG. 4, the protective material that is located over flexible substrate 450 can also comprise a similarly shaped tab. In one embodiment, the tab is not part of the punch cut template and is cut freehand or freestyle into the flexible substrate and the protective material.

[0088] Referring back to FIG. 3, activity 212 can comprise activity 334 of cleaning the flexible substrate. In some examples, the second or non-planarized side of the flexible substrate (i.e., the side without the protective material) can be dry wiped to remove any oligomers, other chemicals, or particles. Afterwards, the planarized side of the flexible substrate having the protective material can be blown clean with a nitrogen gun. In other examples, both sides of the flexible substrate can be dry wiped and/or blown clean.

[0089] In some embodiments, activity 212 can comprise activity 335 of aligning the flexible substrate with a protective template. In some examples, the flexible substrate having the wafer shape with the tab can be aligned with the line trace of a carrier substrate drawn or made on the protective template in activity 331. The line trace of the carrier substrate can be slightly larger than the wafer shape of the flexible substrate.

[0090] In some embodiments, activity 212 can comprise activity 336 of coupling the flexible substrate to the protective template. In some embodiments, the flexible substrate can be attached to the protective template by attaching a portion of the tab of the flexible substrate to the protective template. For example, a piece of double-sided tape can couple the tab of the flexible substrate to the protective template. In some examples, a portion of the protective material can be peeled off of and removed from the tab, and the double-sided tape can be coupled to the exposed portion of the tab of the flexible substrate. In some examples, the portion of the protective material can be peeled using tweezers and can be cut from the protective template using a pair of ceramic scissors. In other examples, in activity 332, the protective material is not applied to the portion the tab to which the double-sided tape will be attached so peeling and removal of a portion of the protective material is not necessary.

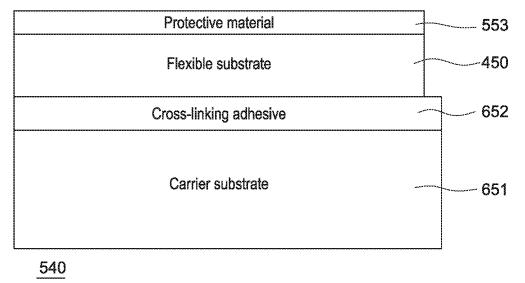

[0091] After coupling the flexible substrate to the protective coating, the protective template is then folded over the flexible substrate. FIG. 5 illustrates a partial cross-sectional view of substrate assembly 540 after attaching flexible substrate 450 to protective template 555, according to the embodiment of FIG. 1. In this example, tape 556 can be coupled to flexible substrate 450 and protective template 555. Protective material 553 can be coupled to flexible substrate 450, as described previously.

[0092] In some examples, only one side of the flexible substrate is attached to the protective template. In other examples, both sides of the flexible substrate are attached to the protective template.

[0093] Turning back to FIG. 3, activity 212 can comprise activity 337 of laminating the flexible substrate, the protective material, and the protective template. The flexible substrate and the protective material can be located between the two folded halves of the protective template. The flexible substrate, the protective material, and the protective template can be laminated using a hot roll laminator to remove air bubbles between the protective material and the protective template and also between the protective material and the flexible substrate. In some examples, the flexible substrate and the protective template can be placed over a guide sheet (e.g., a Lexan® guide sheet) and fed into the hot roll laminator. As an example, the tab of the flexible substrate and the protective material can be fed first into the laminator. The flexible

substrate and the protective template are laminated at a pressure of approximately 120 kPa (kilopascals) to approximately 160 kPa and at a temperature of approximately 90°C to approximately 110°C. The lamination speed can be approximately one meter per minute to approximately two meters per minute.

[0094] In many embodiments, after laminating the flexible substrate and protective template, activity 212 can be complete. Referring back to FIG. 2, activity 110 can comprise activity 213 of providing a carrier substrate. In many embodiments, the carrier substrate can comprise a rigid substrate.

[0095] In some embodiments, the carrier substrate can be a 6, 8, 12, or 18 inch wafer or panel. However, when applicable, the carrier substrate can be any suitable size to accommodate a flexible substrate. In further embodiments, the carrier substrate can be a panel of approximately 300 mm by 350 mm, 300 mm by 400 mm, 320 mm by 400 mm, 365 mm by 460 mm, 370 mm by 400 mm, 370 mm by 470 mm, 400 mm by 500 mm, 550 mm by 650 mm, 680 mm by 880 mm, 730 mm by 920 mm, 1100 mm by 1250 mm, 1500 mm by 1800 mm, 1870 mm by 2200 mm, 2200 mm by 2500 mm, 2400 mm by 2800 mm, 2850 mm by 3050 mm, and 2880 mm by 3130 mm.

[0096] The carrier substrate can comprise a first surface and a second surface opposite the first surface. In some examples, at least one of the first surface and the second surface can be and/or has been polished. Polishing the surface that is not subsequently coupled to the flexible substrate can improve the ability of a vacuum or air chuck to handle the carrier substrate. Also, polishing the surface that is subsequently coupled to the flexible substrate can remove topological features of the surface of the carrier substrate that could cause roughness of the substrate assembly in the z-axis after the coupling with the flexible substrate.

[0097] In various embodiments, the carrier substrate can comprise at least one of the following: alumina (Al<sub>2</sub>O<sub>3</sub>), silicon, low CTE glass, steel, stainless steel, sapphire, barium borosilicate, soda lime silicate, an alkali silicate, or another material that is CTE matched to the flexible substrate. Where the substrate assembly comprises a flexible substrate, the CTE of the carrier substrate can be matched to the CTE of the flexible substrate. Non-matched CTEs can create stress between the carrier substrate and the flexible substrate.

[0098] For example, the carrier substrate could comprise sapphire with a thickness between approximately 0.7 mm and approximately 1.1 mm. The carrier substrate could also comprise 96% alumina with a thickness between approximately 0.7 mm and approximately 1.1 mm. In a different embodiment, the thickness of the 96% alumina is approximately 2.0 mm. In another example, the carrier substrate could be a single crystal silicon wafer with a thickness of at least

approximately 0.65 mm. In still a further embodiment, the carrier substrate could comprise stainless steel with a thickness of at least approximately 0.5 mm. In some examples, the carrier substrate is slightly larger than the flexible substrate.

[0099] In some embodiments, activity 110 can comprise activity 214 of providing a cross-linking adhesive. In some examples, the cross-linking adhesive outgases at a rate of less than approximately 2 x 10-4 Torr-liters per second. In some examples, the cross-linking adhesive is thermally and/or UV (ultraviolet) light curable.

[00100] In various embodiments, the cross-linking adhesive can be a cross-linking acrylic adhesive. In the same or different embodiment, the cross-linking adhesive can be a cross-linking pressure sensitive acrylic adhesive or a cross-linking viscoelastic polymer. In some examples, the CTE of the adhesive can be very large compared to the CTE of the flexible substrate and the carrier substrate. However, the CTE of the adhesive may not be of concern because the adhesive may create marginal stress (i.e., viscoelasticity) between the flexible substrate and carrier substrate because the layer of adhesive is so thin compared to the thickness of the flexible substrate and carrier substrate.

[00101] In some embodiments, activity 110 can comprise activity 215 of depositing the cross-linking adhesive over a first surface of the carrier substrate. In many embodiments, depositing the cross-linking adhesive over a first surface of the carrier substrate can be performed using at least one of the following methods: spin-coating, spray-coating, extrusion coating, preform lamination, slot die coating, screen lamination, and screen printing.

[00102] For example, the carrier substrate can be coated with the cross-linking adhesive. The carrier substrate and the cross-linking adhesive can be spun to distribute the cross-linking adhesive over a first surface of the carrier substrate. In some embodiments, the cross-linking adhesive can be spin coated on the carrier substrate by spinning the carrier substrate with the cross-linking adhesive at approximately 900 rpm (revolutions per minute) to 1100 rpm for approximately 20 seconds to approximately 30 seconds and then spinning the carrier substrate with the cross-linking adhesive at approximately 3400 rpm to approximately 3600 rpm for approximately 10 seconds to 30 seconds. In a different embodiment, the carrier substrate with the cross-linking adhesive can be spun at approximately 600 rpm to approximately 700 rpm to coat the surface of the carrier substrate and then spun at approximately 3400 rpm to approximately 3400 rpm to control the thickness of the cross-linking adhesive.

[00103] Prior to spin coating, the cross-linking adhesive can be dispensed onto or over a geometric center of the carrier substrate. In a different embodiment, the cross-linking adhesive can be dispensed onto or over the carrier substrate while the carrier substrate is spinning.

[00104] The thickness of the cross-linking adhesive over the carrier substrate after the depositing activity can be between approximately three  $\mu m$  and approximately fifteen  $\mu m$ . In the same or different embodiment, the thickness of the cross-linking adhesive over the carrier substrate after the depositing activity can be between approximately ten  $\mu m$  and approximately twelve  $\mu m$ .

[00105] In some embodiments, activity 110 can comprise activity 216 of baking the cross-linking adhesive. In some embodiments, the cross-linking adhesive can be baked to remove solvents. For example, the cross-linking adhesive can be baked at 80°C for thirty minutes and then baked for fifteen minutes at 130°C.

[00106] In other examples, the cross-linking adhesive is not baked. For example, if the cross-linking adhesive does not comprise any solvents, a bake is not necessary. Moreover, if the cross-linking adhesive is very viscous, solvents can even be added to the cross-linking adhesive to decrease the viscosity before the adhesive is deposited in activity 215.

[00107] Afterwards, the carrier substrate can be placed on the protective template. The flexible substrate can be already coupled to one portion (or half) of the protective template as shown in FIG. 6, and the carrier substrate with cross-linking adhesive can be placed on another portion (or half) of the protective template. In some examples, the cross-linking adhesive can still be in liquid form at this point. Thus, the carrier substrate coated with the cross-linking adhesive can be stored horizontally for approximately eight to approximately twelve hours before being coupled with the flexible substrate.

[00108] In many embodiments, activity 110 can comprise activity 217 of coupling the carrier substrate to the flexible substrate (e.g., using the cross-linking adhesive while both substrates are located between the protective template halves). In some embodiments, the second surface of the flexible substrate can be placed over the first surface of the carrier substrate with the adhesive located between the second surface of the flexible substrate and the first surface of the carrier substrate. In other embodiments, one or more of activities 214-216 can be omitted.

[00109] In some examples, the carrier substrate can be coupled to the flexible substrate using the cross-linking adhesive by laminating the substrate assembly between the protective template halves to remove air bubbles between the carrier substrate and the flexible substrate. Laminating the flexible substrate involves first aligning the carrier substrate with the flexible substrate so that, when laminated, the carrier substrate and the flexible substrate are aligned. Then, the aligned structure can be fed through a hot roll laminator, which can be the same laminator of activity 337 of FIG. 3. The substrate assembly can be laminated at an approximate speed of 0.4 to 0.6 meters per minute.

[00110] Also, in various embodiments, the protective material may stick to the protective template when laminated. To avoid this problem, a shield material can be located between the protective template and the protective material before the lamination of activity 337 and/or activity 332. The shield material can be, for example, wax paper. In one embodiment, the shield material is originally coupled to the protective material when acquired from the manufacturer.

[00111] In the same or different embodiments, some of the cross-linking adhesive can be squeezed out from between the carrier and flexible substrates during lamination and adhere to the first side or the top of the flexible substrate, particularly because the carrier substrate and the overlying cross-linking adhesive layer is slightly larger than the flexible substrate. The presence of the protective material, however, prevents this problem from occurring. The cross-linking adhesive that squeezes out and adheres to the top of the protective material (instead of the flexible substrate) is inconsequential because the protective material is eventually removed and discarded.

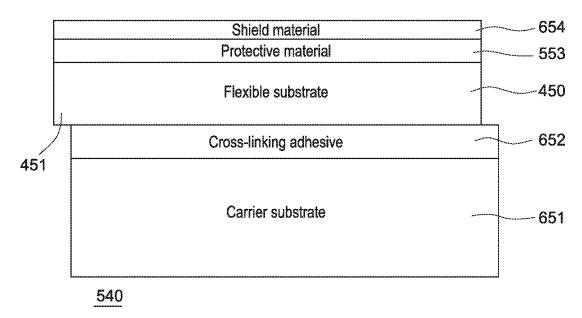

[00112] FIG. 6 illustrates a partial cross-sectional view of substrate assembly 540 after coupling carrier substrate 651 to flexible substrate 450, according to the embodiment of FIG. 1. In this embodiment, cross-linking adhesive 652 can couple surface 661 of carrier substrate 651 to surface 662 of flexible substrate 450. Protective material 553 can be located over surface 656 of flexible substrate 450. Shield material 654 can be located between protective material 553 and protective template 555. Protective template 555 can be folded such that protective template 555 is also located under surface 663 of carrier substrate 651. Tape 556 can couple protective template 555 to tab 451 of flexible substrate 450. In some embodiments, such as where the substrate assembly of activity 110 comprises a rigid substrate but not a flexible substrate, substrate assembly 540 can comprise carrier substrate 651 without cross-linking adhesive 652 and flexible substrate 450.

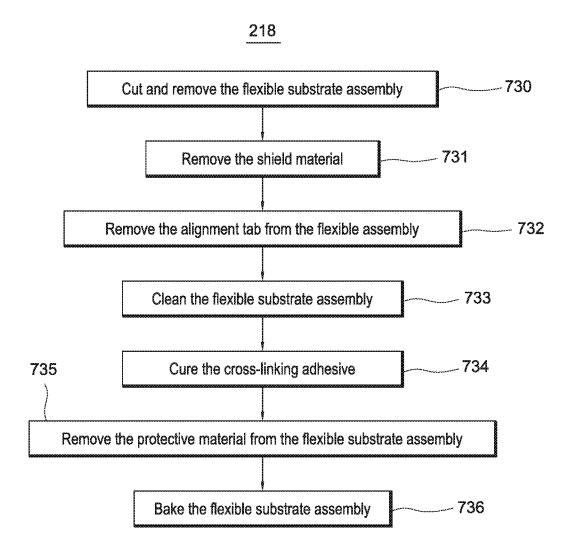

[00113] Referring again back to FIG. 2, activity 110 can comprise activity 218 of processing the substrate assembly. FIG. 7 is a flow chart illustrating activity 218 of processing the substrate assembly, according to the embodiment of FIG. 1.

[00114] Activity 218 can comprise activity 730 of cutting the substrate assembly. In some examples, a pair of ceramic scissors can be used to cut the protective template and across the alignment tab of the flexible substrate located between the protective template, but the alignment tab is not removed entirely. After cutting the substrate assembly, the protective template can be peeled away from or otherwise removed from the shield material and the carrier substrate by hand. FIG. 8 illustrates a cross-sectional view of substrate assembly 540 after cutting the

substrate assembly and removing the protective template, according to the embodiment of FIG.

1. More specifically, in FIG. 8, protective template 555 (FIGs. 5 & 6), and tape 556 (FIGs. 5 & 6) of flexible substrate 450 have been removed.

[00115] Referring again to FIG. 7, activity 218 can comprise activity 731 of removing the shield material by hand. In some examples, the substrate assembly can be placed at an edge of a table with the shield material facing the table. The substrate assembly can be slowly moved off the table while the shield layer is removed (e.g., peeled) from the substrate assembly. That is, the shield layer can be removed by pulling the shield material downward away from the edge of the table while the substrate assembly is moved horizontally off the table. In some examples, if the flexible substrate is not properly centered on or otherwise aligned with the carrier substrate after removing the shield layer, the flexible substrate can be slid into alignment with the carrier substrate.

[00116] Further, activity 218 can comprise activity 732 of removing the alignment tab from the flexible assembly. In some examples, the alignment tab can be cut from the flexible substrate using ceramic scissors. The cut should be made slowly as any movement of the flexible substrate in the z-direction (relative to the carrier substrate) might cause de-lamination of the flexible substrate from the carrier substrate. If de-lamination occurs, the substrate assembly can be re-laminated. FIG. 9 illustrates a cross-sectional view of substrate assembly 540 after removing the alignment tab, according to the embodiment of FIG. 1.

[00117] Activity 218 can comprise activity 733 of cleaning the substrate assembly. In some examples, the substrate assembly can be cleaned with hexanes. The hexanes can be applied by spinning the substrate assembly and spraying the hexanes on the protective material. After the protective material is cleaned, the exposed surface and edge of the carrier substrate can be wiped clean with hexanes.

[00118] Activity 218 can comprise activity 734 of curing the cross-linking adhesive. In the same or different embodiment, the cross-linking adhesive can be UV cured. For example, the substrate assembly can be exposed to UV light for approximately 15 to 25 seconds and room temperature to cure the cross-linking adhesive. In some embodiments, the cross-linking adhesive can be cured with UV light in the UV light range of approximately 320 nm (nanometers) to approximately 390 nm and with an intensity of approximately 75 mW/cm² (milliWatts per square centimeter). A Dymax 2000-EC UV Curing Flood Lamp, manufactured by Dymax Corporation of Torrington, Connecticut, can be used to cure the cross-linking adhesive.

[00119] In various examples, the cross-linking adhesive can be thermally cured during the baking in activity 736. In some examples, the edges of the cross-linking adhesive can be UV cured, and the rest of the cross-linking adhesive can be thermally cured during the baking of activity 736.

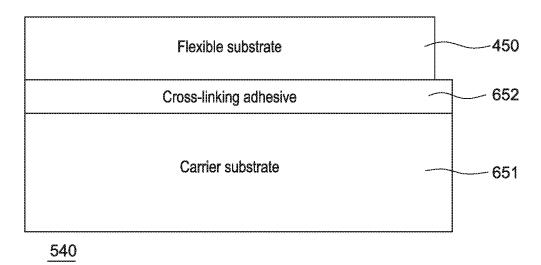

[00120] In many embodiments, activity 218 can comprise activity 735 of removing the protective material from the substrate assembly. In some examples, the protective material can be slowly removed using tweezers. During the removal activity, the protective material can be kept as flat as possible to avoid de-laminating the flexible substrate from the carrier substrate. In other examples, the protective material can be releasable by UV light. In these examples, the protective material would lose its tack during a UV light exposure. FIG. 10 illustrates a cross-sectional view of substrate assembly 540 after removing the protective material from the substrate assembly, according to the embodiment of FIG. 1.

[00121] In many embodiments, activity 218 can comprise activity 736 of baking the substrate assembly. Baking the substrate assembly can help decrease the distortion, bow, and warp in the flexible substrate. In some embodiments, baking can also cure the adhesive.

[00122] In some examples, the substrate assembly can be baked using a vacuum bake activity. For example, the temperature in an oven containing the substrate assembly can be ramped up over two to three hours to approximately 160°C to approximately 190°C. The substrate assembly can be baked for approximately 50 minutes to 70 minutes at 180°C and with a pressure of approximately 1 mTorr to approximately 10 mTorr. The temperature in the oven can then be lowered to between approximately 90°C to 115°C, and the substrate assembly can be baked for approximately seven more hours to approximately nine more hours. Other baking activities also can be used. After the baking activity is complete, the flexible substrate assemblies are cleaned and placed in an oven at approximately 90°C to 110°C for a minimum of approximately two hours.

[00123] In many embodiments, after baking the substrate assembly, activity 218 can be complete, and therefore, activity 110 (FIG. 1) also can be complete.

[00124] Where the substrate assembly of activity 110 (FIG. 1) comprises a flexible substrate (e.g., flexible substrate 450 (FIG. 10)), activity 110 (FIG. 1) and/or activity 120 (FIG. 1), as described herein, and similar activities can allow fabrication of one or more electrical components on the flexible substrate with zero or at least minimal distortion (e.g. approximately the limits of the sensitivity of an Azores 5200, manufactured by Azores Corporation of Wilmington, Massachusetts). Prior art methods of fabricating electrical components on the

flexible substrate suffer from significant distortion problems that can lead to handling errors, photolithographic alignment errors, and line/layer defects.

[00125] However, as indicated previously, it is also possible to perform activity 110 (FIG. 1) and/or activity 120 (FIG. 1), as described herein, and similar activities, where the substrate assembly of activity 110 comprises a rigid substrate (e.g., carrier substrate 651 (FIG. 10) but not a flexible substrate (e.g., flexible substrate 450 (FIG. 10)). Still, performing activity 110 (FIG. 1) such that the substrate assembly comprises the flexible substrate can provide various advantages, not the least of which can be the afore mentioned ability to fabricate one or more flexible electrical components.

[00126] United States Patent No. 8,992,712, which issued March 31, 2015, and United States Patent No. 9,076,822, which issued July 7, 2015, teach similar activities for providing a substrate assembly that can also be implemented in order to perform activity 110. Accordingly, United States Patent No. 8,992,712 and United States Patent No. 9,076,822 each are incorporated by reference herein in their entirety.

[00127] Referring back to FIG. 1, method 100 comprises activity 120 of providing semiconductor elements. FIG. 11 is a flow chart illustrating activity 120 of providing semiconductor elements, according to the embodiment of FIG. 1.

[00128] In many embodiments, activity 120 can comprise activity 1112 of providing one or more first semiconductor elements. FIG. 12 is a flow chart illustrating activity 1112 of providing one or more first semiconductor elements, according to the embodiment of FIG. 1.

[00129] In some embodiments, activity 1112 can comprise activity 1211 of providing a gate metal layer. In some embodiments, the substrate assembly of activity 110 (FIG. 1) can be cleaned by a quick-dump-rinse (QDR) activity with a suitable detergent followed by a spin-rinse-dry (SRD) activity prior to performing activity 1211. An exemplary detergent can comprise Alconox Detergent 8, manufactured by Alconox, Inc. of White Plains, New York, (e.g., 40 mL) mixed with one liter of water. The cleaning can be performed in a megasonic cleaning tank. FIG. 13 illustrates a cross-sectional view of a device build area of an example of semiconductor device 1350 after providing a gate metal layer, according to the embodiment of FIG. 1. As can be seen in FIG. 29, the cross-sectional view of the device build area is the cross-sectional view of a portion of semiconductor device 1350 taken at the "a" lines. The device build cross sectional view comprises a cross-sectional view of contact areas 2980 and via area 2982. In addition, FIG. 14 illustrates a cross-sectional view of a gate contact build area of an example of semiconductor device 1350 after providing a gate metal layer, according to the embodiment of FIG. 1. As can be seen in FIG. 29, the cross-sectional view of the gate contact

build area is the cross-sectional view of a portion of semiconductor device 1350 taken at the "b" lines. The gate contact build cross sectional view comprises a cross-sectional view of gate contact area 2981. FIG. 29 is merely exemplary and is not limited to the embodiments presented herein.

[00130] Referring to FIGs. 13 and 14, for example, passivation layer 1352 can be provided over substrate assembly 540. In many examples, passivation layer 1352 can be deposited onto semiconductor device 1350 over substrate assembly 540 by way of plasma-enhanced chemical vapor deposition (PECVD). In these or other examples, passivation layer 1352 can be deposited at a temperature less than or equal to approximately 200°C. When substrate assembly 540 comprises a flexible substrate (e.g., flexible substrate 450 (FIG. 10)), passivation layer 1352 can be provided over flexible substrate 450 (FIG. 10) of substrate assembly 540. In some embodiments, flexible substrate 450 can be baked prior to the deposition of passivation layer 1352.

[00131] Passivation layer 1352 can comprise a dielectric material. The dielectric material can comprise silicon dioxide and/or silicon nitride. Further, passivation layer 1352 can be greater than or equal to approximately 200 nanometers thick and less than or equal to approximately 400 nanometers thick. For example, passivation layer 1352 can be approximately 300 nanometers thick. In some embodiments, passivation layer 1352 can protect one or more other layers of semiconductor device 1350 (e.g., patterned active layer 1555 (FIGs. 15, 17, 19, 21, 24-26, & 32) from atmospheric contamination.

[00132] In addition, patterned metal gate 1353 can be provided over passivation layer 1352. Patterned metal gate 1353 can comprise molybdenum, tantalum, aluminum, neodymium, chromium, niobium, titanium, silicon, and/or tungsten. Further, patterned metal gate 1353 can be greater than or equal to approximately 100 nanometers thick and less than or equal to approximately 200 nanometers thick. In specific examples, an approximately 150 nanometer layer of molybdenum can be deposited over passivation layer 1352 and then pattern etched to form patterned metal gate 1353. In these or other examples, patterned metal gate 1353 can be deposited over passivation layer 1352 by sputtering.

[00133] In some examples, patterned metal gate 1353 can be deposited using a KDF 744, manufactured by KDF Electronic, Inc., of Rockleigh, New Jersey. Patterned metal gate 1353 can be deposited such that the sidewalls of patterned metal gate 1353 slope downwardly and/or outwardly toward passivation layer 1353 at an angle of less than or equal to approximately 45 degrees with respect to the horizontal. In the same or different examples, patterned metal gate 1353 can be etched using a reactive ion etcher, such as, for example, an AMAT 8330,

manufactured by Applied Material, Inc. of Santa Clara, California. Passivation layer 1352 can act as a moisture barrier and an etch stop for patterned metal gate 1353. The etchant can comprise any suitable dry etchant (e.g., a chlorine and oxygen dry etchant) or any suitable wet etchant, such as, for example, a mixture of phosphoric acid, acetic acid, and/or water.

[00134] Referring again to FIG. 12, activity 1112 can comprise activity 1212 of providing an active stack. In some embodiments, the substrate assembly of activity 110 (FIG. 1) and the gate metal layer of activity 1211 can be cleaned by a QDR activity with a suitable detergent followed by a SRD activity prior to performing activity 1212. An exemplary detergent can comprise Alconox Detergent 8, manufactured by Alconox, Inc. of White Plains, New York, (e.g., 40 mL) mixed with one liter of water. The cleaning can be performed in a megasonic cleaning tank. FIGs. 15 and 16 illustrate an example of semiconductor device 1350 after providing an active stack, according to the embodiment of FIG. 1.

[00135] Referring to FIGs. 15 and 16, for example, gate dielectric 1554 can be formed over patterned metal gate layer 1353 and passivation layer 1352. Referring to FIG. 15, for example, in the device build area of semiconductor device 1350, patterned active layer 1555 can be provided over gate dielectric 1554, and patterned intermetal dielectric (IMD) layer 1556 can be provided over patterned active layer 1555. In some embodiments, the substrate assembly of activity 110 (FIG. 1) and the gate metal layer of activity 1211 can be cleaned with a solution of ammonium hydroxide and water in ratio of one part to ten parts, respectively. In some examples, patterned active layer 1555 can be referred to as a transistor active layer.

[00136] In some examples, as shown in FIGs. 15 and 16, gate dielectric 1554 can be deposited onto semiconductor device 1350 over metal gate layer 1353 and/or passivation layer 1352 by way of PECVD. Gate dielectric 1554 can comprise one or more gate dielectric materials. Exemplary gate dielectric material(s) can comprise one or more oxides (e.g., silicon dioxide), one or more nitrides (e.g., silicon nitride), one or more silicon oxynitrides, one or more hafnium oxynitrides, one or more aluminum oxynitrides, one or more barium oxynitrides, and/or one or more strontium oxynitrides. Further exemplary gate dielectric material(s) can comprise one or more organic polymer materials. In some embodiments, gate dielectric 1154 can be buffered with silicon nitride and/or one or more other dielectric materials on the side of gate dielectric 1154 closest to patterned metal gate 1353. Accordingly, in certain examples, gate dielectric 1554 can be deposited onto semiconductor device 1350 by way of PECVD using silane (SiH<sub>4</sub>) and nitrous oxide (N<sub>2</sub>O) precursor gases. The ratio of silane to nitrous oxide can be 100 to 1 parts by volume to minimize the hydrogen content in gate dielectric 1554. When gate dielectric 1554 comprises silicon nitride, the silicon nitride can be hydrogenated. The index

of refraction of gate dielectric 1554 can be tuned to greater than or equal to 1.8 and less than or equal to 1.85 (e.g., at 633 nanometers). Gate dielectric 1554 can be greater than or equal to approximately 100 nanometers thick and less than or equal to approximately 300 nanometers thick, such as, for example, approximately 200 nanometers thick.

With reference to FIG. 15, as an example, patterned active layer 1555 can be [00137] deposited over gate dielectric 1554 by way of PECVD and/or by way of sputtering. In some embodiments, patterned active layer 1555 can comprise amorphous silicon (a-Si) and/or hydrogenated amorphous silicon (a-Si:H). In these examples, in certain examples, patterned active layer 1555 can be deposited onto semiconductor device 1350 by way of PECVD using silane (SiH<sub>4</sub>) and hydrogen (H<sub>2</sub>) precursor gases. The index of refraction of patterned active layer 1555 can be tuned to greater than or equal to 3.65 and less than or equal to 3.75 (e.g., at 633 nanometers), such as, for example, to provide a particular silicon and hydrogen composition. In other embodiments, patterned active layer 1555 can comprise one or more metal oxides. For example, patterned active layer 1555 can comprise indium, indium oxide, zinc, zinc oxide, gallium, gallium oxide, tin, tin oxide, hafnium, hafnium oxide, zirconium, zirconium oxide, aluminum, aluminum oxide, silicon, silicon oxide, copper, copper oxide, cobalt, and/or cobalt oxide, in equal or unequal proportions to one another. Further, patterned active layer 1555 can comprise one or more organic polymer materials. In the same or different examples, patterned active layer 1555 can be greater than or equal to approximately 50 nanometers thick and less than or equal to approximately 80 nanometers thick. In some embodiments, patterned active layer 1555 can comprise a single active layer or multiple constituent active layers.

[00138] Turning ahead in the drawings, FIG. 31 illustrates patterned active layer 1555 when patterned active layer 1555 comprises multiple constituent active layers, such as, for example, first constituent active layer 3156 and second constituent active layer 3157, according the embodiment of FIG. 1. First constituent active layer 3156 and/or second constituent active layer 3157 can be patterned. Patterned active layer 1555 is shown after patterned active layer 1555 is deposited over gate dielectric 1554 but prior to deposition of patterned IMD layer 1556. Accordingly, first constituent active layer 3156 can be over gate dielectric 1554, and/or second constituent active layer 3157 can be over first constituent active layer 3156. Further, although not shown at FIG. 31, in some embodiments, patterned IMD layer 1556 (FIG. 15) can be over and/or on second constituent active layer 3157.

[00139] With respect to composition, first constituent active layer 3156 can comprise one or more first metal oxides and a first conductivity and/or resistivity. Further, second constituent

active layer 3157 can comprise one or more second metal oxides and a second conductivity and/or resistivity. Implementing patterned active layer 1555 to comprise both first constituent active layer 3156 and second constituent active layer 3157 can help to ensure that semiconductor device 1350 can be turned off, which may not happen if patterned active layer 1555 comprises first constituent active layer 3156 only.

[00140] For example, the first metal oxide(s) can comprise one or more of indium, indium oxide, zinc, zinc oxide, gallium, gallium oxide, tin, tin oxide, hafnium, hafnium oxide, zirconium, zirconium oxide, aluminum, aluminum oxide, silicon, silicon oxide, copper, copper oxide, cobalt, and/or cobalt oxide, in equal or unequal proportions to one another. More specifically, the first metal oxide(s) can comprise approximately sixty percent zinc oxide and approximately forty percent indium oxide. In other examples, the first metal oxide(s) can comprise indium oxide, gallium oxide, and zinc oxide in equal proportions to each other. Meanwhile, the second metal oxide(s) can be similar to, identical to, or different from the first metal oxide(s). For example, where the second metal oxide(s) comprise the first metal oxide(s), the second metal oxide(s) can comprise (i) the same or different constituent compounds/elements of the first metal oxide(s) and/or (ii) the same or different relative proportions of the constituent compounds/elements of the first metal oxide(s). examples, the first metal oxide(s) can comprise approximately sixty percent zinc oxide and approximately forty percent indium oxide; meanwhile, the second metal oxide(s) can comprise indium oxide, gallium oxide, and zinc oxide in equal proportions to each other; or vice versa. In other examples, both the first and second metal oxide(s) can comprise zinc oxide and indium oxide with the second metal oxide having an approximately 60:40 ratio of zinc oxide to indium oxide and with the first metal oxide having an approximately 59:41 ratio of zinc oxide to indium oxide.

[00141] With respect to thickness, first constituent active layer 3156 can be greater than or equal to approximately 5 nanometers thick and less than or equal to approximately 40 nanometers thick. In further embodiments, first constituent active layer 3156 can be greater than or equal to approximately 5 nanometers thick and less than or equal to approximately 20 nanometers thick, such as, for example, approximately 20 nanometers thick. Meanwhile, second active layer 3157 can be greater than or equal to approximately 10 nanometers thick and less than or equal to approximately 45 nanometers thick, such as, for example, approximately 30 nanometers thick. In some embodiments, a combined thickness of first constituent active layer 3156 and second constituent active layer 3157 does not exceed approximately 50 nanometers.

[00142] The conductivity/resistivity first be than the can greater second conductivity/resistivity, or vice versa. For example, the first resistivity of first constituent active layer 3156 can comprise approximately 0.002 Ohm-centimeters. Further, the second conductivity/resistivity of second constituent active layer 3157 can comprise greater than or equal to approximately 10 Ohm-centimeters and less than or equal to approximately 200 Ohmcentimeters. Accordingly, in many examples, the second resistivity greatly exceeds the first resistivity. Correspondingly, the second conductivity can be less than the first conductivity. The greater conductivity of first constituent active layer 3156 versus second constituent active layer 3157 can result from second constituent active layer 3157 comprising a higher oxygen content than first constituent active layer 3156. As the oxygen content of second constituent active layer 3157 increases, so too can the resistivity of second constituent active layer 3157. The differential in the conductivities between first constituent active layer 3156 and second constituent active layer 3157 can greatly affect (e.g., reduce) the rate of change or shift in the threshold voltage of semiconductor device 1350 due to an applied gate voltage when compared to a similar semiconductor device that has a single active layer. A stable threshold voltage can permit semiconductor device 1350 to provide a repeatable signal. The manner of implementing second constituent active layer 3157 to comprise greater oxygen content than first constituent active layer 3156 is described in further detail below.

[00143] In many examples, implementing patterned active layer 1555 as multiple constituent active layers (e.g., first constituent active layer 3156 and/or second constituent active layer 3157) comprising metal oxides and/or different conductivities can provide improved mobility, on/off current ratio, and threshold voltage stability over implementing patterned active layer 1555 as (i) a single active layer, whether or not comprising amorphous silicon, and/or (ii) multiple constituent active layers comprising amorphous silicon and/or similar or identical conductivities. As a result, one or more electronic devices of semiconductor device 1350 can be fabricated smaller and/or with higher device resolution.

[00144] Referring now back to FIG. 15, as an example, patterned IMD layer 1556 can be deposited over patterned active layer 1555 by way of PECVD. Patterned IMD layer 1556 can comprise silicon nitride and/or silicon dioxide. In some examples, patterned IMD layer 1556 can be buffered with silicon nitride or other dielectrics on the side farthest from patterned active layer 1555. In other examples, when patterned active layer 1555 comprises a-Si and/or a-Si:H, patterned IMD layer 1556 can comprise hydrogenated silicon nitride. Further, patterned IMD layer 1556 can be greater than or equal to approximately 50 nanometers thick and less than or

equal to approximately 200 nanometers thick. For example, patterned IMD layer 1556 can be approximately 100 nanometers thick.

[00145] In some examples, gate dielectric 1554, patterned active layer 1555, and/or patterned IMD layer 1556 can all be deposited via PECVD using an AMAT P5000, manufactured by Applied Materials, Inc. of Santa Clara, California. In the same or different examples, the temperature at which gate dielectric 1554, patterned active layer 1555, and/or patterned IMD layer 1556 are deposited onto semiconductor device 1350 can be greater than approximately 180°C. For example, the temperature at which gate dielectric 1554, patterned active layer 1555, and/or patterned IMD layer 1556 are deposited onto semiconductor device 1350 can be greater than or equal to approximately 180°C and less than or equal to approximately 250°C. As an example, the temperature at which gate dielectric 1554, patterned active layer 1555, and patterned IMD layer 1556 are deposited onto semiconductor device 1350 can be from approximately 188°C to approximately 193°C. Furthermore, the deposition of gate dielectric 1554, patterned active layer 1555, and patterned IMD layer 1556 onto semiconductor device 1350 can be done at approximately vacuum.

In other examples, such as, for example, when patterned active layer 1555 comprises [00146] multiple constituent active layers (e.g., first constituent active layer 3156 (FIG. 31) and/or second constituent active layer 3157 (FIG. 31)), the multiple constituent active layers can be deposited via sputtering (as opposed to PECVD). In these examples, sputtering the first constituent active layer 3156 (FIG. 31) can comprise sputtering the first metal oxide(s) of first constituent active layer 3156 with a first feed gas comprising (i) argon and/or nitrogen and (ii) being approximately devoid of oxygen. Further, sputtering the second constituent active layer 3157 (FIG. 31) (e.g., over and/or on first constituent active layer 3156 (FIG. 31) can comprise sputtering the second metal oxide(s) of second constituent active layer 3157 with a second feed gas comprising (i) argon and/or nitrogen and (ii) oxygen. For example, the second feed gas can be greater than or equal to approximately 2 percent oxygen by volume and less than or equal to approximately 10 percent oxygen by volume. The threshold voltage shift of the semiconductor device(s) comprising patterned active layer 1555 can be reduced as a function of increasing the oxygen content of the second feed gas toward 10 percent oxygen by volume. In many examples, this improved voltage shift can be achieved with little or no measurable effect on other electrical properties (e.g., mobility, on/off current ratio, etc.) of the semiconductor device(s). Accordingly, the threshold voltage shift of the semiconductor device(s) comprising patterned active layer 1555 can be greater than or equal to -1 Volt and less than or equal to 1 Volt for a ±20 Volt direct current bias stress applied for 10,000 seconds.

[00147] In some examples, the second feed gas can comprise the first feed gas, such as, for example, when oxygen is combined with the first feed gas to form the second feed gas. Accordingly, in these or other examples, second constituent active layer 3157 can be deposited directly after first constituent active layer 3156 is deposited, such as, for example, where depositing first constituent active layer 3156 transitions directly into depositing second constituent active layer 3157 by selectively adding oxygen to the first feed gas when desirable. In this example, the chamber in which first and second constituent active layers 3156 and 3157 are deposited does not need to break vacuum between layers, and a single etch mask can be used to pattern both layers.

[00148] In many examples, the temperature at which first constituent active layer 3156 (FIG. 31) and/or second constituent active layer 3157 (FIG. 31) are deposited onto semiconductor device 1350 can be greater than or equal to approximately 25°C and less than or equal to approximately 39°C. Further, the deposition of first constituent active layer 3156 (FIG. 31) and/or second constituent active layer 3157 (FIG. 31) onto semiconductor device 1350 can be done at a pressure of greater than or equal to approximately 10 milliTorr and less than or equal to approximately 20 milliTorr, such as, for example, at a pressure of approximately 16 milliTorr. After gate dielectric 1554, patterned active layer 1555, and patterned IMD layer 1556 [00149] are deposited onto semiconductor device 1350, the resulting layers can be pattern etched. Prior to etching gate dielectric 1554, patterned active layer 1555, and patterned IMD layer 1556, the substrate assembly of activity 110 (FIG. 1), the gate metal layer of activity 1211, and the active stack of activity 1212 can be cleaned by a QDR activity with a suitable detergent followed by a SRD activity prior to performing activity 1212. An exemplary detergent can comprise Alconox Detergent 8, manufactured by Alconox, Inc. of White Plains, New York, (e.g., 40 mL) mixed with one liter of water. The cleaning can be performed in a megasonic cleaning tank. In many examples, gate dielectric 1554 can provide an etch stop for the patterned etches of patterned active layer 1555 and/or patterned IMD layer 1556.

[00150] In some examples, patterned IMD layer 1556 can be etched using a 10:1 buffered oxide etch (BOE), such as, for example, when patterned IMD layer 1556 comprises silicon nitride. In other examples, patterned IMD layer 1556 can be etched using a dry etchant, such as, for example, when patterned IMD layer 1556 comprises silicon dioxide. For example, the dry etchant can comprise oxygen, hydrogen chloride, and methane. Further, the oxygen, hydrogen chloride, and methane can comprise ten, one hundred, and twenty parts per volume, respectively. Meanwhile, gate dielectric 1554 and patterned active layer 1555 can be etched in similar or identical manner to and/or as part of the etching of ITO layer 2667 (FIG. 26), as

described below. For example, gate dielectric 1554 and patterned active layer 1555 can be etched using a reactive ion etcher, such as, for example, an AMAT 8330. In some examples, patterned IMD layer 1556 and patterned active layer 1555 can be etched so that patterned active layer 1555 is exposed, i.e., patterned active layer 1555 is not completely covered by patterned IMD layer 1556. Where patterned active layer 1555 comprises multiple constituent active layers (e.g., first constituent active layer 3156 (FIG. 31) and second constituent active layer 3157 (FIG. 31)), each of the multiple constituent active layers can be etched (i) immediately sequentially and/or (ii) separately, such as, for example, (a) the etch can be performed after each layer of the multiple constituent active layers is deposited or (b) the etch can be performed for each layer of the multiple constituent active layers after all of the multiple constituent active layers are deposited so that they are etched in the reverse order of deposition.

[00151] In many examples, the active stack of activity 1212 can comprise a layer-to-layer registration error of less than or equal to approximately 1 pixel per million. Further, the active stack of activity 1212 can comprise a change in wafer bow of between approximately  $\pm 5$  microns.

[00152] Referring again to FIG. 12, activity 1112 can comprise activity 1213 of providing a mesa passivation layer. Prior to performing activity 1213, the substrate assembly of activity 110 (FIG. 1), the gate metal layer of activity 1211, and the active stack of activity 1212 can be cleaned by a QDR activity with a suitable detergent followed by a SRD activity. An exemplary detergent can comprise Alconox Detergent 8, manufactured by Alconox, Inc. of White Plains, New York, (e.g., 40 mL) mixed with one liter of water. The cleaning can be performed in a megasonic cleaning tank. Additionally or alternatively, the substrate assembly of activity 110 (FIG. 1), the gate metal layer of activity 1211, and the active stack of activity 1212 can be cleaned with a solution of ammonium hydroxide and water in ratio of one part to ten parts, respectively. FIGs. 17 and 18 illustrate an example of semiconductor device 1350 after providing a mesa passivation layer, according to the embodiment of FIG. 1.